Manufacturing method of three-dimensional array grid-last type Si-NWFET (Nanowire Field Effect Transistor) based on SOI (Silicon On Insulator)

A technology of three-dimensional arrays and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, nanotechnology for information processing, electrical components, etc., can solve problems such as inconvenience, unsuitability for field-effect transistor gate oxide layers, and large interface states. Achieve the effects of simplifying the process, increasing the number of nanometer lines, and increasing the current driving capability of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0068] First, if Figure 22 As shown, in order to describe this embodiment more clearly, define the fin-shaped active region or the length direction of the subsequently formed silicon nanowire as XX' direction, XX' direction runs through the gate and source and drain regions, and is perpendicular to X-X' direction is Y-Y' direction. Combine below Figures 1 to 22 Describe in detail the method for manufacturing a bulk silicon-based three-dimensional array Si-NWFET according to an embodiment of the present invention, specifically including:

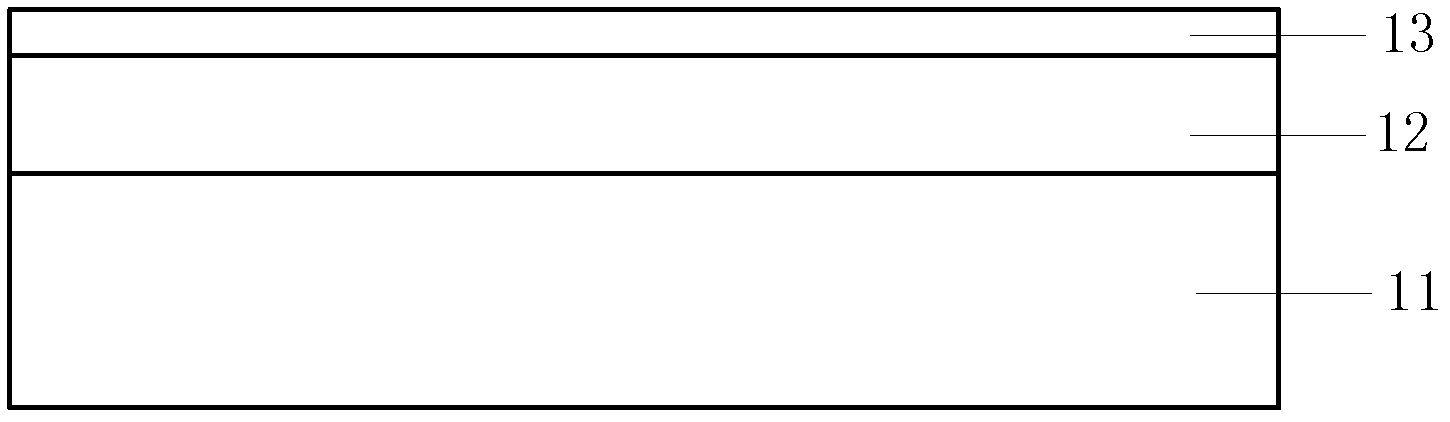

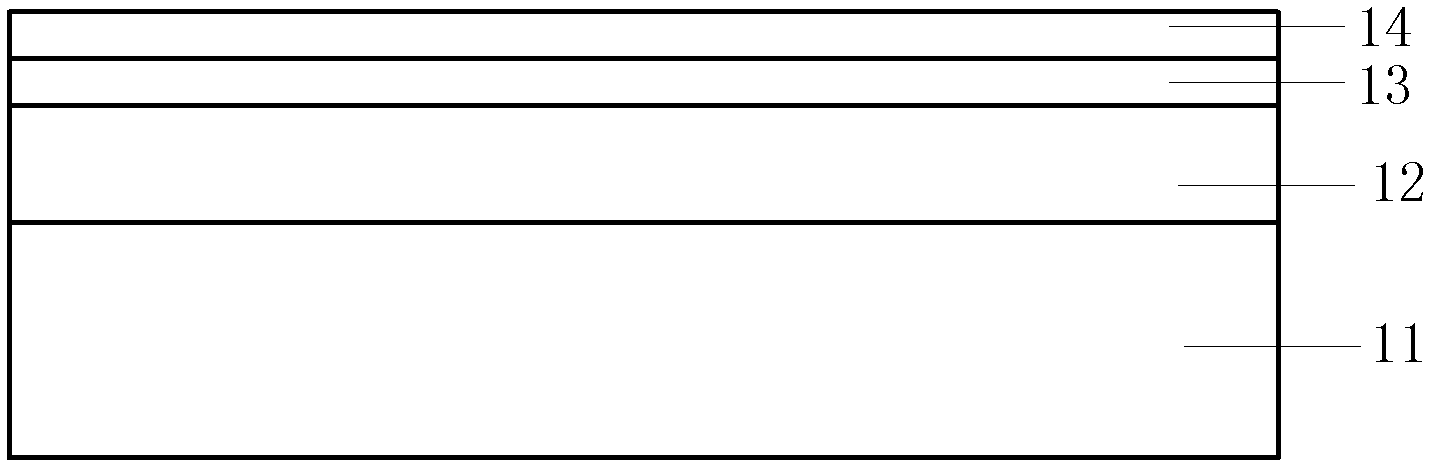

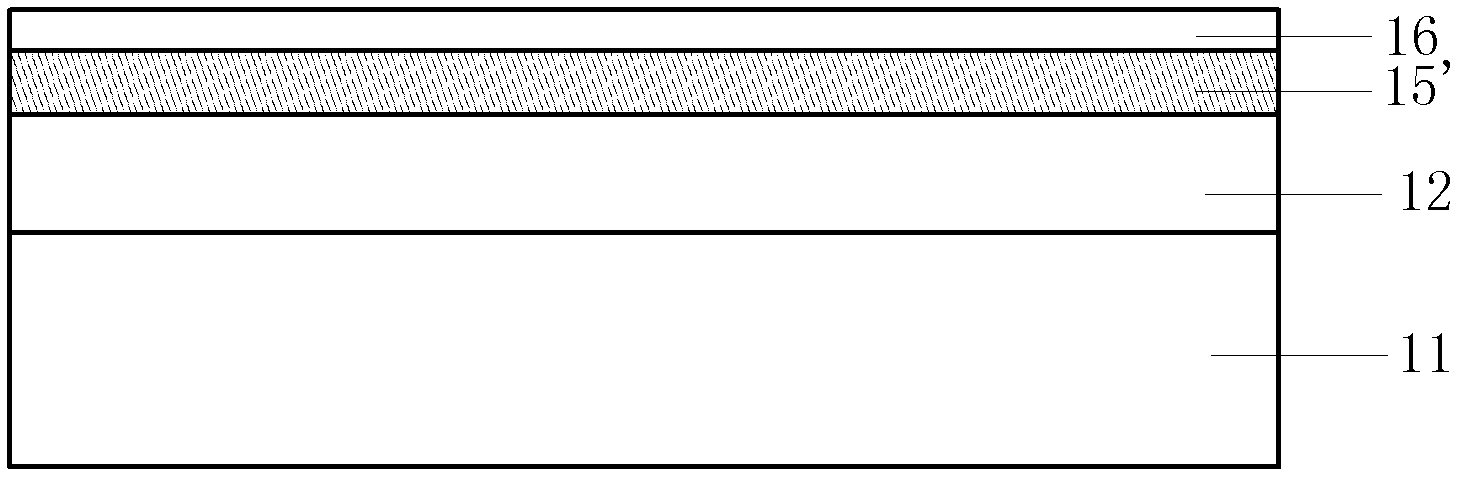

[0069] Please refer to figure 1 , provide an SOI substrate, the bottom layer of the SOI substrate is a silicon liner 11 for providing mechanical support, an insulator layer is provided on the sil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More