MSD integrated circuits with shallow trench

a technology of integrated circuits and trenches, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, diodes, etc., can solve the problems of high gate charge, poor performance, and high manufacturing cost of conventional deep gate trenches, so as to reduce the space occupied and improve the effect of performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0027]FIG. 5B is another cross-section C-D of the first embodiment as shown in FIG. 5C. The only difference between FIG. 5B and FIG. 5A is that there is an open area 250 of the drain metal on the top of the termination. A conventional metal field plate in the termination is provided to sustain breakdown voltage.

[0028]FIG. 5C is a top view of the first embodiment which shows Gate-Drain diode across termination with the open areas 250 in FIG. 5B of the drain metal. These open areas allow electrical field penetrate through the oxides during avalanche, and thus make benefits to avoid avalanche degradation caused by the metal field plate cross over the termination as shown in FIG. 5A.

[0029]FIG. 6 is a normalized measurement result of the relationship between breakdown voltage and metal width cross over metal field plate termination, which shows that breakdown voltage will be degraded when metal width W is greater than 5 um, It means that electrical field underneath the cross-over metal c...

second embodiment

[0030]FIG. 7A is the cross-section A-B of the present invention. The only difference between the structure of FIG. 7A and FIG. 5.A is that the embedded Schottky rectifier is a trench Schottky rectifier instead of junction barrier Schottky rectifier. The trench Schottky contact trench 272 is formed in said N epitaxial layer and other contact trench 271 formed in the trench gate 270 adjacent to said contact trench.

[0031]FIG. 7B is another cross-section C-D of the second embodiment. The only difference between FIG. 7B and FIG. 7A is that there is an open area 251 of the drain metal on the top of the termination.

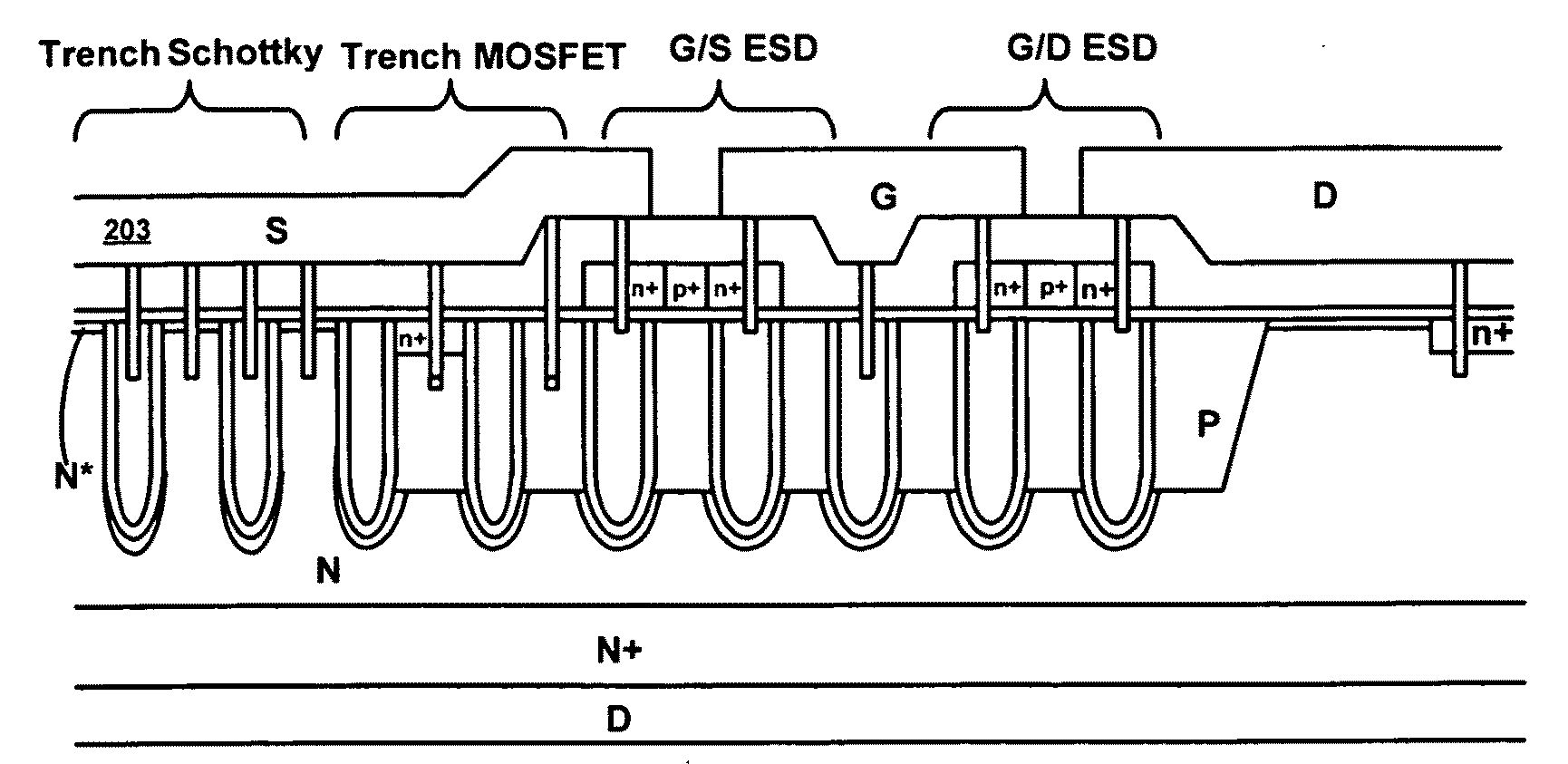

[0032]FIGS. 8A to 8D is a serial of exemplary steps that are performed to form the inventive device configuration of FIG. 7A. FIG. 8A shows that an N doped epitaxial layer 200 is grown on an N+ doped substrate 201. A trench mask (not shown) is applied to open a plurality of trenches by employing a dry silicon etch process. In order to remove the plasma damage introduced in etchi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More