Plasma for patterning advanced gate stacks

a technology of advanced gate stacks and plasma, which is applied in the direction of basic electric elements, semiconductor/solid-state device manufacturing, electrical equipment, etc., can solve the problems of incompatibility of stack materials, gate profiles that cannot be re-arranged, and none of them can achieve the effect of preserving the vertical profile of the gate stack after patterning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

Application of BCl3 / N2 Plasma for TaN Gate Profile Control

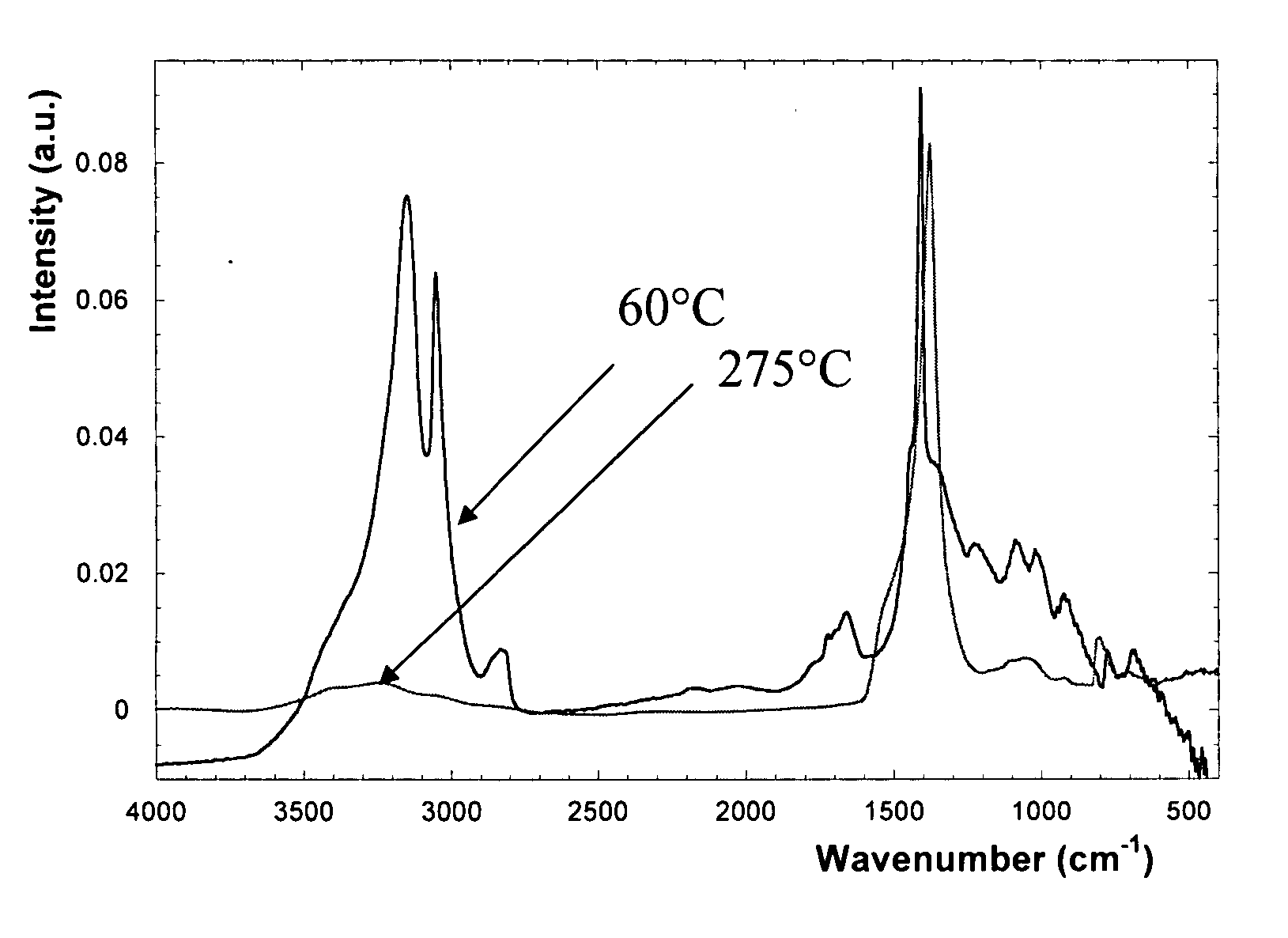

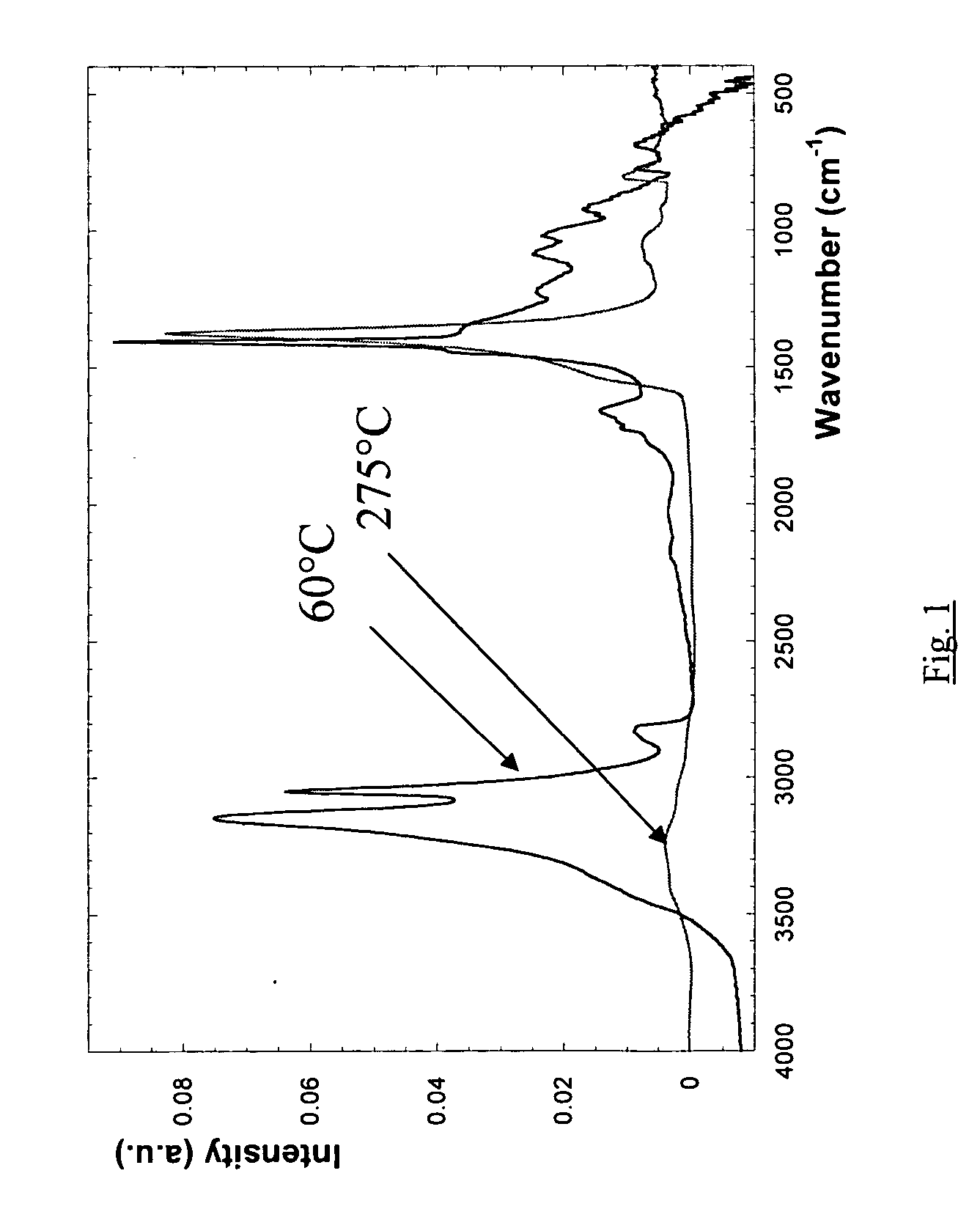

[0093] The BCl3 / N2 plasma was used to etch TaN metal gates, in the example presented here said TaN metal gate is present in a TiN / TaN gate stack where 15 nm TaN is in the contact with the gate dielectric and 70 nm TiN covers the TaN or in other words 70 nm TiN is situated on top of said 15 nm TaN.

[0094] The most critical step is TaN etching after TiN patterning. BCl3 plasma is used here for the TaN patterning as it is selective to the Si substrate and can be used as high-k removal as well.

[0095] If TaN is etched with pure BCl3 plasma, then a notch (lateral attack) is observed in the TaN layer.

[0096]FIG. 4A shows the gate profile after etching in pure BCl3, an arrow indicates the lateral attack of TaN.

[0097] The addition of 5% of N2 to the BCl3 plasma resulted in a straight TaN profile without the lateral attack of the TaN layer.

[0098] The effect of N2 addition is illustrated in FIG. 4B. A BxNy comprising passivation lay...

example 2

Application of BCl3 / N2 Plasma for Pure Ge Gate Profile Control

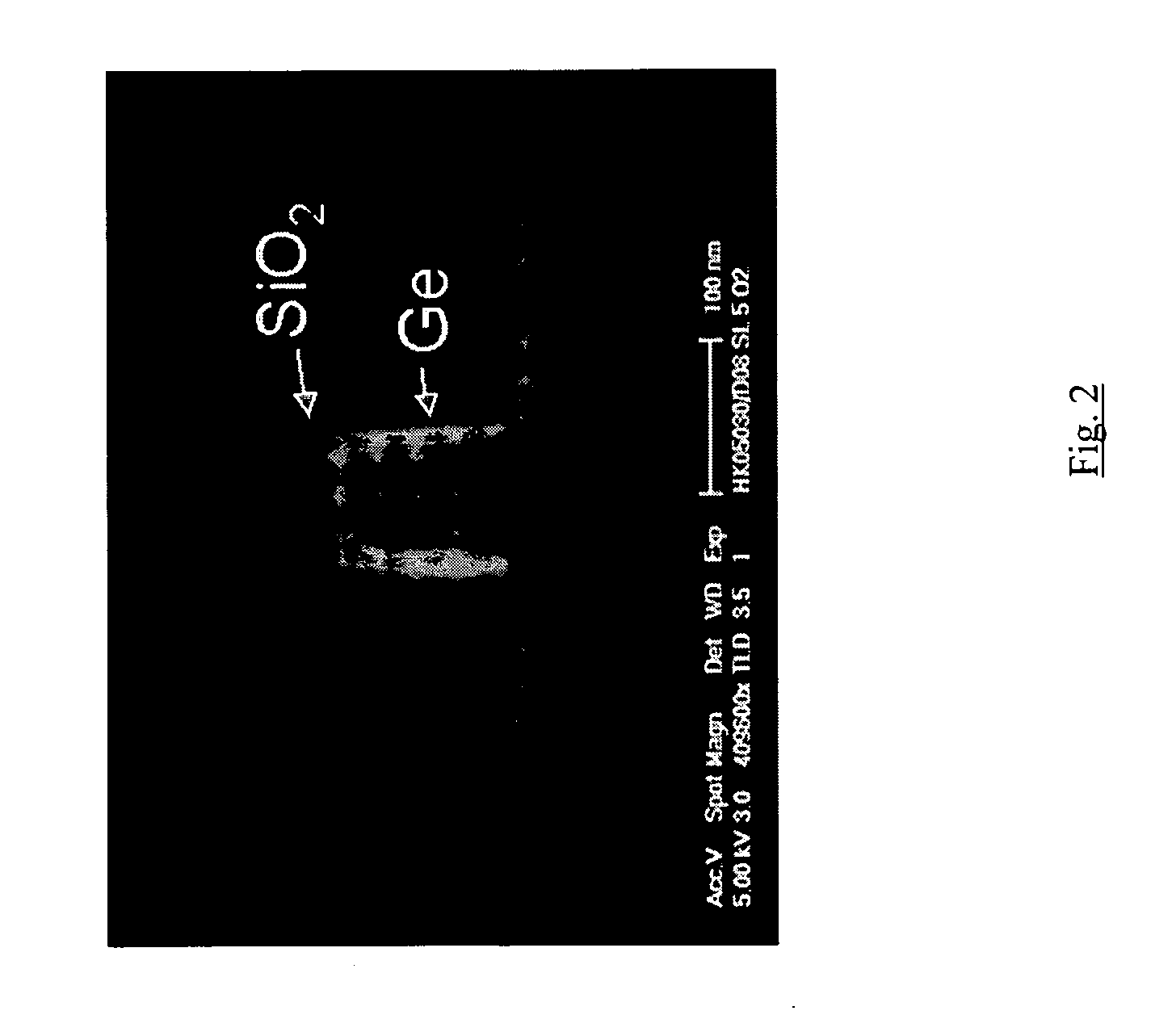

[0103] The BCl3 / N2 plasma was used to pattern pure Ge gates having a high-k dielectric underneath (in the presented case the high-k dielectric is HfO2). The high-k dielectric must be removed selectively to the underlying Si substrate.

[0104] The Ge gate profile just after patterning and before high-k removal as shown in FIG. 2 is straight.

[0105] The conventional way of HfO2 removal is etching in BCl3 plasma. If high-k is removed by such plasma, the Ge gate suffers from profile distortion while addition of 10% N2 to the BCl3 plasma preserves the profile even if the removal time is doubled as shown in FIG. 3.

[0106]FIG. 3A shows the Ge gate profile after high-k removal by a pure BCl3 plasma for 10 seconds and FIG. 3B shows the Ge gate profile after high-k removal by a BCl3 / N2 (10% N2) plasma for 20 seconds. No lateral attack of the Ge profile is seen in FIG. 3B.

[0107] It can be concluded that addition of small amounts of...

example 3

Plasma Parameters Used to Deposit a BxNy Passivation Film

[0108] The plasma parameters used for the deposition of a BxNy passivation film during TaN metal gate patterning as presented in Example 1 using a plasma of a preferred embodiment are as follows: pressure 0.666 Pa (5 mT), plasma power 450 W, flow BCl3 95 sccm (standard centimeter cube per minute), flow N2 5 sccm, and substrate bias 55V.

[0109] The plasma parameters used for the deposition of a BxNy passivation film during high-k removal in a Ge gate stacks as presented in Example 2 are as follows: pressure 0.666 Pa (5 mT), plasma power 450 W, substrate bias 30V, BCl3 90 sccm, N2 10 sccm.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More