Circuit substrate for packaging semiconductor device, method for producing the same, and method for producing semiconductor device package structure using the same

a semiconductor device and circuit substrate technology, applied in the direction of transportation and packaging, layered products, chemical instruments and processes, etc., can solve the problems of reducing the performance of a semiconductor circuit, failures, or breakages, and the diameter of solder bumps is so large, so as to achieve high productivity, prevent degradation, and high productivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiments

Embodiment 1

[0098]FIG. 11 shows a schematic section of a package structure for a semiconductor device 5 used in a test that will be described below, i.e., a structure in which bump electrodes of the semiconductor device 5 are mounted on input / output terminal electrodes of a circuit substrate, with junction layers between, and which structure is reinforced with a sealing resin.

[0099] In Embodiment 1, Au bumps formed as the bump electrodes by performing a wire bonding method were mounted on the input / output terminal electrodes of the circuit substrate through conductive adhesive as the junction layers, and sealing with an epoxy sealing resin was executed.

[0100] In conventional example 1, Ni—Au electroless plated bumps were used as bump electrodes, solder was used as junction layers, and an ultraviolet curing epoxy resin was used as a sealing resin.

[0101] In each of Embodiment 1 and conventional example 1, a package structure for an n-channel MOS transistor was produced, and deteri...

embodiment 2

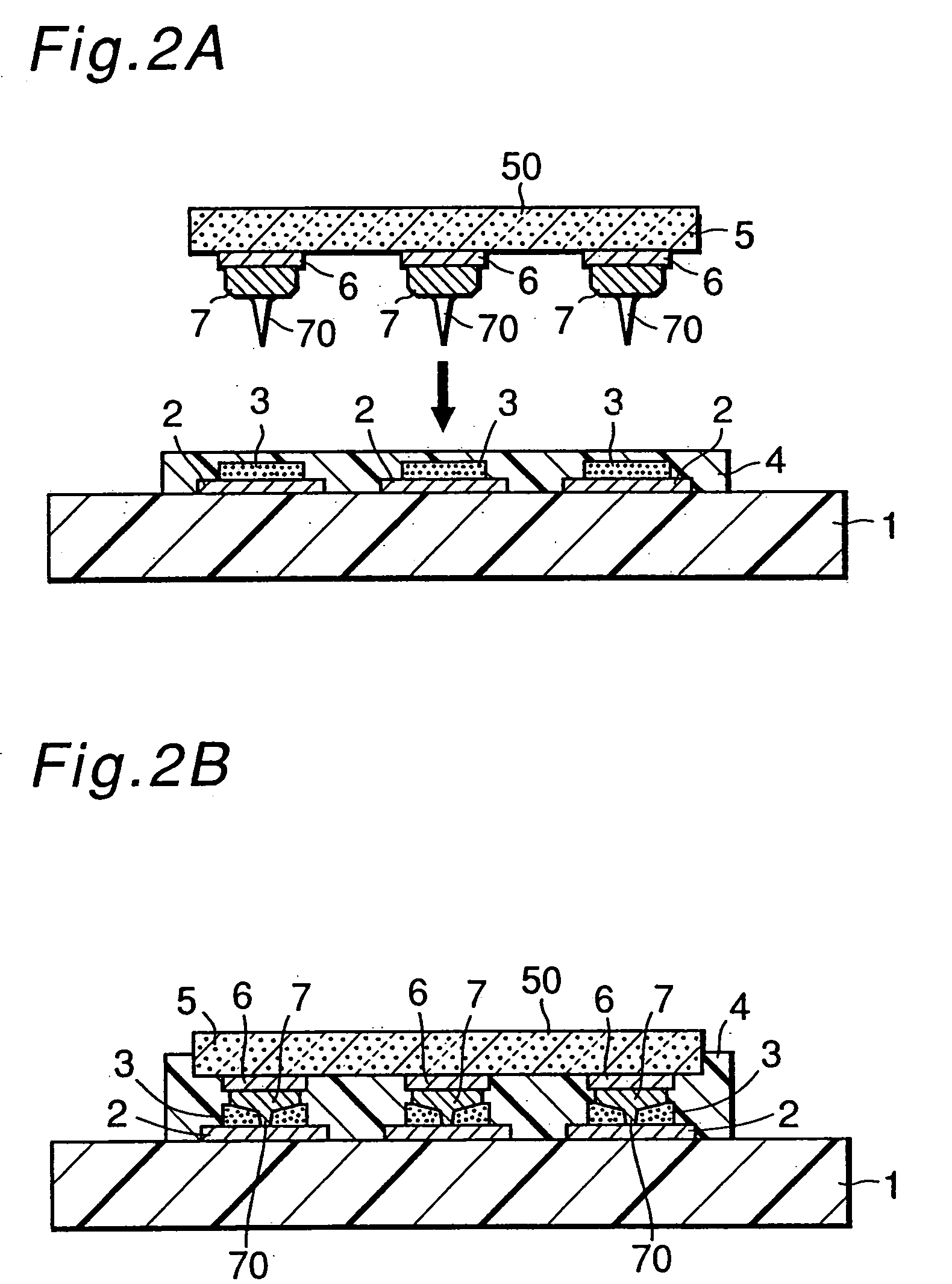

[0111] Packaging tests were conducted with use of a circuit substrate of the invention. A circuit substrate having a glass-epoxy main body (FR4) was used, and the package structure shown in FIGS. 2A and 2B was tested. An epoxy resin film having a thickness of 50 μm was attached to a surface of the main body of the circuit substrate, including top surfaces of input / output terminal electrodes.

[0112] As bump electrodes of a semiconductor device, Au bumps with a size of its pointed head being 20 square μm were formed according to a wire bonding method. In a mounting structure, semiconductor device 5 had the bump electrodes on a chip pressed against and connected to the input / output terminal electrodes of the circuit substrate having the resin film previously bonded to the main body thereof, and the structure was reinforced by sealing resin filled into a space between the resin film and the chip. Tests were conducted with a variation of loads for pressing the bump electrodes of the semi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More