Semiconductor device and method of manufacturing the same

a semiconductor device and manufacturing method technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of difficult to apply this manufacturing method to a semiconductor device that requires high-speed operation, difficult to obtain a semiconductor device suitable for high-speed operation, and a possible problem of interconnect length of 2 to 3 mm, so as to reduce the path length of signals transmitted, prevent metal contamination, and reduce the effect of path length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The invention will be now described herein with reference to illustrative embodiments. Those skilled in the art will recognize that many alternative embodiments can be accomplished using the teachings of the present invention and that the invention is not limited to the embodiments illustrated for explanatory purposes.

[0050] Hereafter, preferable embodiments of a semiconductor device and a method of manufacturing the same according to the present invention will be described in detail with reference to the attached drawings. Here, in the description of the drawings, the same elements will be denoted with the same reference numerals, and the description thereof will not be repeated.

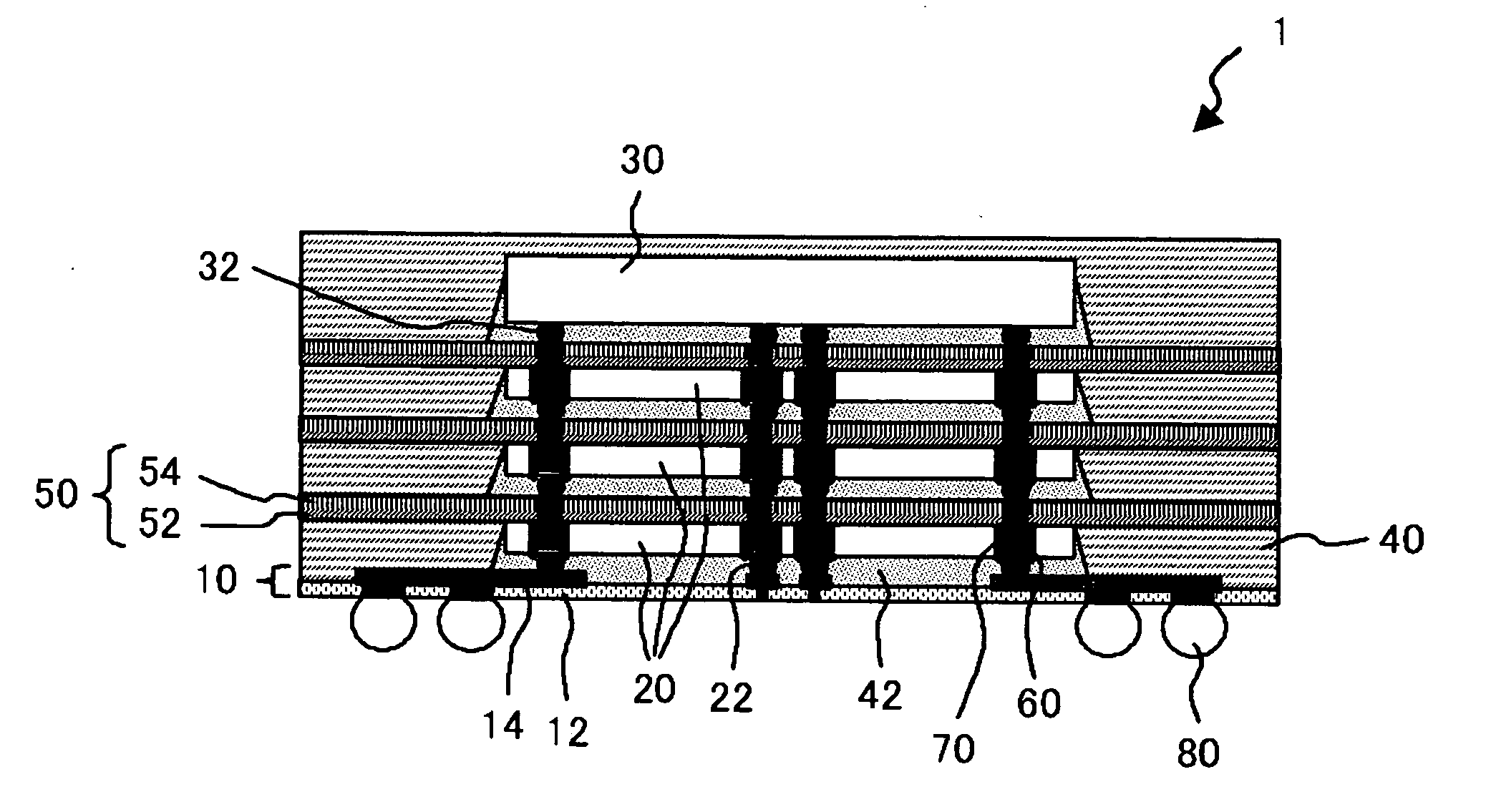

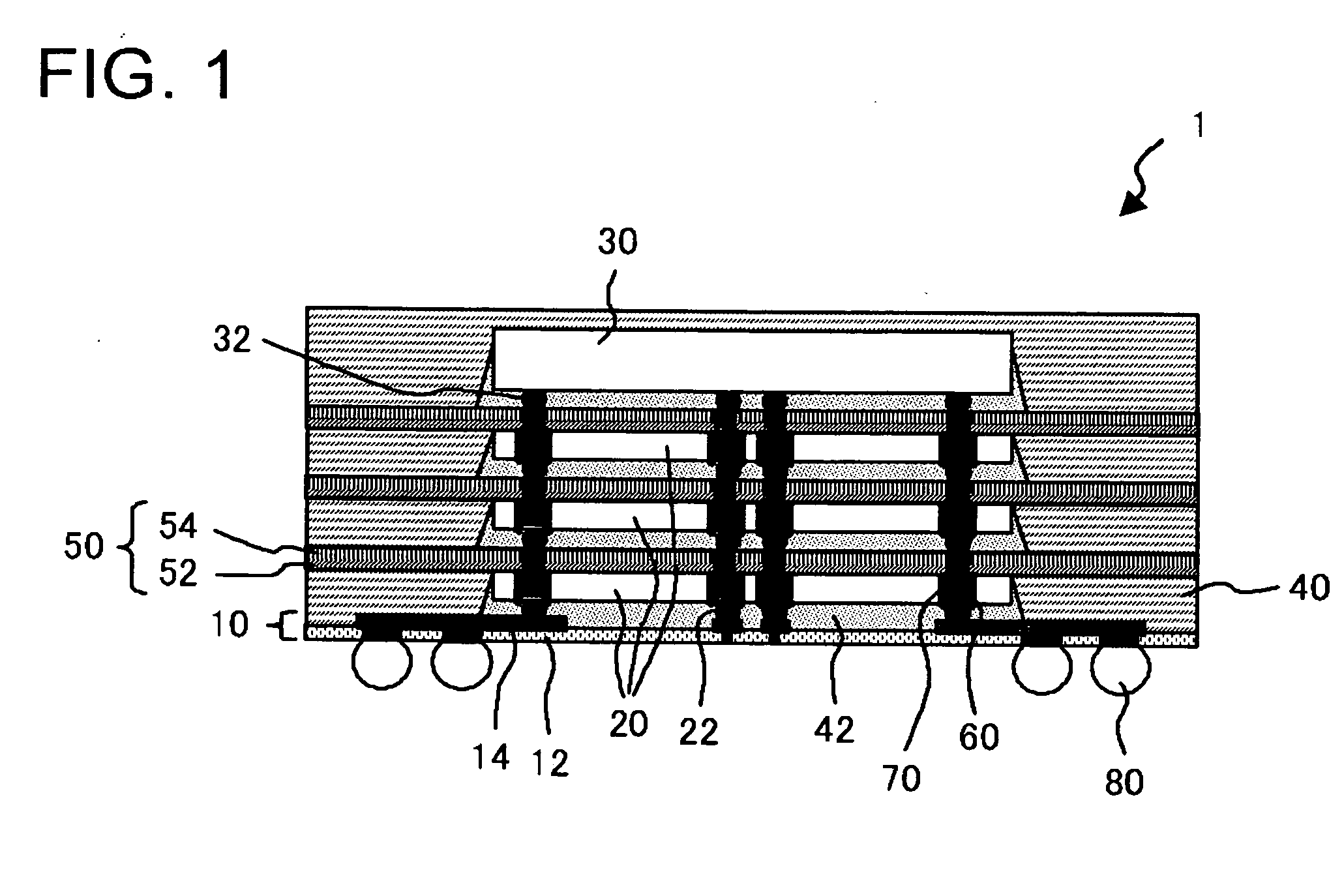

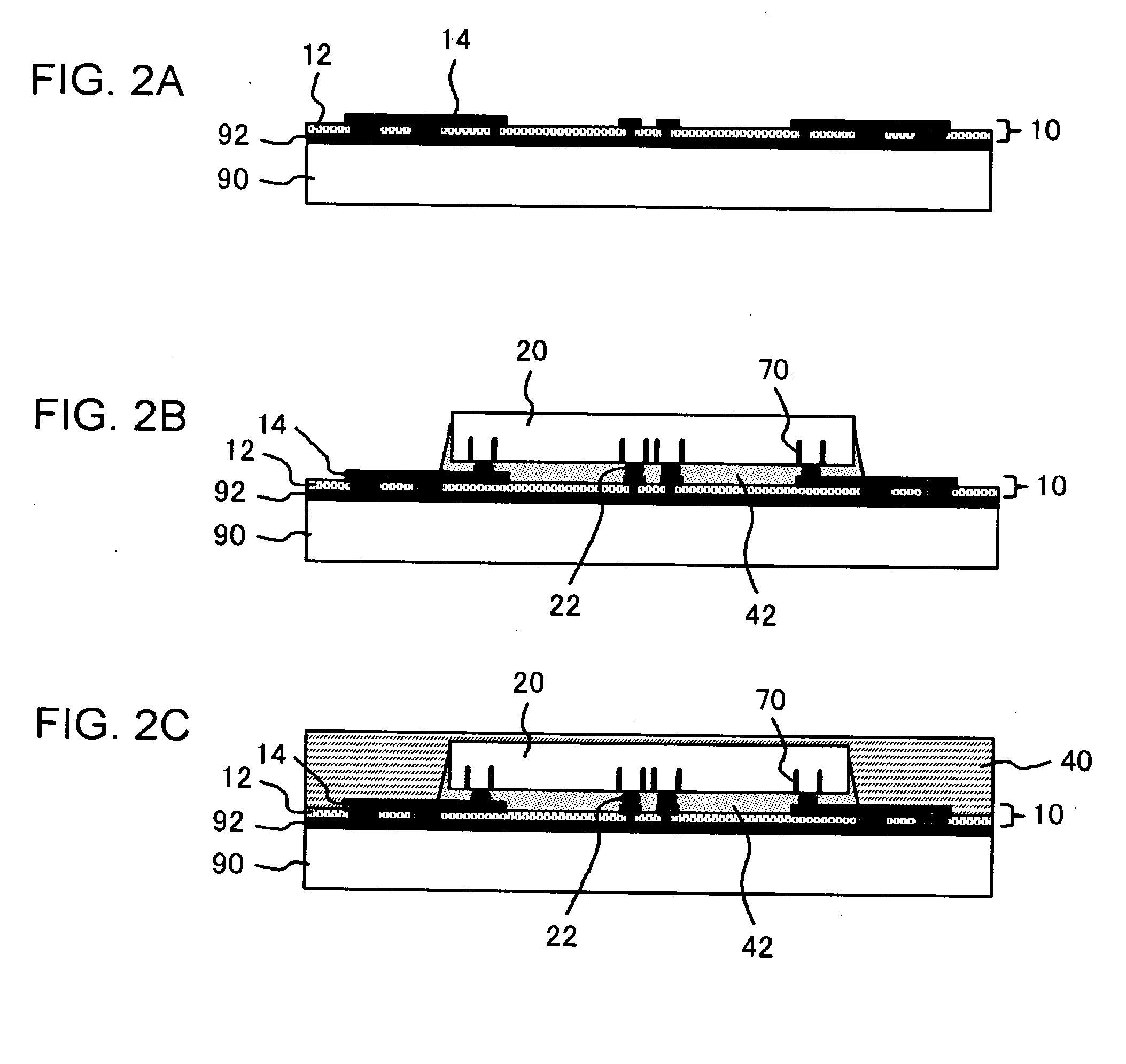

[0051]FIG. 1 is a cross-sectional view illustrating an embodiment of a semiconductor device according to the present invention. The semiconductor device 1 includes an interconnect member 10, a semiconductor chip 20 (first semiconductor chip), a semiconductor chip 30 (second semiconductor chip), a r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More