Patents

Literature

50results about How to "Large processing window" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

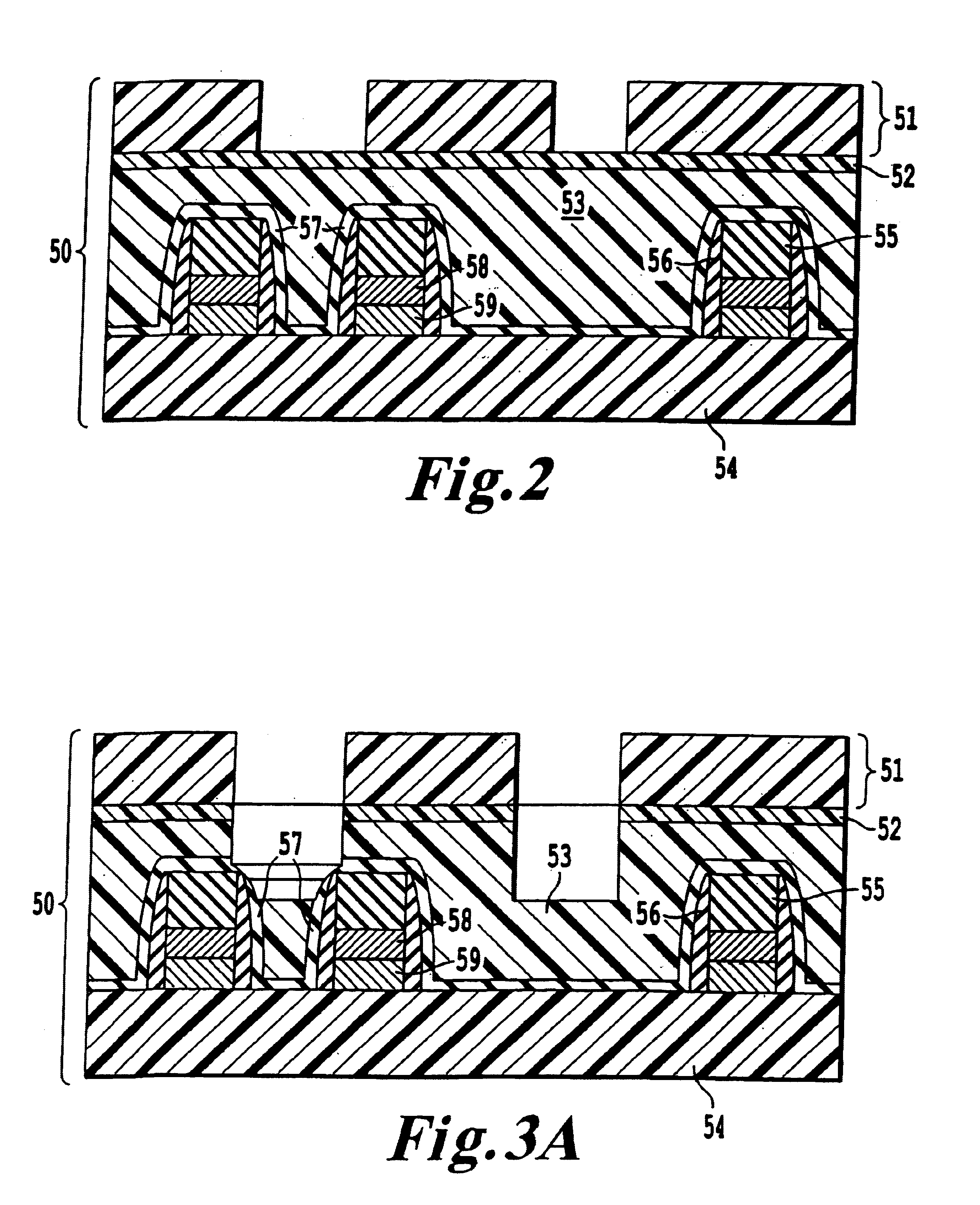

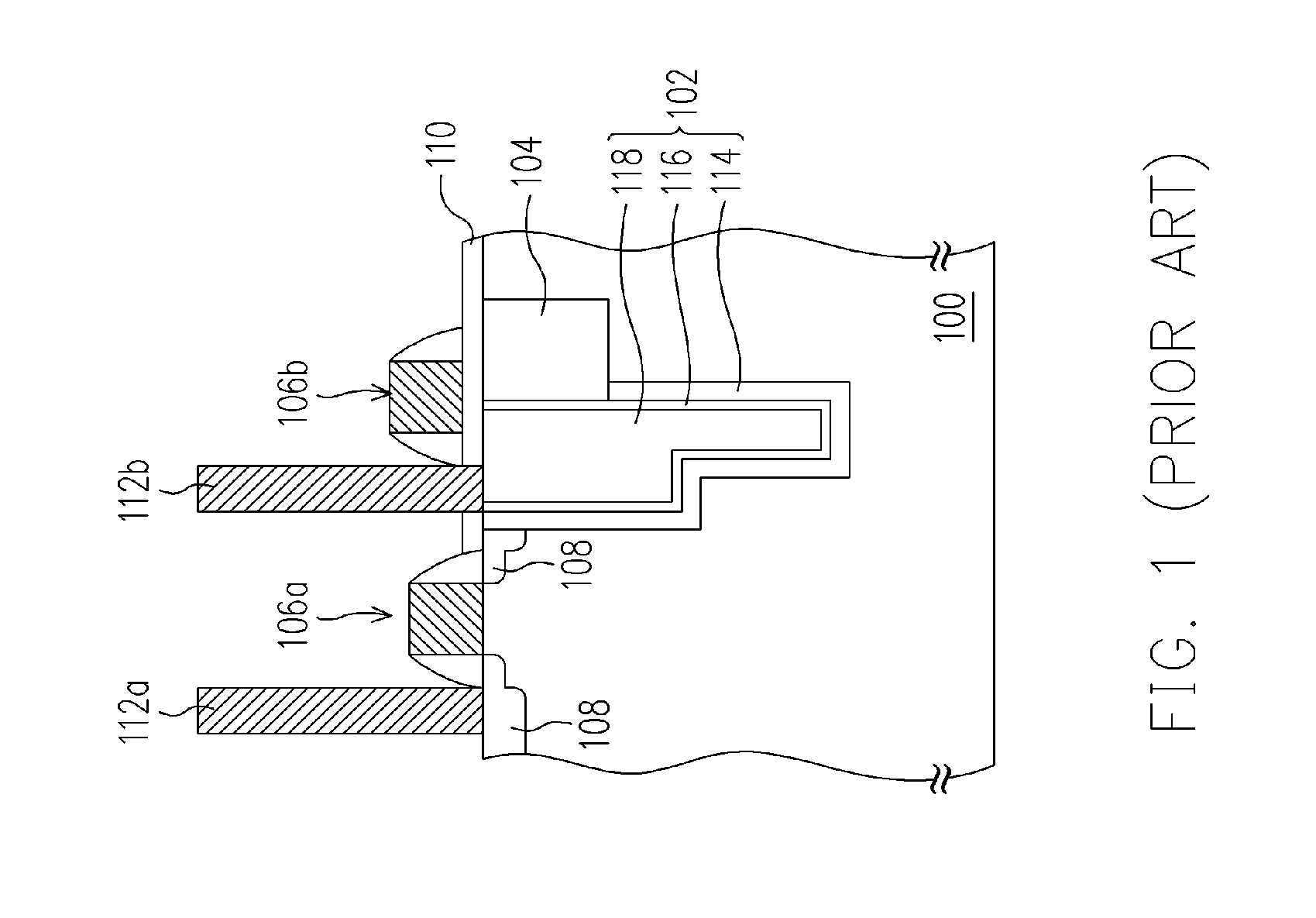

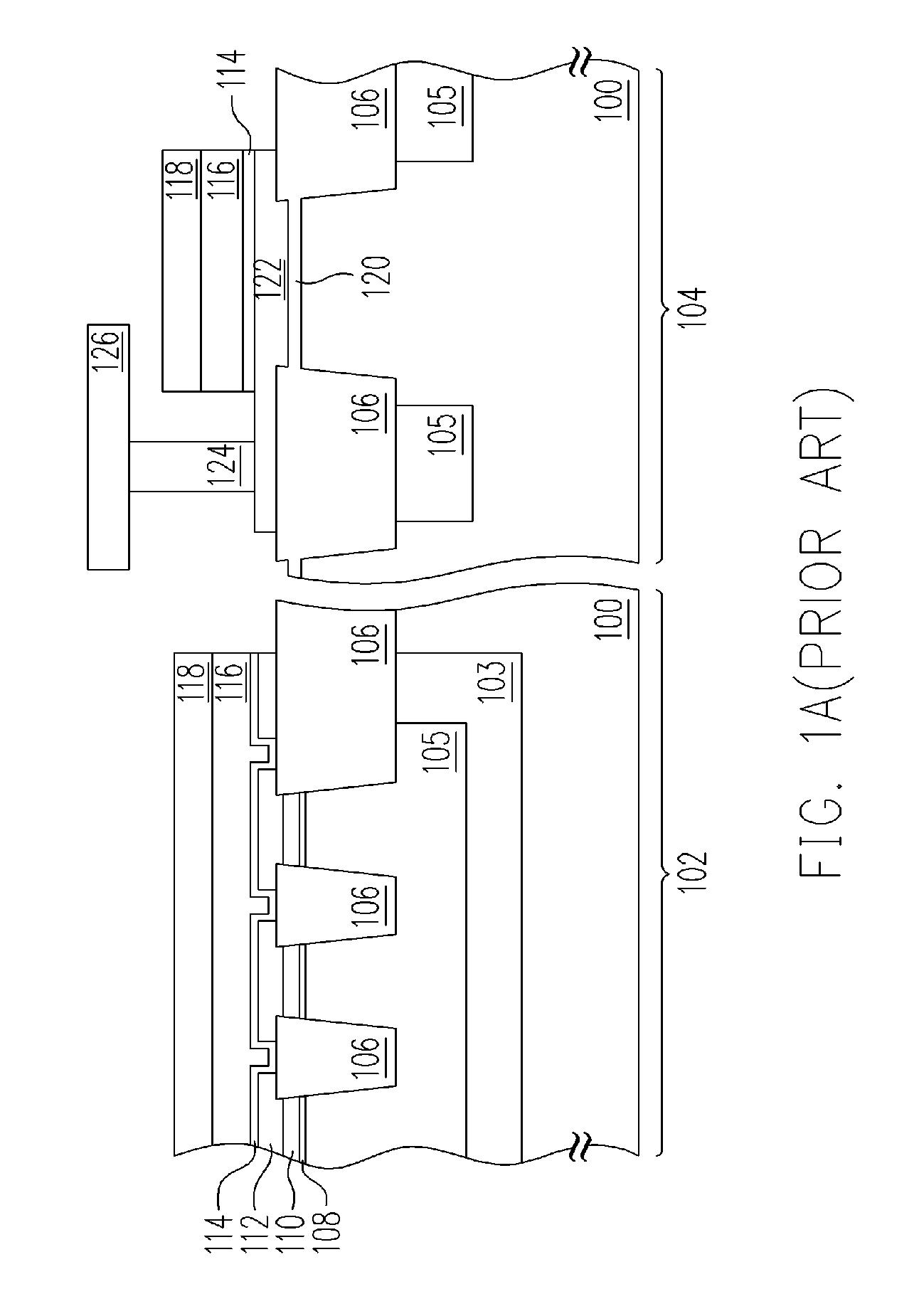

Method for preventing the etch transfer of sidelobes in contact hole patterns

InactiveUS6905621B2Inhibit transferLarge processing windowDecorative surface effectsPhotomechanical apparatusPhotoresistResist

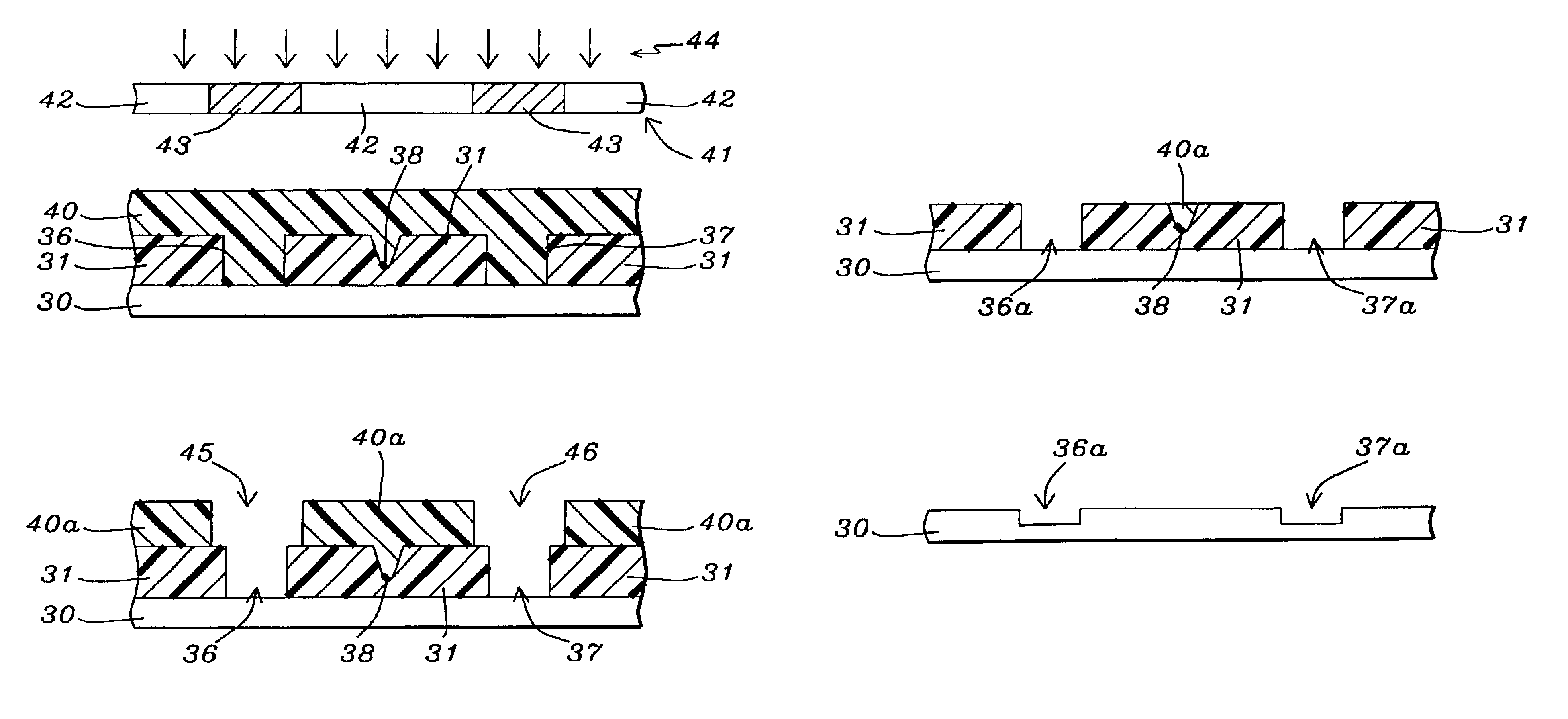

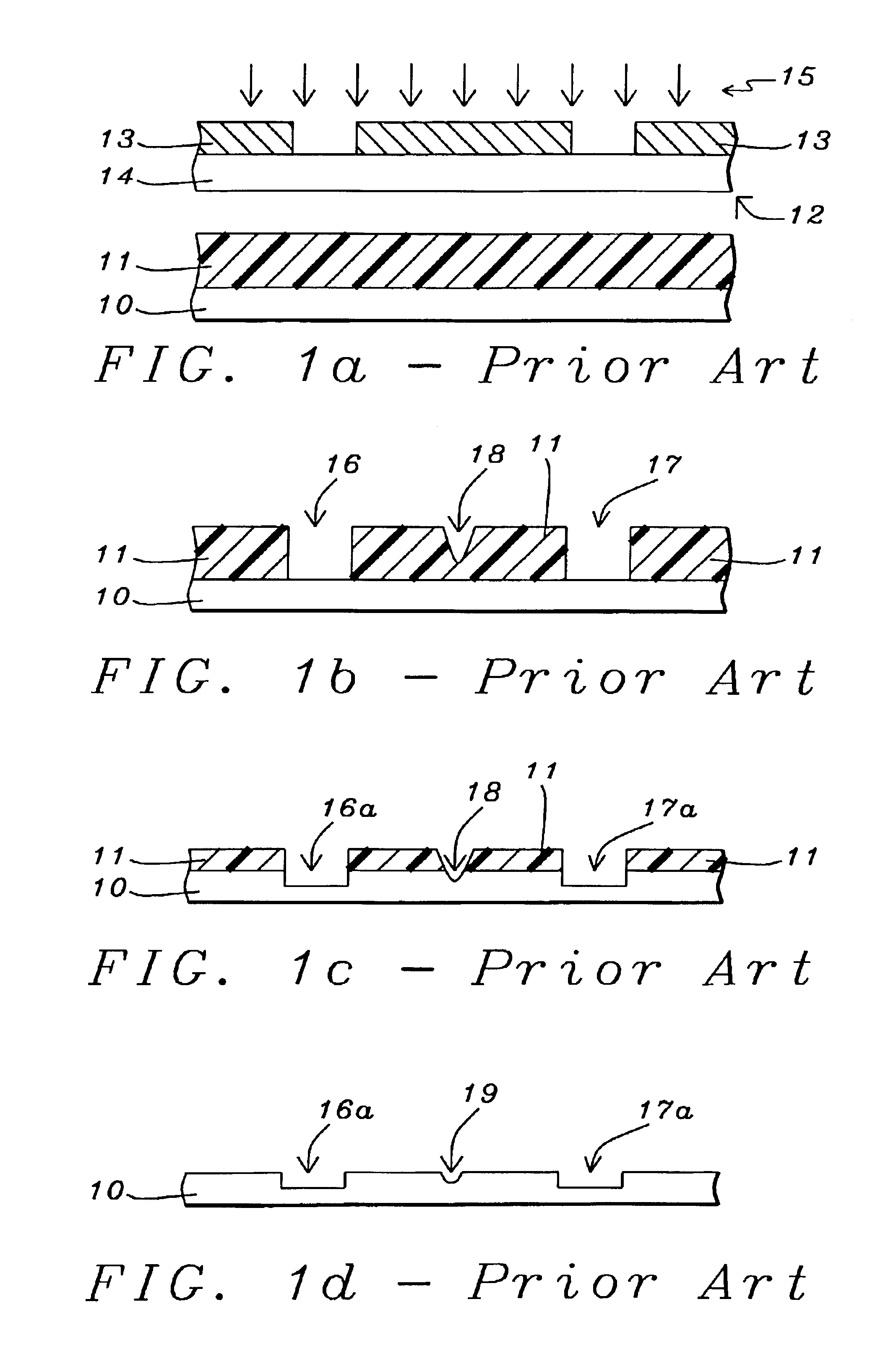

A method is provided for removing sidelobes that are formed when patterning a positive photoresist layer with an Att. PSM, Alt. PSM or a binary mask with scattering bars. A water soluble negative tone photoresist is coated over the positive photoresist pattern and is exposed through a mask having small islands that correspond in shape, size and location to the small holes in the mask used to pattern the positive tone photoresist. After development, exposed negative tone photoresist covers sidelobes formed by the positive tone process. The negative tone photoresist functions as a mask for a subsequent etch transfer of the positive tone pattern into the substrate. A method of aligning openings in a positive tone pattern over the same openings in a negative tone pattern is also useful in preventing sidelobes in the positive tone photoresist from being transferred into the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

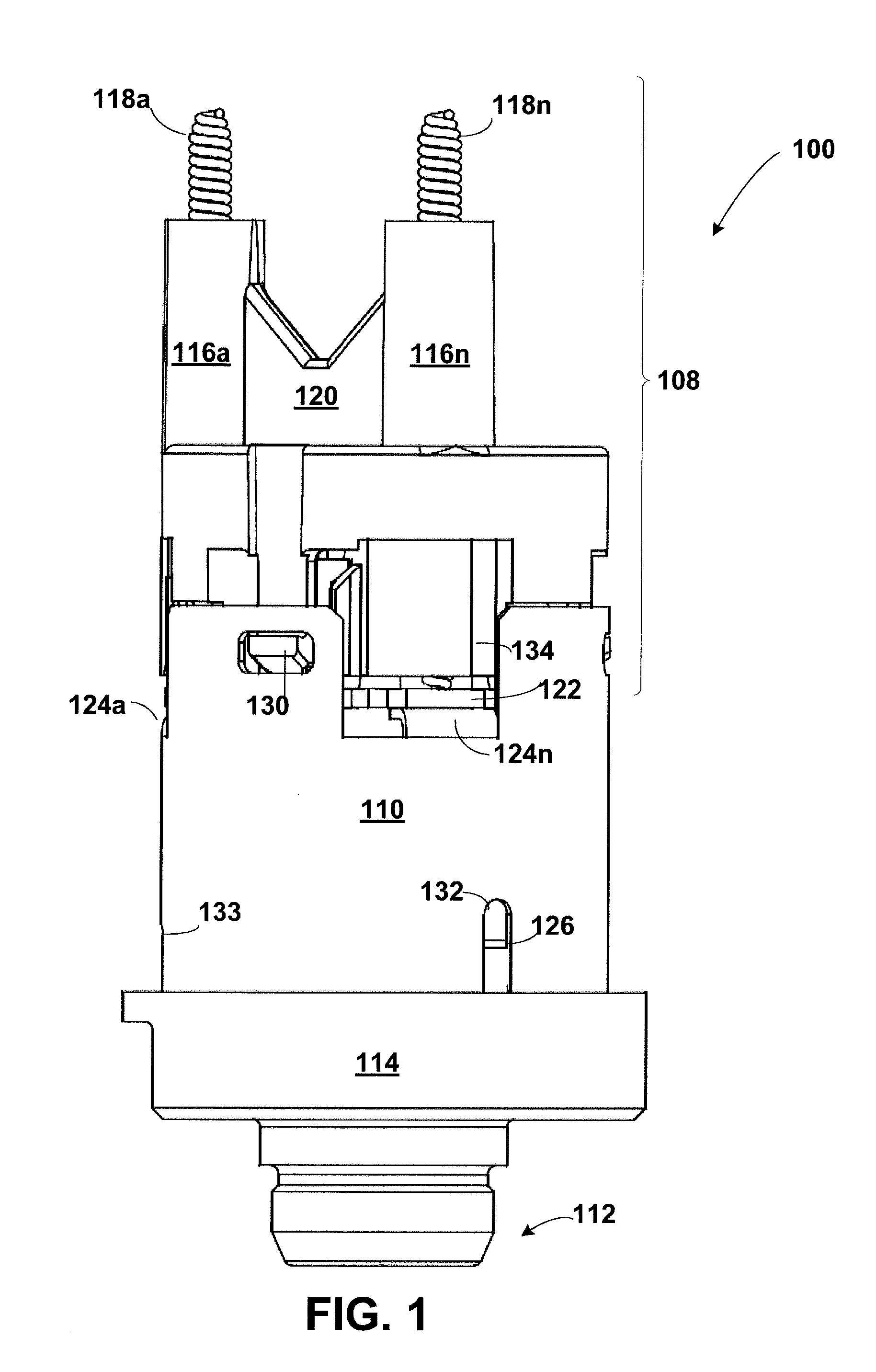

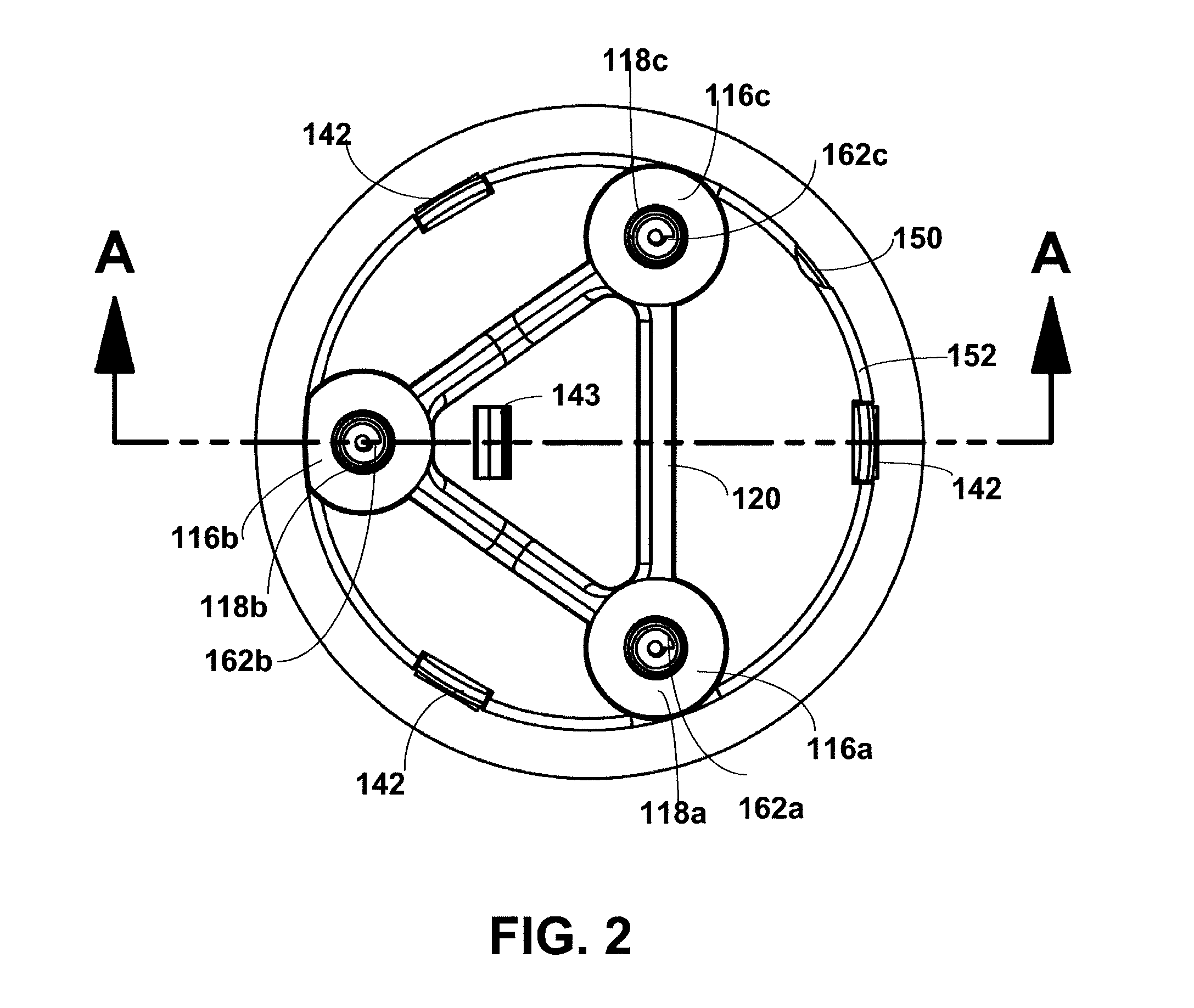

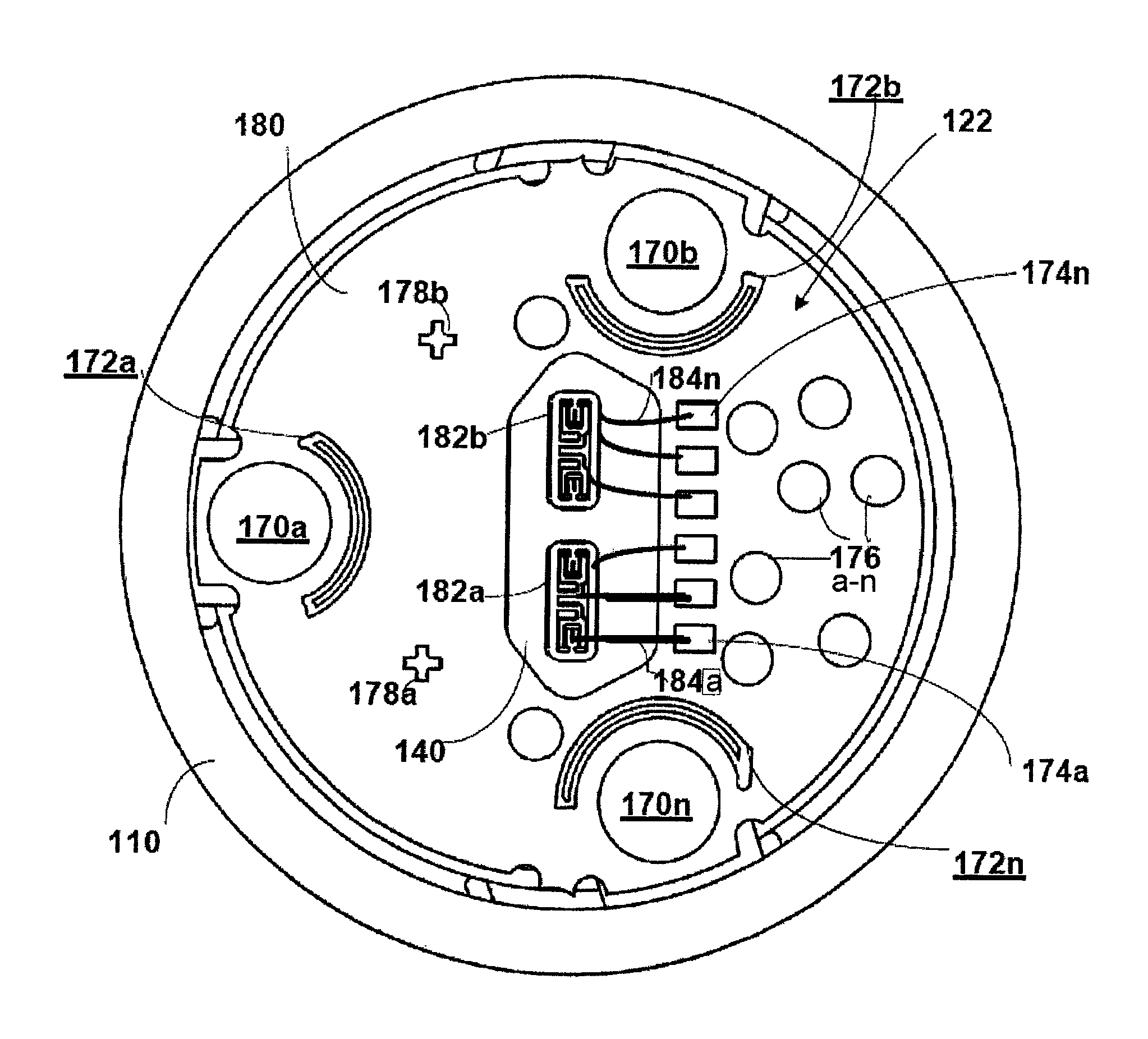

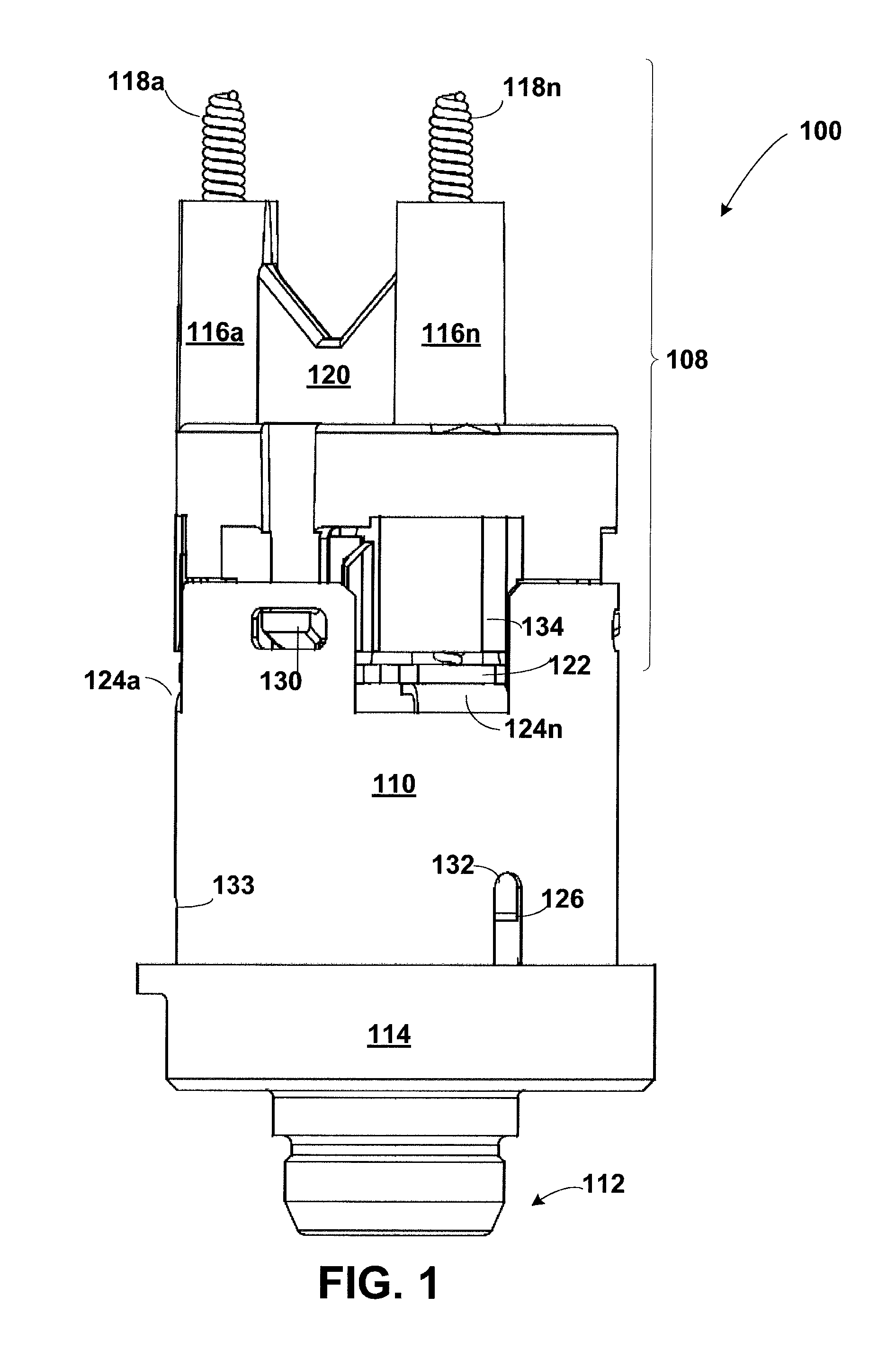

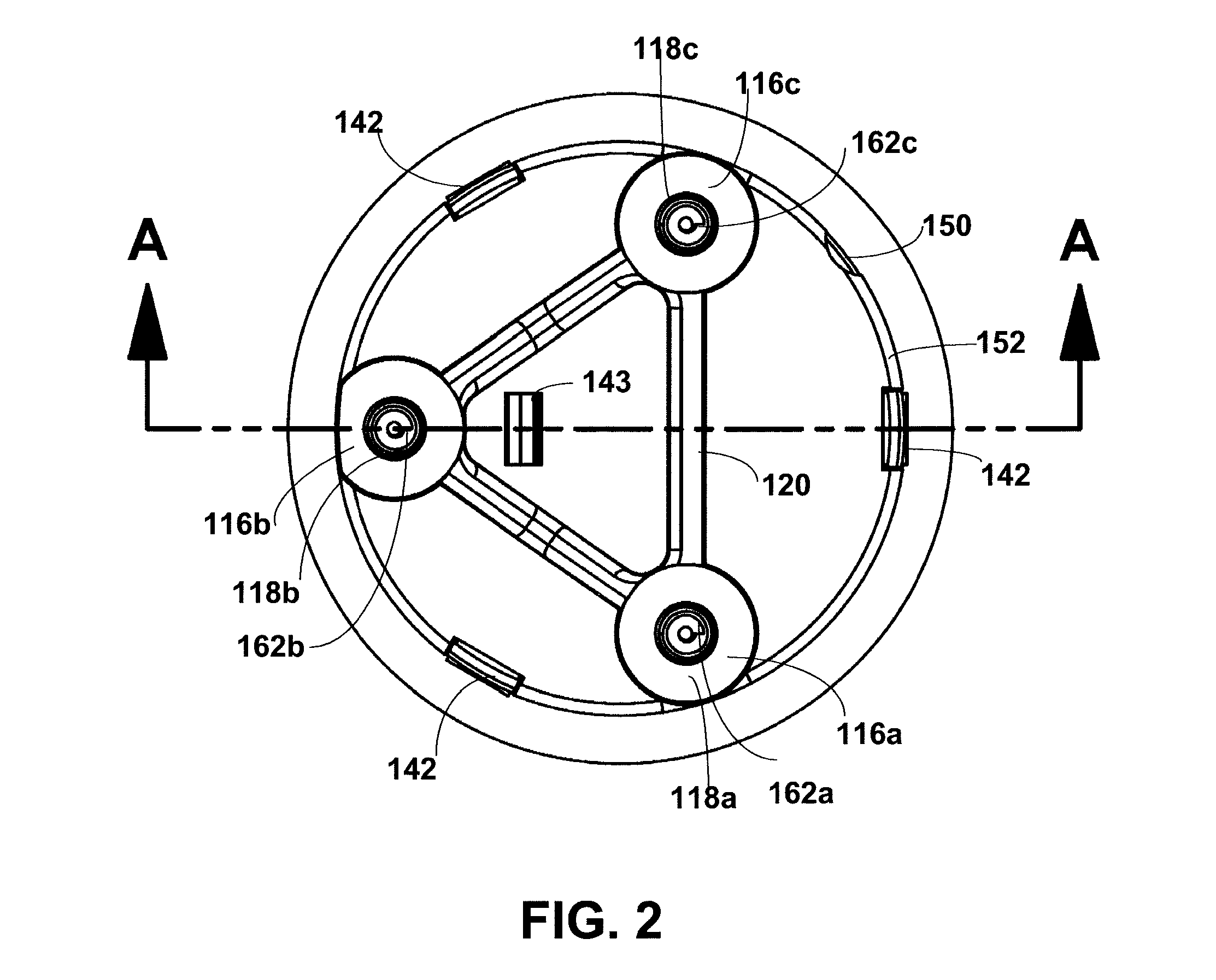

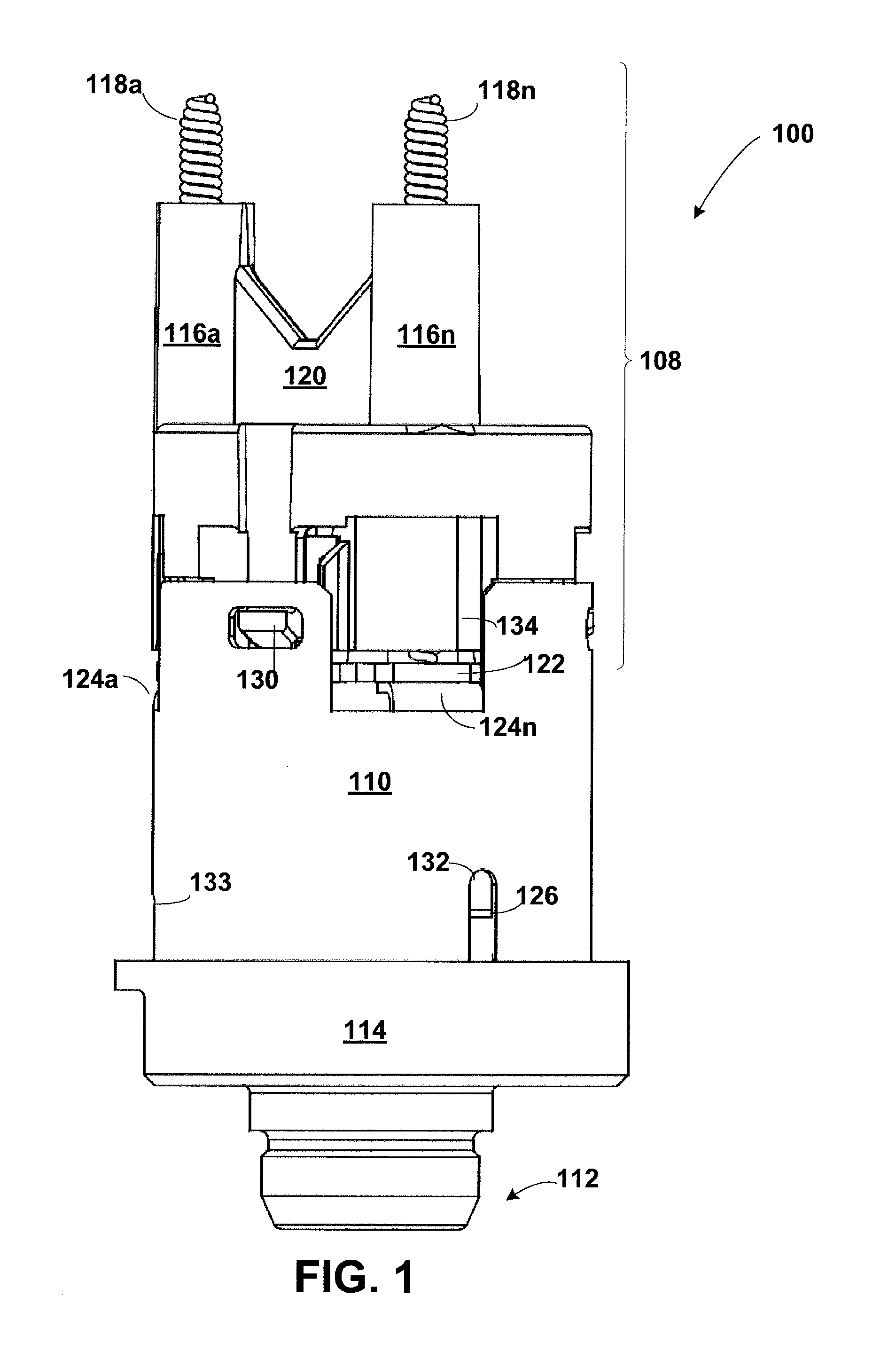

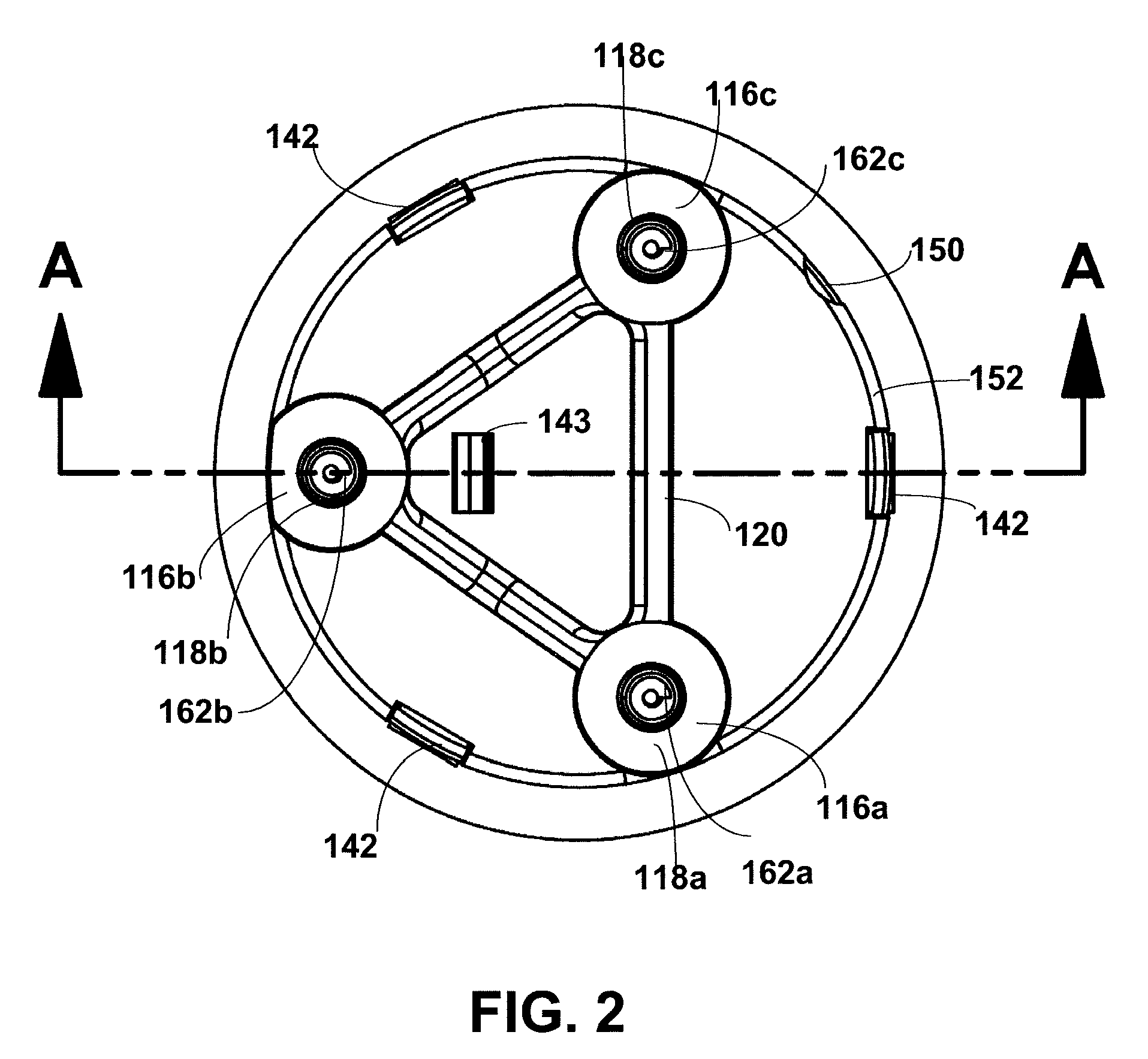

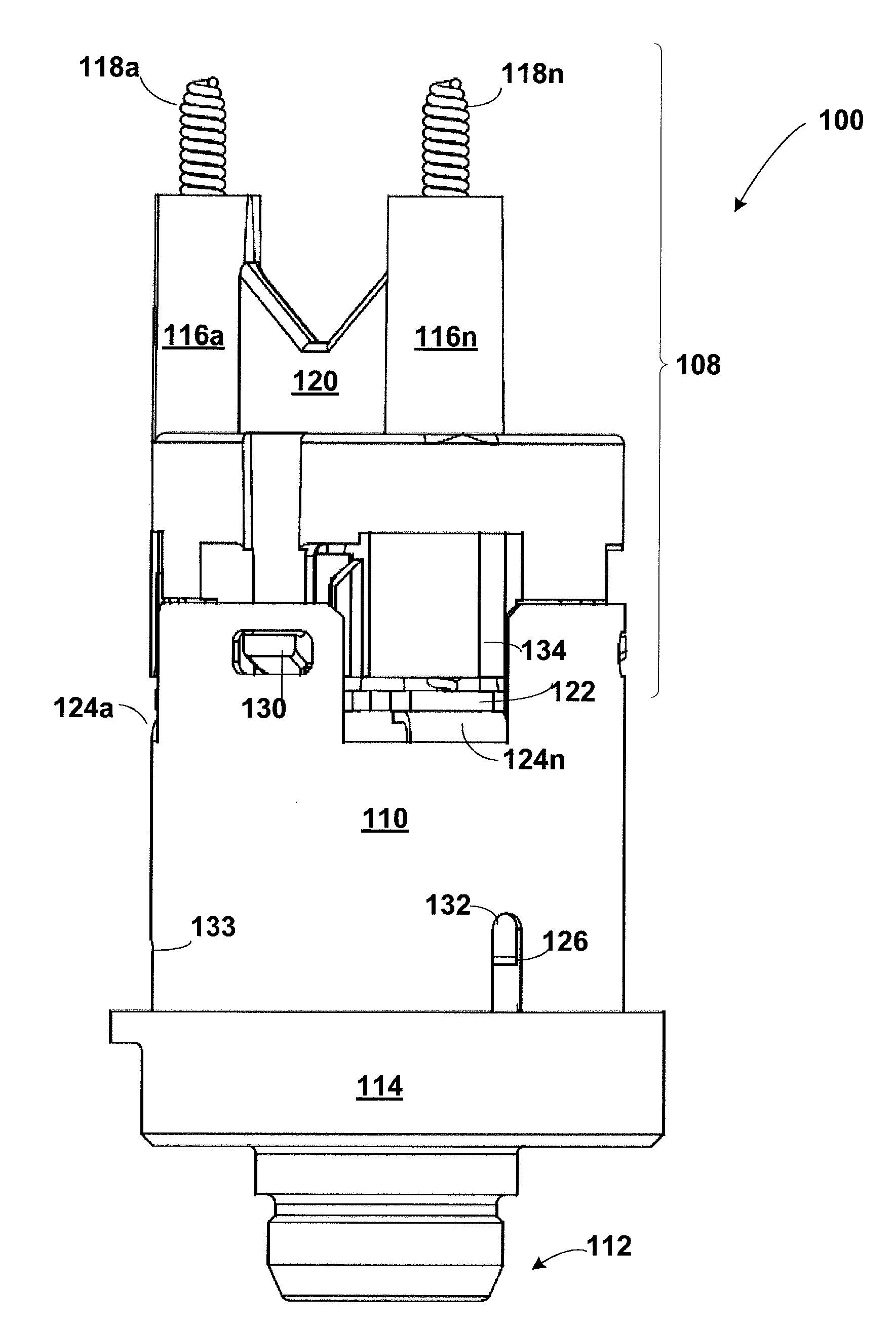

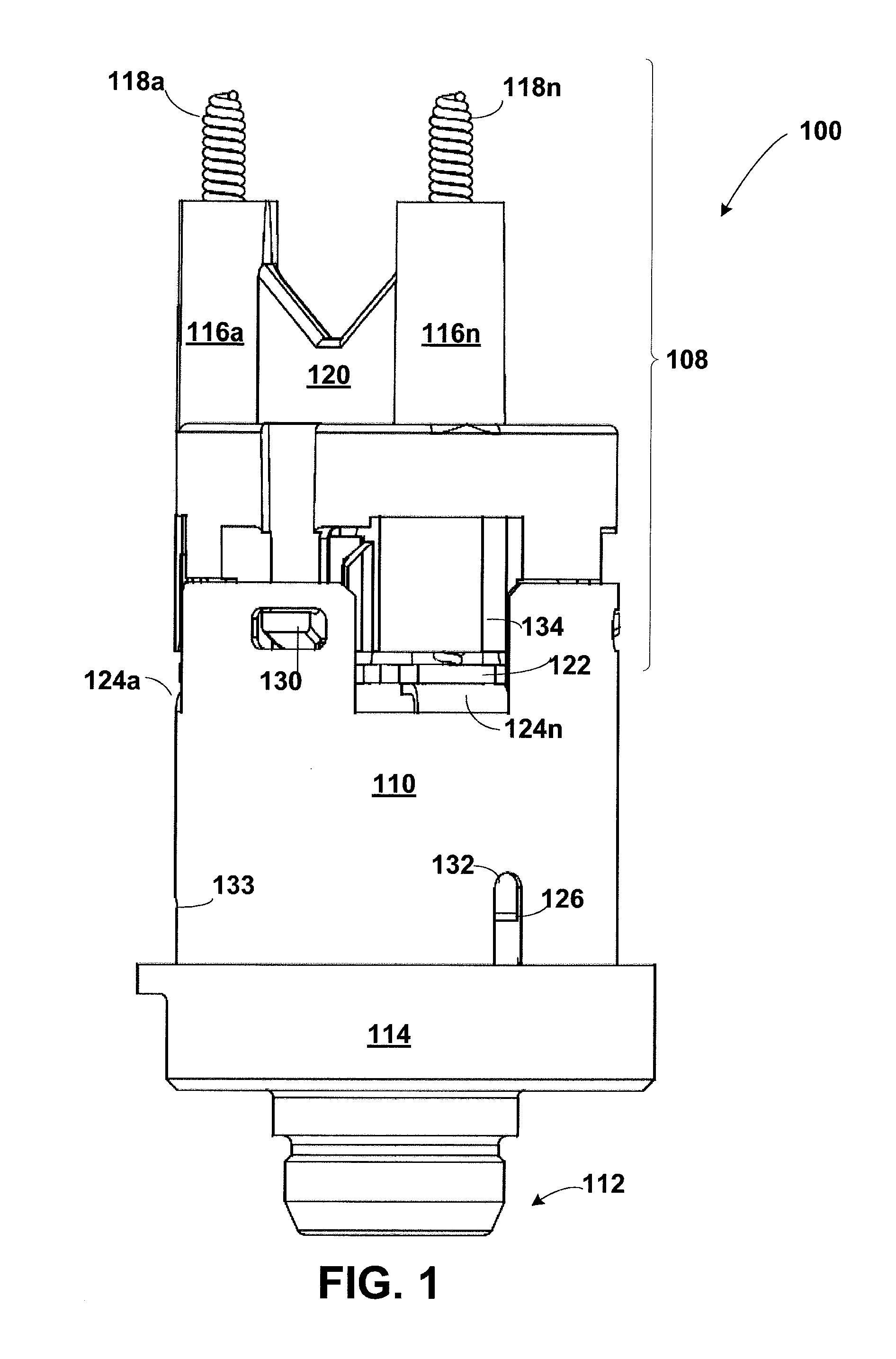

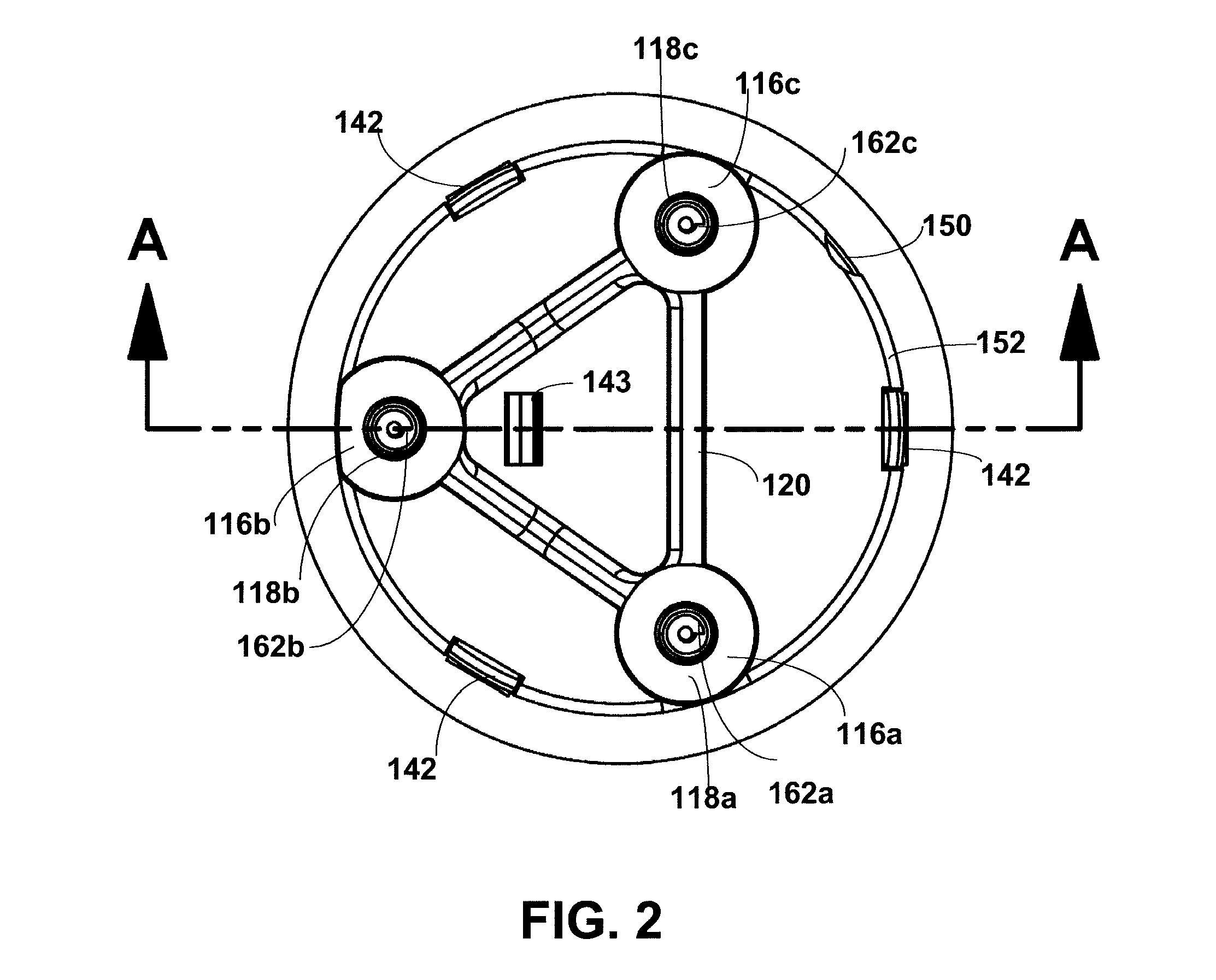

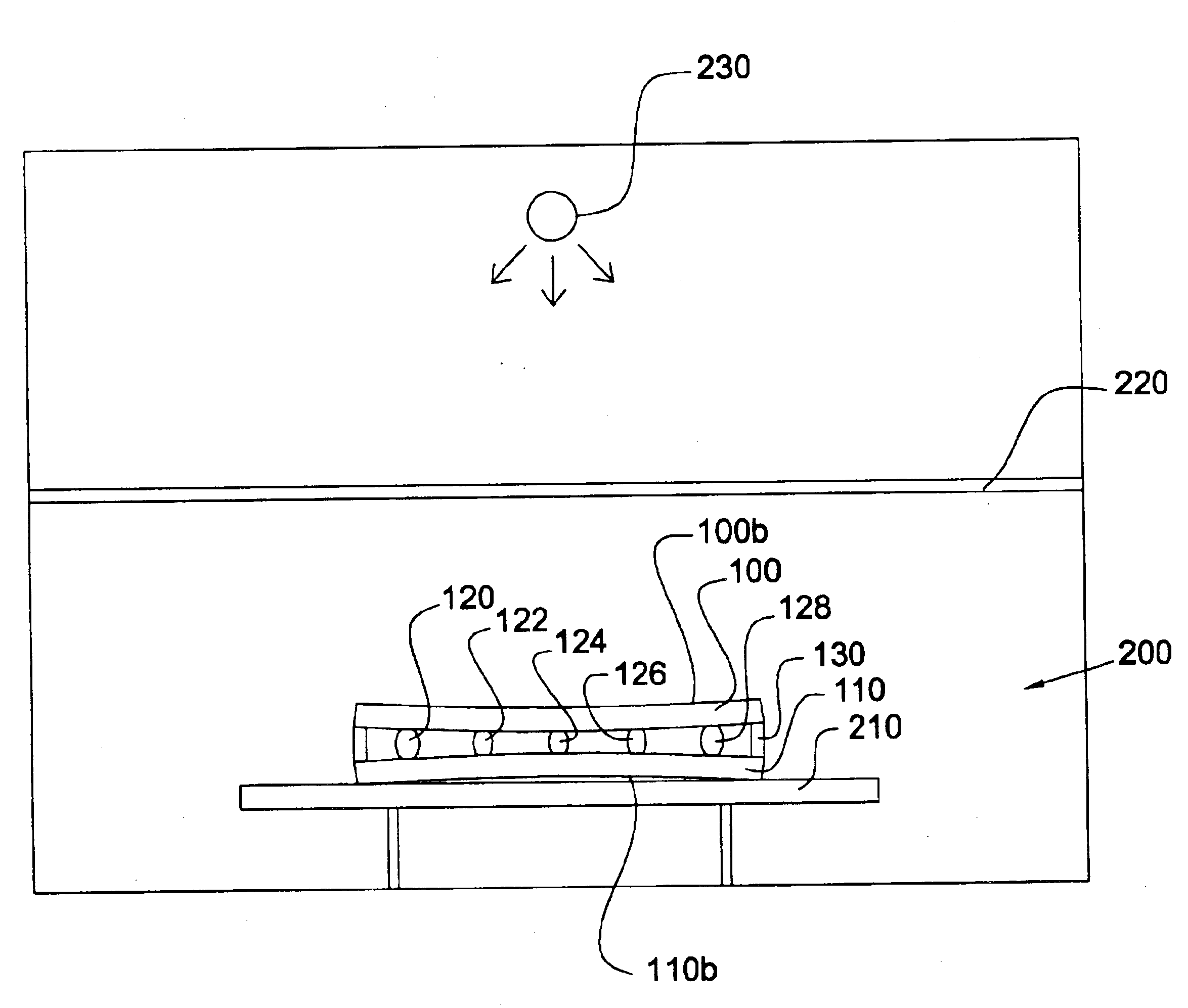

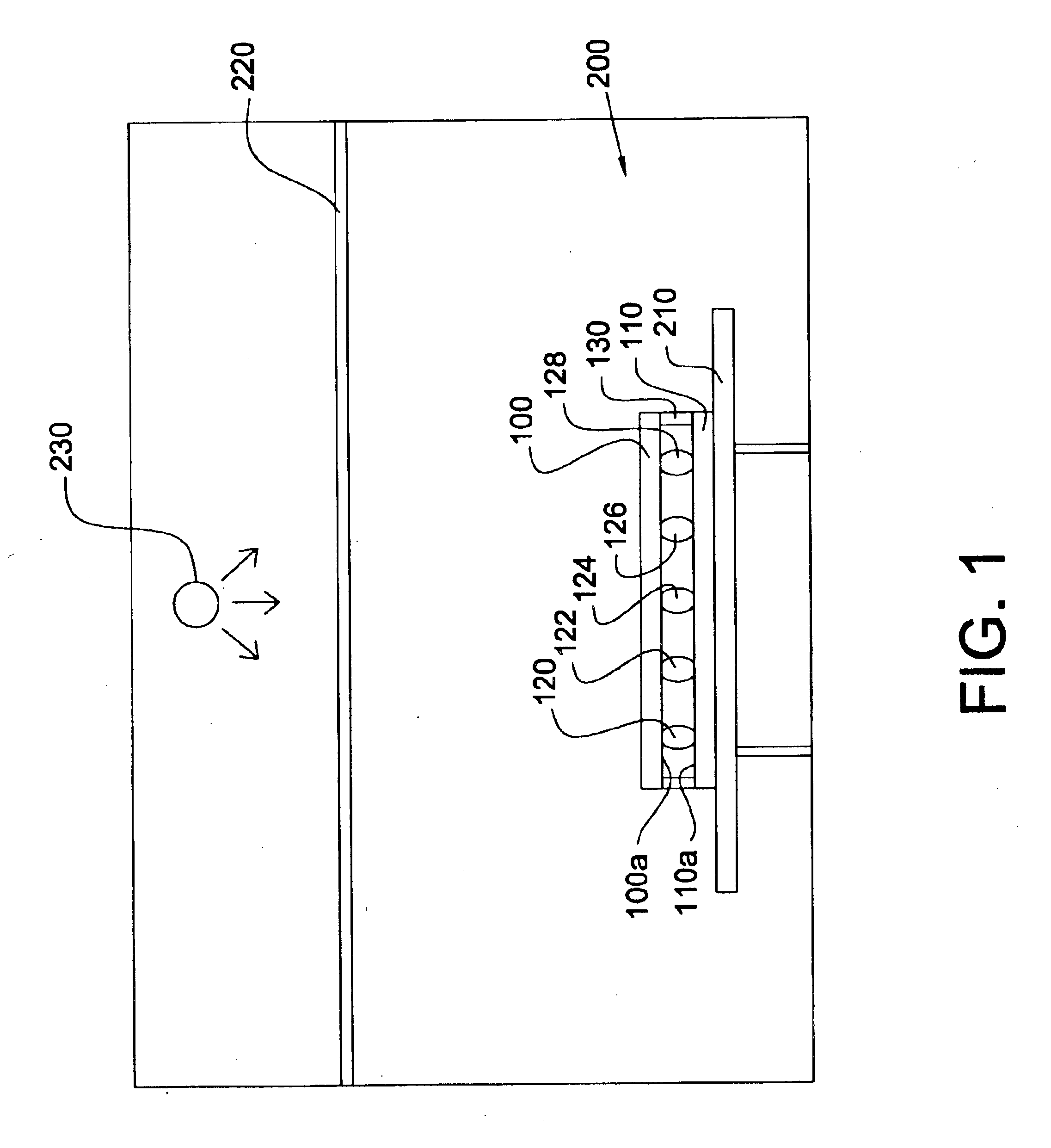

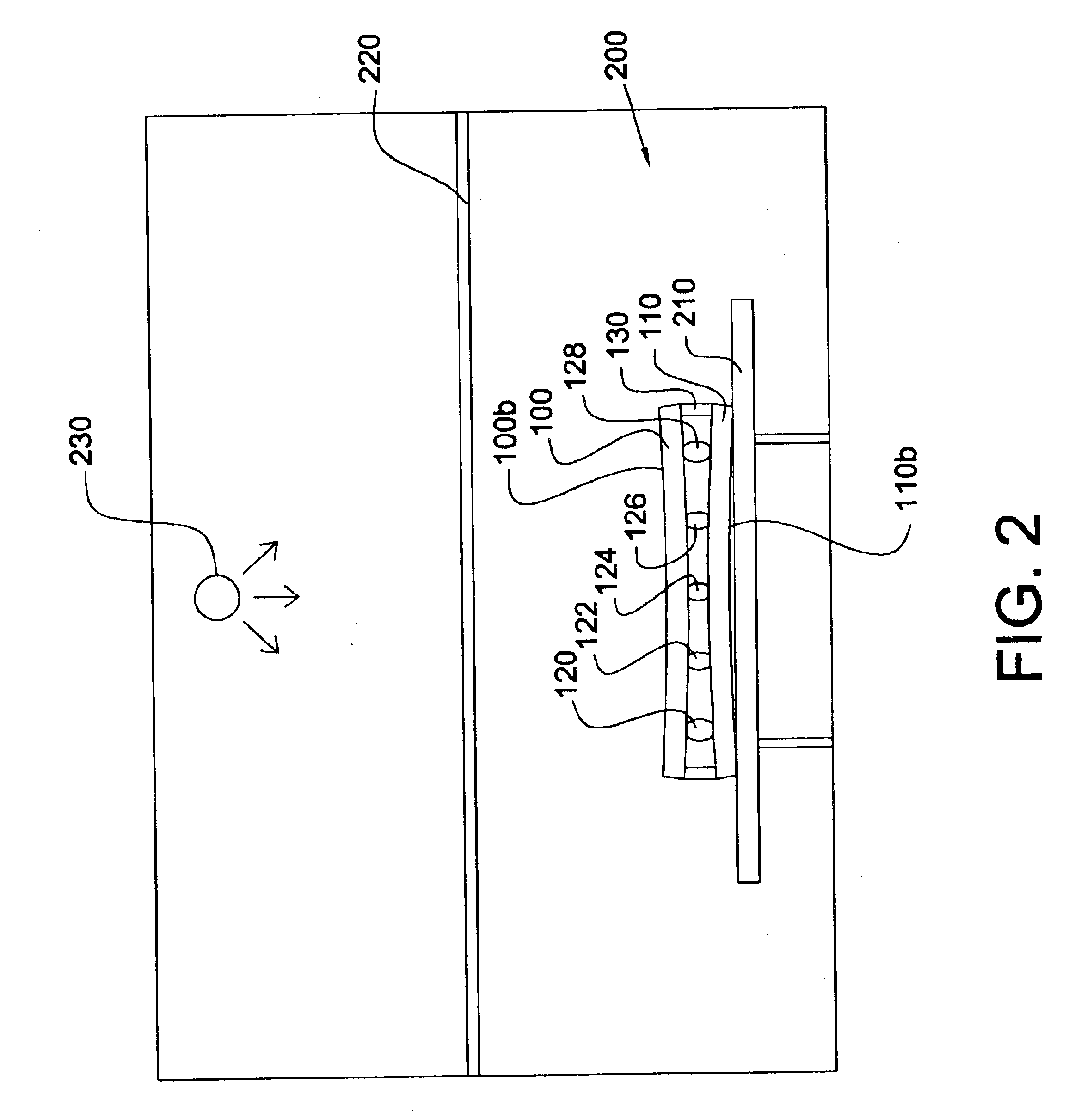

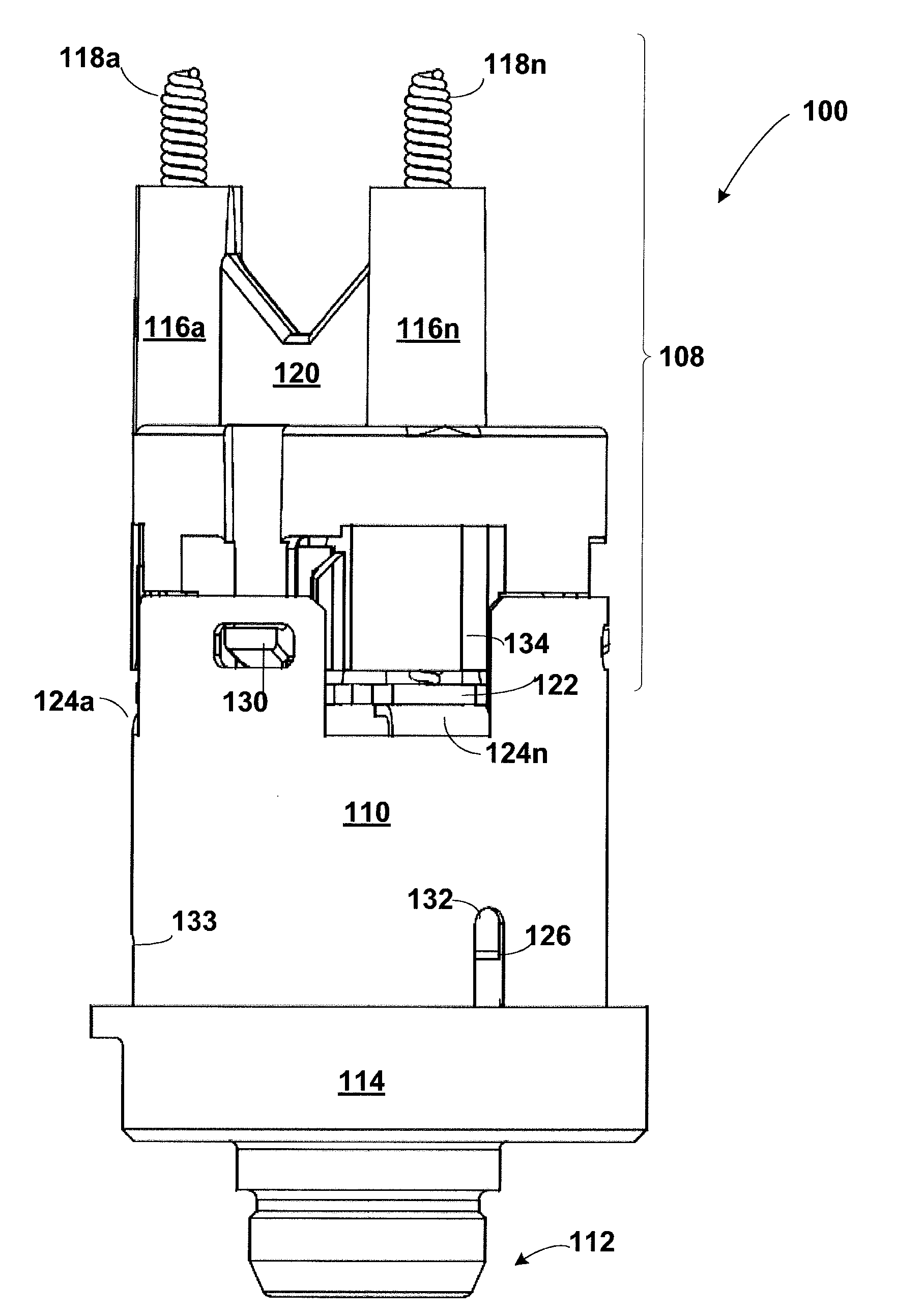

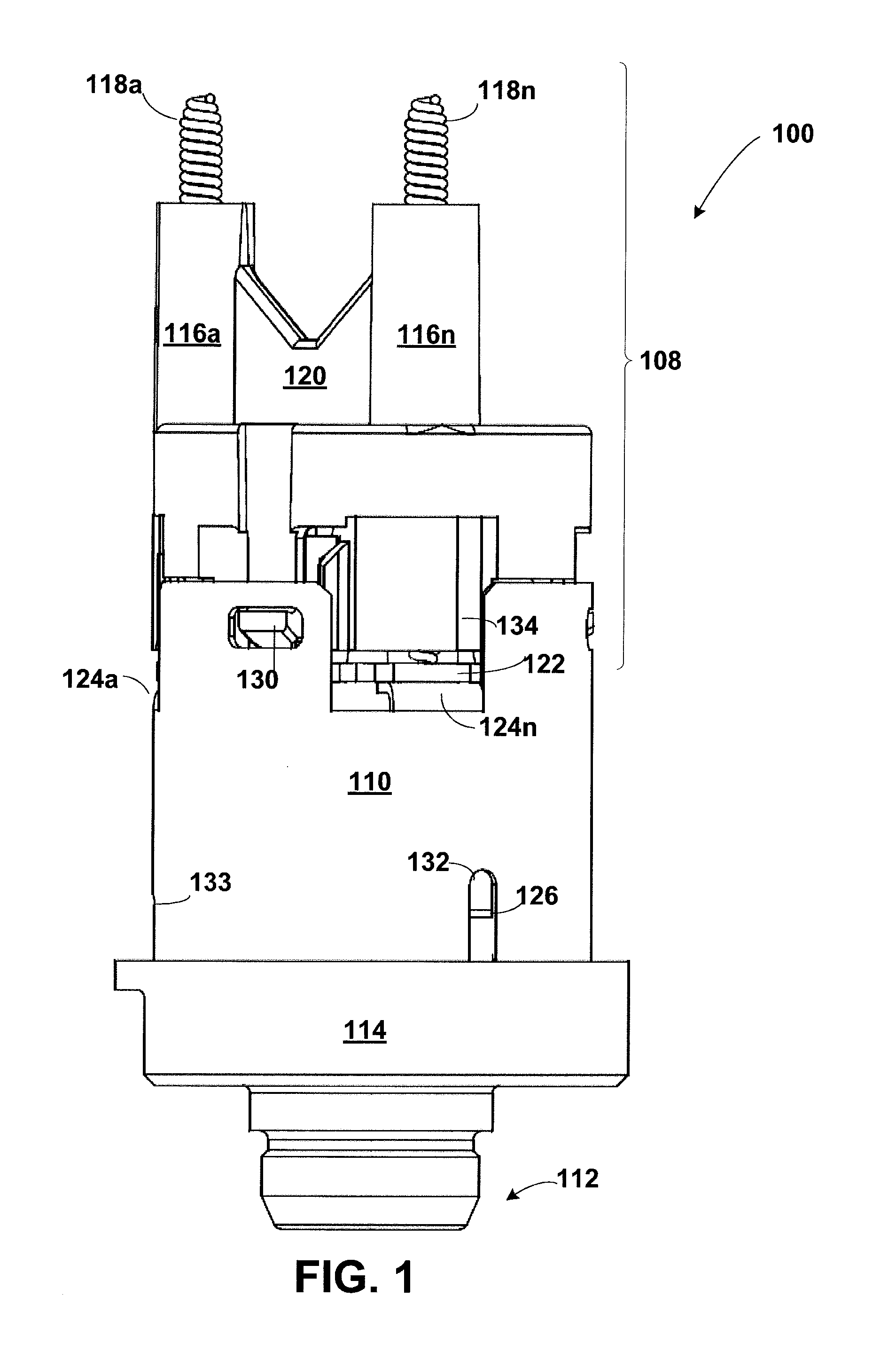

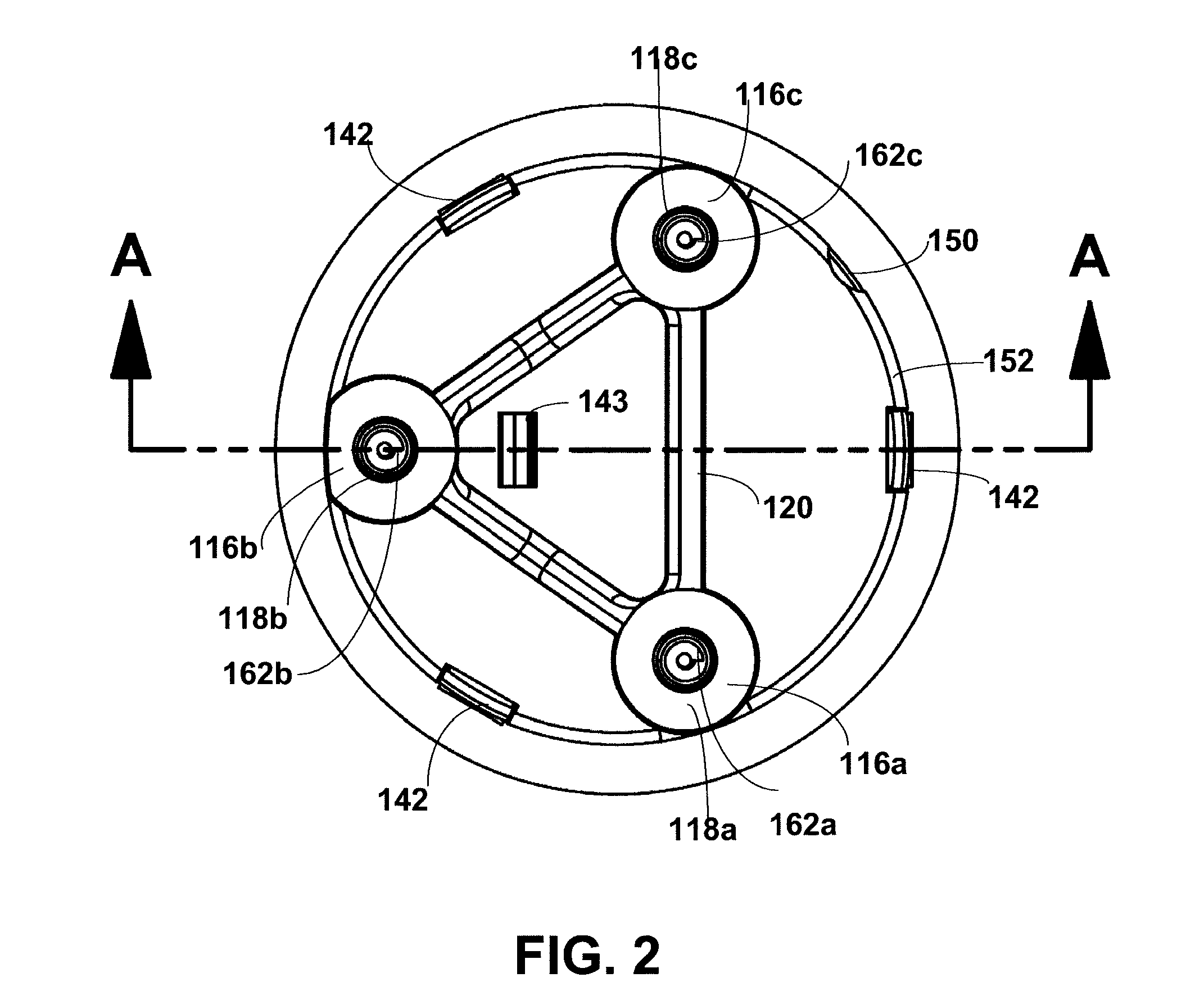

Pressure sensor

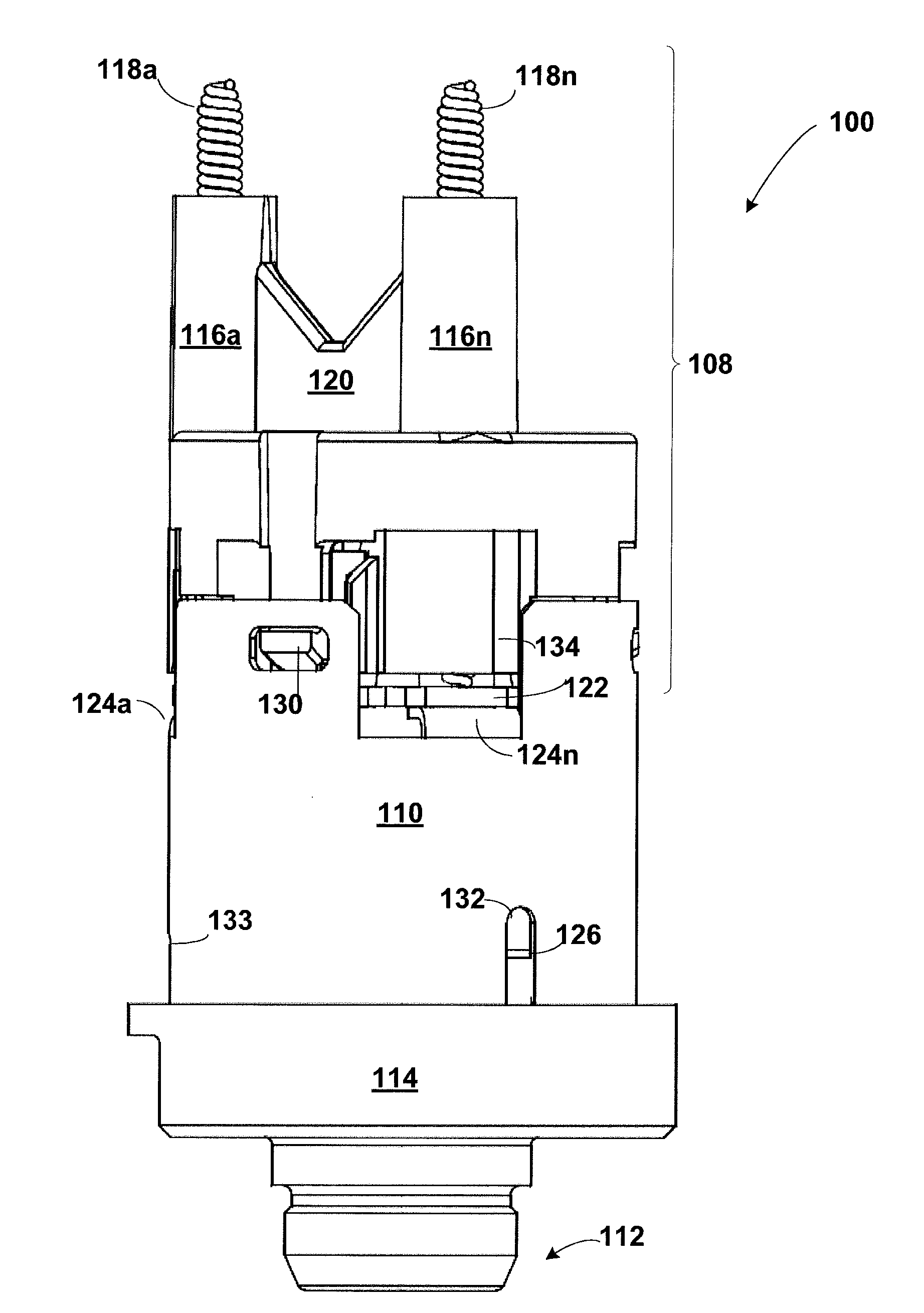

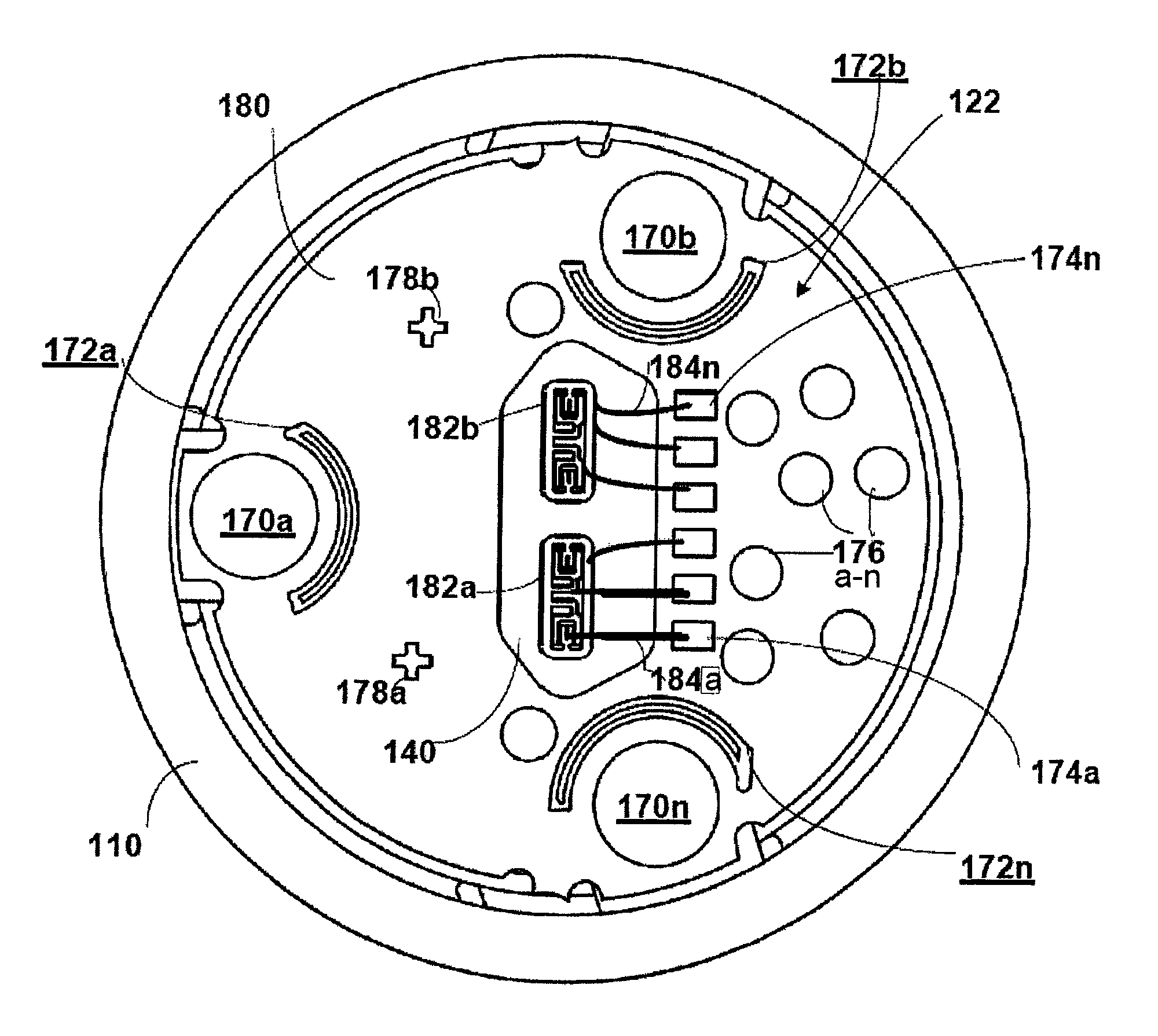

ActiveUS20110290030A1Facilitate wire bondingImprove visibilityFluid pressure measurement using ohmic-resistance variationFluid pressure measurement using elastically-deformable gaugesInterference fitElectronic board

A pressure sensor includes a sense element port, a support ring and a plurality of interference fit slits to provide a flexible interference fit between the sense element port and the support ring to form a substantially flush lap joint. The sensor also includes an electronics board inside the support ring and attached to planar mounting tabs which provide a stable mounting. Gel flow barriers protect electronics board features from unwanted non-conductive gel. Double-ended symmetrical, tapered contact springs provide manufacturing cost savings and contribute to improved alignment of an interface connector of the sensor.

Owner:SENSATA TECHNOLOGIES INC

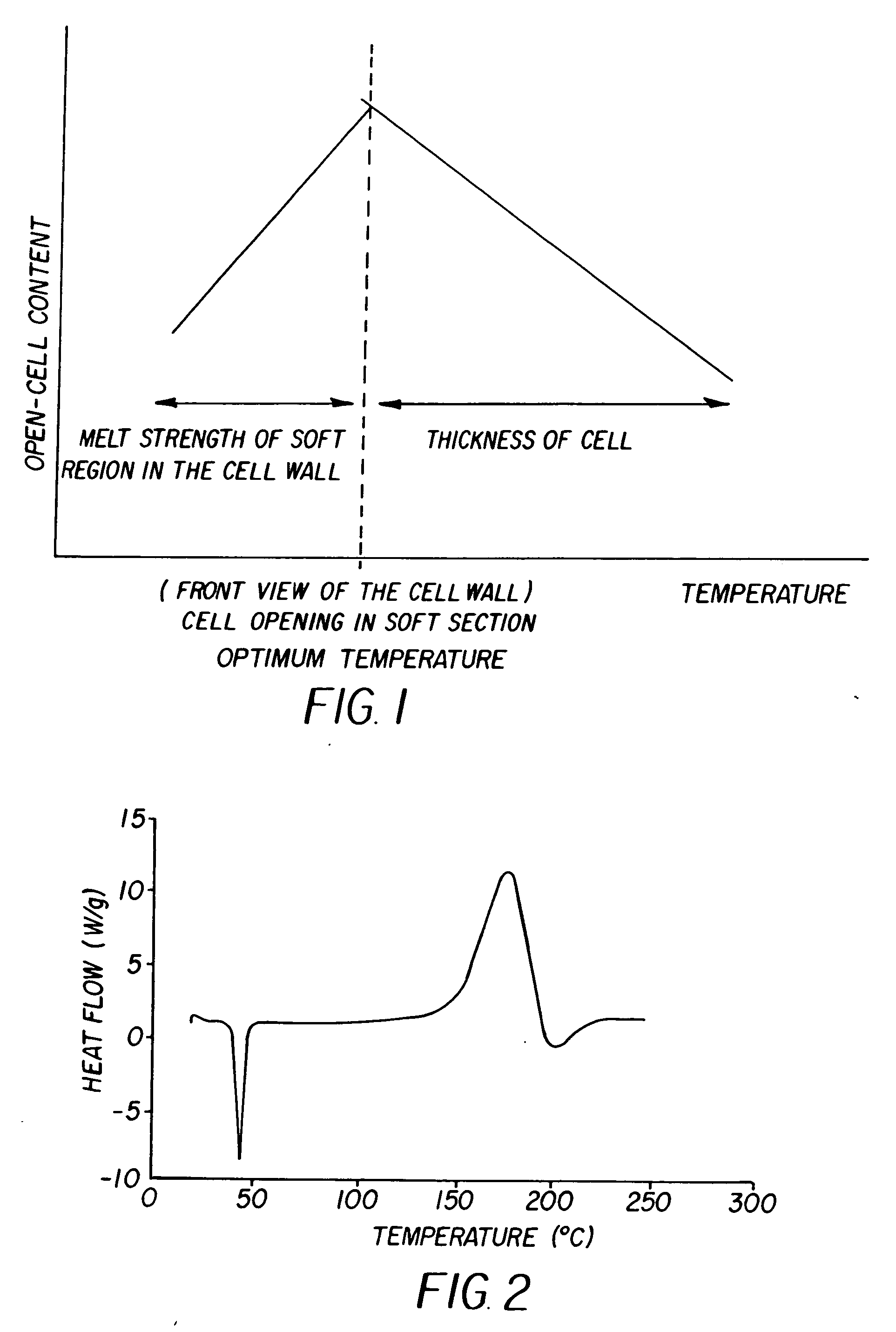

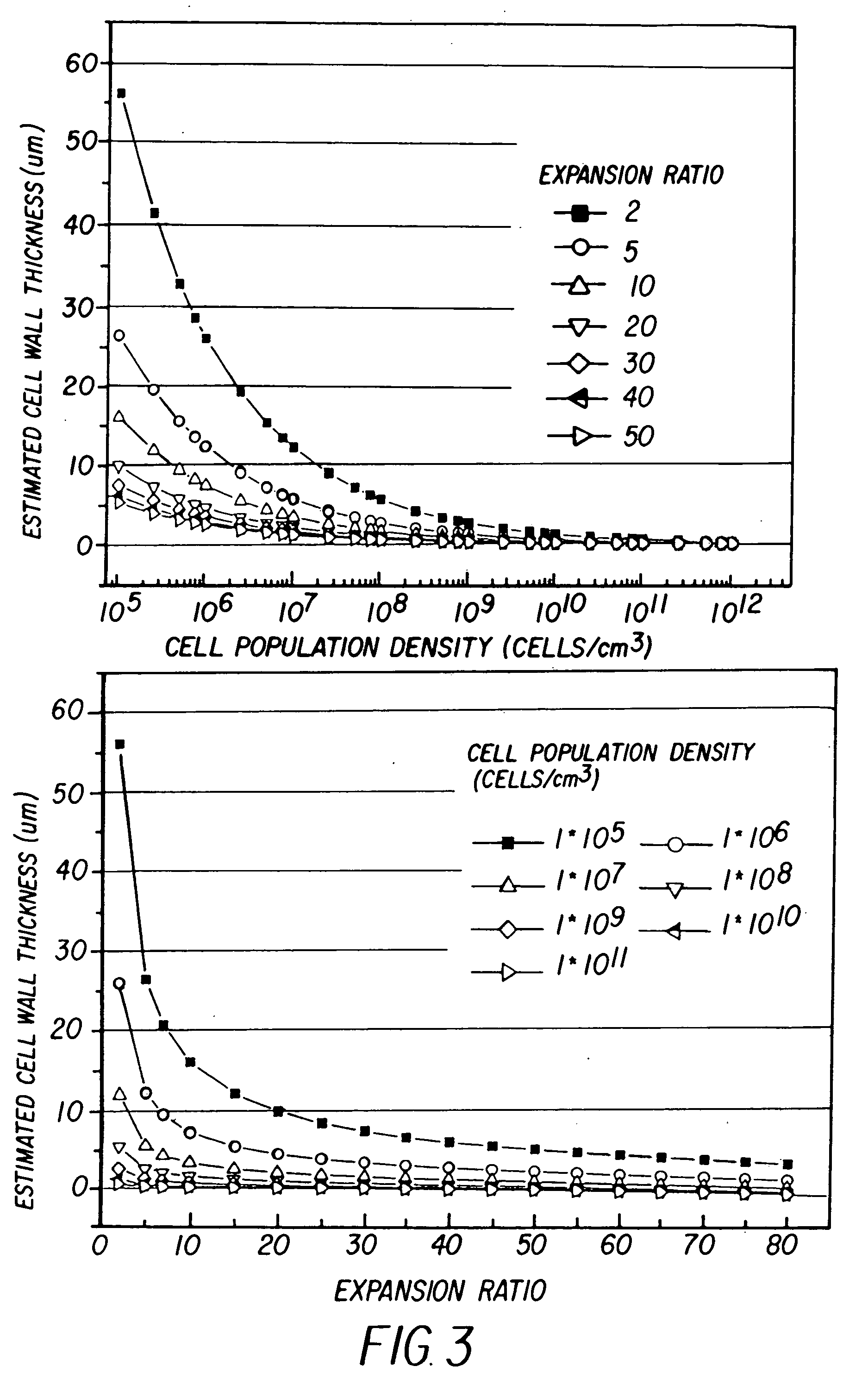

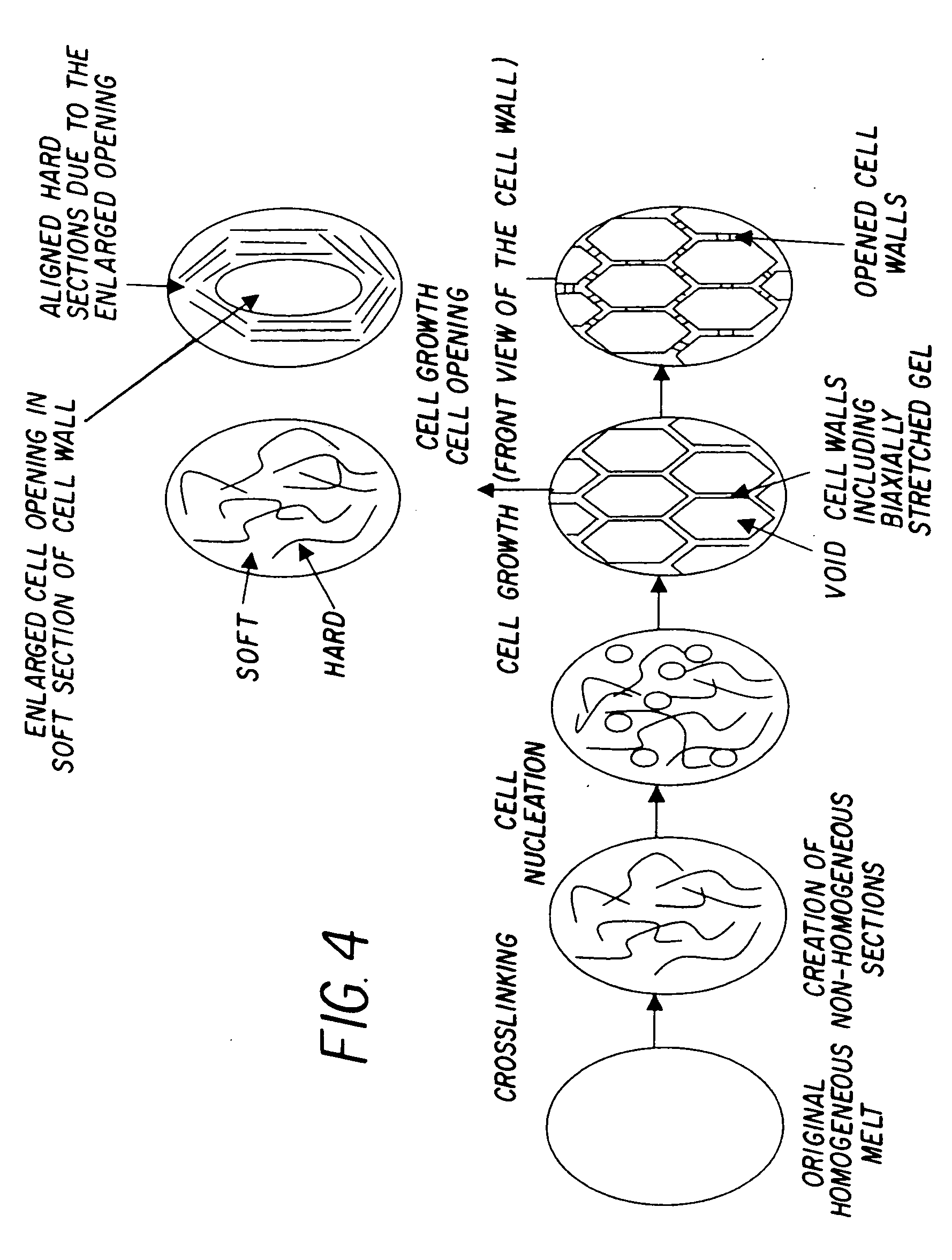

Manufacturing process for open celled microcellular foam

The present invention relates to a method for making an open celled microcellular foam comprising providing at least one foamable polymer and a crosslinking agent in an extruder, injecting at least one blowing agent into said at least one foamable polymer and said crosslinking agent in said extruder, blending said blowing agent injected into said at least one foamable polymer and said crosslinking agent in said extruder, feeding said blended blowing agent, at least one foamable polymer and said crosslinking agent in said extruder to a die, and depressurizing said blended blowing agent, said at least one foamable polymer and said crosslinking agent.

Owner:DONTULA NARASIMHARAO +6

Pressure sensor

ActiveUS8129624B2Conducive to environmental protectionLess expensiveSludge treatmentVolume/mass flow measurementInterference fitElectronic board

A pressure sensor includes a sense element port, a support ring and a plurality of interference fit slits to provide a flexible interference fit between the sense element port and the support ring to form a substantially flush lap joint. The sensor also includes an electronics board inside the support ring and attached to planar mounting tabs which provide a stable mounting. Gel flow barriers protect electronics board features from unwanted non-conductive gel. Double-ended symmetrical, tapered contact springs provide manufacturing cost savings and contribute to improved alignment of an interface connector of the sensor.

Owner:SENSATA TECHNOLOGIES INC

Bond pad structure and method of manufacturing the same

ActiveUS20140116760A1Reduce the possibilityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesProtection layerMechanical engineering

A method of manufacturing a bond pad structure, comprising the steps of forming a pad material layer on a passivation layer, forming a protection layer on the pad material layer, performing an etching process to pattern the protection layer and the pad material layer into a bond pad structure, and removing the protection layer on the bond pad structure.

Owner:MARLIN SEMICON LTD

Pressure sensor

ActiveUS8156816B2Conducive to environmental protectionLess expensiveFluid pressure measurement using ohmic-resistance variationFluid pressure measurement by mechanical elementsInterference fitElectronic board

A pressure sensor includes a sense element port, a support ring and a plurality of interference fit slits to provide a flexible interference fit between the sense element port and the support ring to form a substantially flush lap joint. The sensor also includes an electronics board inside the support ring and attached to planar mounting tabs which provide a stable mounting. Gel flow barriers protect electronics board features from unwanted non-conductive gel. Double-ended symmetrical, tapered contact springs provide manufacturing cost savings and contribute to improved alignment of an interface connector of the sensor.

Owner:SENSATA TECHNOLOGIES INC

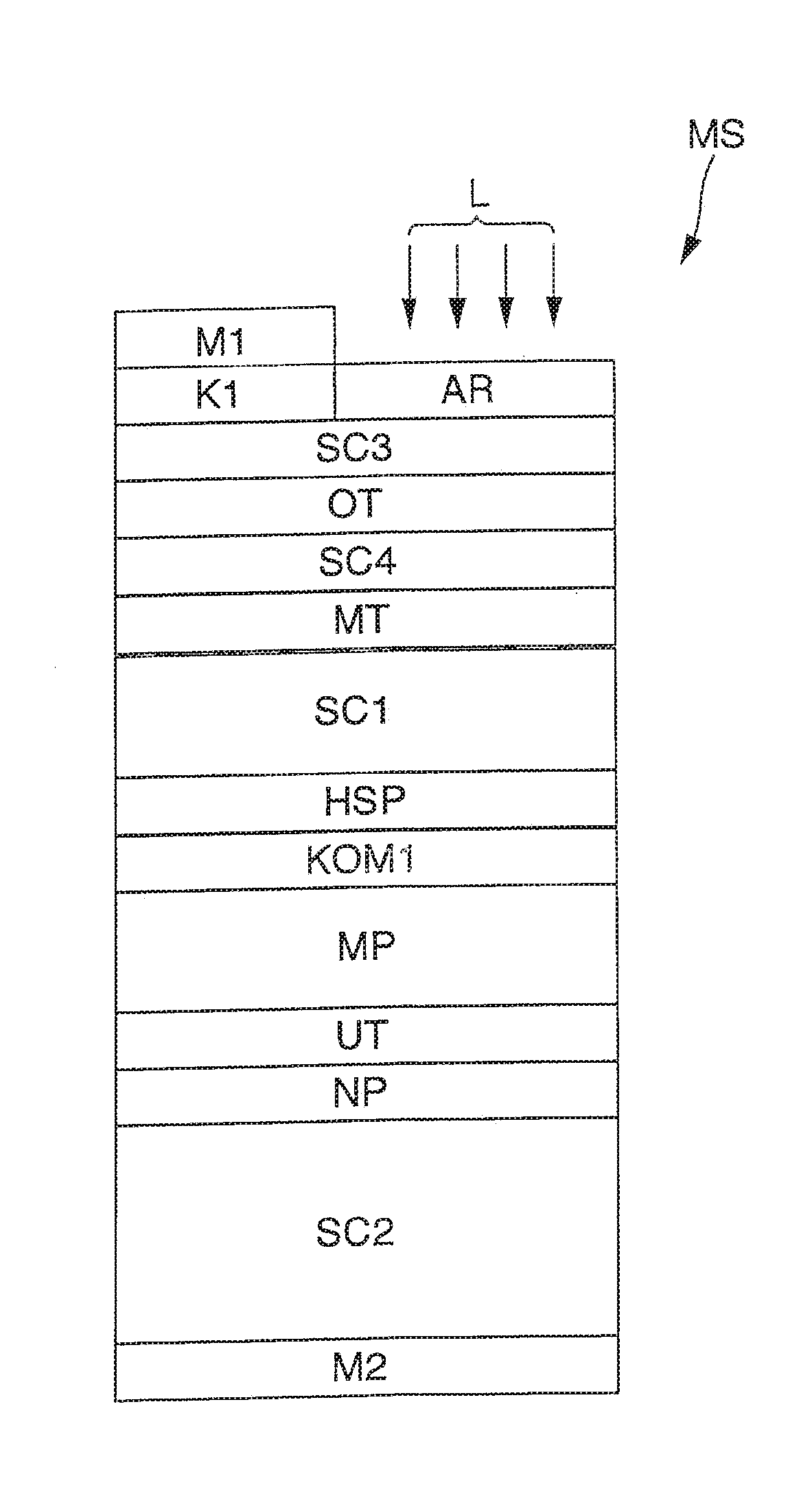

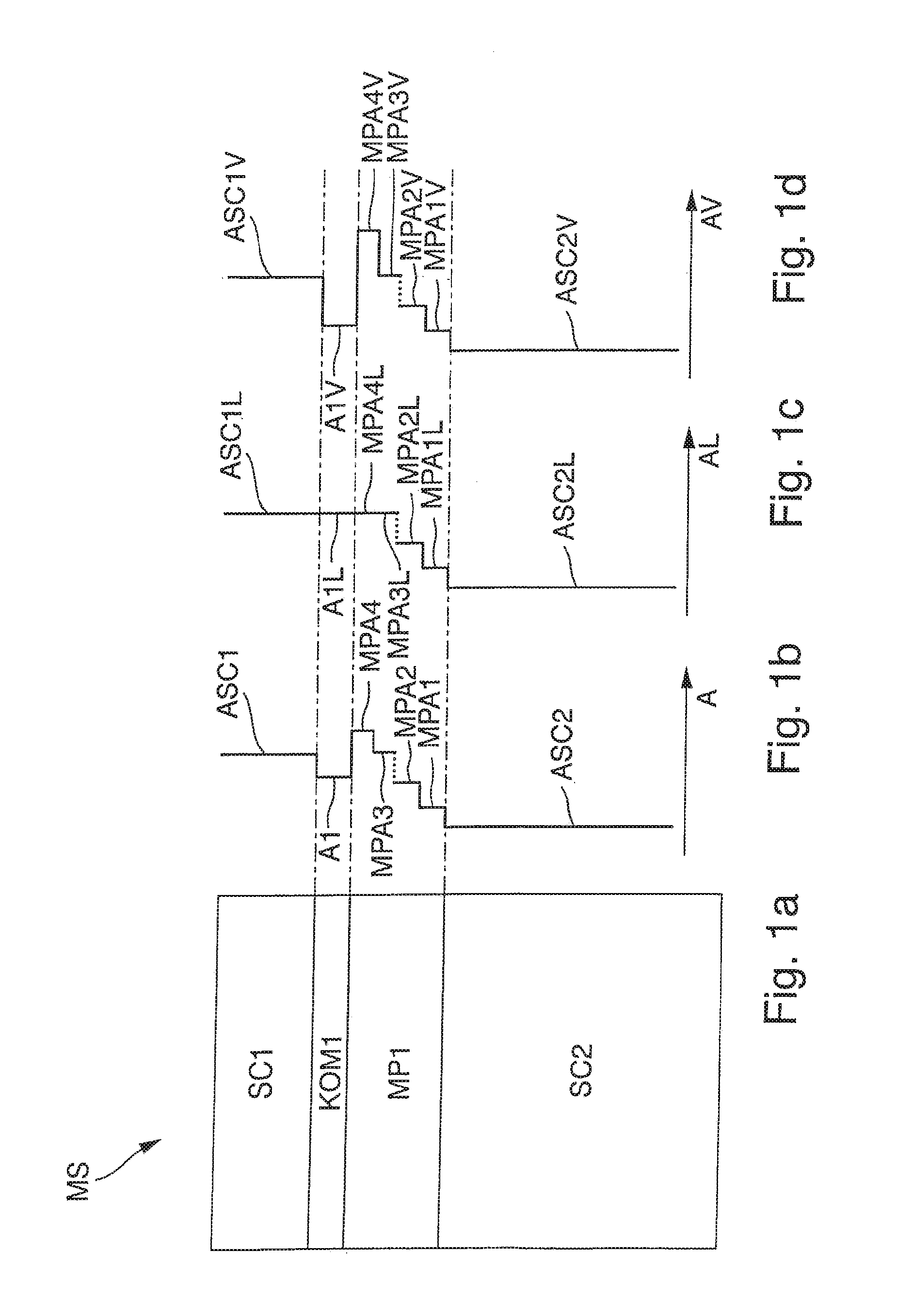

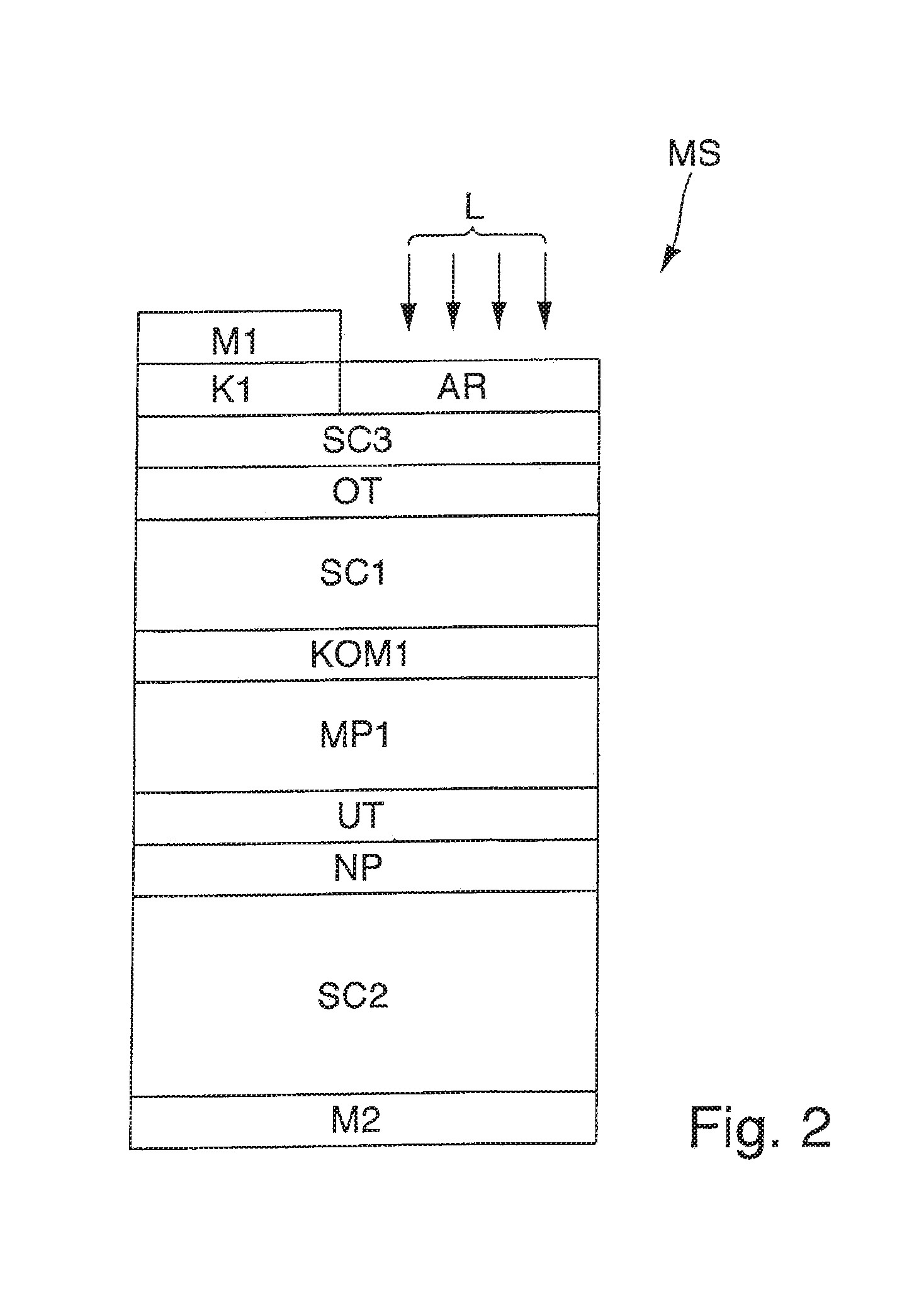

Multi solar cell

ActiveUS20160380142A1Reduce thicknessIncrease productionFinal product manufactureSemiconductor/solid-state device manufacturingLattice constantMultijunction photovoltaic cell

A multi-junction solar cell having a first subcell made of an InGaAs compound. The first subcell has a first lattice constant and A second subcell has a second lattice constant. The first lattice constant is at least 0.008 Å greater than the second lattice constant. A metamorphic buffer is formed between the first subcell and the second subcell and has a sequence of at least three layers and a lattice constant increases from layer to layer in the sequence in the direction toward the first subcell. The lattice constants of the layers of the buffer are greater than the second lattice constant, and a layer of the metamorphic buffer has a third lattice constant that is greater than the first lattice constant. A number N of compensation layers for compensating the residual stress of the metamorphic buffer is formed between the metamorphic buffer and the first subcell.

Owner:AZUR SPACE SOLAR POWER

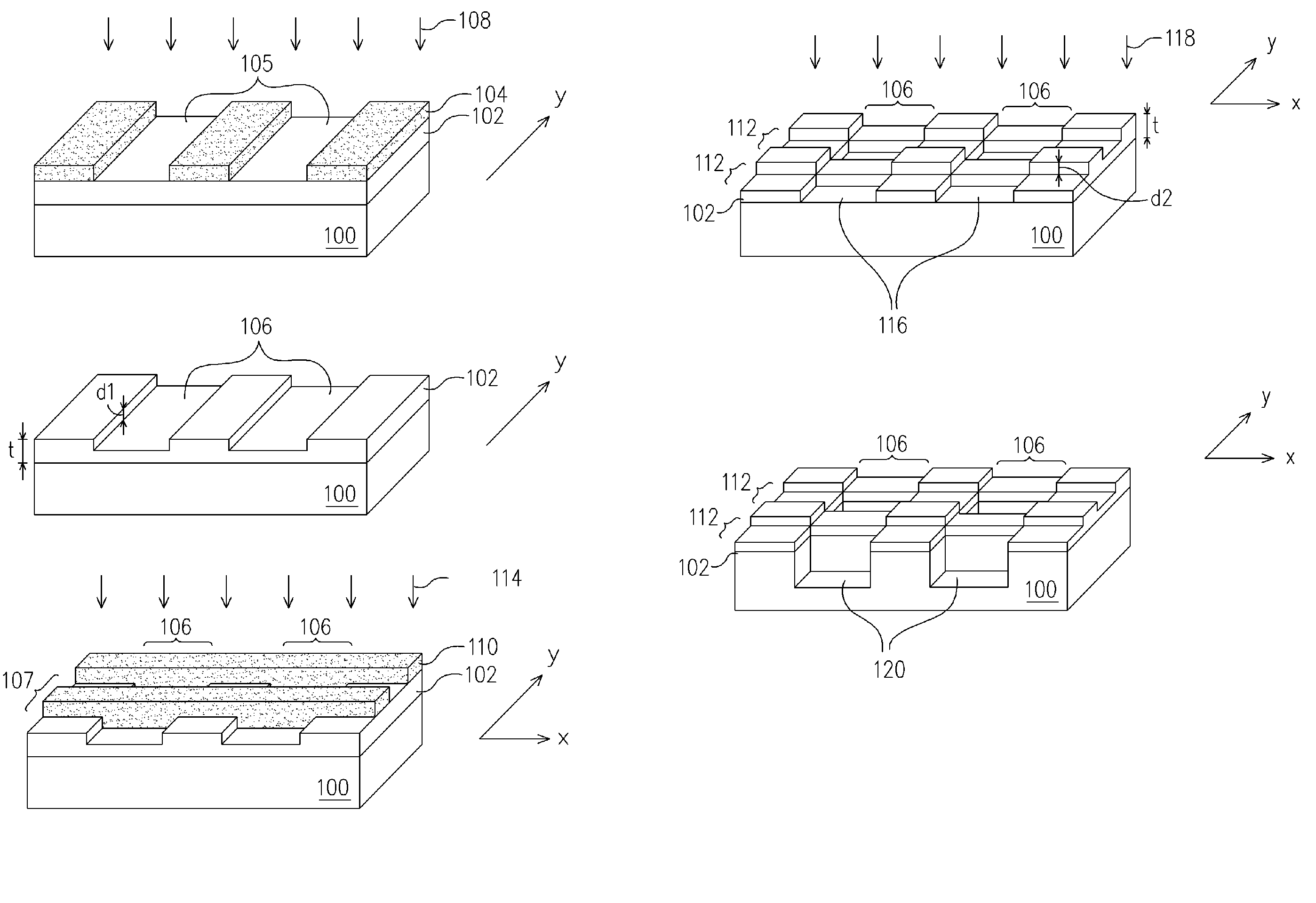

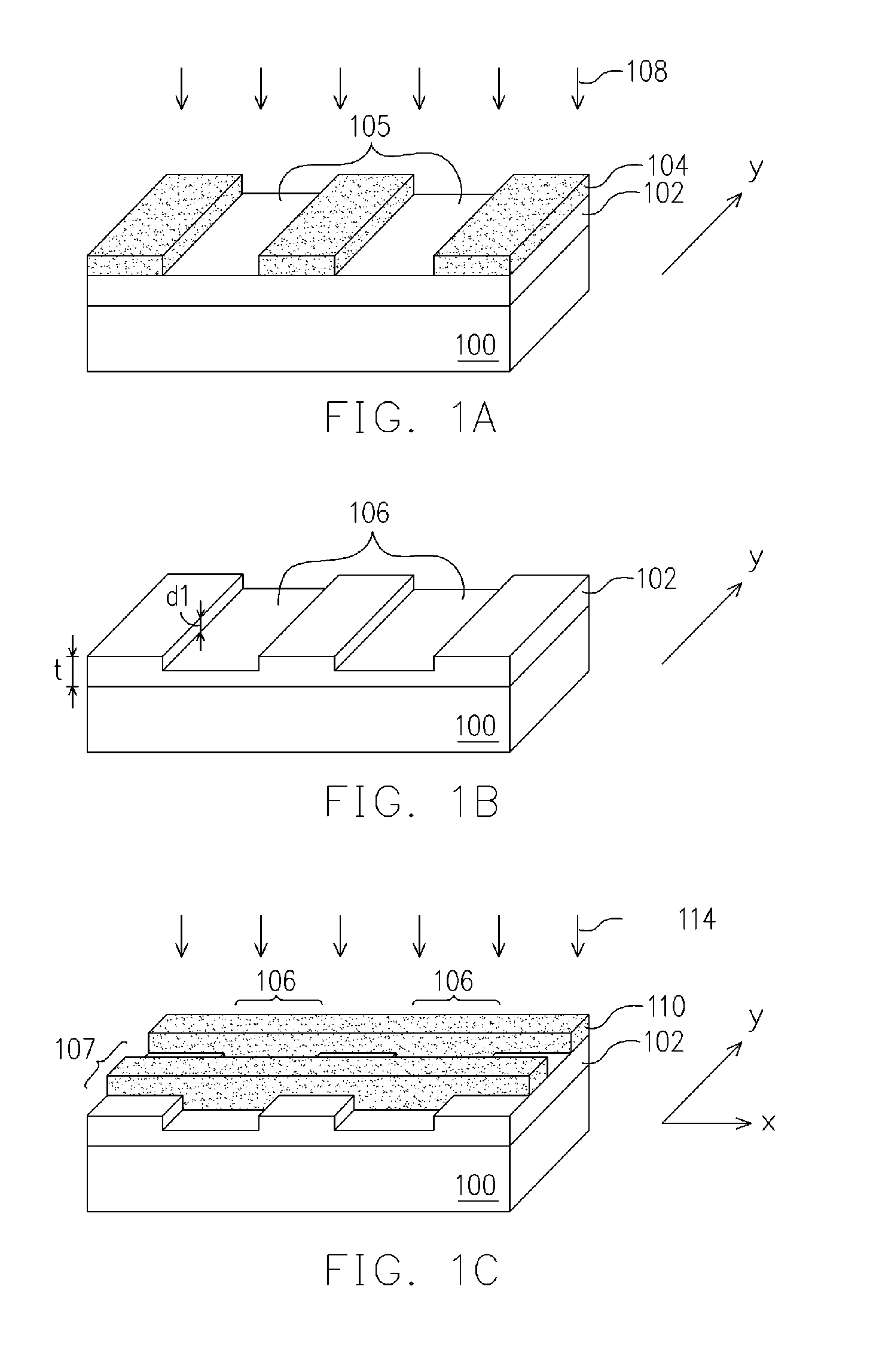

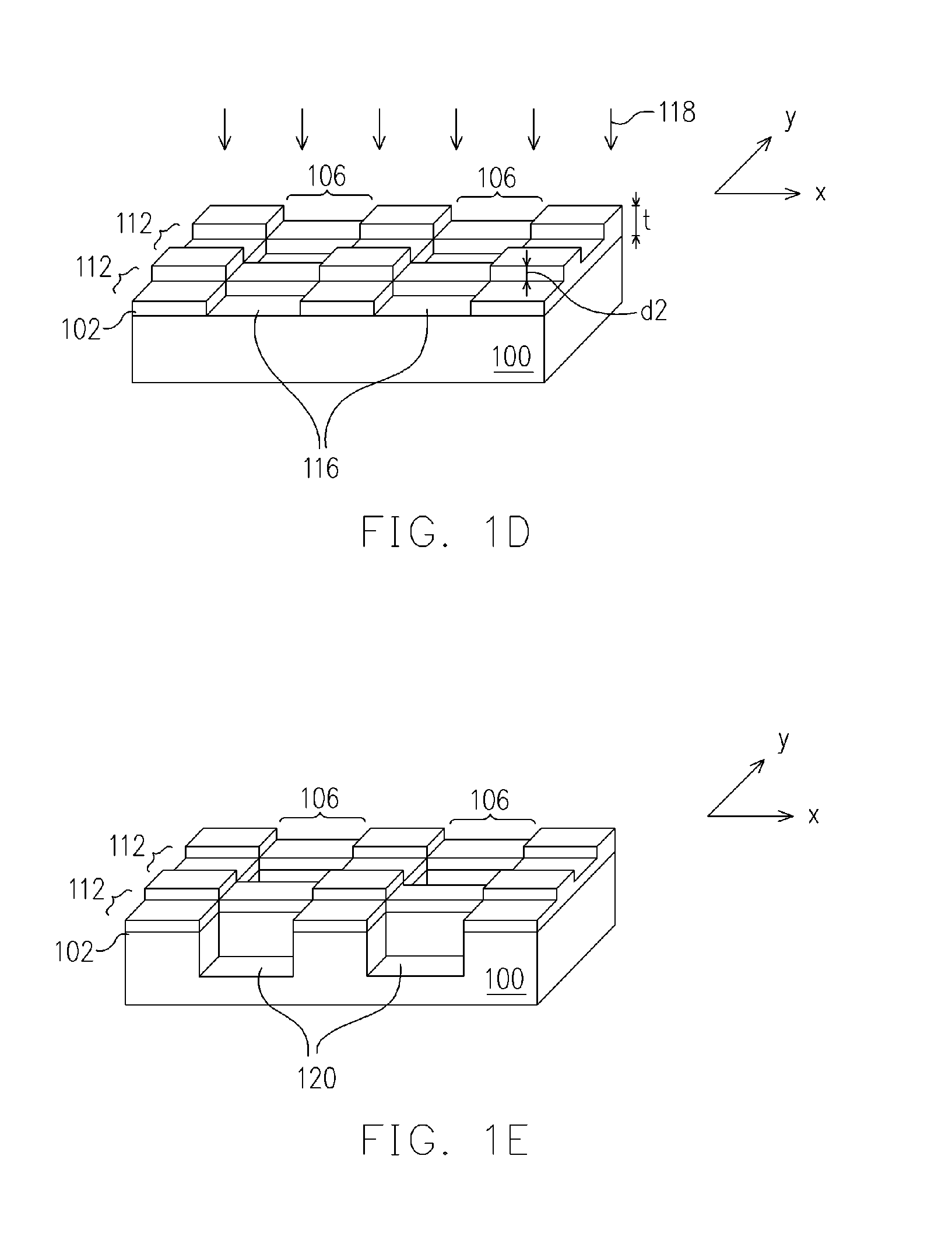

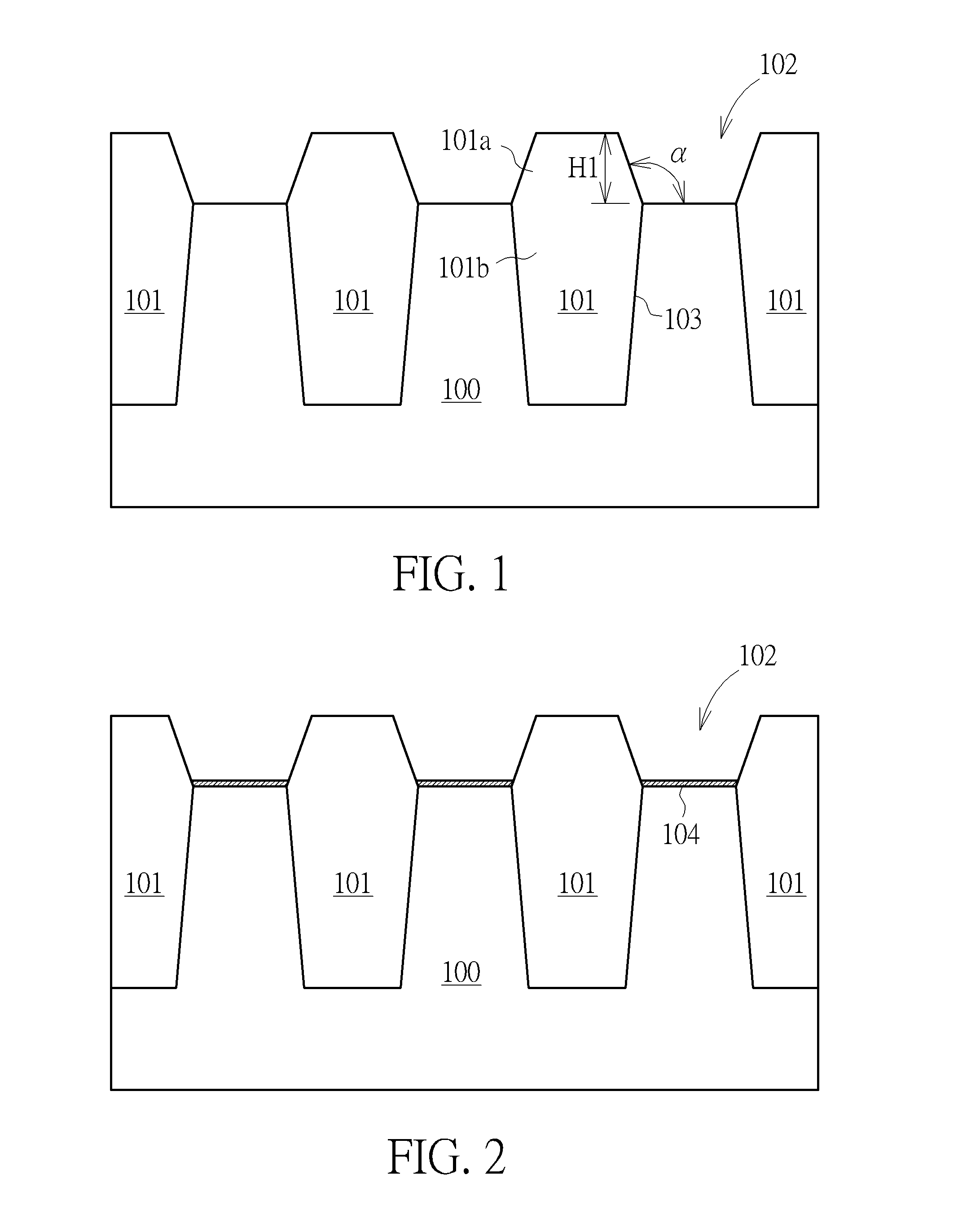

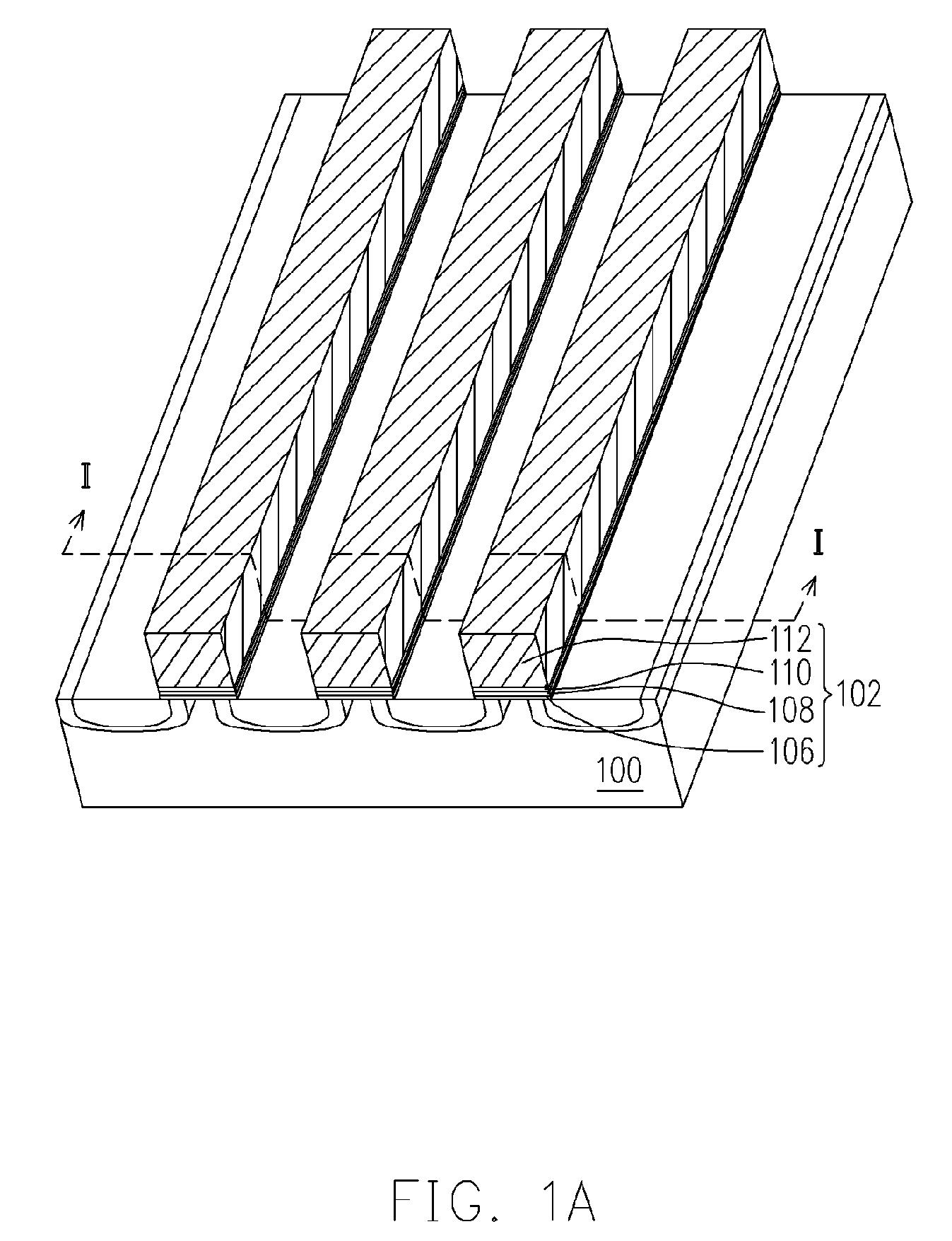

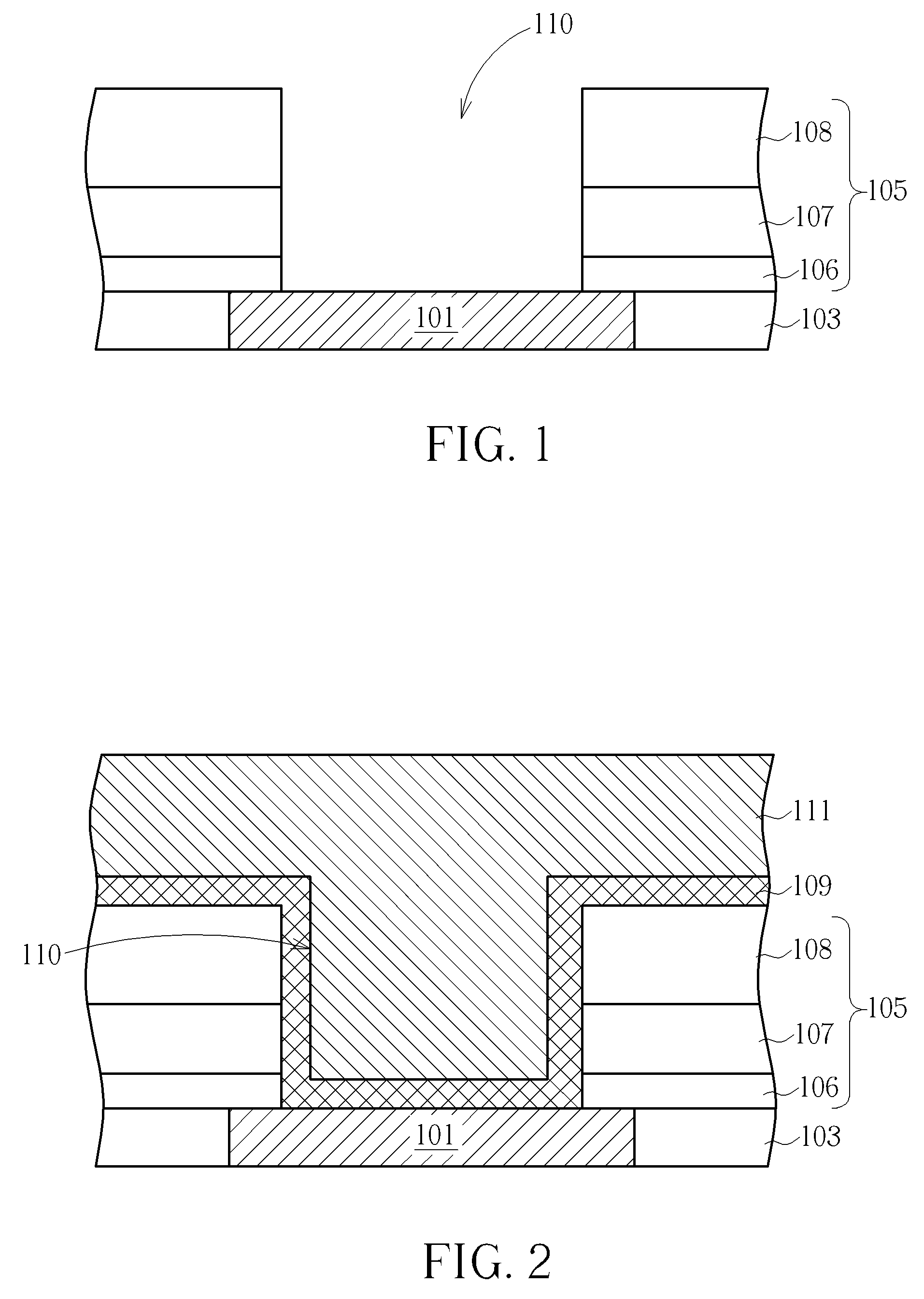

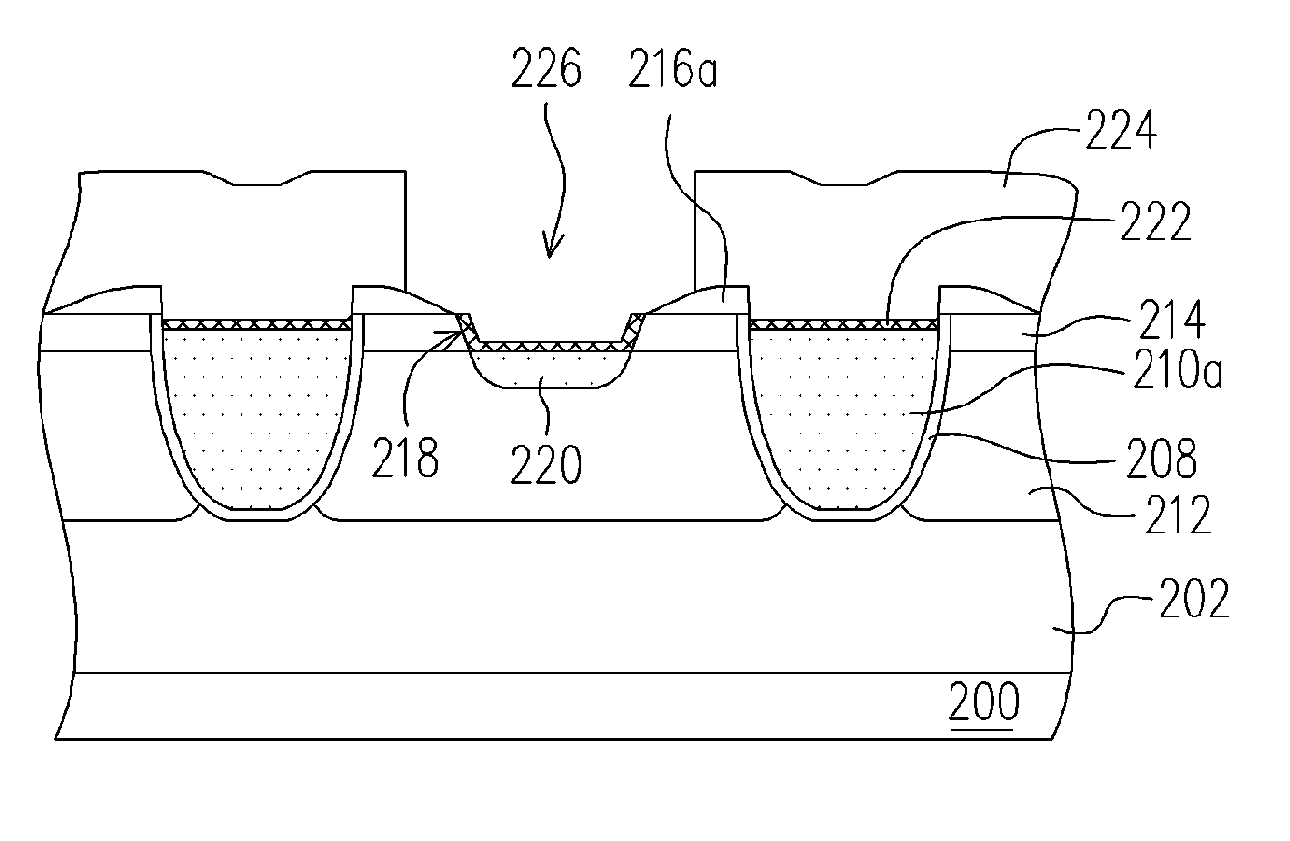

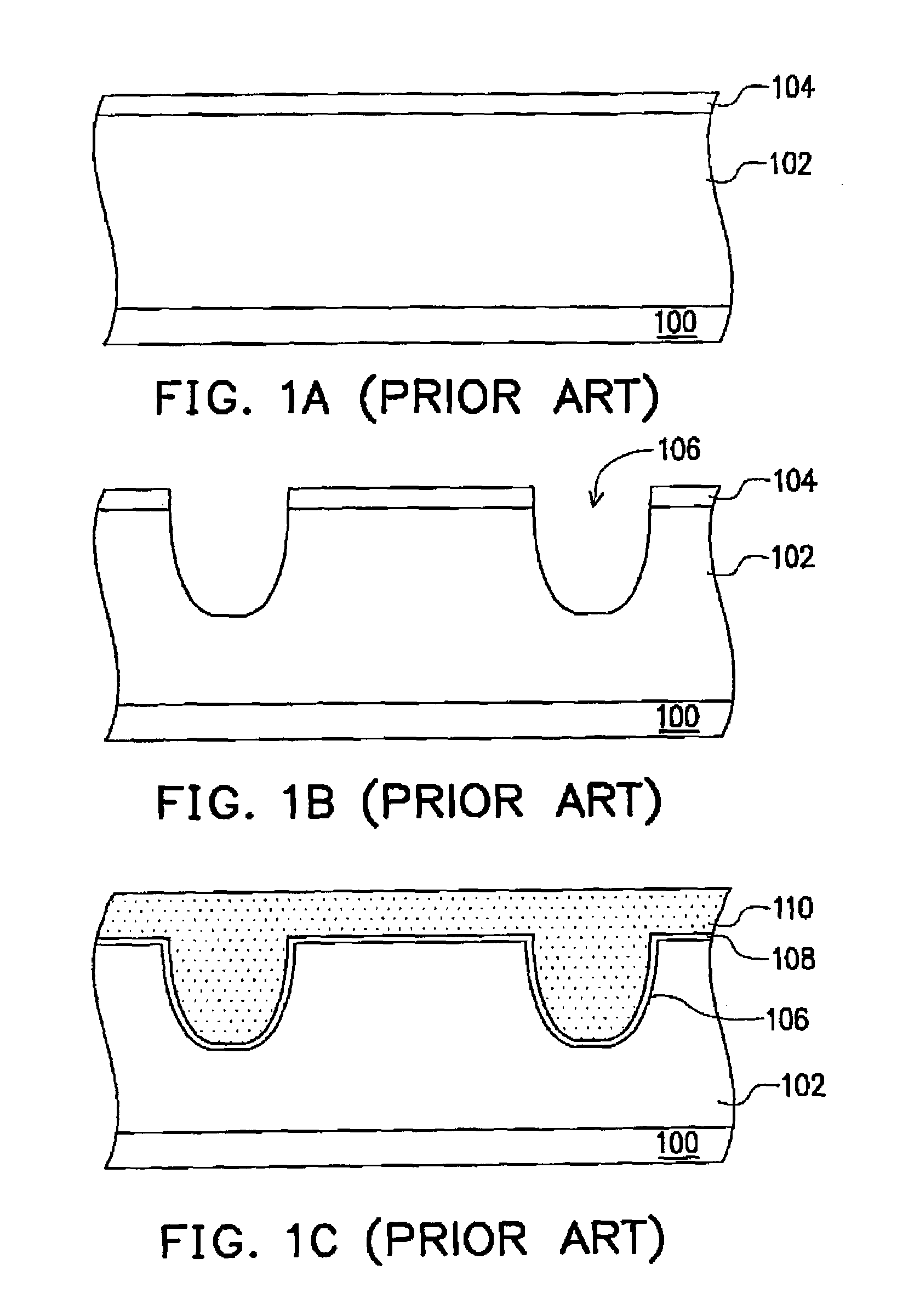

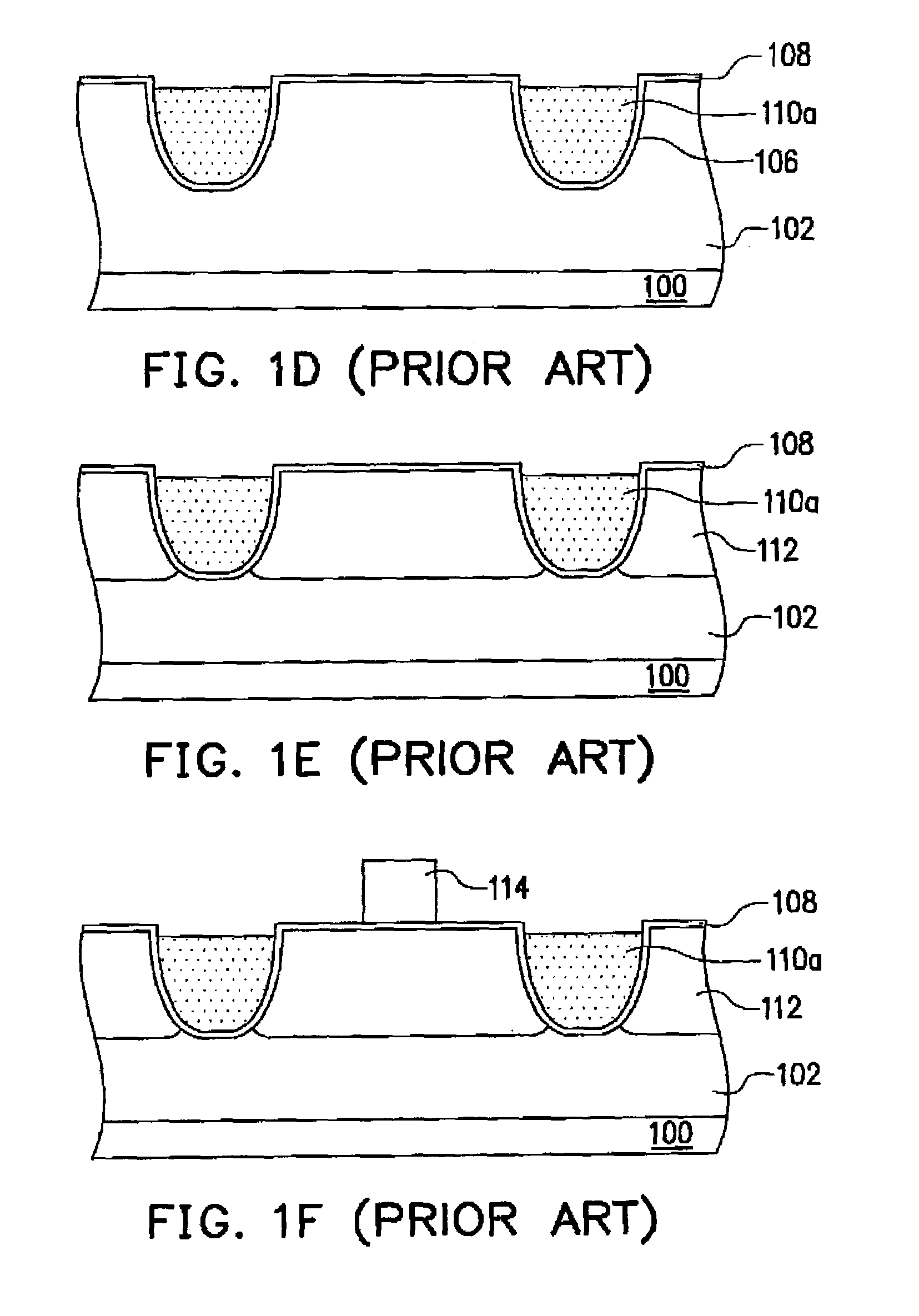

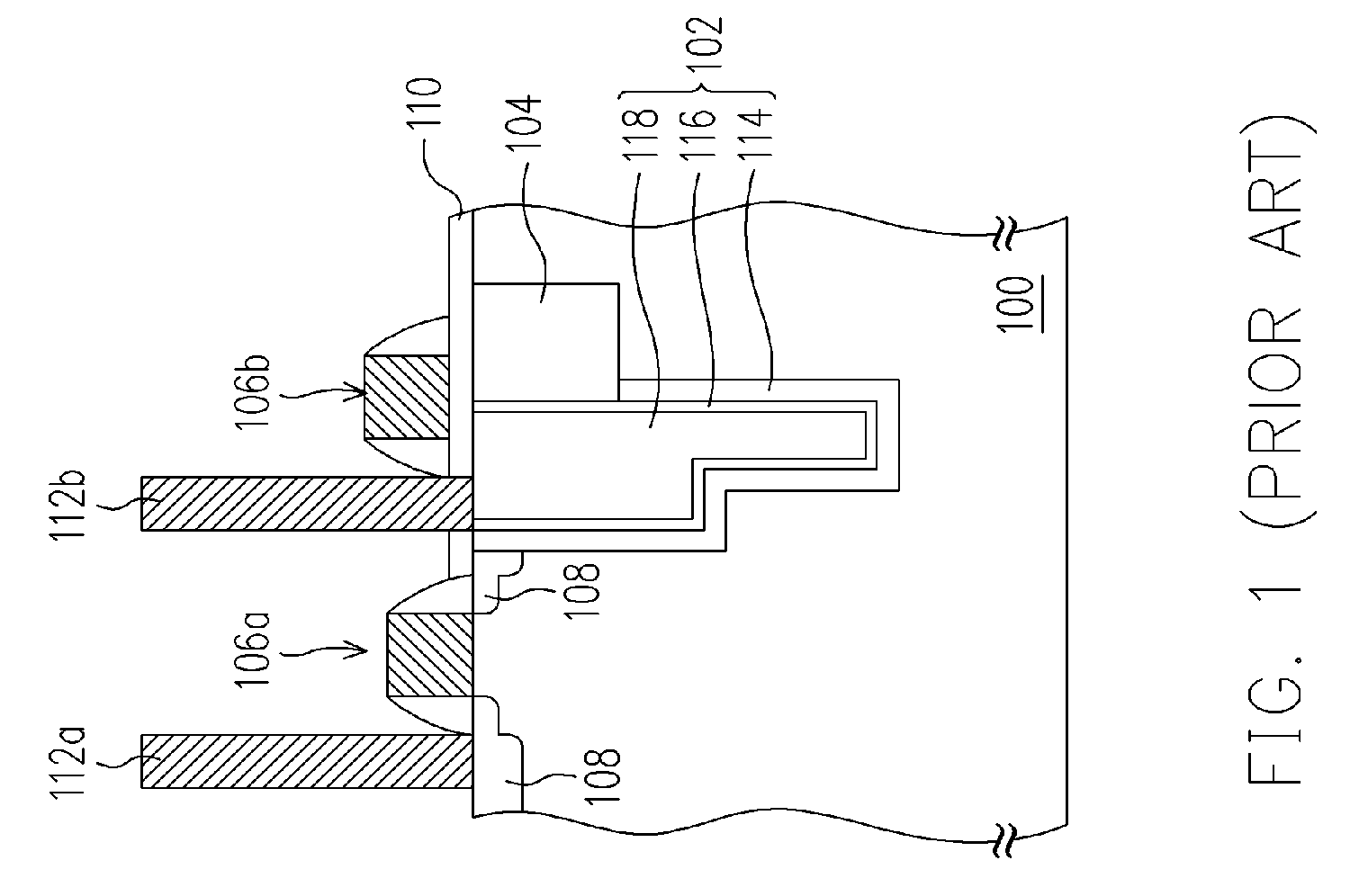

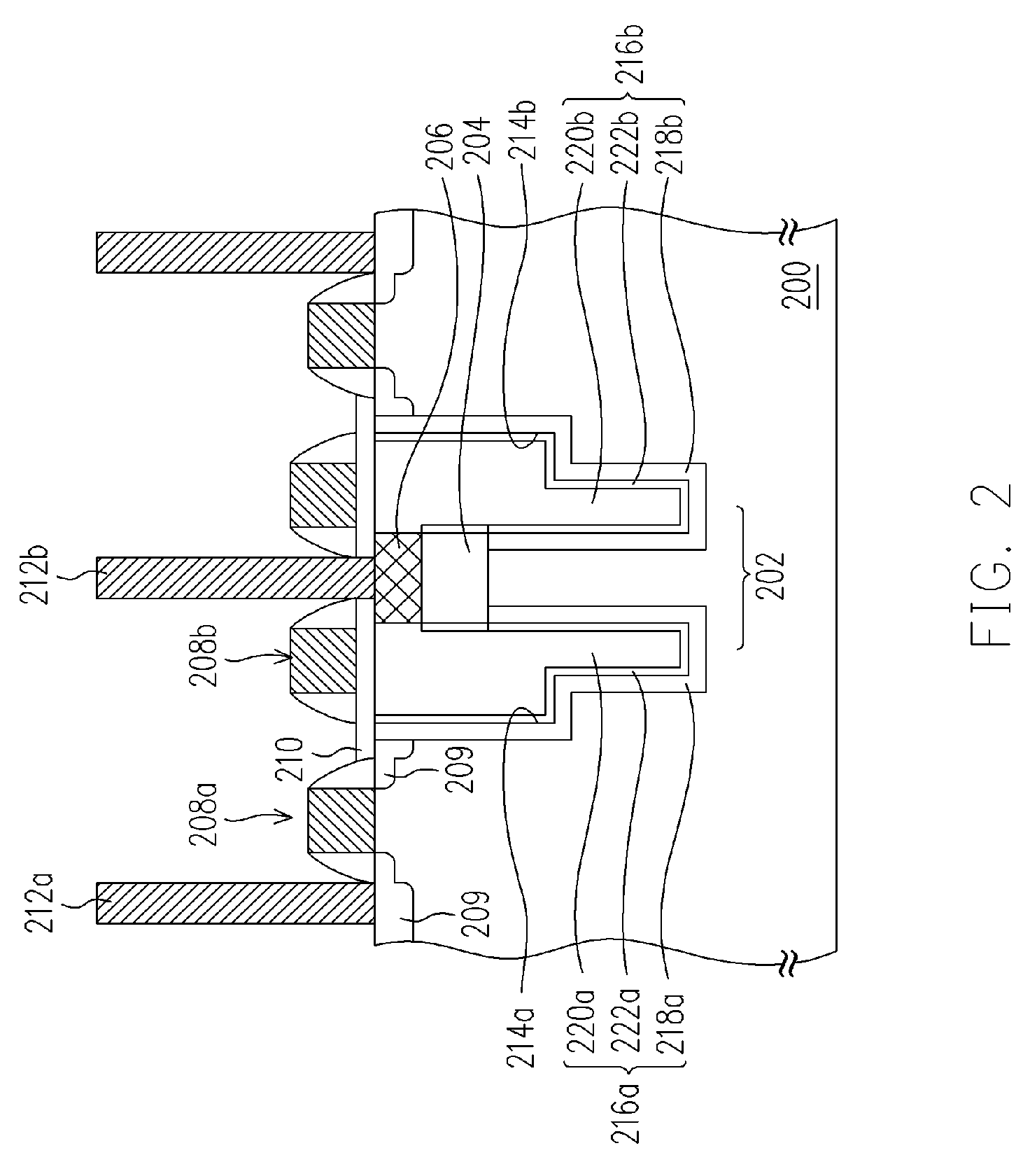

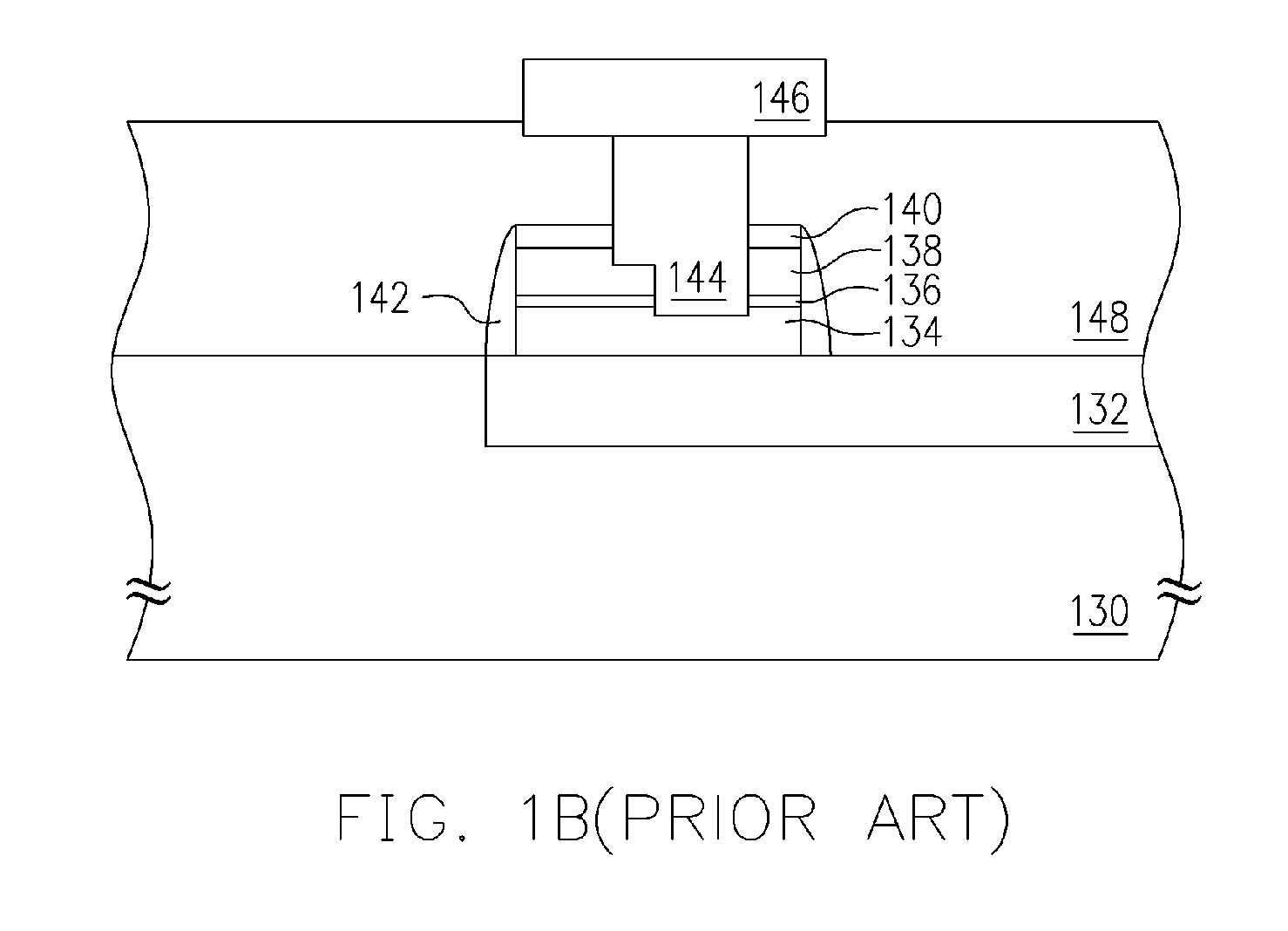

Method of manufacturing contact hole

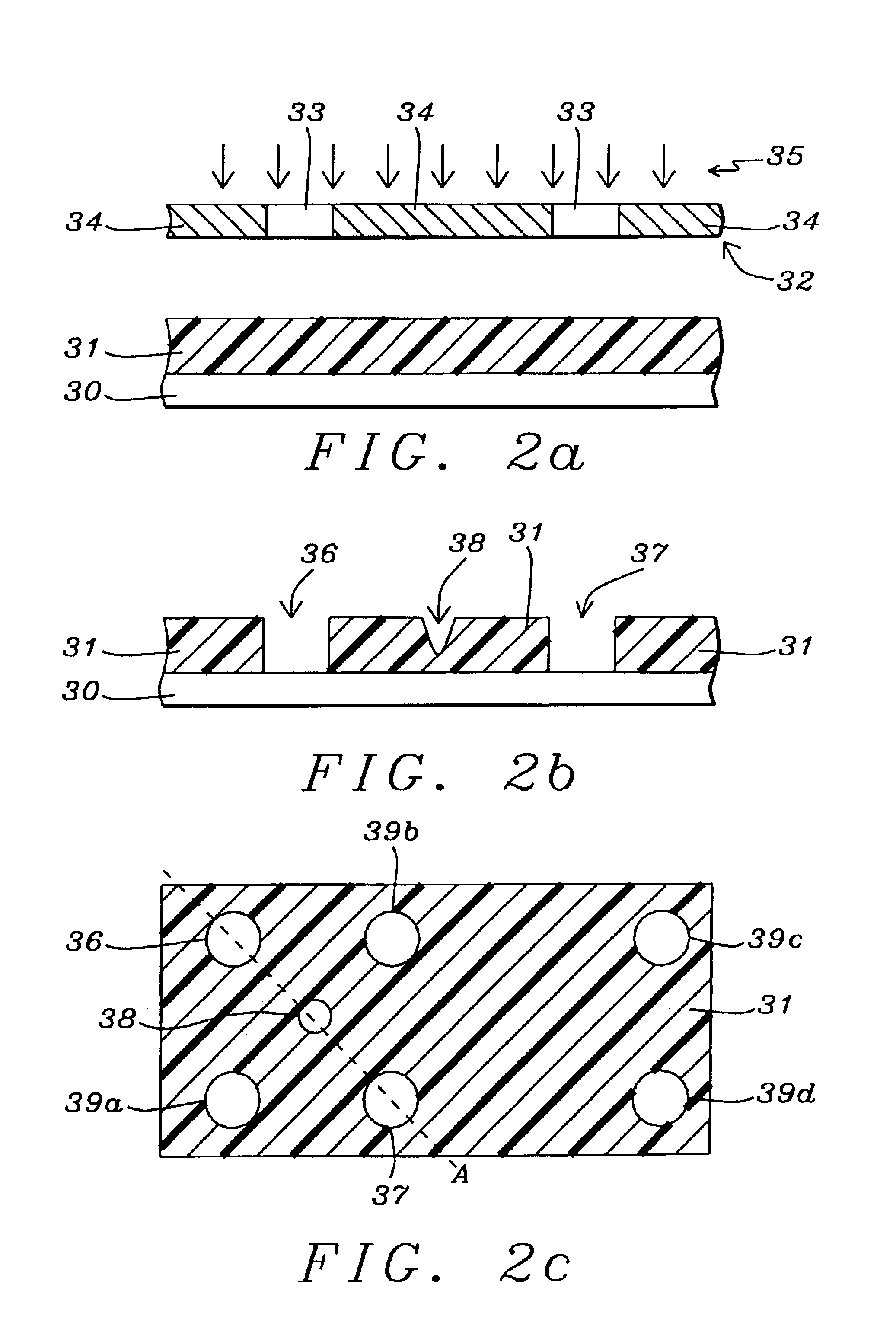

InactiveUS20070082472A1Improve abilitiesIncreased process windowSemiconductor/solid-state device manufacturingEngineeringPhotolithography

A method of manufacturing contact hole is provided. First, a mask layer is formed on a substrate and a plurality of trenches is formed in the mask layer along two directions that cross over each other. The depth of the trenches is not greater than the thickness of the mask layer. However, there is an opening in the mask layer in the place where the trenches cross over each other. The opening exposes the substrate. Part of the substrate exposed by the opening is removed to form a contact hole in the substrate. In photolithography, it is easier to form lines than to form dots. Hence, the dimensions of contact holes are more precisely controlled.

Owner:POWERCHIP SEMICON CORP

Pressure sensor

ActiveUS20110290539A1Facilitate wire bondingImprove visibilitySludge treatmentVolume/mass flow measurementInterference fitEngineering

A pressure sensor includes a sense element port, a support ring and a plurality of interference fit slits to provide a flexible interference fit between the sense element port and the support ring to form a substantially flush lap joint. The sensor also includes an electronics board inside the support ring and attached to planar mounting tabs which provide a stable mounting. Gel flow barriers protect electronics board features from unwanted non-conductive gel. Double-ended symmetrical, tapered contact springs provide manufacturing cost savings and contribute to improved alignment of an interface connector of the sensor.

Owner:SENSATA TECHNOLOGIES INC

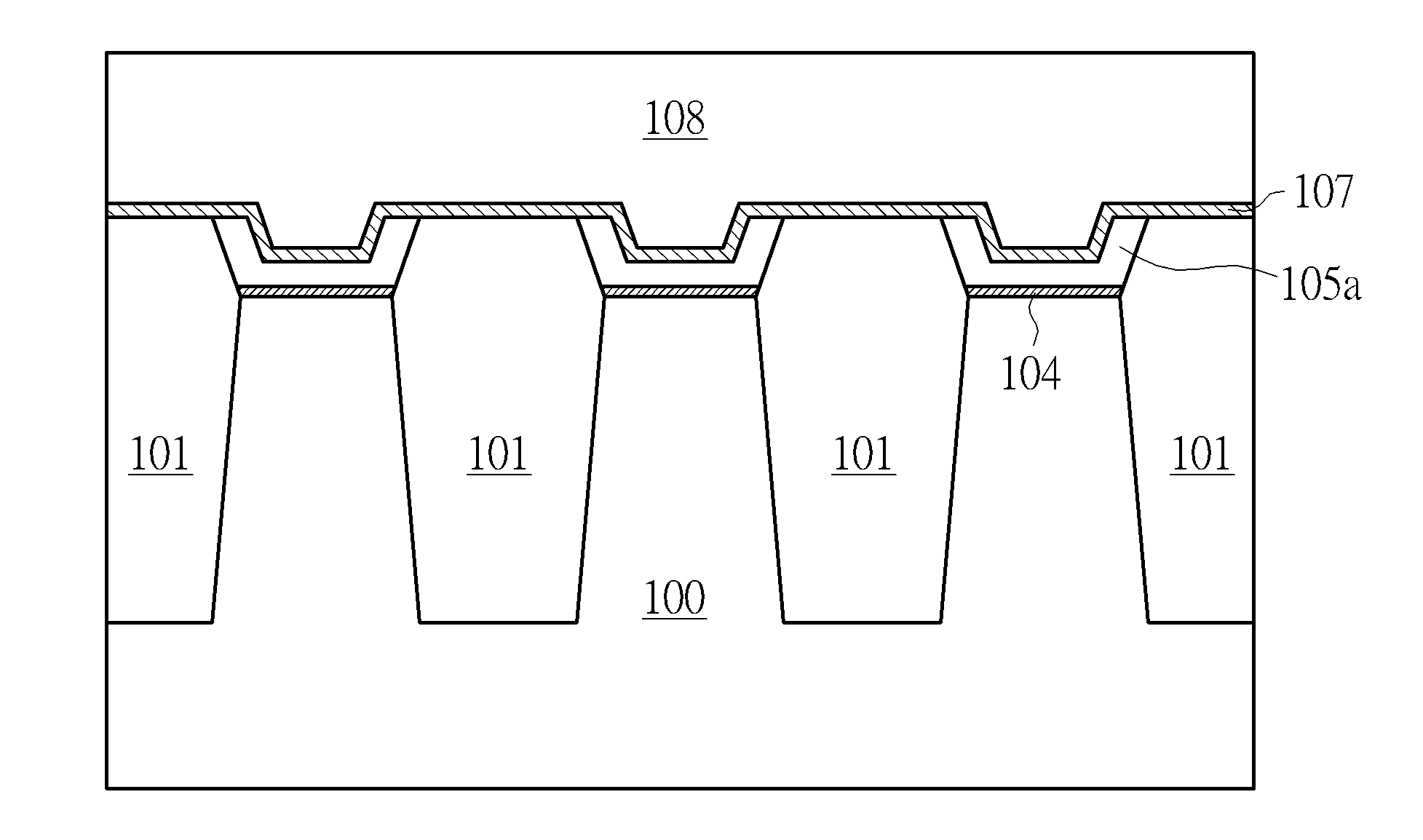

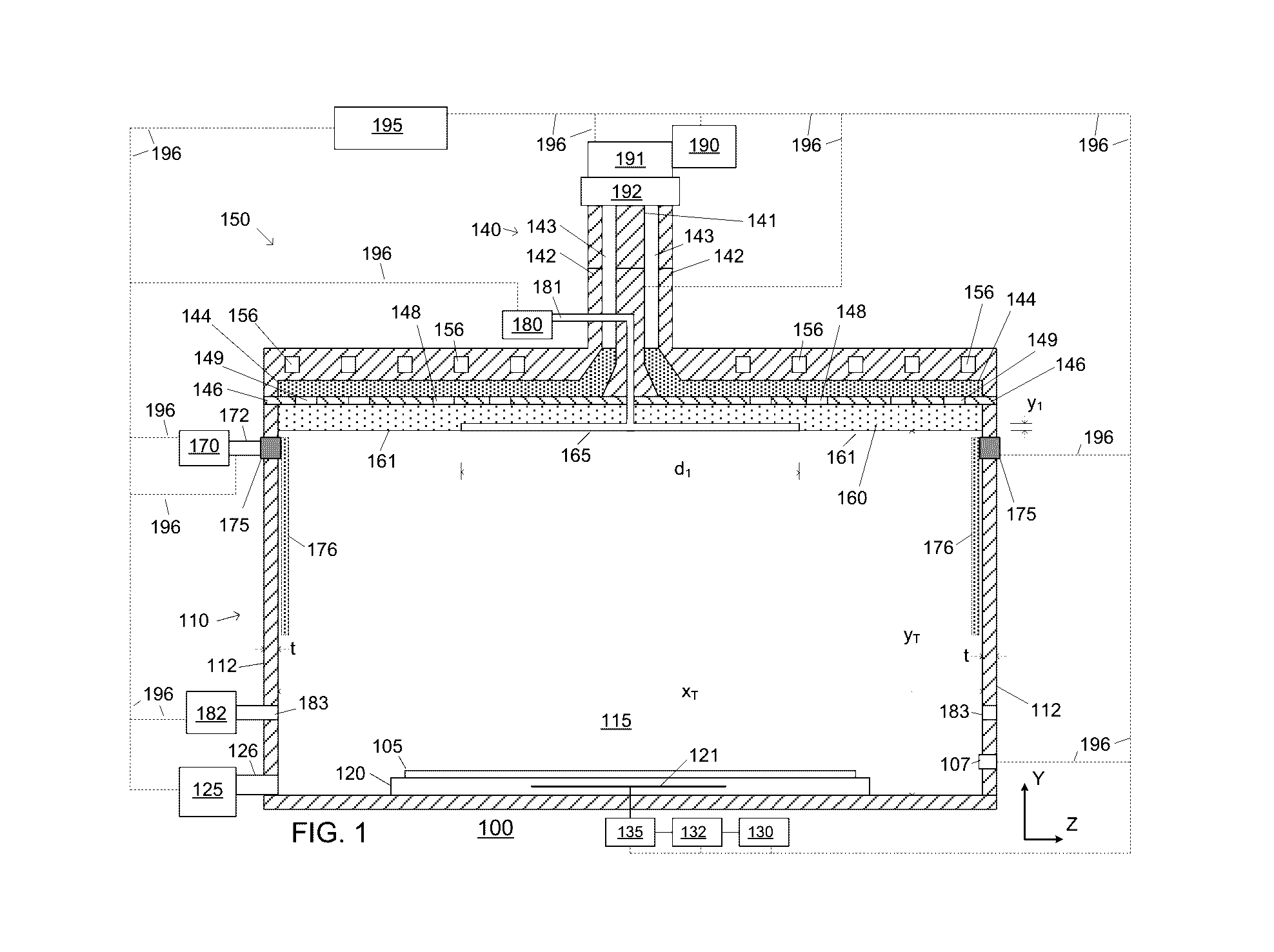

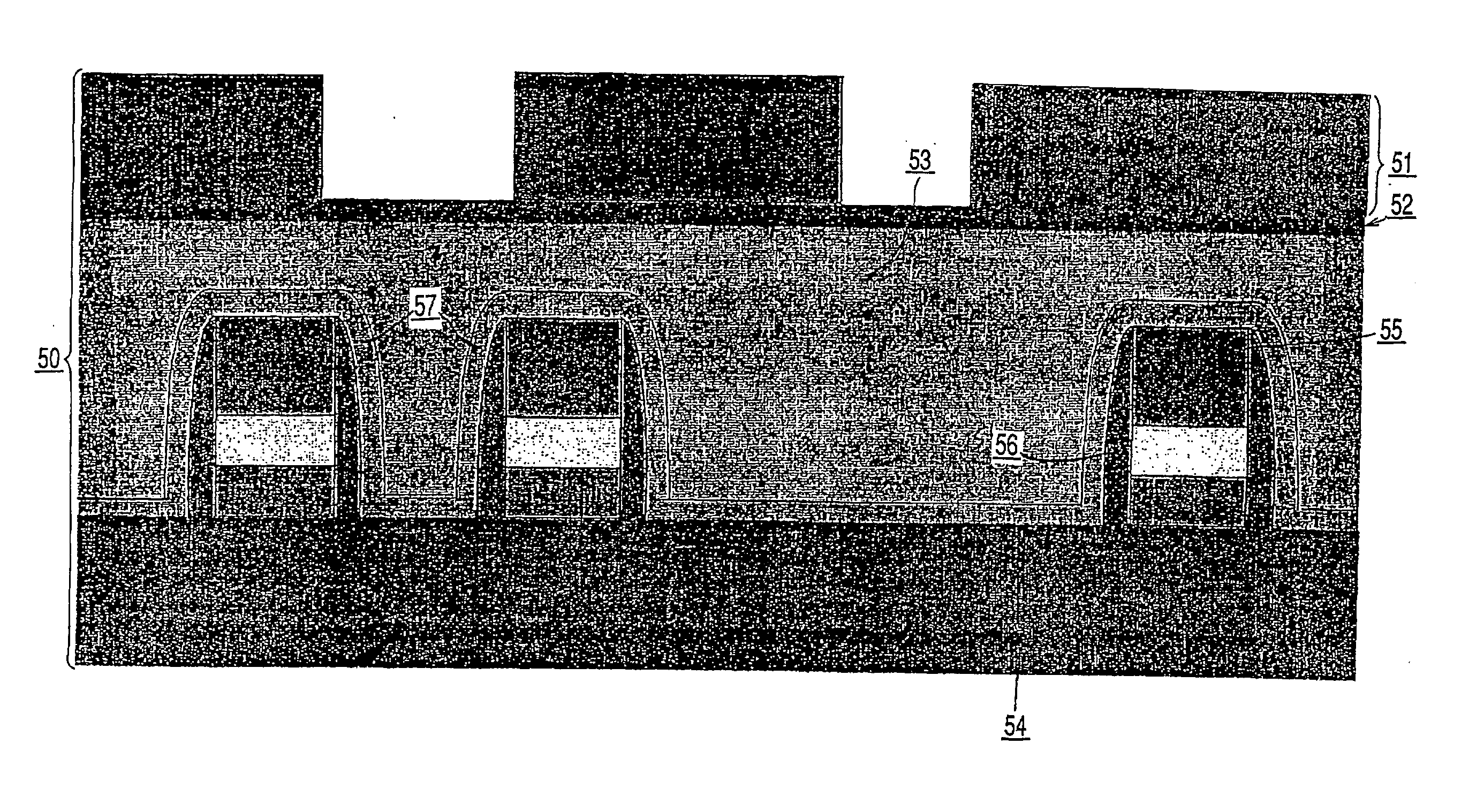

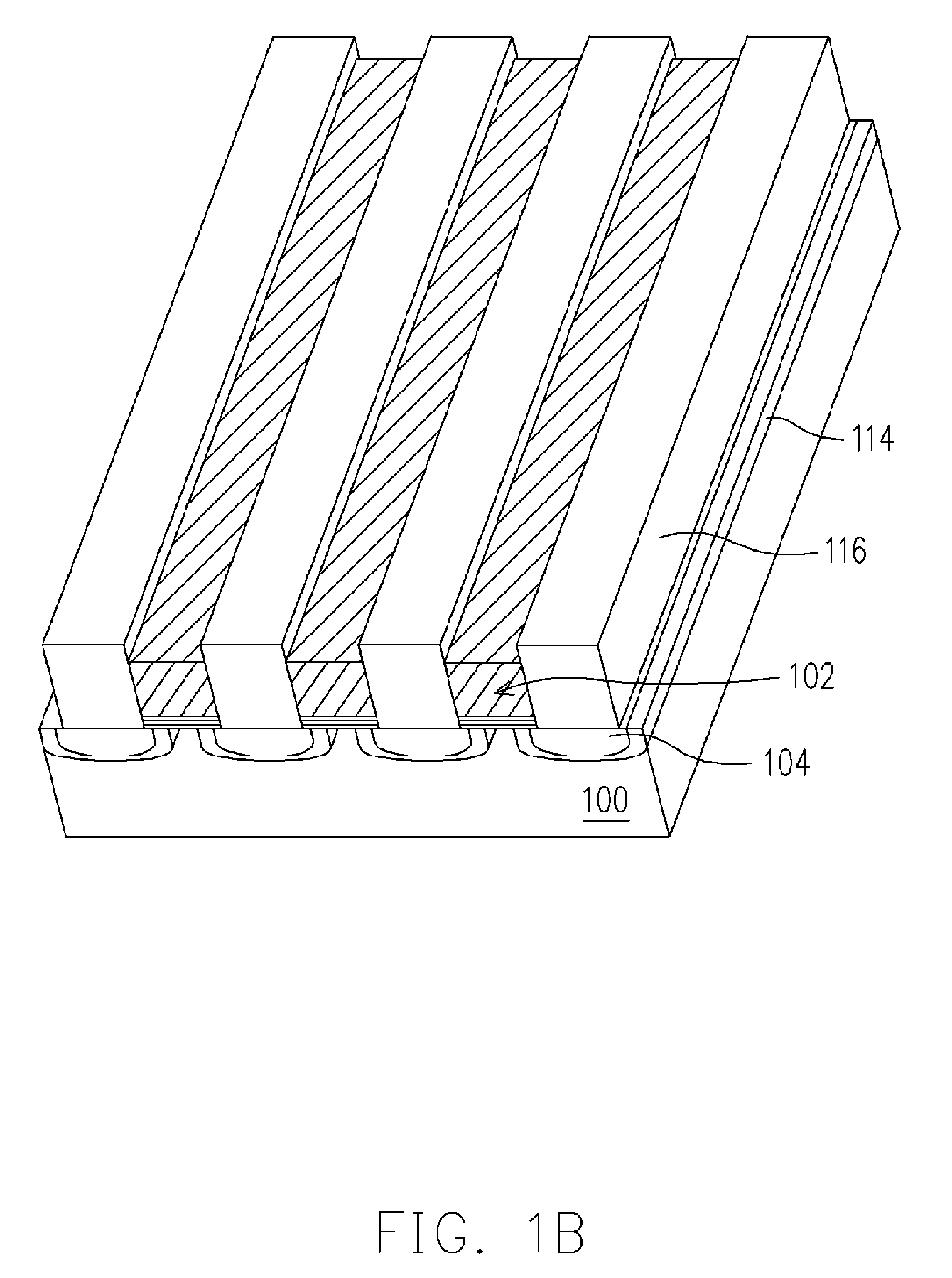

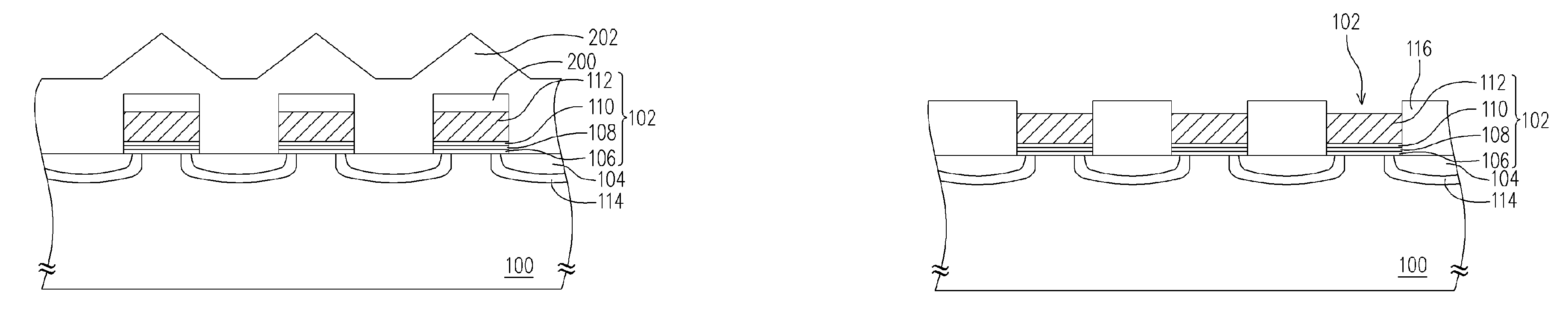

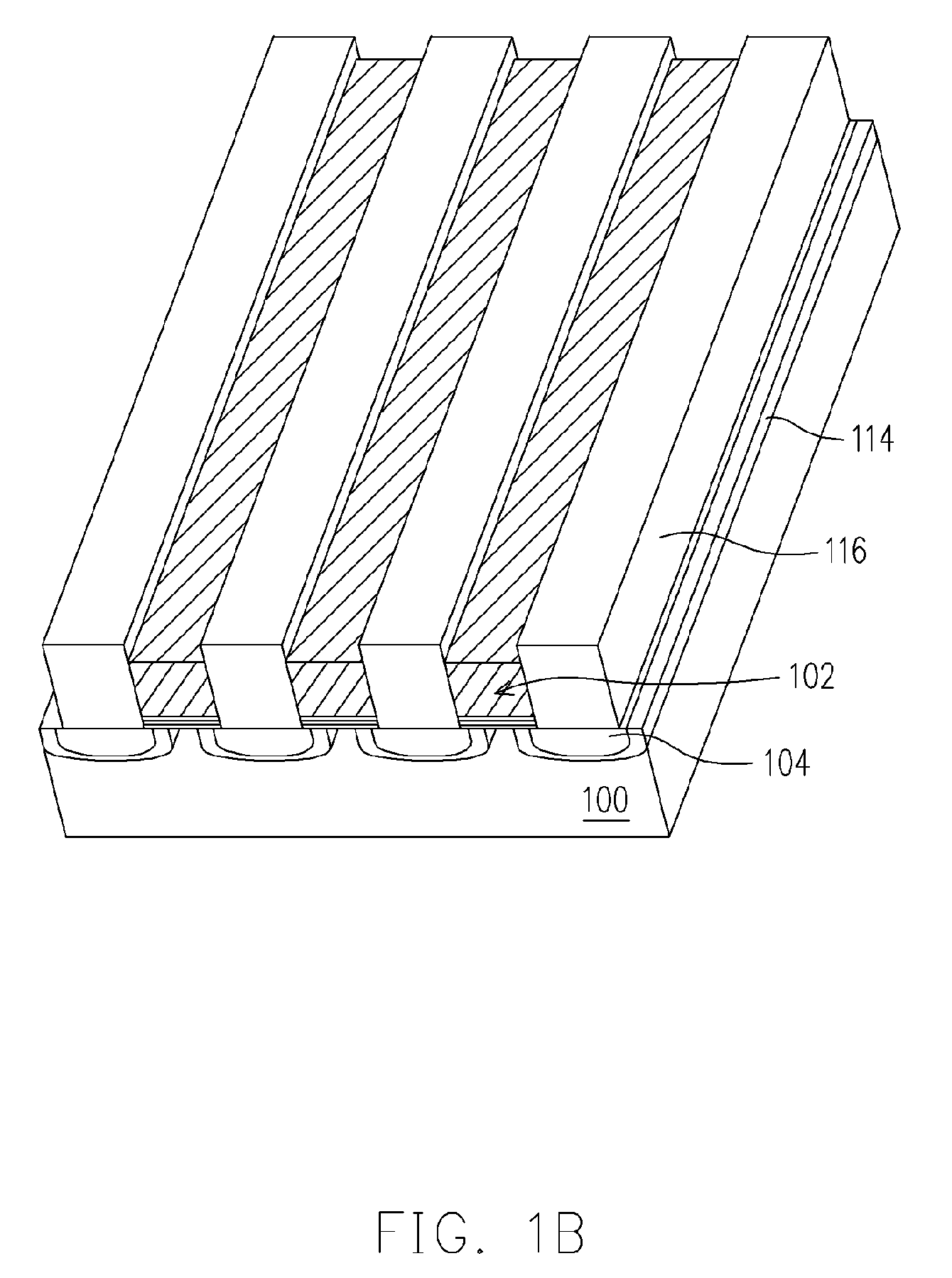

Semiconductor memory device and method for manufacturing the same

InactiveUS20150115346A1Large gate coupling ratioImprove performanceTransistorSolid-state devicesDielectric layerMaterials science

A semiconductor memory device includes a substrate, shallow trench isolations protruding from the substrate, a floating gate formed conformally on the surface of the recess between each shallow trench isolation, a tunnel layer formed between each floating gate and the substrate, a dielectric layer formed conformally on the floating gates, and a control gate formed on the dielectric layer.

Owner:UNITED MICROELECTRONICS CORP

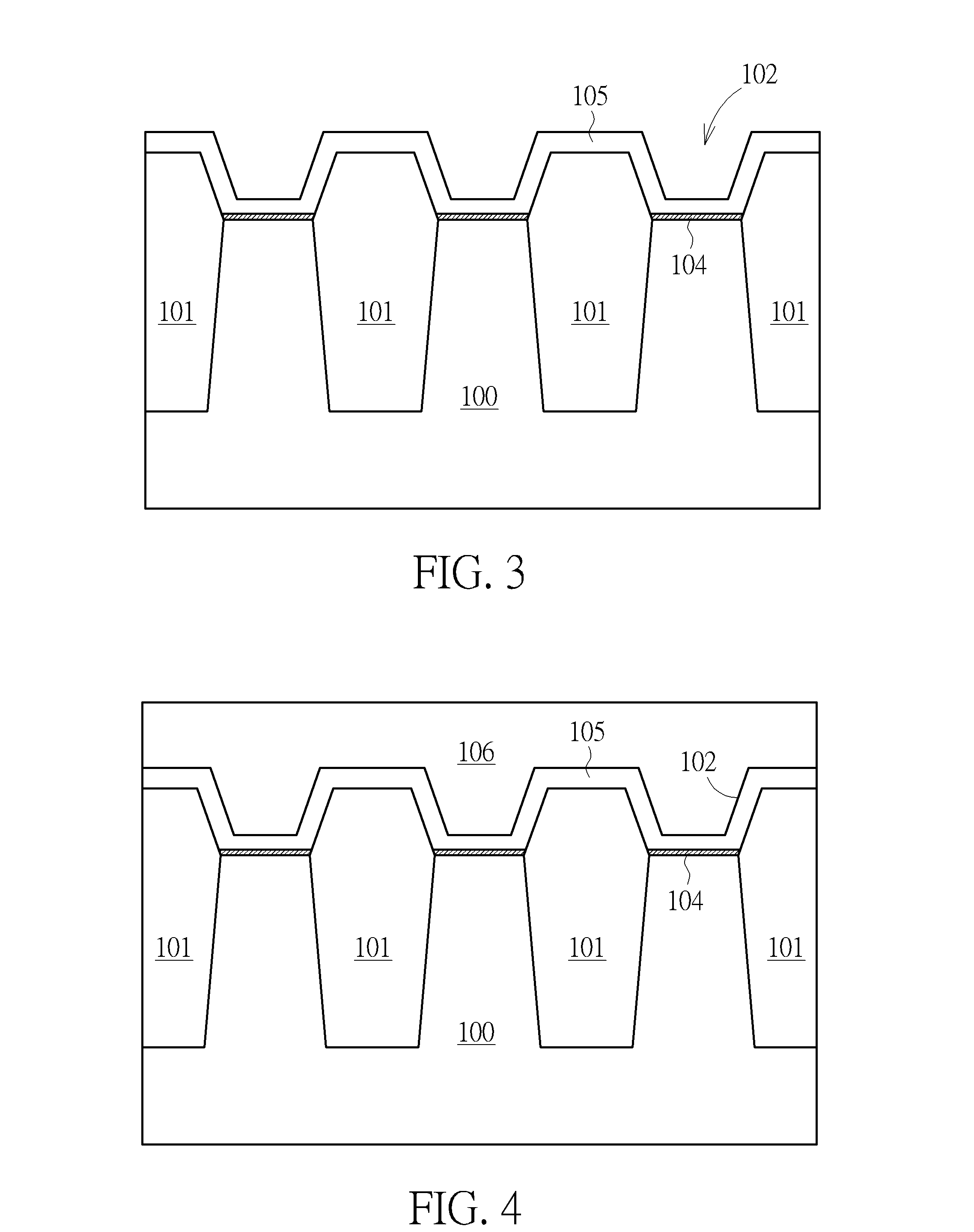

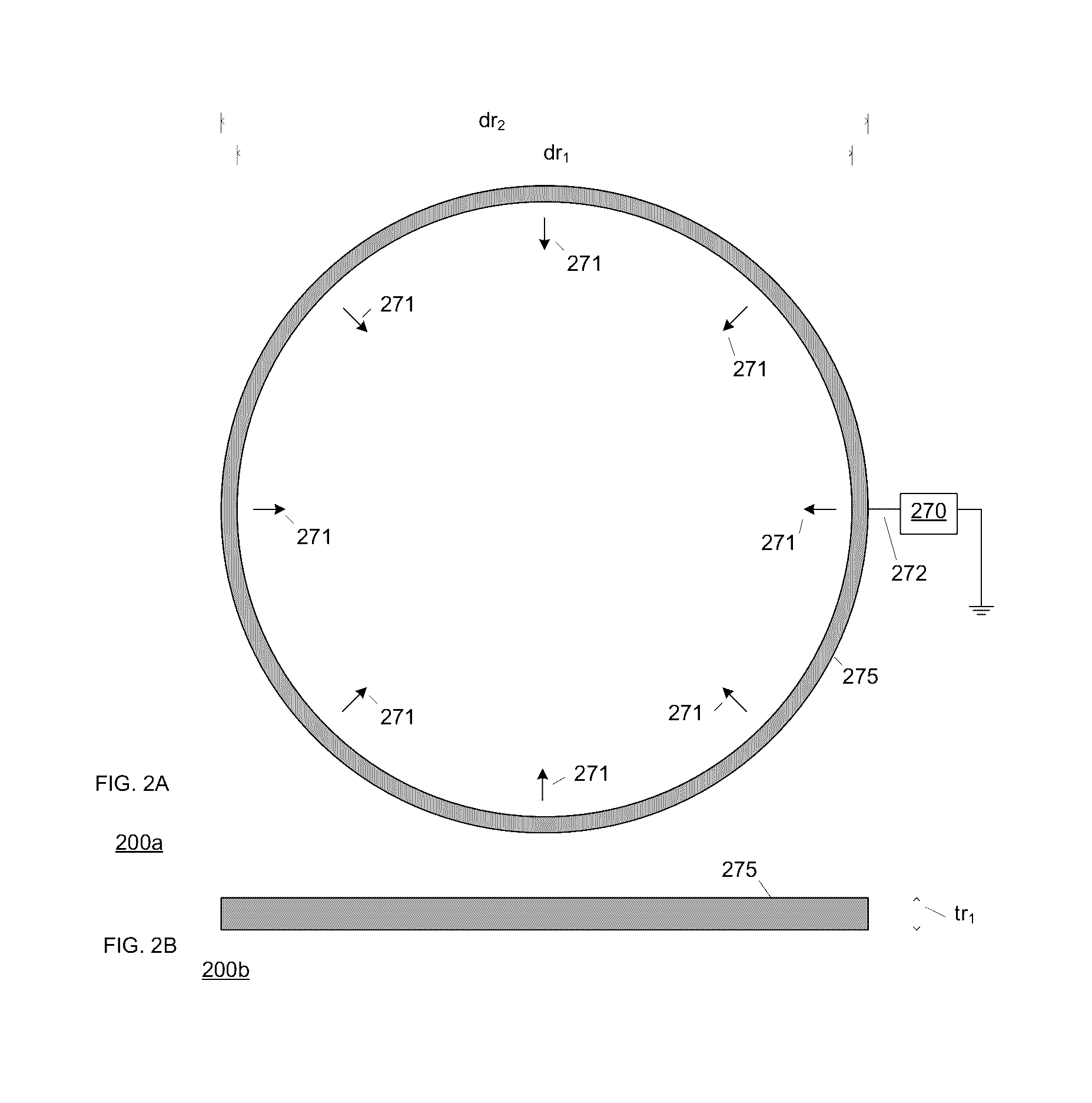

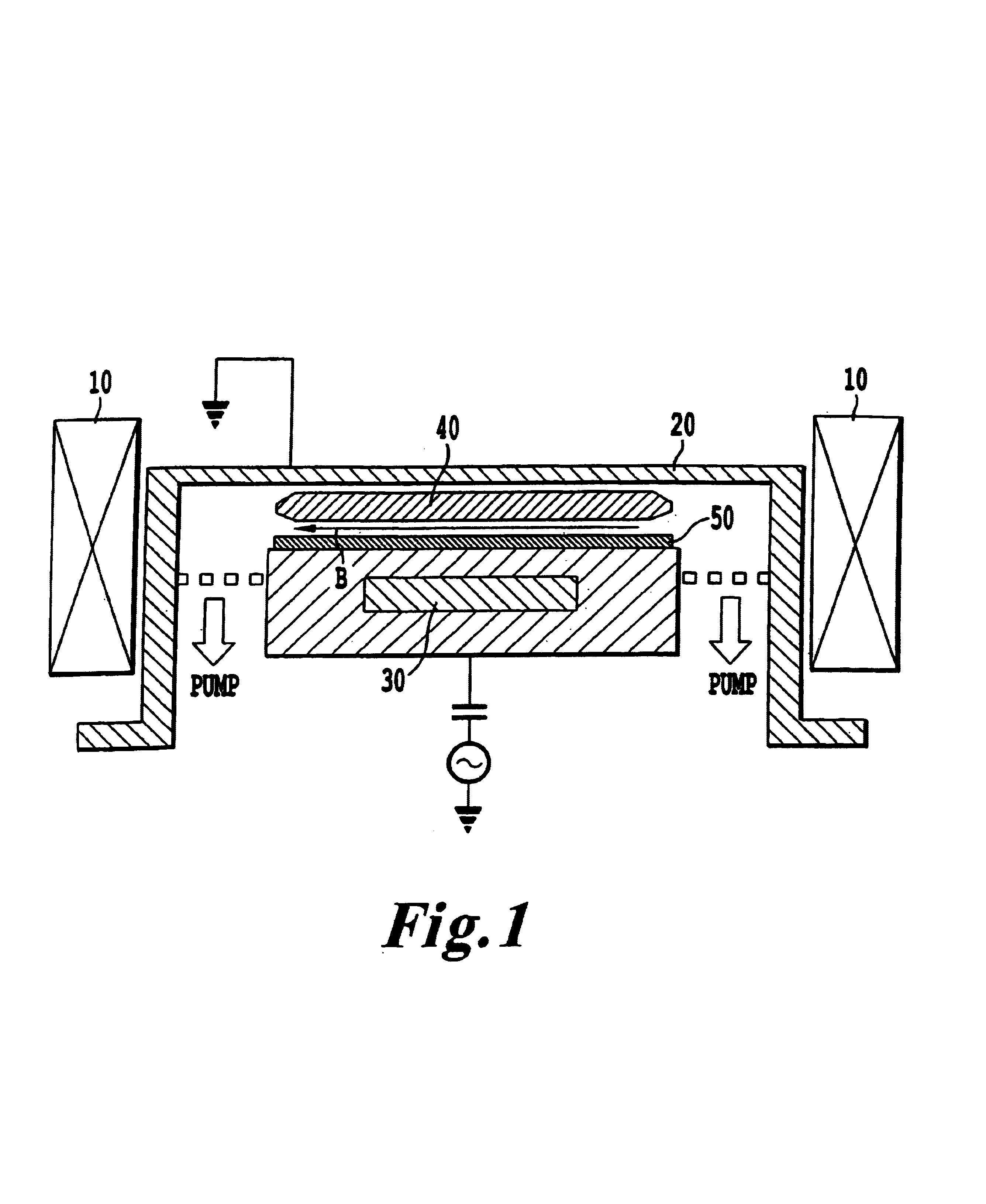

Plasma Generation and Control Using a DC Ring

ActiveUS20160300738A1Large processing windowUnified controlElectric discharge tubesSemiconductor/solid-state device manufacturingSurface waveProcess window

The present invention provides a SWP (surface wave plasma) processing system that does not create underdense conditions when operating at low microwave power and high gas pressure, thereby achieving a larger process window. The DC ring subsystem can be used to adjust the edge to central plasma density ratio to achieve uniformity control in the SWP processing system.

Owner:TOKYO ELECTRON LTD

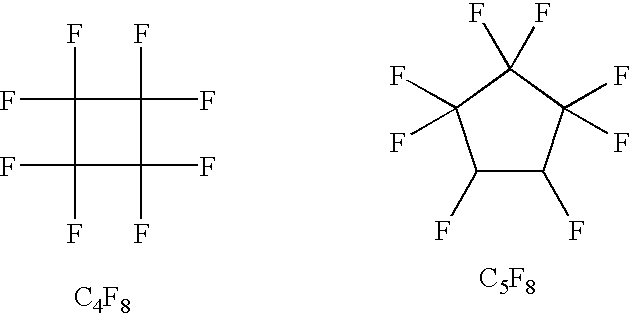

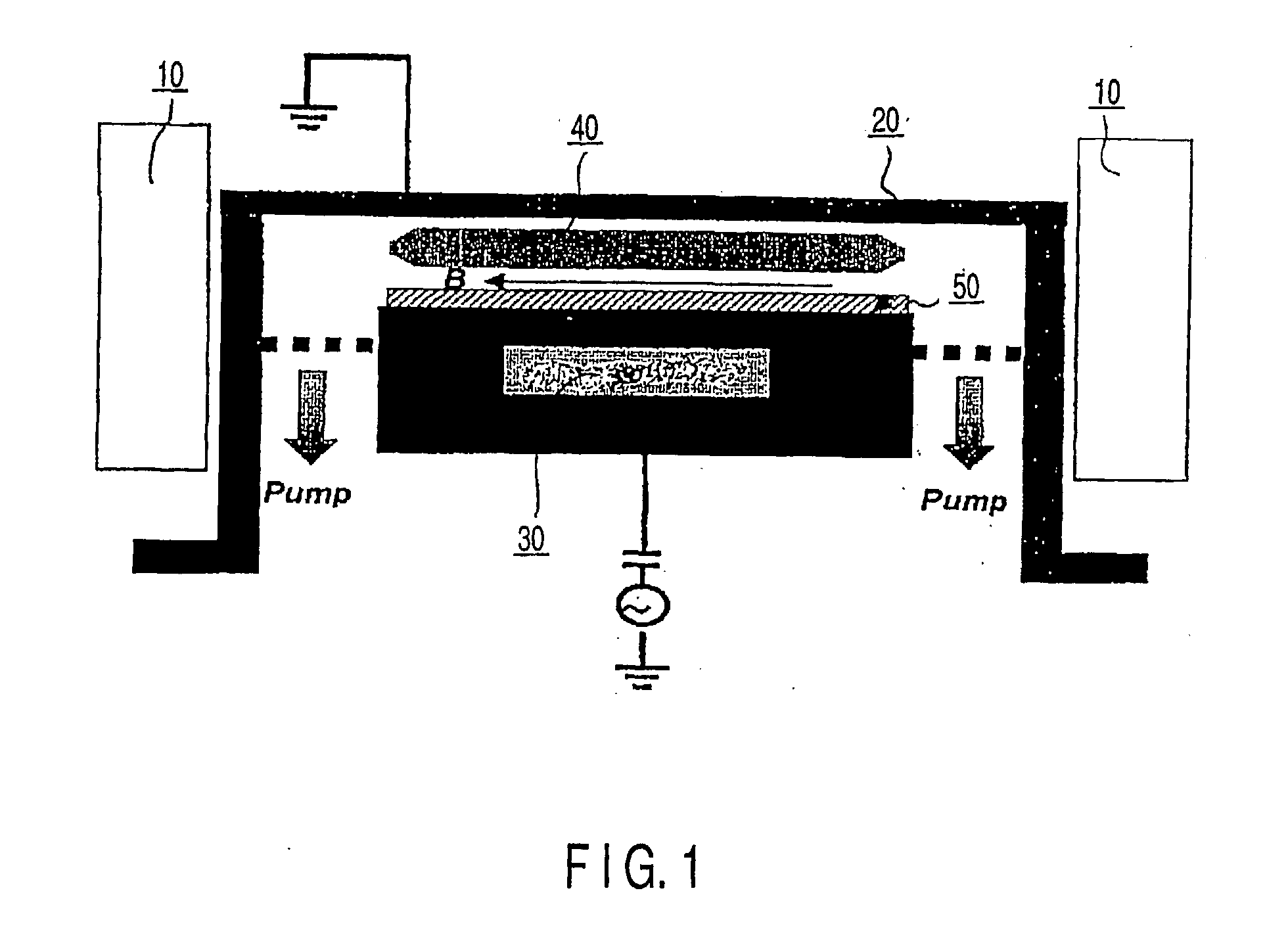

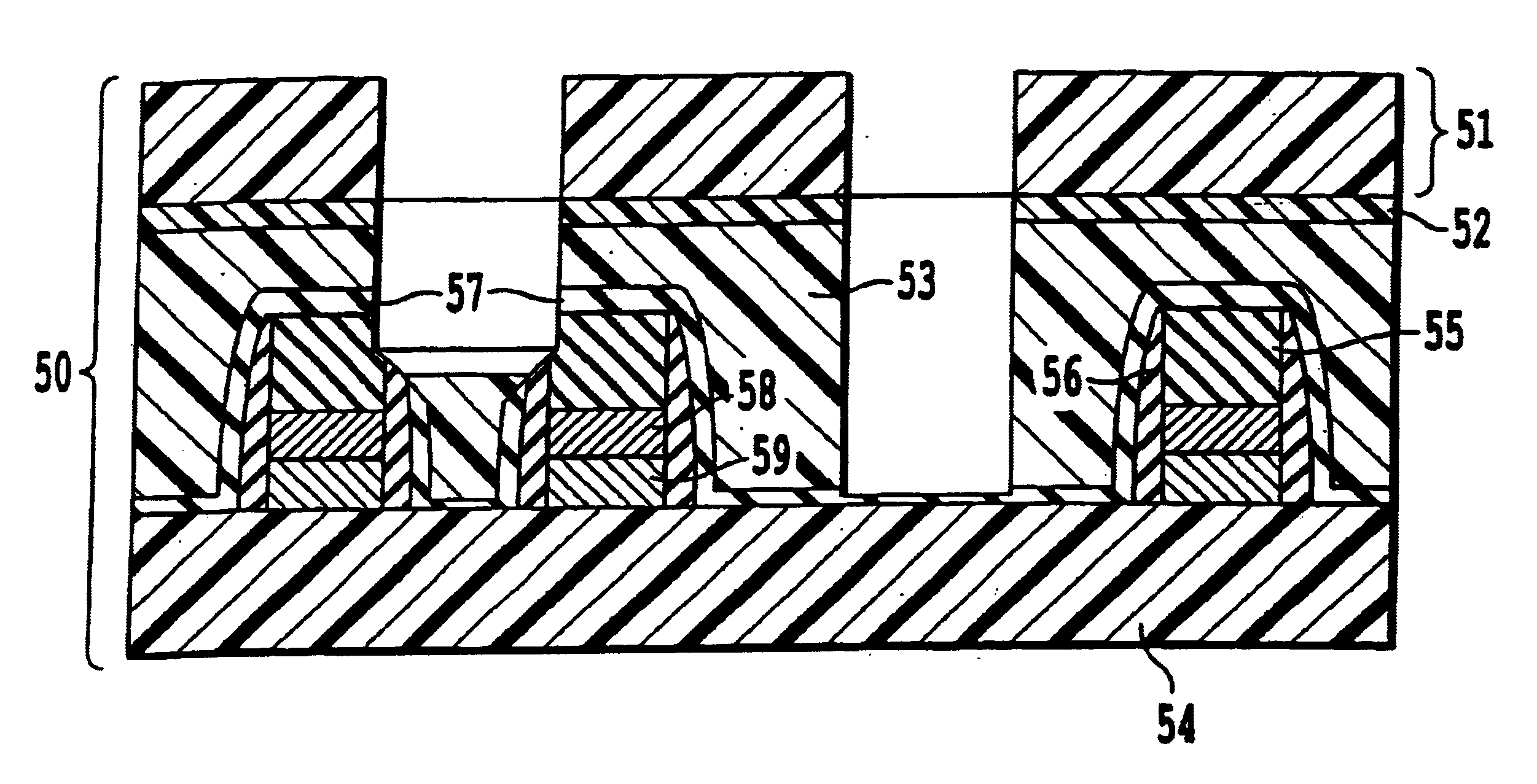

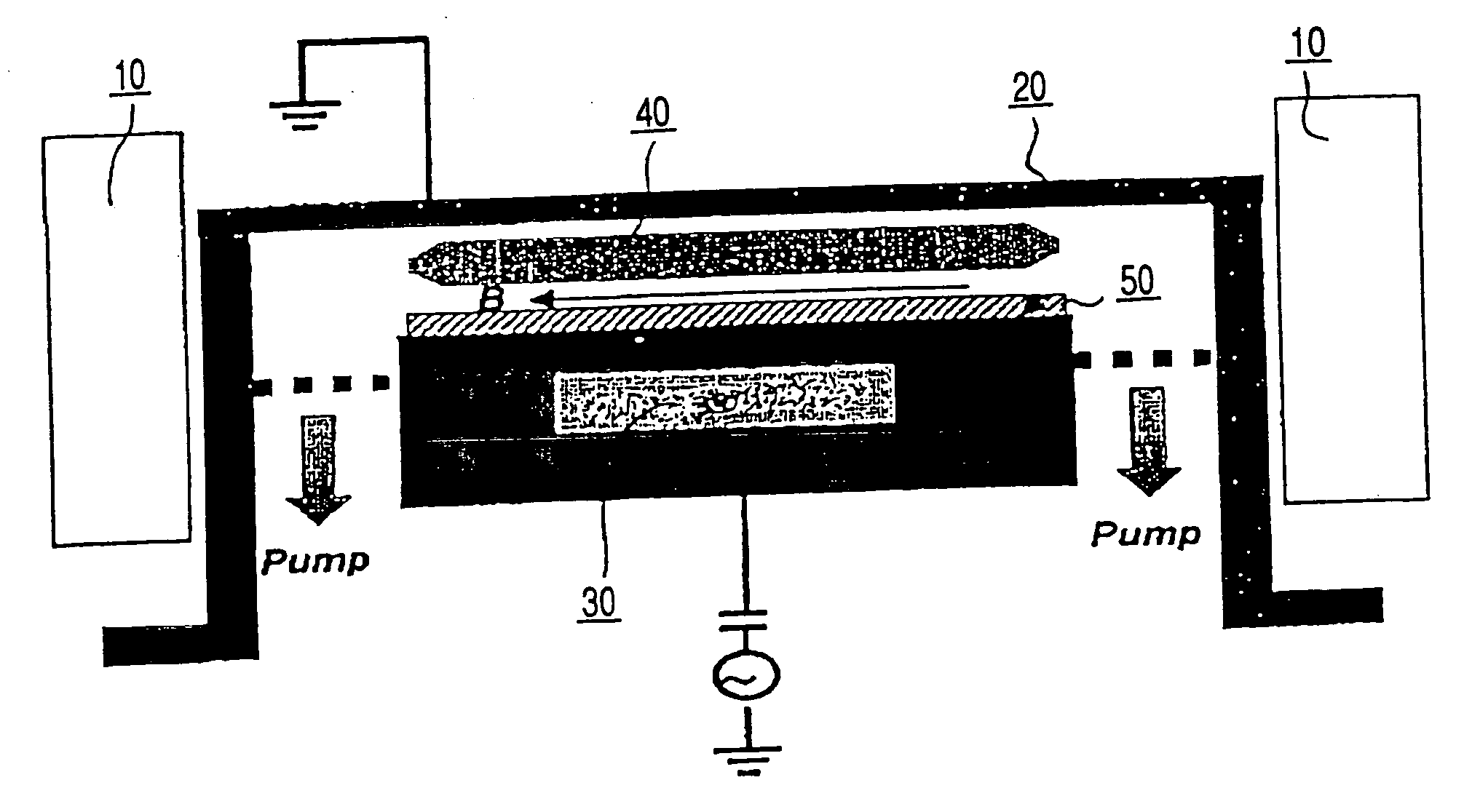

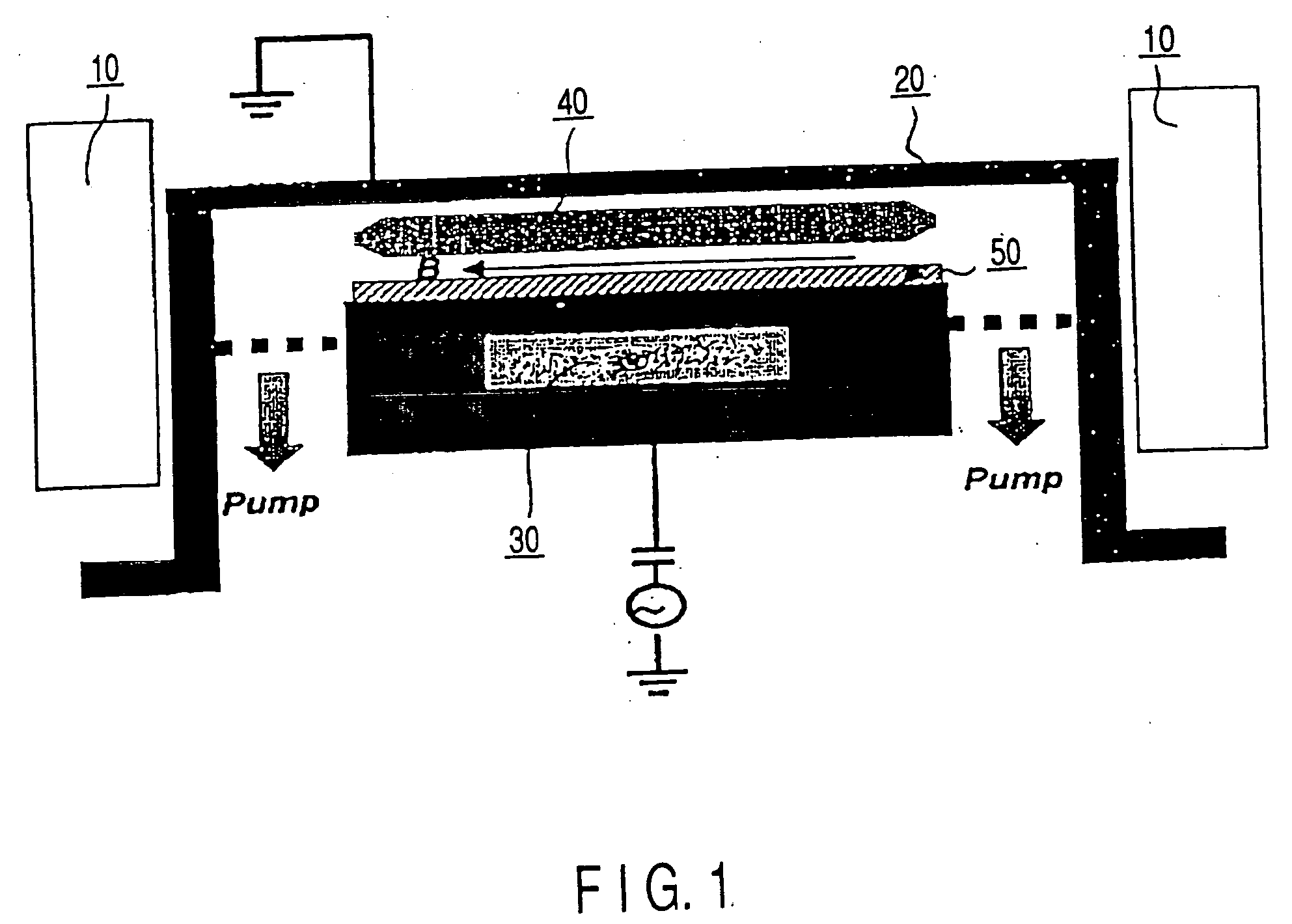

Method of high selectivity sac etching

InactiveUS20030127422A1High SiO/SiN selectivityAvoiding etch stopDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingProcess window

A method for SAC etching is provided involving a) etching a Si wafer having a nitride present thereon with a first etching gas containing a first perfluorocarbon and carbon monoxide, and b) etching the resultant Si wafer having an initially etched nitride photoresist thereon with a second etching gas containing a second perfluorocarbon in the substantial absence of carbon monoxide, wherein the etching steps a) and b) are performed at high RF power and low pressure compared to conventional processes to provide higher selectivity etching and a larger process window for SAC etching, as well as the ability to perform SAC etching and island contact etching under the same conditions with high verticality of the island contact and SAC walls.

Owner:TOKYO ELECTRON LTD

Method of high selectivity SAC etching

InactiveUS7030029B2High selectivityAvoiding etch stopDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingProcess window

A method for SAC etching is provided involving a) etching a Si wafer having a nitride present thereon with a first etching gas containing a first perfluorocarbon and carbon monoxide, and b) etching the resultant Si wafer having an initially etched nitride photoresist thereon with a second etching gas containing a second perfluorocarbon in the substantial absence of carbon monoxide, wherein the etching steps a) and b) are performed at high RF power and low pressure compared to conventional processes to provide higher selectivity etching and a larger process window for SAC etching, as well as the ability to perform SAC etching and island contact etching under the same conditions with high verticality of the island contact and SAC walls.

Owner:TOKYO ELECTRON LTD

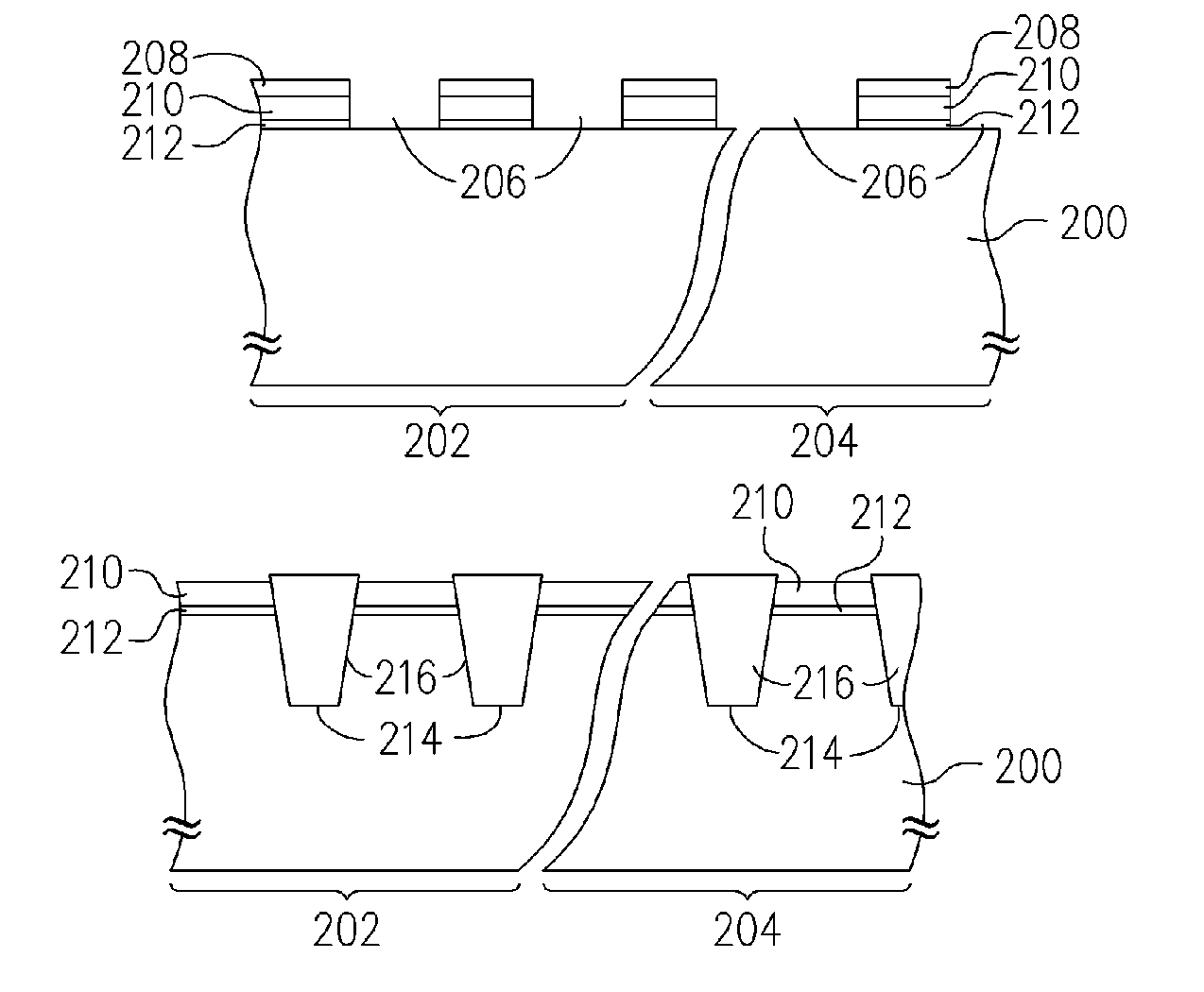

Non-volatile memory and fabricating method thereof

ActiveUS7214983B2Misalignment problemHighly integratedSolid-state devicesSemiconductor devicesEngineeringDielectric layer

Owner:MACRONIX INT CO LTD

Method of high selectivity SAC etching

InactiveUS20050263487A1High selectivityAvoiding etch stopDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingProcess window

Owner:TOKYO ELECTRON LTD

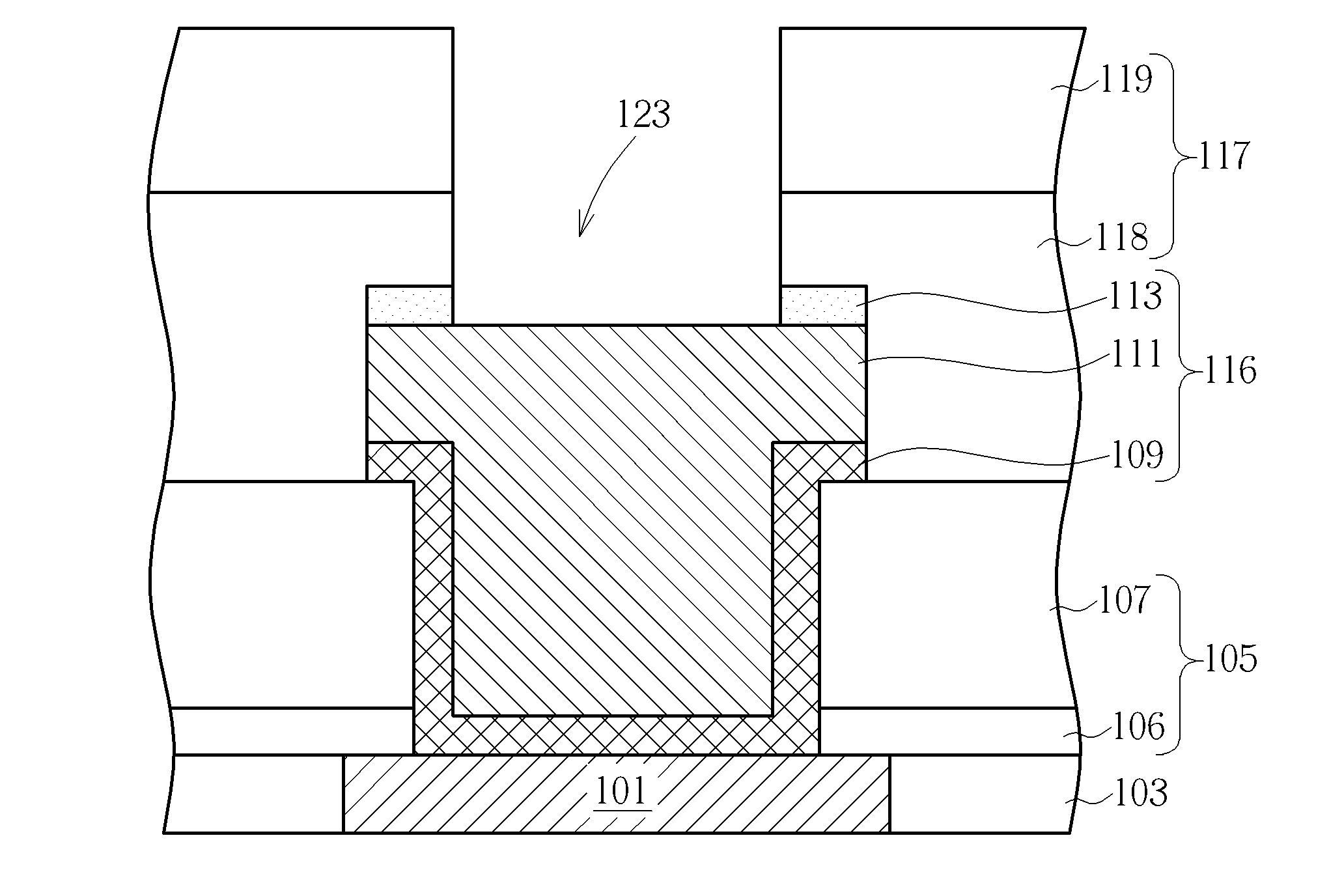

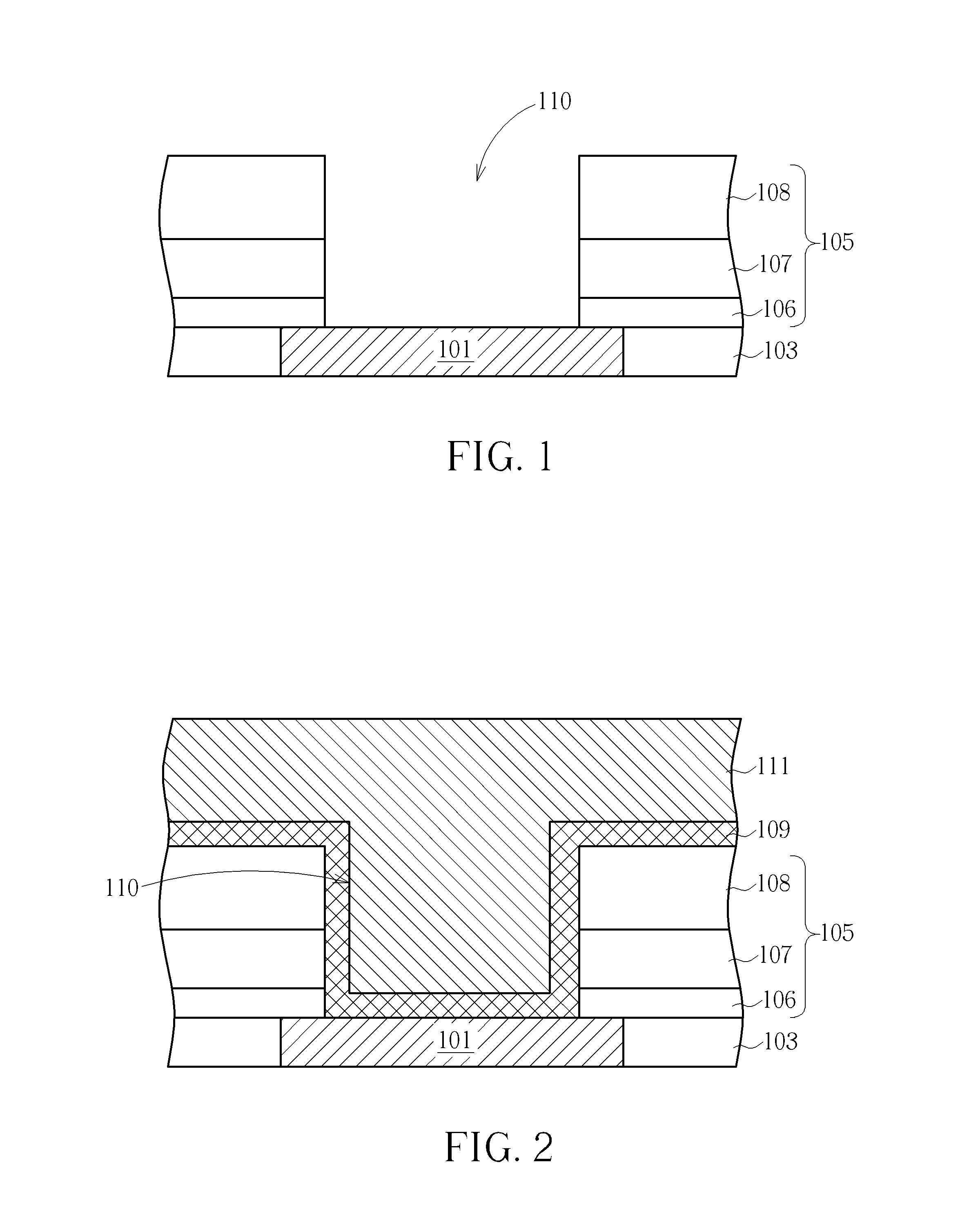

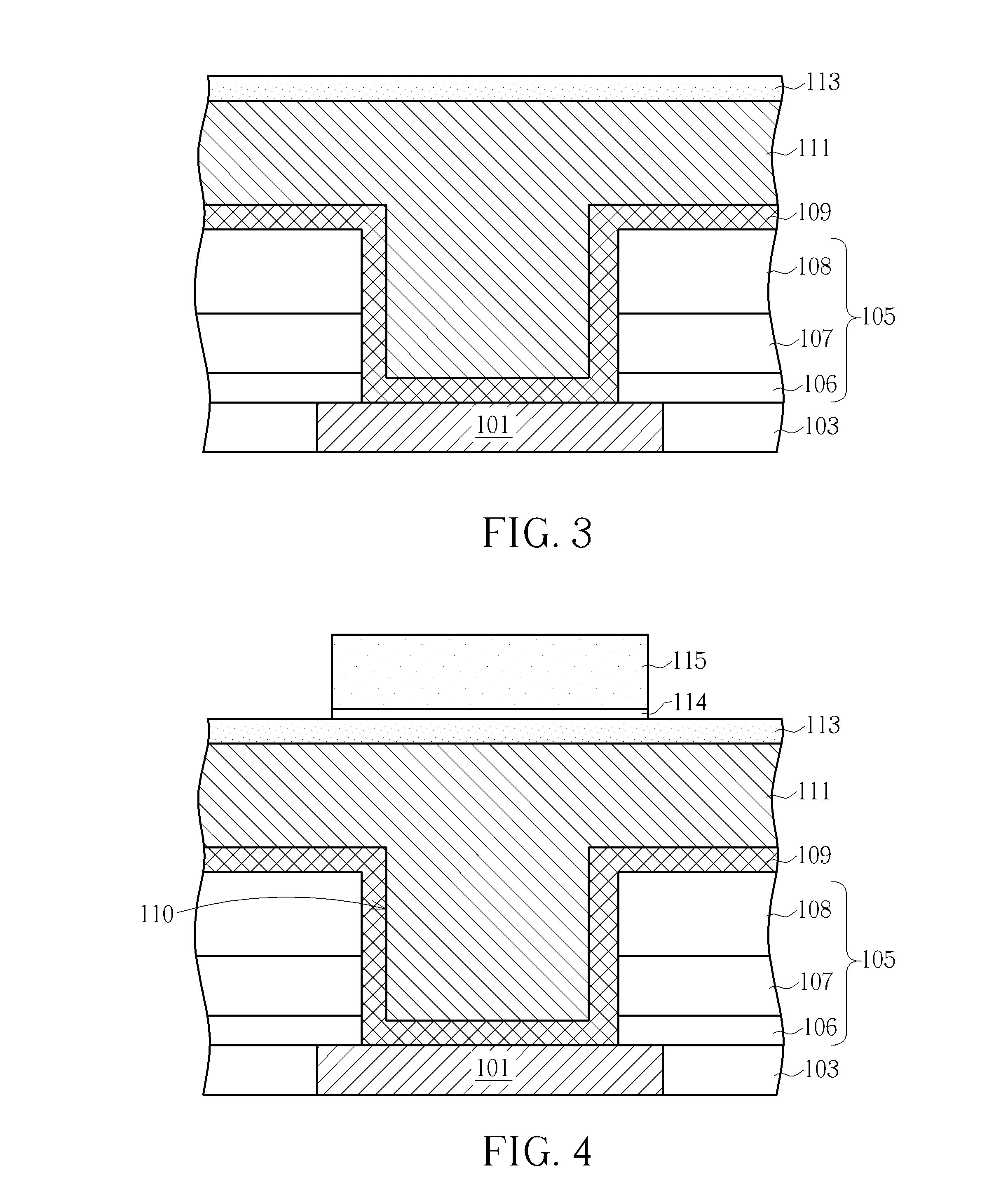

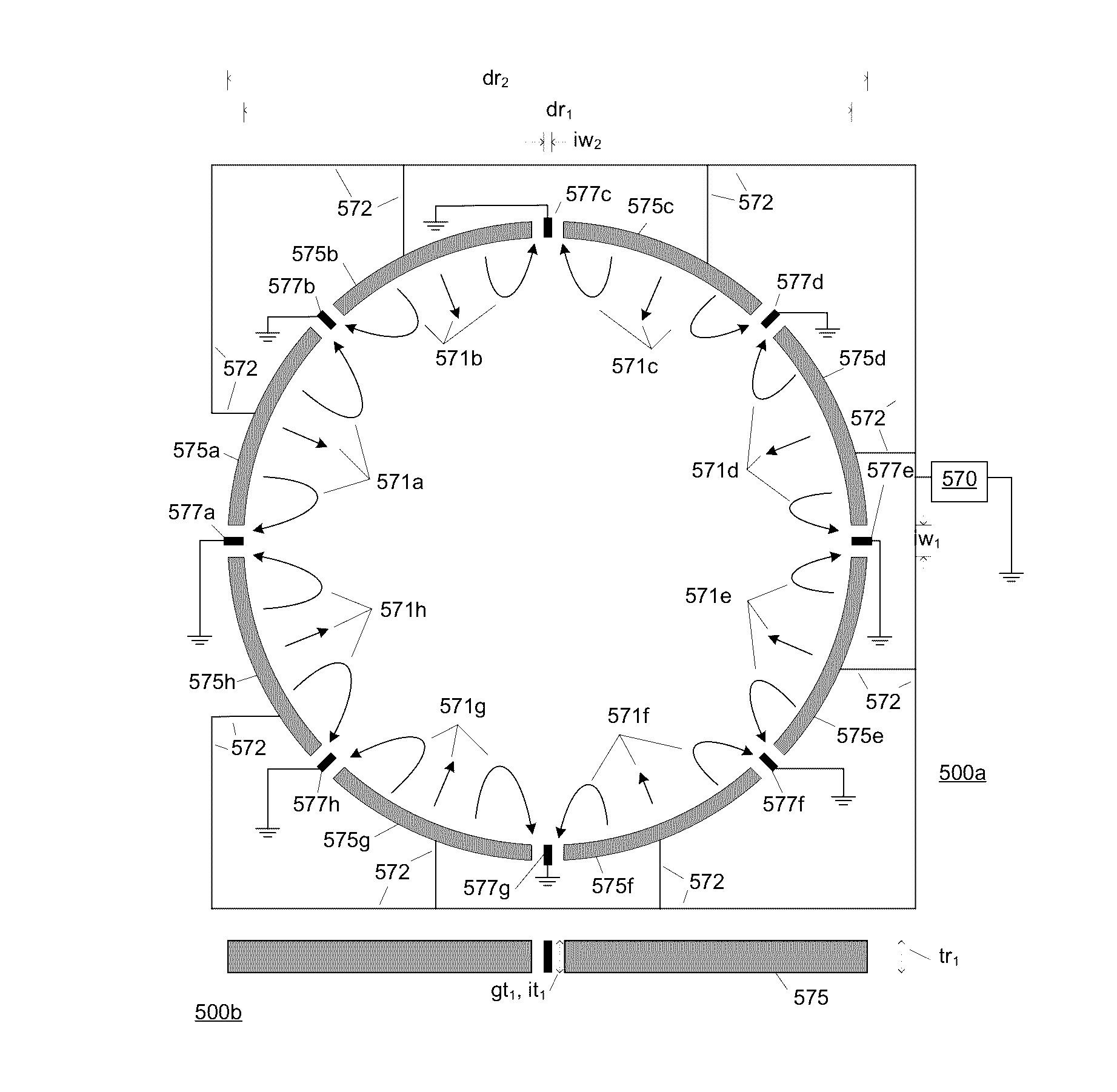

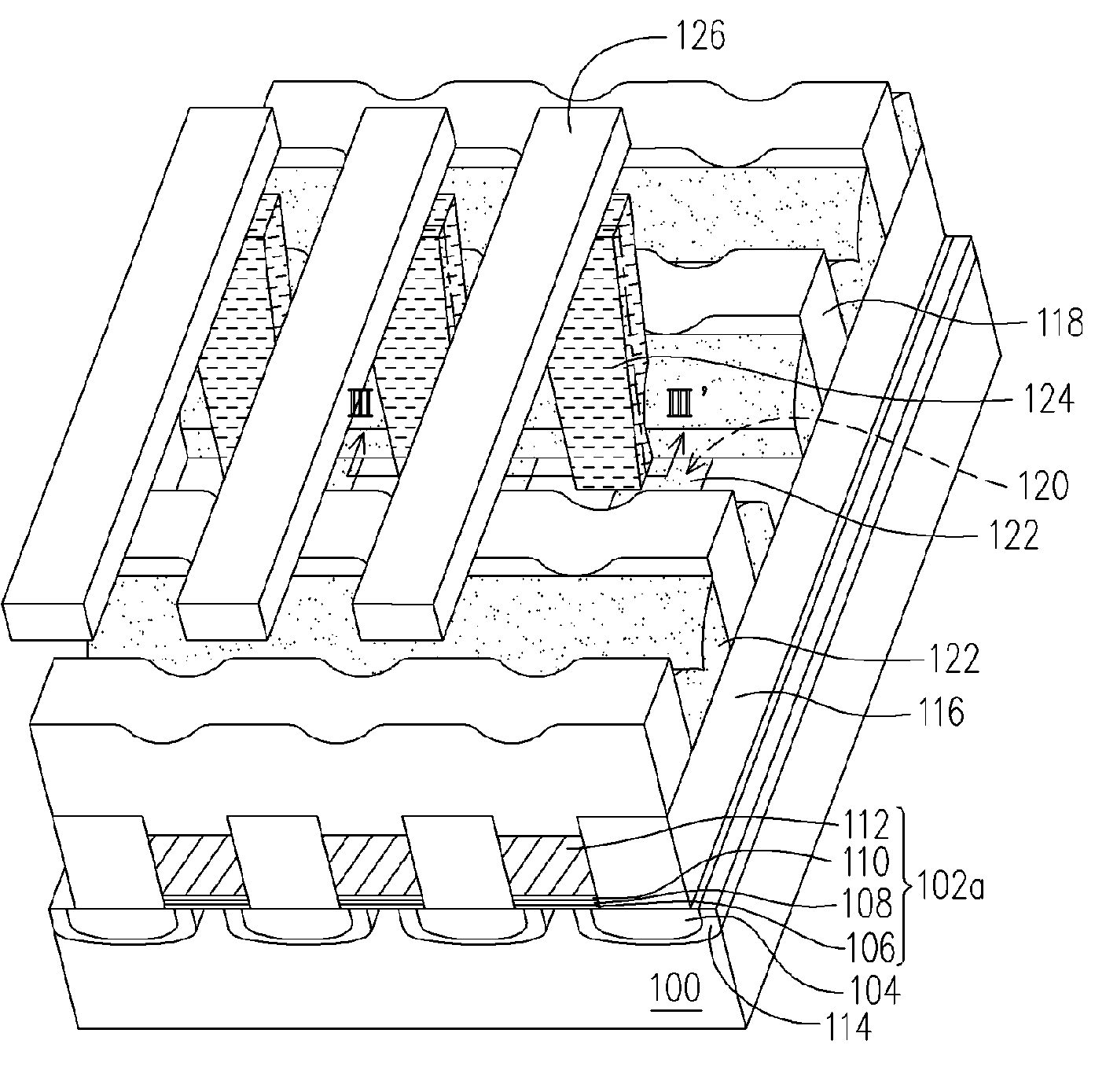

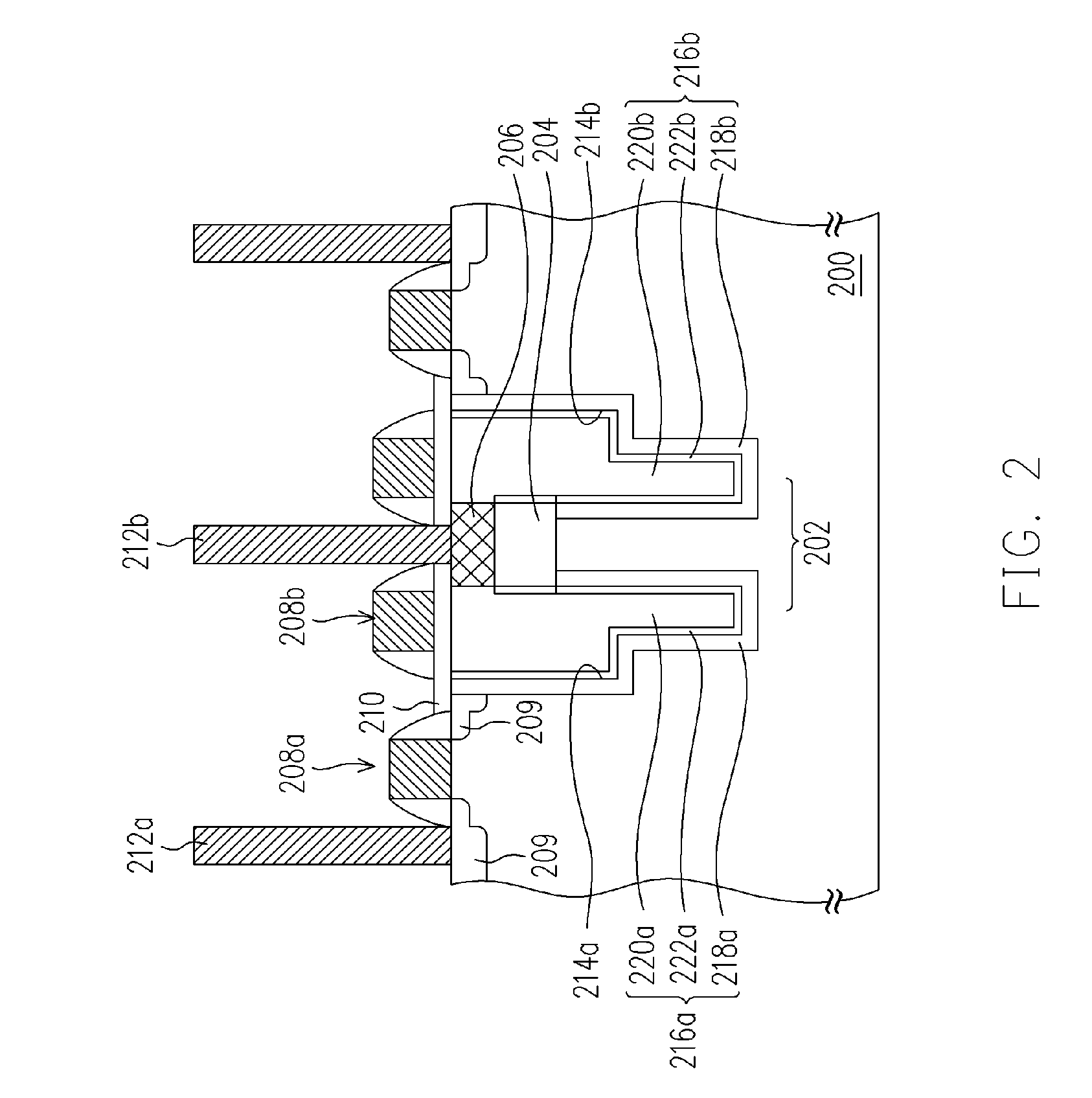

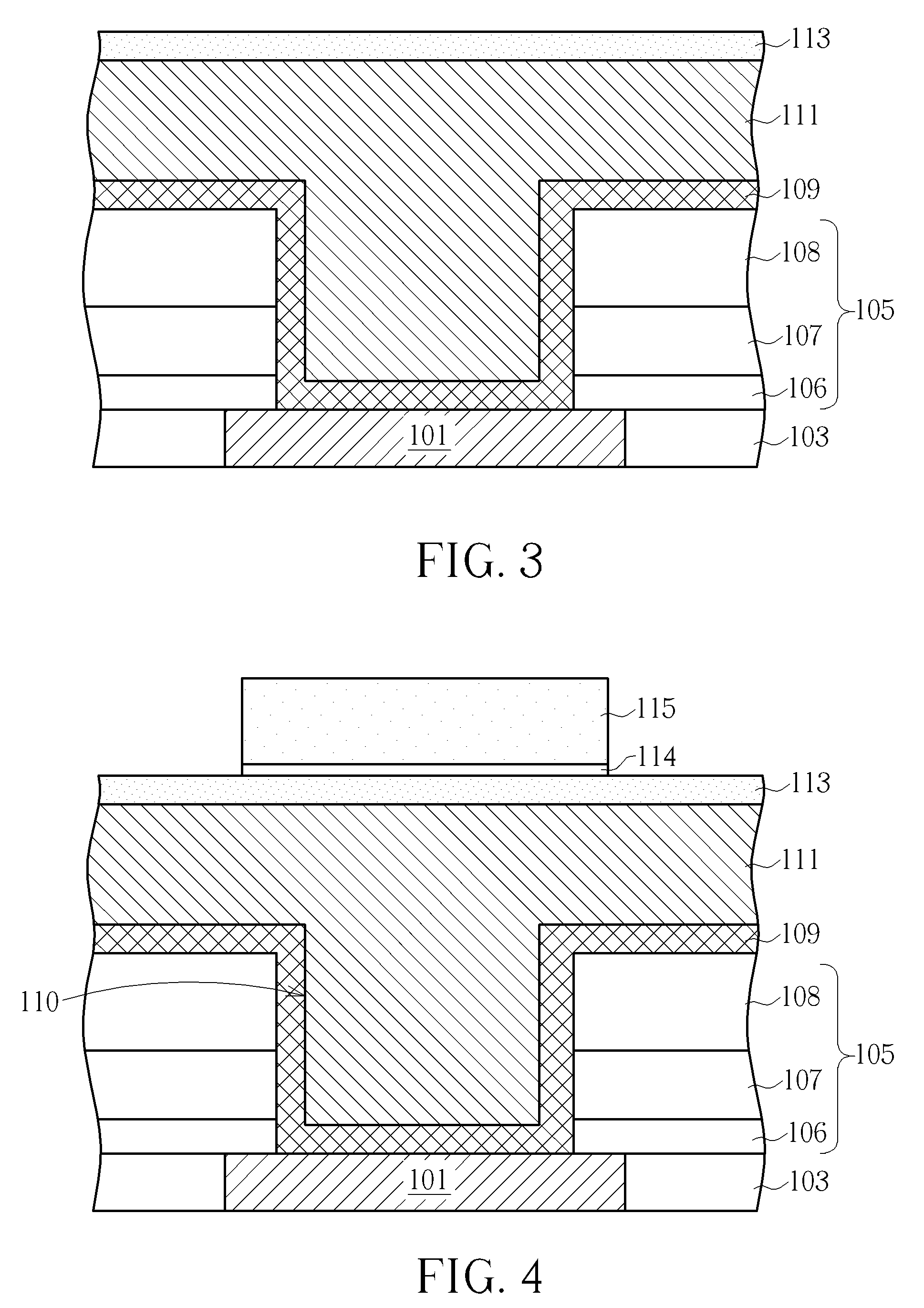

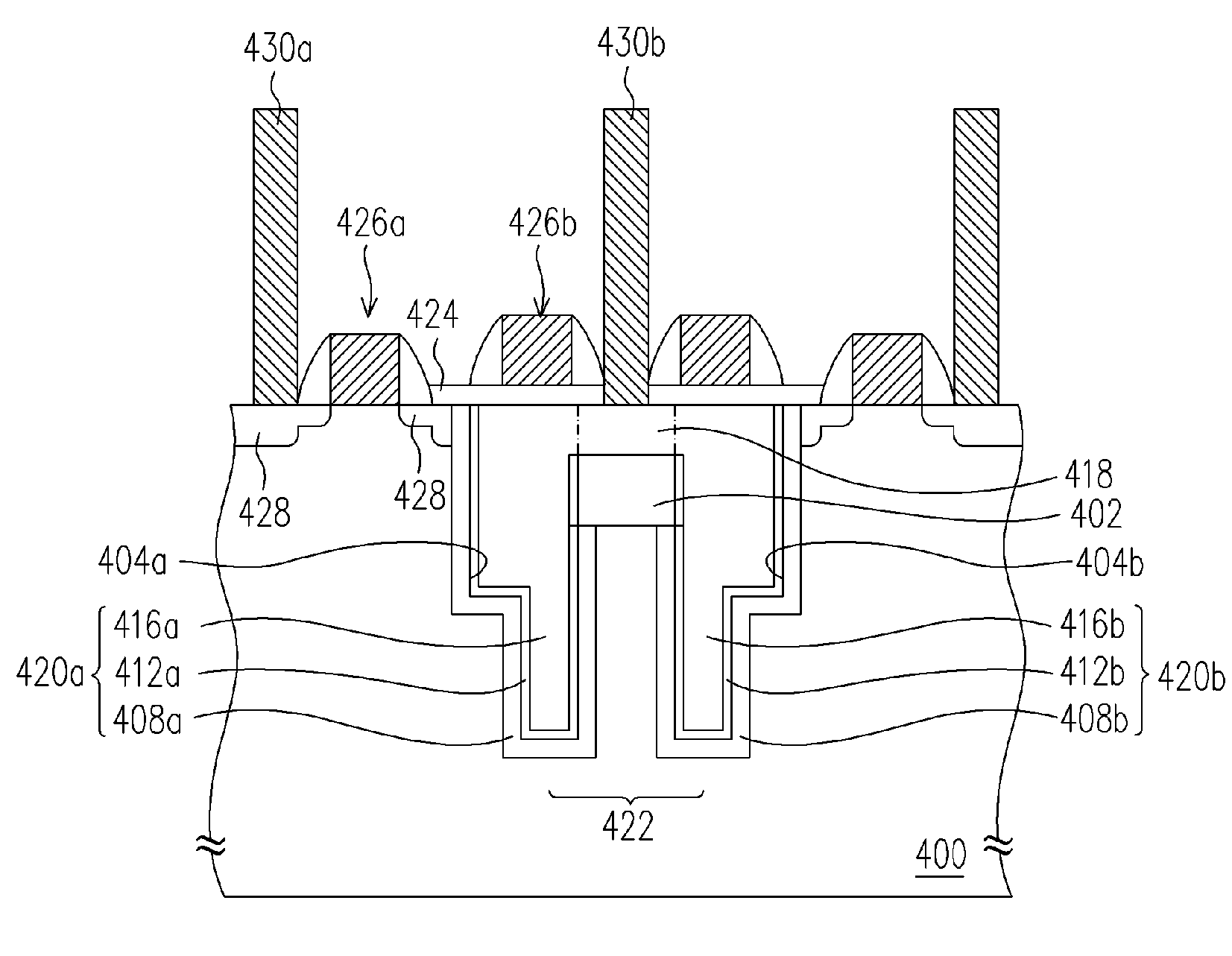

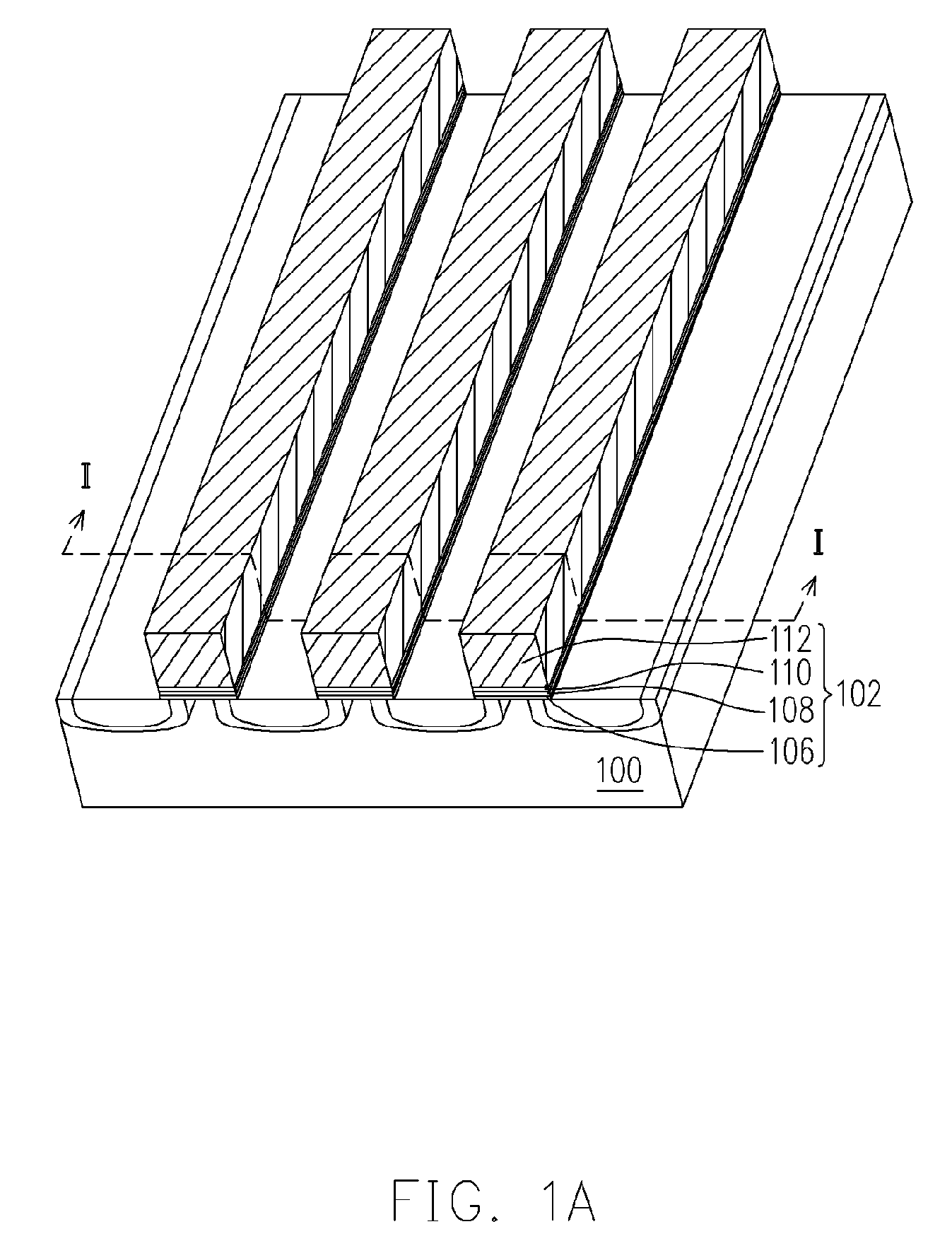

Trench capacitor and fabricating method thereof

ActiveUS20070040201A1Improve level of integrationLarge processing windowTransistorSolid-state devicesEngineeringElectrical and Electronics engineering

A method of fabricating trench capacitors is described. A substrate having at least one isolation structure is provided. A first trench and a second trench are formed in the substrate beside the isolation structure. A first lower electrode and a second lower electrode are formed in the substrate around the first trench and the second trench. A first capacitor dielectric layer and a second capacitor dielectric layer are formed on the respective surfaces of the first trench and the second trench. A first upper electrode and a second upper electrode are formed to fill the first trench and the second trench. A portion of the isolation structure between the first trench and the second trench is removed to form an opening. A conductive layer is formed to fill the opening and connect electrically with the first upper electrode and the second upper electrode.

Owner:MARLIN SEMICON LTD

Formulations for environmentally friendly photoresist film layers

ActiveUS8394575B2Precise alignmentImprove imaging effectPhotosensitive materialsPhotosensitive materials for photomechanical apparatusEpoxyPhotoacid generator

Owner:LEXMARK INT INC

Mineral filled polyethylene for inner liners

ActiveUS7585911B2Improve adhesionLow shrinkagePigmenting treatmentDomestic cooling apparatusMaterials sciencePolyethylene

Inner liners of foam insulated refrigerators and freezers are made of mineral filled bimodal polyethylene.

Owner:BOREALIS TECH OY

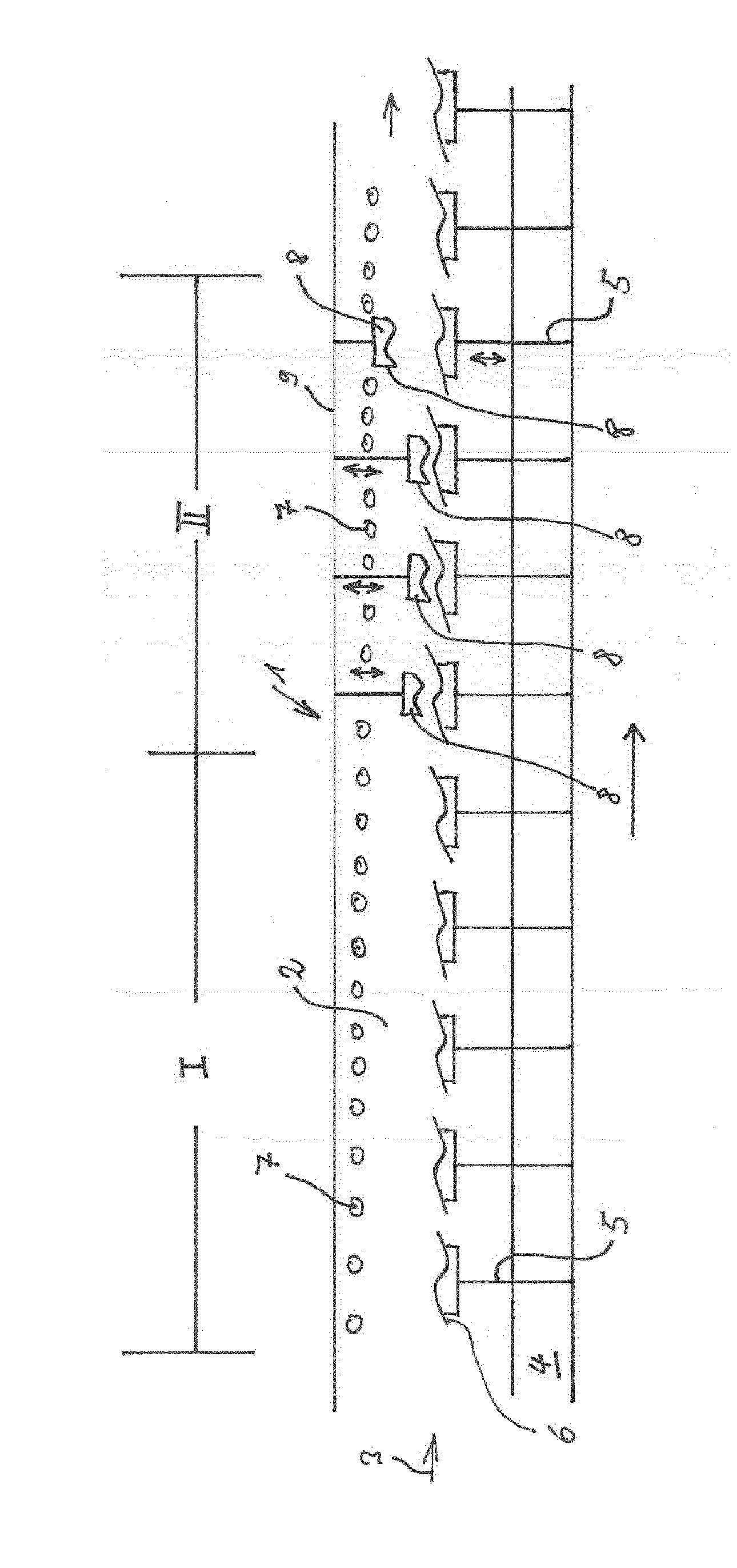

Method and device for partially hardening sheet metal components

ActiveUS20140345757A1Simple designImprove throughputHot-dipping/immersion processesFurnace typesCold formedRadiating element

The invention relates to a method for producing partially-hardened components from steel sheets, in which a component that is cold-formed from a hardenable steel sheet material is heated, in a furnace, to a temperature below the austenitisation temperature (<AC3), and a radiating element acts upon the component in sections where said component is to be austenitised (<AC3), this radiating element having a component-side contour that corresponds to the contour of the component in the section to be austenitised. The invention also relates to a device for carrying out said method.

Owner:VOESTALPINE METAL FORMING

Bond pad structure and method of manufacturing the same

ActiveUS9269678B2Reduce the possibilityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesEngineeringProtection layer

A method of manufacturing a bond pad structure, comprising the steps of forming a pad material layer on a passivation layer, forming a protection layer on the pad material layer, performing an etching process to pattern the protection layer and the pad material layer into a bond pad structure, and removing the protection layer on the bond pad structure.

Owner:MARLIN SEMICON LTD

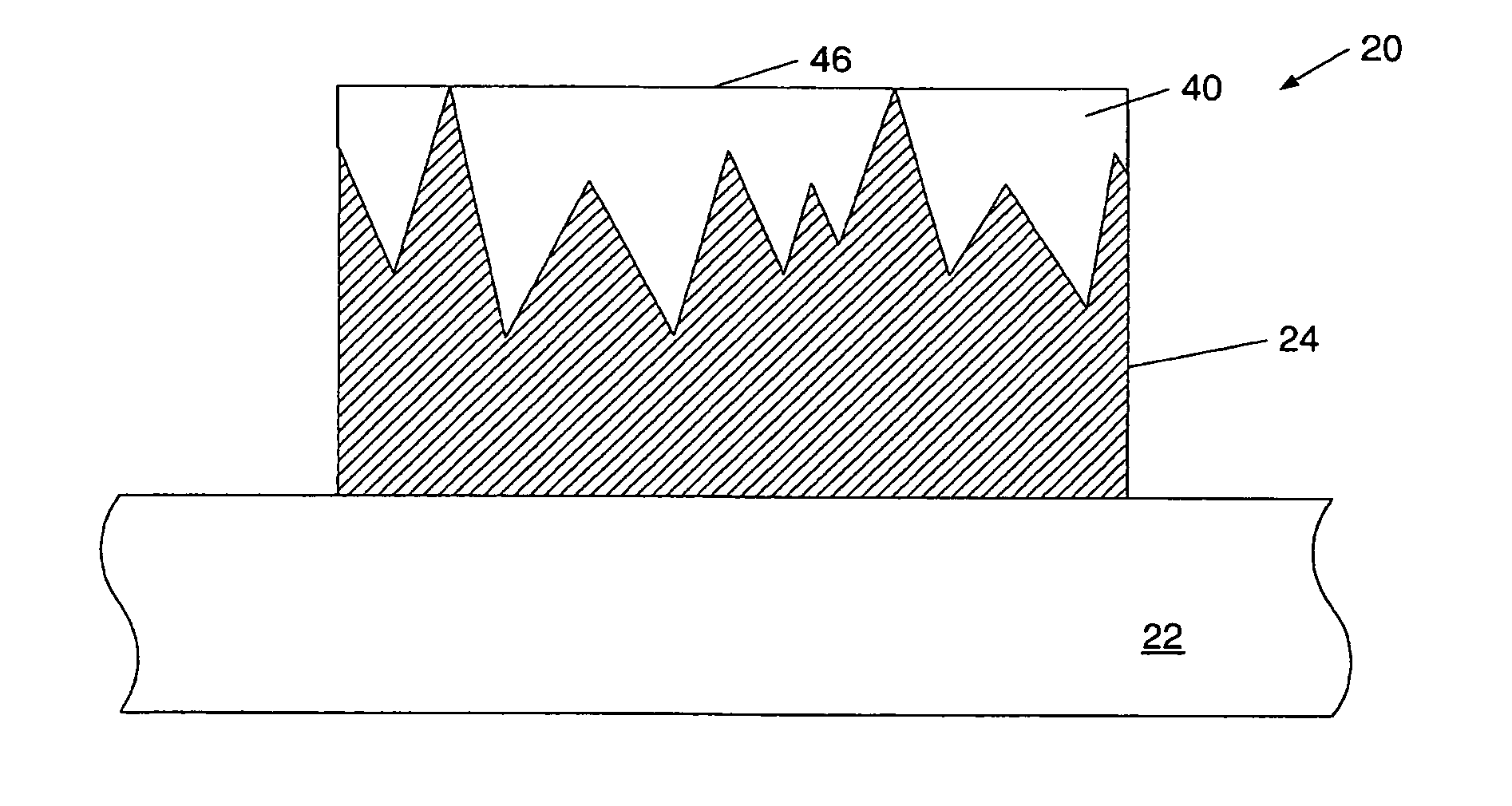

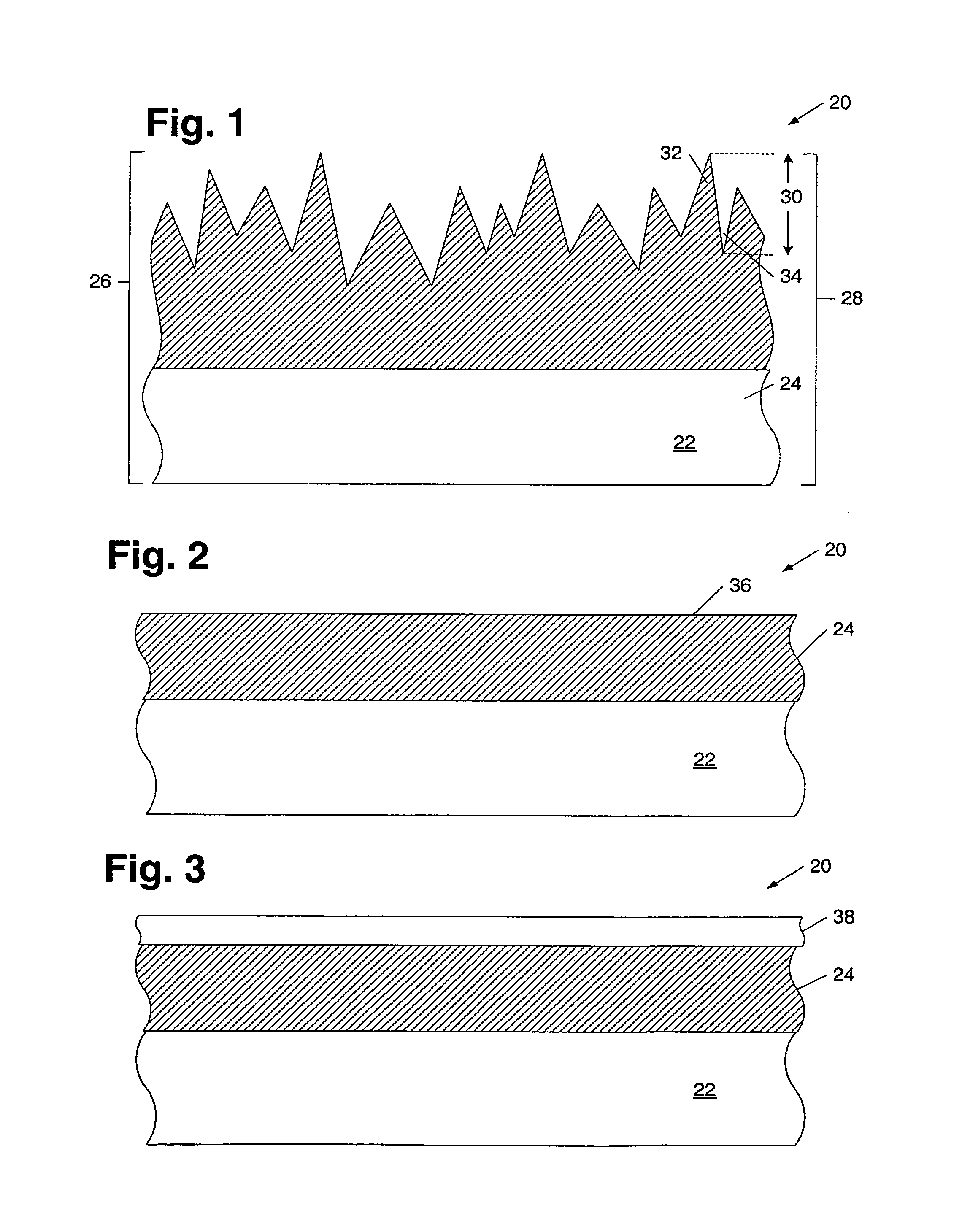

Smooth metal semiconductor surface and method for making the same

InactiveUS7329934B1Reduce surface roughnessConsume less powerSemiconductor/solid-state device detailsSolid-state devicesSurface roughnessTopography

A method for reducing the surface roughness of a metal layer is provided. In some embodiments, the method may include polishing the metal layer to a level substantially above any layers arranged directly beneath the metal layer. In some cases, the semiconductor topography comprising the metal layer may be substantially absent of any material laterally adjacent to the metal layer during polishing. In either case, a semiconductor topography having a metal layer with a mean surface roughness less than the mean surface roughness obtained during the deposition of the metal layer may be obtained. As such, the method may include reducing the mean surface roughness of a metal layer. For example, the method may include reducing the mean surface roughness of a metal layer by at least a factor of ten.

Owner:MONTEREY RES LLC

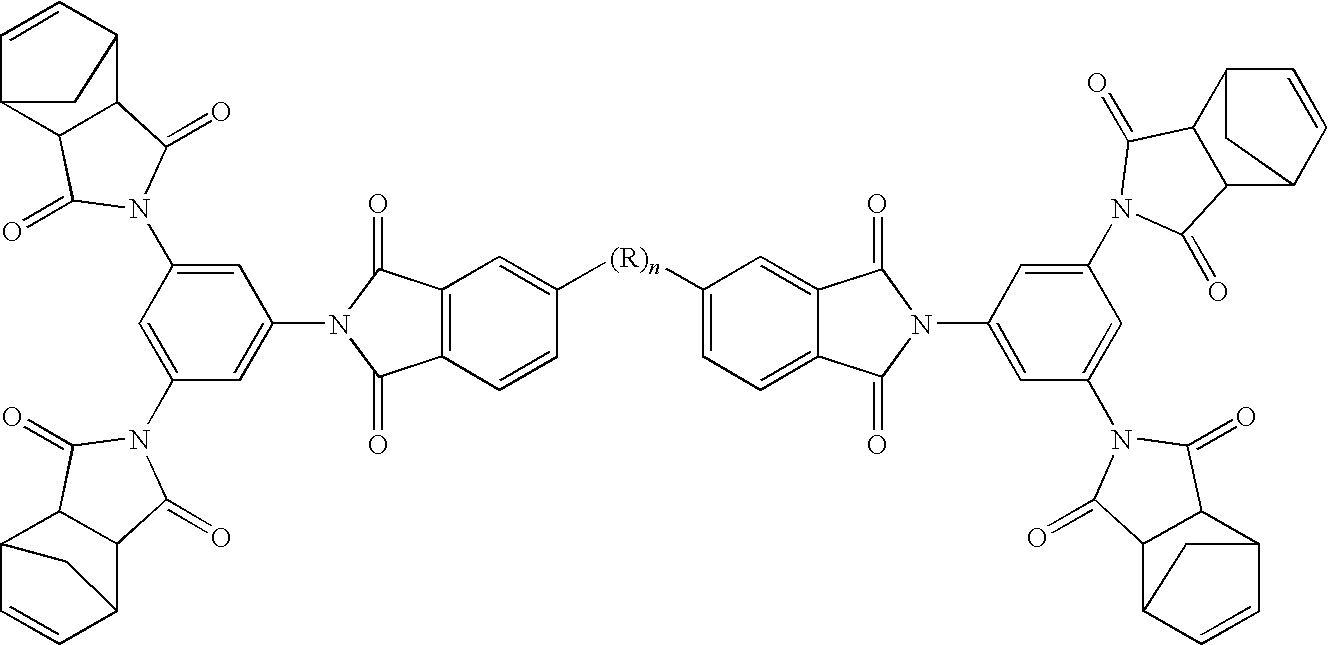

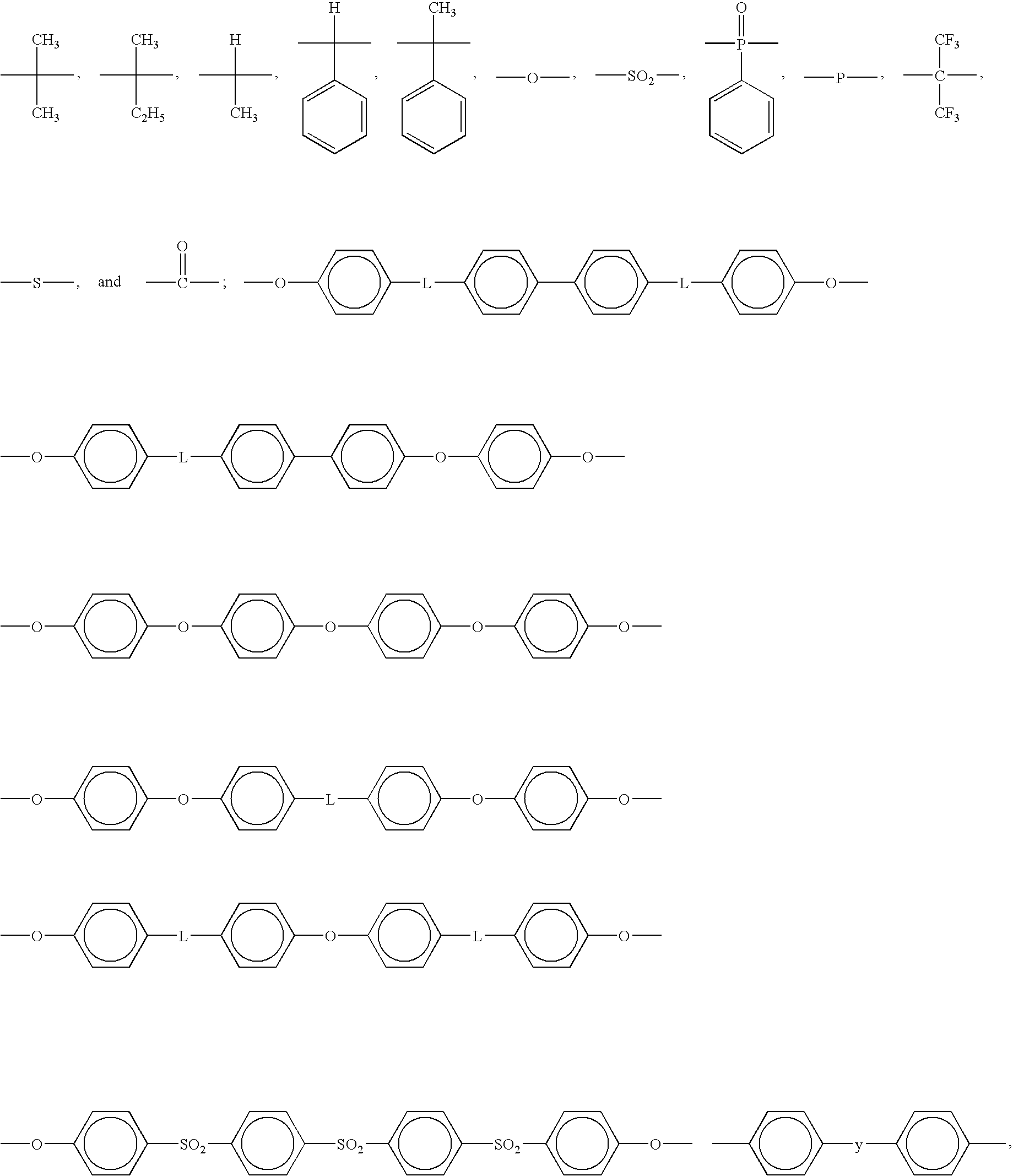

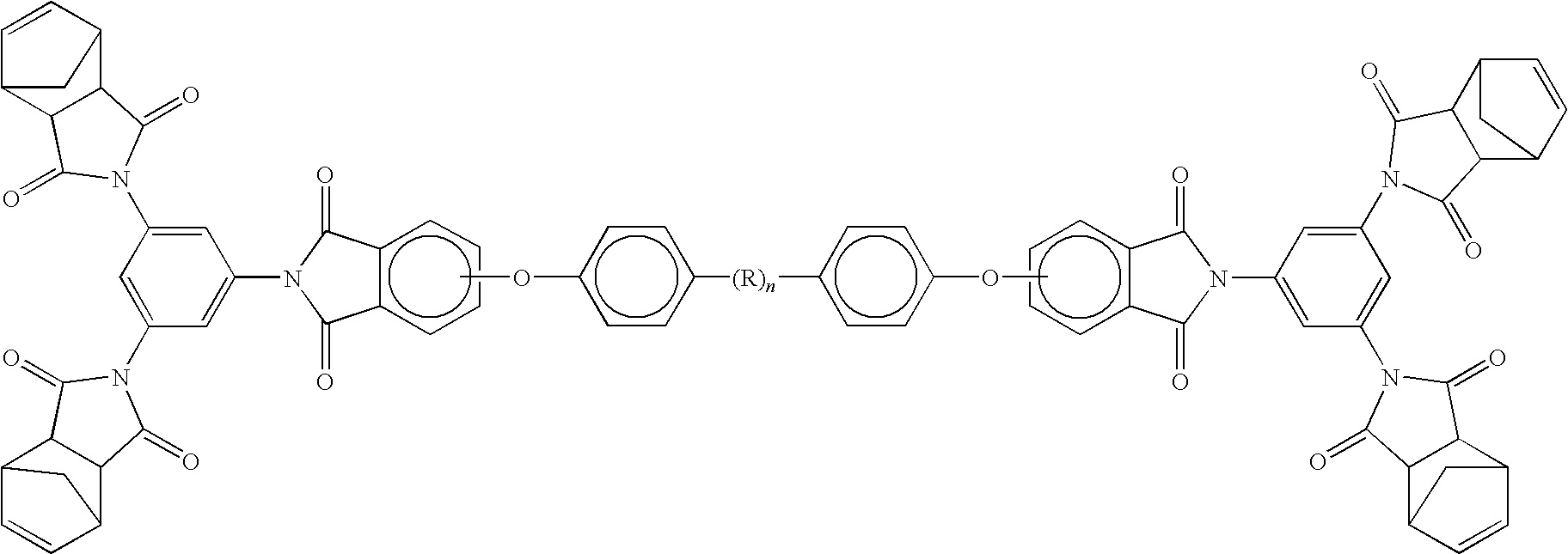

Single-step-processable polyimides

ActiveUS7825211B2Large processing windowEasy melt-processabilityOrganic chemistryOligomerSingle step

A process for synthesizing formulations for polyimides suitable for use in high-temperature composites in which all reactions other than chain-extension have already taken place prior to making a composite is described, wherein the resulting oligomers comprise a backbone and at least one difunctional endcap. The resulting resin systems have only the single step of endcap-to-endcap reactions during composite processing. Prior to the initiation temperature of these endcap-to-endcap reactions, the resins are stable affording the composite manufacturer a very large processing window.

Owner:THE BOEING CO

Formulations for environmentally friendly photoresist film layers

ActiveUS20120082933A1Precise alignmentImprove imaging effectPhotosensitive materialsPhotosensitive materials for photomechanical apparatusEpoxyPhotoacid generator

Environmentally friendly thick film layers for a micro-fluid ejection head and micro-fluid ejection heads are disclosed. The environmentally friendly thick film layer includes a negative photoresist layer derived from a composition comprising a multi-functional epoxy compound, a low molecular weight polymeric difunctional epoxy compound, a monomeric difunctional epoxy compound, a methide-based photoacid generator that does not contain antimony, a chromophore and an aryl ketone solvent. Optionally the photoresist layer contains an adhesion enhancer. The negative photoresist layer is environmentally friendly and provides good resolution, well defined critical dimensions, straight side walls, and a large processing window.

Owner:LEXMARK INT INC

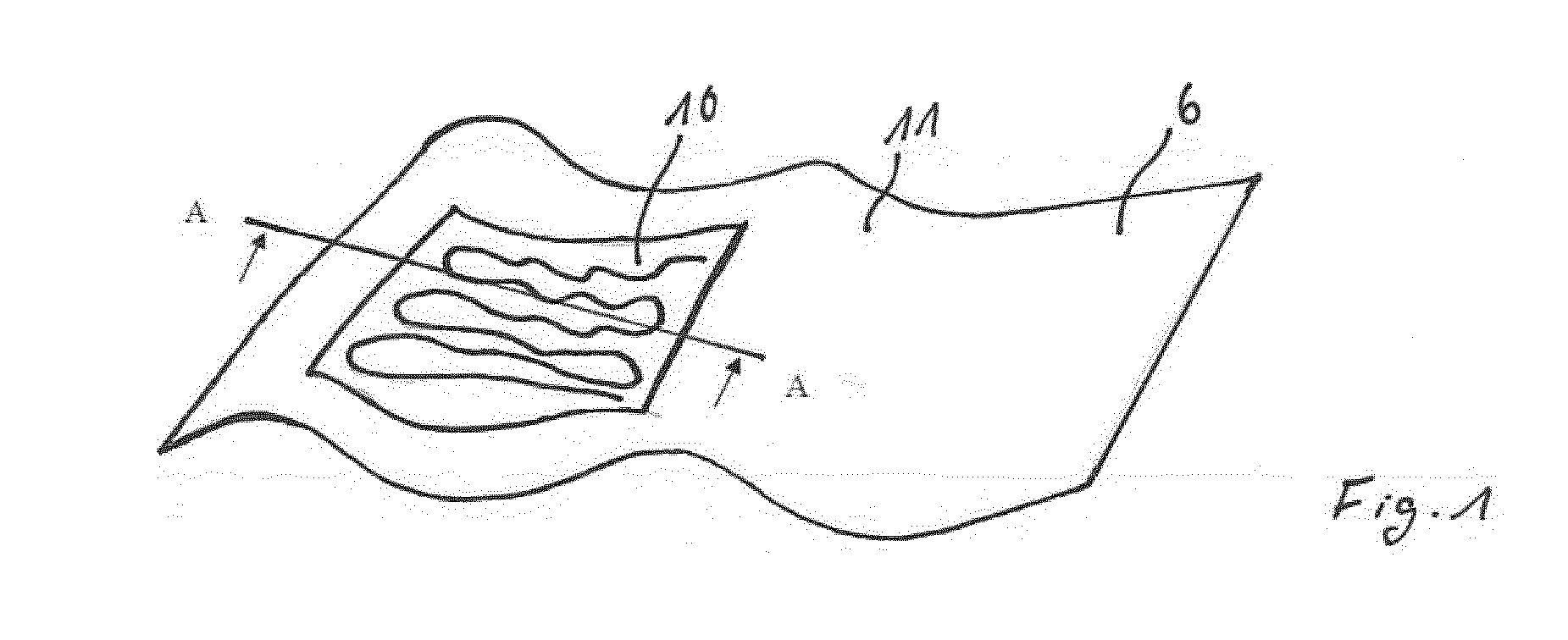

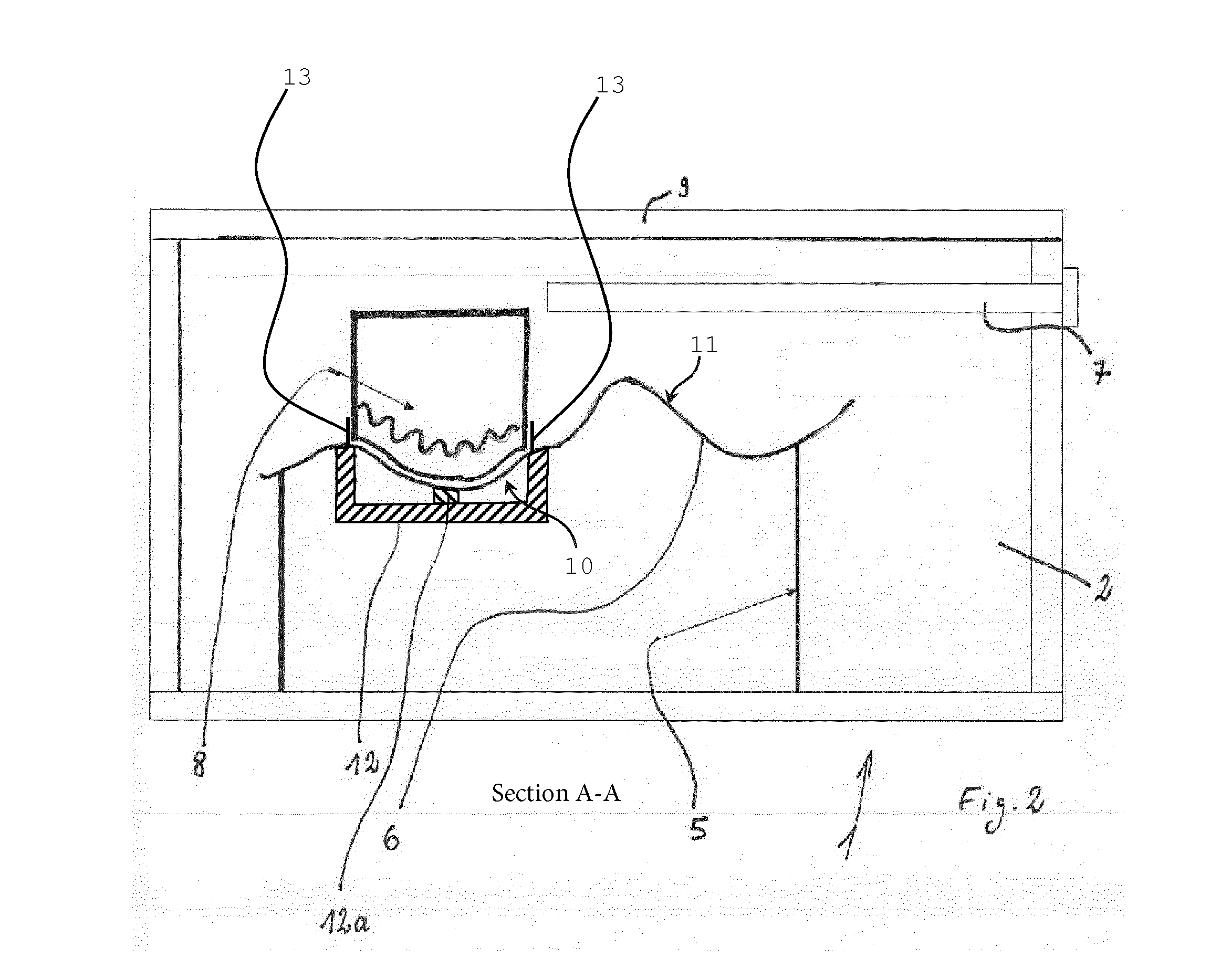

Liquid crystal display having a concave substrate and manufacturing method thereof

InactiveUS6859251B2Large LC dispensing process windowLarge processing windowNon-linear opticsLiquid-crystal displayAdhesive

A liquid crystal display and a method for manufacturing the liquid crystal display is disclosed. The method includes the steps of: (a) applying an adhesive onto at least one of a pair of substrates; (b) dispensing a liquid crystal material to at least one of the pair of substrates; (c) superposing one of the pair of substrates upon the other substrate; and (d) conducting a curing process of the adhesive in an air pressure greater than atmospheric pressure such that one of the substrates is concave toward the other substrate in the finished liquid crystal display.

Owner:INNOLUX CORP

Pressure sensor

ActiveUS20110290029A1Conducive to environmental protectionLess expensiveFluid pressure measurement using ohmic-resistance variationFluid pressure measurement by mechanical elementsInterference fitElectronic board

A pressure sensor includes a sense element port, a support ring and a plurality of interference fit slits to provide a flexible interference fit between the sense element port and the support ring to form a substantially flush lap joint. The sensor also includes an electronics board inside the support ring and attached to planar mounting tabs which provide a stable mounting. Gel flow barriers protect electronics board features from unwanted non-conductive gel. Double-ended symmetrical, tapered contact springs provide manufacturing cost savings and contribute to improved alignment of an interface connector of the sensor.

Owner:SENSATA TECHNOLOGIES INC

Method for fabricating a trench power MOSFET

InactiveUS7084033B2High response rateAvoid problemsSemiconductor/solid-state device manufacturingSemiconductor devicesPower MOSFETGate oxide

A method for fabricating a trench power MOSFET, comprising an epitaxial layer and a mask layer formed over a substrate, a trench formed in the epitaxial layer and the mask layer, a gate oxide layer formed on the trench, then the mask layer removed, a body well region formed in the epitaxial layer beside the trench, a source region formed in and adjacent to the body well region, and a spacer formed on the sidewalls of the exposed gate layer exposing the source region partially. Masking by spacer, an opening exposing the body well is formed by partially removing the source region and the gate layer. A body region is formed in the body well region under the opening. A silicide layer is formed on the surfaces of the gate layer and the opening.

Owner:EPISIL TECH INC

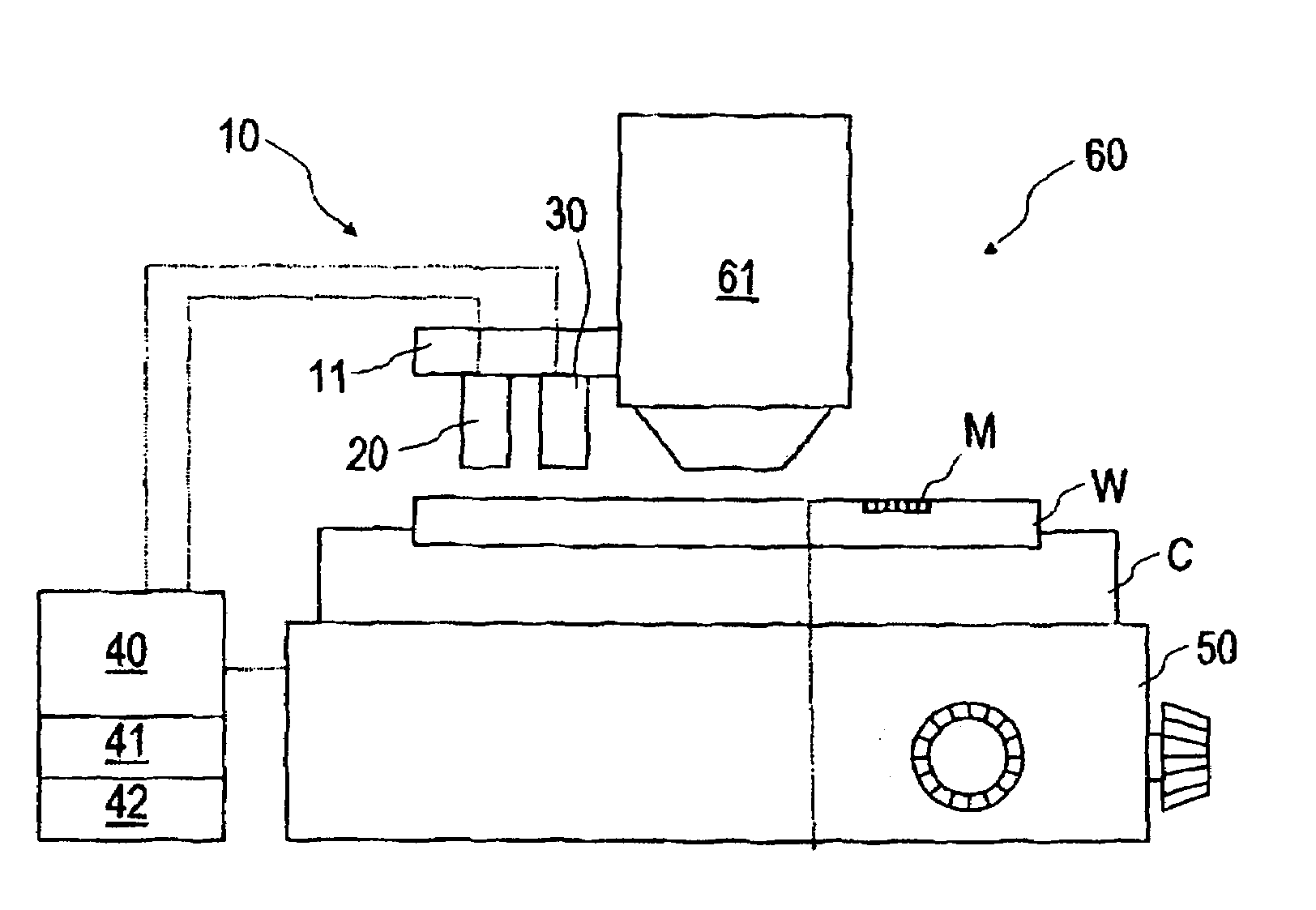

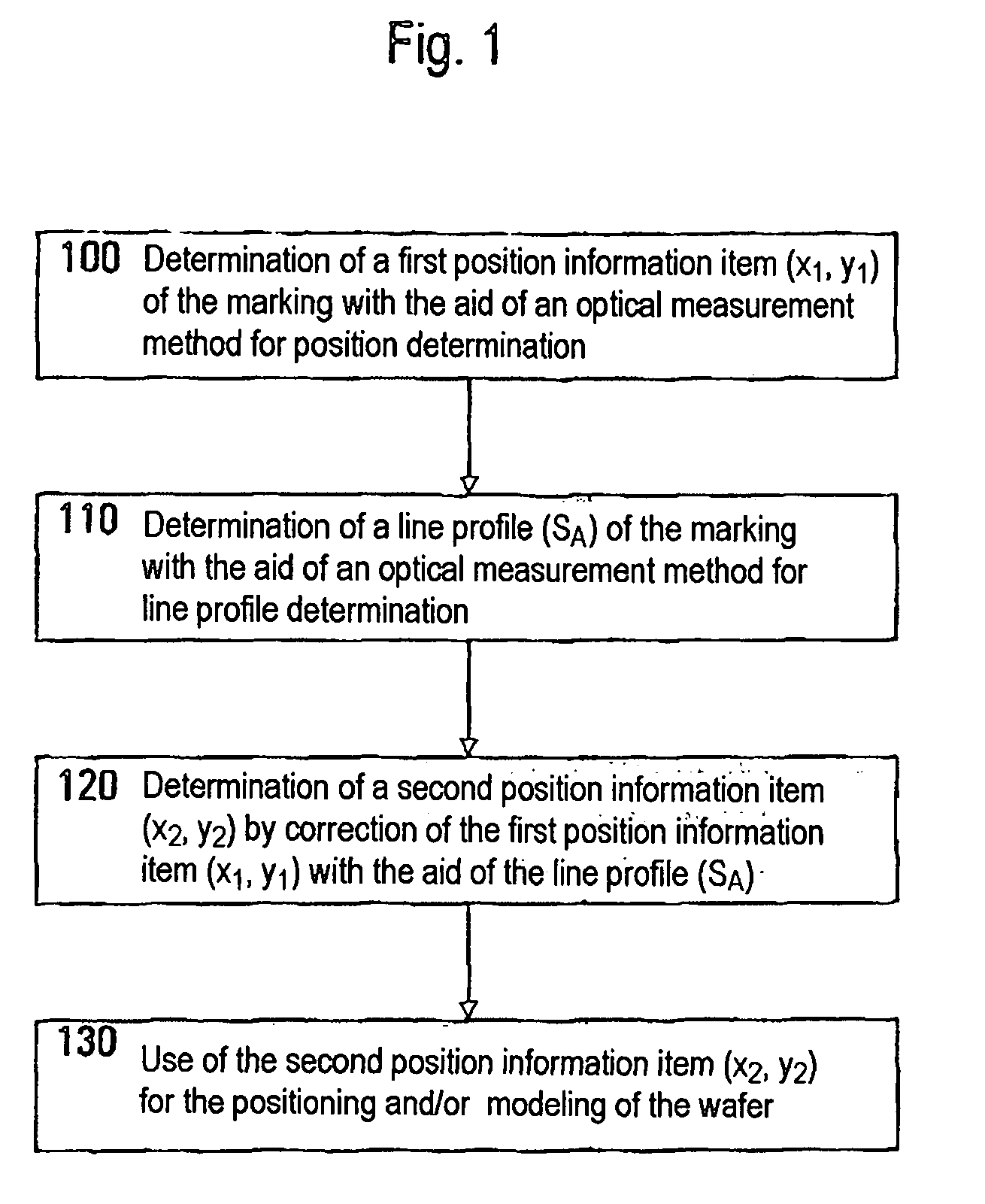

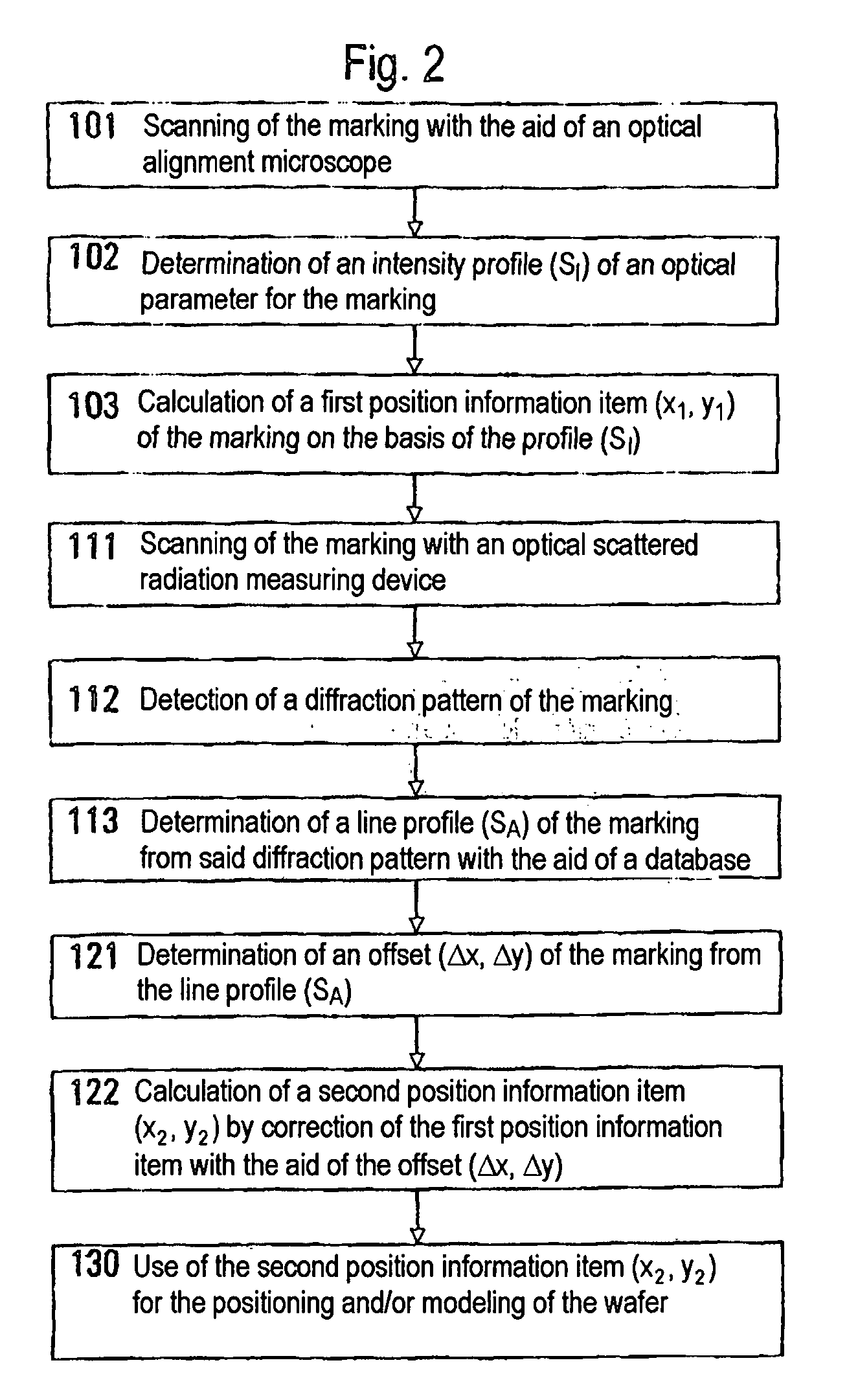

Method and apparatus for orienting semiconductor wafers in semiconductor fabrication

InactiveUS7268877B2High bulk densityAccurate informationPhotomechanical treatmentUsing optical meansEngineeringSemiconductor

Described are systems and methods for orienting a semiconductor wafer during semiconductor fabrication with the aid of an optical alignment system, the semiconductor wafer having an alignment mark with regular structures, on the basis of which the position of the semiconductor wafer can be determined.

Owner:POLARIS INNOVATIONS

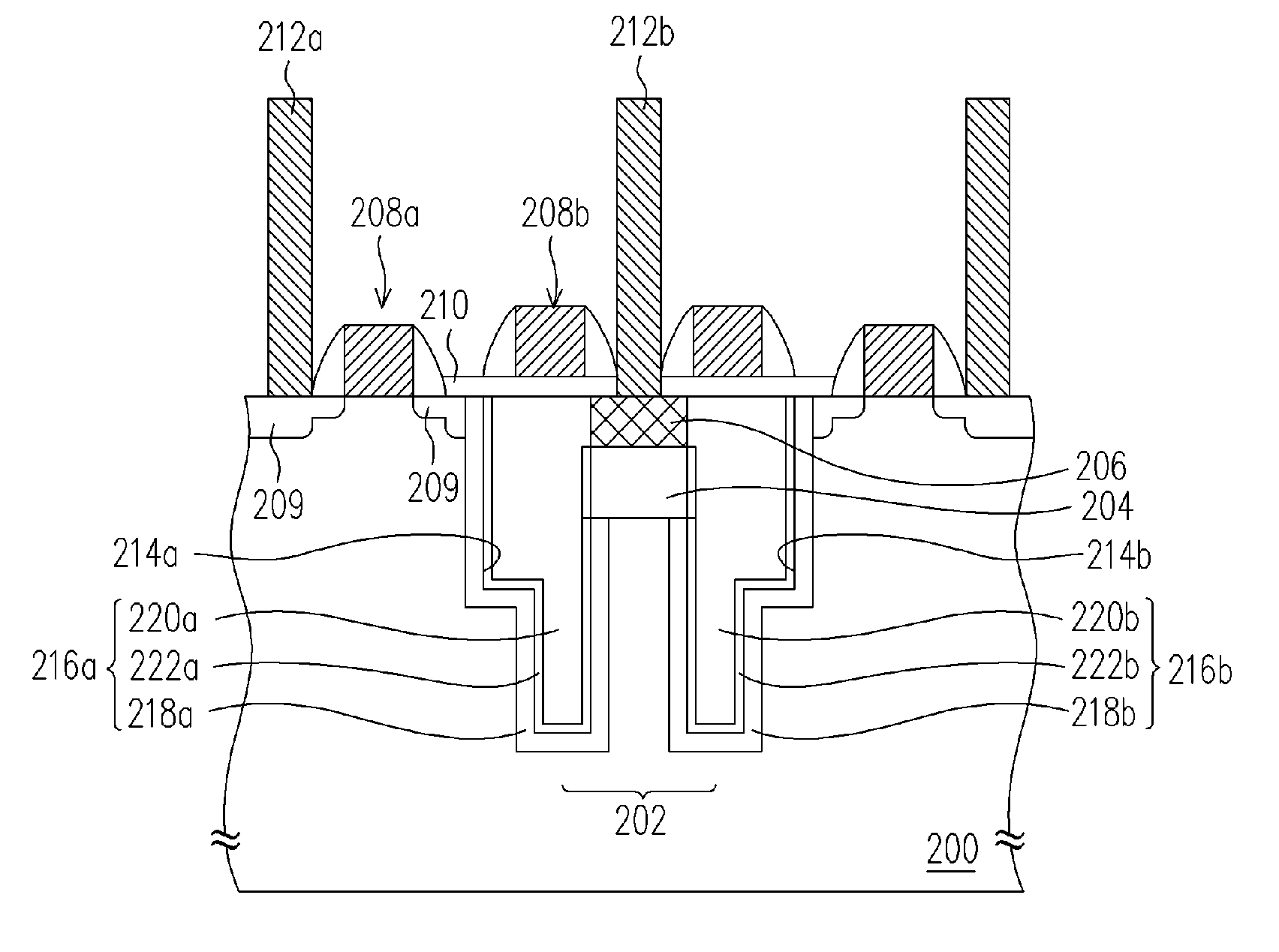

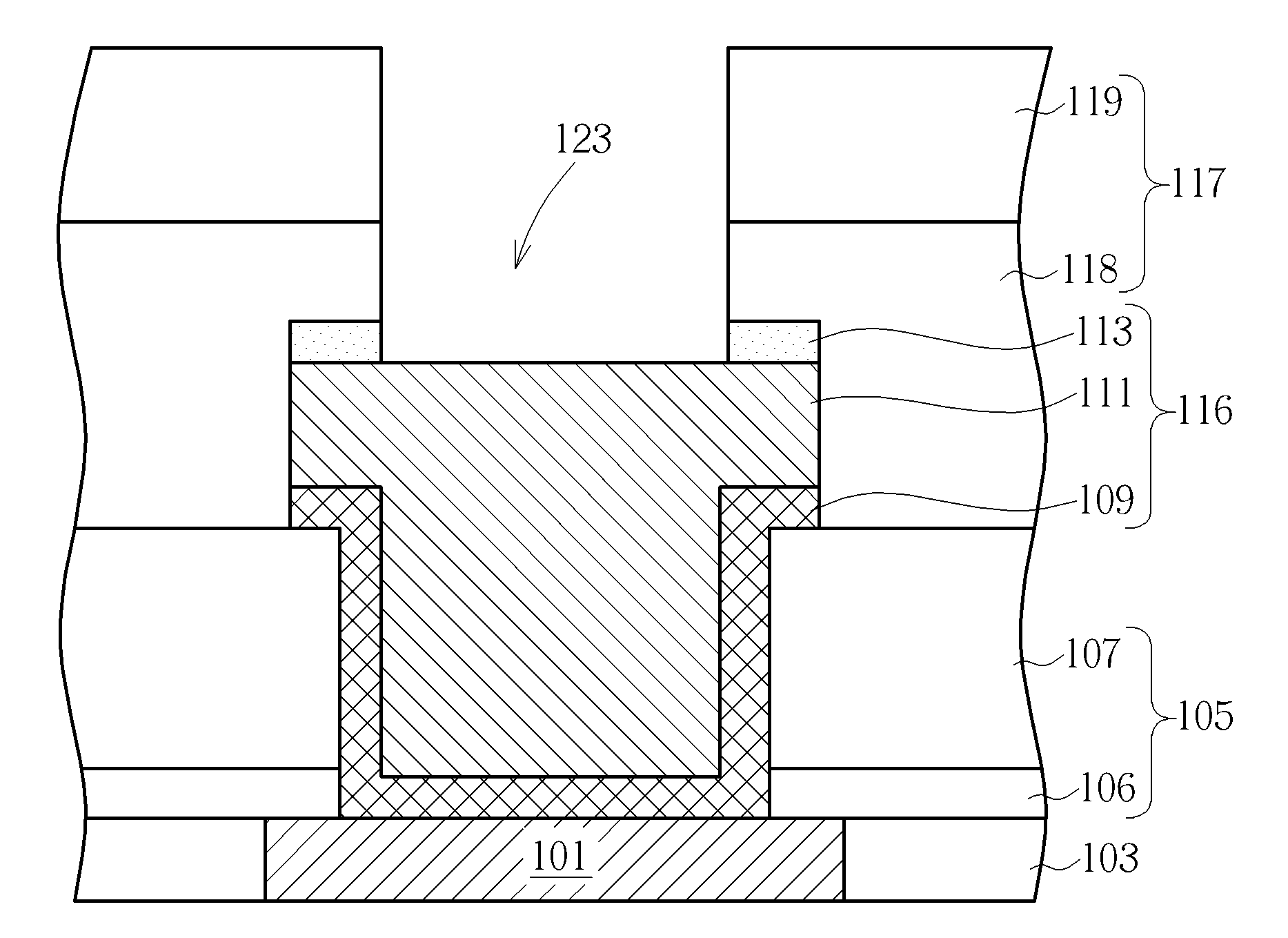

Trench capacitor of a DRAM and fabricating method thereof

ActiveUS7407852B2Highly integratedLarge processing windowTransistorSolid-state devicesEngineeringDielectric layer

A method of fabricating trench capacitors is described. A substrate having at least one isolation structure is provided. A first trench and a second trench are formed in the substrate beside the isolation structure. A first lower electrode and a second lower electrode are formed in the substrate around the first trench and the second trench. A first capacitor dielectric layer and a second capacitor dielectric layer are formed on the respective surfaces of the first trench and the second trench. A first upper electrode and a second upper electrode are formed to fill the first trench and the second trench. A portion of the isolation structure between the first trench and the second trench is removed to form an opening. A conductive layer is formed to fill the opening and connect electrically with the first upper electrode and the second upper electrode.

Owner:MARLIN SEMICON LTD

Fabrication method of flash memory

InactiveUS20070032006A1Contact resistanceReduce gate sizeSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricCell region

A fabrication method of a flash memory is provided. The substrate having a cell region and a peripheral circuitry region is provided. A patterned dielectric layer and a patterned conductive layer are formed on the substrate, and isolation structures are formed in the substrate. An inter gate dielectric layer and a poly layer are formed sequentially over the substrate. The poly layer and the inter gate dielectric in peripheral circuitry region are removed. After forming a second conductive layer and a mask layer over substrate, memory cells are formed in the cell region and a gate structure is formed in the peripheral circuitry region. A conductive plug is formed above the gate structure for electrically connecting the second conductive layer. Since the inter gate dielectric layer in the peripheral circuitry region is removed, the fabrication of the conductive plug can be simpler and the process window thereof can be improved.

Owner:POWERCHIP SEMICON CORP

Non-volatile memory and fabricating method thereof

ActiveUS20060110879A1Resolution problemMisalignment problemSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringNon-volatile memory

A method of fabricating a non-volatile memory is provided. A plurality of stack gate strips is formed on a substrate and a plurality of source / drain regions is formed in the substrate beside the stack gate strips. A plurality of dielectric strips is formed on the source / drain regions. A plurality of word lines is formed on the stack gate strips and the dielectric strips. Thereafter, the stack gate strips exposed by the word lines are removed to form a plurality of openings. A plurality of spacers is formed on the sidewalls of the openings and the word lines. A dielectric layer is formed over the substrate. A plurality of contacts is formed in the dielectric layer and the dielectric strips between two adjacent word lines.

Owner:MACRONIX INT CO LTD