Memory buffers for merging local data from memory modules

a memory buffer and local data technology, applied in the memory field, can solve the problems of slowing down the read and write access of data, bogging down the high frequency memory circuit, and adding parasitic capacitive load,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In the following detailed description of embodiments of the invention, numerous specific details are set forth in order to provide a thorough understanding of the invention. However, it will be obvious to one skilled in the art that the embodiments of the invention may be practiced without these specific details. In other instances well known methods, procedures, components, and circuits have not been described in detail so as not to unnecessarily obscure aspects of the embodiments of the invention.

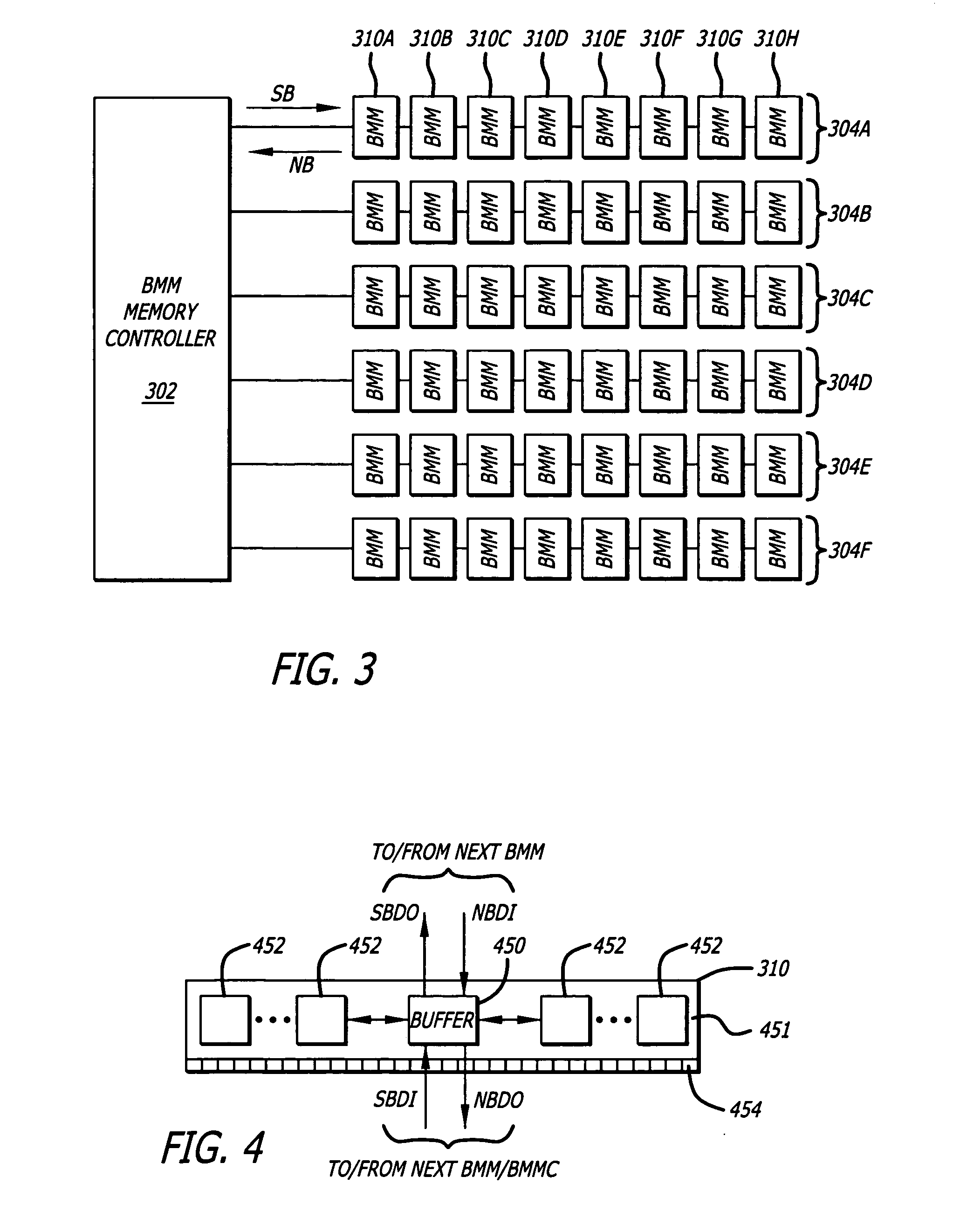

[0020] Generally the embodiments of the invention provide a data merge feature, referred to as a Northbound Data Merge (NBDM), that replaces parts of the data on a high speed link with its own data, on the fly. That is, the embodiments of the invention replace part of the incoming serial data traffic (e.g., “idle packets or frames”) over a serial data link with its local data, without having internal core logic process (e.g., serial-to-parallel conversion, assemblage into frames, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More