Patents

Literature

84results about How to "The formation process is simple" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

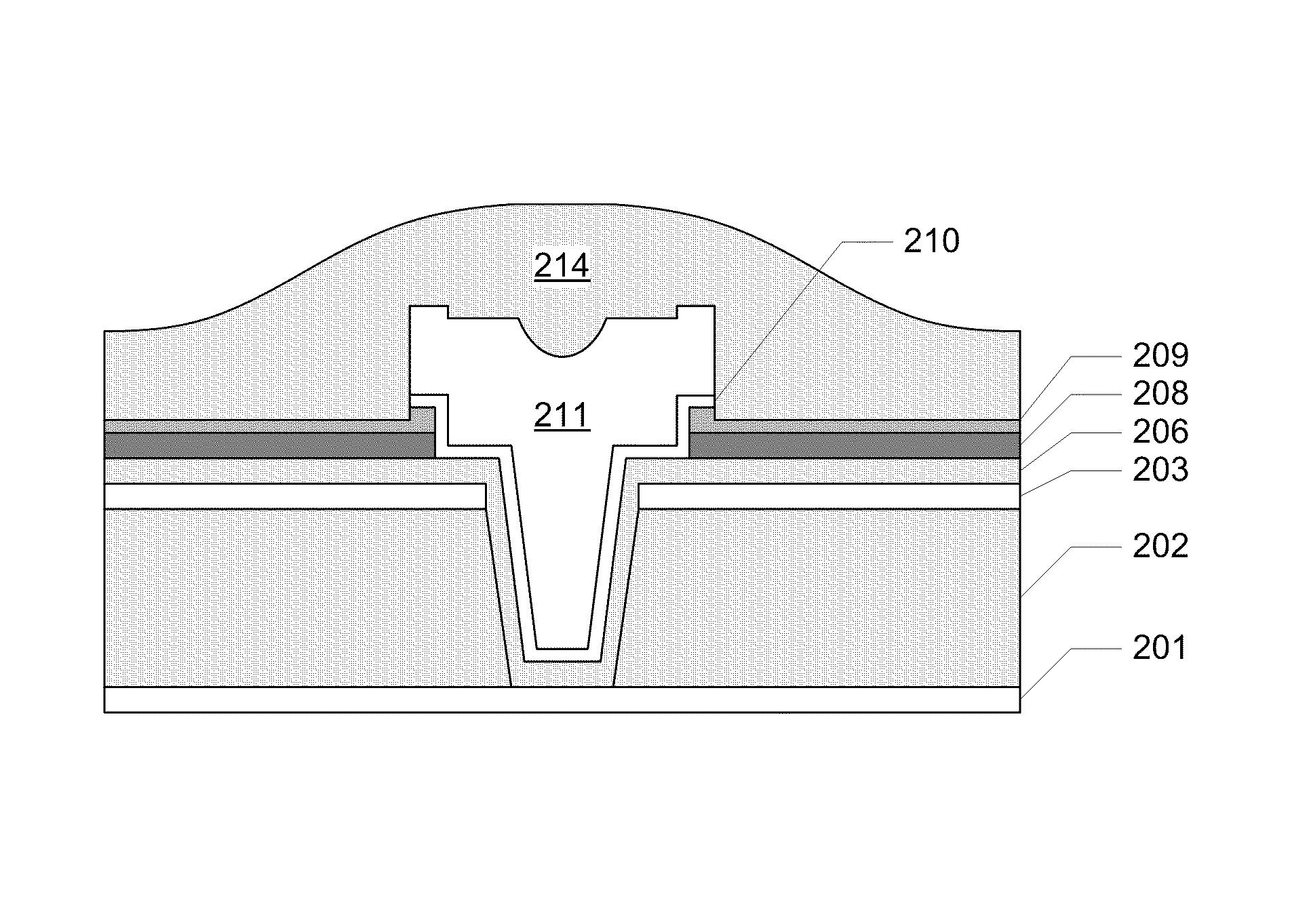

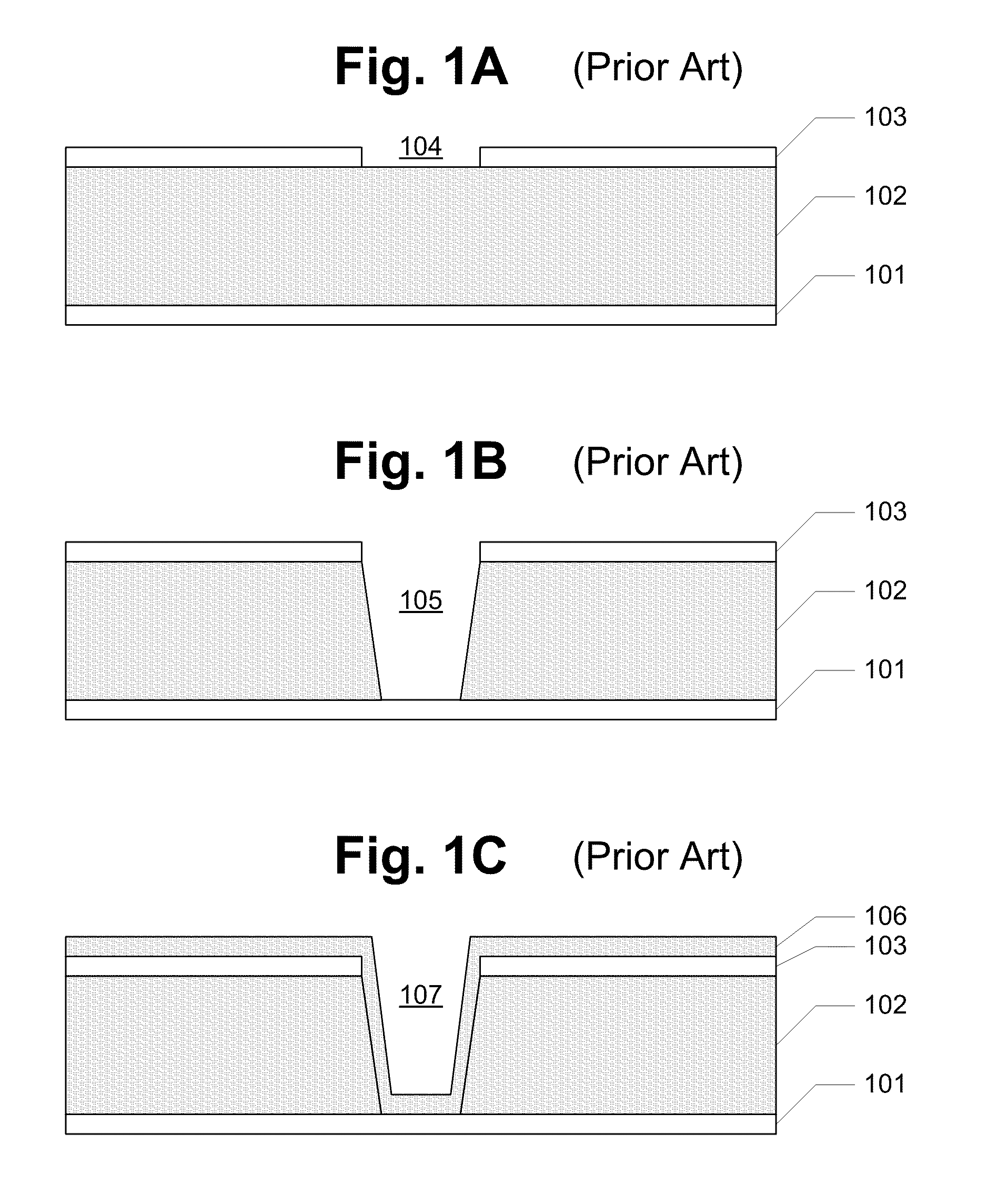

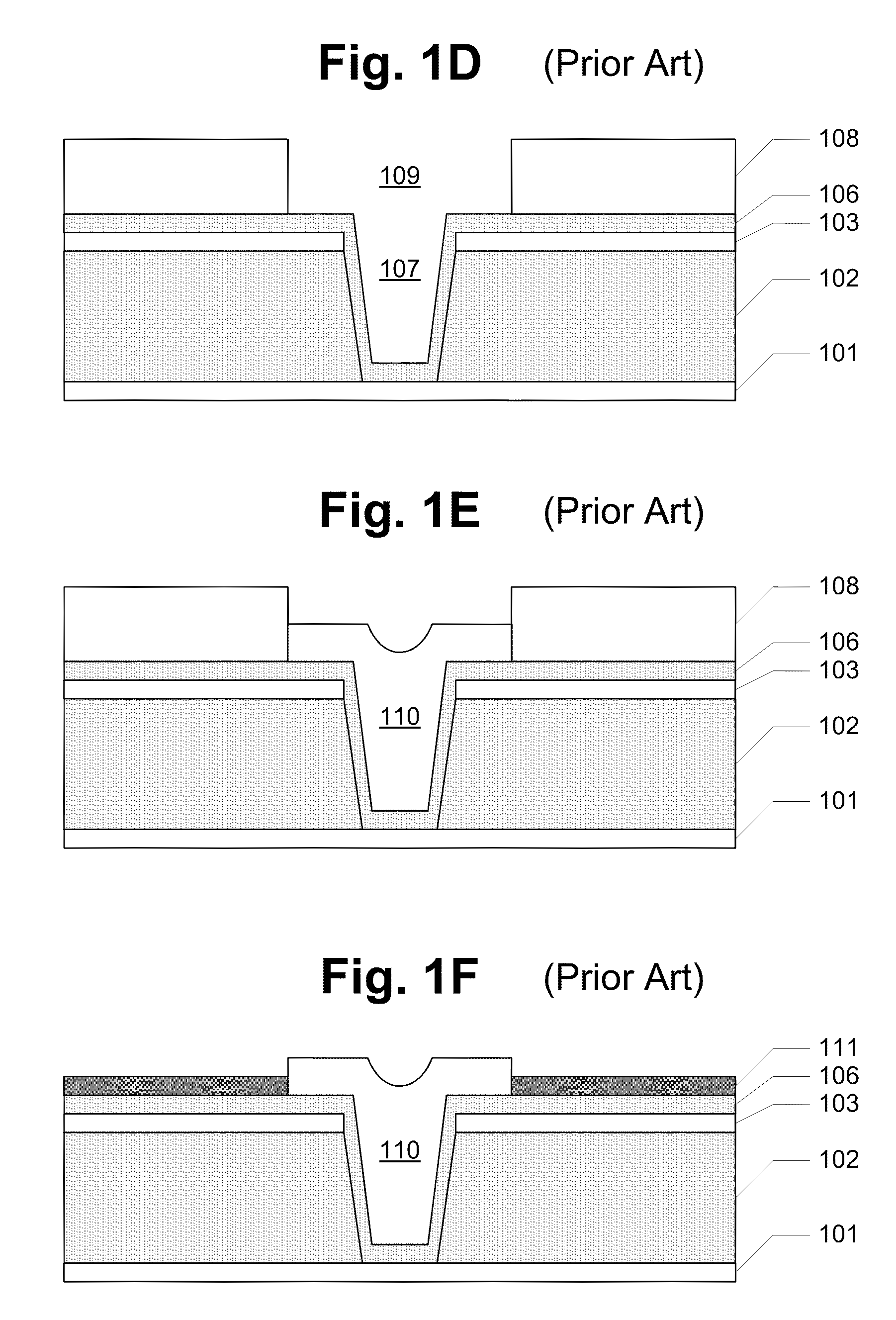

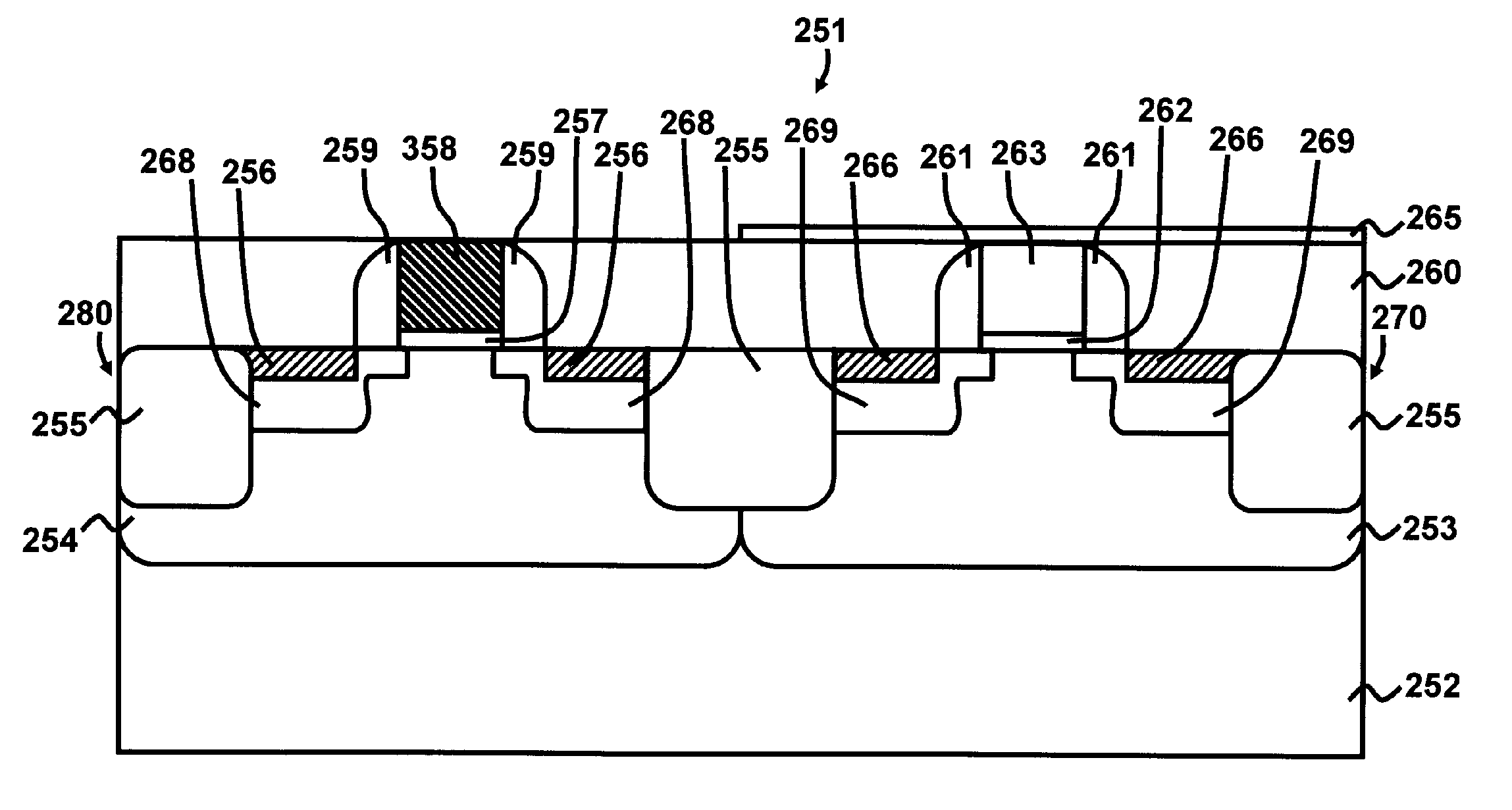

Damascene write poles produced via full film plating

InactiveUS8486285B2The formation process is simpleElectrical transducersDecorative surface effectsEngineeringElectroplating

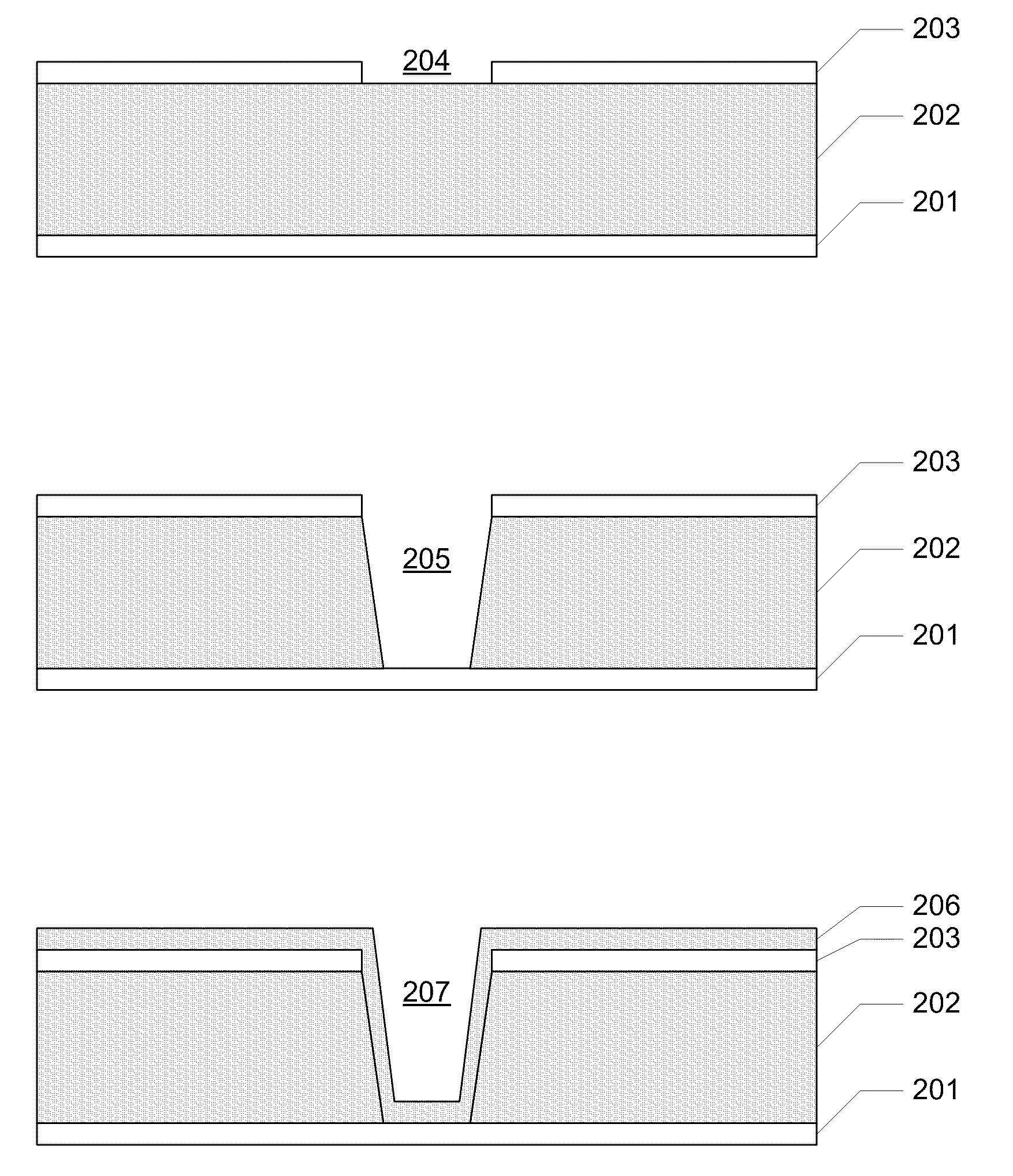

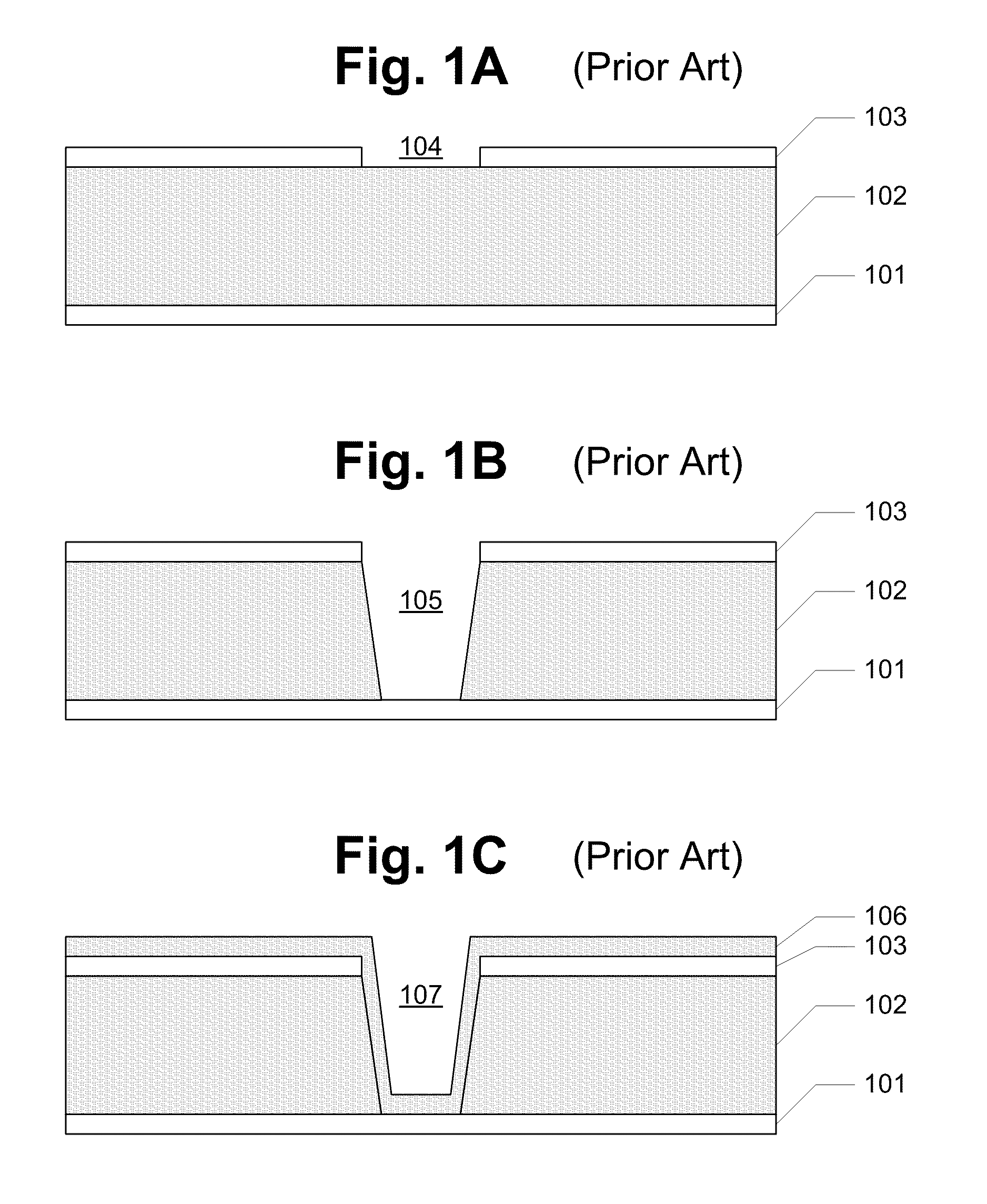

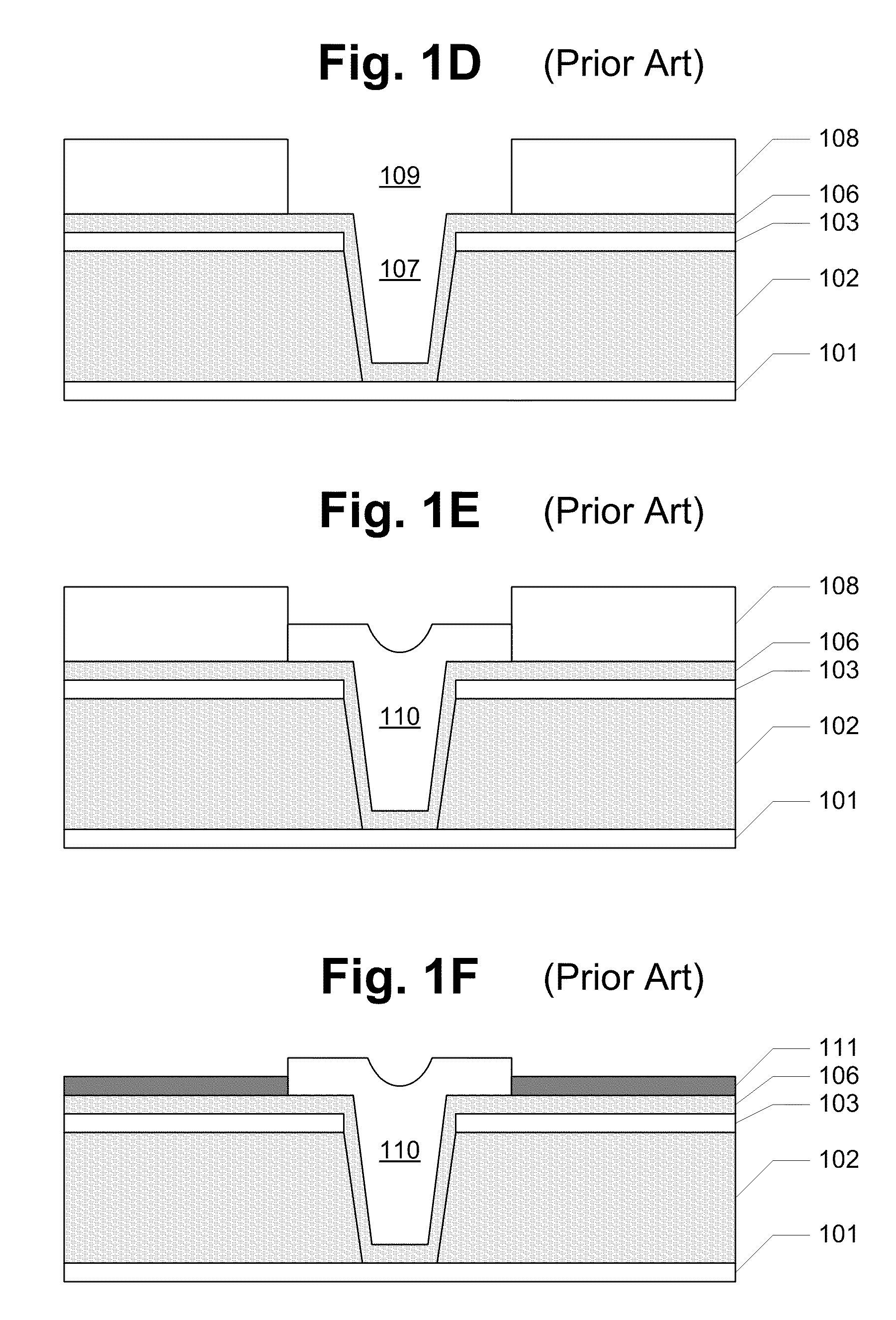

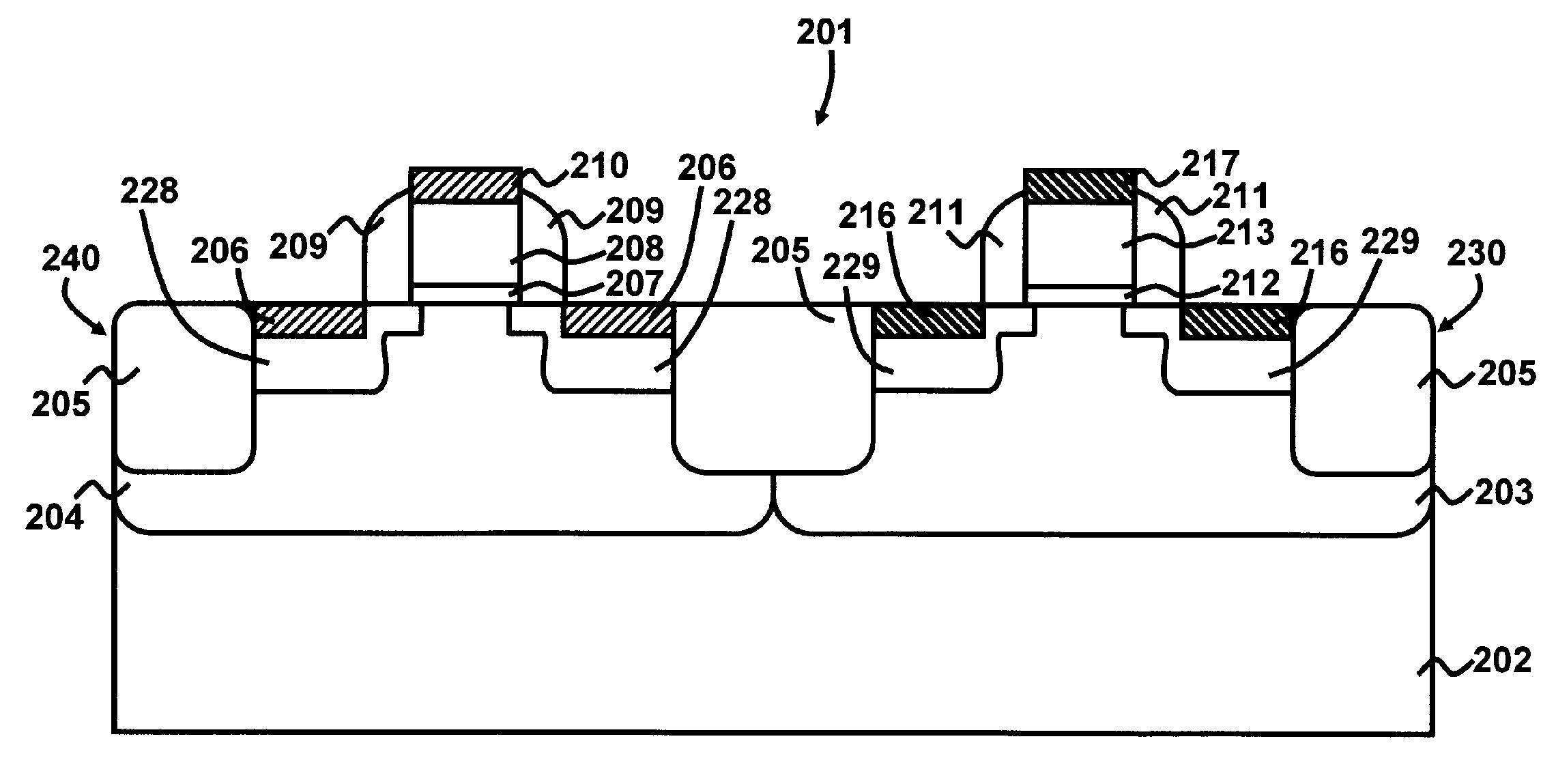

A method for forming a write pole comprises forming a stop layer over a substrate layer of a wafer, the stop layer having an opening above a damascene trench in the substrate layer, and forming a buffer layer over the stop layer, the buffer layer having an opening above the opening of the stop layer. The method further comprises plating a layer of magnetic material over the wafer, disposing a first sacrificial material over a region of the magnetic material above the damascene trench, performing a milling or etching operation over the wafer to remove the magnetic material not covered by the first sacrificial material and to remove the first sacrificial material, disposing a second sacrificial material over the wafer, and performing a polishing operation over the wafer to remove the region of the magnetic material above the damascene trench, the second sacrificial material, and the buffer layer.

Owner:WESTERN DIGITAL TECH INC

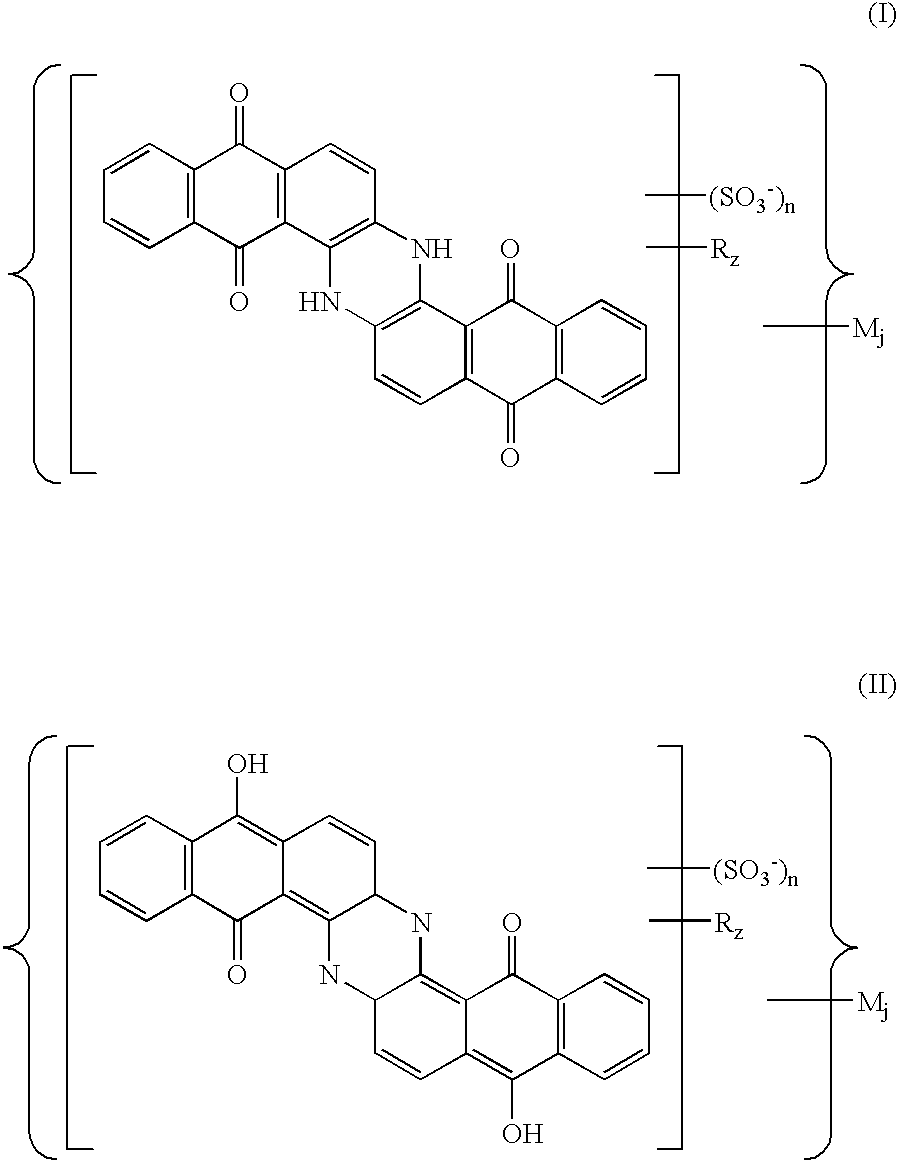

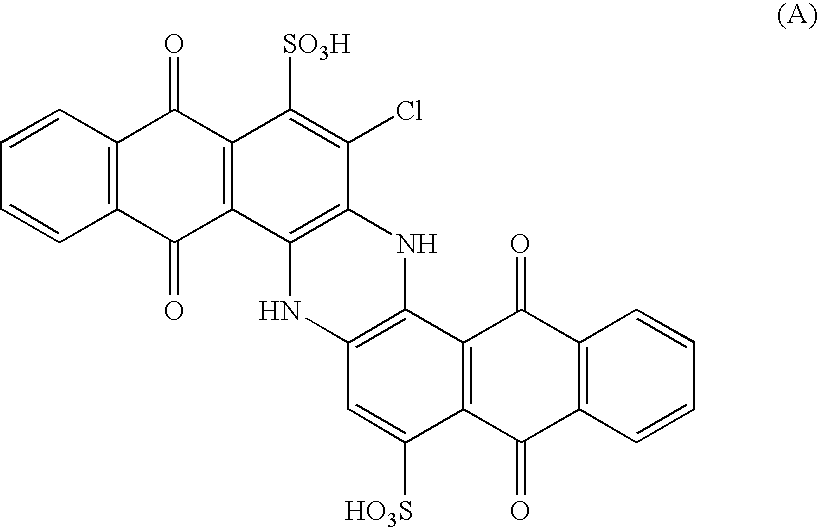

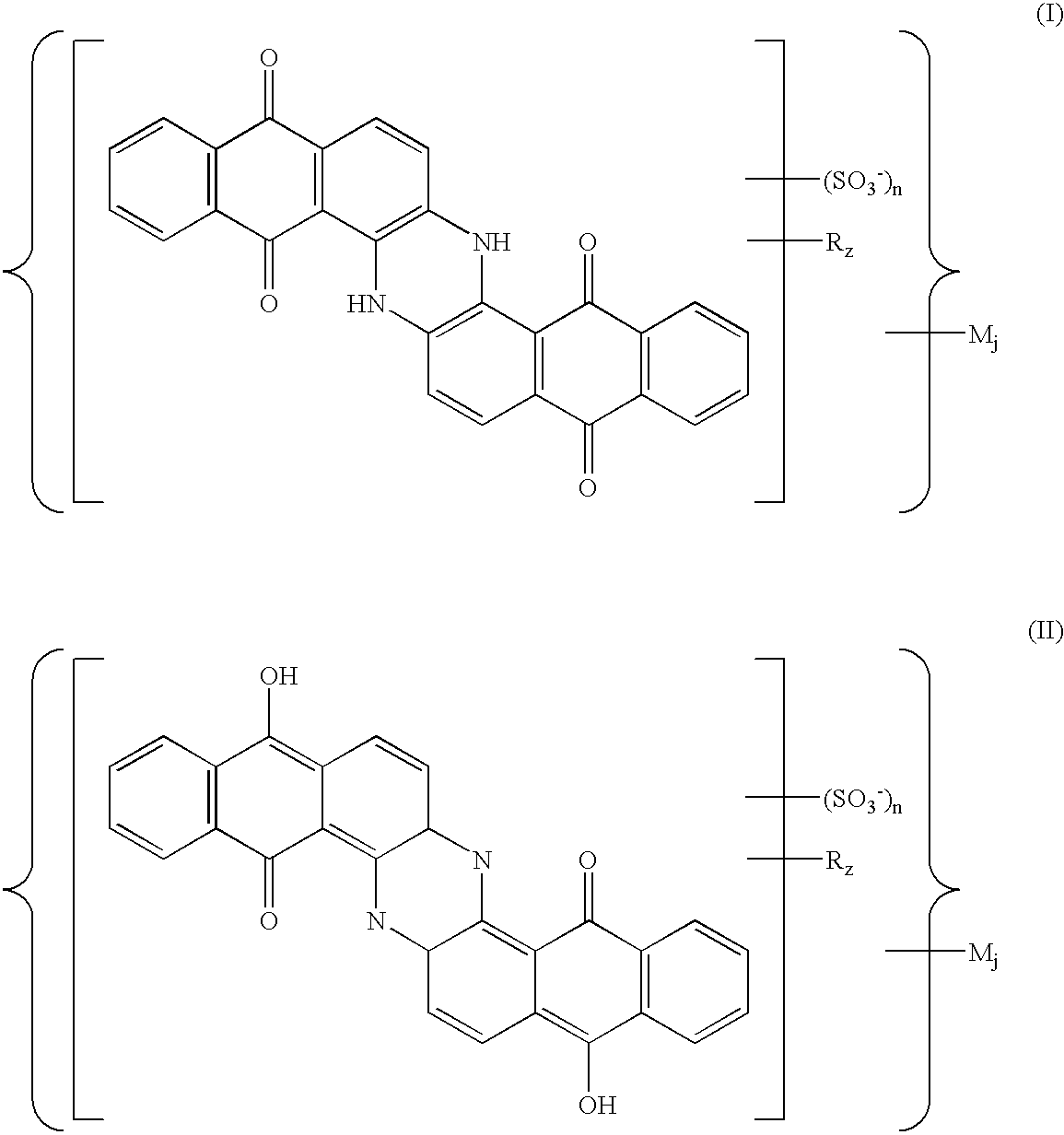

Sulfoderivatives of indanthrone, lyotropic liquid crystal system and anisotropic film on their base

InactiveUS6962734B2High phase stabilityExcellent optical propertiesLiquid crystal compositionsOrganic chemistryCrystallographyPolycyclic compound

Owner:NITTO DENKO CORP

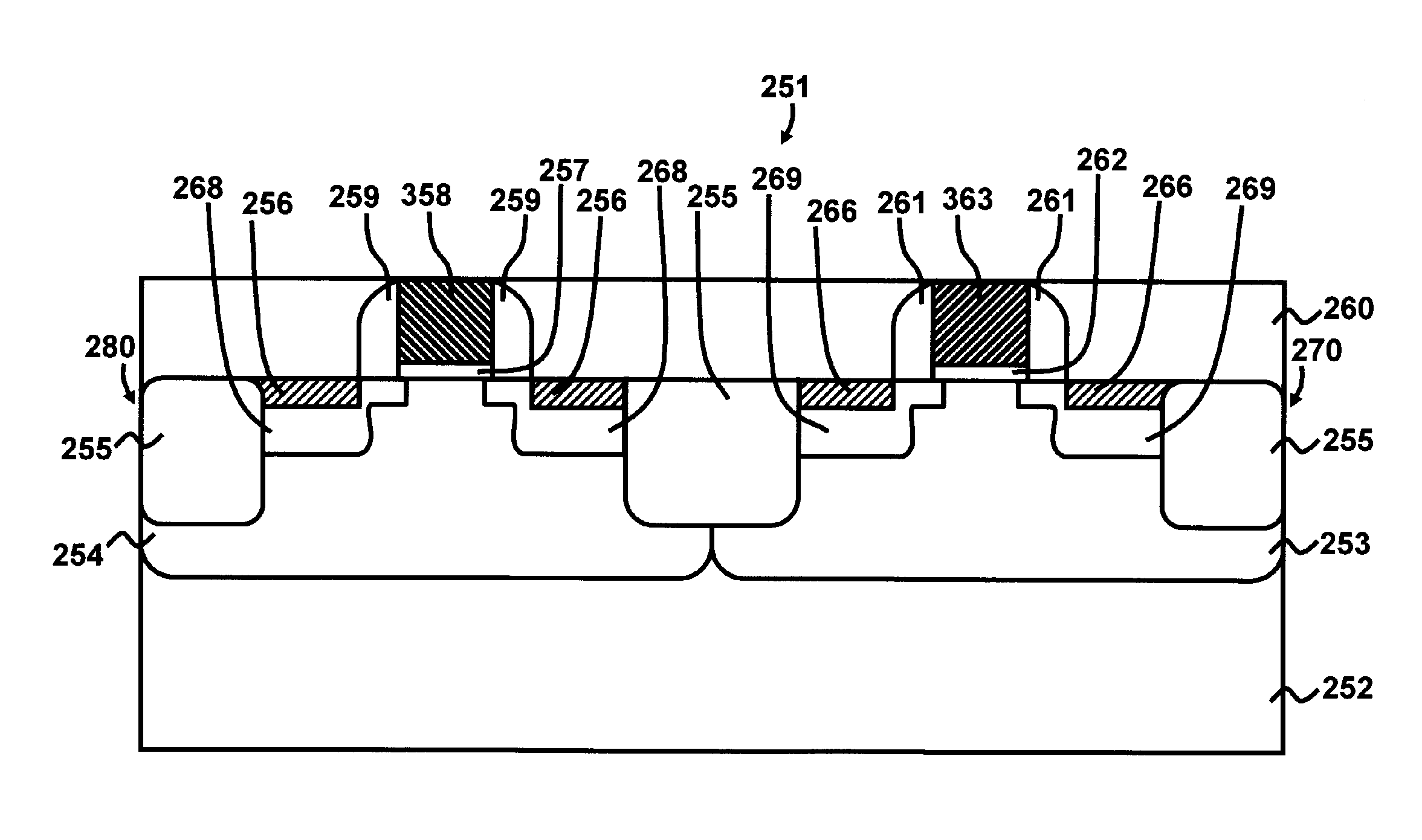

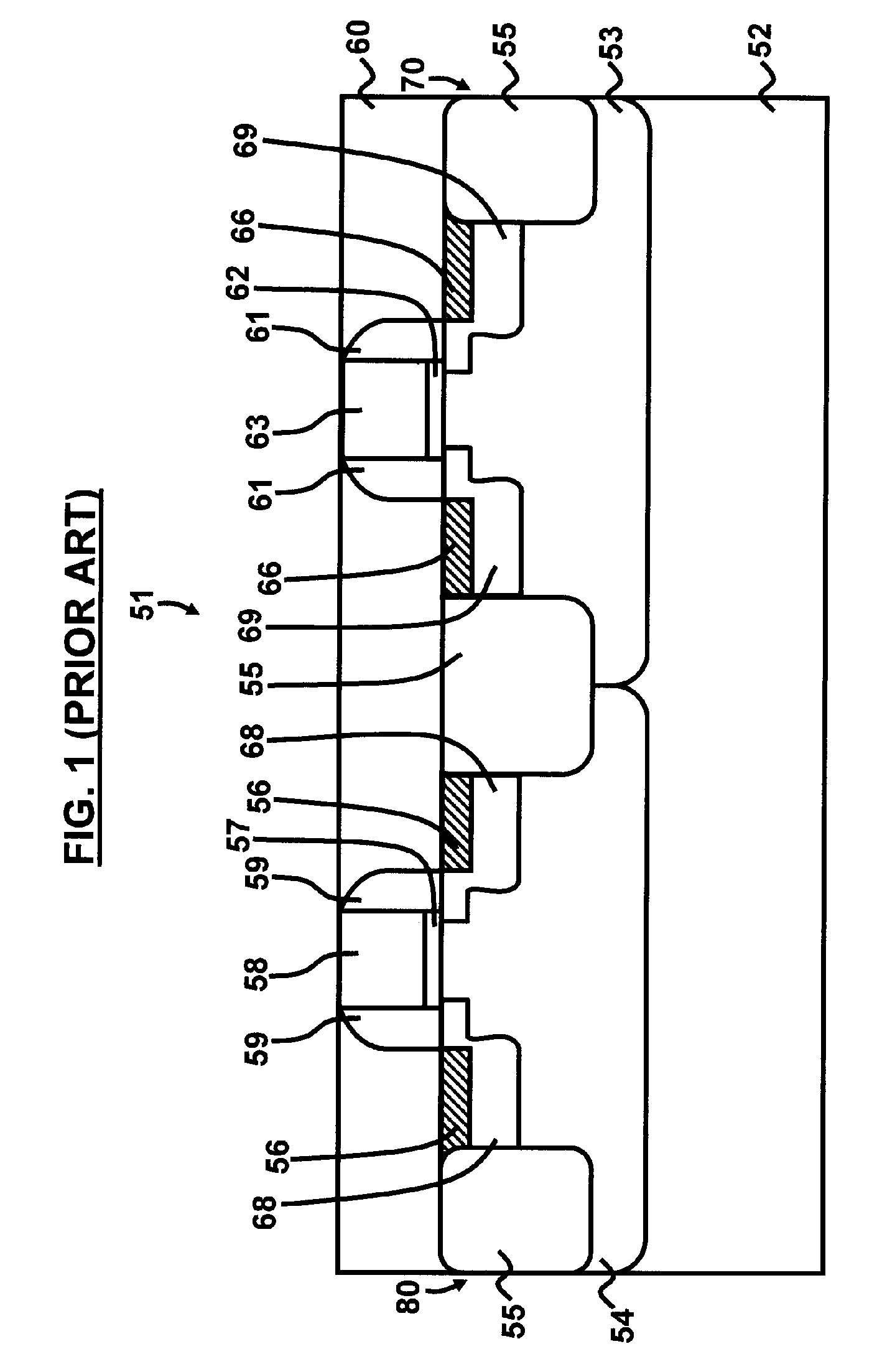

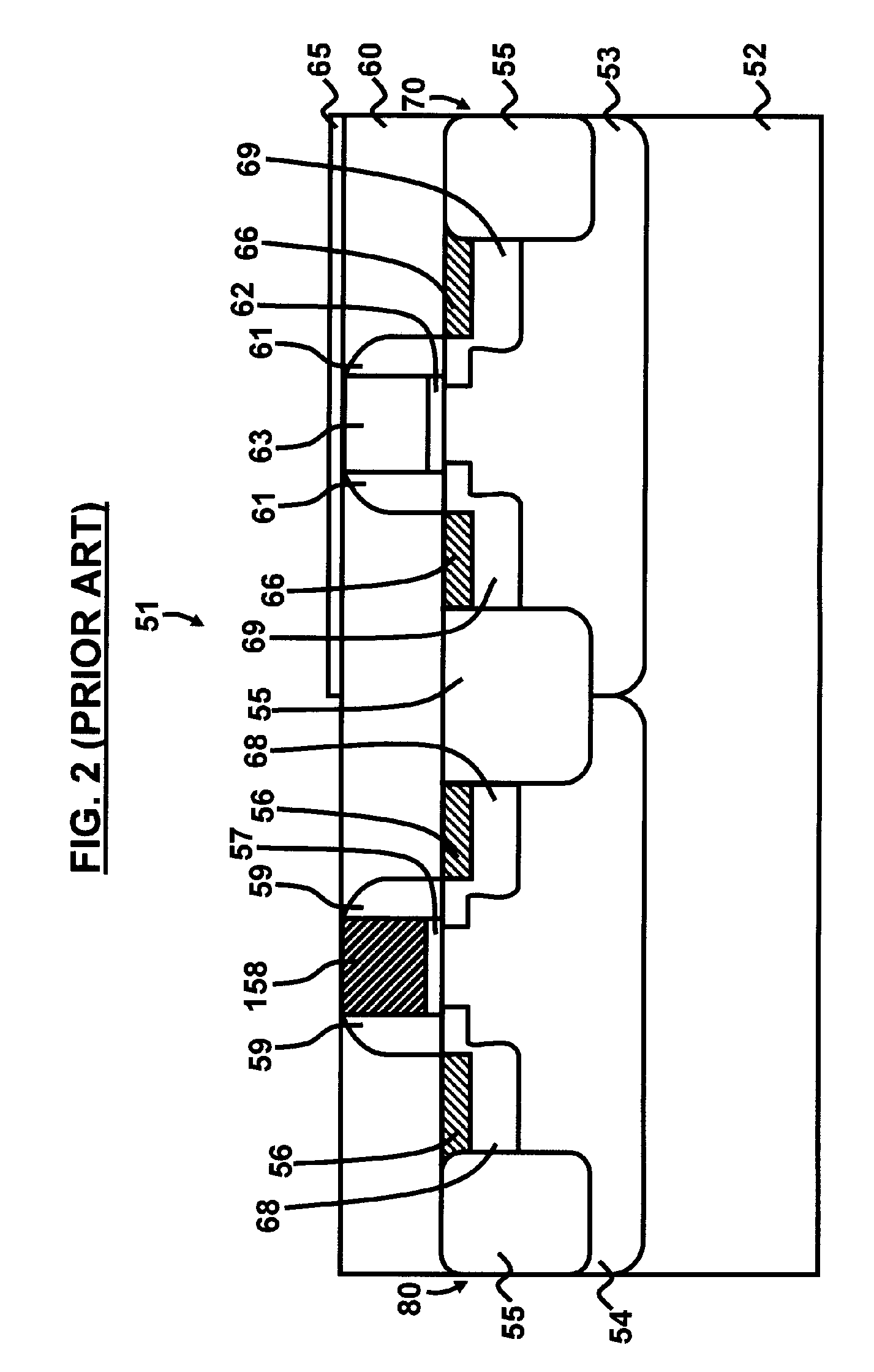

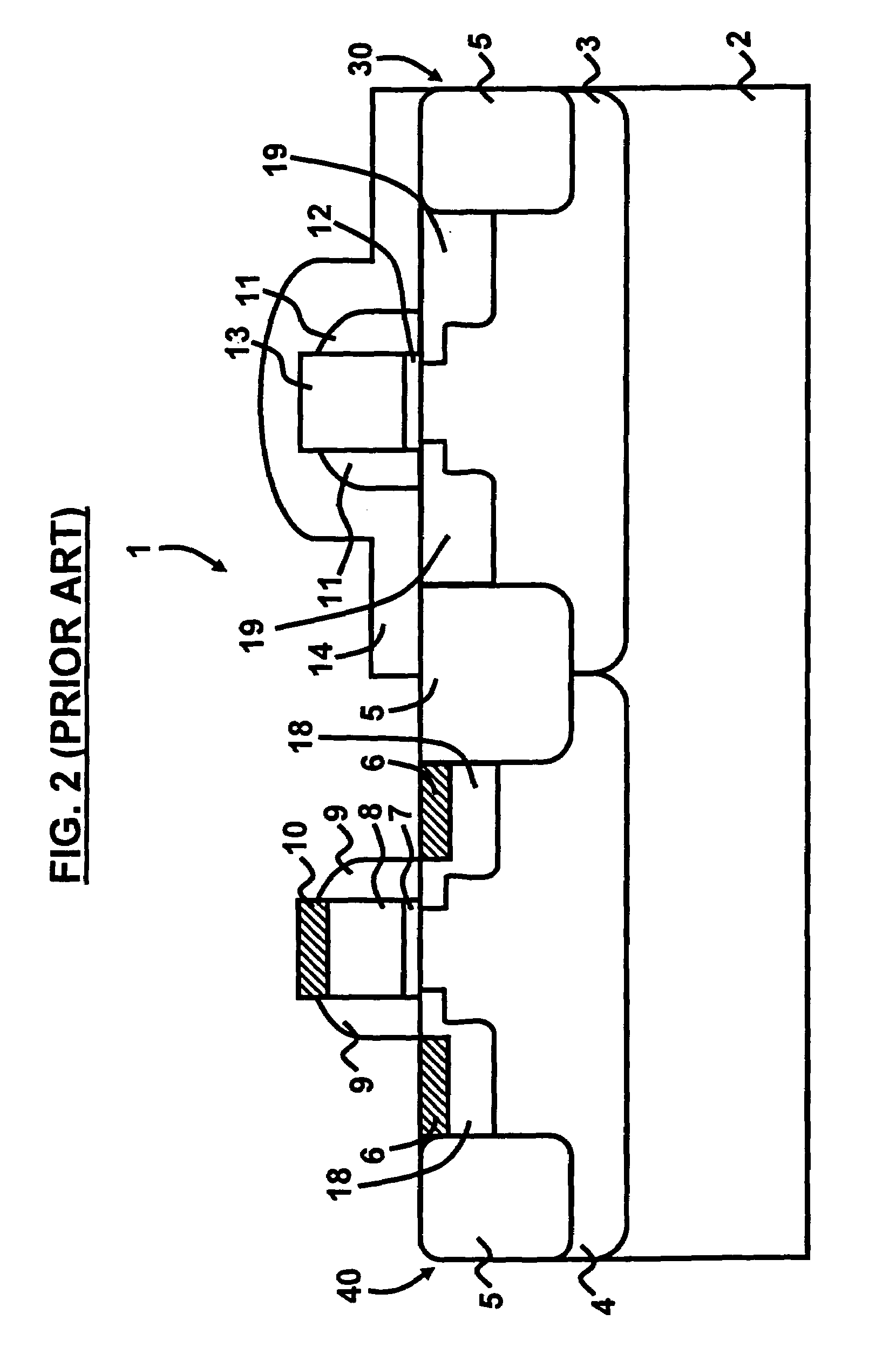

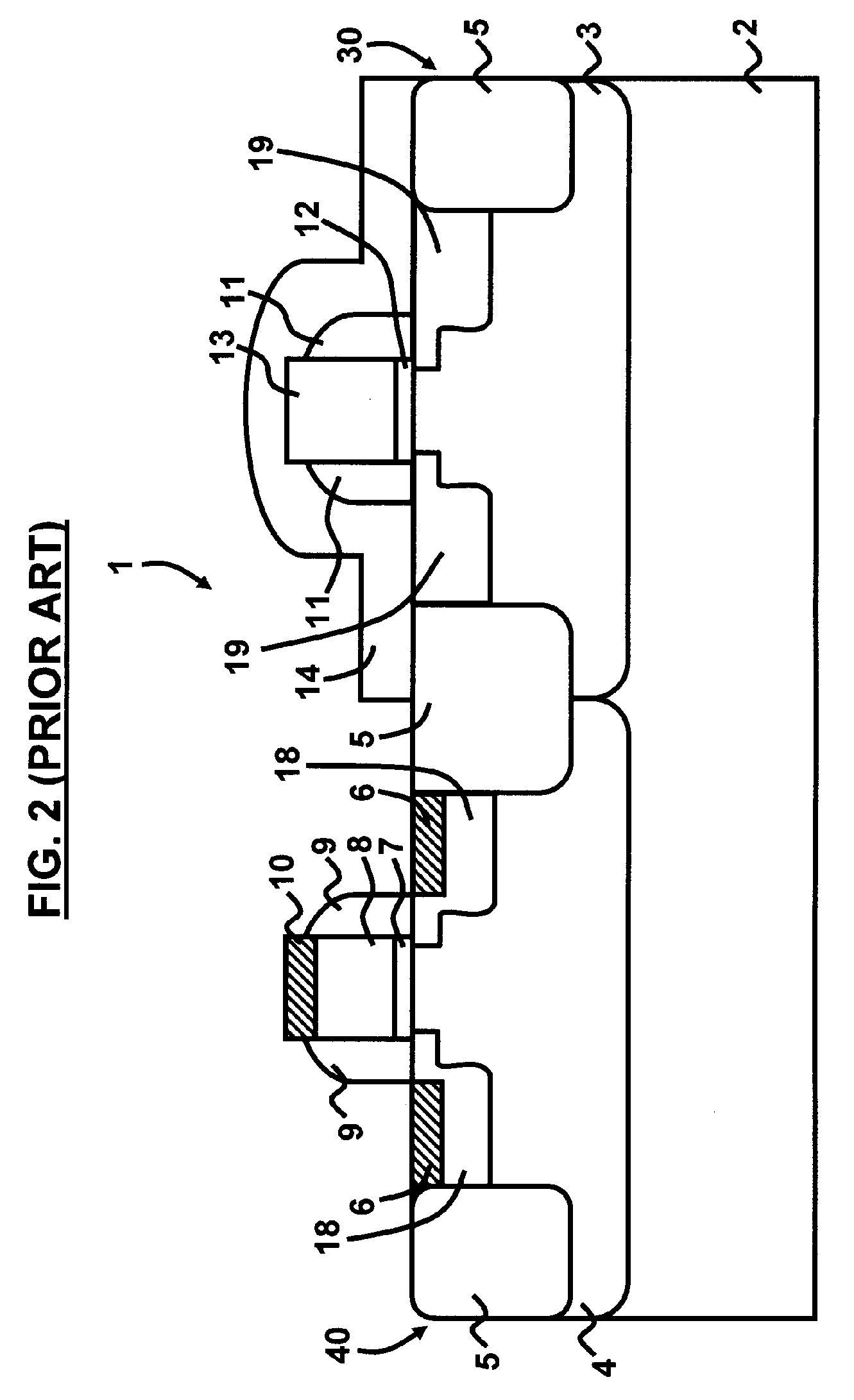

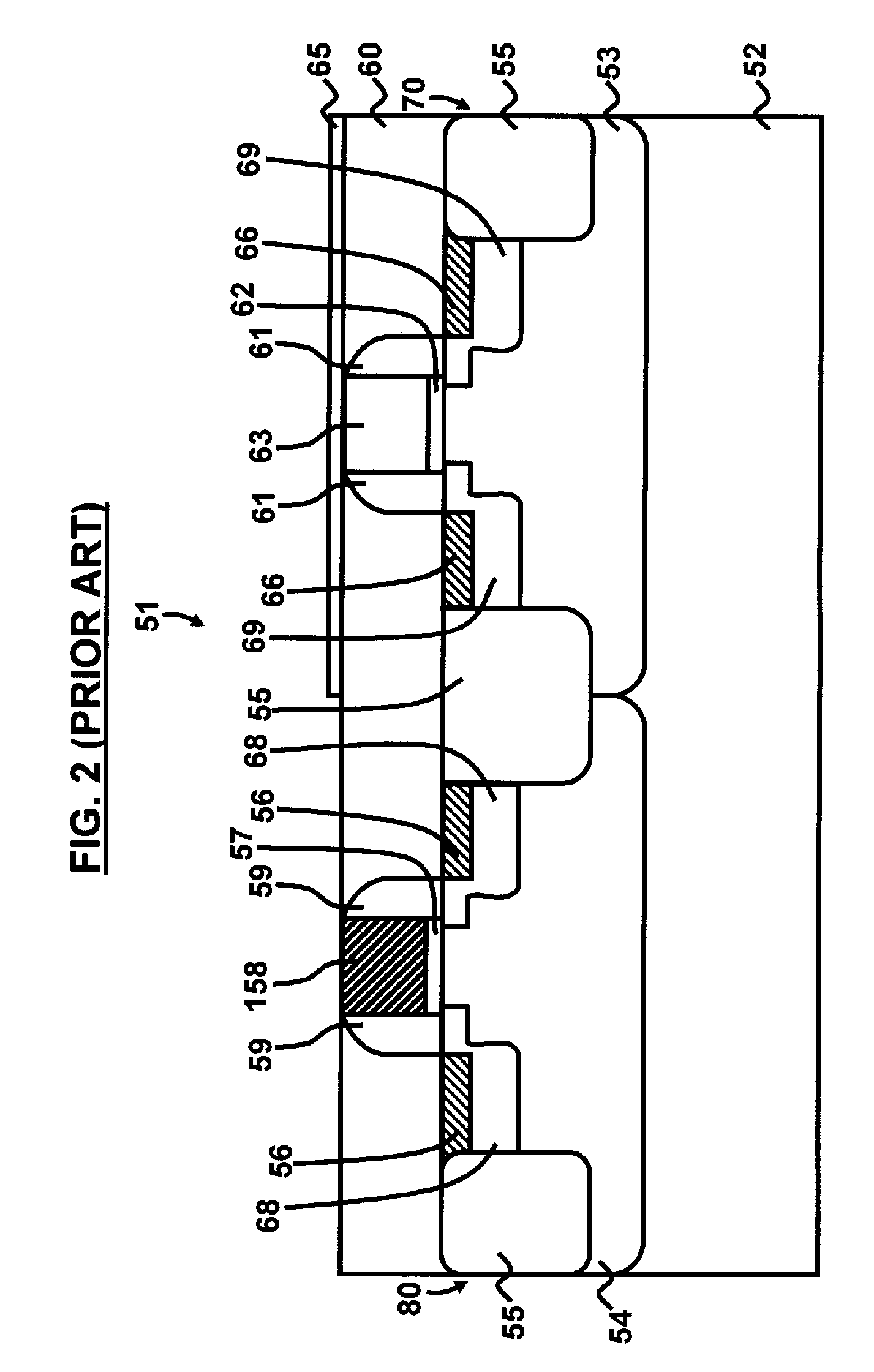

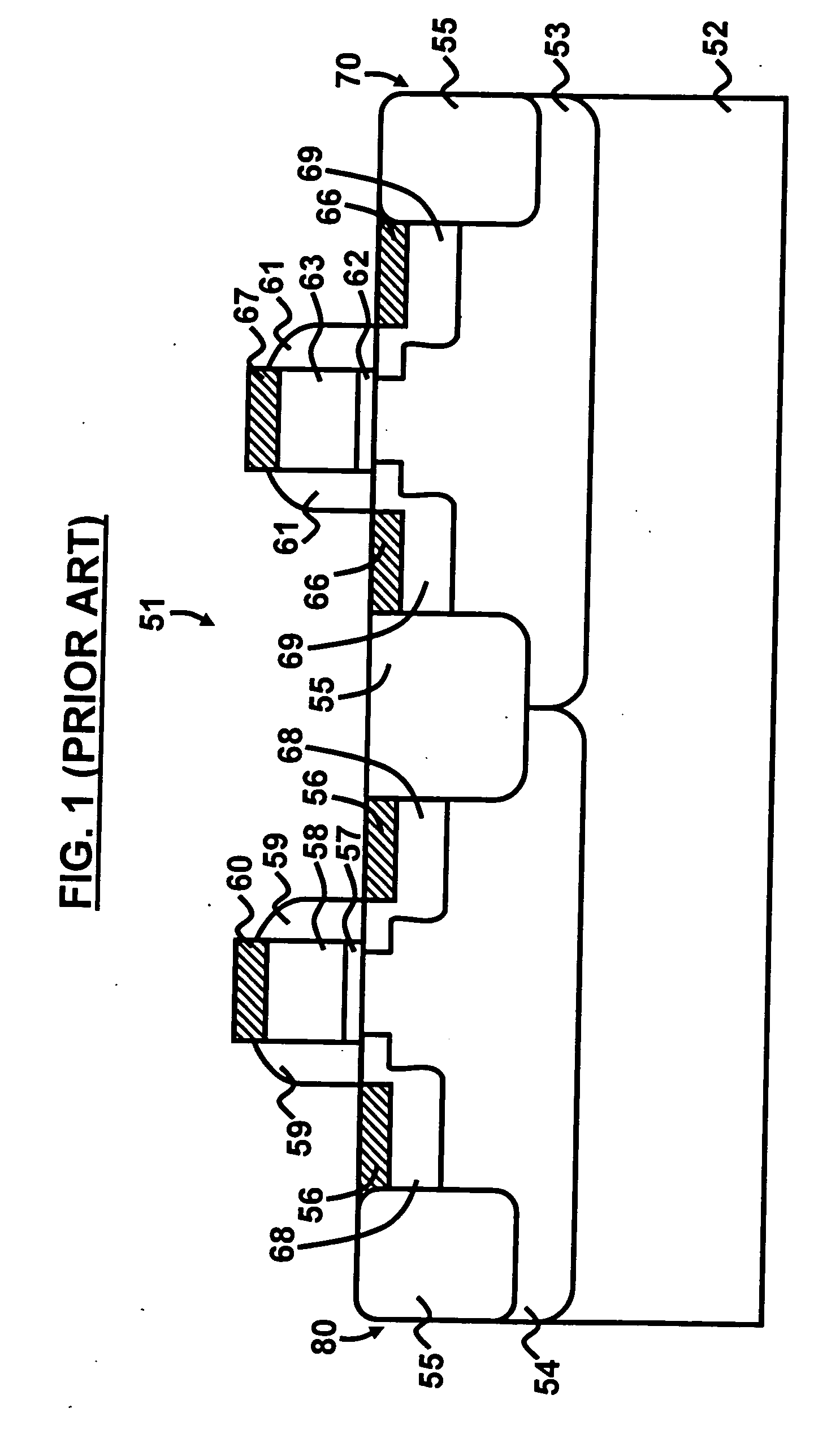

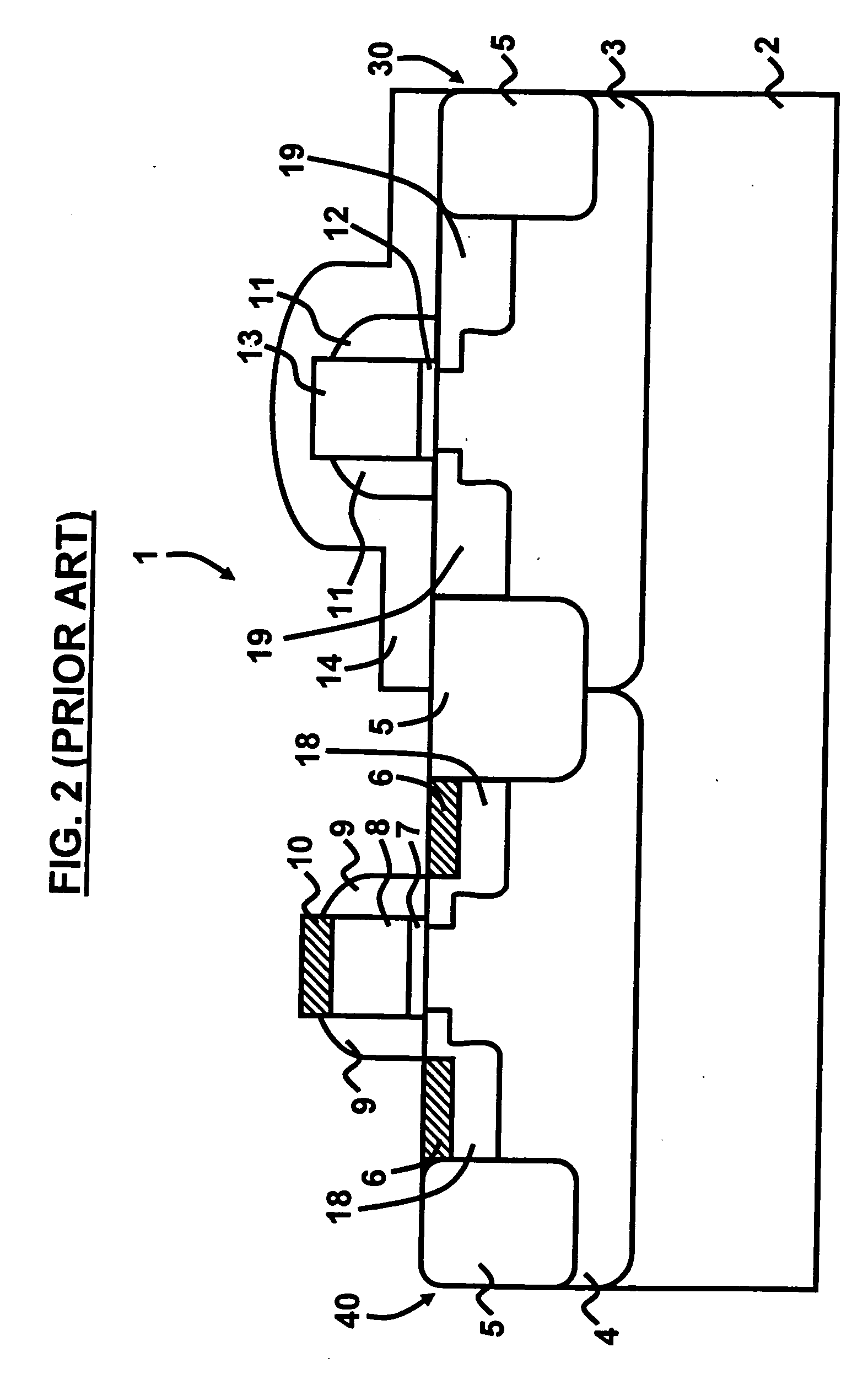

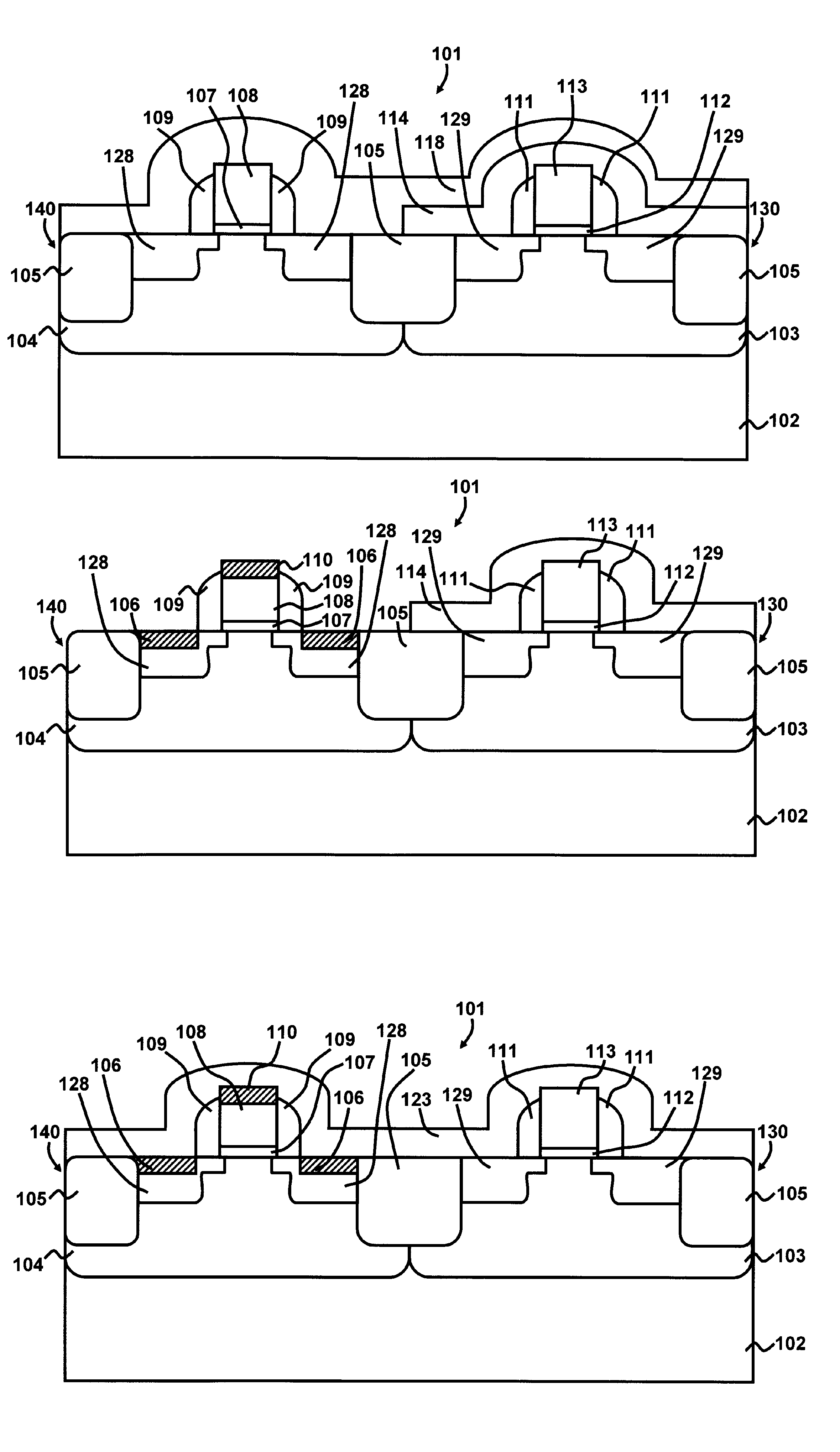

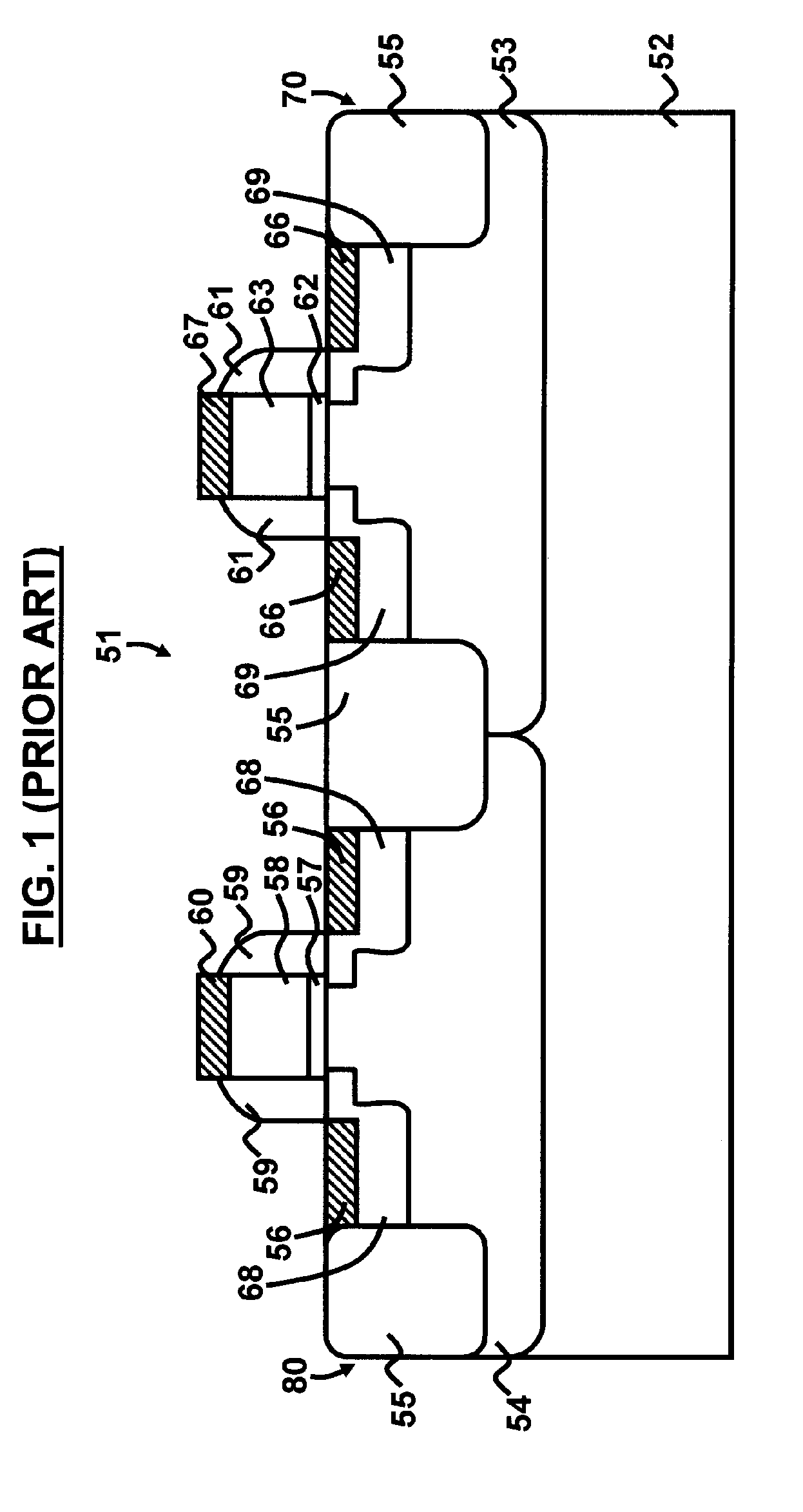

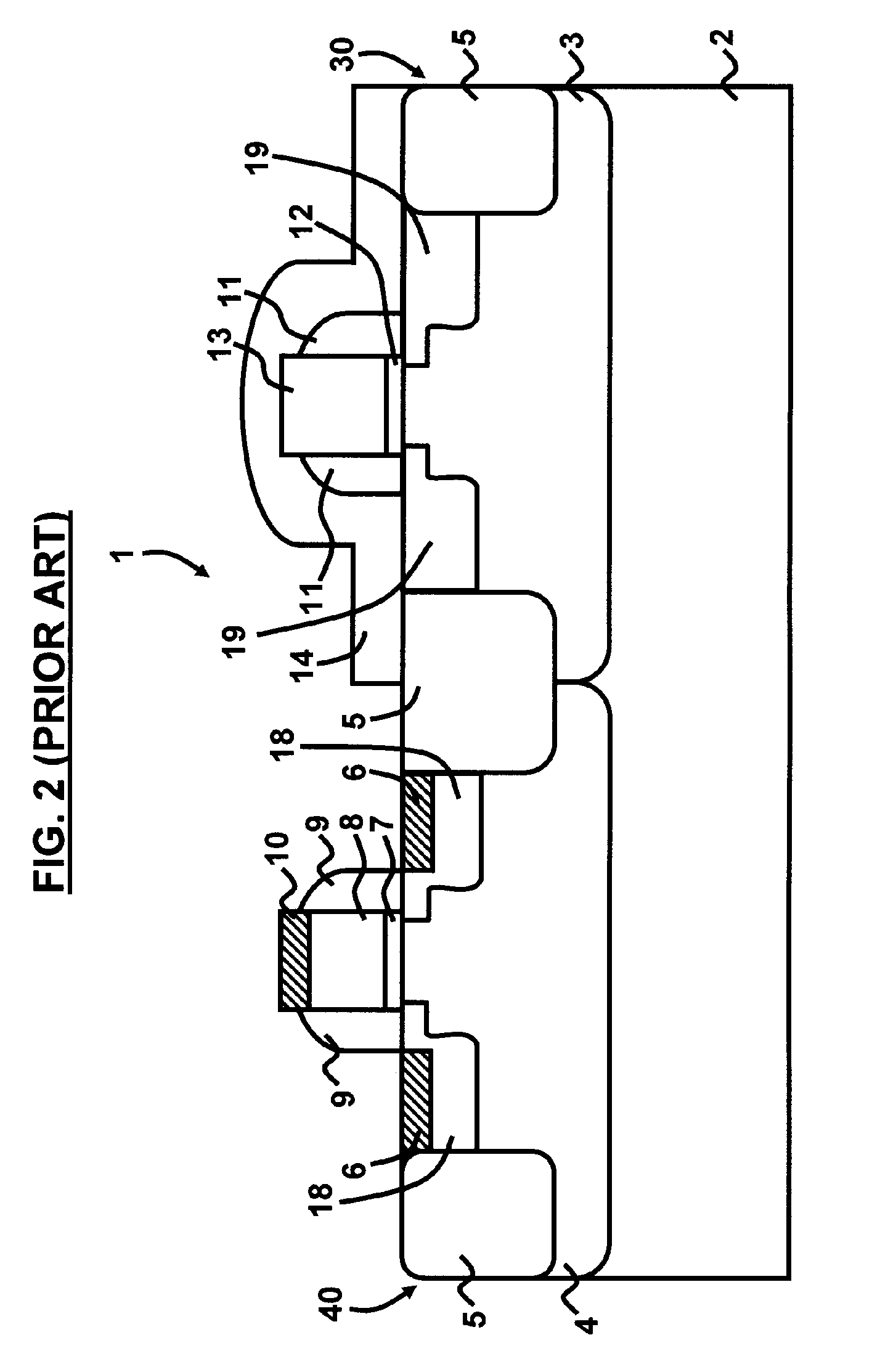

Method for forming self-aligned dual fully silicided gates in CMOS devices

InactiveUS7122472B2Lower Level RequirementsThe formation process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideCMOS

A method of forming a dual self-aligned fully silicided gate in a CMOS device requiring only one lithography level, wherein the method comprises forming a first type semiconductor device having a first well region in a semiconductor substrate, first source / drain silicide areas in the first well region, and a first type gate isolated from the first source / drain silicide areas; forming a second type semiconductor device having a second well region in the semiconductor substrate, second source / drain silicide areas in the second well region, and a second type gate isolated from the second source / drain silicide areas; selectively forming a first metal layer over the second type semiconductor device; performing a first fully silicided (FUSI) gate formation on only the second type gate; depositing a second metal layer over the first and second type semiconductor devices; and performing a second FUSI gate formation on only the first type gate.

Owner:INT BUSINESS MASCH CORP

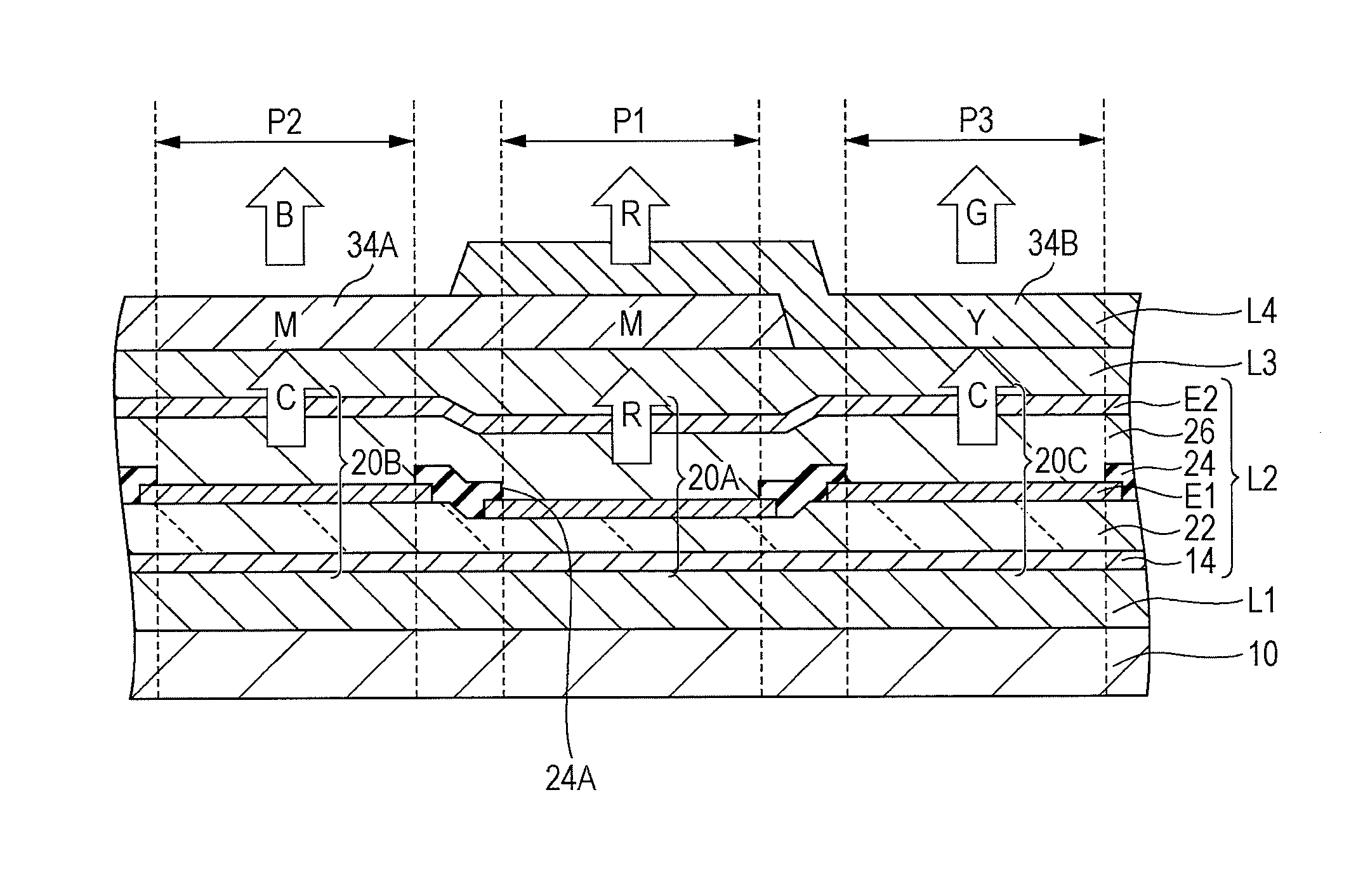

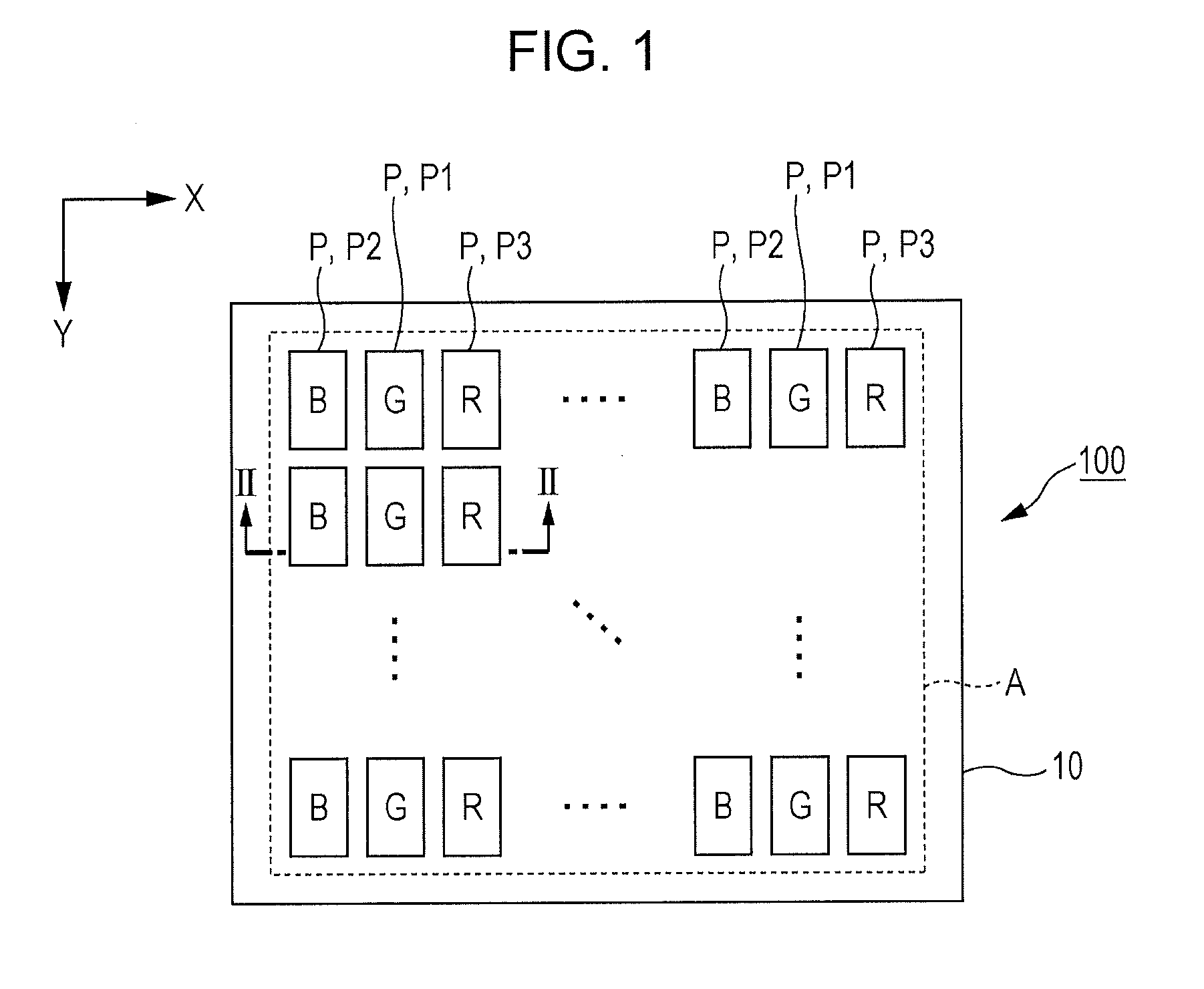

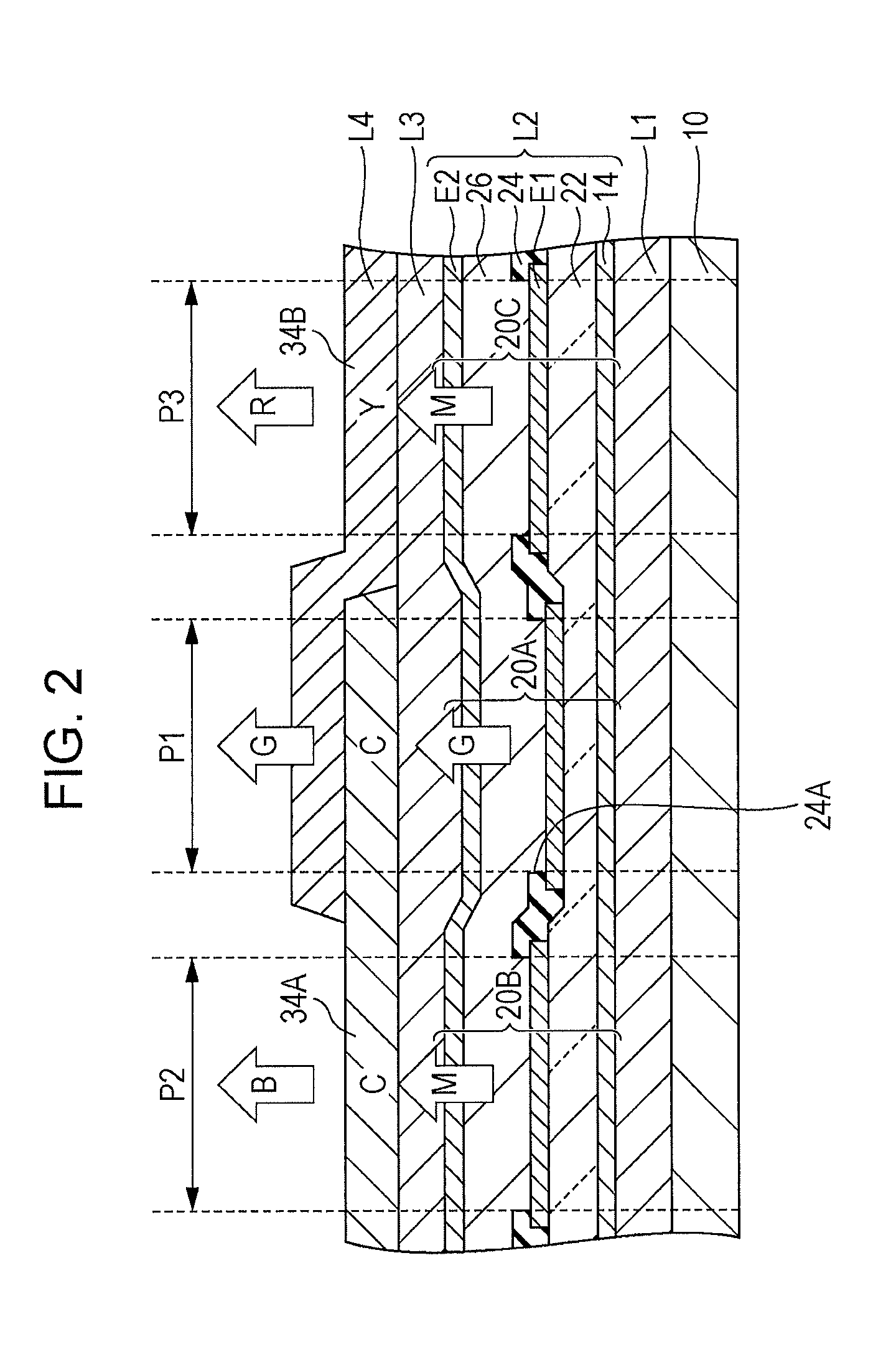

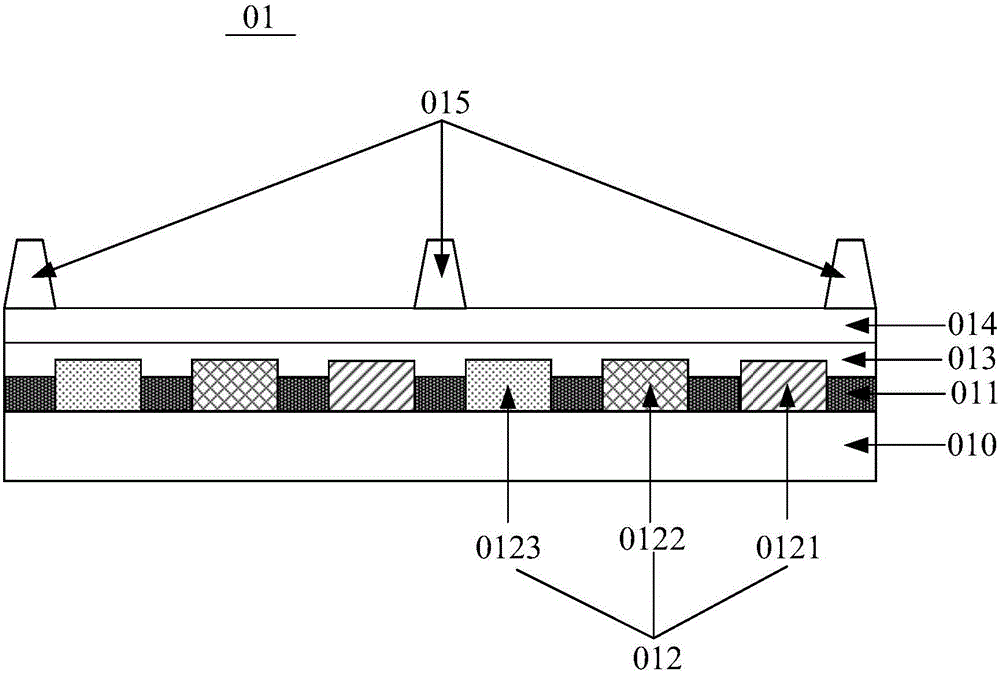

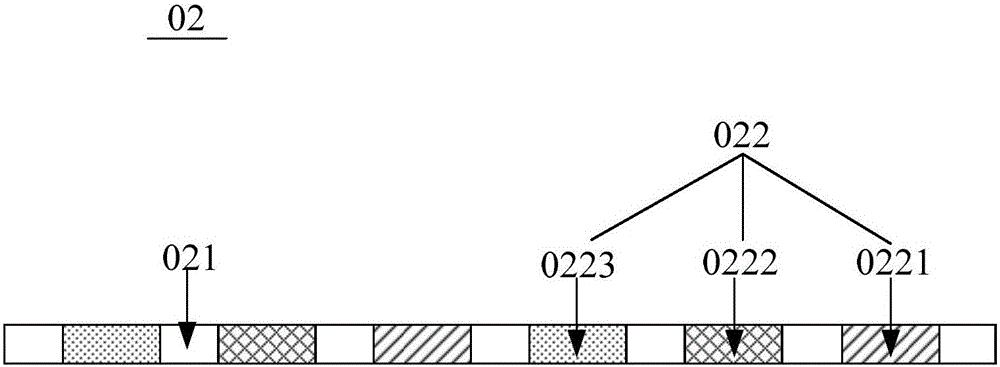

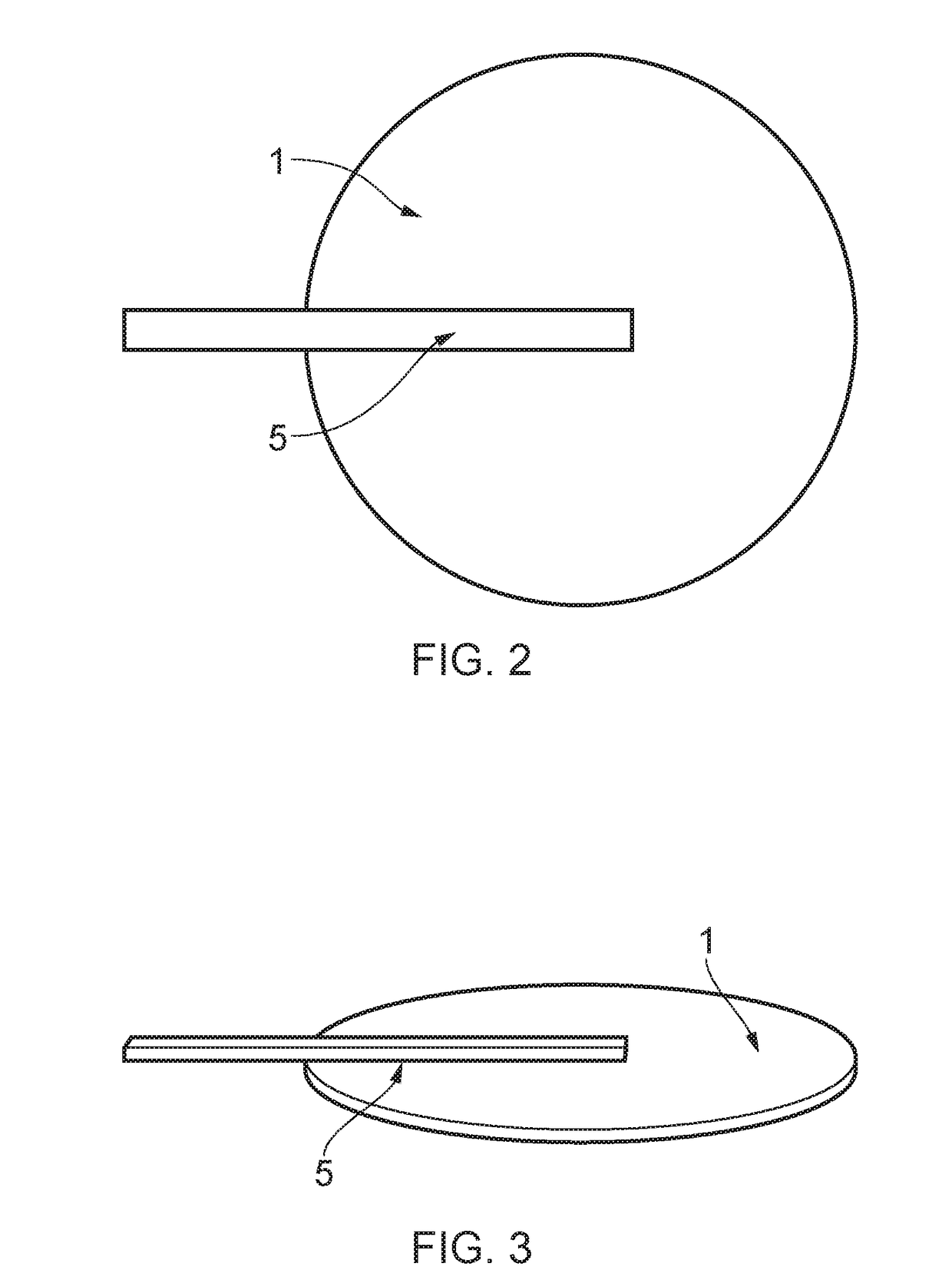

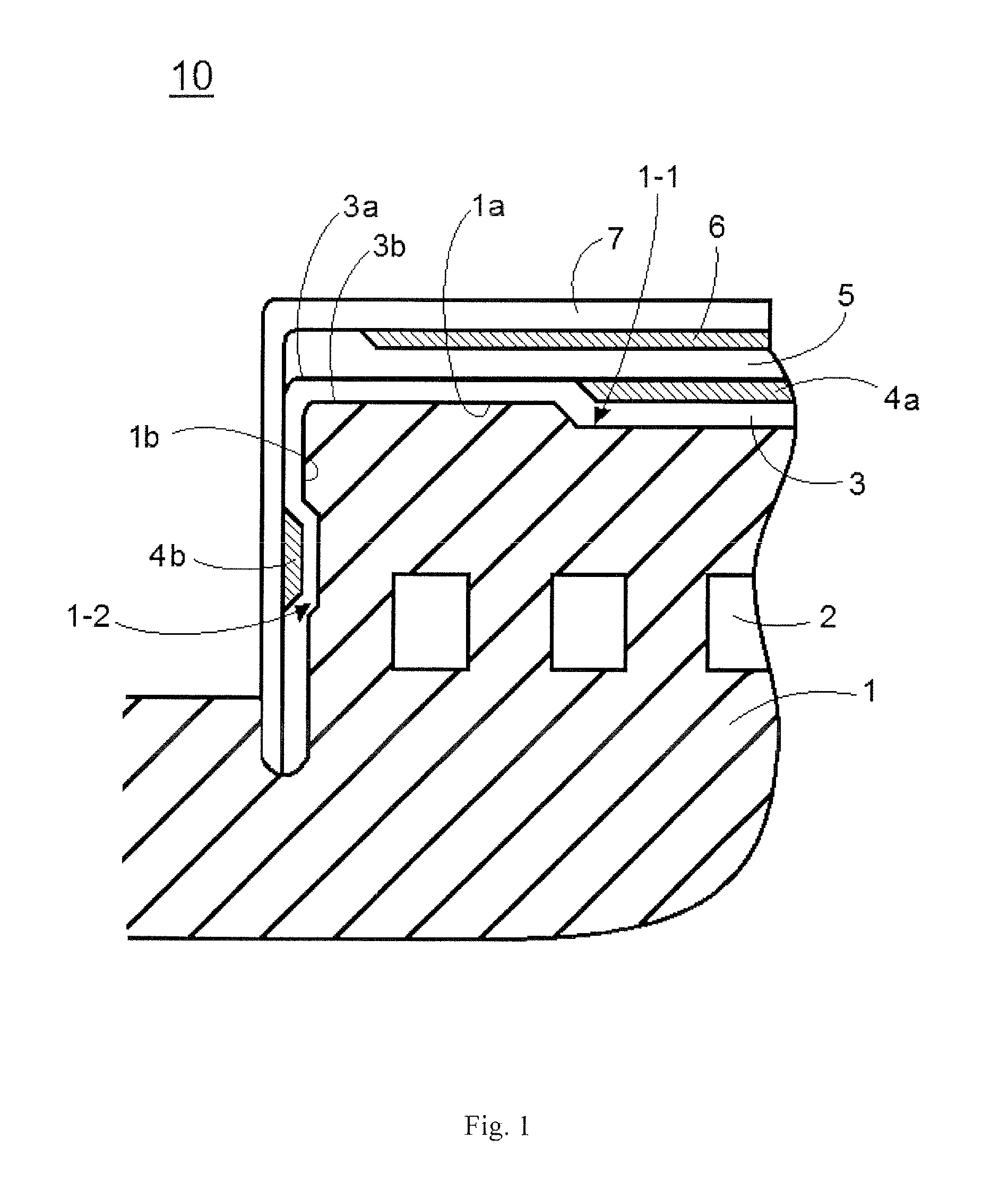

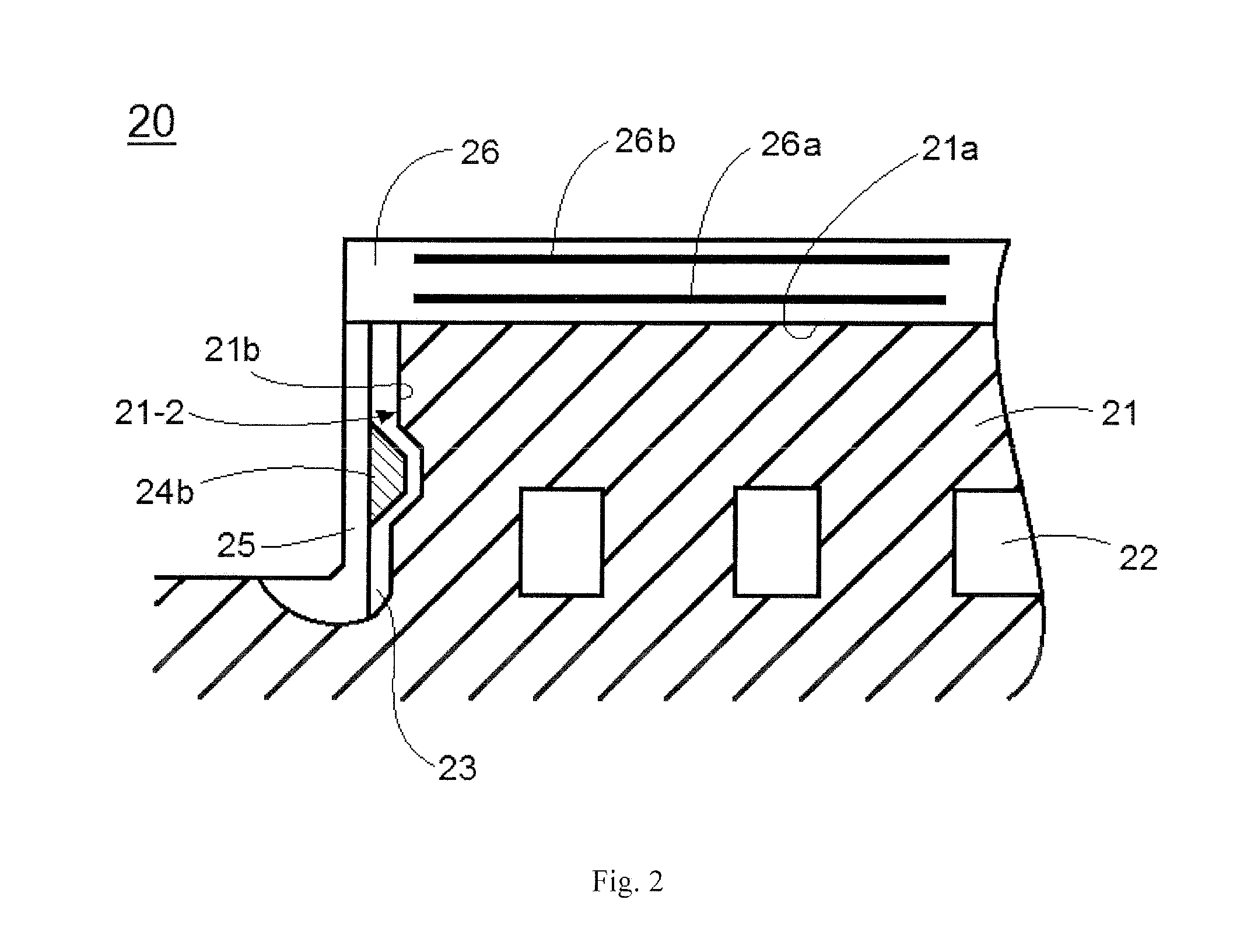

Light-emitting device and electronic apparatus

ActiveUS20160025302A1Simple formatSimple structureElongate light sourcesSpectral modifiersWavelength rangeTransmitted light

A light-emitting device includes a first pixel, a second pixel, and a third pixel. The first pixel includes a first light-emitting element that emits light in a first wavelength range. The second pixel includes a second light-emitting element that emits light in a fourth wavelength range that is different from the first wavelength range and that includes a second wavelength range and a third wavelength range and a first color filter that transmits light in the second wavelength range emitted from the second light-emitting element. The third pixel includes a third light-emitting element that emits light in the fourth wavelength range and a second color filter that transmits light in the third wavelength range emitted from the third light-emitting element.

Owner:SEIKO EPSON CORP

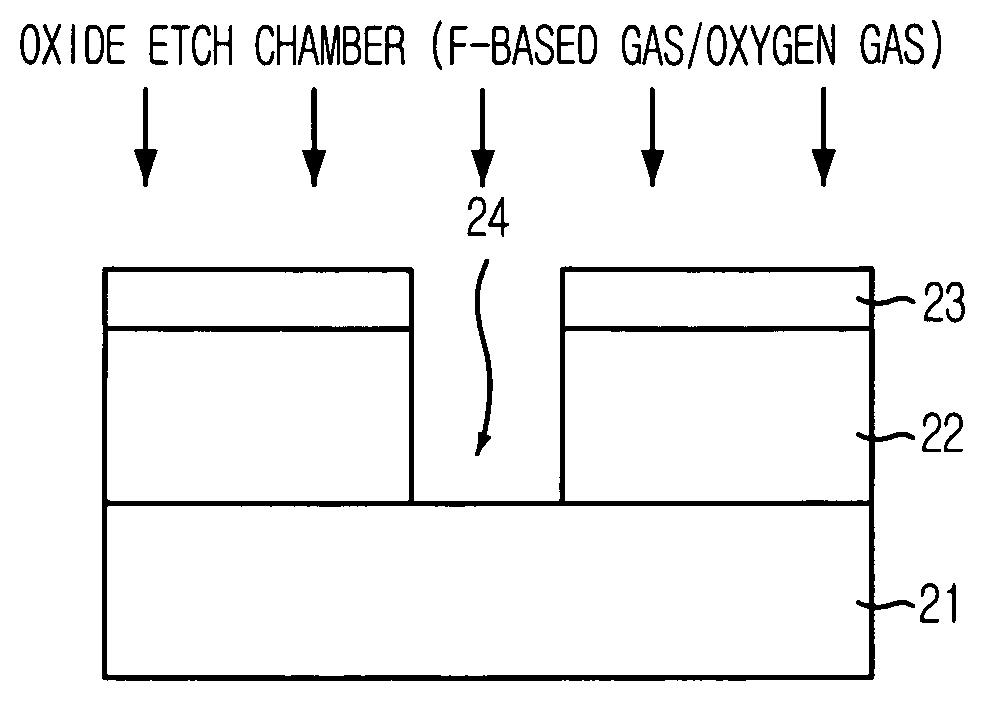

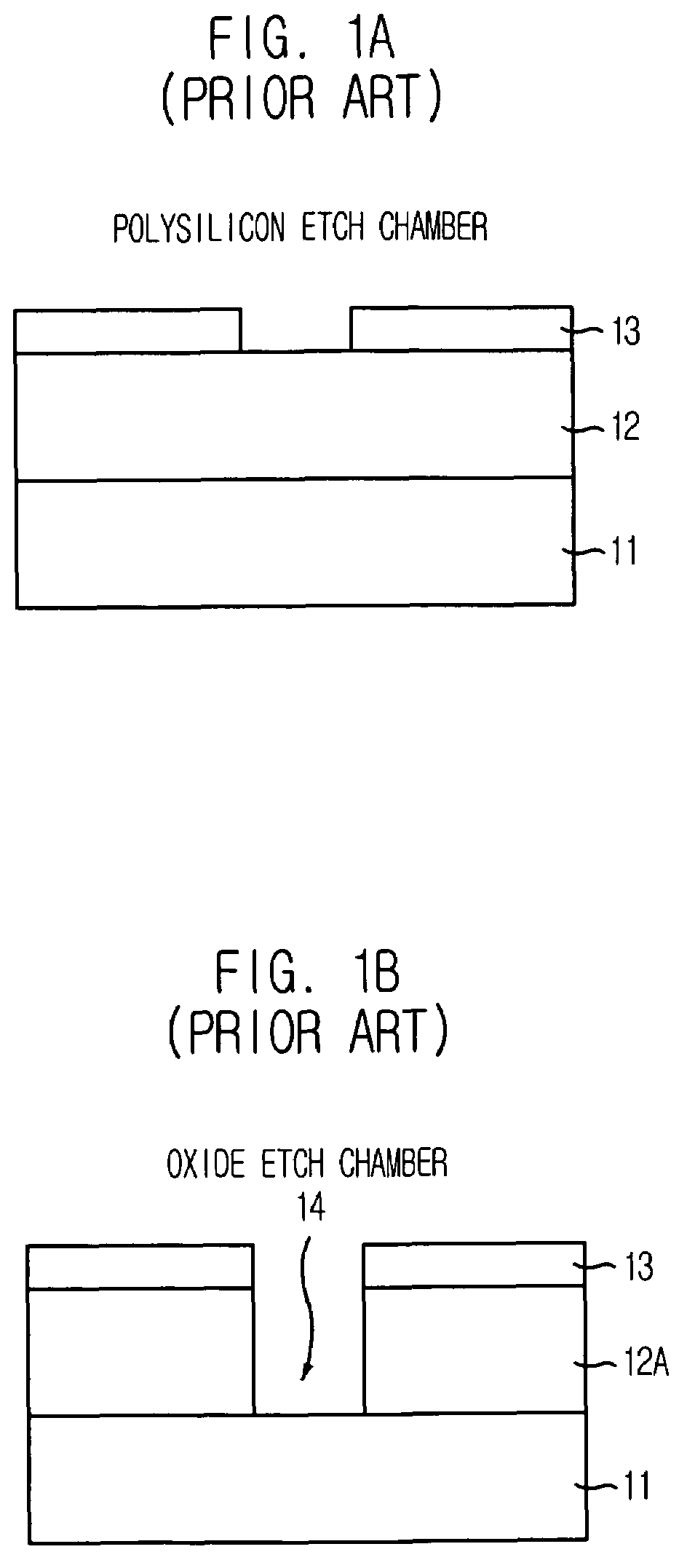

Method for fabricating semiconductor device

InactiveUS7256129B2Avoid it happening againThe formation process is simpleDecorative surface effectsSemiconductor/solid-state device manufacturingInsulation layerInter layer

A method for fabricating a semiconductor device is provided. The method includes: forming an inter-layer insulation layer on a substrate; forming a hard mask layer on the inter-layer insulation layer; etching the hard mask layer using a contact mask; and etching the inter-layer insulation layer using the hard mask layer as an etch barrier, thereby obtaining an opening wherein the etching of the hard mask layer and the etching of the inter-layer insulation layer are performed in one etch chamber.

Owner:SK HYNIX INC

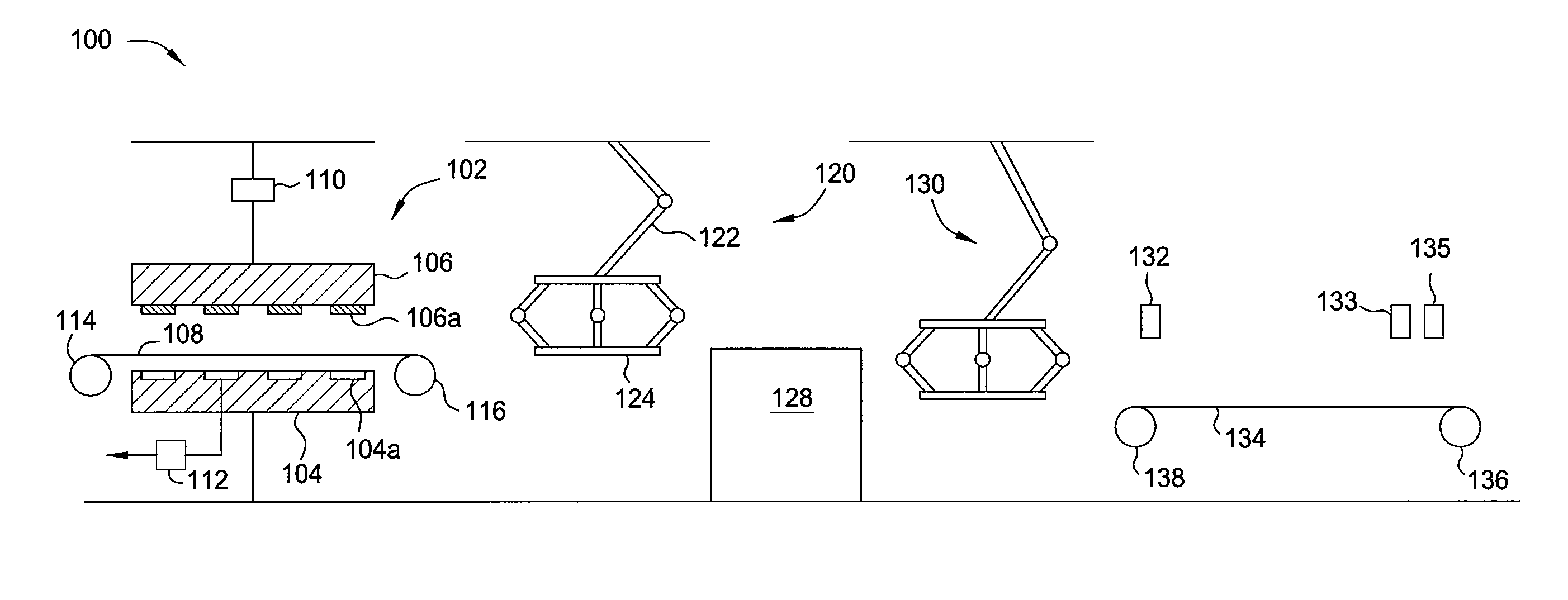

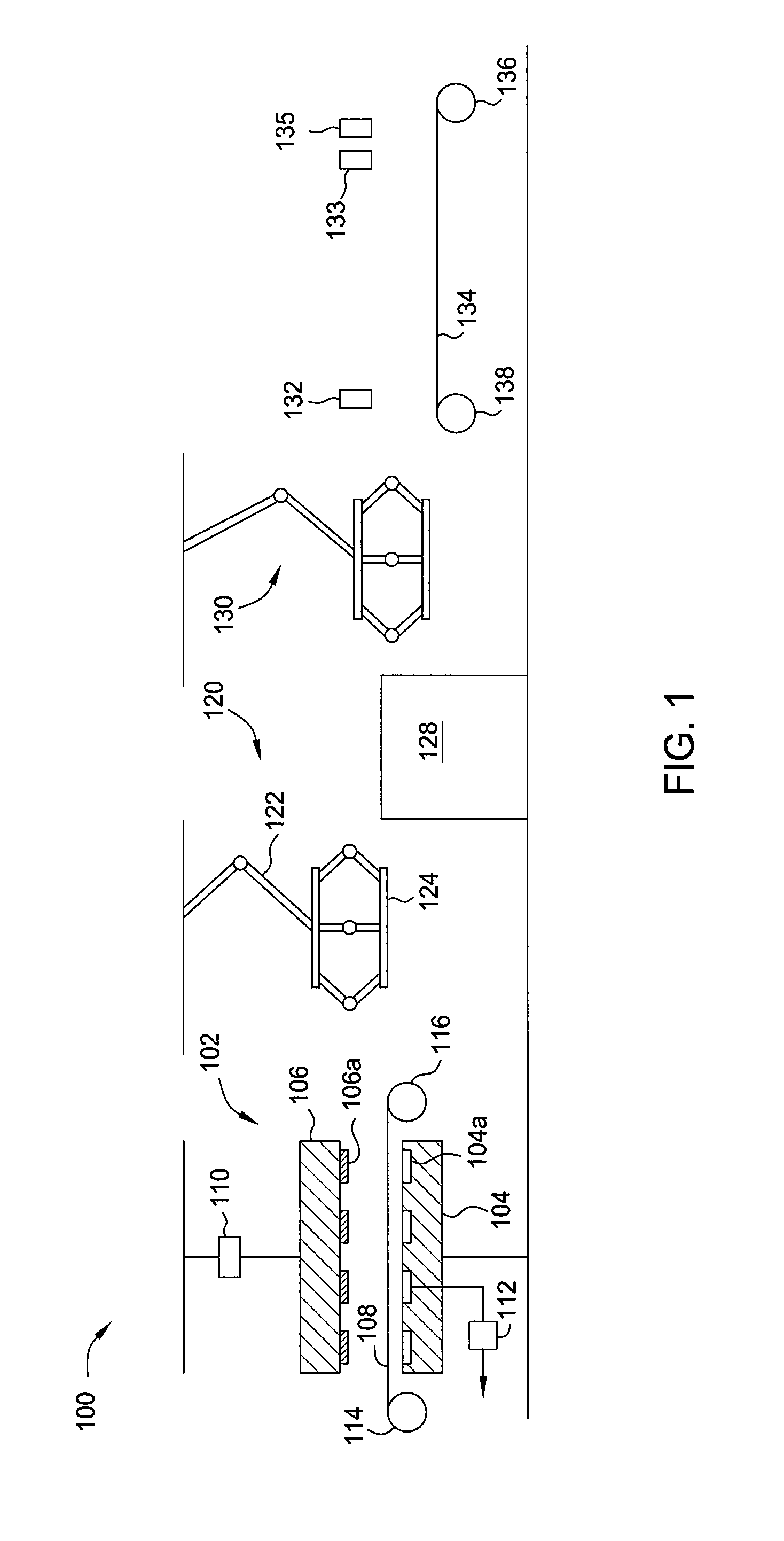

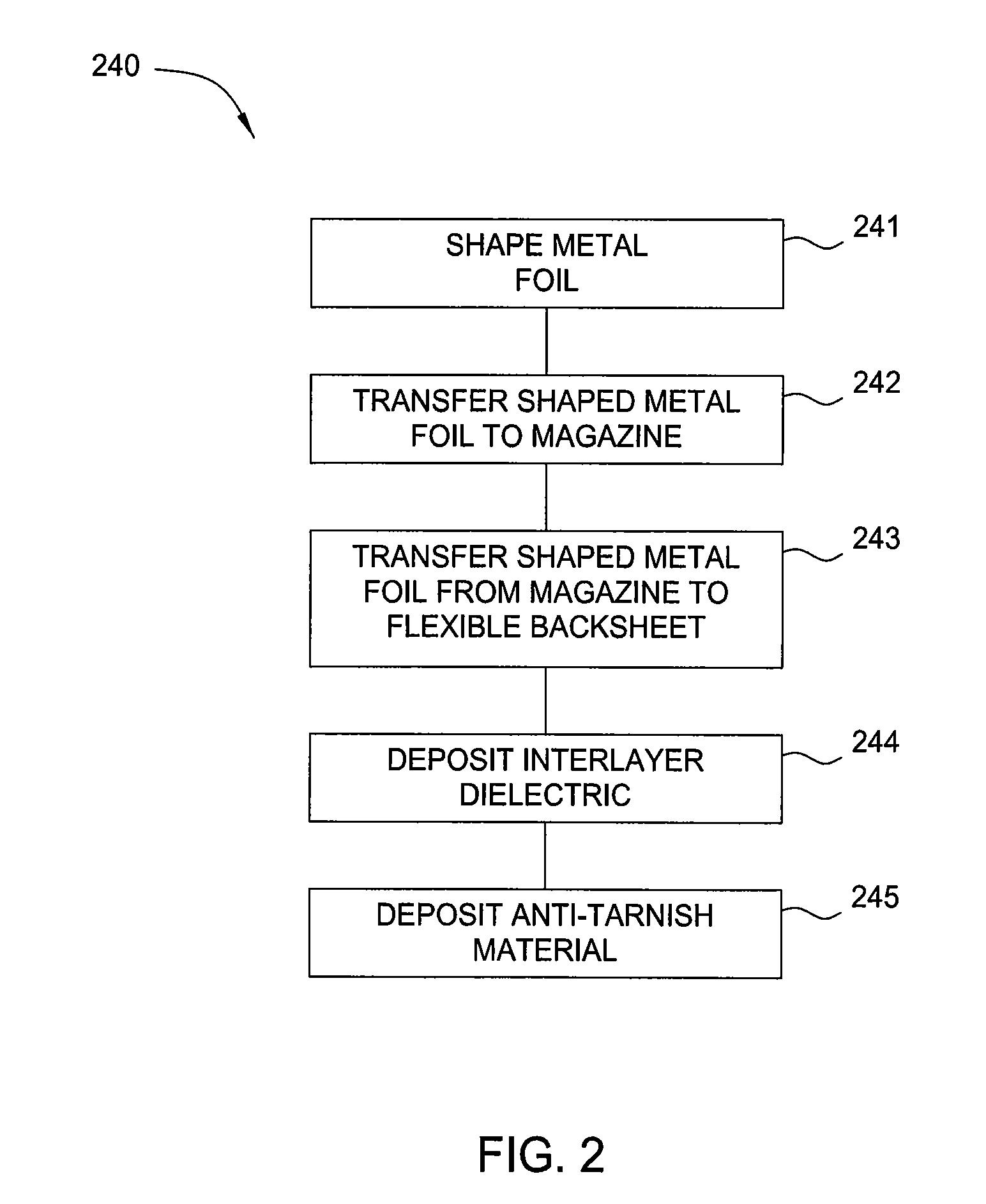

Process for forming flexible substrates using punch press type techniques

InactiveUS20120234586A1Simplify flexible substrate formation processReduce consumptionConductive pattern formationCircuit susbtrate materialsResistPunch press

Embodiments of the invention generally relate to methods of forming flexible substrates for use in photovoltaic modules. The methods include shaping a metal foil and adhering the metal foil to a flexible backsheet. An optional interlayer dielectric and anti-tarnish material may then be applied to the upper surface of the shaped metal foil disposed on the flexible backsheet. The metal foil may be shaped using die cutting, roller cutting, or laser cutting techniques. The die cutting, roller cutting, and laser cutting techniques simplify the flexible substrate formation processes by eliminating resist-printing and etching steps previously used to pattern metal foils. Additionally, the die cutting, roller cutting, and laser cutting techniques reduce the consumption of consumable materials previously used in the patterning of metal foils.

Owner:APPLIED MATERIALS INC

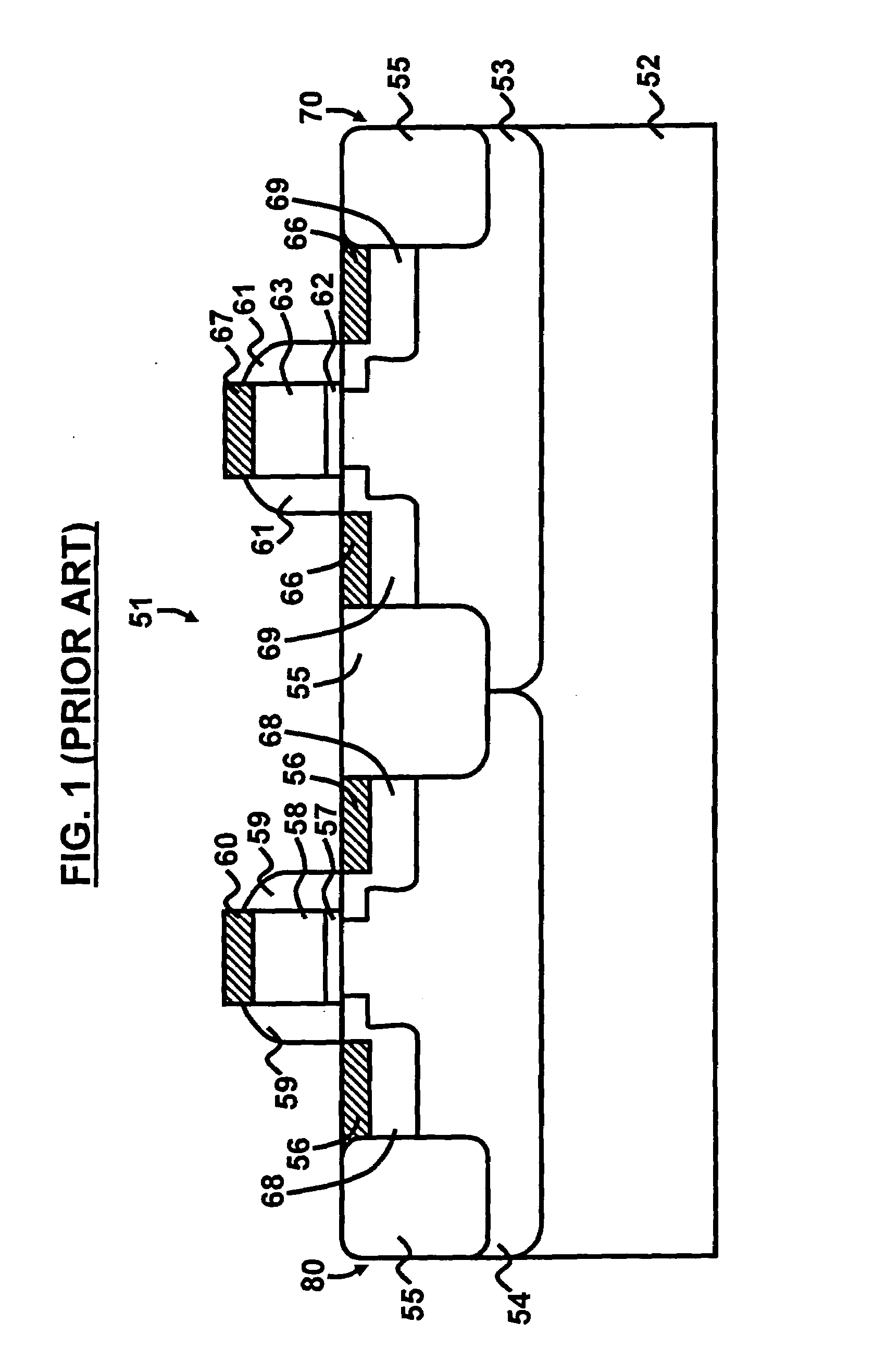

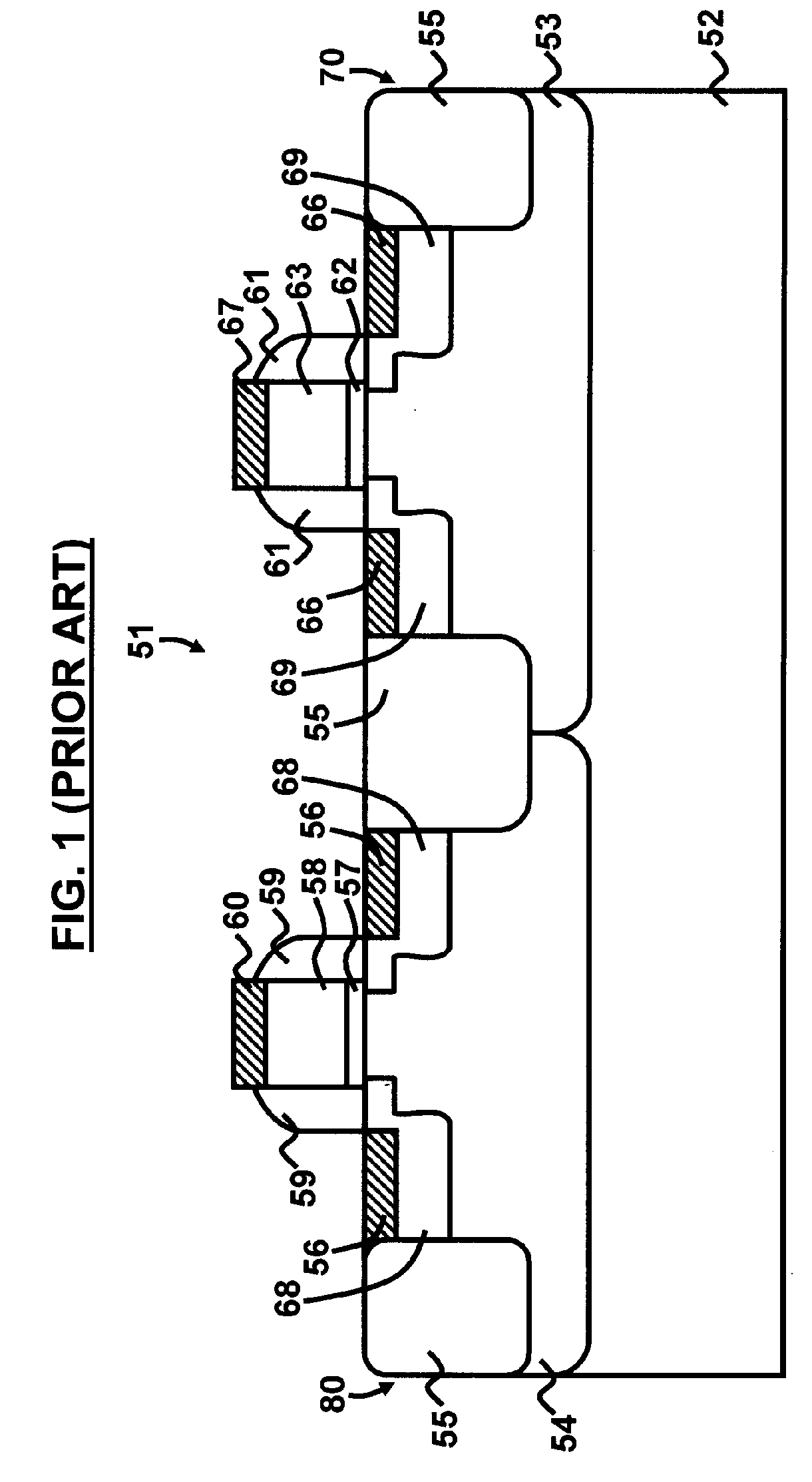

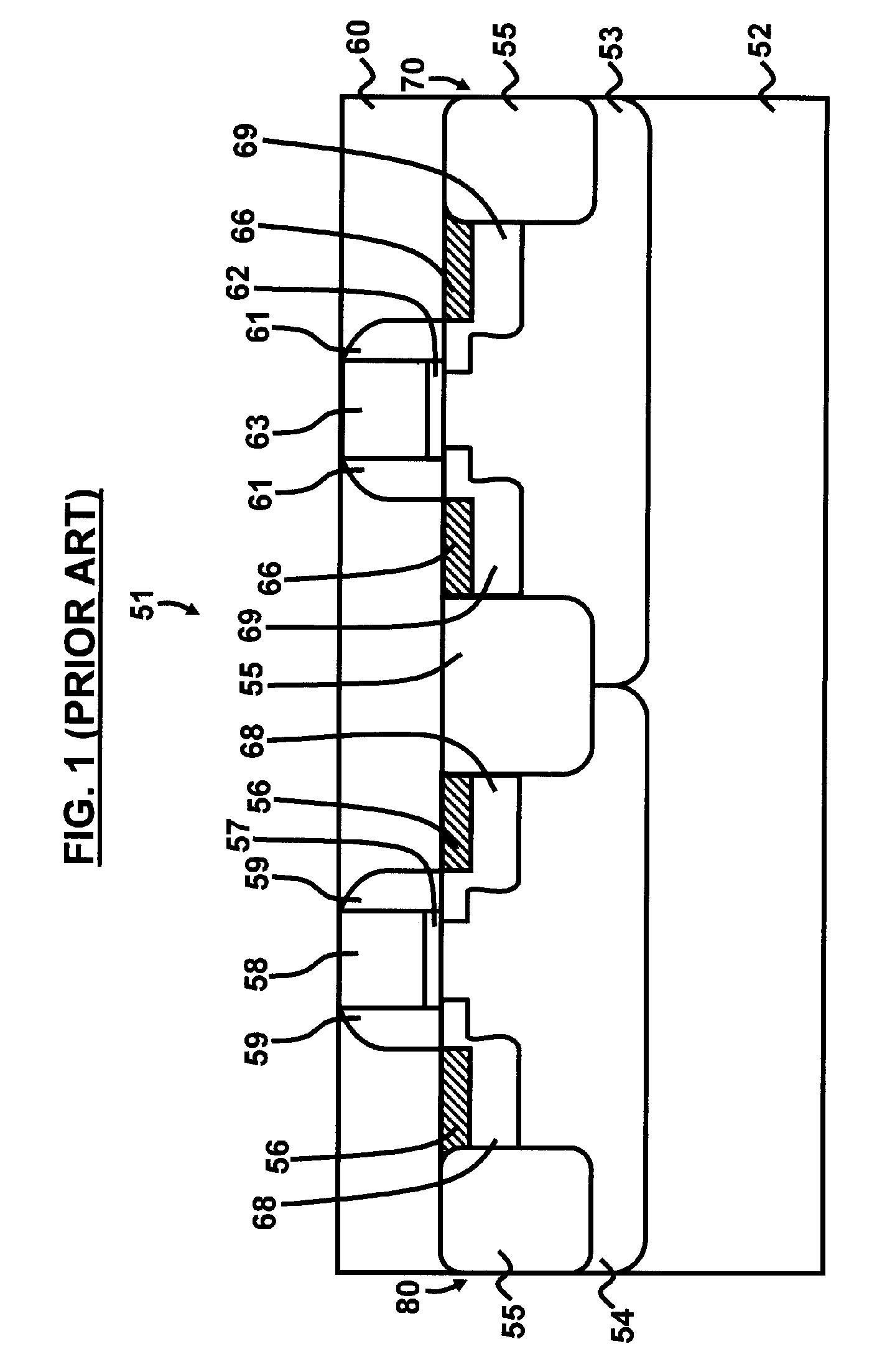

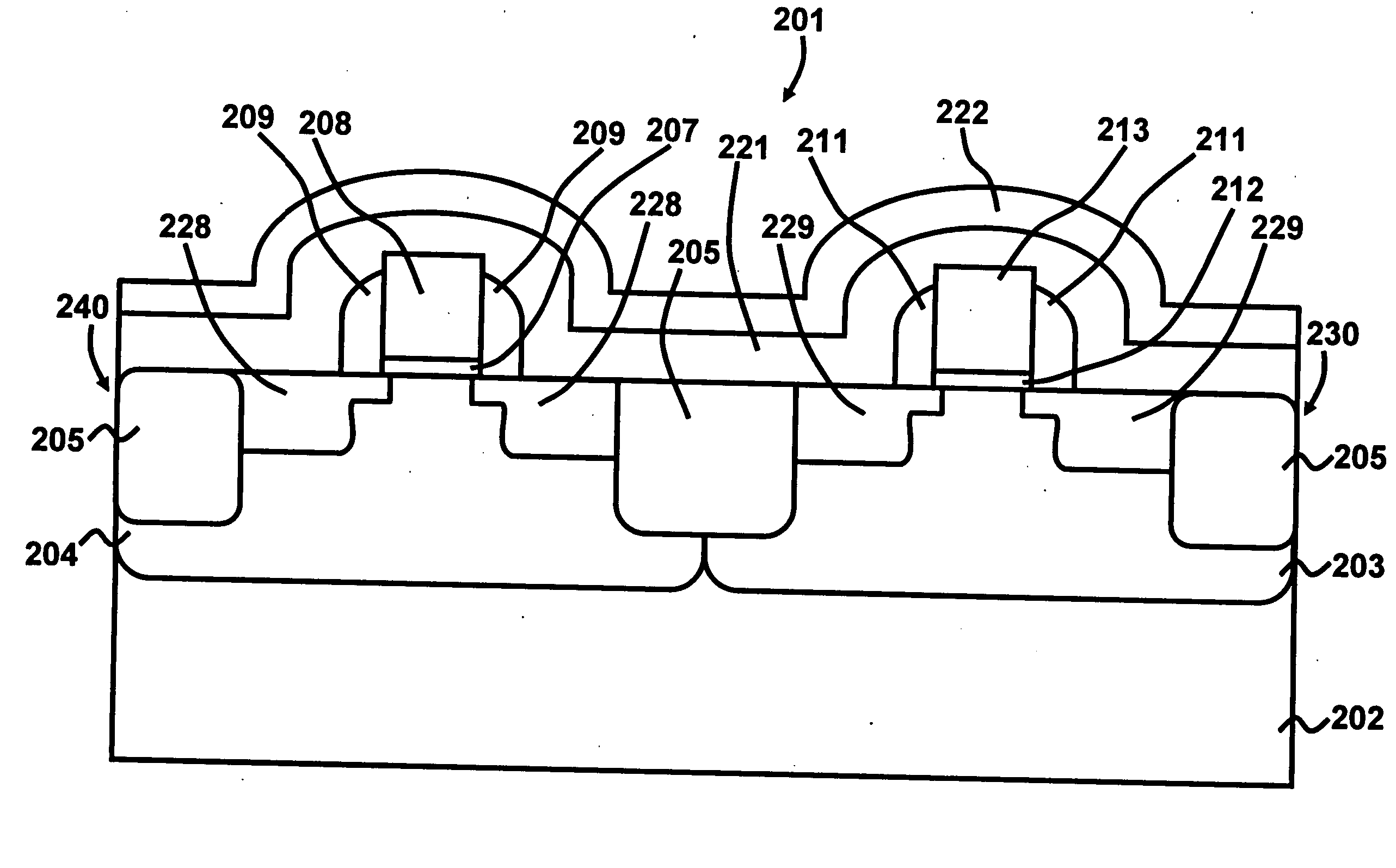

Method for forming self-aligned dual salicide in CMOS technologies

ActiveUS7067368B1Lower Level RequirementsThe formation process is simpleSemiconductor/solid-state device manufacturingCMOSSalicide

A method of fabricating a complementary metal oxide semiconductor (CMOS) device, wherein the method comprises forming a first well region in a semiconductor substrate for accommodation of a first type semiconductor device; forming a second well region in the semiconductor substrate for accommodation of a second type semiconductor device; shielding the first type semiconductor device with a mask; depositing a first metal layer over the second type semiconductor device; performing a first salicide formation on the second type semiconductor device; removing the mask; depositing a second metal layer over the first and second type semiconductor devices; and performing a second salicide formation on the first type semiconductor device. The method requires only one pattern level and it eliminates pattern overlay as it also simplifies the processes to form different silicide material over different devices.

Owner:AURIGA INNOVATIONS INC

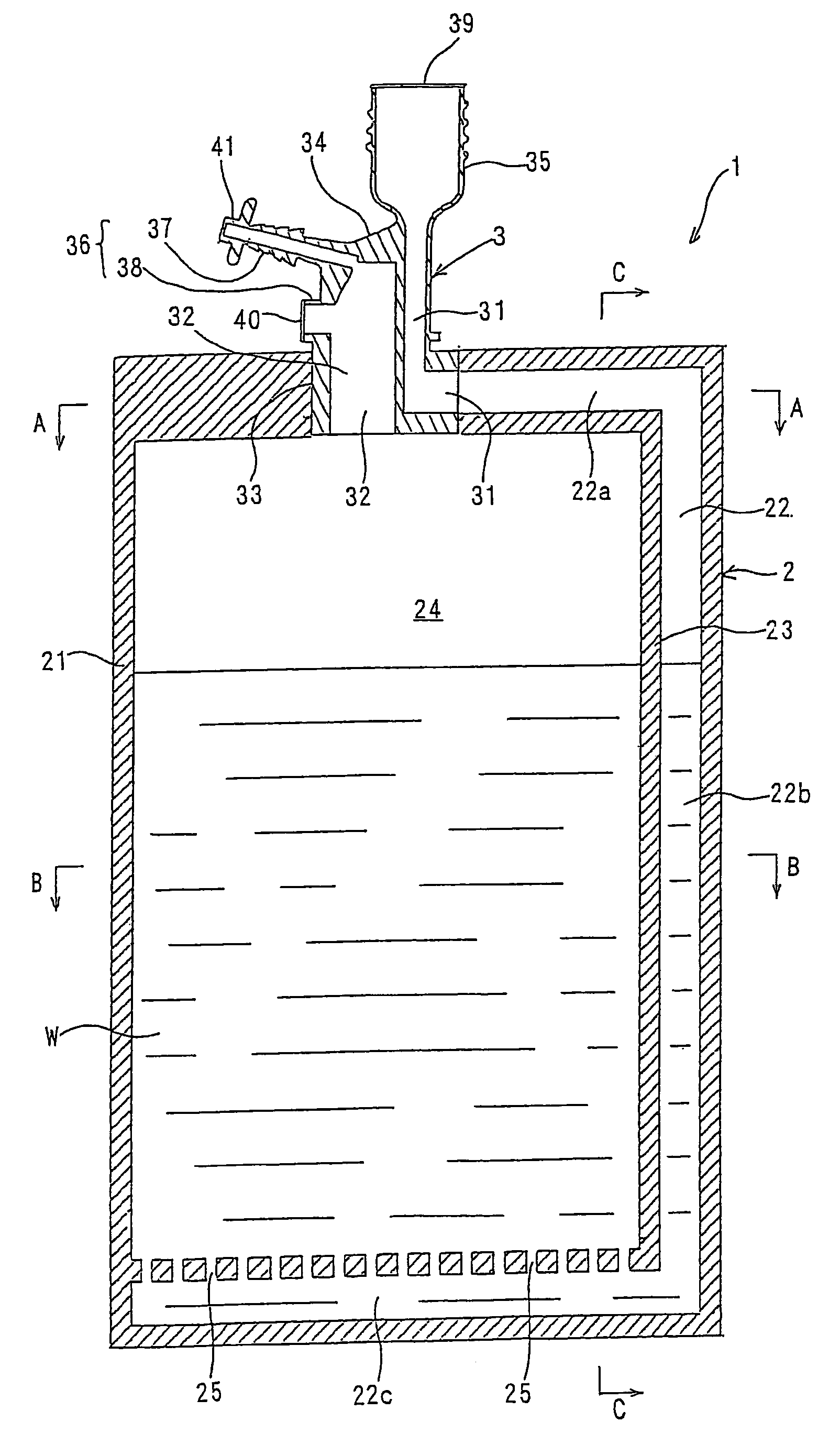

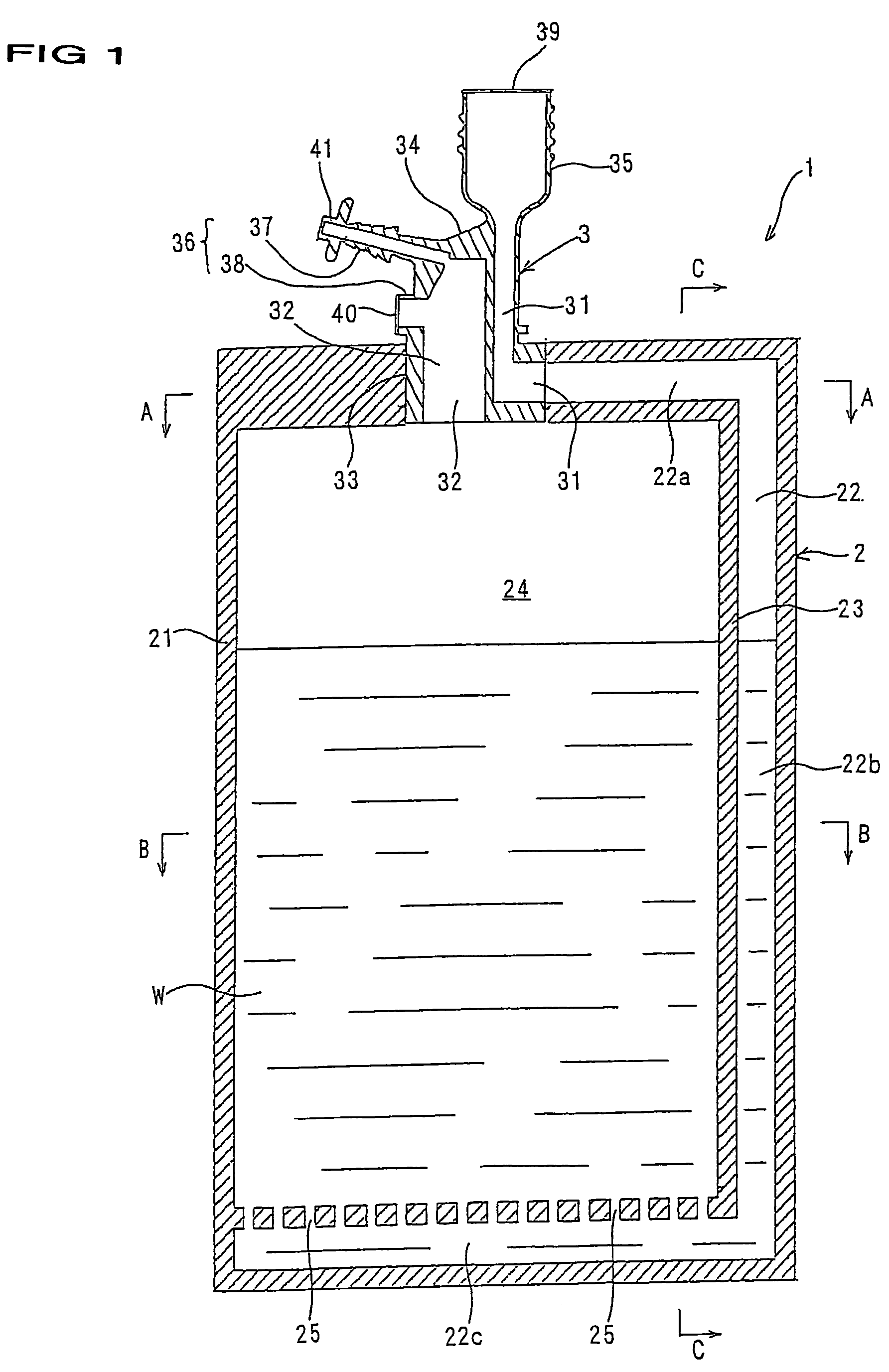

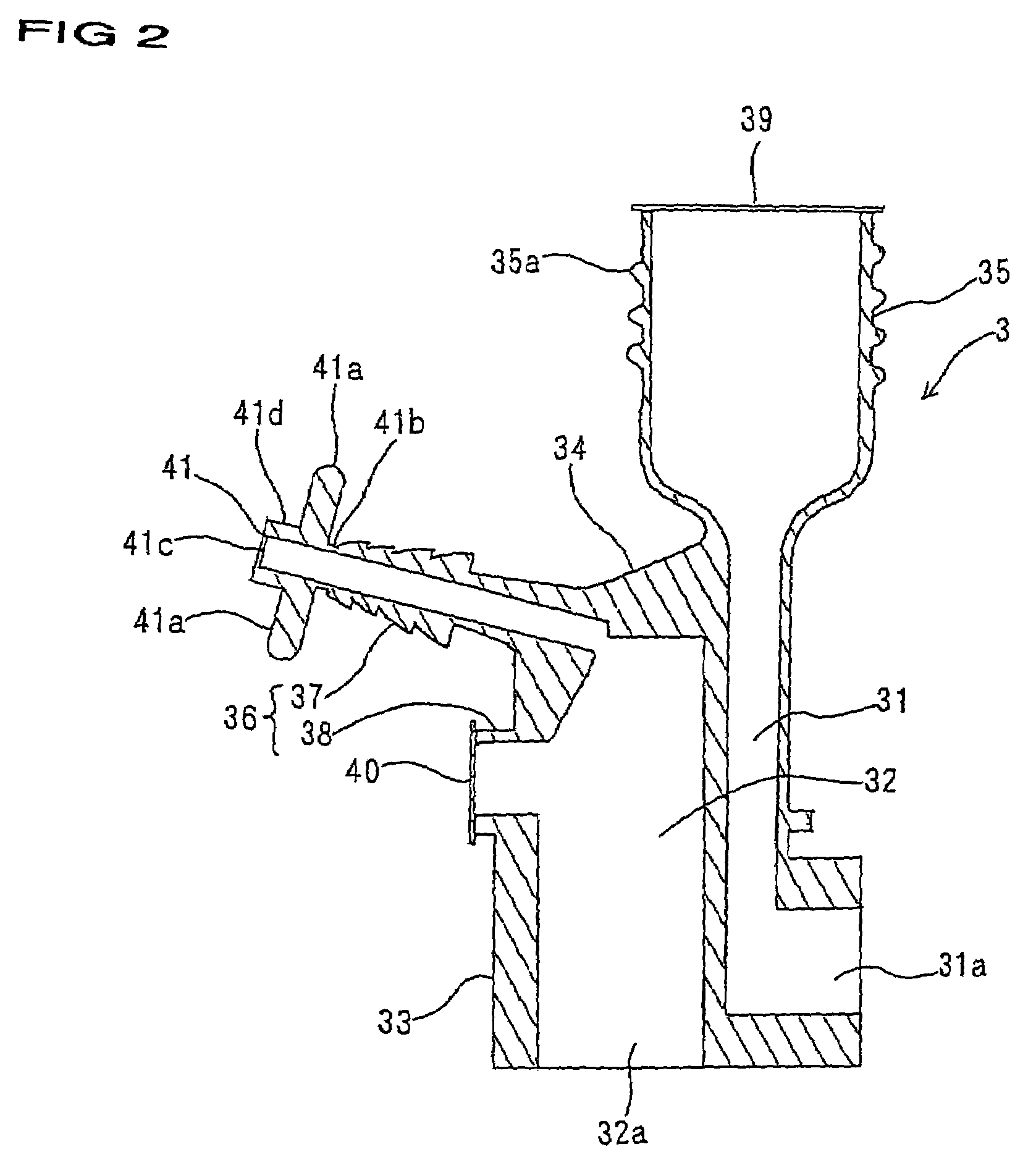

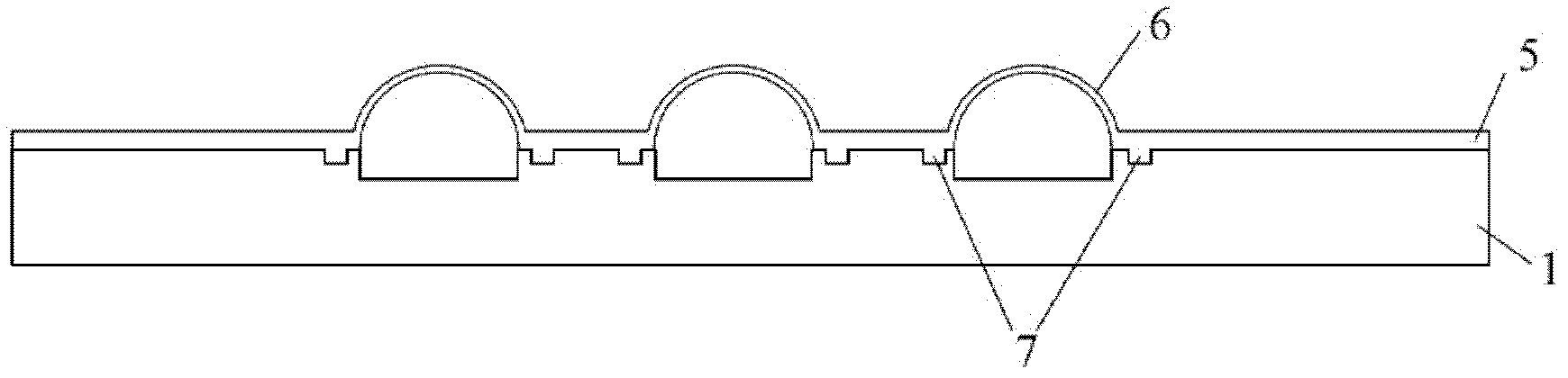

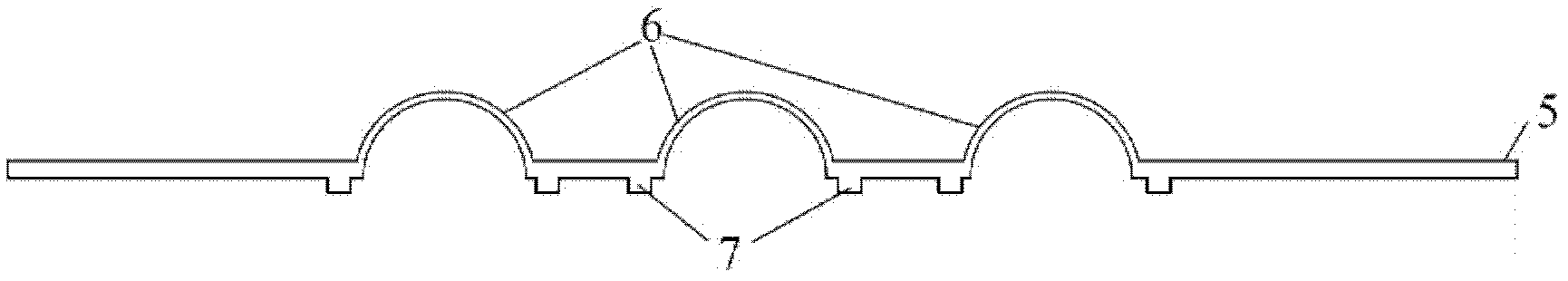

Liquid bag, liquid bag mouth member, and method of producing the same

An object of the present invention is to provide a liquid bag that makes bubbling possible with a simple structure without increasing the number of parts.The liquid bag according to the present invention includes: a bag main body for containing a liquid, the bag main body constructed of a flexible thermoplastic resin sheet; and a mouth member constructed of a thermoplastic resin, the mouth member sealingly bonded to a part of a periphery of the bag main body. The mouth member has a sleeve-like seal portion sealingly bonded to the bag main body, the seal portion including a first flow path and a second flow path. The first flow path opens and extends along the periphery of the bag main body and the second flow path opens at a bottom surface of the seal portion to an inside of the bag main body.

Owner:SENKO MED INSTR MFG CO LTD

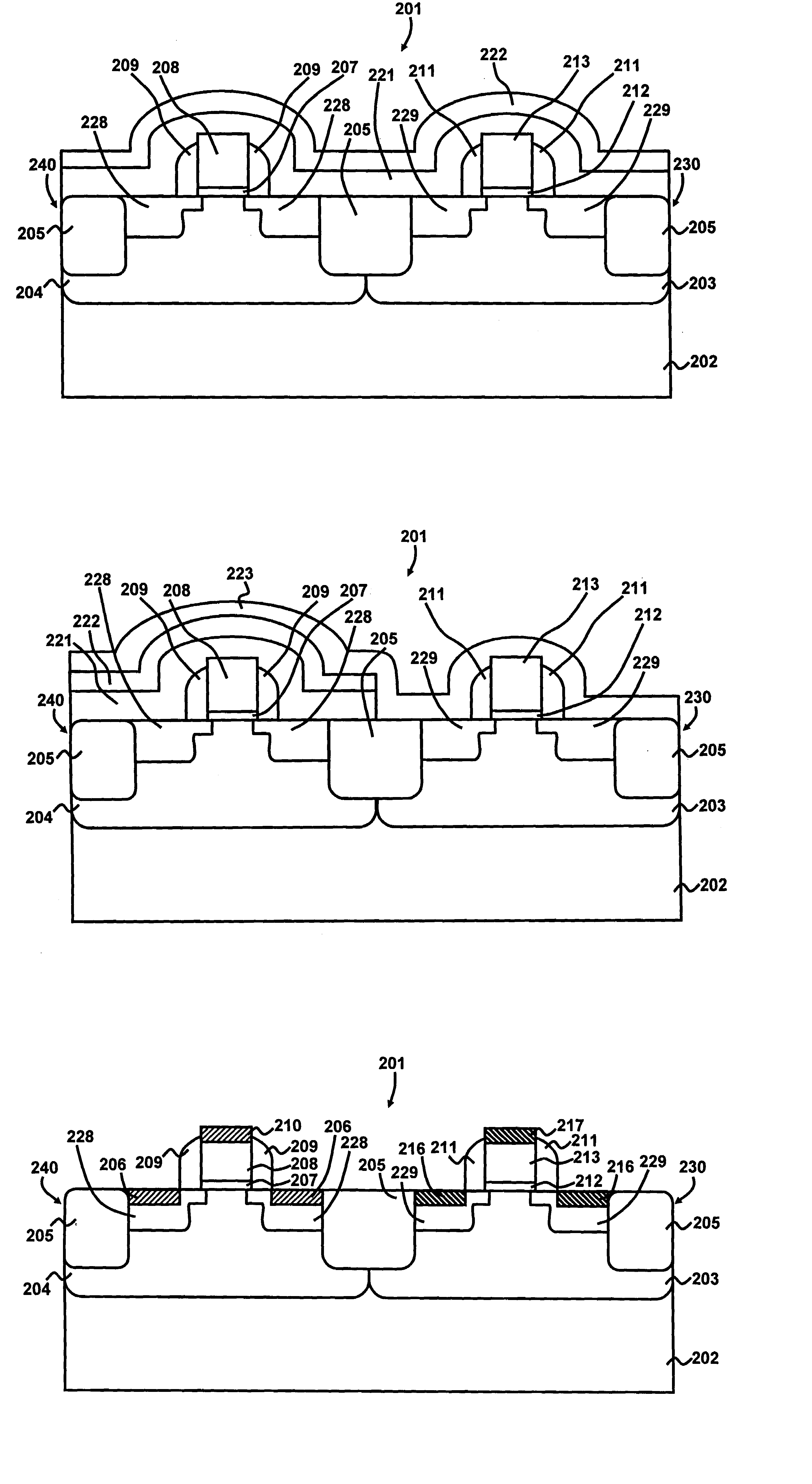

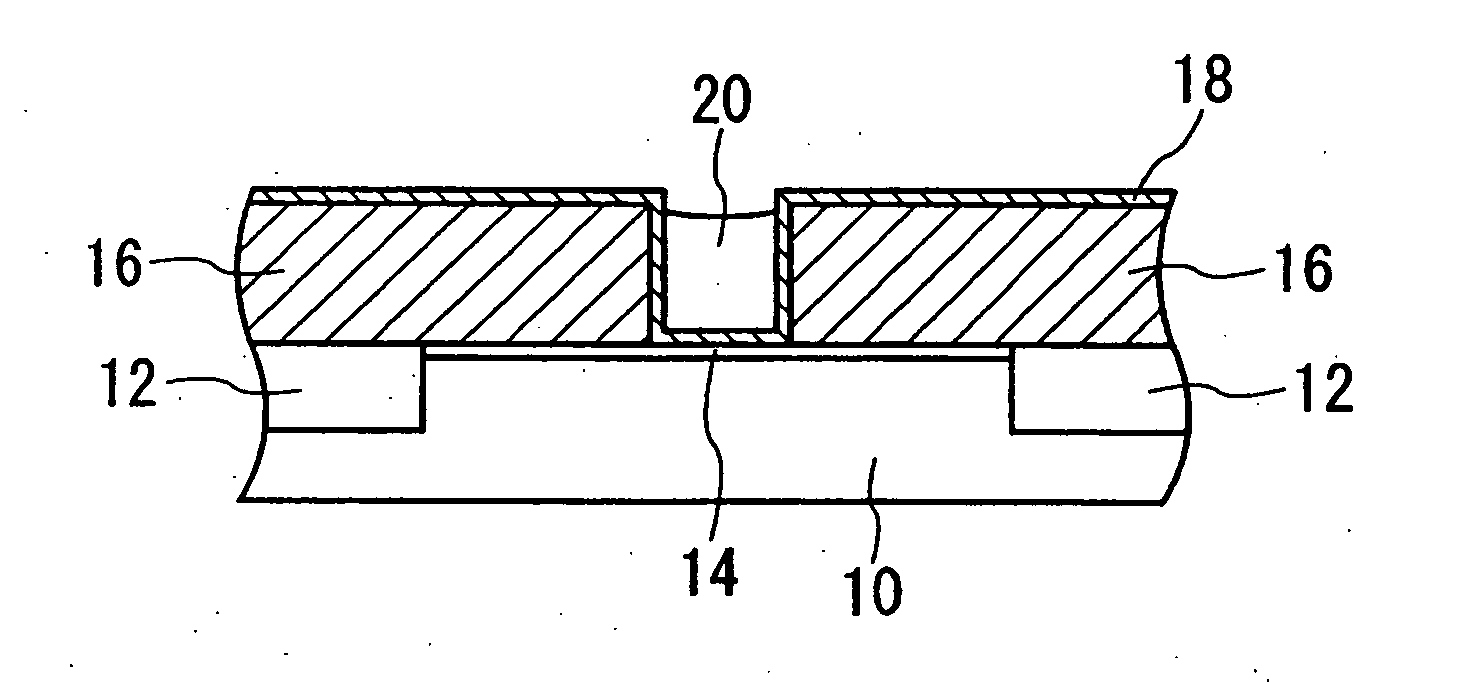

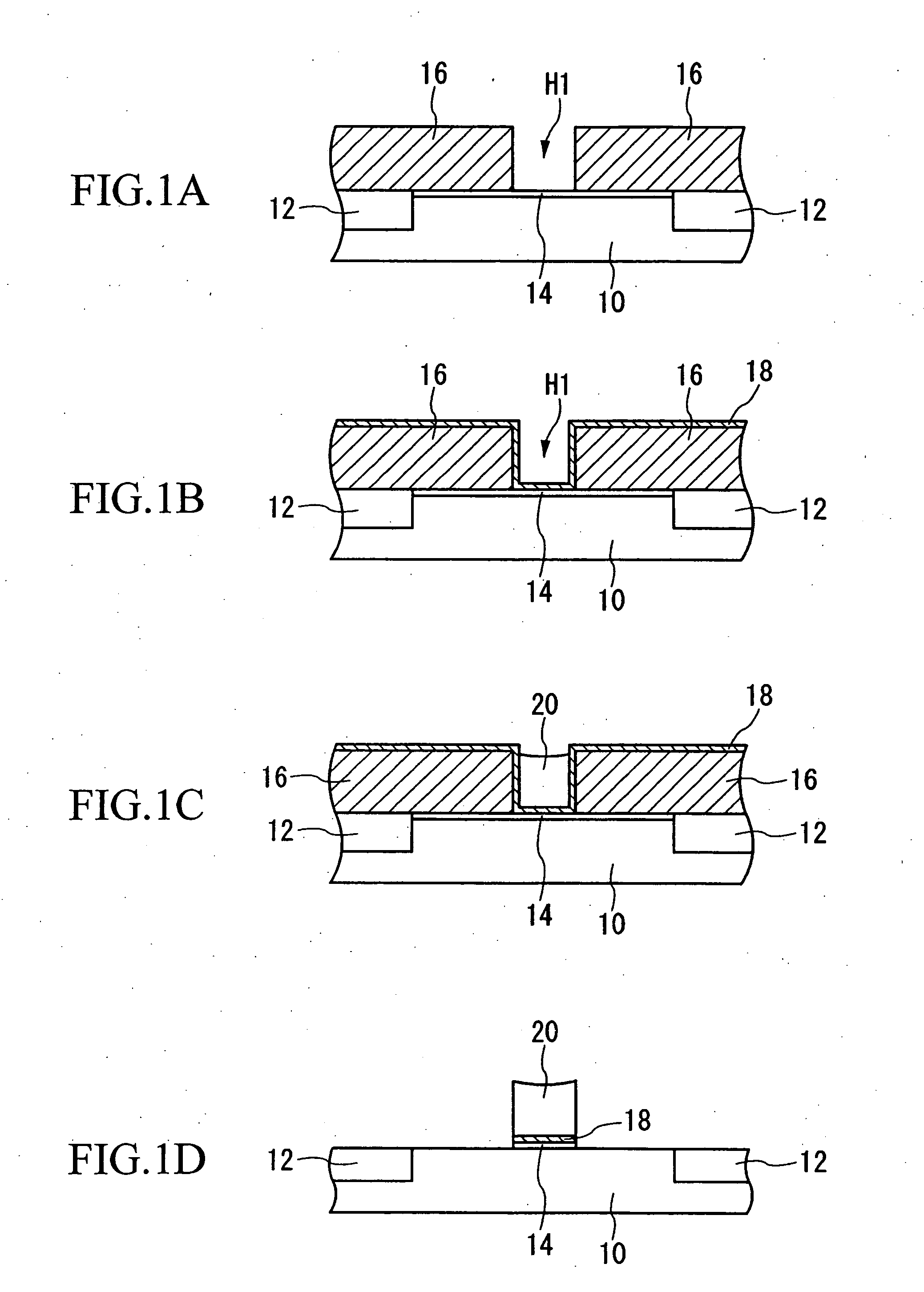

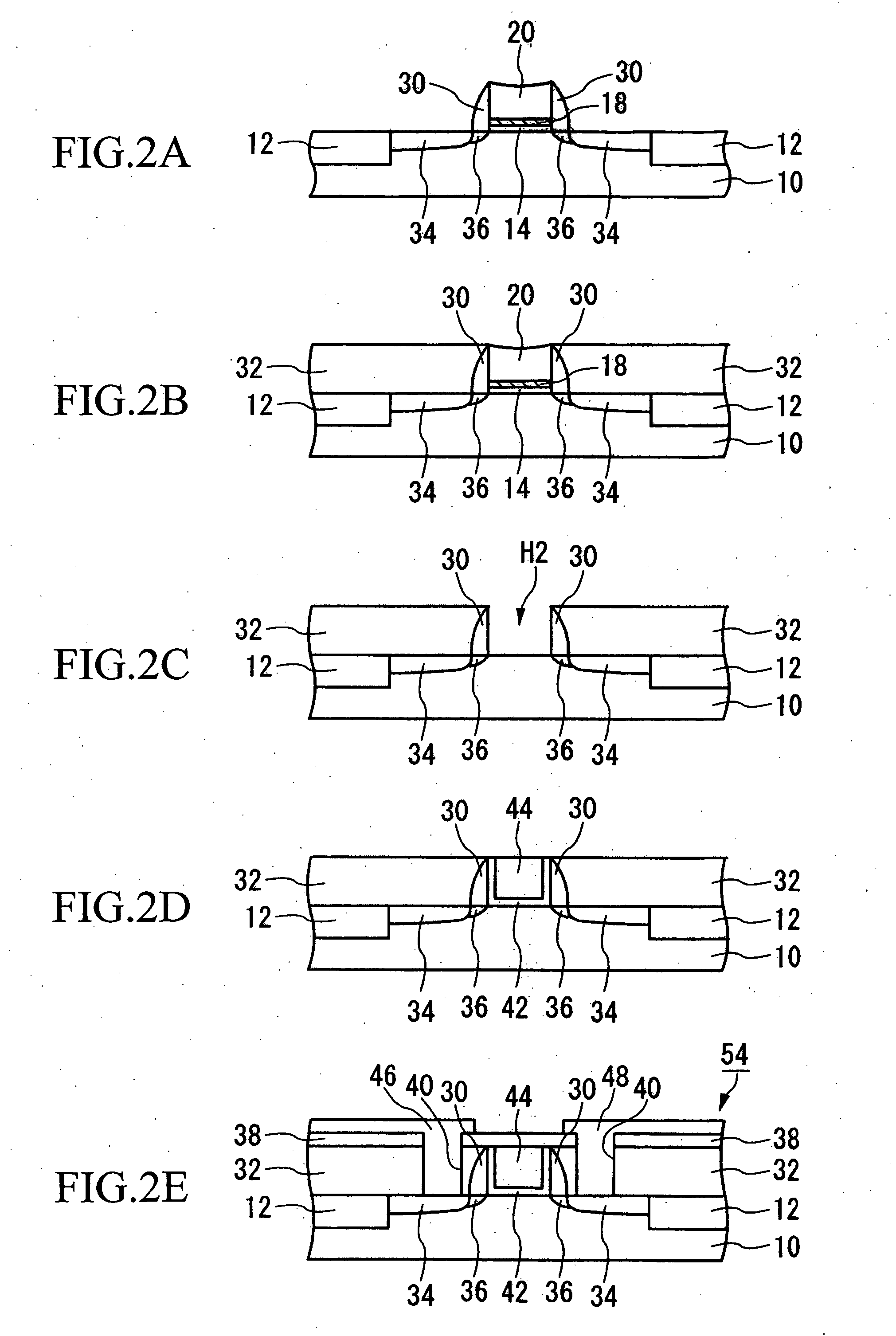

Damascene write poles produced via full film plating

InactiveUS20110042349A1Simplifies formation processImpact their effectivenessElectrical transducersDecorative surface effectsElectroplatingElectrical and Electronics engineering

A method for forming a write pole comprises forming a stop layer over a substrate layer of a wafer, the stop layer having an opening above a damascene trench in the substrate layer, and forming a buffer layer over the stop layer, the buffer layer having an opening above the opening of the stop layer. The method further comprises plating a layer of magnetic material over the wafer, disposing a first sacrificial material over a region of the magnetic material above the damascene trench, performing a milling or etching operation over the wafer to remove the magnetic material not covered by the first sacrificial material and to remove the first sacrificial material, disposing a second sacrificial material over the wafer, and performing a polishing operation over the wafer to remove the region of the magnetic material above the damascene trench, the second sacrificial material, and the buffer layer.

Owner:WESTERN DIGITAL TECH INC

Method for forming self-aligned dual salicide in CMOS technologies

ActiveUS20060121662A1Reduce required lithography levelSimplify dual salicide formation processSemiconductor/solid-state device manufacturingCMOSSalicide

A method of fabricating a complementary metal oxide semiconductor (CMOS) device, wherein the method comprises forming a first well region in a semiconductor substrate for accommodation of a first type semiconductor device; forming a second well region in the semiconductor substrate for accommodation of a second type semiconductor device; shielding the first type semiconductor device with a mask; depositing a first metal layer over the second type semiconductor device; performing a first salicide formation on the second type semiconductor device; removing the mask; depositing a second metal layer over the first and second type semiconductor devices; and performing a second salicide formation on the first type semiconductor device. The method requires only one pattern level and it eliminates pattern overlay as it also simplifies the processes to form different silicide material over different devices.

Owner:AURIGA INNOVATIONS INC

Method for forming self-aligned dual fully silicided gates in CMOS devices

InactiveUS20060121663A1Reduce required lithography levelSimplify dual salicide formation processSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSLithographic artist

A method of forming a dual self-aligned fully silicided gate in a CMOS device requiring only one lithography level, wherein the method comprises forming a first type semiconductor device having a first well region in a semiconductor substrate, first source / drain silicide areas in the first well region, and a first type gate isolated from the first source / drain silicide areas; forming a second type semiconductor device having a second well region in the semiconductor substrate, second source / drain silicide areas in the second well region, and a second type gate isolated from the second source / drain silicide areas; selectively forming a first metal layer over the second type semiconductor device; performing a first fully silicided (FUSI) gate formation on only the second type gate; depositing a second metal layer over the first and second type semiconductor devices; and performing a second FUSI gate formation on only the first type gate.

Owner:IBM CORP

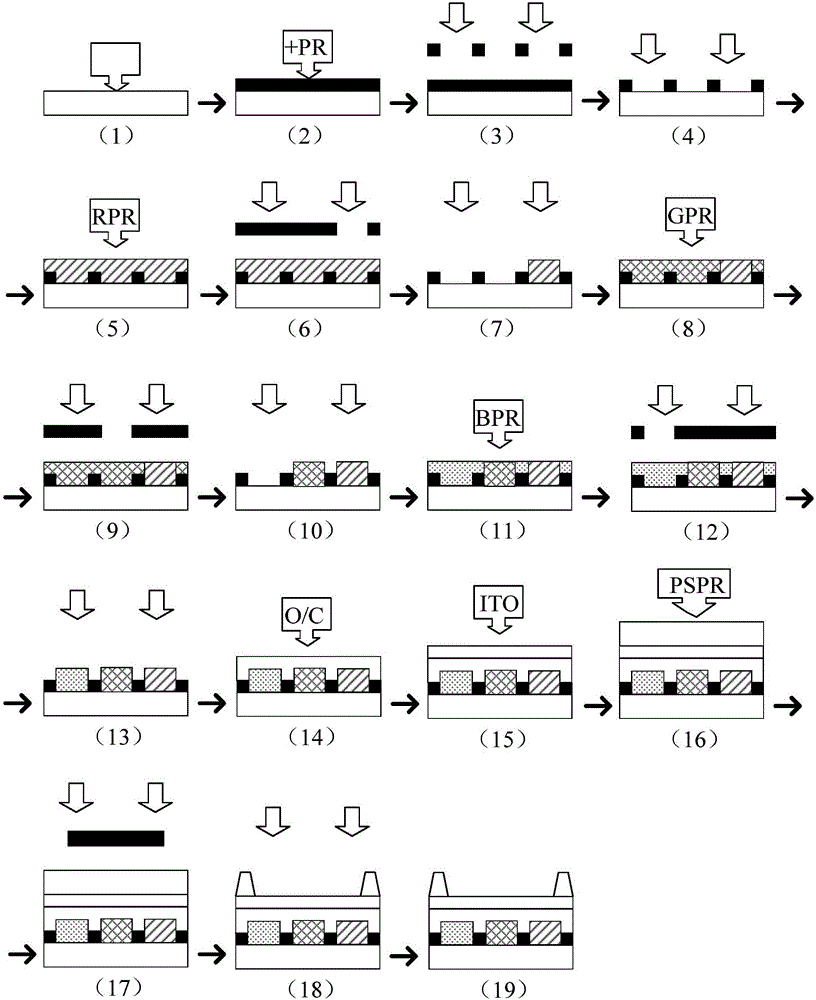

Color film substrate, manufacturing method of color film substrate, mask, manufacturing method of mask and display device

InactiveCN105974653ASolve the complicated productionThe formation process is simpleOriginals for photomechanical treatmentNon-linear opticsColor filmDisplay device

The invention discloses a color film substrate, a manufacturing method of the color film substrate, a mask, a manufacturing method of the mask and a display device, and belongs to the technical field of displaying. The manufacturing method of the color film substrate includes the steps that a photochromic resin layer is formed on a substrate body through photochromic resin materials, wherein the photochromic resin materials contain various photosensitive groups with different absorption wavelengths; the photosensitive resin layer is processed with the patterning technology, and a color light filtering layer is obtained, wherein the color light filtering layer comprises various light filtering units, and black matrixes are arranged between the adjacent light filtering units in the color light filtering layer. By means of the manufacturing method of the color film substrate, the problem that as the forming process of the color light filtering layer is complex, the manufacturing process of the color film substrate is complex is solved, and the effects that the forming process of the color light filtering layer is simplified, and then the manufacturing process of the color film substrate is simplified are achieved. The manufacturing method is used for manufacturing the color film substrate.

Owner:BOE TECH GRP CO LTD +1

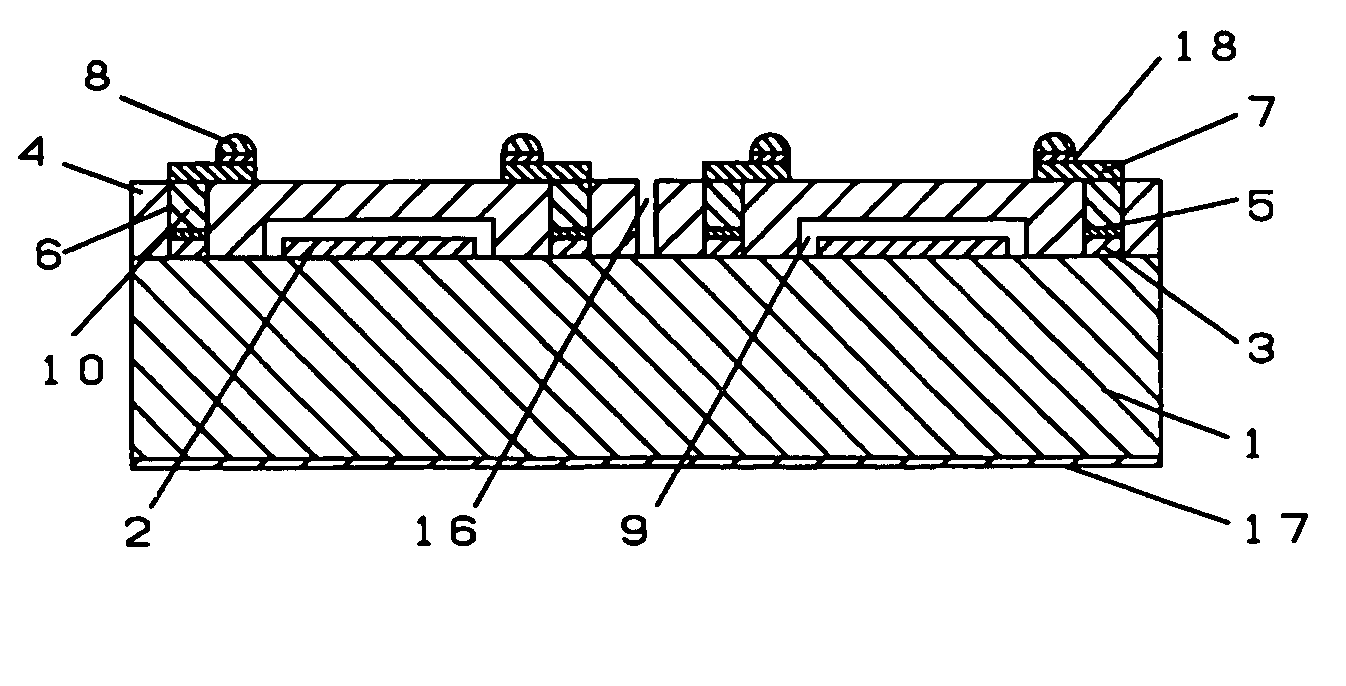

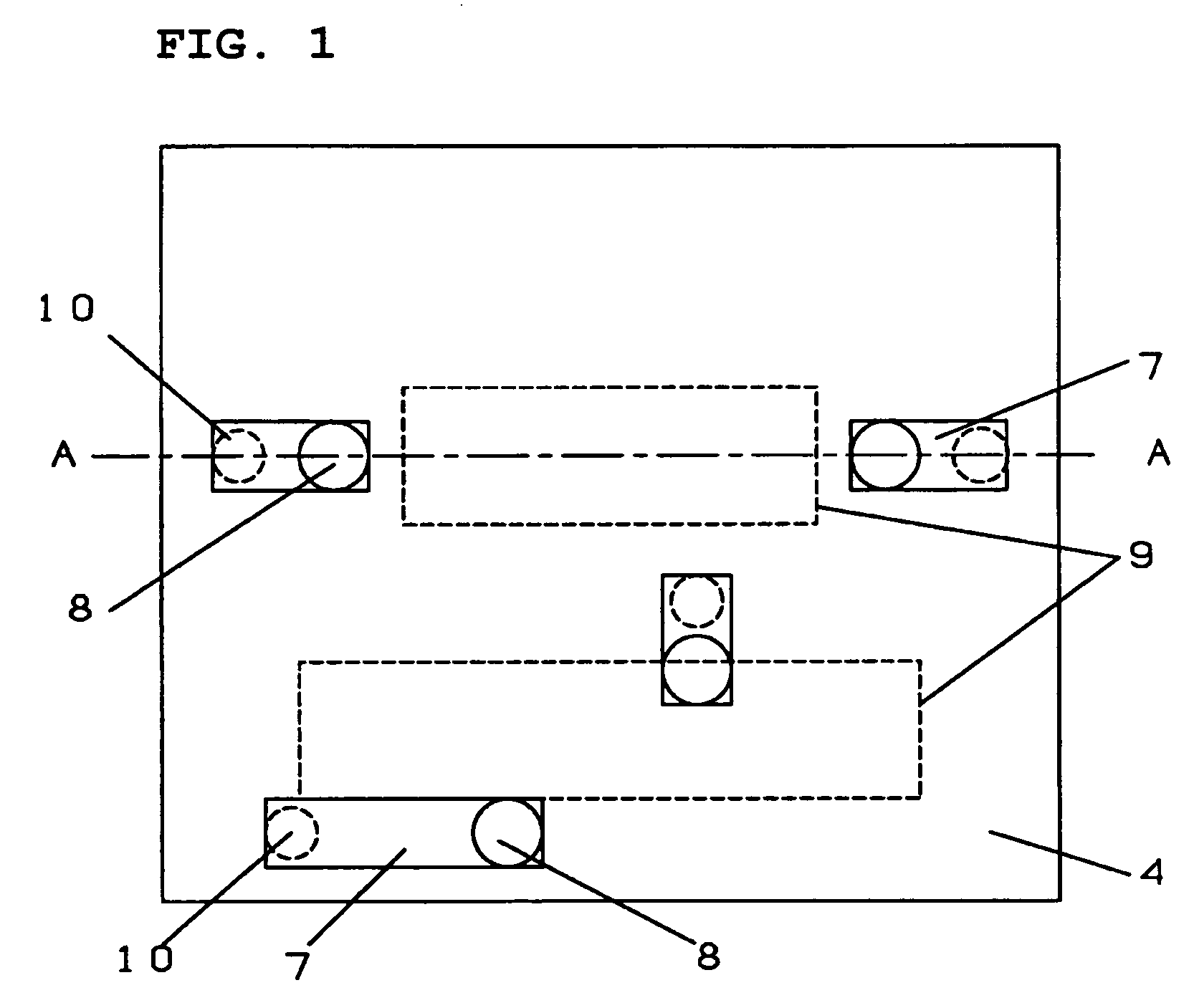

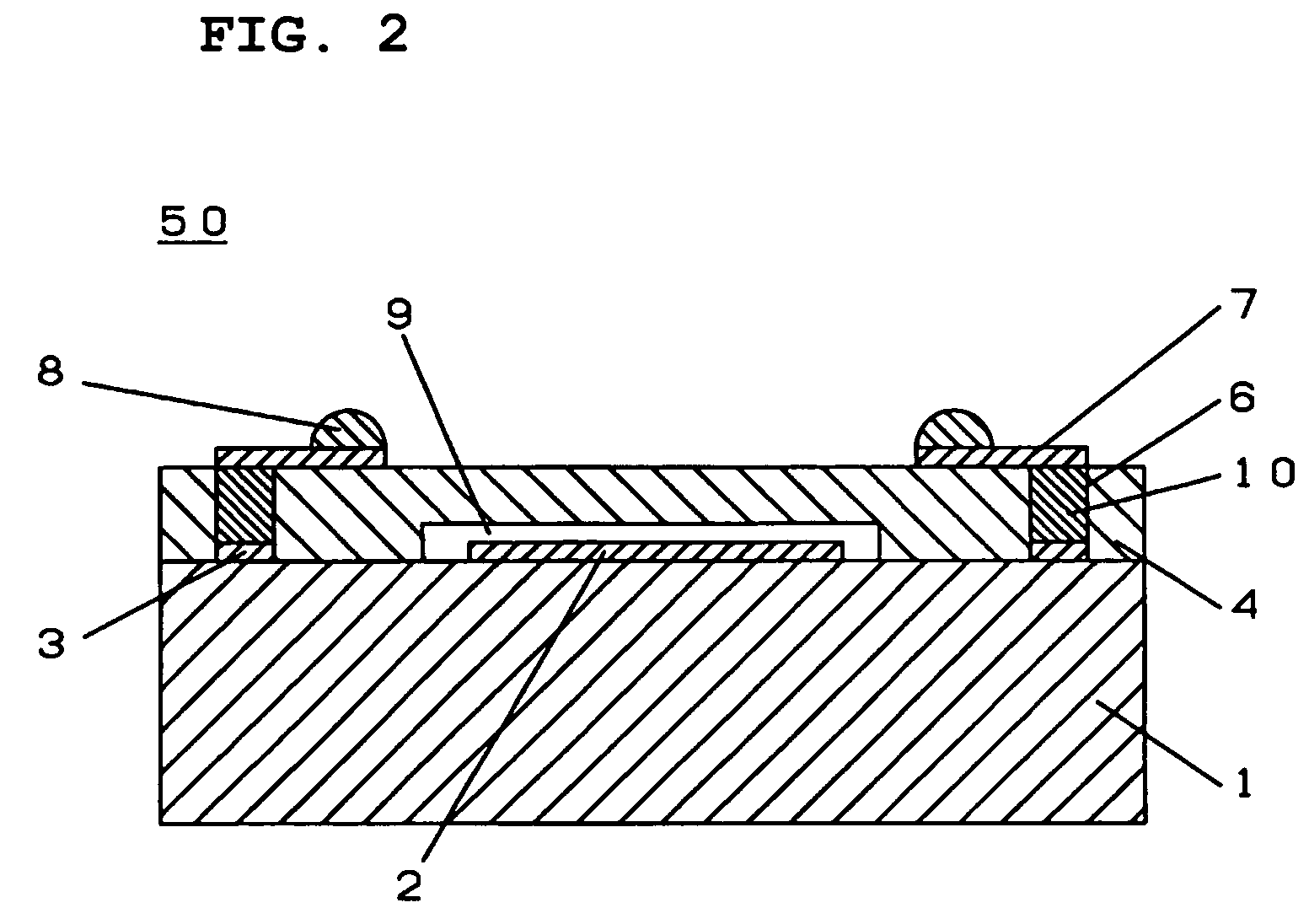

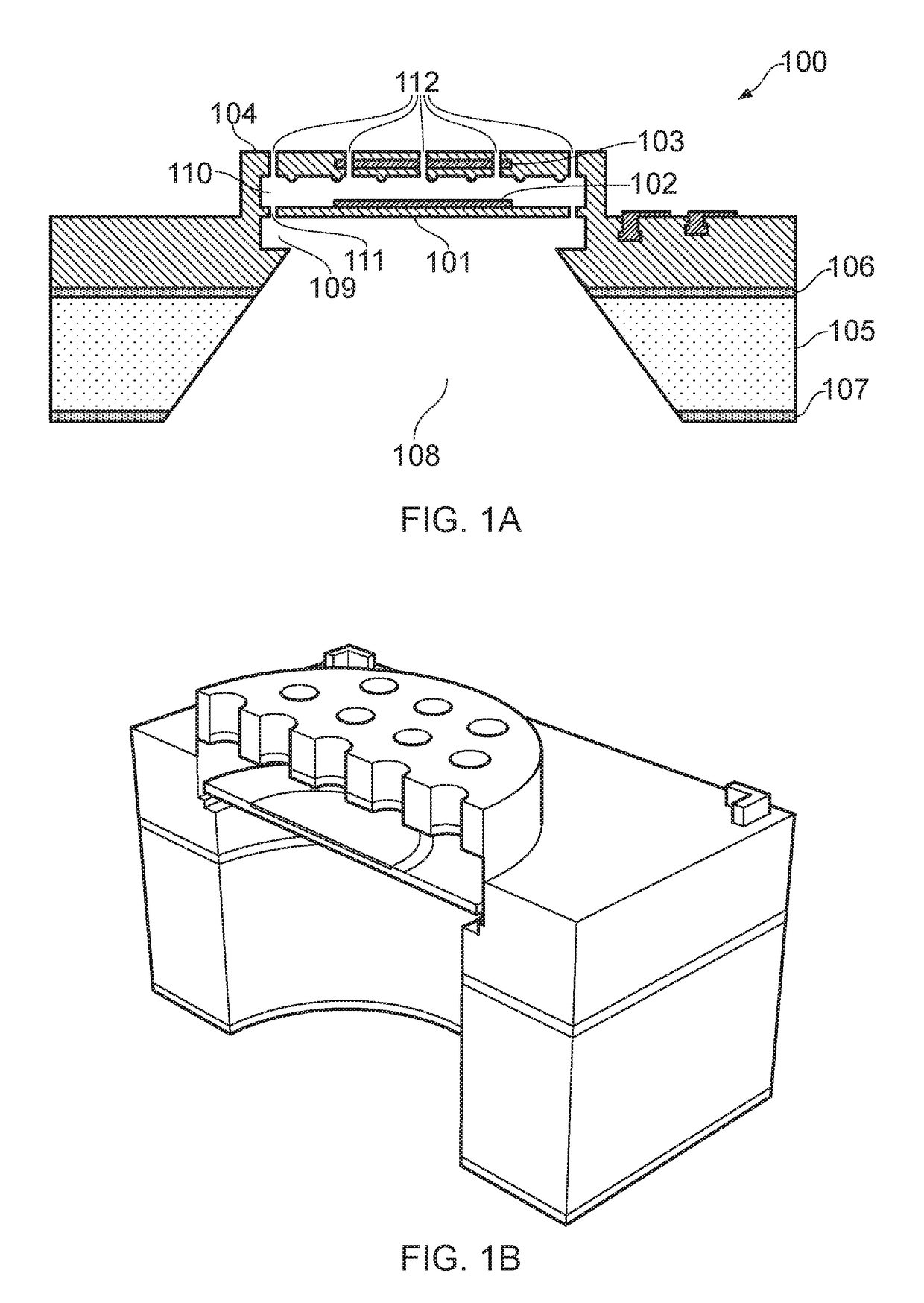

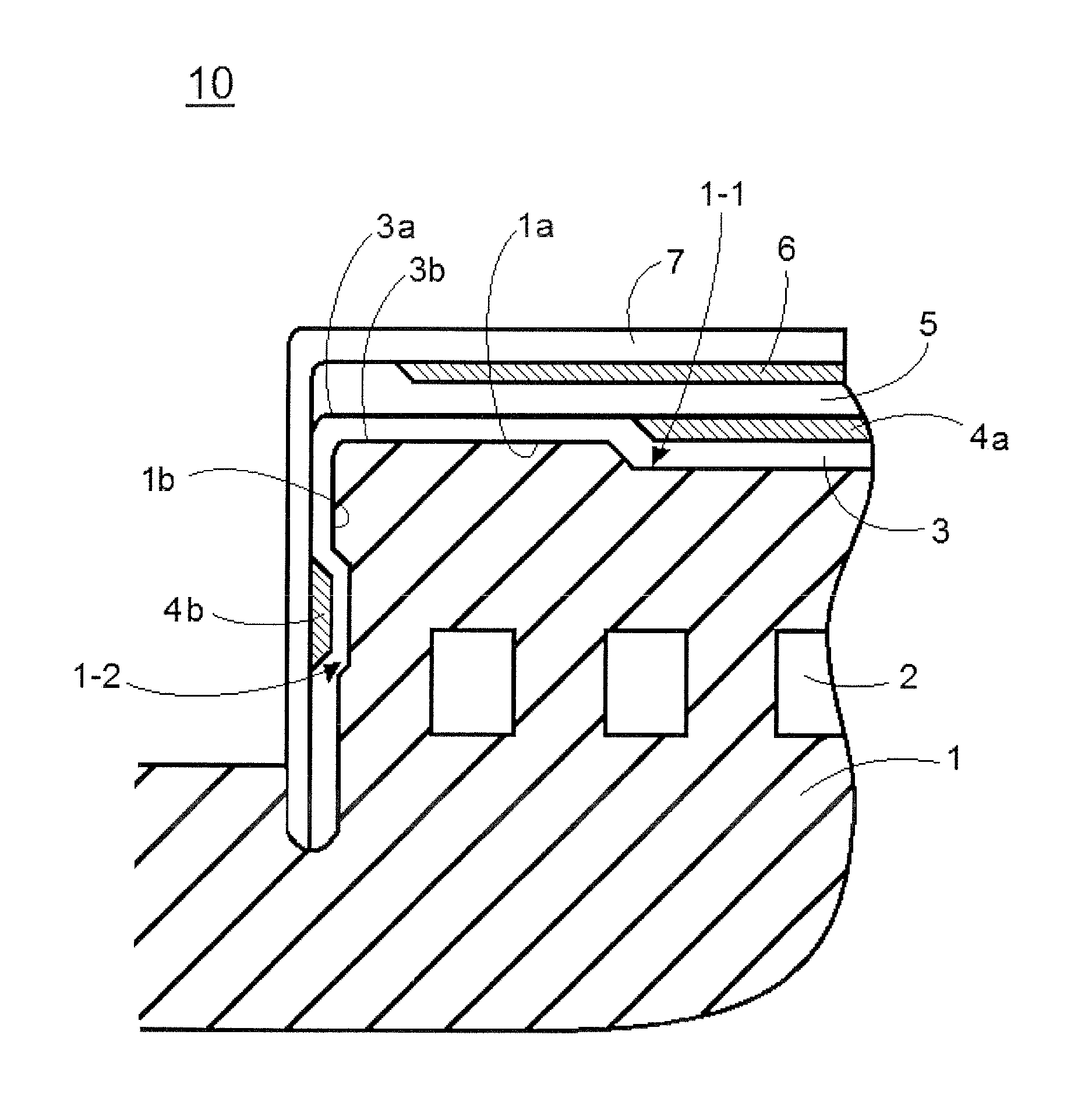

Electronic component and method of producing the same

ActiveUS7205705B2Reduced size and heightReduce chip sizeImpedence networksPiezoelectric/electrostriction/magnetostriction machinesEngineeringElectronic component

An electronic component includes at least one piezoelectric vibrating portion, a connecting portion provided on a substrate, a structural piece including a concavity so as not to disturb the vibration of the piezoelectric vibrating portion, and a connecting wiring for electrically connecting a pad on the substrate to a mounting wiring disposed on the upper surface of the structural piece. The structural piece further includes a through hole having an electroconductive material filled therein. The structural piece seals the piezoelectric vibrating portion.

Owner:MURATA MFG CO LTD

High-bonding-strength environment-friendly supermolecular physical gel adhesive and preparation method thereof

ActiveCN108841346AEasy to useHigh bonding strengthNon-macromolecular adhesive additivesAcid polymer adhesivesEnvironmental resistanceWater based

The invention relates to a high-bonding-strength environment-friendly supermolecular physical gel adhesive and a preparation method thereof, and belongs to the technical field of preparation of a water-based adhesive. The preparation method comprises the following steps: dissolving nanoparticles into water, stirring until the nanoparticles dissolve completely, adding one or two monomers and stirring until the monomers dissolve completely; adding an initiator into deionized water, performing ultrasonic treatment until the initiator dissolves completely, and adding an initiator solution into a prepolymerization solution containing the nanoparticles and the monomers; adding a catalyst, stirring and allowing standing still at room temperature to obtain the gel adhesive. The gel adhesive is formed on the basis of multiple weak interaction hydrogen bonds among polymers, chain entanglement as well as the physical adsorption effect between the nanoparticles and the polymers; the forming process is simple and efficient; organic solvent do not need to be added in the preparation process; the adhesive does not have peculiar smell and is non-toxic and environmentally friendly; the use raw materials are the common chemical raw materials and are low in price. The adhesive is applied to adhesion of various materials such as optical glass, metal, wood and plastic, and has high bonding strength.

Owner:JILIN UNIV

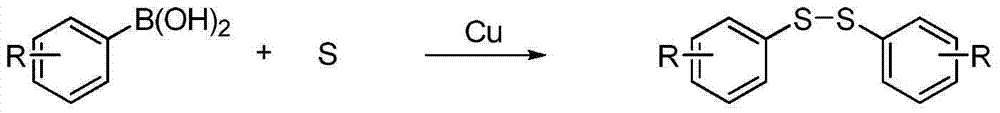

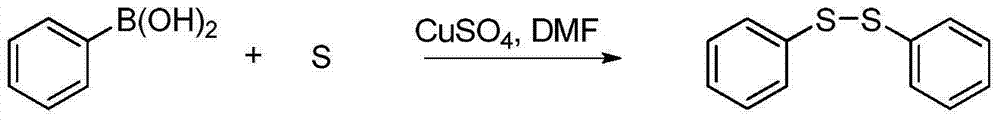

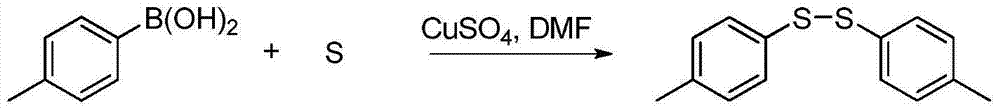

Synthetic method for symmetrical diaryl disulfide

ActiveCN103497128AProduct separation is simpleSimplify the formation processHydropoly/poly sulfide preparationOrganic chemicalsCopper salt

The invention provides a synthetic method for symmetrical diaryl disulfide, which relates to the fields of organic chemical industry and fine chemical engineering. The method uses arylboronic acid and elemental sulfur powder as raw materials and a metallic copper salt as a catalyst; a reaction is carried out under the conditions of heating and stirring, and reaction time is 5 to 8 h; a mol ratio of arylboronic acid to elemental sulfur is 1: 1.5, the usage amount of the Cu catalyst is 5% of the mol fraction of the arylboronic acid, and an excellent effect is obtained when the raw materials react with the catalyst at a temperature of 50 to 80 DEG C for 5 to 8 h under stirring and heating. According to the invention, the inorganic substance, elemental sulfur, is used as a sulfur source, elemental sulfur and safe low-toxicity arylboronic acid undergo a coupling reaction to directly introduce an inorganic non-metallic element into an organic molecule, so greenness of synthetic route is realized; the reaction is easy to operate, the usage amount of the catalyst is small, the synthetic method is superior to other synthetic methods in the prior art, synthesized symmetrical diaryl disulfide is easy to separate, and good environmental protection performance is obtained.

Owner:铜陵汇泽科技信息咨询有限公司

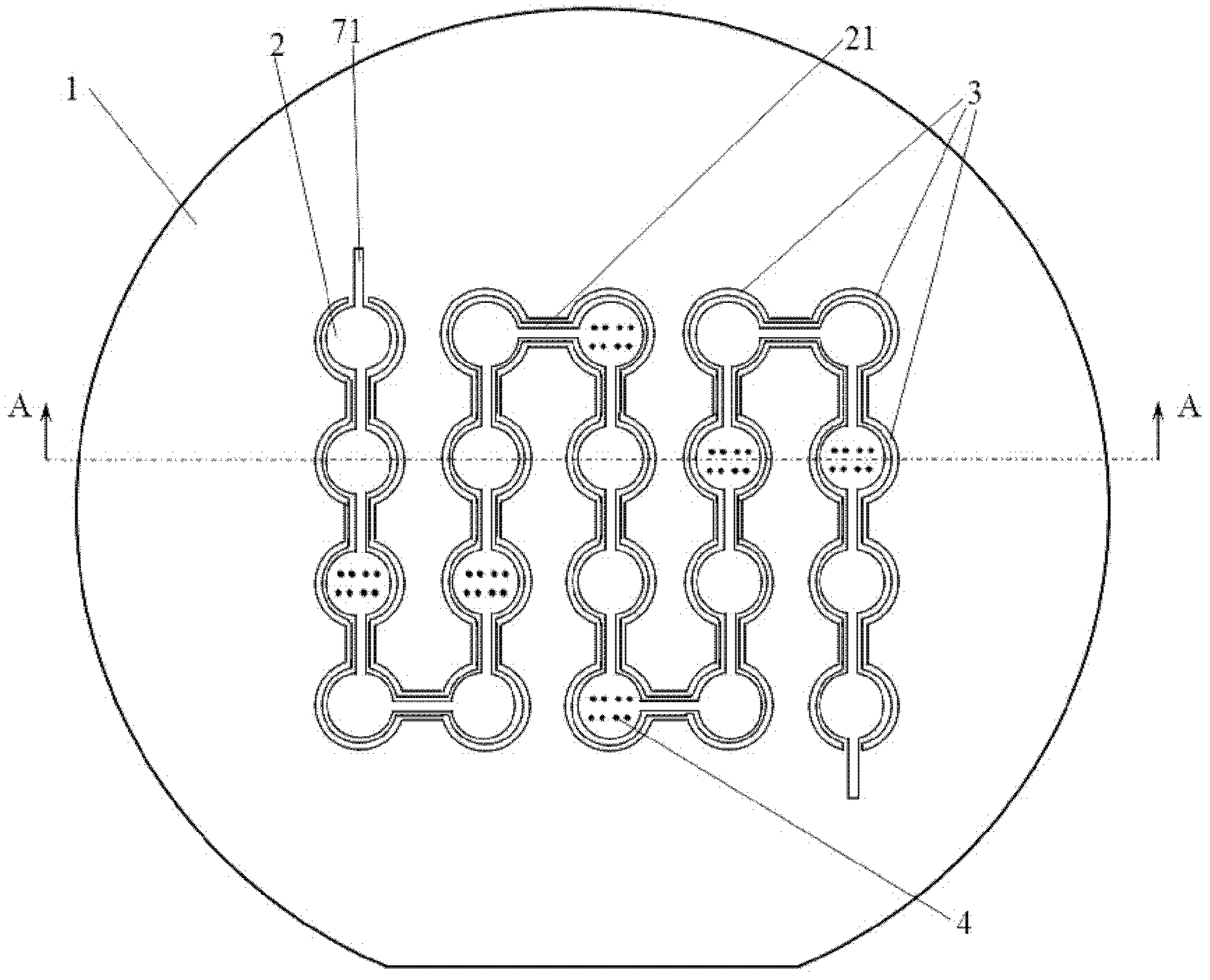

Wafer level packaging method of light emitting diode with adjustable lens focus

InactiveCN102569563AQuick GlueImprove light outputDecorative surface effectsChemical vapor deposition coatingLight-emitting diodeMaterials science

The invention discloses a wafer level packaging method of a light emitting diode with an adjustable lens focus. The method comprises the following steps: in a first step, etching a light emitting diode lens mould microchannel array and a spacing control mould microchannel array surrounding a light emitting diode lens mould groove on a silicon wafer, and disposing proper amount of thermal outgassing agents in a light emitting diode lens mould microchannel; in a second step, carrying out anode bonding of the silicon wafer and a borosilicate glass water in vacuum to form a sealed cavity; in a third step, carrying out heating and heat preservation on a bonding wafer in the air, forming a spherical glass micro-cavity and a spacing control projection ring, carrying out cooling and annealing, and removing silicon to obtain a light emitting diode packaging lens array; in a fourth step, pasting a light emitting diode chip on a substrate; in a fifth step, bonding a wafer level glass micro-cavity and the substrate; in a sixth step, filling up glue into a gap between a light emitting diode chip and the wafer level glass micro-cavity through a spacing control ring gap, and carrying out solidification. The method can be carried out on a wafer level, and the method has the advantages of simplicity and low cost.

Owner:吕思远

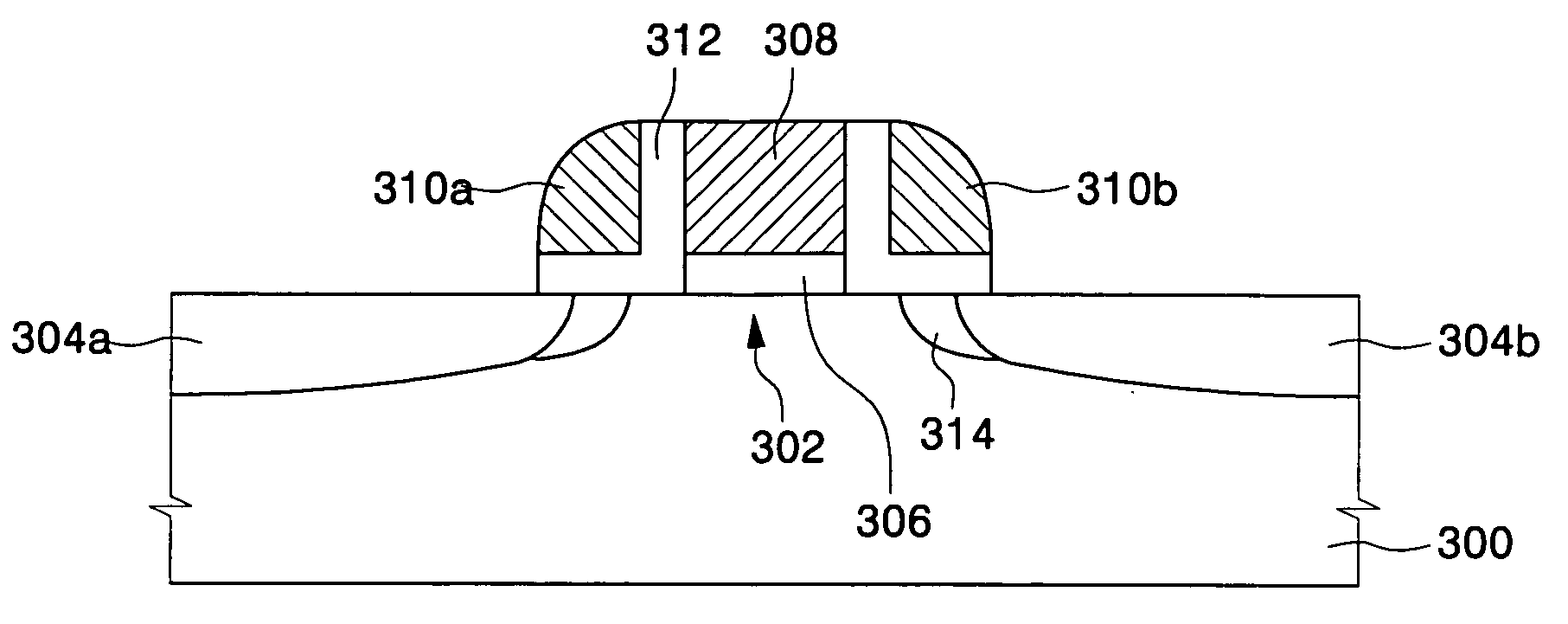

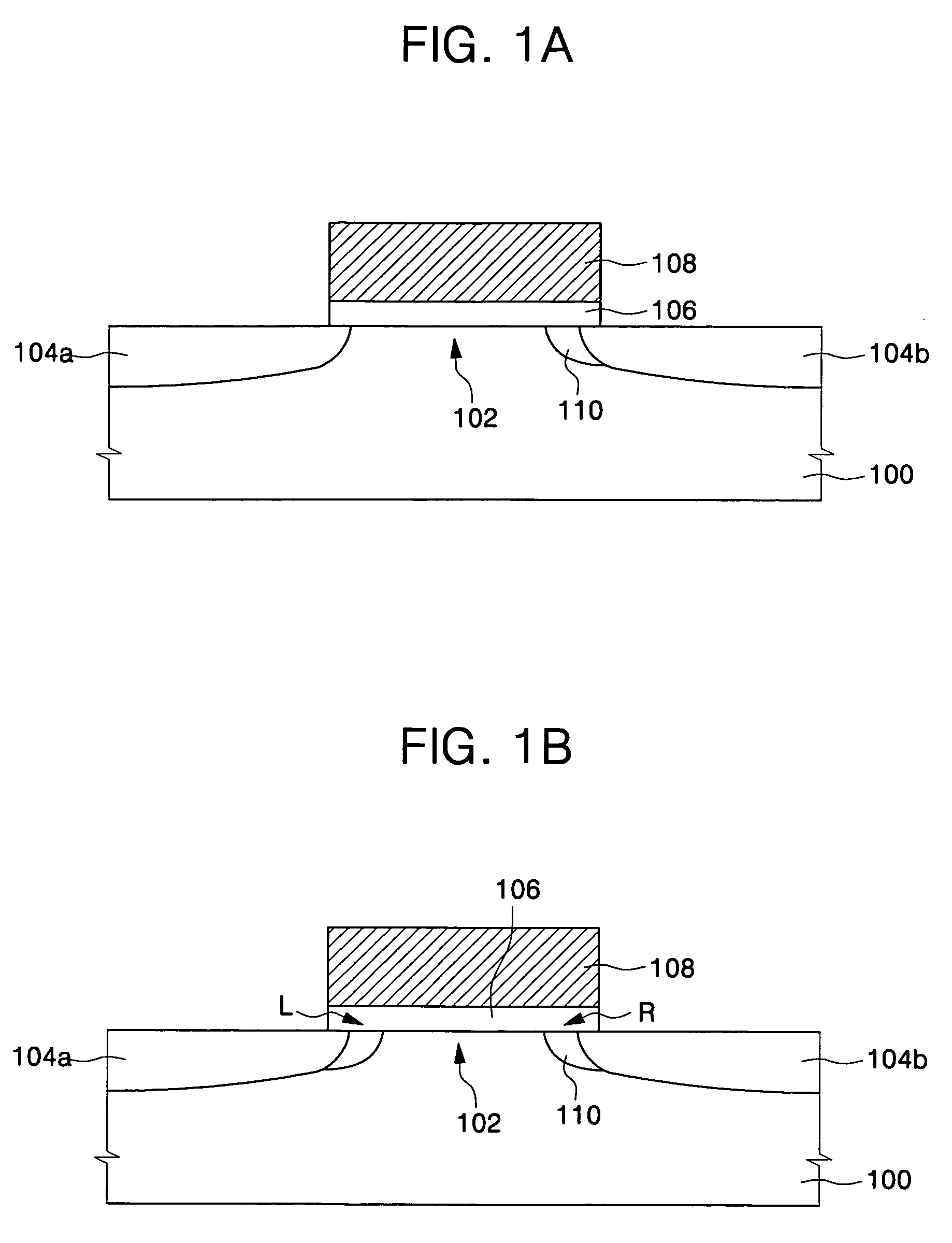

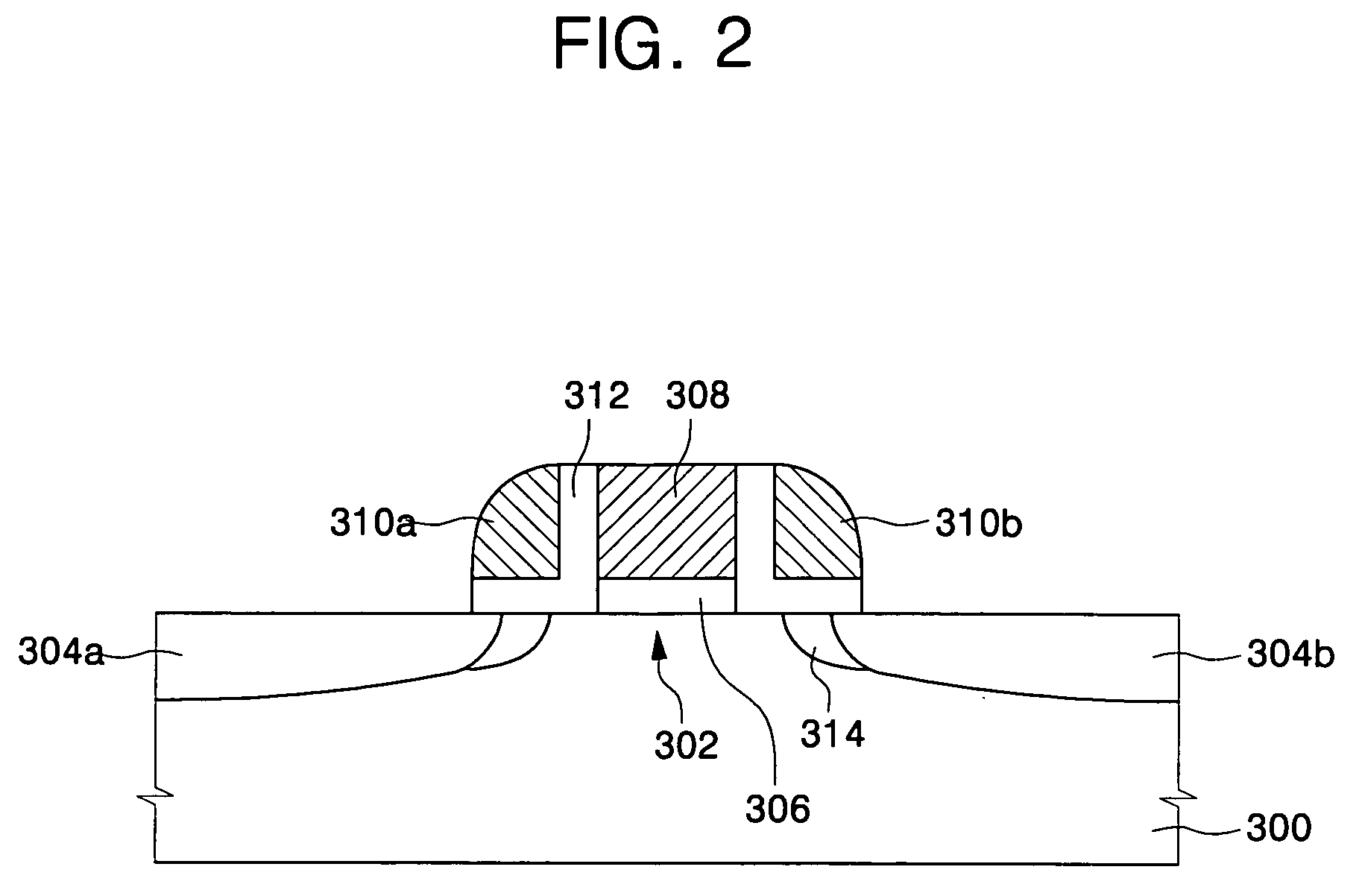

Non-volatile memory device having a charge storage oxide layer and operation thereof

InactiveUS20050184334A1Simple processImprove productivitySolid-state devicesSemiconductor/solid-state device manufacturingIon implantationSemiconductor

A non-volatile memory device includes a pair of source / drain regions disposed in a semiconductor substrate, having a channel region between them. A charge storage oxide layer is disposed on the channel region and overlaps part of each of the pair of source / drain regions. A gate electrode is disposed on the charge storage oxide layer. At least one halo implantation region is formed in the semiconductor substrate adjacent to one of the pair of source / drain regions, and overlapping the charge storage oxide layer. A program operation is performed by trapping electrons in the charge storage oxide layer located near the source / drain region where the halo ion implantation region is formed, and an erase operation is performed by injecting holes into the charge storage oxide layer located near the source / drain region where the halo ion implantation region is formed.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for forming self-aligned dual salicide in CMOS technologies

ActiveUS20060121665A1Reduce required lithography levelSimplify dual salicide formation processSemiconductor/solid-state device manufacturingCMOSSalicide

A method of fabricating a complementary metal oxide semiconductor (CMOS) device, wherein the method comprises forming a first well region in a semiconductor substrate for accommodation of a first type semiconductor device; forming a second well region in the semiconductor substrate for accommodation of a second type semiconductor device; shielding the first type semiconductor device with a mask; depositing a first metal layer over the second type semiconductor device; performing a first salicide formation on the second type semiconductor device; removing the mask; depositing a second metal layer over the first and second type semiconductor devices; and performing a second salicide formation on the first type semiconductor device. The method requires only one pattern level and it eliminates pattern overlay as it also simplifies the processes to form different silicide material over different devices.

Owner:AURIGA INNOVATIONS INC

Flexible membrane

ActiveUS20180208454A1The formation process is simpleBehaviour of the flexible membrane is more predictableOptical signal transducersDecorative surface effectsMicroelectromechanical systemsWaveguide

There is provided a flexible membrane for use in a microelectromechanical transducer, the flexible membrane comprising an electromagnetic waveguide. There is further provided a microelectromechanical system comprising a substrate which comprises the flexible membrane, and a process for forming the flexible membrane. The flexible membrane may be configured to operate within an optical microphone system.

Owner:CIRRUS LOGIC INC

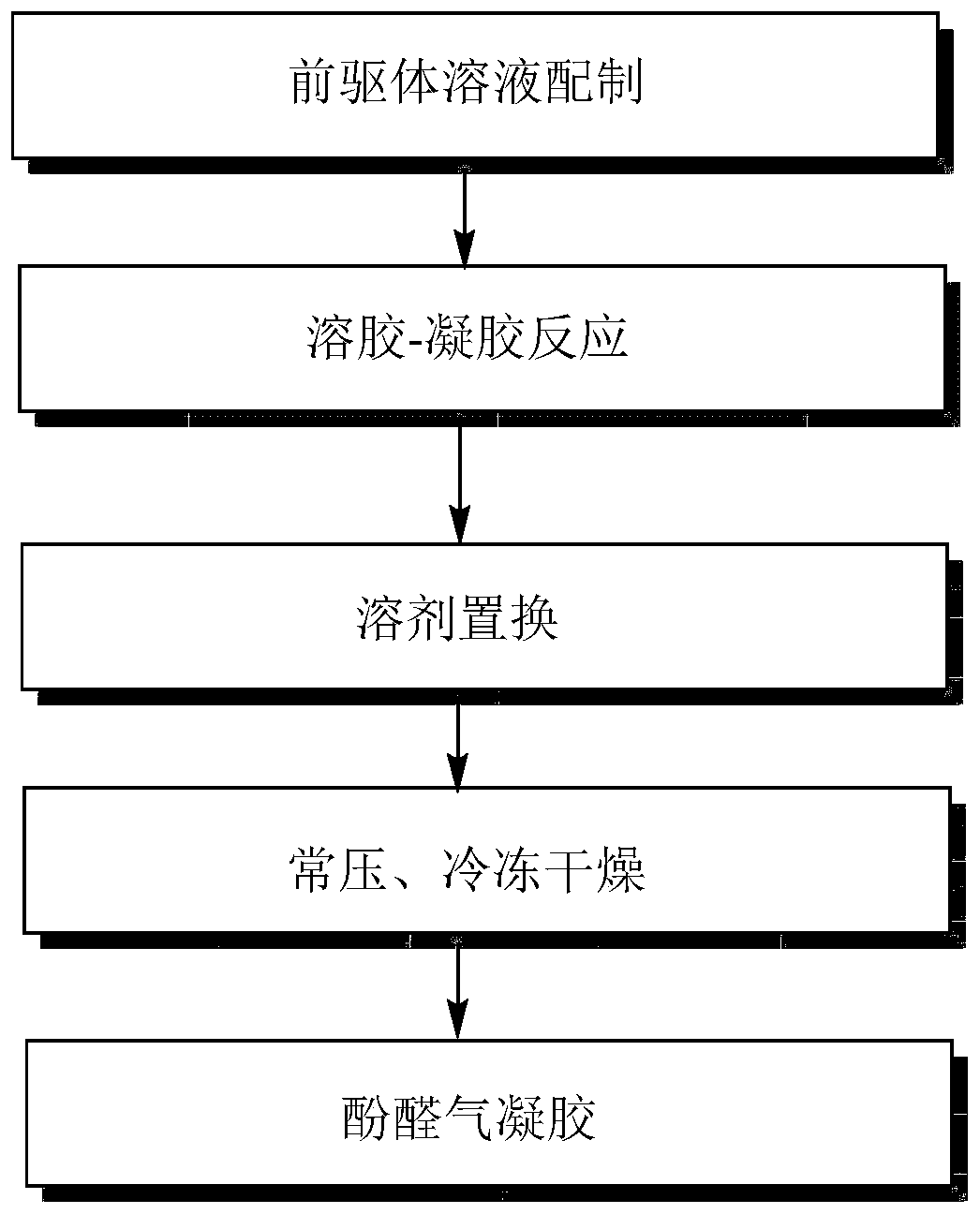

Preparation method for phenolic aerogel

InactiveCN110467742AThe formation process is simpleReduce investmentMaterials preparationWater baths

The invention provides a preparation method for a phenolic aerogel. The phenolic aerogel is prepared from a template polymer, phenols, amines and aldehydes through water blending, crosslinking and drying, and belongs to the field of material preparation technology. The preparation method for the phenolic aerogel of the invention comprises the following successive steps: a, mixing phenols, aldehydes, amines, a catalyst, an initiator and the like in water, and carrying out heating in a water bath; b, adding the template polymer, adjusting a pH value, carrying out a sol-gel reaction, and performing standing and ageing so as to obtain a wet gel; and c, immersing the obtained gel in an organic solvent for replacement, and carrying out drying to obtain the organic phenolic aerogel. The preparation method of invention has mild reaction conditions, prepares the aerogel under low-temperature heating conditions, is simple to operate, is safe and reliable, and uses easily-available and cheap rawmaterials.

Owner:INST OF CHEM IND OF FOREST PROD CHINESE ACAD OF FORESTRY +1

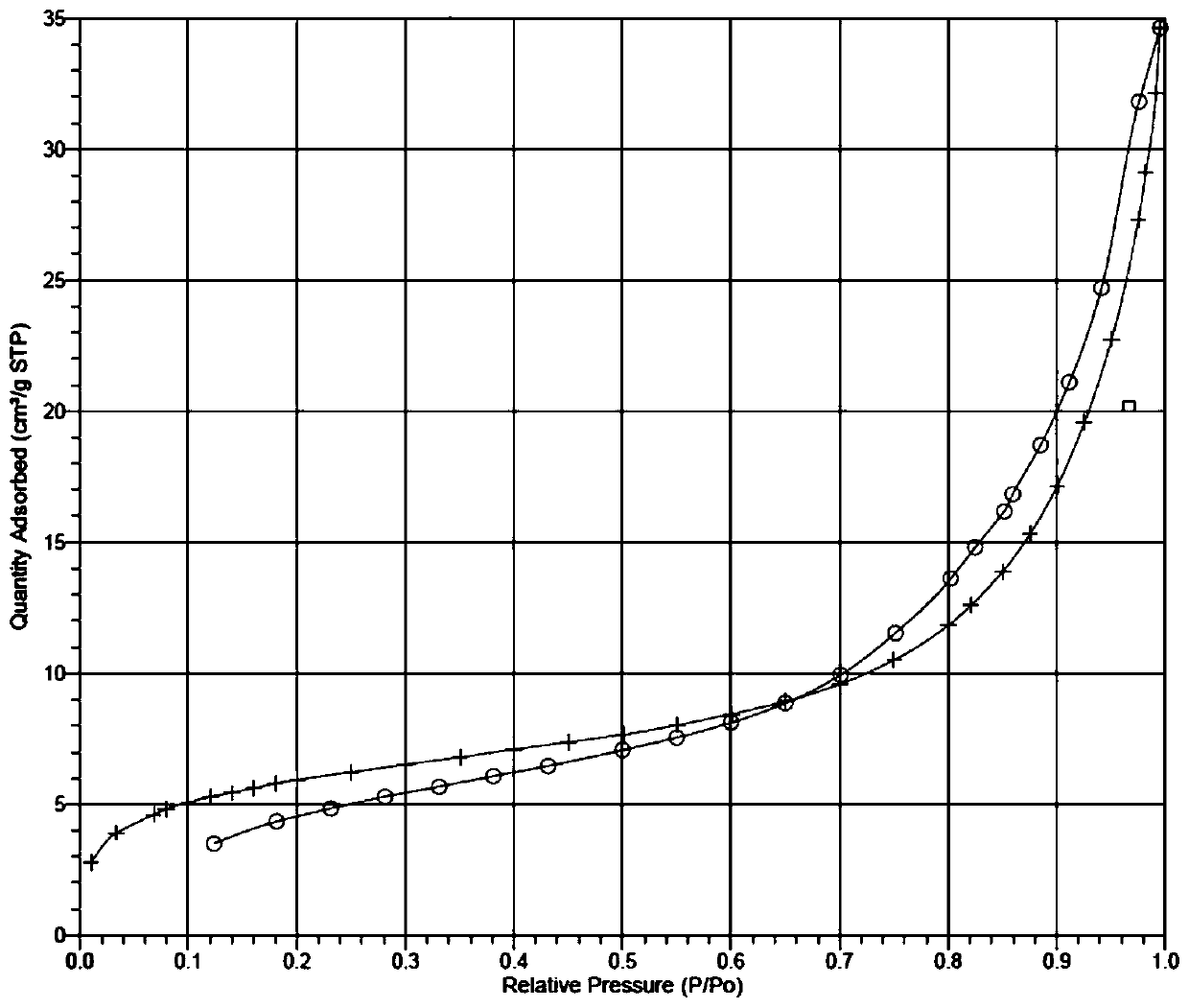

Heated electrostatic chuck and semiconductor wafer heater and methods for manufacturing same

ActiveUS20140291311A1Improved performance characteristicsHigh porositySemiconductor/solid-state device manufacturingOhmic-resistance heatingPlasma depositionEngineering

A heated electrostatic chuck is provided, including a base having an upper surface and peripheral side surfaces, a thermal barrier coating formed by plasma deposition directly on at least the upper surface of the base, at least one heating element formed on portions of the thermal barrier coating, an electrically insulating layer formed on the heating element and exposed portions of the thermal barrier coating, at least one chucking electrode formed on at least a portion of the electrically insulating layer, and a protective layer formed on the chucking electrode.

Owner:FM INDS

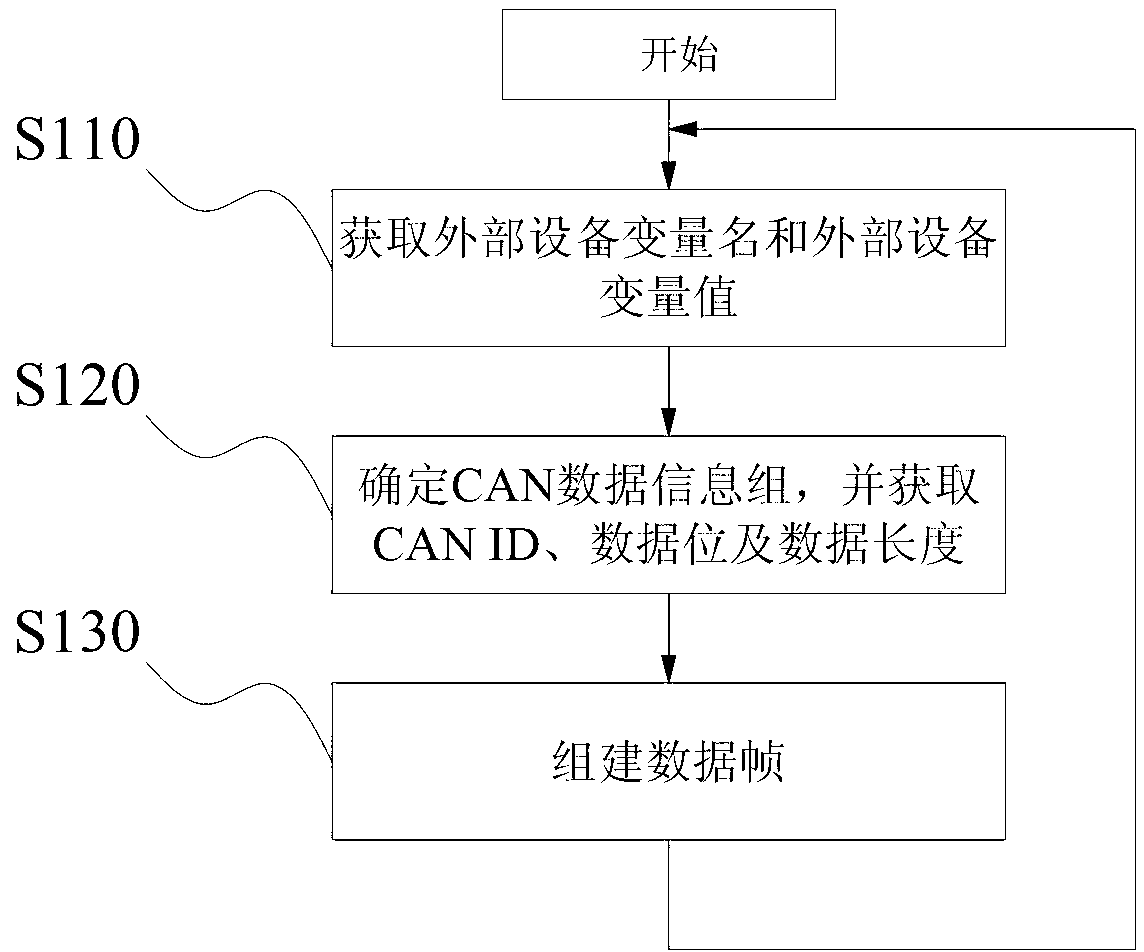

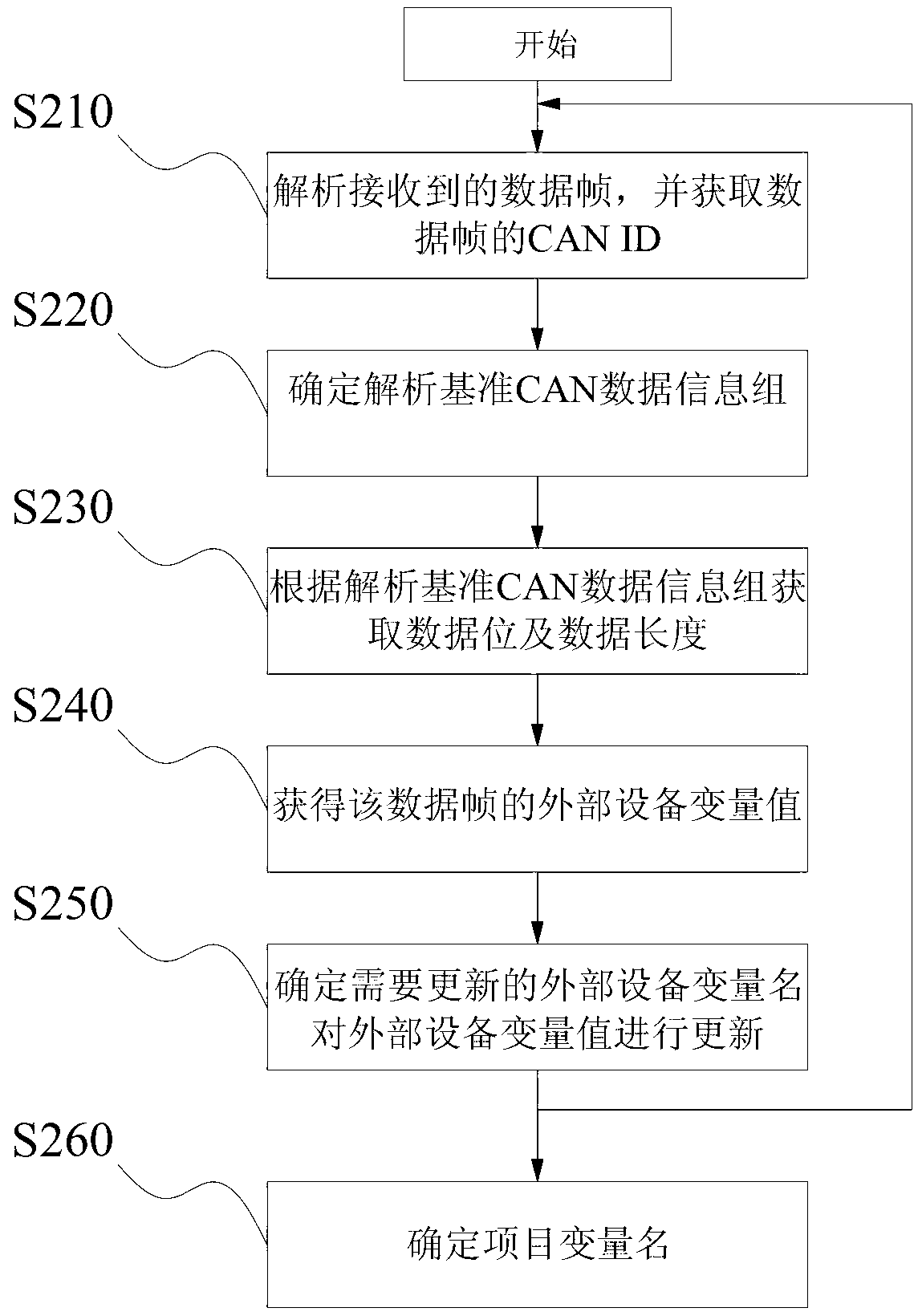

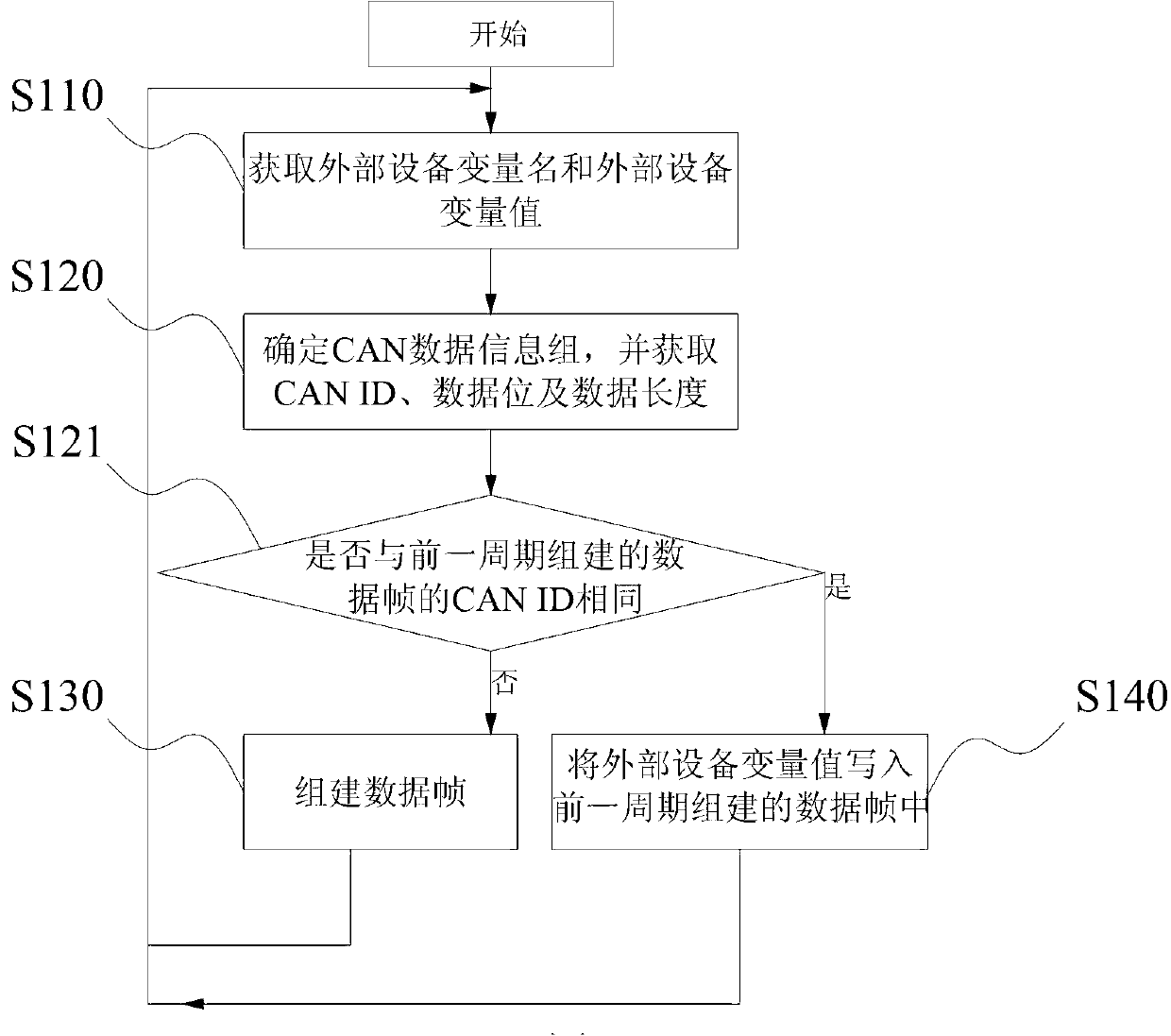

Industrial control system as well as control method and control device thereof

ActiveCN103217956AThe formation process is simpleImprove stabilityTotal factory controlProgramme total factory controlArea networkData information

The invention discloses an industrial control system as well as a control method and a control device thereof. The control method of the industrial control system comprises a data frame framing process and a data frame resolving process. The data frame framing process comprises the following steps of acquiring CAN (Controller Area Network) ID (Identity), data bits and data length according to variable names of external equipment; and framing data frames according to external equipment variable values as well as the CAN ID, the data bits and the data length. The data frame resolving process comprises the following steps of acquiring the data bits and the data length according to the CAN ID of data frames; and acquiring the external equipment variable values of the data frames according to the acquired data bits and data length. By utilizing the control method, by virtue of updating or increasing the information of an external equipment variable information group and a CAN data information group, the communication between the control device and the external equipment can be ensured, the data frame framing and the data frame resolving can be realized, while the universality of the control device is improved or kept, the assembling process of the industrial control system is simplified, and the stability and reliability of the industrial control system are improved.

Owner:SANY HEAVY IND CO LTD (CN)

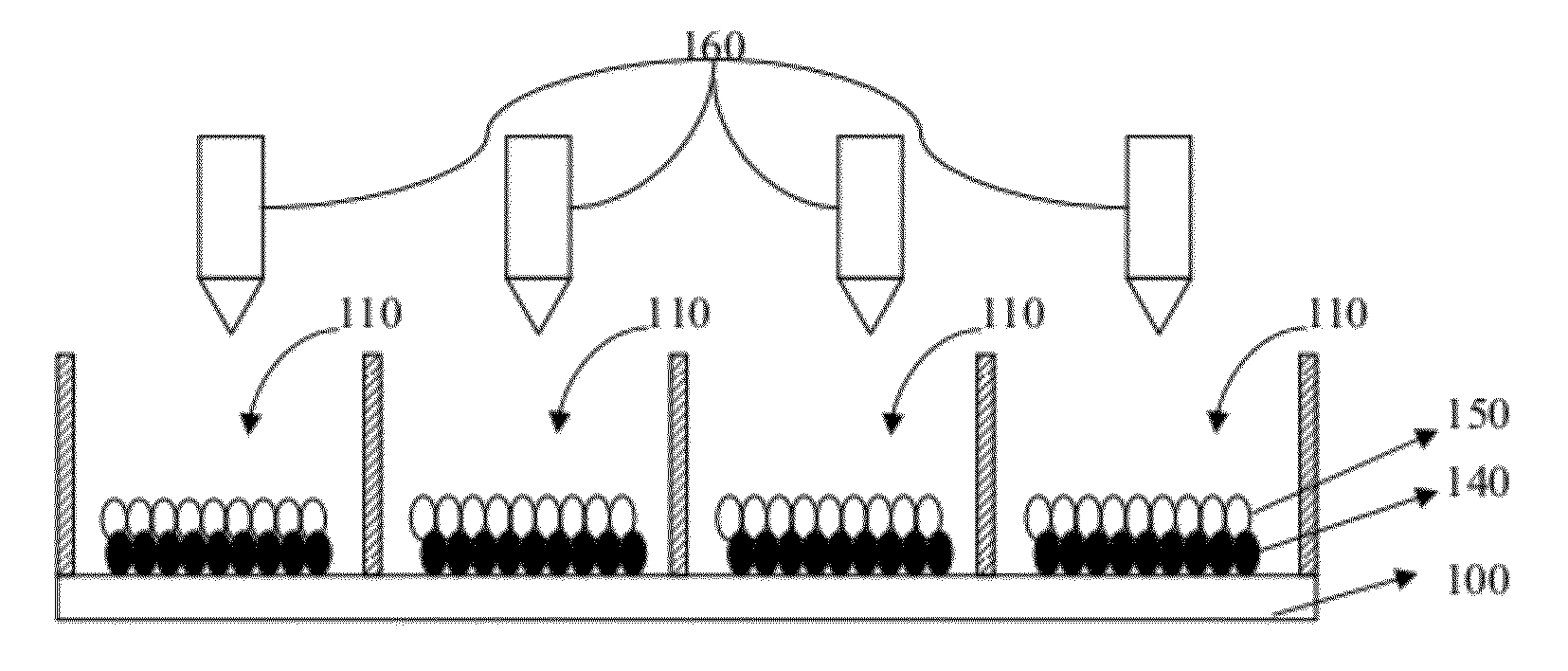

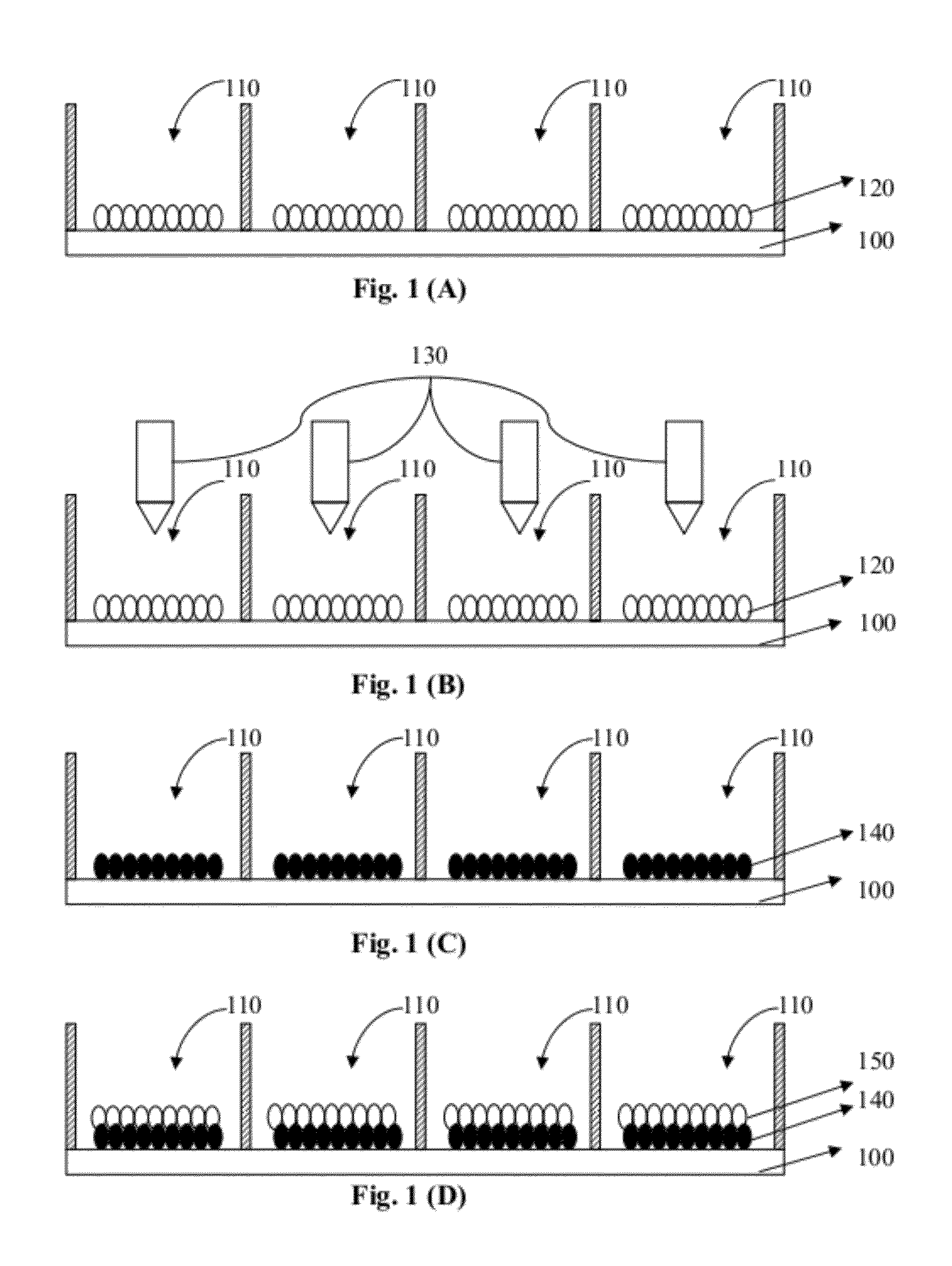

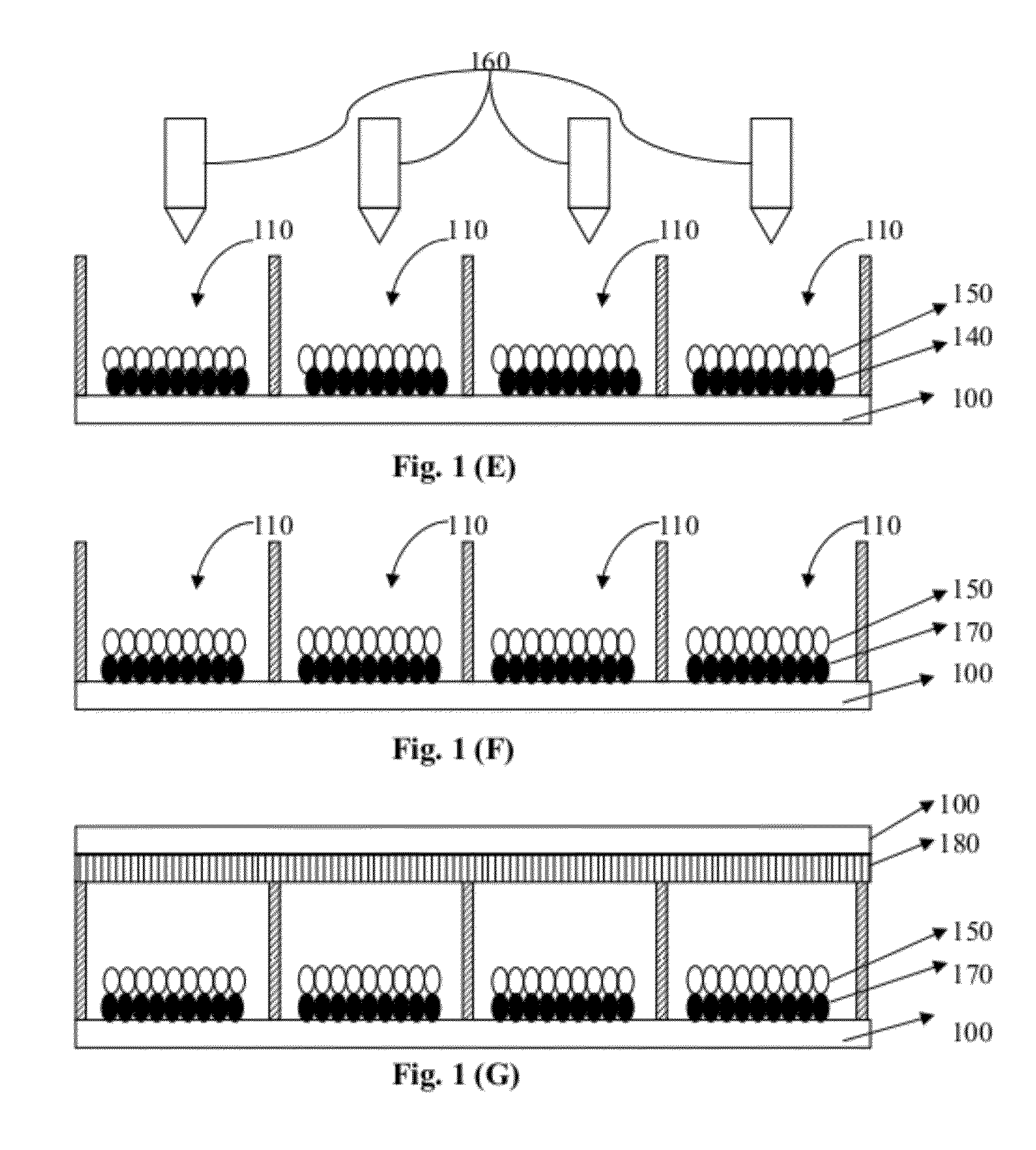

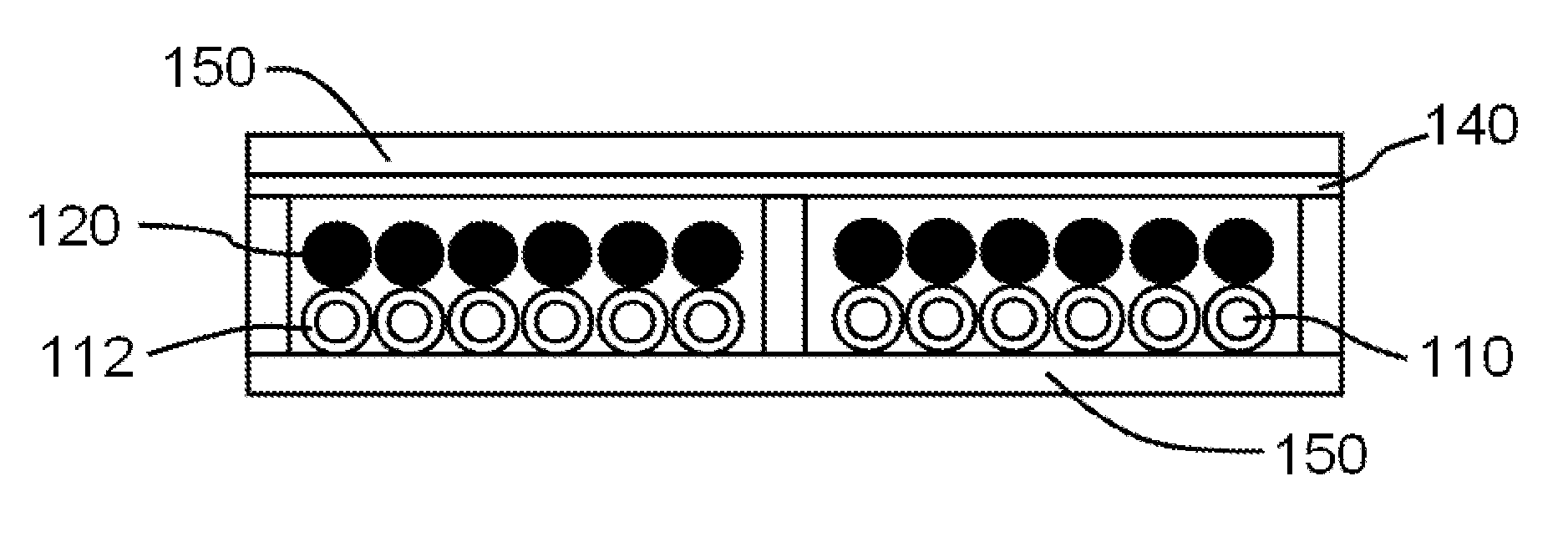

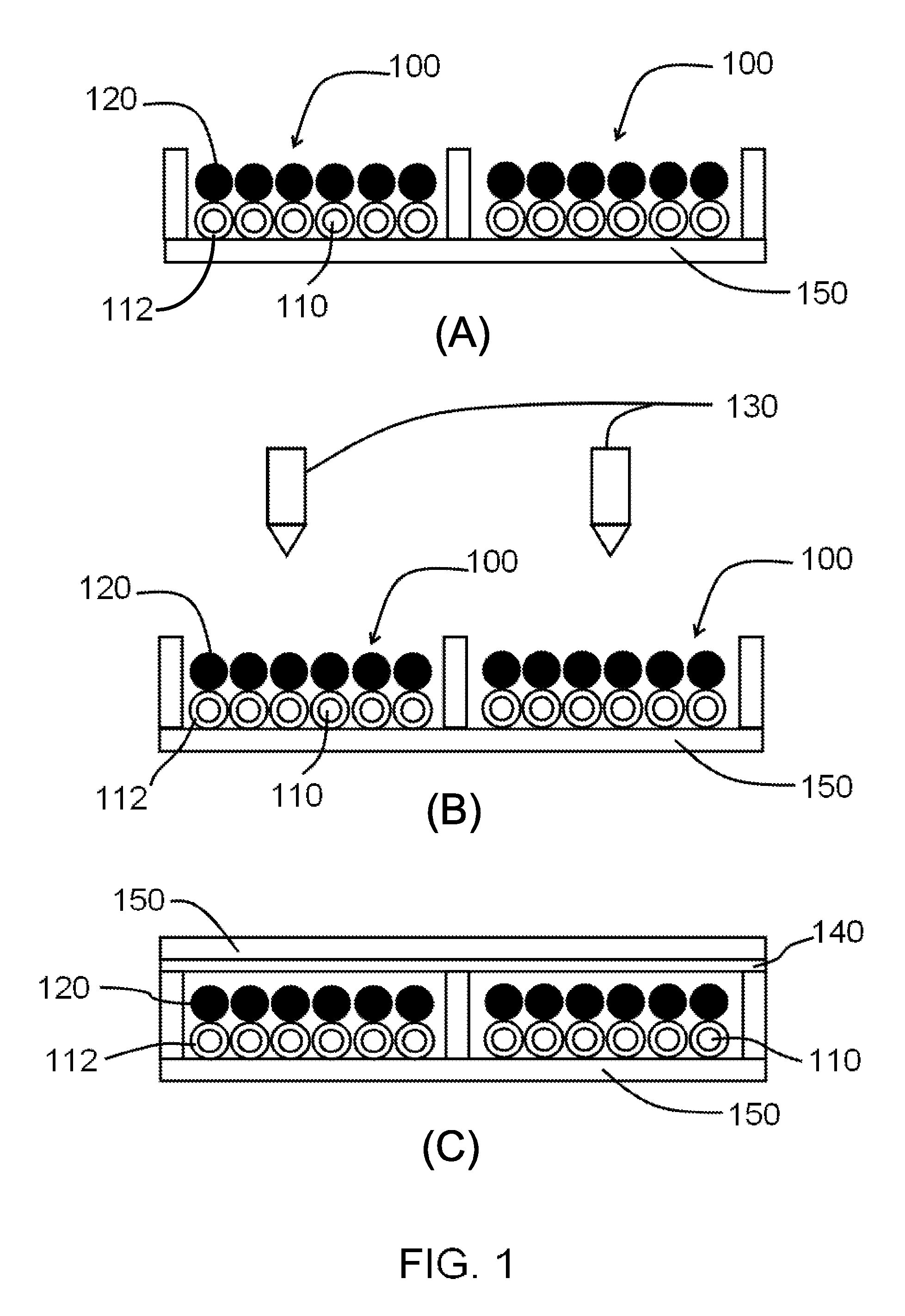

Switchable color particle-based display and method of manufacturing same

InactiveUS20120329356A1The formation process is simpleLow costVessels or leading-in conductors manufactureNon-linear opticsDisplay deviceBiomedical engineering

The invention in one relates to a method for manufacturing a switchable particle-based display having a plurality of display units spatially arranged in a matrix form, wherein each display unit comprises one or more cells. In one embodiment, the method includes filling a plurality of first-type particles into the one or more cells of each display unit, filling one or more solutions into the one or more cells of each display unit, respectively, so that each cell contains one of the one or more solutions, where each of the one or more solutions comprises a respective colorant, and the respective colorant in each cell reacts with or adsorbs on the first-type particles therein, and filling a plurality of second-type particles into the one or more cells of each display unit.

Owner:DELTA ELECTRONICS INC

Semiconductor device manufacturing method

InactiveUS20060099784A1Low costSimplifies formation processSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device fabrication

A semiconductor device manufacturing method is provided in which, in the dummy gate pattern formation process, the pattern formation process is simplified and costs are reduced. A semiconductor device manufacturing method including: forming a mask element on a substrate; patterning the mask element into a prescribed shape, and forming a depression in the mask element; placing a functional liquid in the depression; drying the functional liquid placed in the depression so as to form a functional film; annealing the functional film; and, removing the mask element so as to form a dummy gate pattern of a residue of the functional liquid.

Owner:SEIKO EPSON CORP

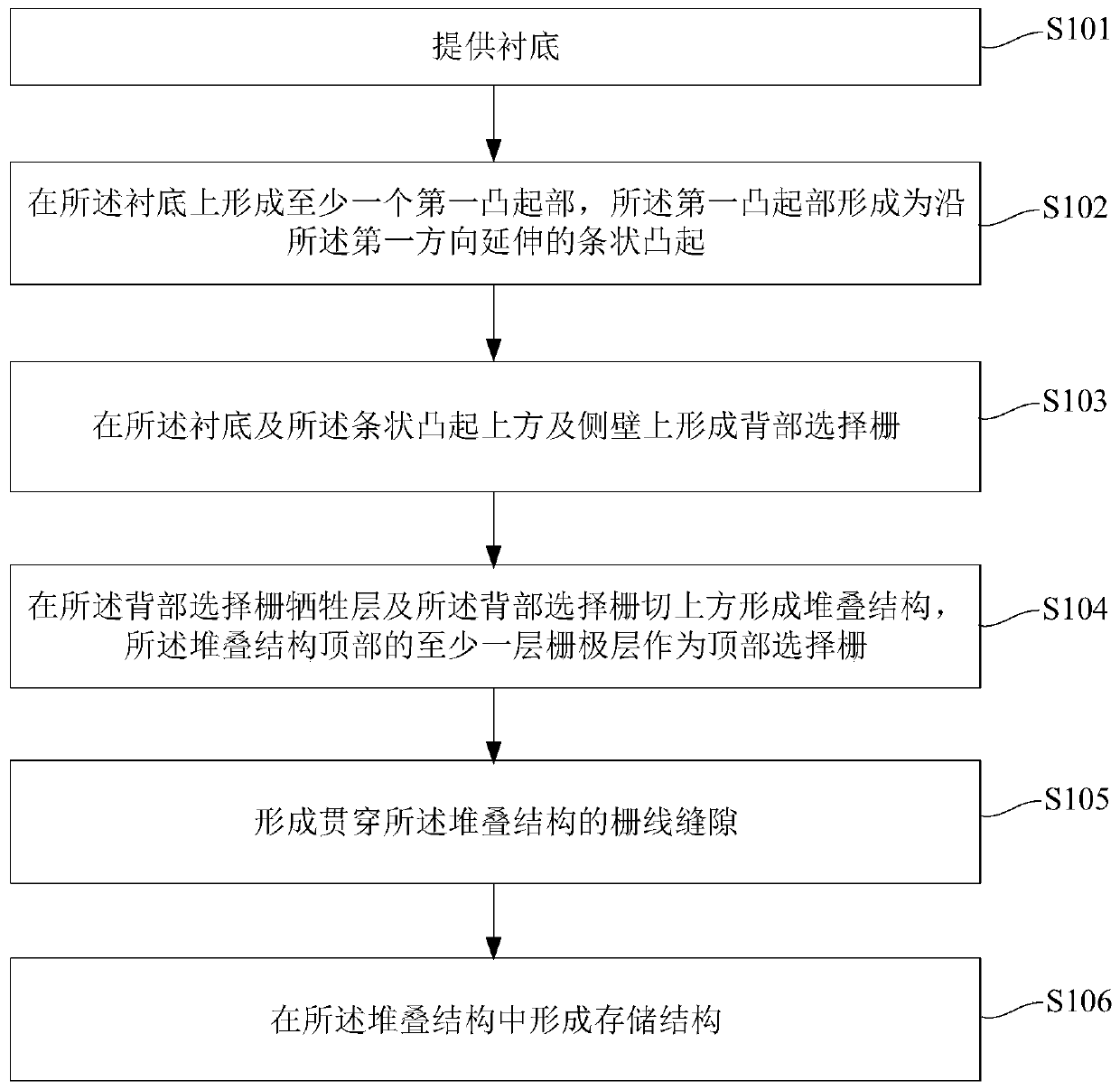

3D NAND memory and manufacturing method thereof

InactiveCN111162078AAvoid damageSimplify the graphing processSolid-state devicesSemiconductor devicesStructural engineeringGate oxide

The invention provides a 3D NAND memory and a manufacturing method thereof. The method comprises the following steps of: by etching a substrate, strip-shaped raised first raised parts are formed on the substrate; the back selection gate oxides formed on the upper portions and the side walls of the first raised parts form back selection gate tangent lines, the subsequently-formed back selection gates are cut off, separation control over the back selection gates is achieved, the control time of the device is prolonged, and the RC delay effect of a word line layer of the device is reduced. Or while the first raised part is formed, columnar raised second raised parts which are distributed in an array manner are formed on the substrate. The storage structures distributed in an array mode and formed in the stacking structure correspond to the second protruding parts in a one-to-one mode, and part of the storage structures are formed on the first raised parts. The first raised parts and the second raised parts replace a selective epitaxial structure formed in a channel hole, the substrate patterning process is easy to control, and etching post-processing is not needed.

Owner:YANGTZE MEMORY TECH CO LTD

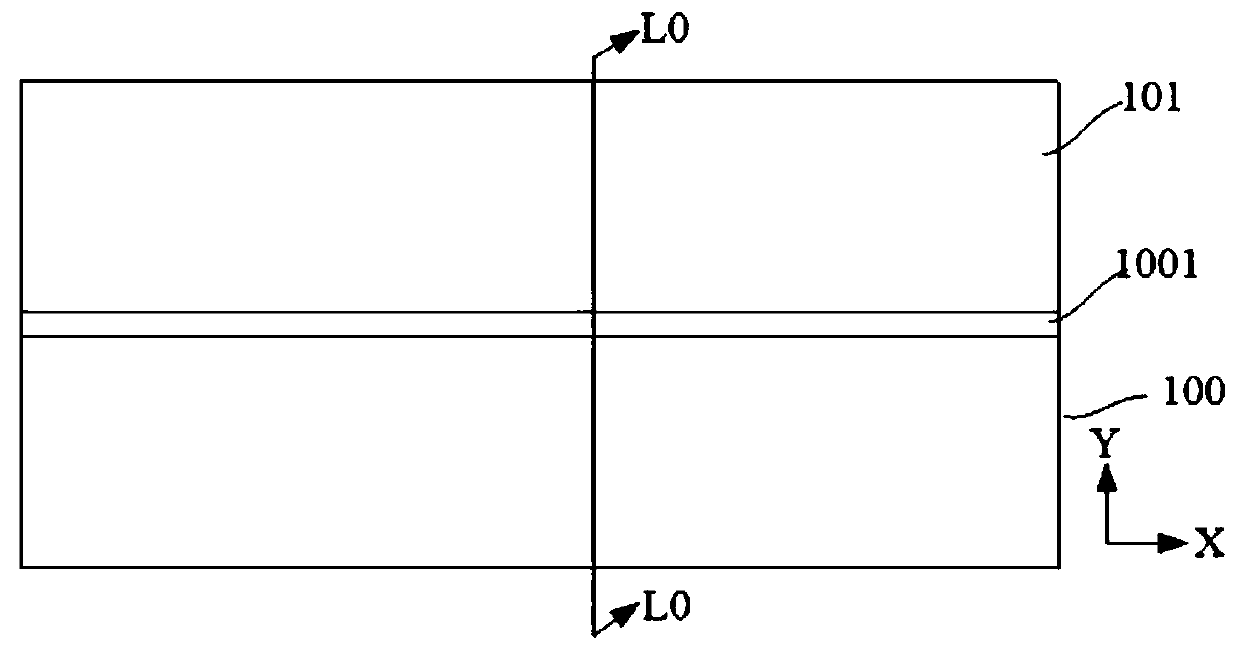

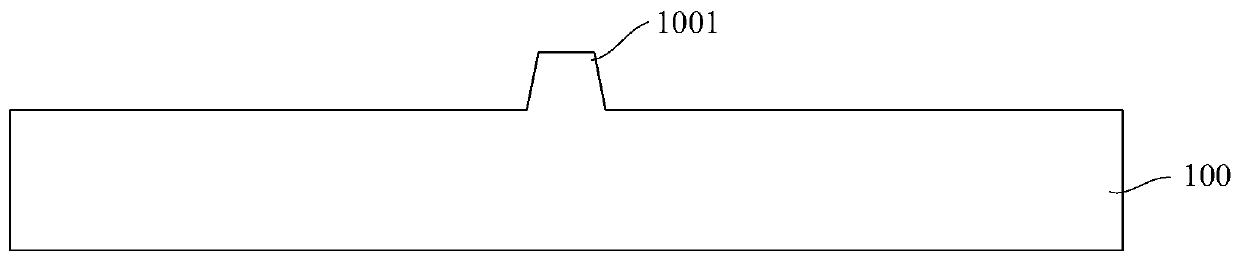

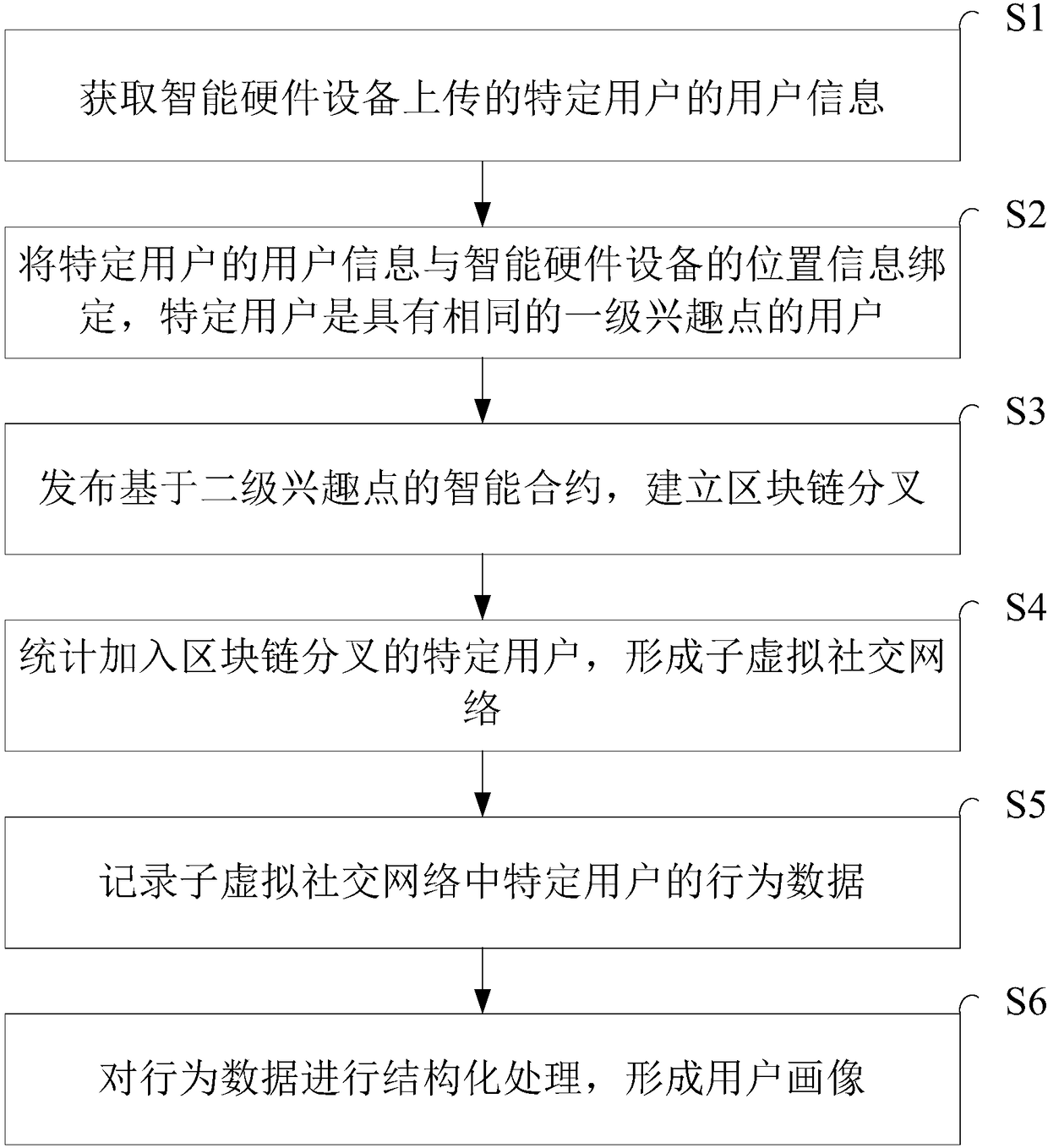

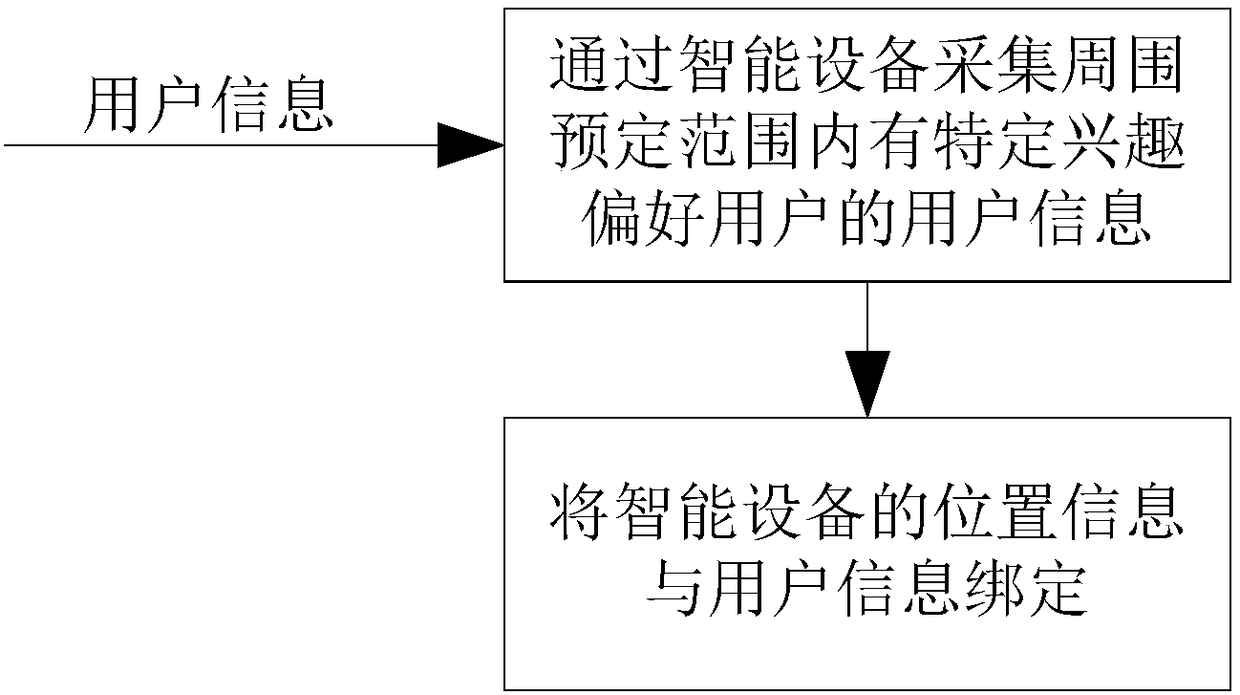

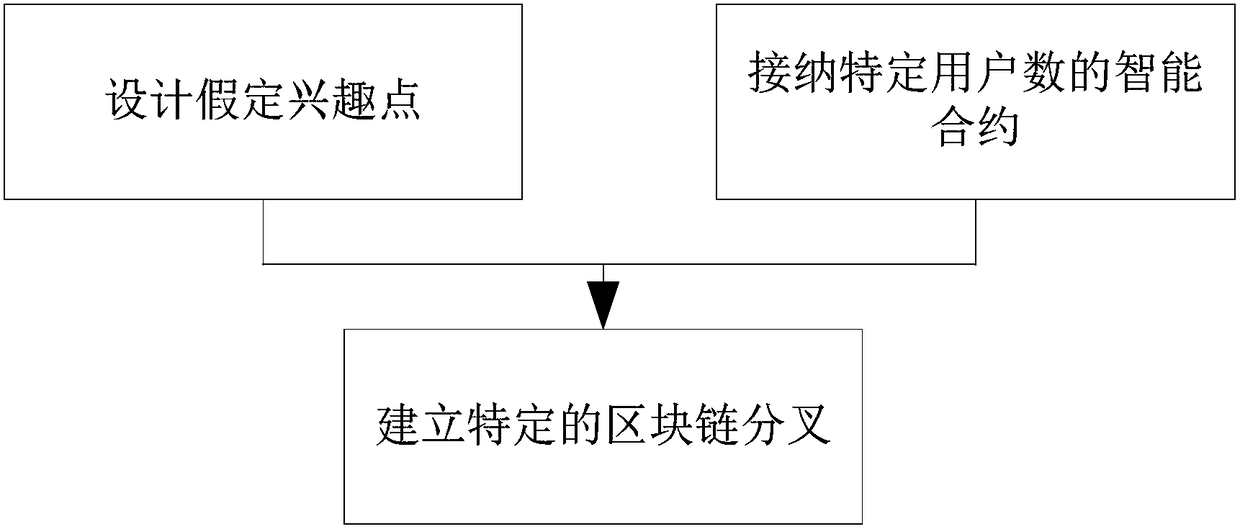

Data processing method for social network

ActiveCN108537542AThe formation process is simpleImprove accuracyFinancePayment protocolsCredit systemSmart contract

The invention, which belongs to the technical field of computers, provides a data processing method for a social network. The method comprises: user information, uploaded by an intelligent hardware device, of a specific user is obtained; the user information of the specific user is bound with the location information of the intelligent hardware device; a smart contract is issued; a blockchain bifurcation is established; statistics of specific users added into the blockchain bifurcation is carried out; a sub-virtual social network is formed; behavior data of members in the sub-virtual social network are recorded; structural processing is carried out on the behavior data to form various user portraits. With the method provided by the invention, the user's behavior data can be analyzed comprehensively; the user portrait formation process is simplified; and the novel social credit system is constructed based on the user portrait.

Owner:北京天材科技有限公司

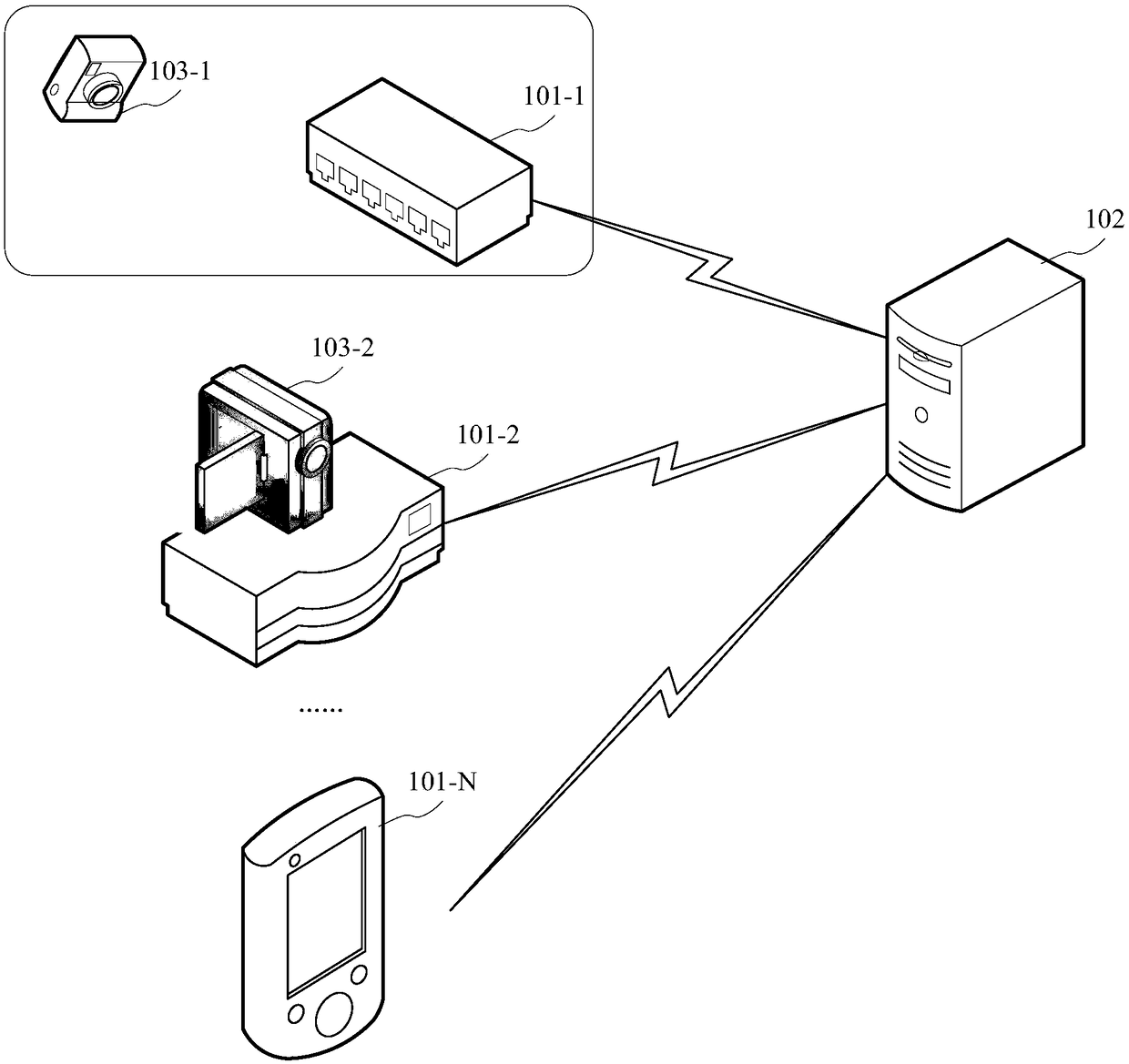

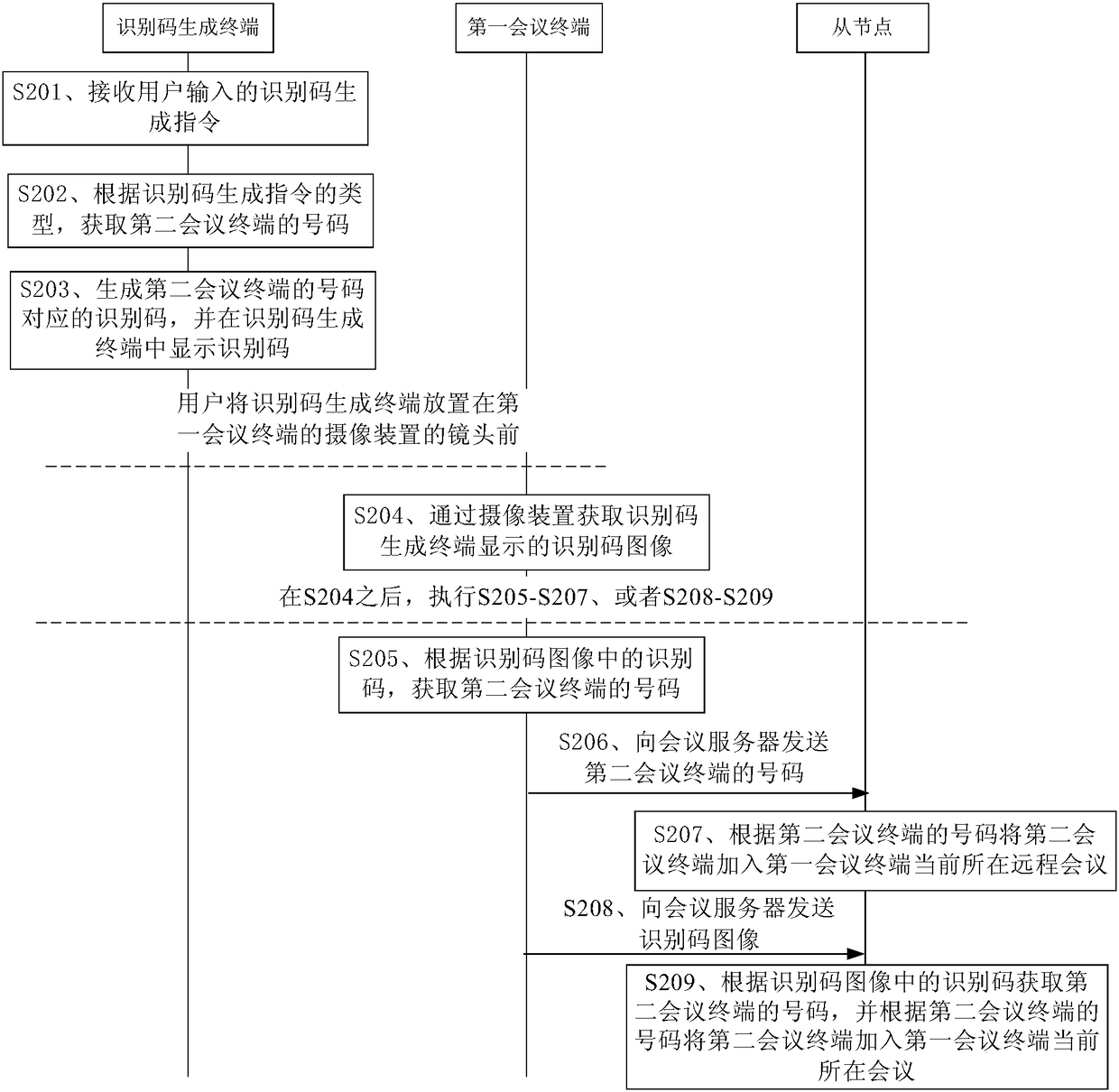

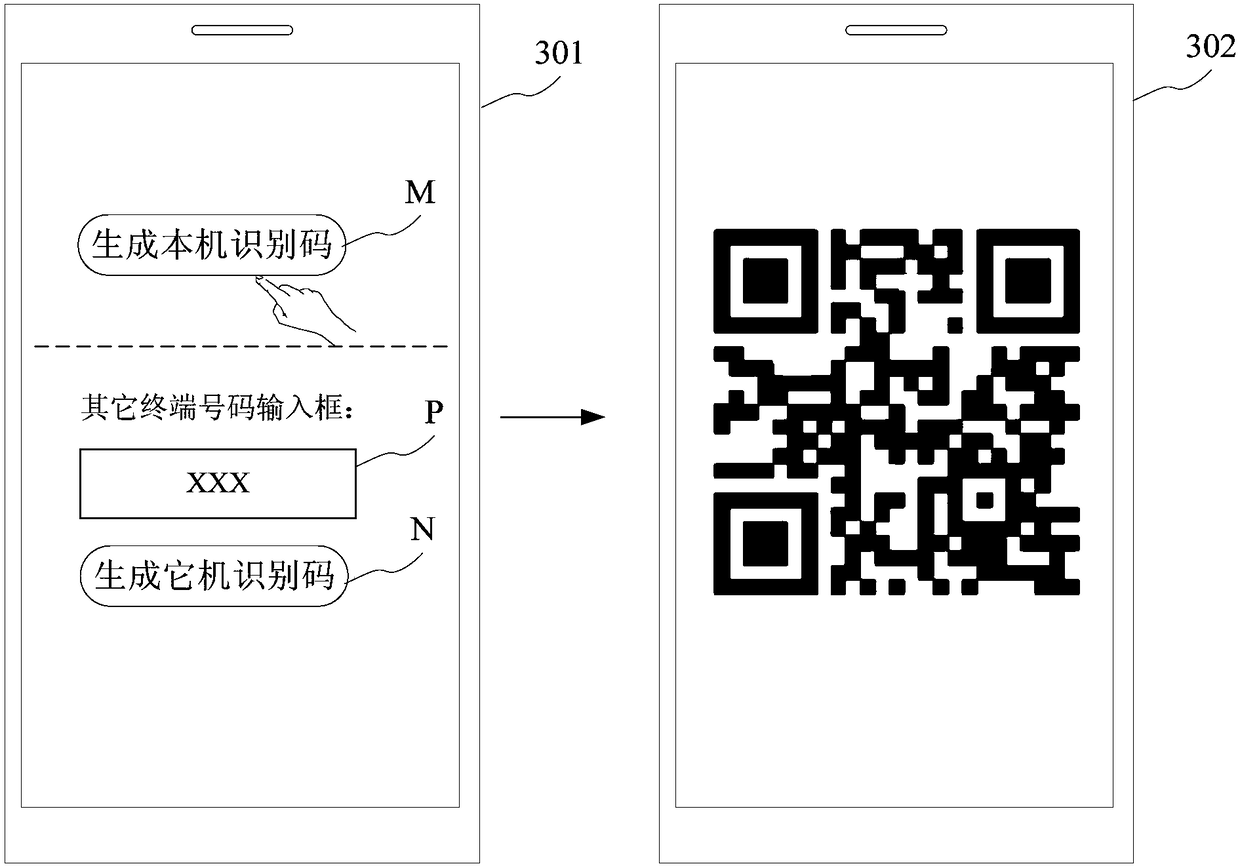

Remote conference implementation method and system, and equipment

ActiveCN108243319AThe formation process is simpleImprove efficiencyTelevision conference systemsTwo-way working systemsSoftware engineeringComputer terminal

The embodiment of the invention provides a remote conference implementation method and system, and equipment. The method comprises: a shooting device is used for acquiring an identification code image, wherein the identification code image includes an identification code corresponding to the number of a second conference terminal and the second conference terminal is a terminal making a request ofparticipating in a remote conference in which a first conference terminal is currently located; according to the identification code in the identification code image, the number of the second conference terminal is obtained; the number of the second conference terminal is sent to a conference server, so that the conference server adds the second conference terminal in the conference in which thefirst conference terminal is currently located according to the number of the second conference terminal; or the identification code image is sent to the conference server and thus the conference server obtains the number of the second conference terminal based on the identification code in the identification code image, and the second conference terminal is added in a conference in which the first conference terminal is currently located based on the number of the second conference terminal. The remote conference implementation method and system, and equipment are used for improving the efficiency of organizing remote conferences.

Owner:HUAWEI TECH CO LTD

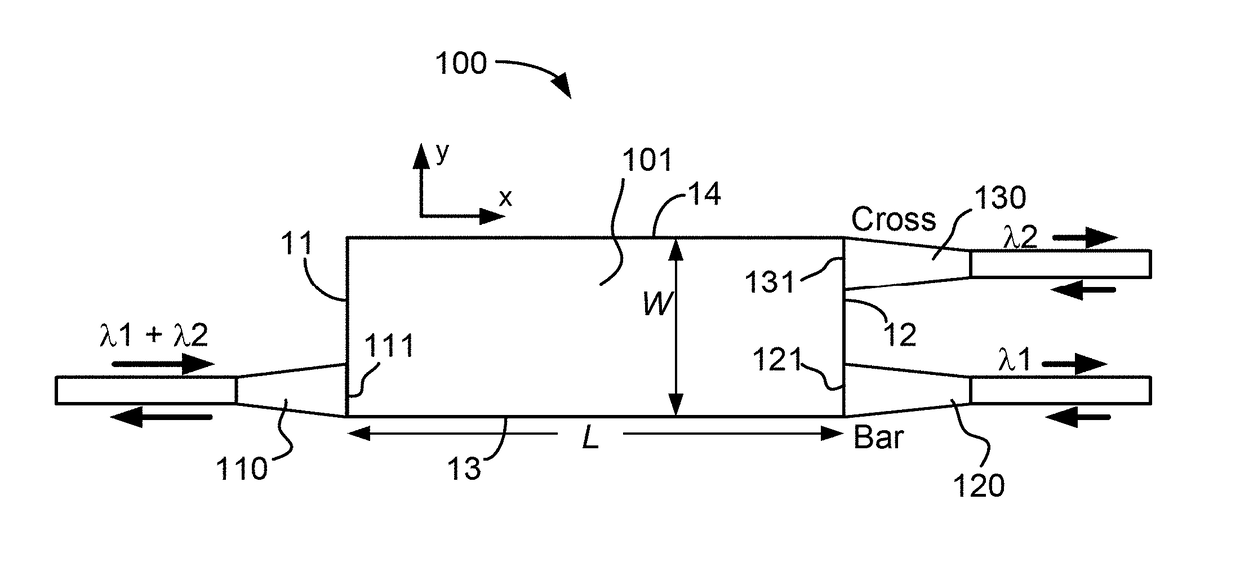

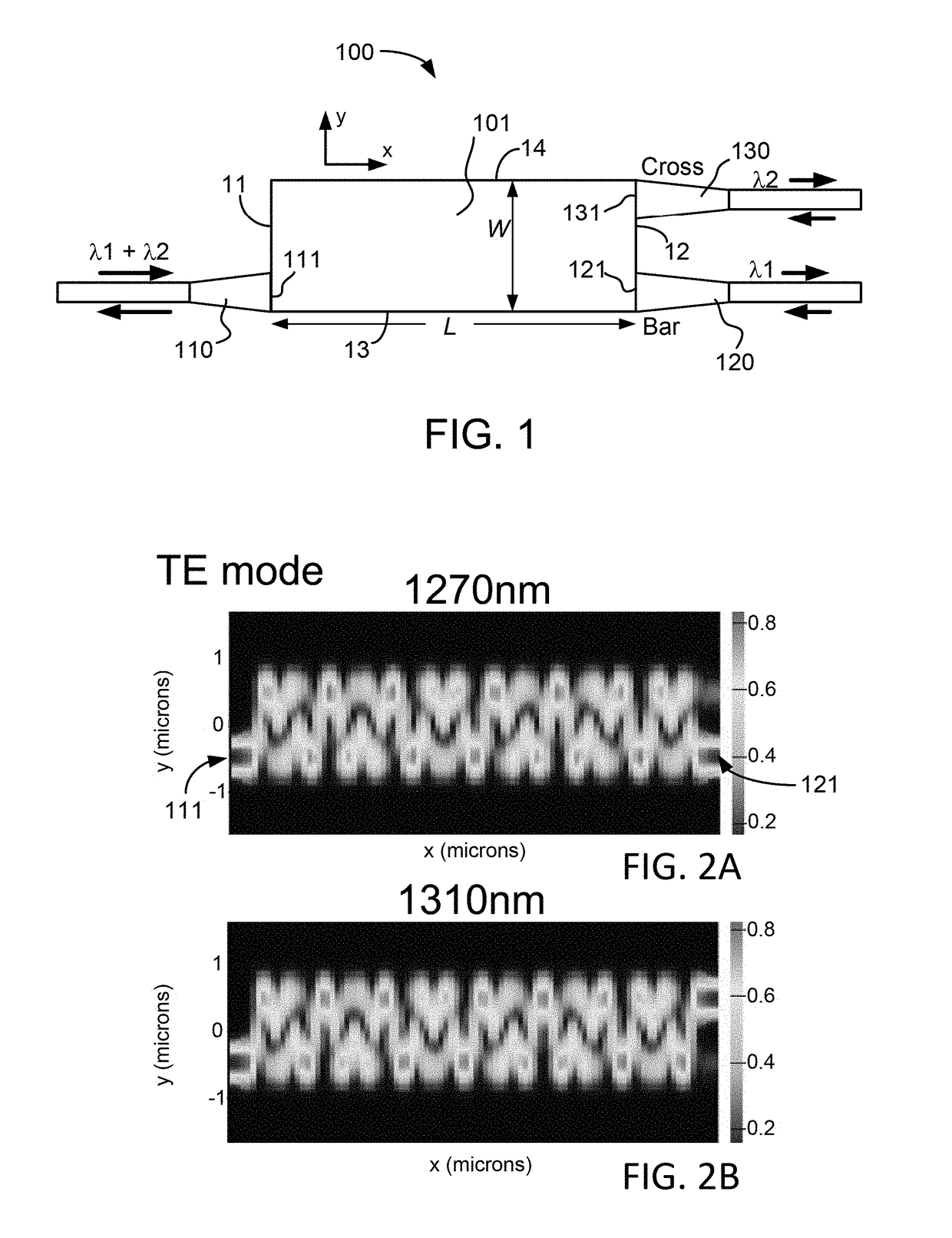

Silicon-based multiplexer/demultiplexer for O-band

ActiveUS10036853B1Improve production yieldSimplifies waveguide formation processOptical waveguide light guideMultiplexerLength wave

A multiplexer / demultiplexer for at least two wavelengths in O-band. The multiplexer / demultiplexer includes a silicon waveguide block having a first port, a second / third port respectively in bar / cross position at an opposing end plane relative to the first port. The silicon waveguide block is configured to provide a general interference excitation of a light wave of a first wavelength and a second wavelength respectively selected from two windows in O-band. The light wave is either inputted via the first port and split into a first output light of the first wavelength out of the second port and a second output light of the second wavelength out of the third port, or is combined of a first input light of the first wavelength from the second port and a second input light of the second wavelength from the third port and outputted via the first port with both wavelengths.

Owner:MARVELL ASIA PTE LTD

Method for forming self-aligned dual salicide in CMOS technologies

ActiveUS7064025B1Lower Level RequirementsThe formation process is simpleSemiconductor/solid-state device manufacturingSalicideCMOS

A method of fabricating a complementary metal oxide semiconductor (CMOS) device, wherein the method comprises forming a first well region in a semiconductor substrate for accommodation of a first type semiconductor device; forming a second well region in the semiconductor substrate for accommodation of a second type semiconductor device; shielding the first type semiconductor device with a mask; depositing a first metal layer over the second type semiconductor device; performing a first salicide formation on the second type semiconductor device; removing the mask; depositing a second metal layer over the first and second type semiconductor devices; and performing a second salicide formation on the first type semiconductor device. The method requires only one pattern level and it eliminates pattern overlay as it also simplifies the processes to form different silicide material over different devices.

Owner:AURIGA INNOVATIONS INC

Switchable particle-based display and method of manufacturing same

InactiveUS20120329355A1High charge densityImprove sealingVessels or leading-in conductors manufactureNon-linear opticsElectrical polarityCharge control

A method for manufacturing a switchable PBD includes filling a plurality of first-type particles and a plurality of second-type particles into each cell, where the plurality of first-type particles carries charges of a first charge polarity having a first charge density and the plurality of second-type particles is substantially electrically neutral, or carries charges having a second charge density that is substantially lower than the first charge density of the first-type particles, and filling a fluid into each cell, where the fluid comprises a charge controlling agent having a second charge polarity opposite to the first charge polarity, and the charge controlling agent has a substantially selective wettability, absorbability or adsorbability on the plurality of second-type particles. As such, at least part of the plurality of second-type particles is charged to have the second charge polarity in each cell.

Owner:DELTA ELECTRONICS INC