Method for forming self-aligned dual salicide in CMOS technologies

a technology of self-aligning and dual salicide, which is applied in the direction of semiconductor/solid-state device manufacturing, basic electric elements, electric apparatus, etc., can solve the problems of inferior device/circuit performance, non-optimal device performance, and misalignment caused, so as to simplify the dual salicide formation process and reduce the required lithography level , the effect of eliminating the problem of misalignmen

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0032] Next, as illustrated in FIG. 8, the silicide blocking film 114 is removed from the device 101, and a second metal layer 123 is deposited over the entire device 101 (i.e., over both the NFET 140 and PFET 130 regions). Optionally, a cap layer (not shown) may be formed over the second metal layer 123 to prevent oxidation of the silicide during the subsequent annealing process. Furthermore, those skilled in the art would readily understand how to incorporate the optional capping layer over the second metal layer 123. Thereafter, as depicted in FIG. 9, after an annealing process is conducted, the resulting silicide layer 117 over the PFET gate 113 as well as the source / drain silicide contacts 116 on opposite sides of the PFET gate 113 is formed. As shown in FIG. 9, the silicide on the NFET portion 140 of the device 101 is different from the silicide on the PFET portion 130 of the device 101. Moreover, the dual salicide process provided by the invention is performed with only one l...

second embodiment

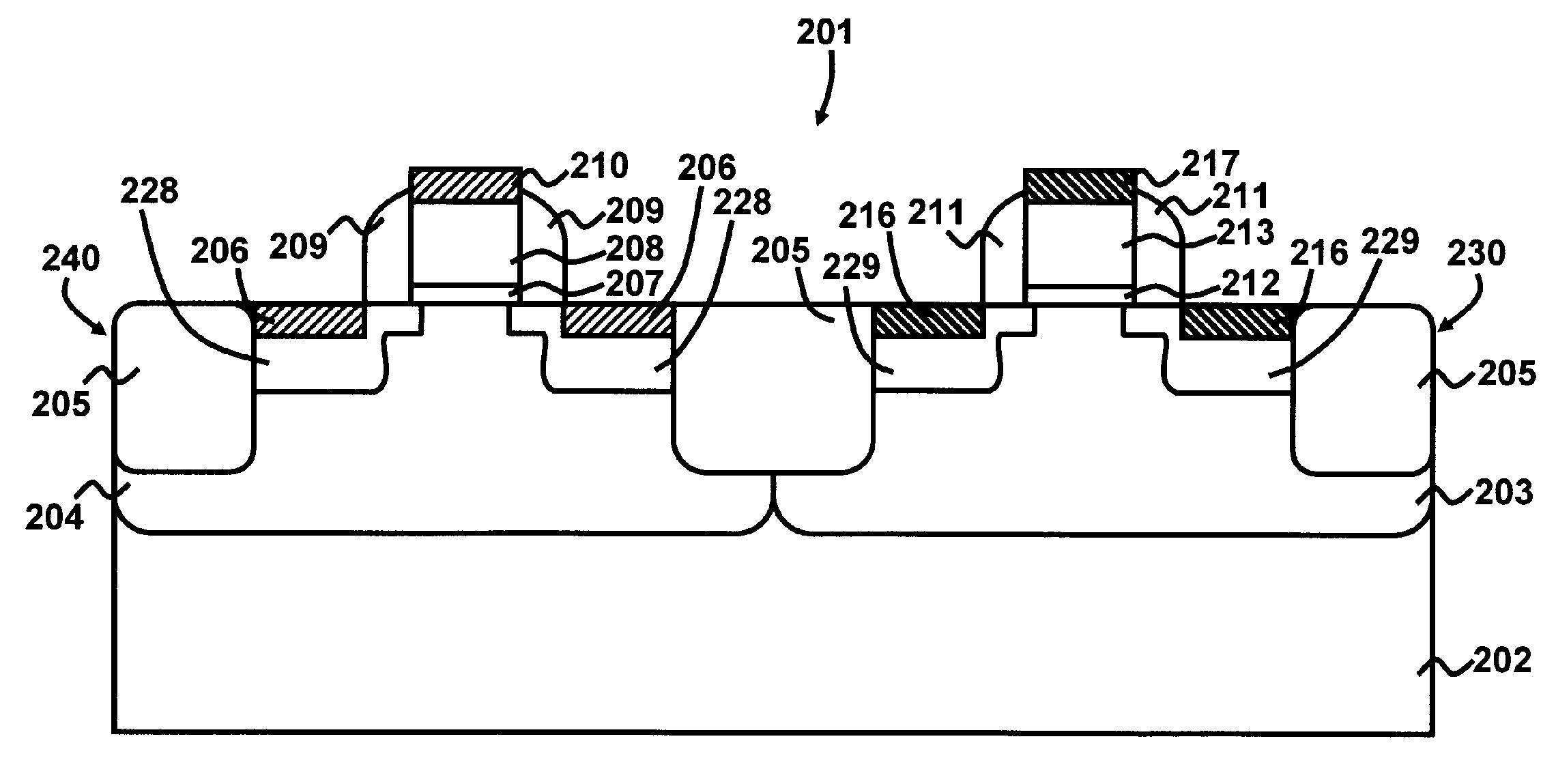

[0043]FIG. 18 illustrates the process flow according to the invention, which describes a method of forming metal silicide layers over a semiconductor substrate 202, wherein the method comprises forming (501) a first well region 203 in the semiconductor substrate 202 for accommodating a first type semiconductor device 230; forming (503) a second well region 204 in the semiconductor substrate 202 for accommodating a second type semiconductor device 240; selectively forming (505) a first metal layer 221 over the second type semiconductor device 240; depositing (507) a capping layer 222 over the first metal layer 221; depositing (509) a second metal layer 223 over the capping layer 222 and the first type semiconductor device 230; and performing (511) a salicide formation on the first and second type semiconductor devices 230, 240, wherein the process of performing (511) the salicide formation is accomplished by annealing the first and second metal layers 221, 223, removing the capping l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More