Patents

Literature

83 results about "Charge pump phase locked loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

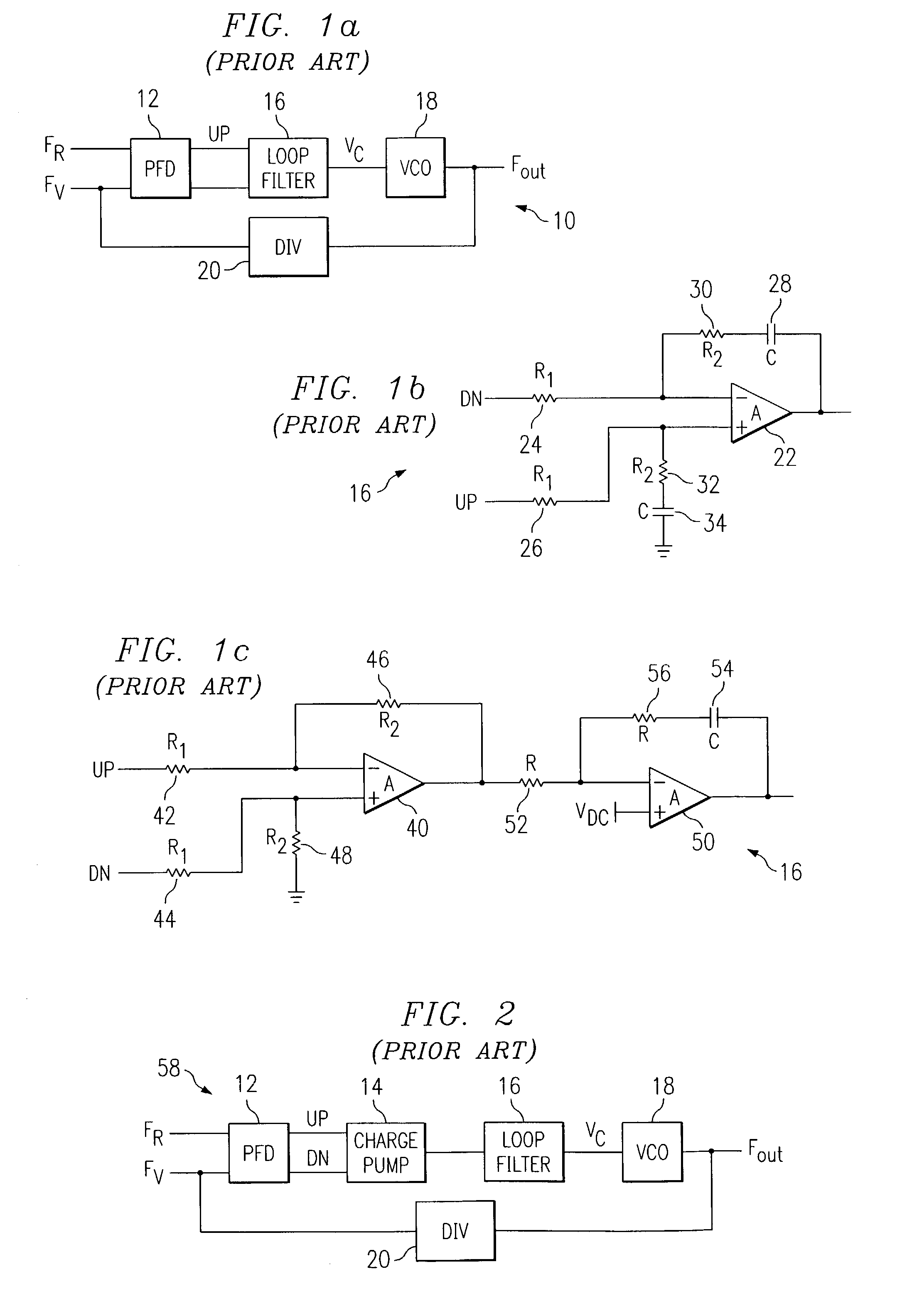

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

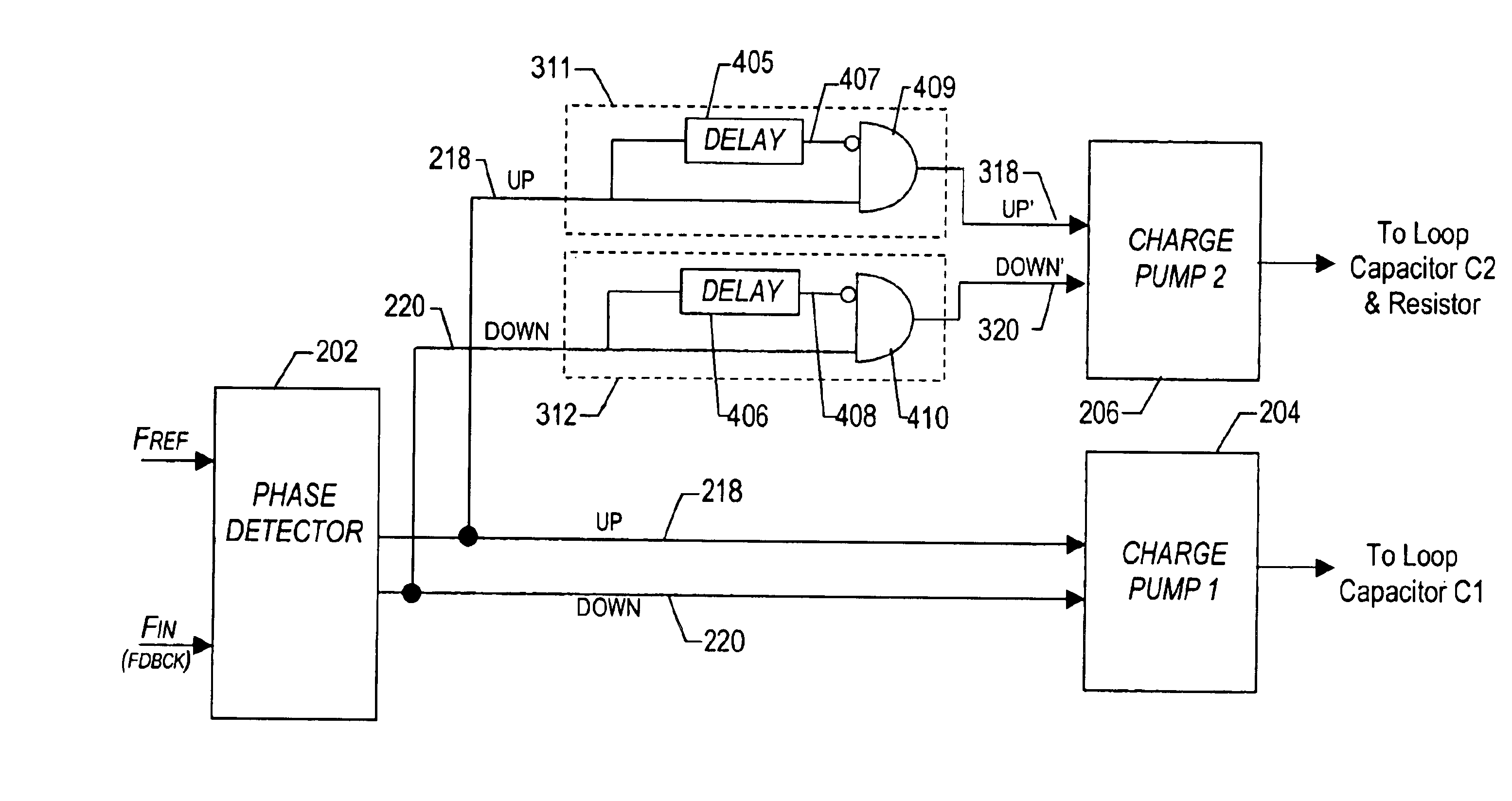

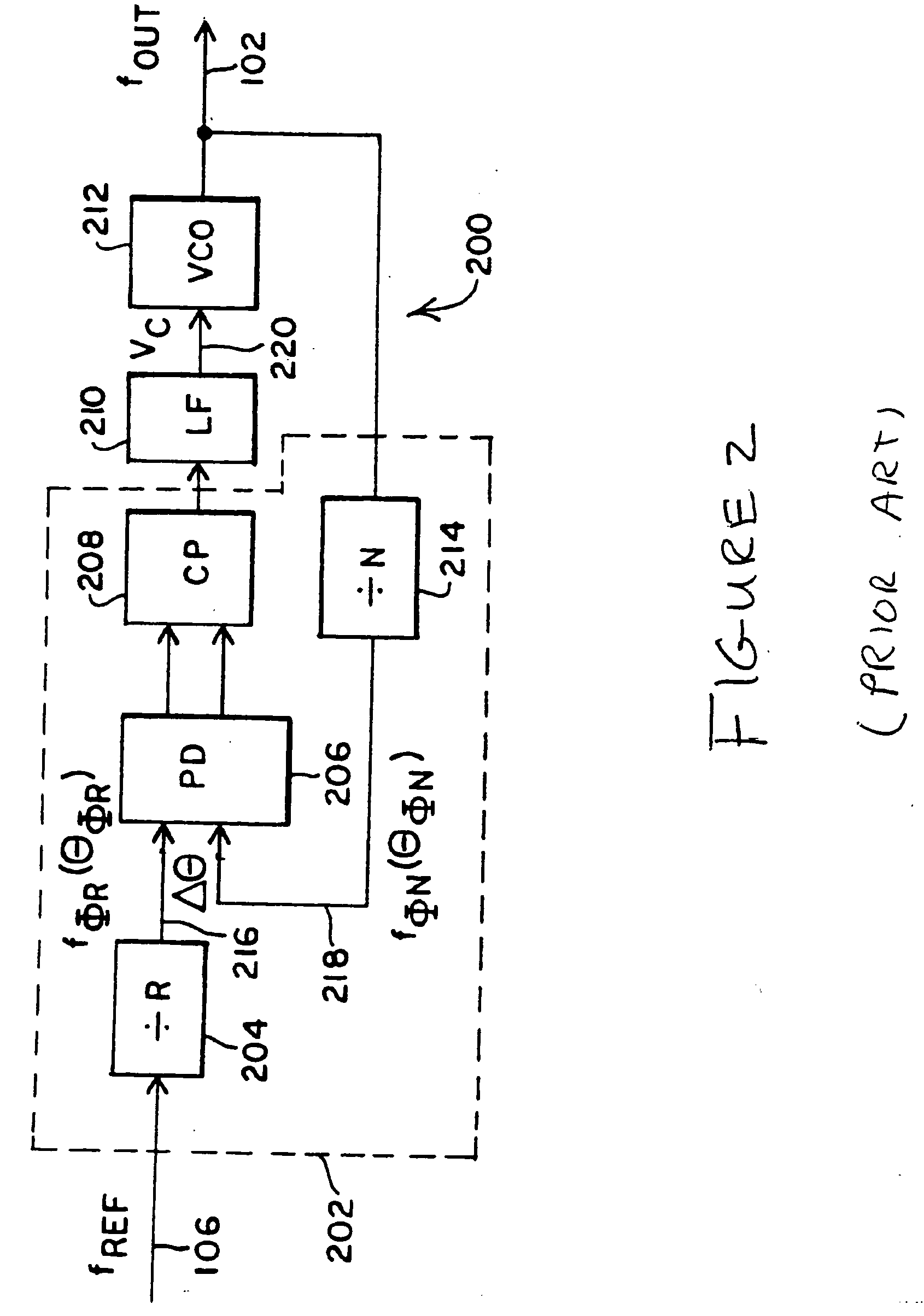

Method and apparatus for reducing lock time in dual charge-pump phase-locked loops

InactiveUS6937075B2Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorControl signal

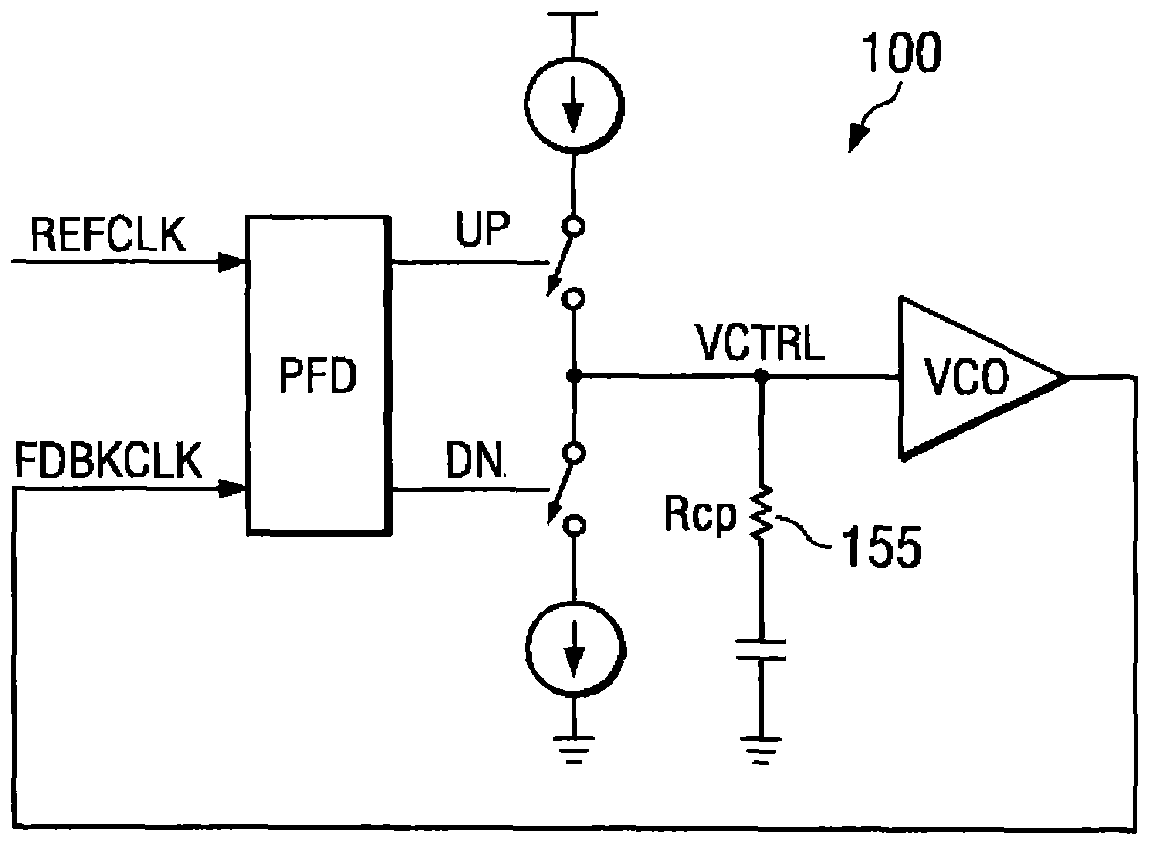

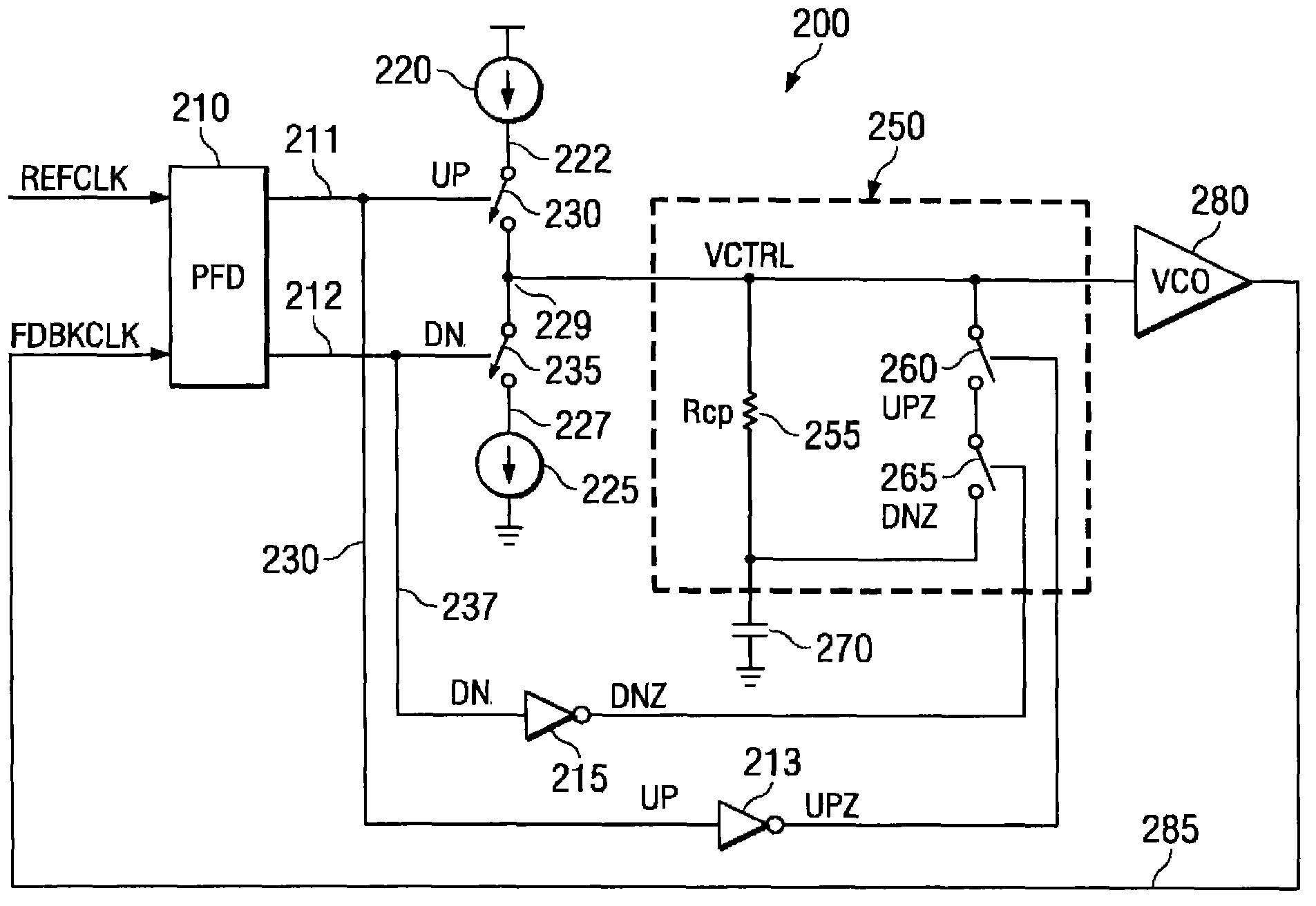

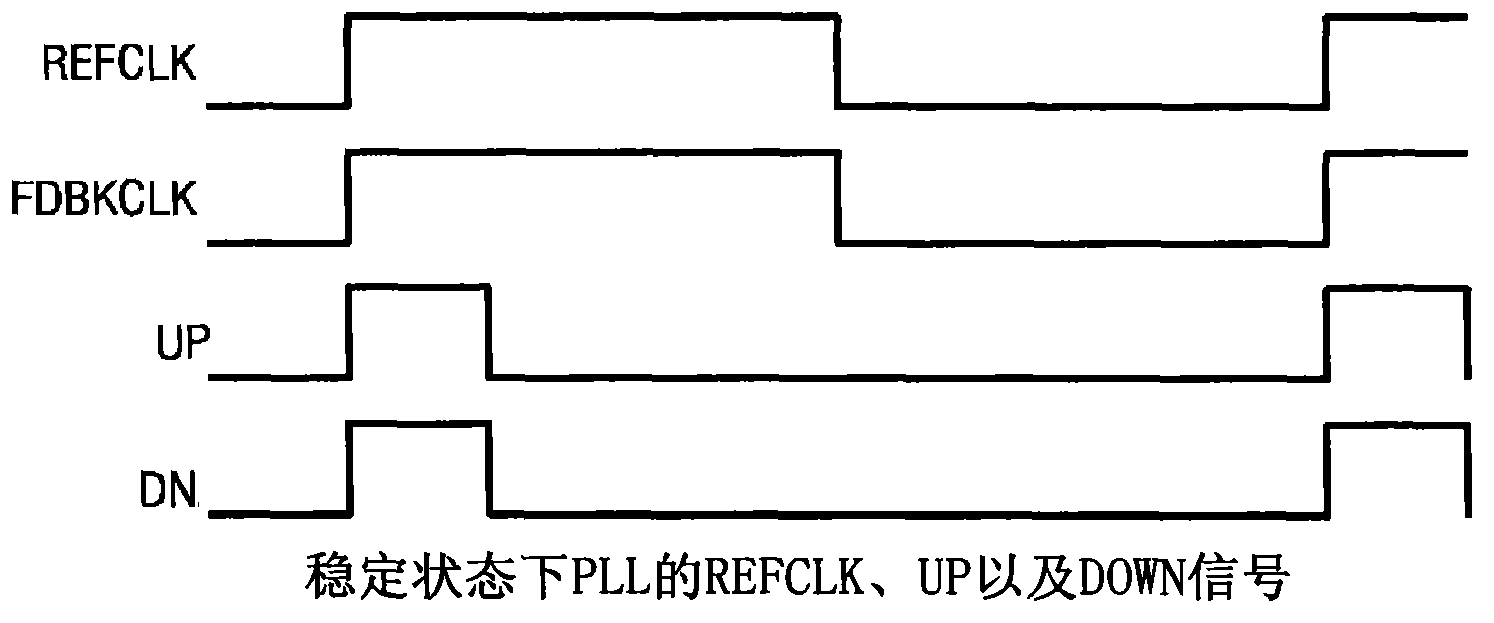

A phase-locked loop includes a phase detector to measure a phase offset between a reference clock signal and a feedback clock signal, and to generate first and second output control signals having a pulse width corresponding to the phase offset. The phase locked loop further includes a first pulse width control circuit coupled to the phase detector to reduce the pulse width of the first output control signal producing a first modified output control signal, a second pulse width control circuit coupled to the phase detector to reduce the pulse width of the second output control signal producing a second modified output control signal, a first charge pump coupled to the phase detector to provide a first charge signal responsive to the first and second output control signals, and a second charge pump coupled to the first and second pulse width control circuits to provide a second charge signal responsive to the first and second modified output control signals.

Owner:INTEL CORP

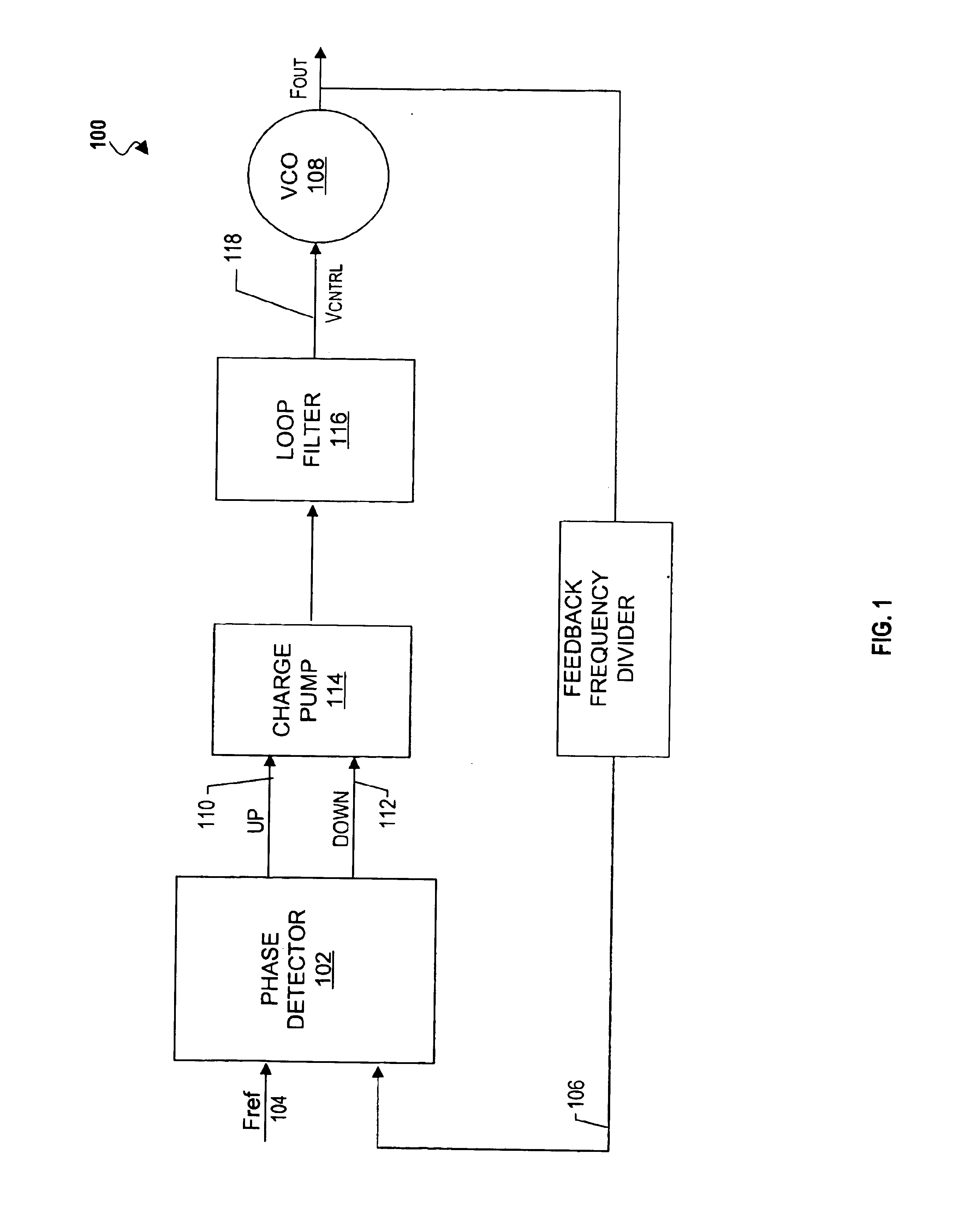

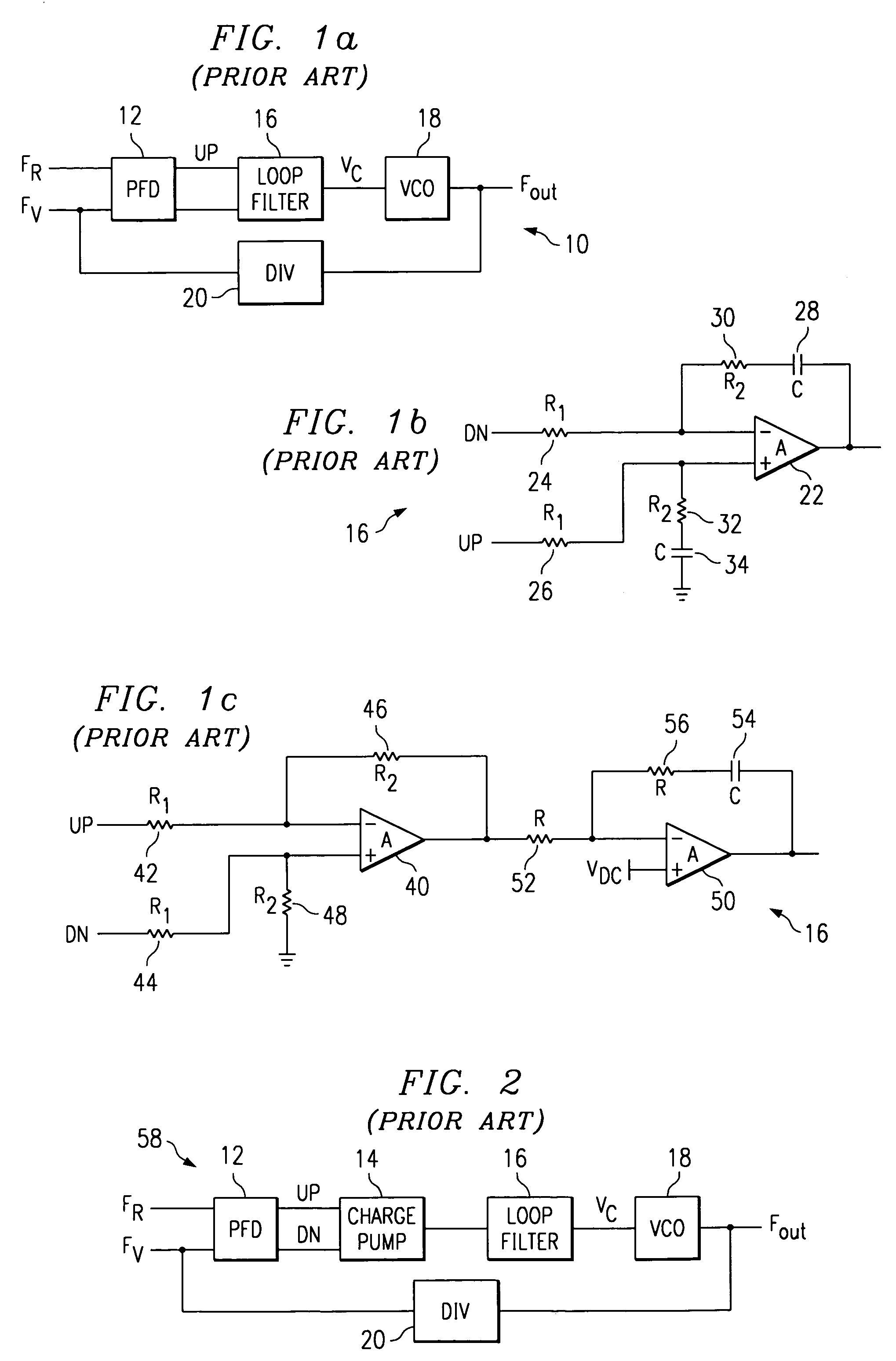

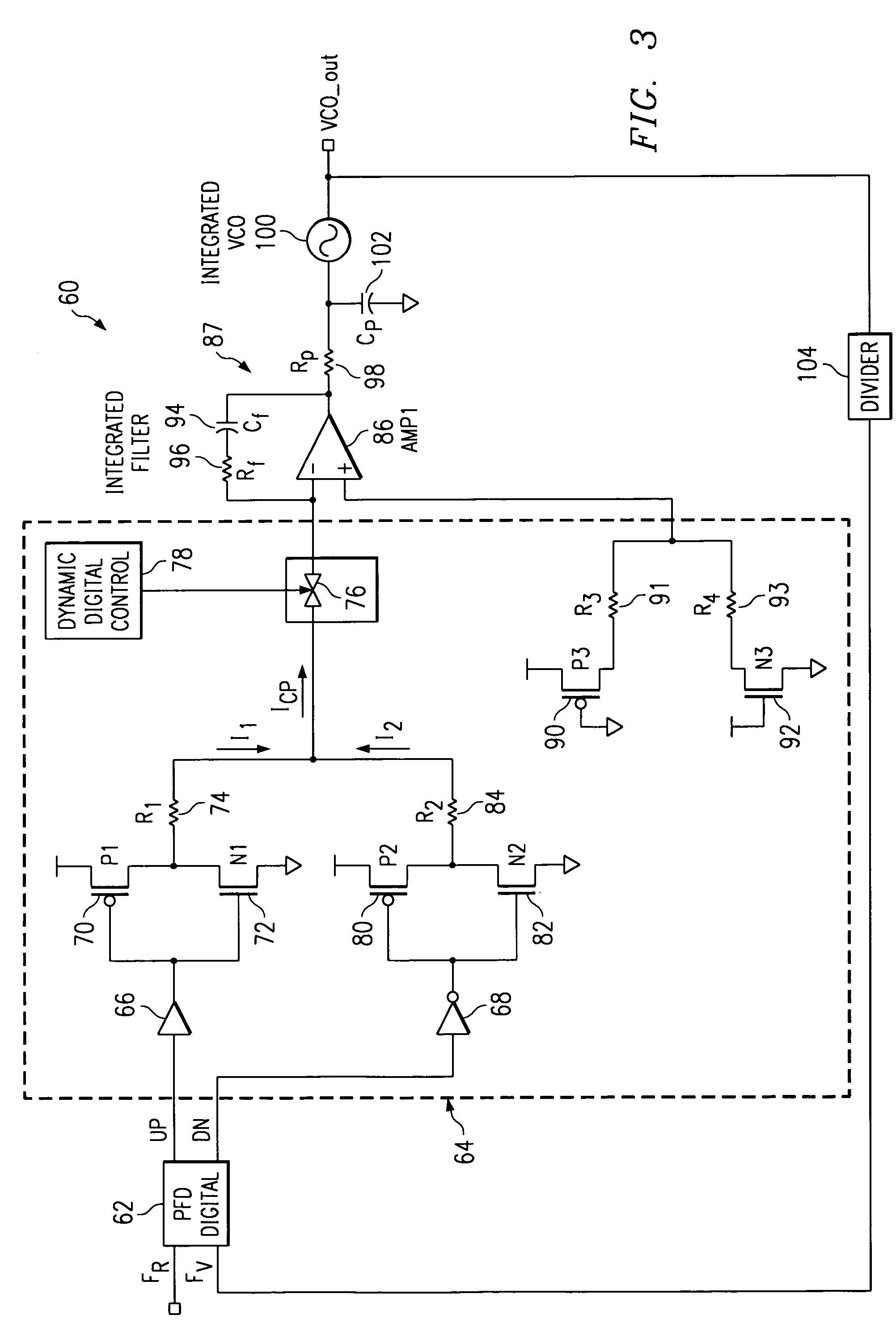

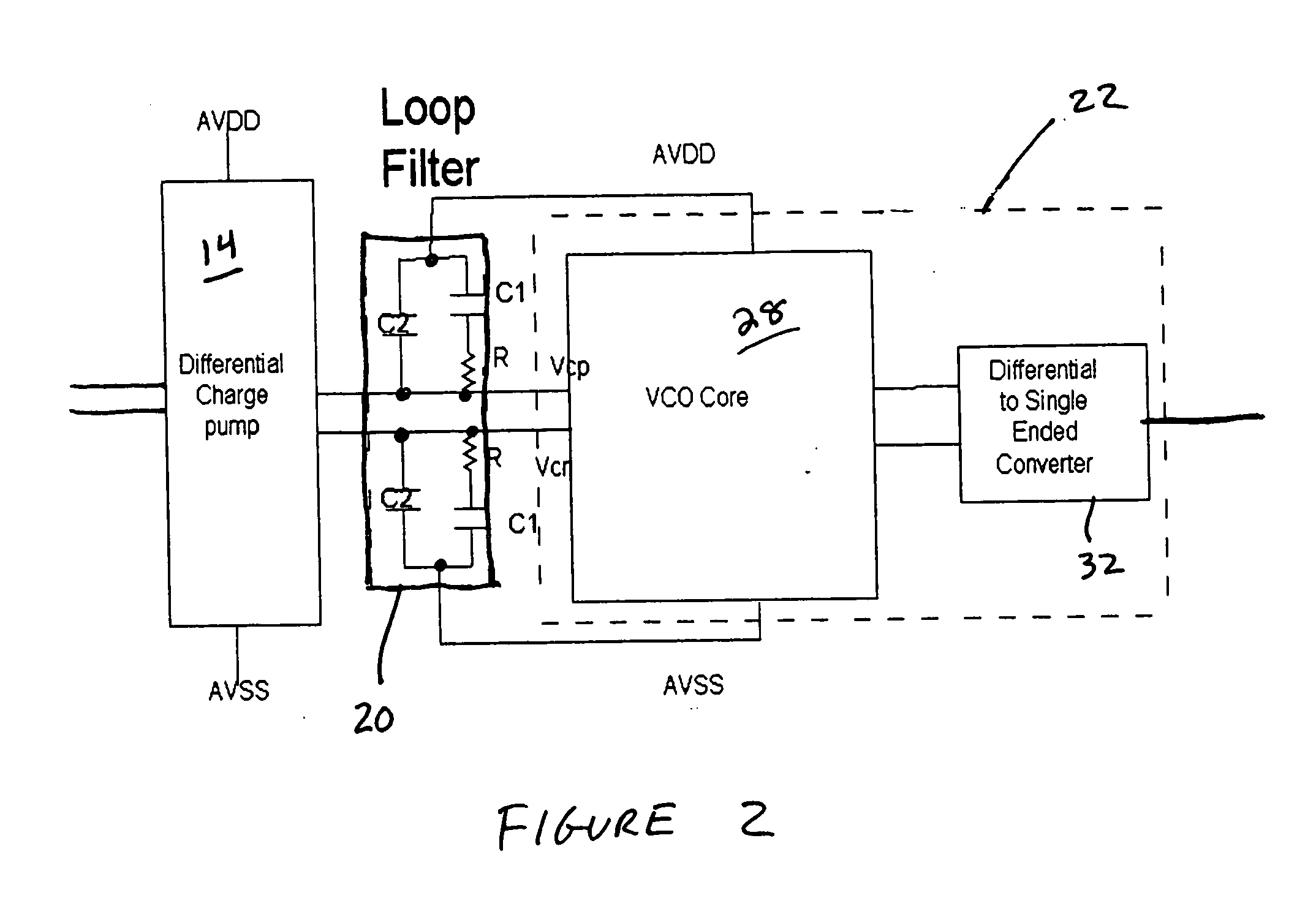

Charge pump phase locked loop with improved power supply rejection

ActiveUS6963233B2Improve power supply rejection ratioVoltage variationPulse automatic controlElectric variable regulationPhase detectorElectricity

A phase lock loop circuit (60) has a phase frequency detector (62), a charge pump (64), an active filter (87) and a voltage-controlled oscillator (100). The phase detector generates signals responsive to reference signal FR and VCO output signal FV. A charge pump generates a voltage at the input of a first transmission gate (76) according to the values of the phase detector signals. A predetermined voltage is generated at the input of a second transmission gate (112). When the transmission gates (76, 110) are closed (low impedance) the charge pump may sink or source current to the inverting input of the operational amplifier (86) of the active filter 86 and the predetermined voltage is applied to the non-inverting input. When the transmission gates are open (high impedance state) the inverting input is electrically isolated from the node and the non-inverting output is isolated from the power supply.

Owner:TEXAS INSTR INC

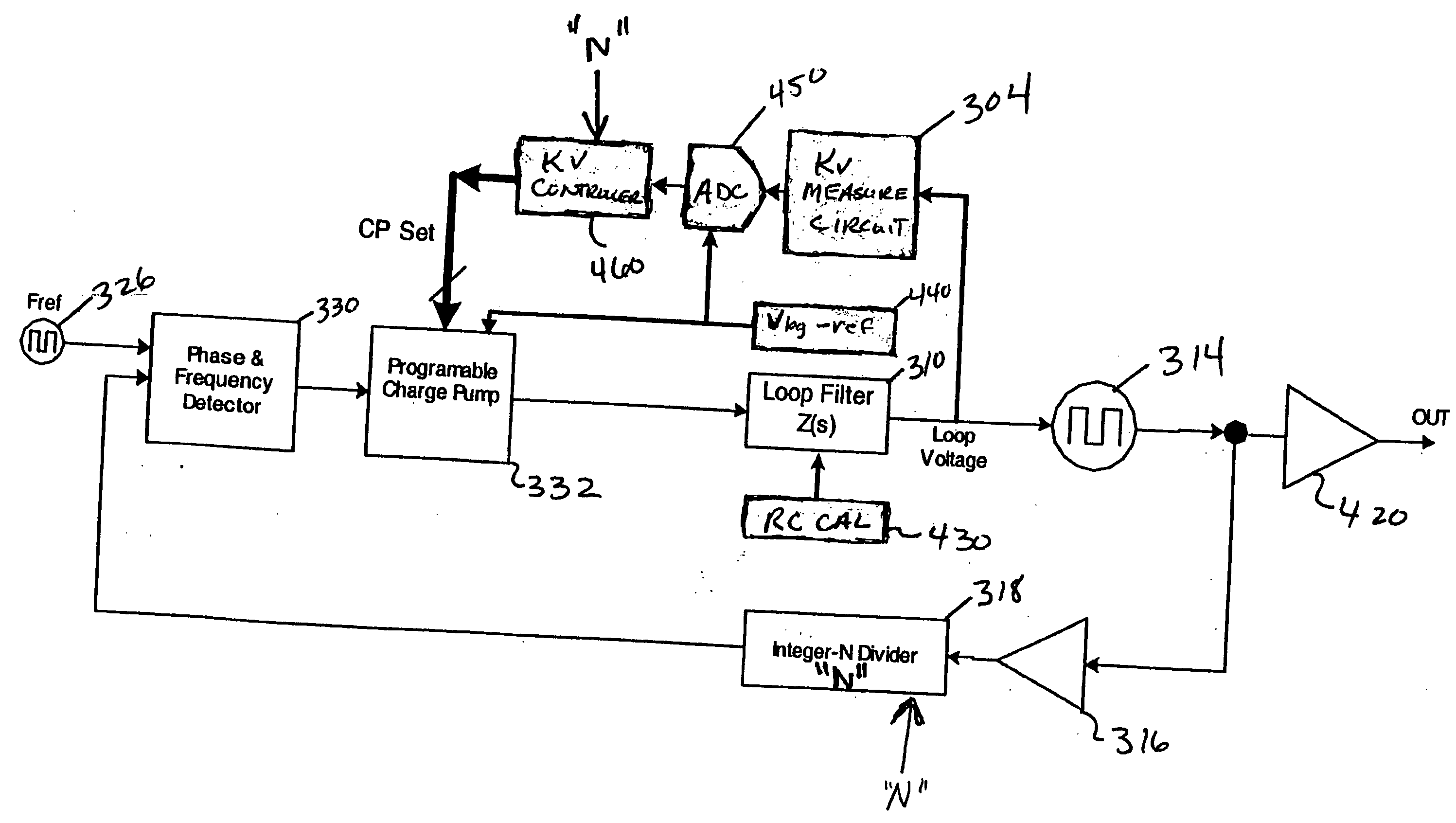

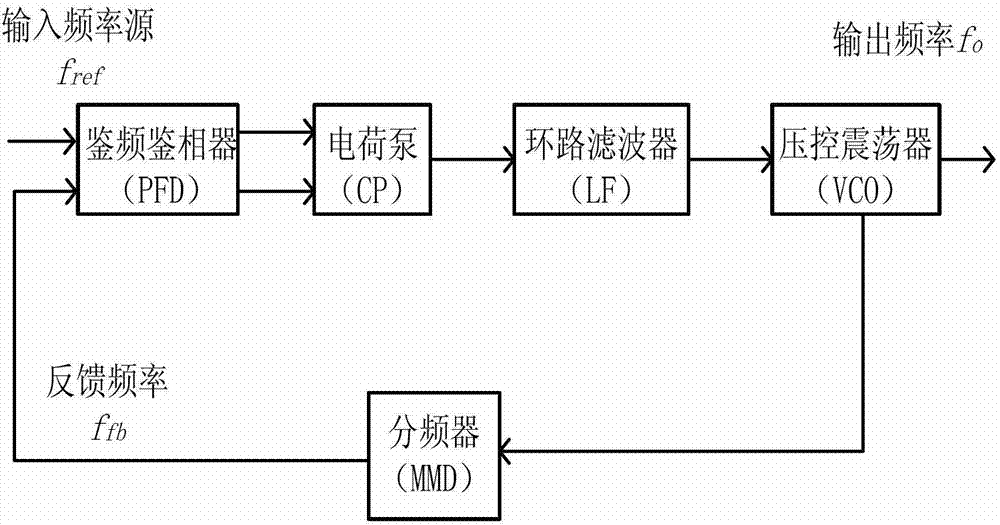

Phase-locked loop bandwidth calibration circuit and method thereof

ActiveUS20050073369A1Adjustable levelModulated-carrier systemsPulse automatic controlFrequency synthesizerEngineering

A phase-locked loop frequency synthesizer has a charge pump, phase-locked loop filter, voltage-controlled oscillator, and a bandwidth calibration circuit. The bandwidth calibration circuit measures the gain of the voltage-controlled oscillator and uses the measured voltage-controlled oscillator gain to adjust the charge pump level. The charge pump level is adjusted so that a product of the voltage-controlled oscillator gain and the measured charge pump level results in a constant phase-locked loop bandwidth.

Owner:MEDIATEK INC

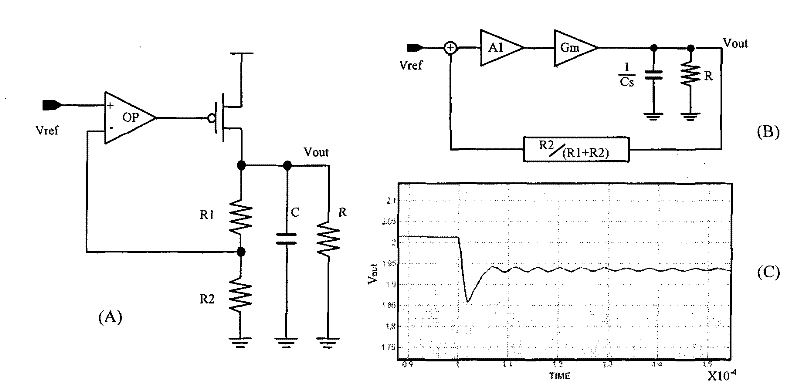

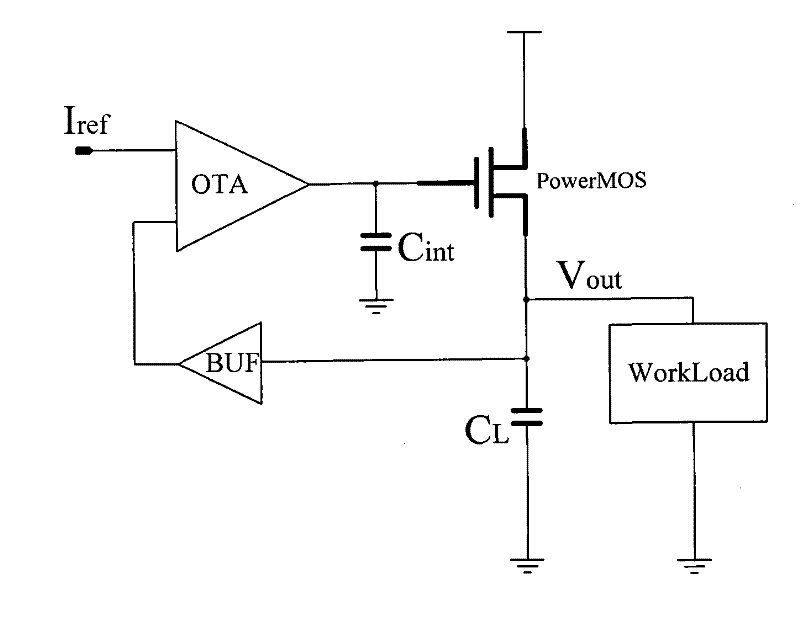

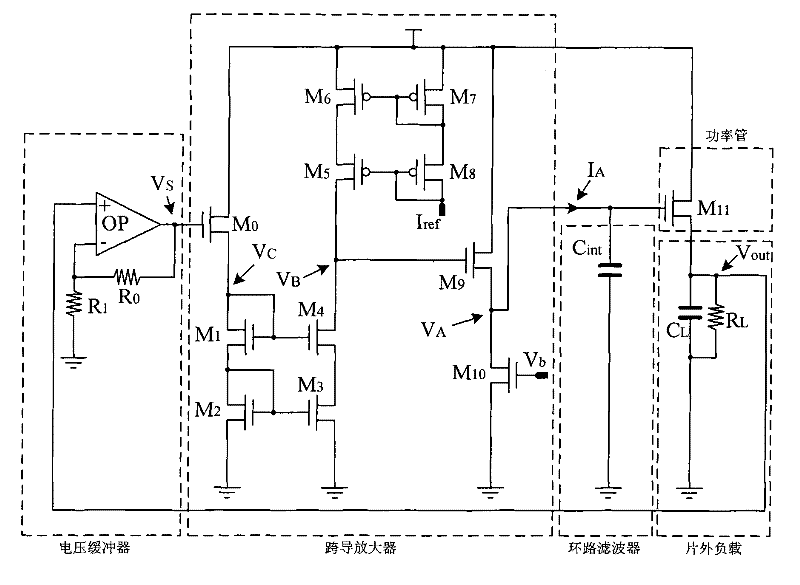

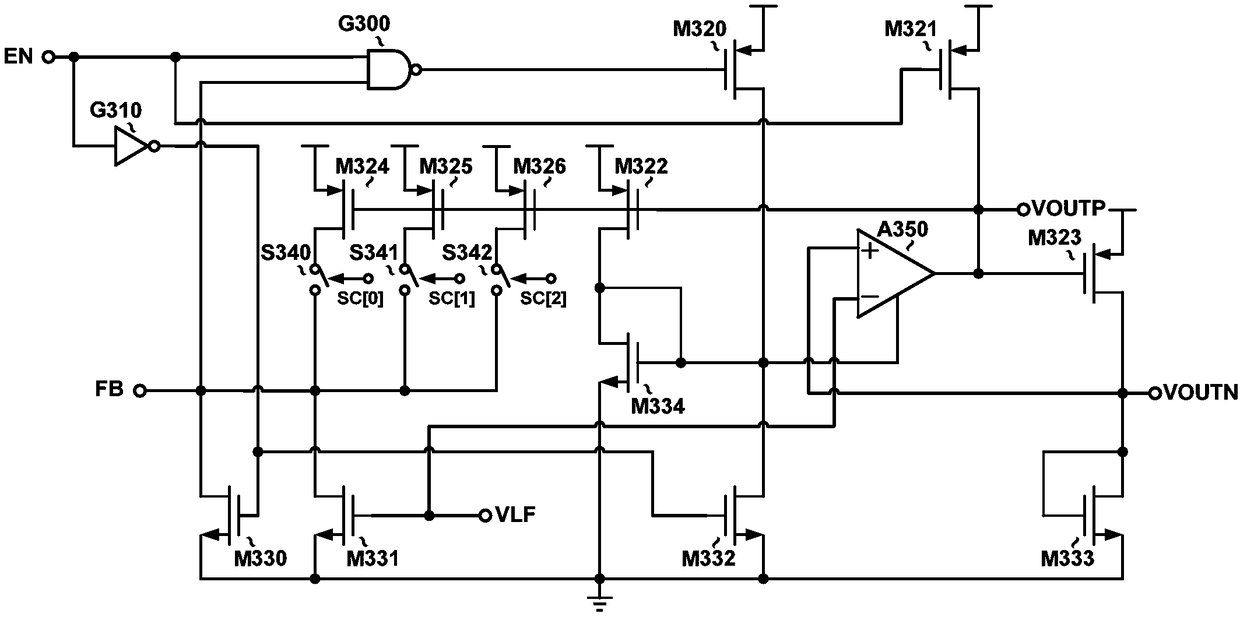

Low Output Voltage Fast Response LDO Circuit Based on Current Control Loop

InactiveCN102298407AGuaranteed response speedImprove stabilityElectric variable regulationElectricityIntegrator

The response ability to the transient change of the load is an important indicator of the LDO performance of the low dropout voltage regulator. The present invention learns from the loop control method of the charge pump type phase-locked loop, discloses a low output voltage fast response LDO structure based on the current control loop, the feedback voltage is converted into current, and the current signal is used as the carrier in the control loop. Operation, the difference current is integrated by the loop filter to form the control voltage of the power tube. Low-dropout regulators based on current control loops respond well to load transients and can produce voltage outputs lower than typical bandgap reference voltages. The fast-response LDO circuit based on the current control loop disclosed by the invention is composed of a voltage buffer, a transconductance amplifier, a loop filter, a power tube and an off-chip load.

Owner:NAT UNIV OF DEFENSE TECH

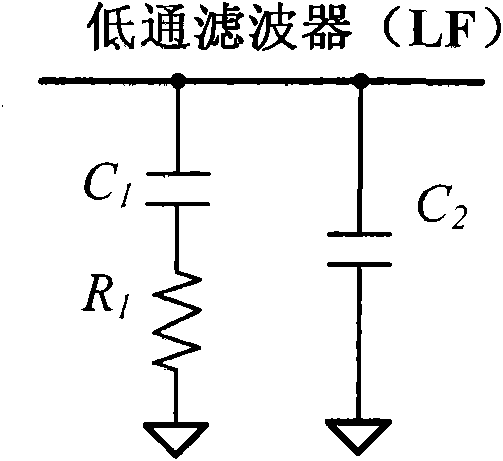

Loop filter circuit for charge pump phase-locked loop

InactiveCN101409554AImprove performanceTroubleshoot reference spursPulse automatic controlElectronic switchingDiscriminatorTime delays

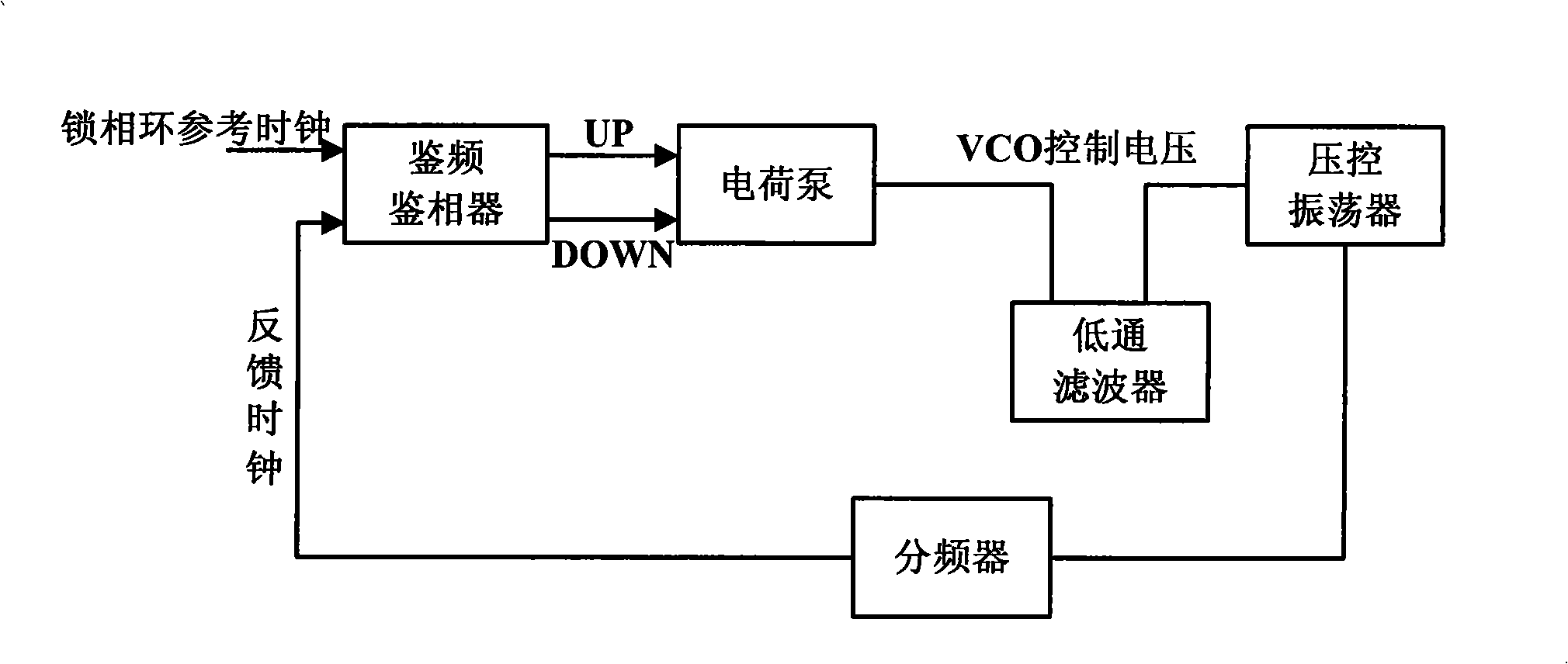

The invention provides a loop filter circuit used in a charge pump phase-locked loop. The charge pump phase-locked loop comprises a frequency and phase discriminator, a charge pump, a loop filter, a frequency divider and a voltage-controlled oscillator; the front end of the loop filter is connected with the charge pump and the rear end is connected with the voltage-controlled oscillator; the loop filter circuit comprises a control logic, a front buffer circuit, a time delay switch and a rear filter circuit; when the time delay switch is conducted, the whole loop filter circuit can operate normally; but when the time delay switch is off, the charge pump is conducted with the front buffer circuit and is not conducted with the rear filter circuit; the time delay circuit of the time delay switch refers delays time of the clock, and the on-off of the time delay switch is controlled by the control logic of the loop filter circuit; by adopting the circuit, the problem of stray reference caused by the mismatching of the upper and lower branch currents in the charge pump is solved, and the performance of the loop filter circuit of the charge pump phase-locked loop is improved.

Owner:BEIJING RFMC TECH CORP

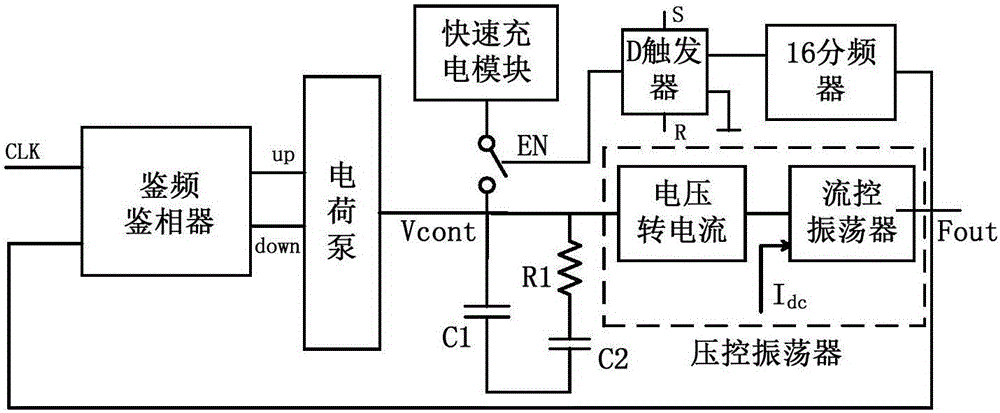

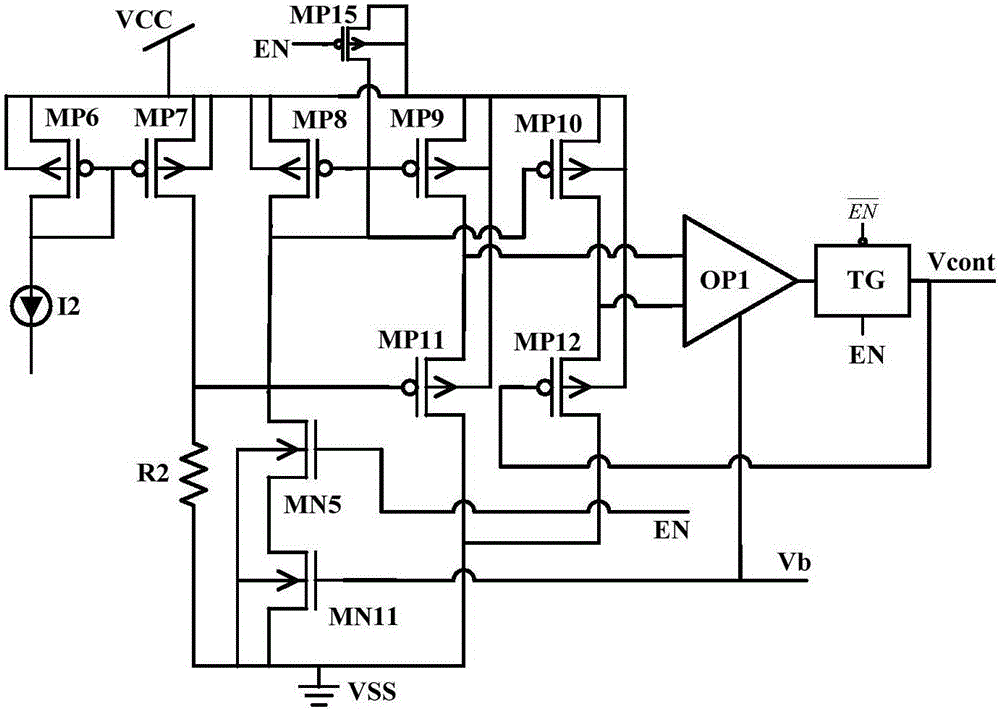

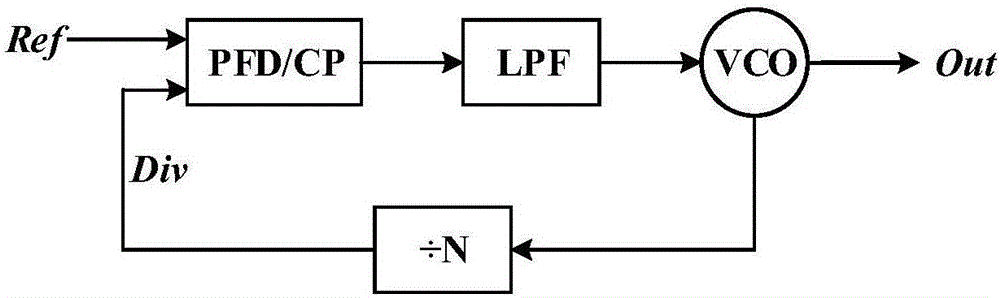

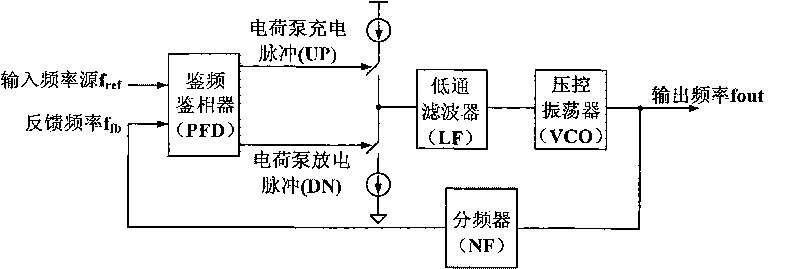

Quick starting circuit for charge pump phase-locked loop

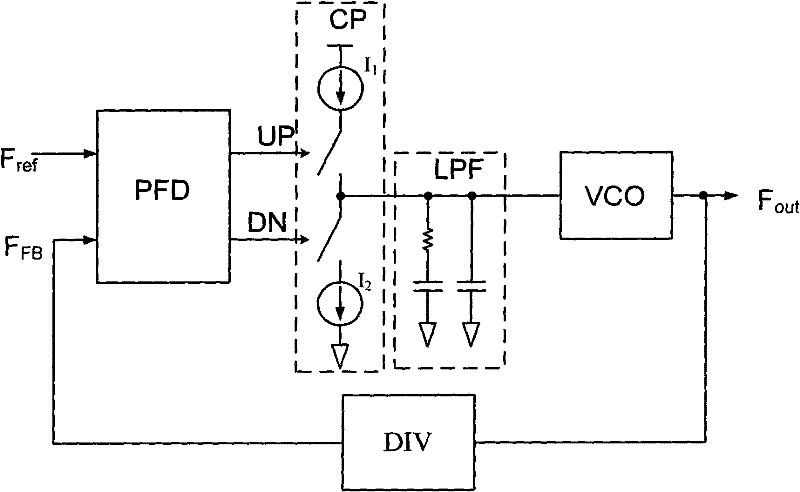

The invention belongs to the technical field of an electronic circuit and specifically relates to a quick starting circuit for a charge pump phase-locked loop. The quick starting circuit comprises a phase-frequency detector, a rapid charging module, a charge pump, a low-pass filter, a voltage-controlled oscillator and a frequency divider. The phase-frequency detector is connected with an external clock signal, the input end thereof is connected with the output end of the voltage-controlled oscillator, the first output end thereof is connected with the first input end of the charge pump, and the second output end is connected with the second input end of the charge pump; the output end of the charge pump is connected with the input end of the voltage-controlled oscillator through the low-pass filter; the output end of the rapid charging module is connected with the low-pass filter through a switching tube; the output end of the voltage-controlled oscillator is connected with the input end of the frequency divider; the output end of the frequency divider outputs an enable signal through a D trigger; and the enable signal is connected to the control end of the switching tube. The circuit has the beneficial effect of providing the charge pump phase-locked loop capable of rapidly locking.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

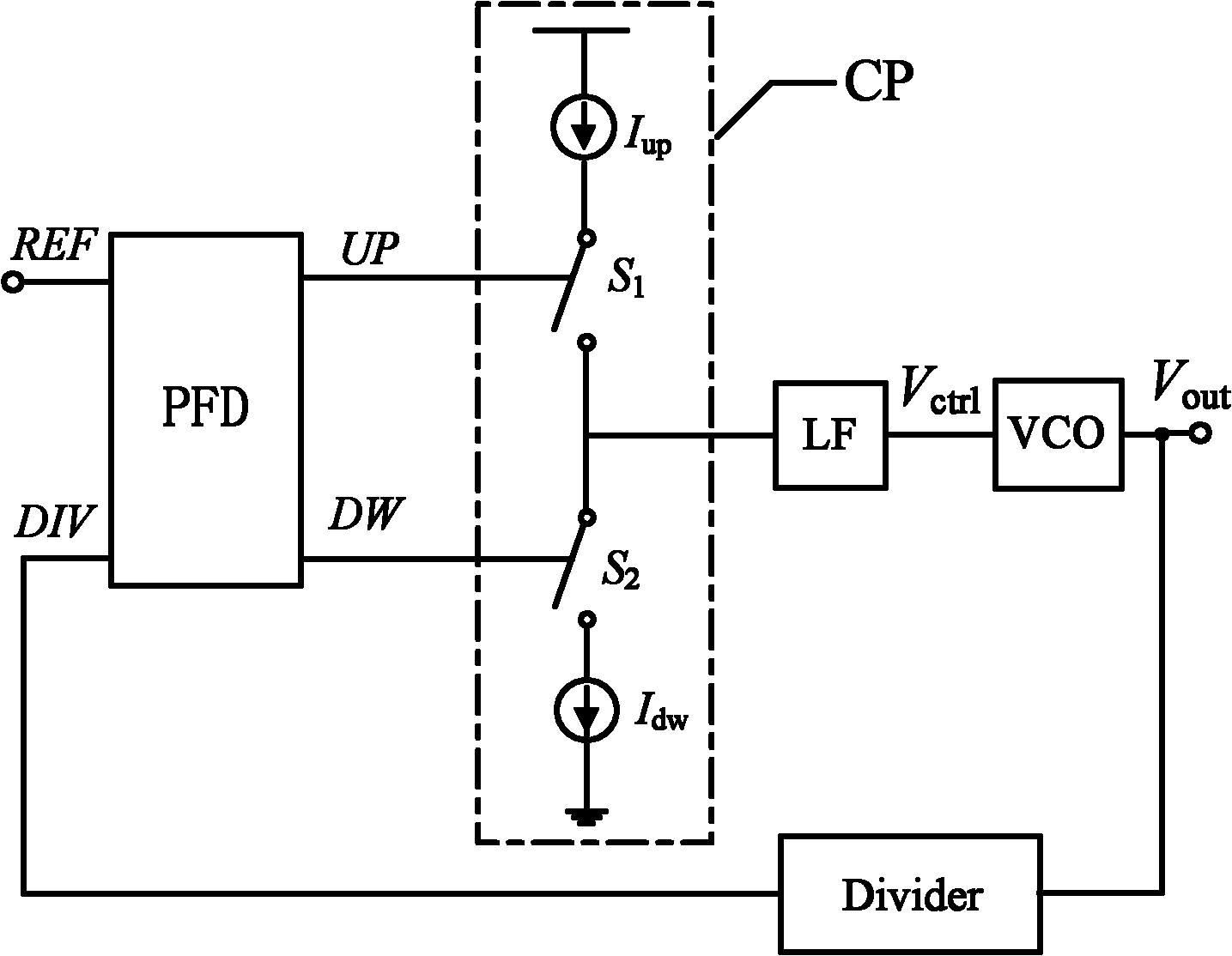

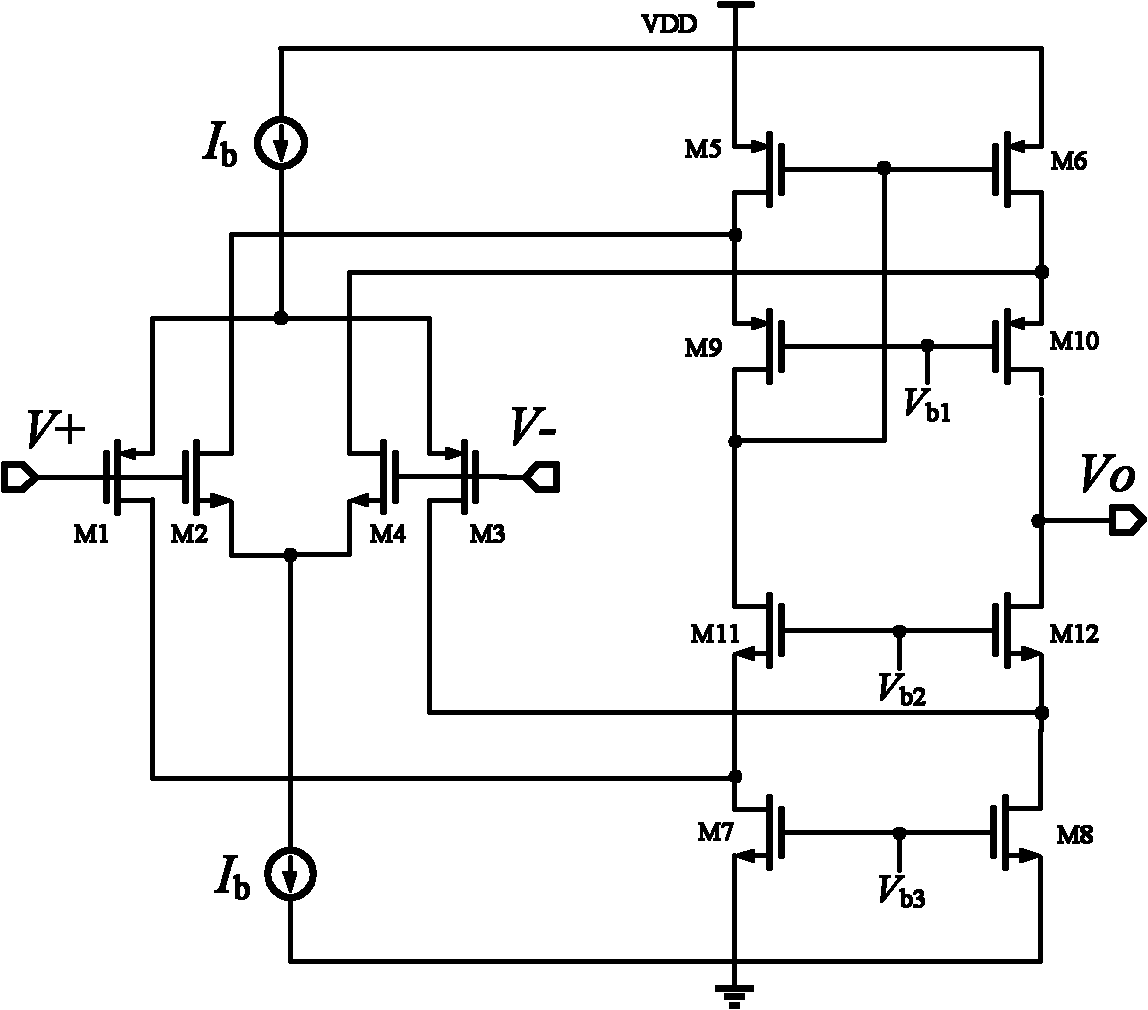

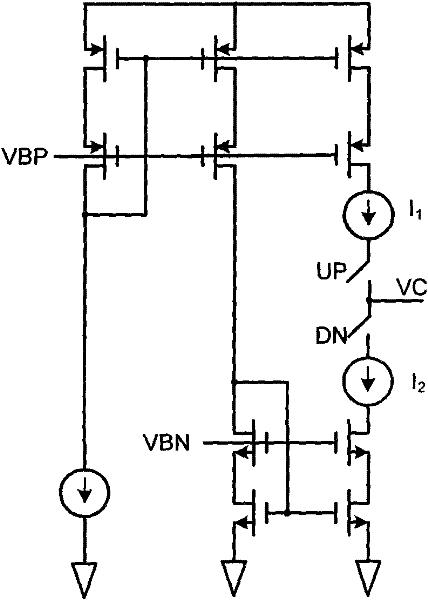

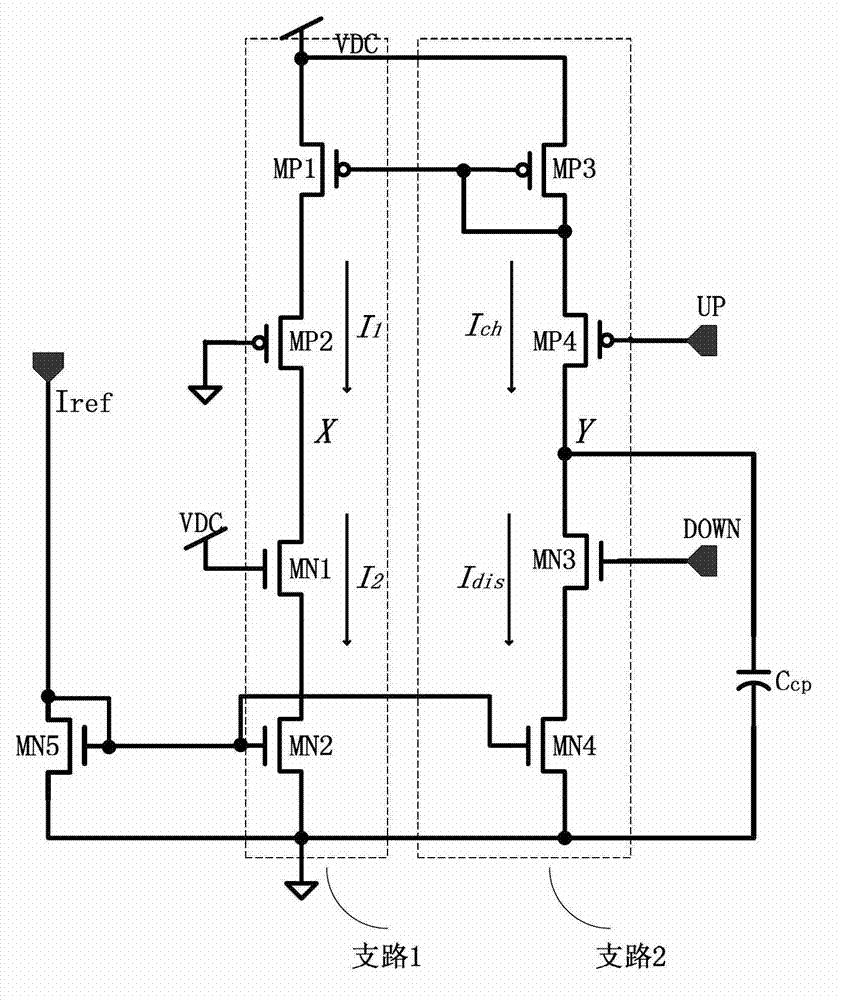

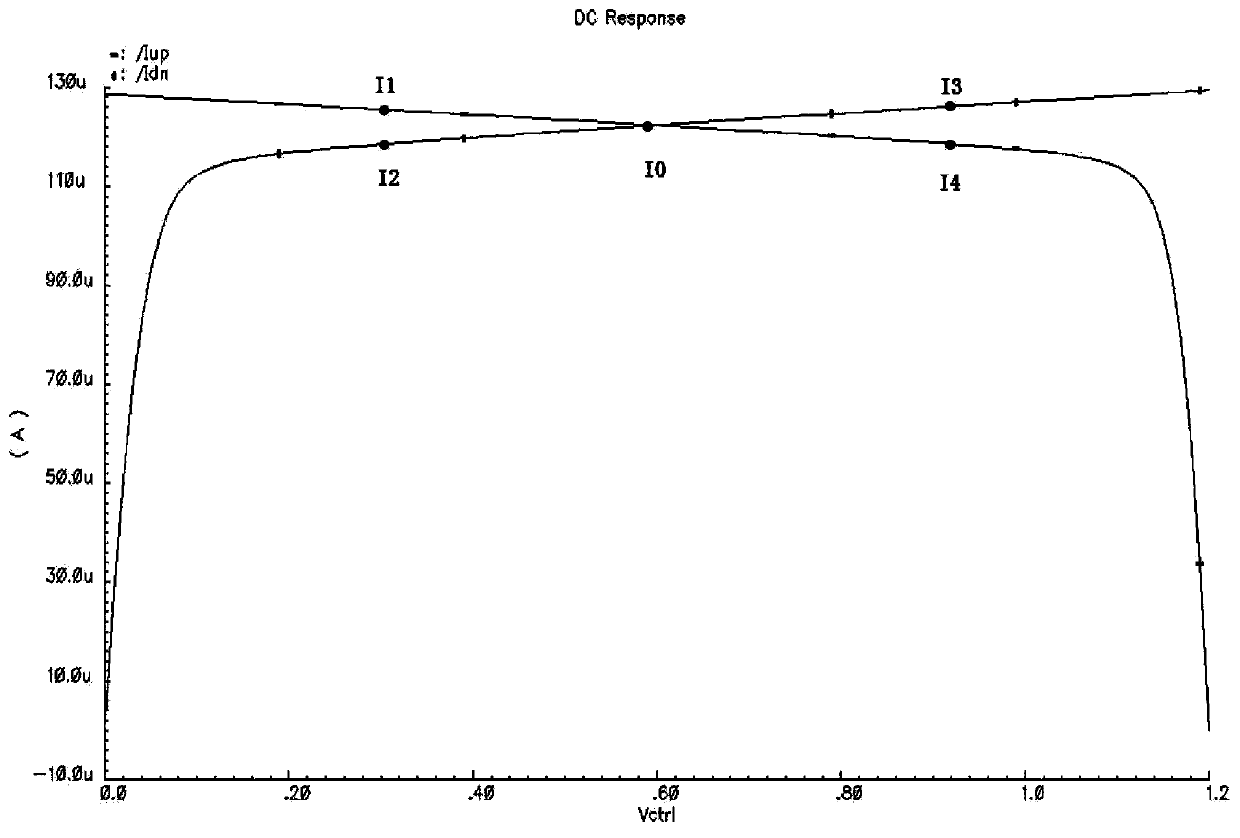

Charge pump circuit in charge pump phase-locking loop

InactiveCN102158075AIncrease charging currentReduced settling timePulse automatic controlApparatus without intermediate ac conversionReference currentEngineering

The invention relates to a charge pump circuit in a charge pump phase-locking loop, which is provided with an automatic bias current mirror circuit, a charging and discharging circuit, a copy circuit, a precharging bias circuit and a rail-to-rail operational amplification circuit. The automatic bias current mirror circuit is provided with a resistor R, three MOS (Metal Oxide Semiconductor) pipes and a reference current source. The charging and discharging circuit is provided with a charging and discharging current source consisting of a charging and discharging switch pipe and four MOS (MetalOxide Semiconductor) pipes. The copy circuit is copied from a charging and discharging circuit structure, and corresponding transistor sizes are correspondingly equal. The precharging bias circuit isprovided with five MOS pipes, the input end of the rail-to-rail operational amplification circuit is bridged between the charging and discharging circuit and the copy circuit, and the output end is connected with a charge pump charging current source.

Owner:SOUTHEAST UNIV

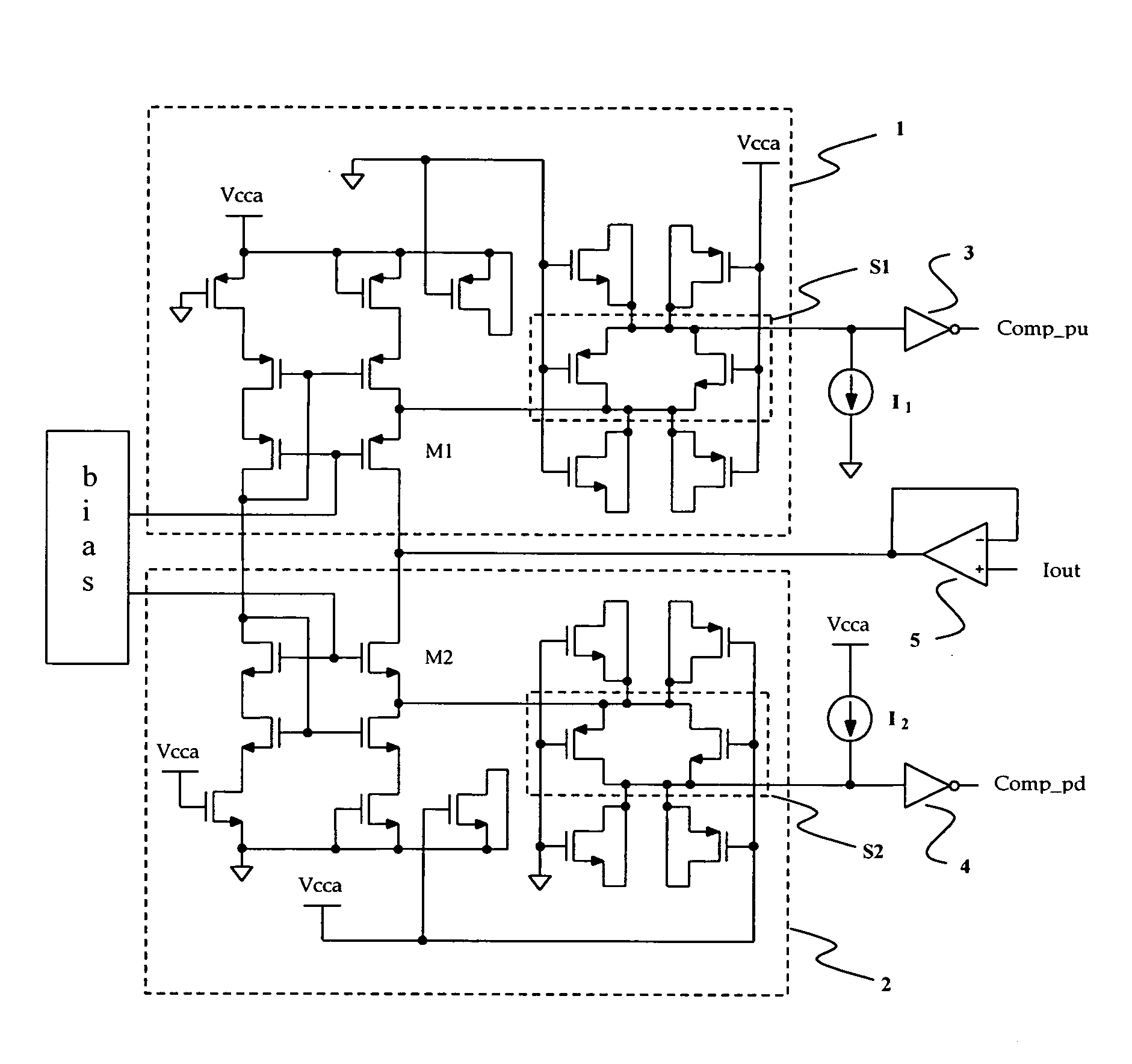

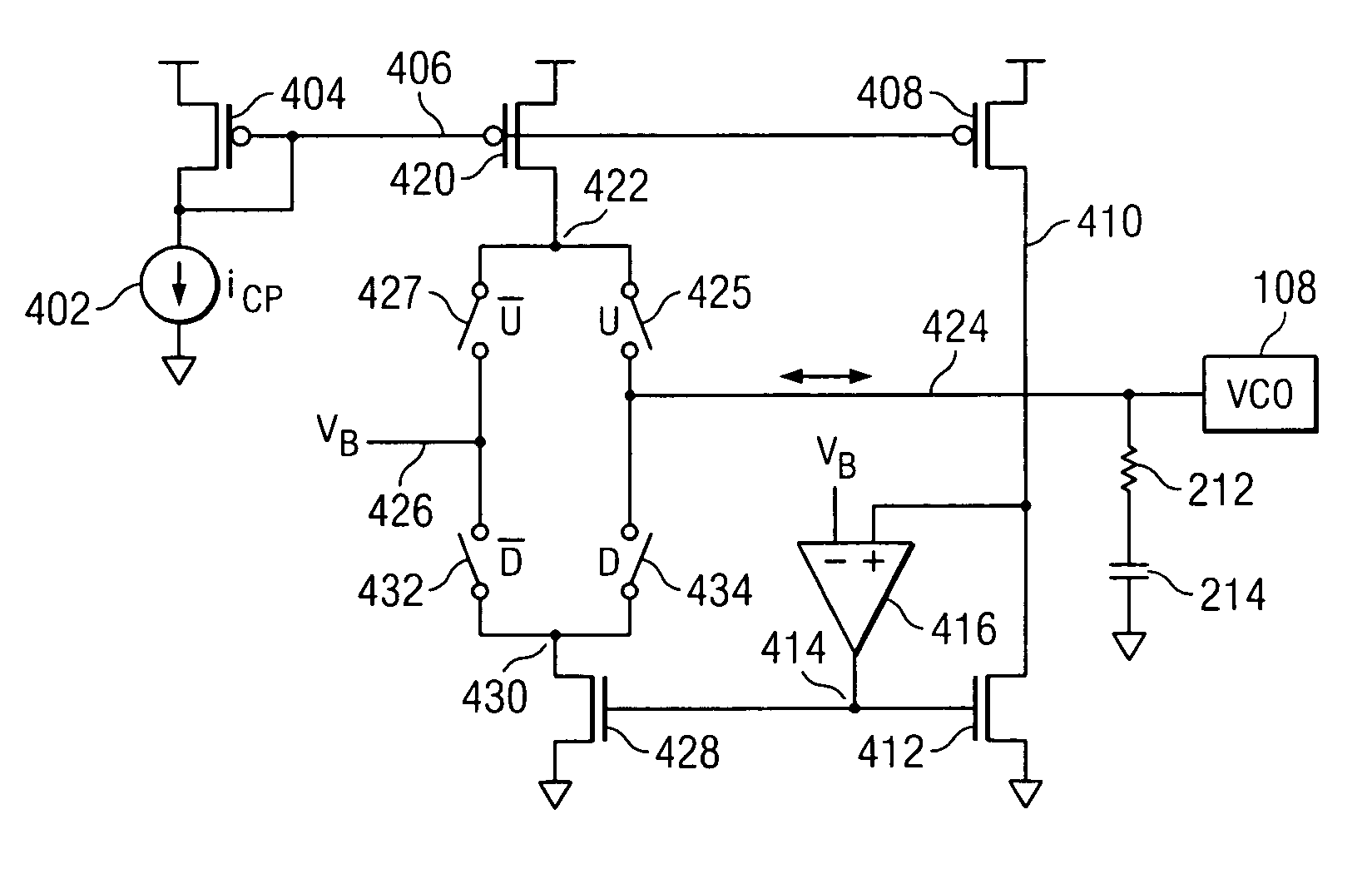

Symmetric charge pump replica bias detector

Owner:SUDJIAN DOUGLAS +1

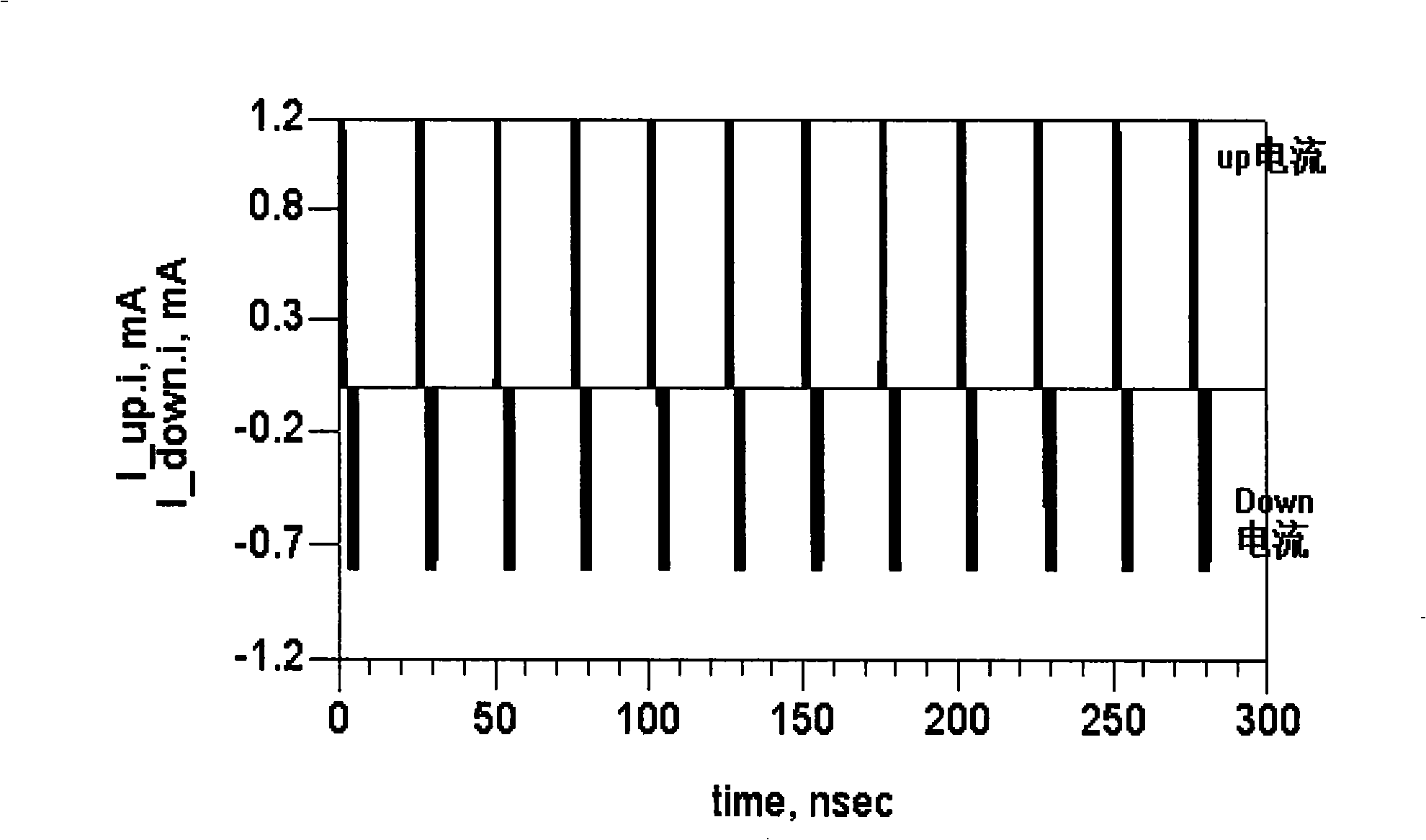

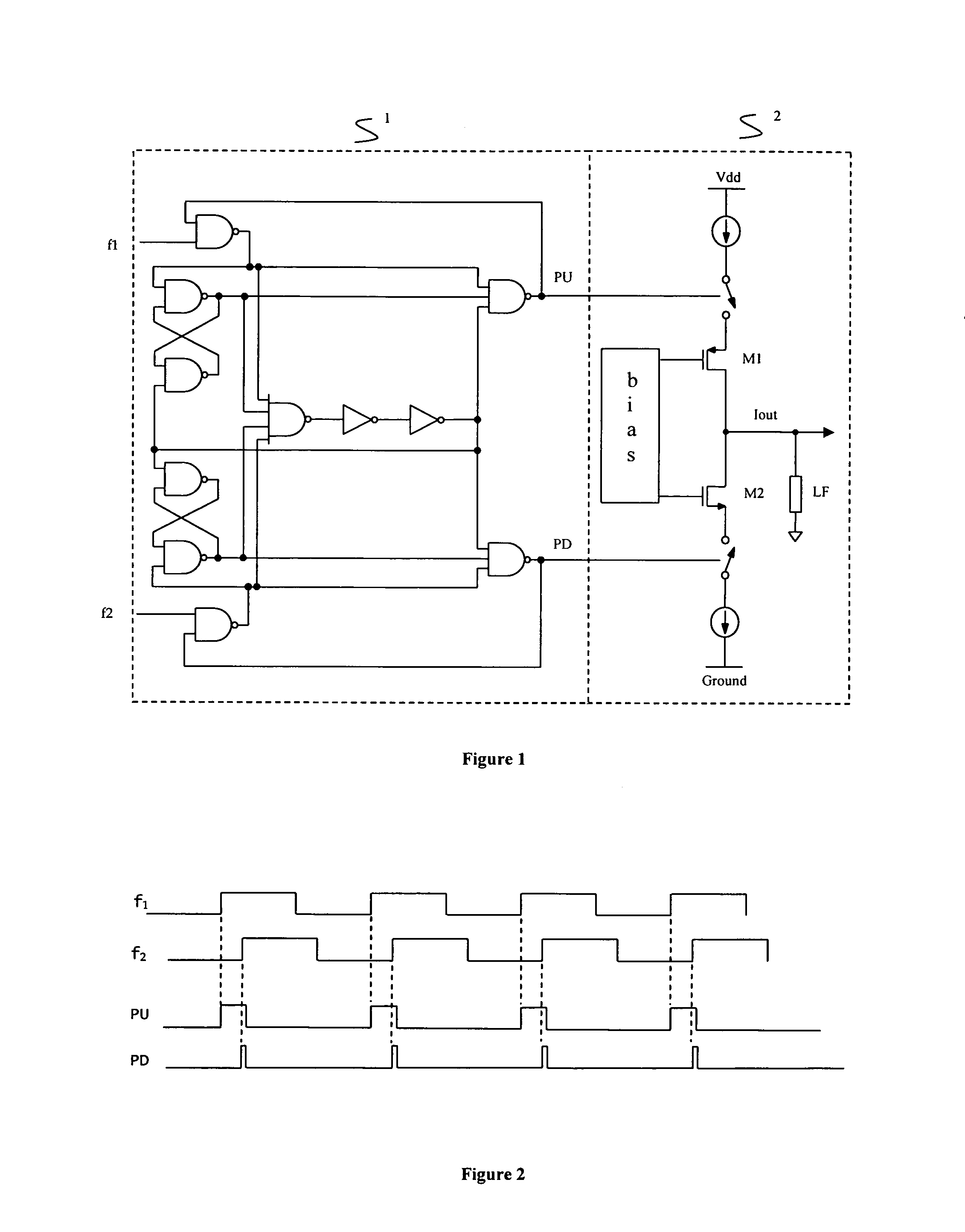

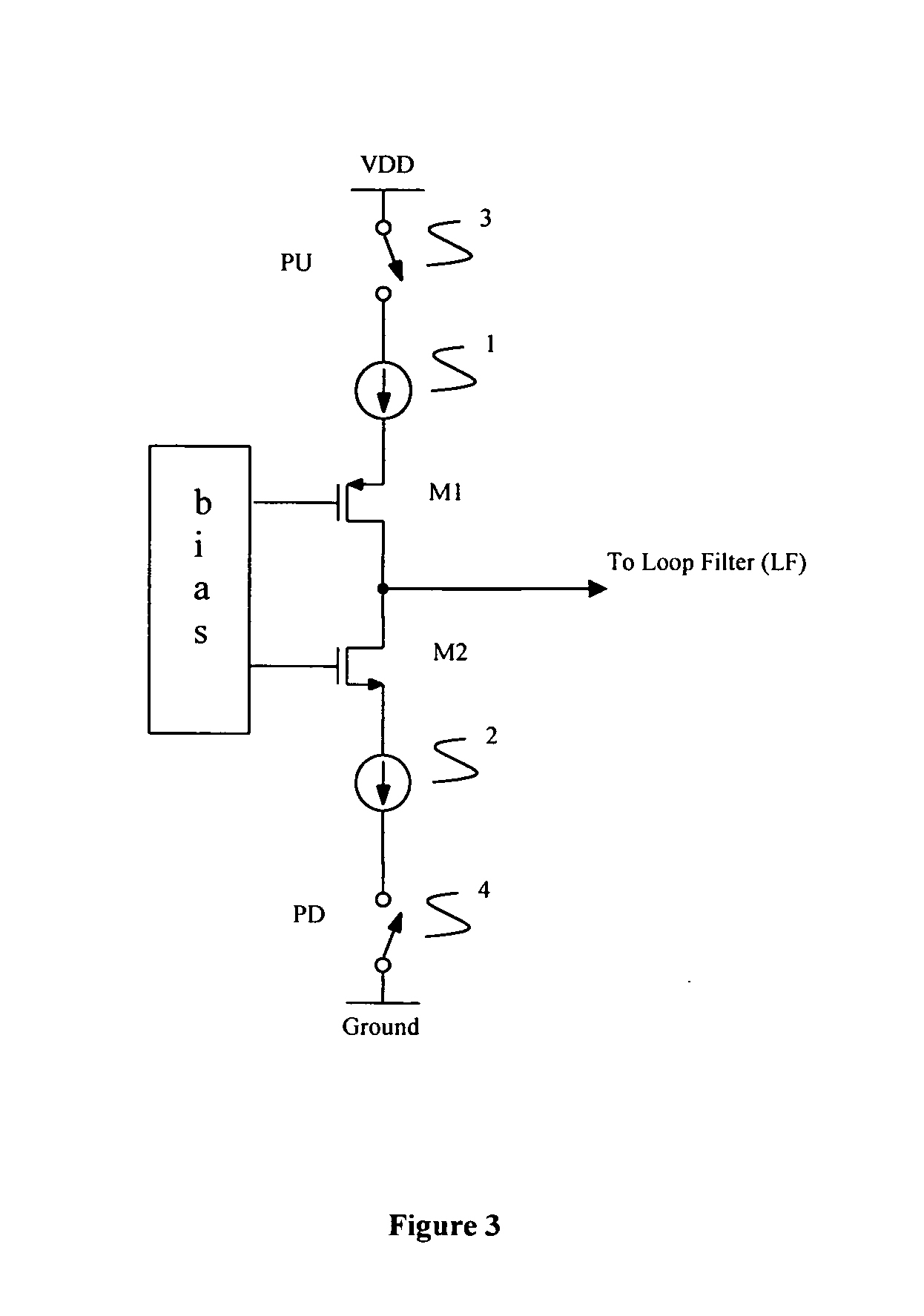

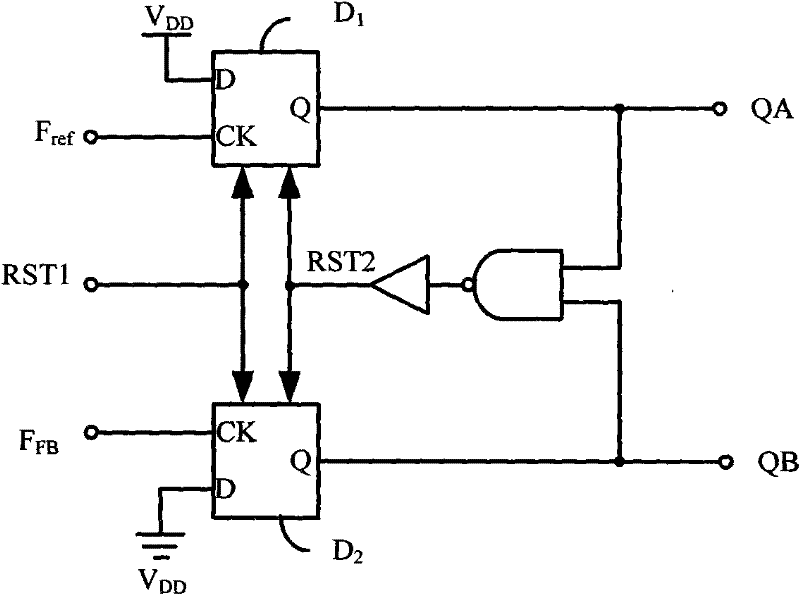

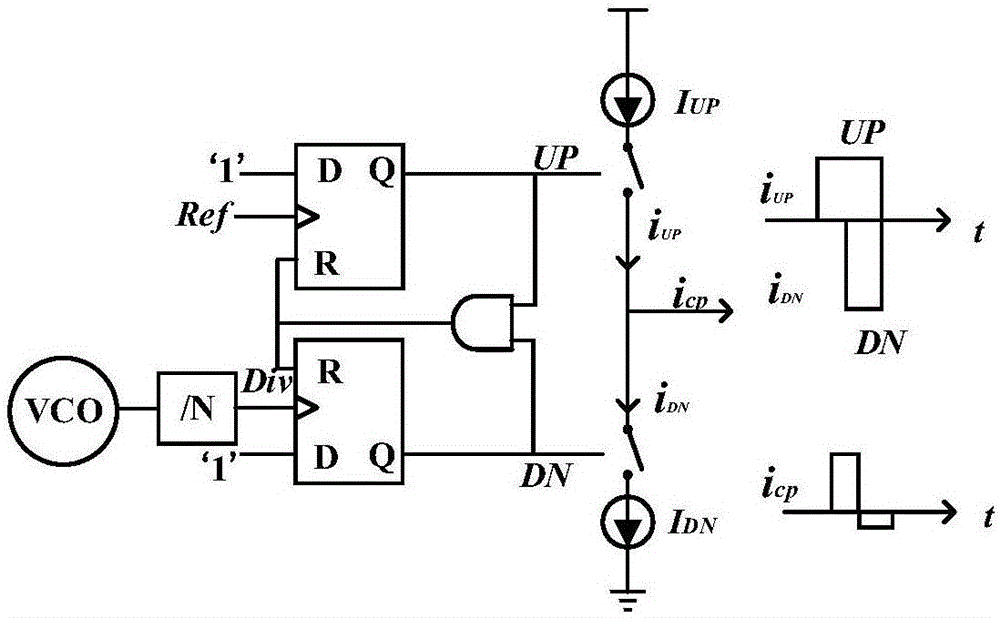

Frequency discrimination phase discriminator and method applying to phase-locked loop

The embodiment of the invention discloses a frequency discrimination phase discriminator. The phase discriminator comprises two D triggers D1 and D2, as well as a nand gate NA1 and a buffer 1, the output ends of the two D triggers D1 and D2 are utilized as an input end of the nand gate; an output end of the nand gate NA1 passes through the buffer 1 to utilize as a second reset terminal RST 2 of the two D triggers, and the output ends of the D trigger D1 and the D trigger D2 can respectively obtain signal Q1 and Q2; and the phase discriminator also comprises a timing control unit, the signals Q1 and Q2 are input signals of the timing control unit, and the timing control unit is used for controlling phase and pulse width of an output signal of the frequency discrimination phase discriminator. The invention also discloses a charge pump phase locked loop applying to the frequency discrimination phase discriminator and a method of a phase locked loop applying to the frequency discrimination phase discriminator. The technical scheme of the phase discriminator and the phase locked loop and the method can effectively avoid an error caused by mismatch charge pump current through a simple circuit structure.

Owner:ARKMICRO TECH

Charge pump circuit used for charge pump phase-locked loop

InactiveCN103036422ASimple structureEasy to integratePulse automatic controlApparatus without intermediate ac conversionCapacitanceLow voltage

The invention provides a charge pump circuit used for a charge pump phase-locked loop, and belongs to the technical field of electronics. The charge pump circuit comprises a charge and discharge unit, a first complementary circuit unit, a first operational amplifier unit, a phase inverter unit, a second complementary circuit unit, a current mirror unit and a second operational amplifier unit. According to the charge pump circuit, the problems of charge and discharge current matching and charge sharing of an existing charge pump circuit are resolved, the two complementary circuit units and the two operational amplifier units are used, the two complementary circuit units achieve forward and reverse complementation for the charge and discharge unit, charge currents and discharge currents for capacitors keep constant, therefore the problem of charge and discharge current changing is resolved, capacitor voltage linear variation of a charge pump is achieved, and charging and discharging for the capacitors can be accurately controlled. The charge pump circuit is simple in structure, easy to integrate, high in charge and discharge current source matching precision, and suitable for being used in low voltage and low power consumption.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

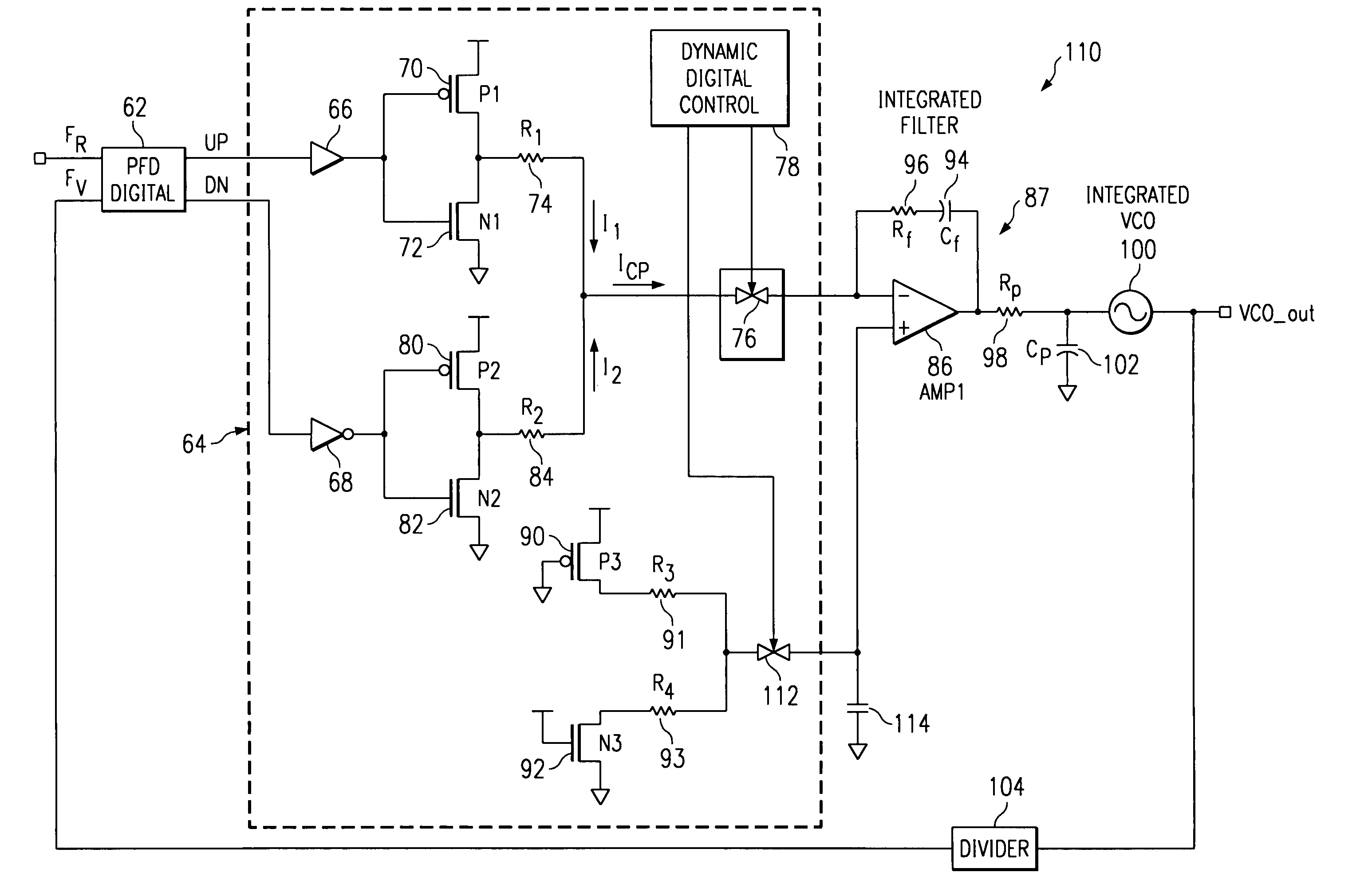

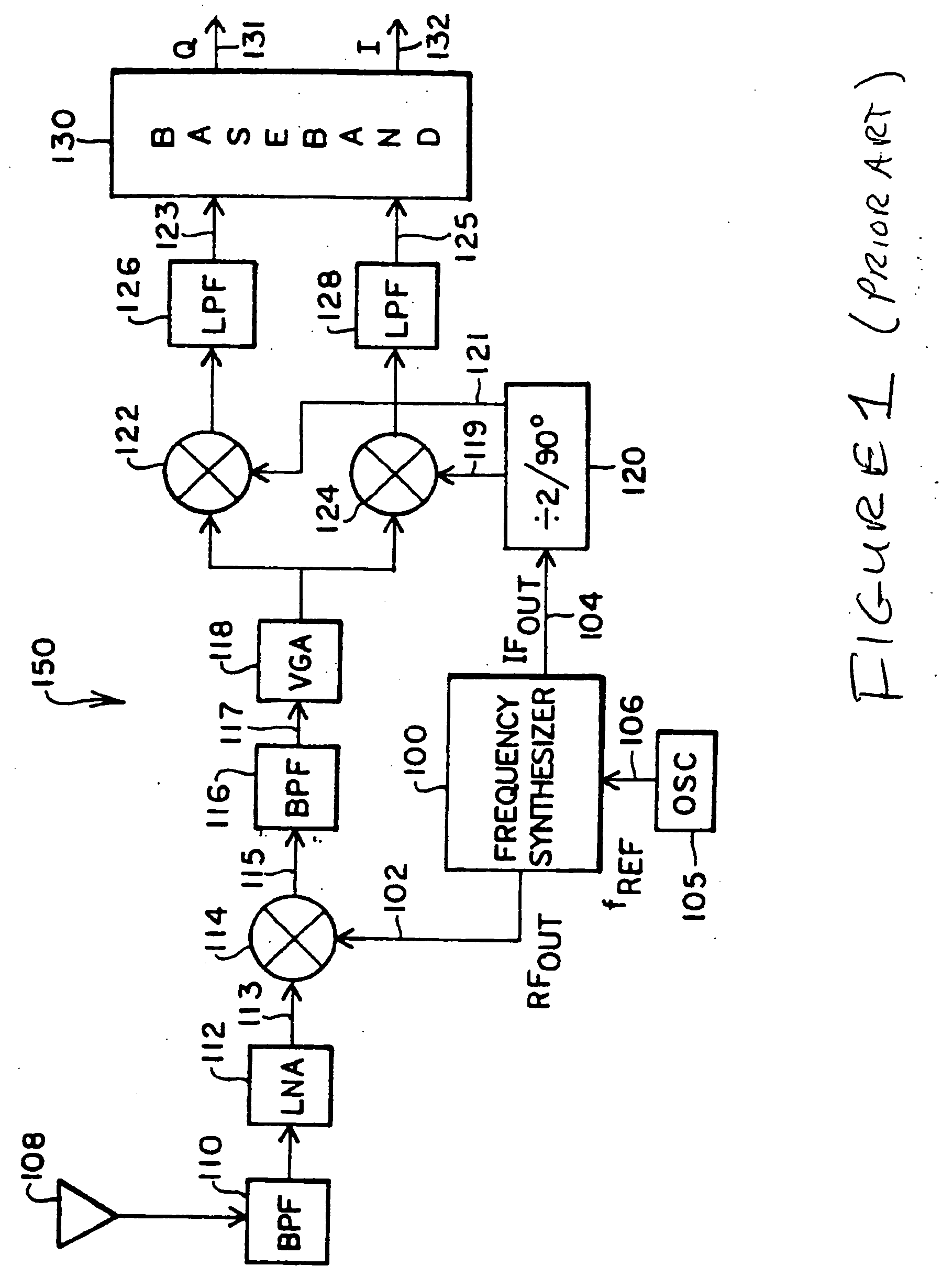

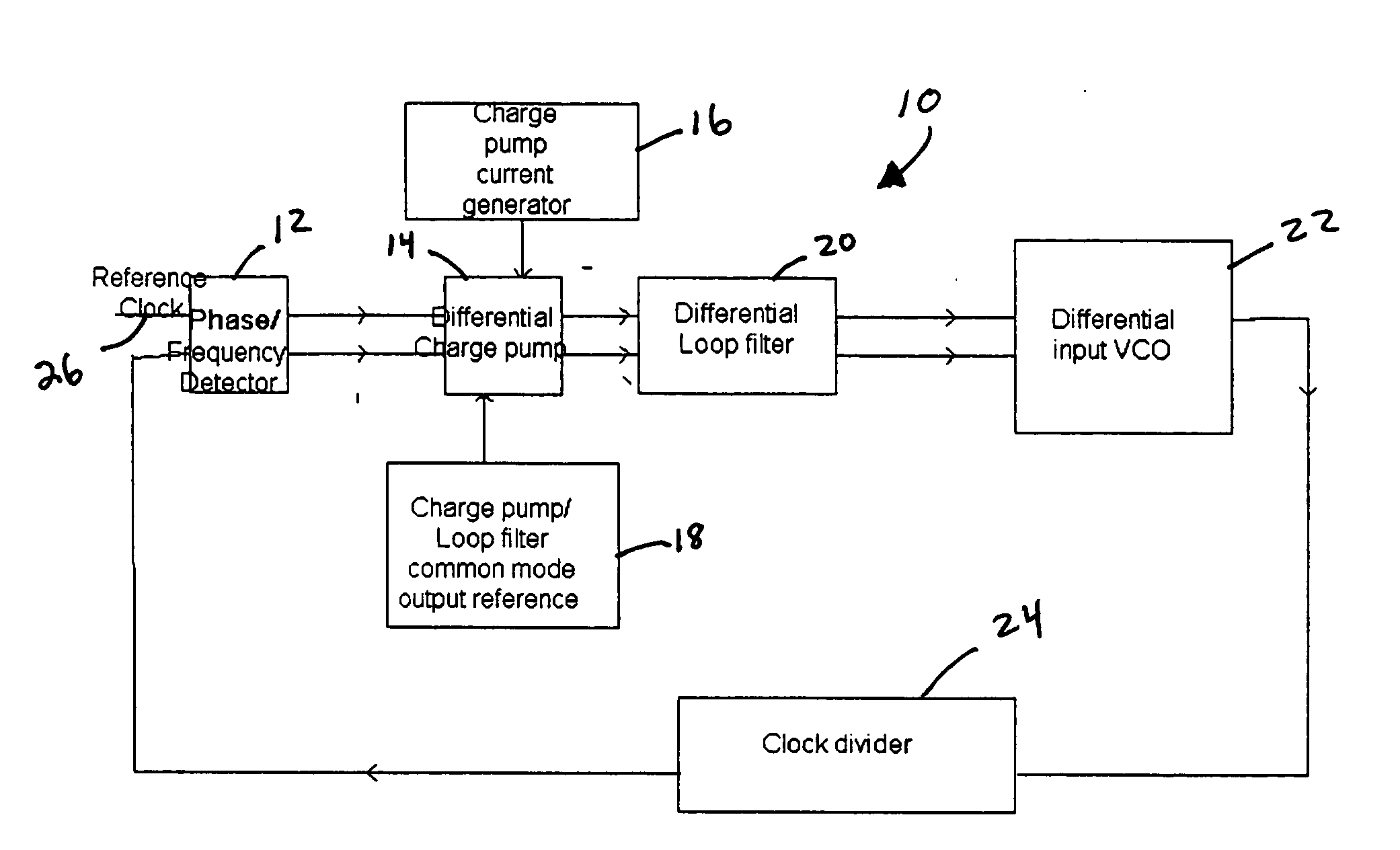

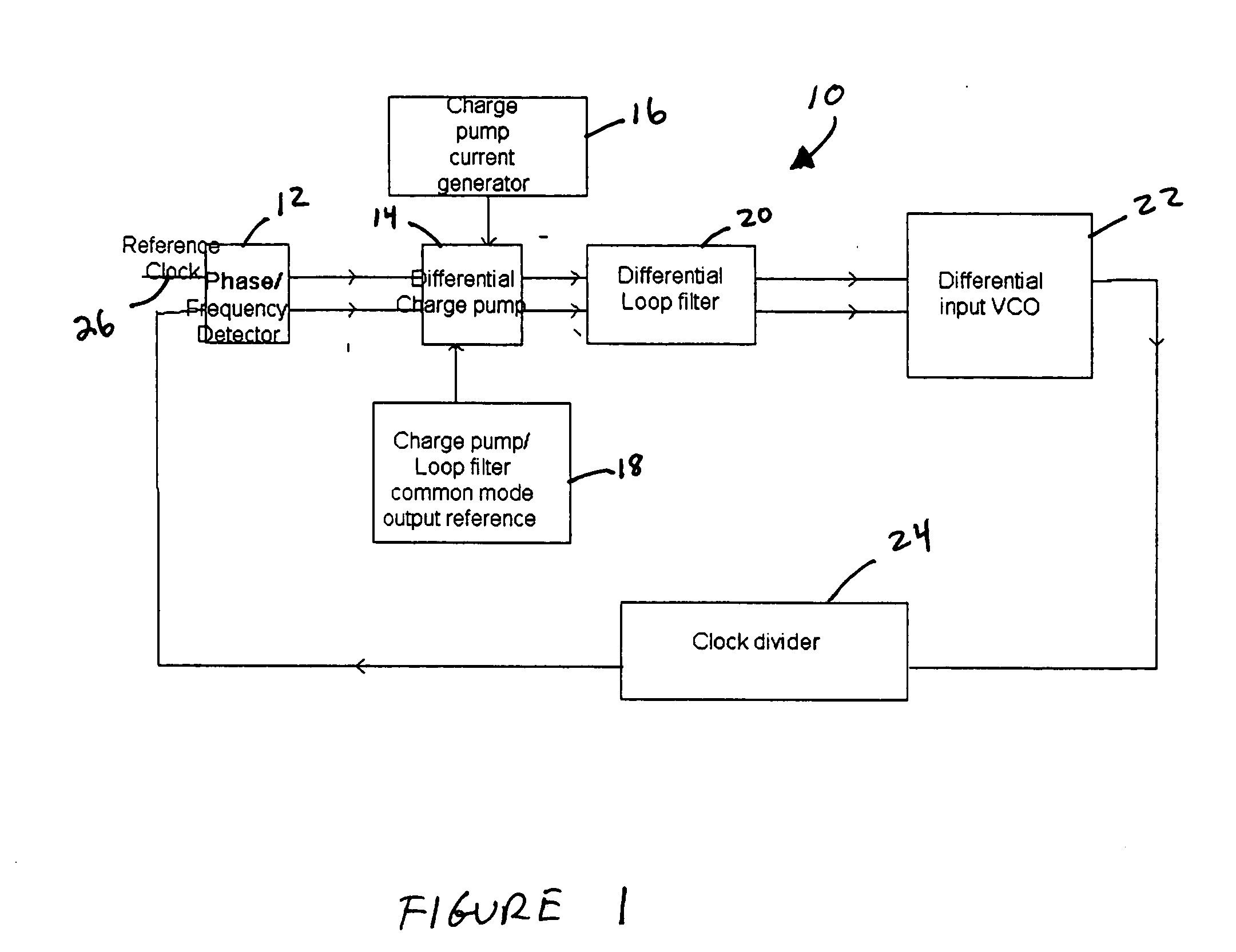

High performance analog charge pumped phase locked loop (PLL) architecture with process and temperature compensation in closed loop bandwidth

ActiveUS20060071716A1Improve performanceReduce variationPulse automatic controlPulse generation by logic circuitsDamping factorAudio power amplifier

The present invention achieves technical advantages as a high performance analog charge pumped phase locked loop (PLL)(10) with process and temperature compensation in closed loop bandwidth. The PLL reduces the variation in bandwidth and stability by making the product KVCO*ICP independent of process and temperature variation. The PLL achieves a higher performance than existing PLL architectures, achieving a high dynamic range up to at least 110 dB, such that a PWM class-D amplifier is realizable with this PLL. The PLL has a constant bandwidth and damping factor while using an analog charge pump (16).

Owner:TEXAS INSTR INC

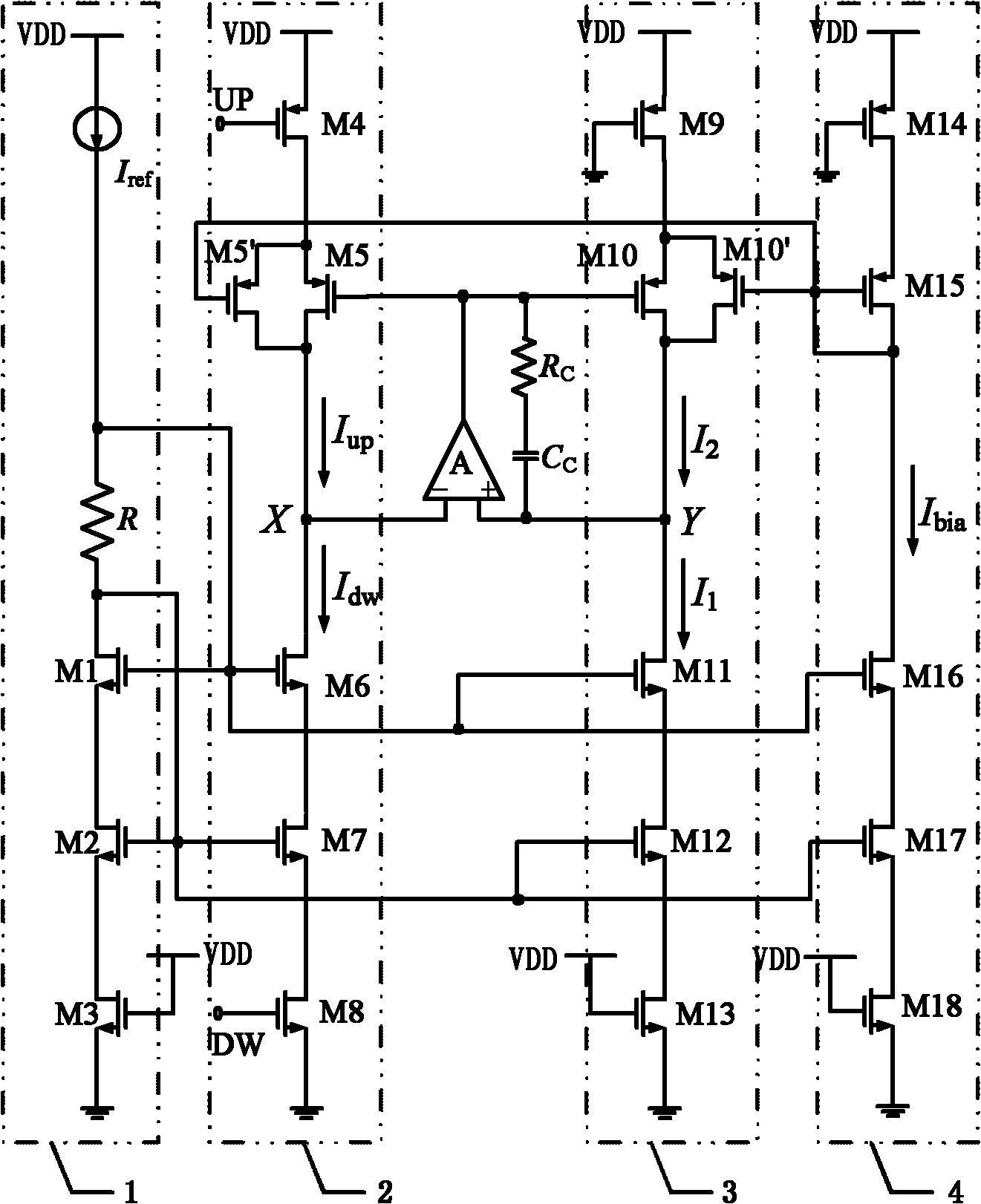

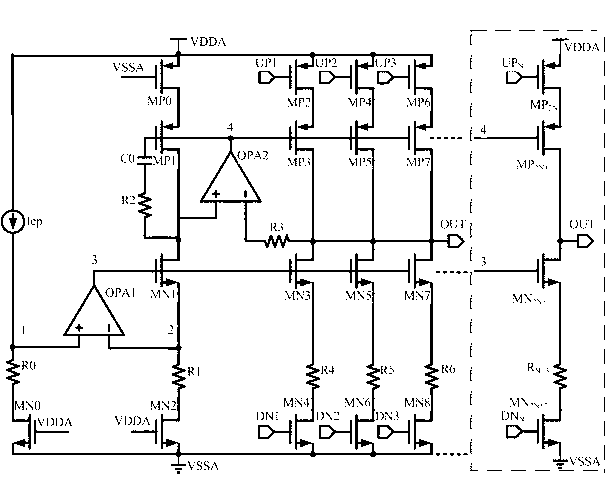

Matching type charge pump circuit for phase-locked loop

ActiveCN103346784AAccurate and reliable matchingPrecise size controlPulse automatic controlExternal referenceCharge discharge

The invention discloses a matching type charge pump circuit for a phase-locked loop. The matching type charge pump circuit comprises an in-proportion bias circuit, a current duplication circuit, a sunk constant-current source circuit, a pull-up constant-current circuit and a switch circuit. The in-proportion bias circuit magnifies an external reference current proportionally. The current duplication circuit strictly duplicates a current in an NMOS current mirror for a PMOS current mirror. The sunk constant-current source is used for discharging a later-stage load. The pull-up constant-current circuit is used for charging the later-stage load. The switch circuit is used for controlling switching-on and switching-off of a charge-discharge current source. According to the matching type charge pump circuit for the phase-locked loop, the bias current mirror image proportion of the in-proportion bias circuit depends on the ratio of resistance values of a resistor R0 and a resistor R1. The matching type charge pump circuit for the phase-locked loop is more reliable in structure compared with a traditional structure and is not affected by technology angles and temperature variation so as to accurately control loop parameters of the phase-locked loop of a charge pump, and the charge sharing effect existing in common charge pump design is well eliminated.

Owner:CHENGDU GANIDE TECH

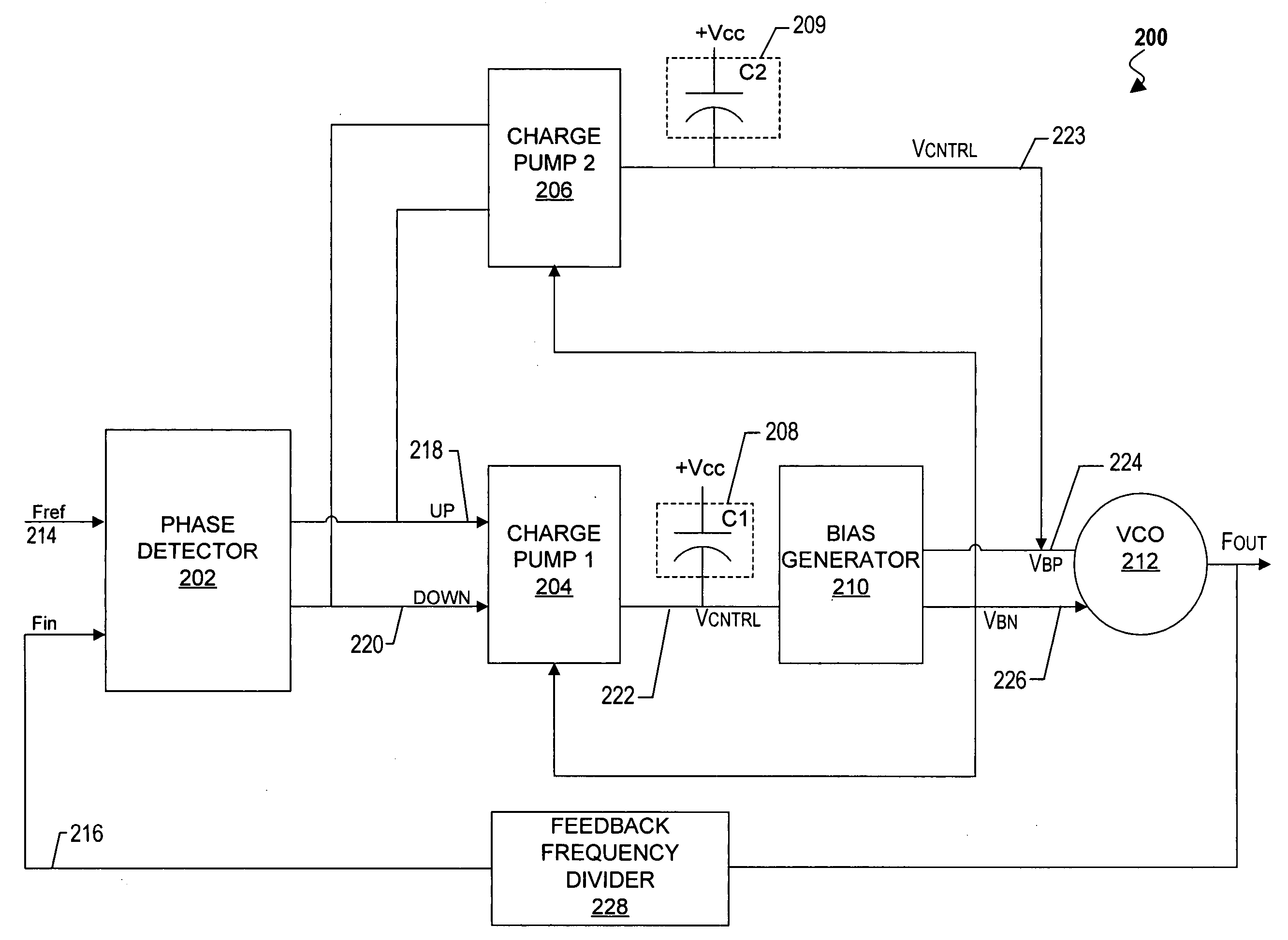

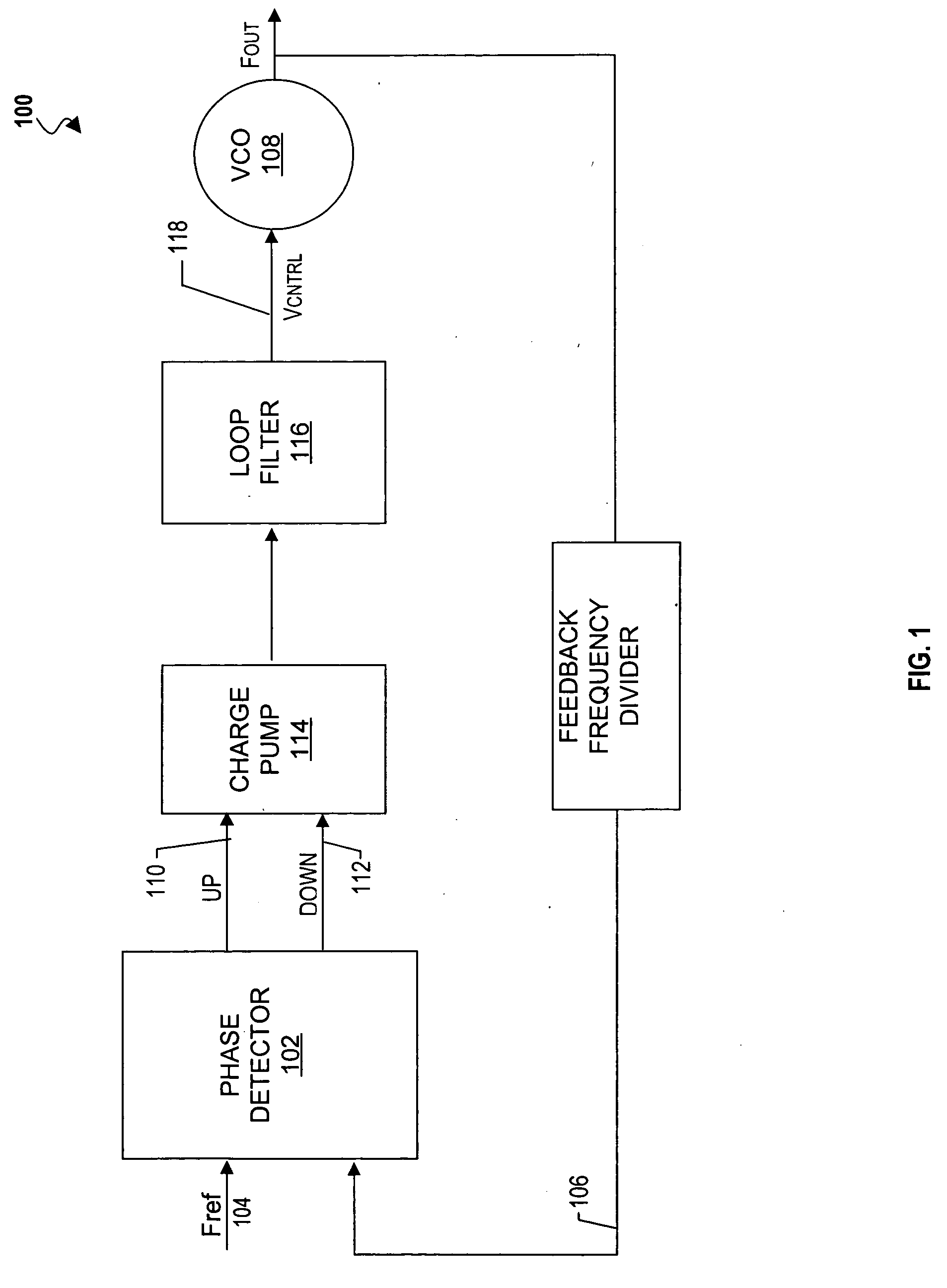

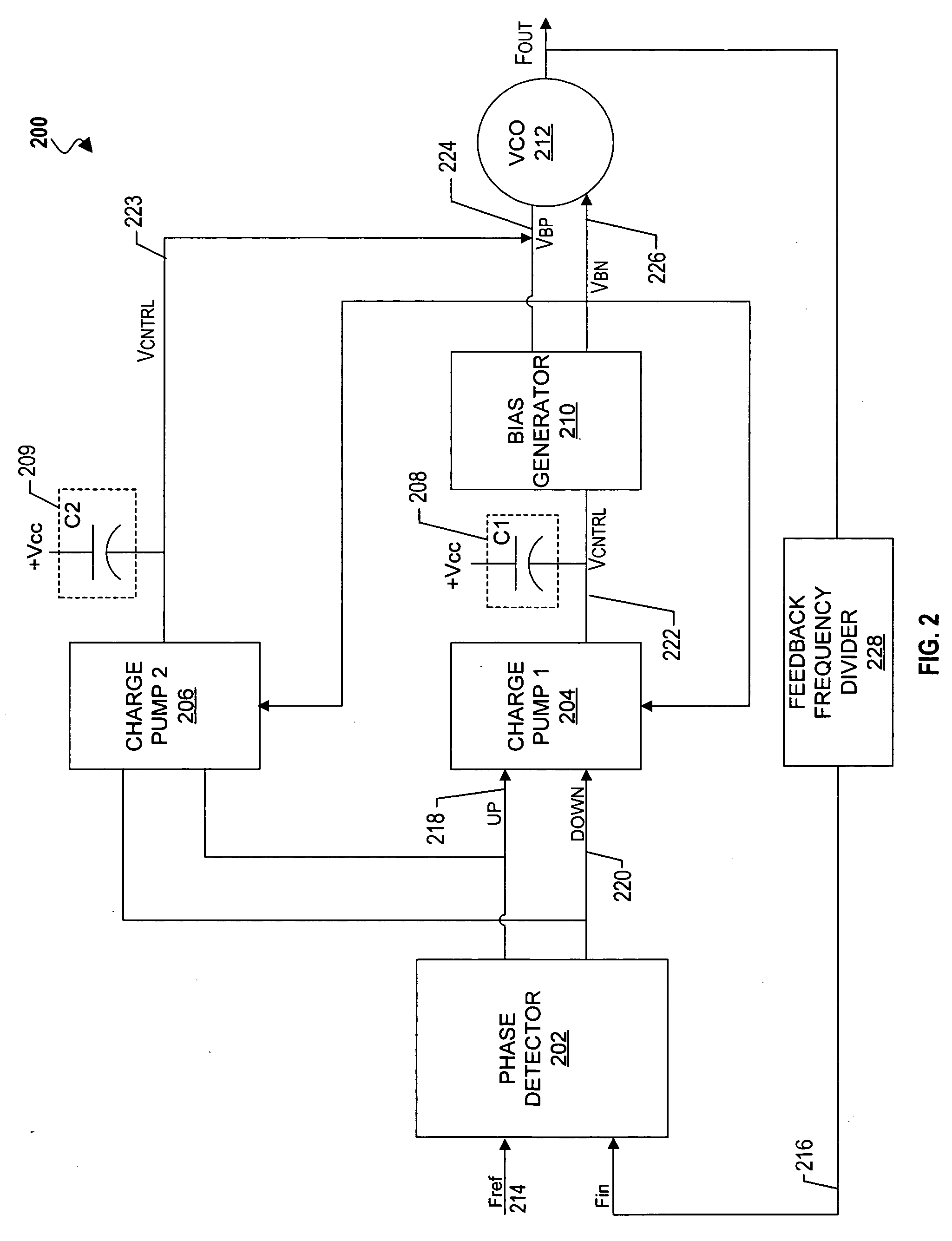

Method and apparatus for reducing lock time in dual charge-pump phase-locked loops

InactiveUS20040239386A1Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorControl signal

A phase-locked loop includes a phase detector to measure a phase offset between a reference clock signal and a feedback clock signal, and to generate first and second output control signals having a pulse width corresponding to the phase offset. The phase locked loop further includes a first pulse width control circuit coupled to the phase detector to reduce the pulse width of the first output control signal producing a first modified output control signal, a second pulse width control circuit coupled to the phase detector to reduce the pulse width of the second output control signal producing a second modified output control signal, a first charge pump coupled to the phase detector to provide a first charge signal responsive to the first and second output control signals, and a second charge pump coupled to the first and second pulse width control circuits to provide a second charge signal responsive to the first and second modified output control signals.

Owner:INTEL CORP

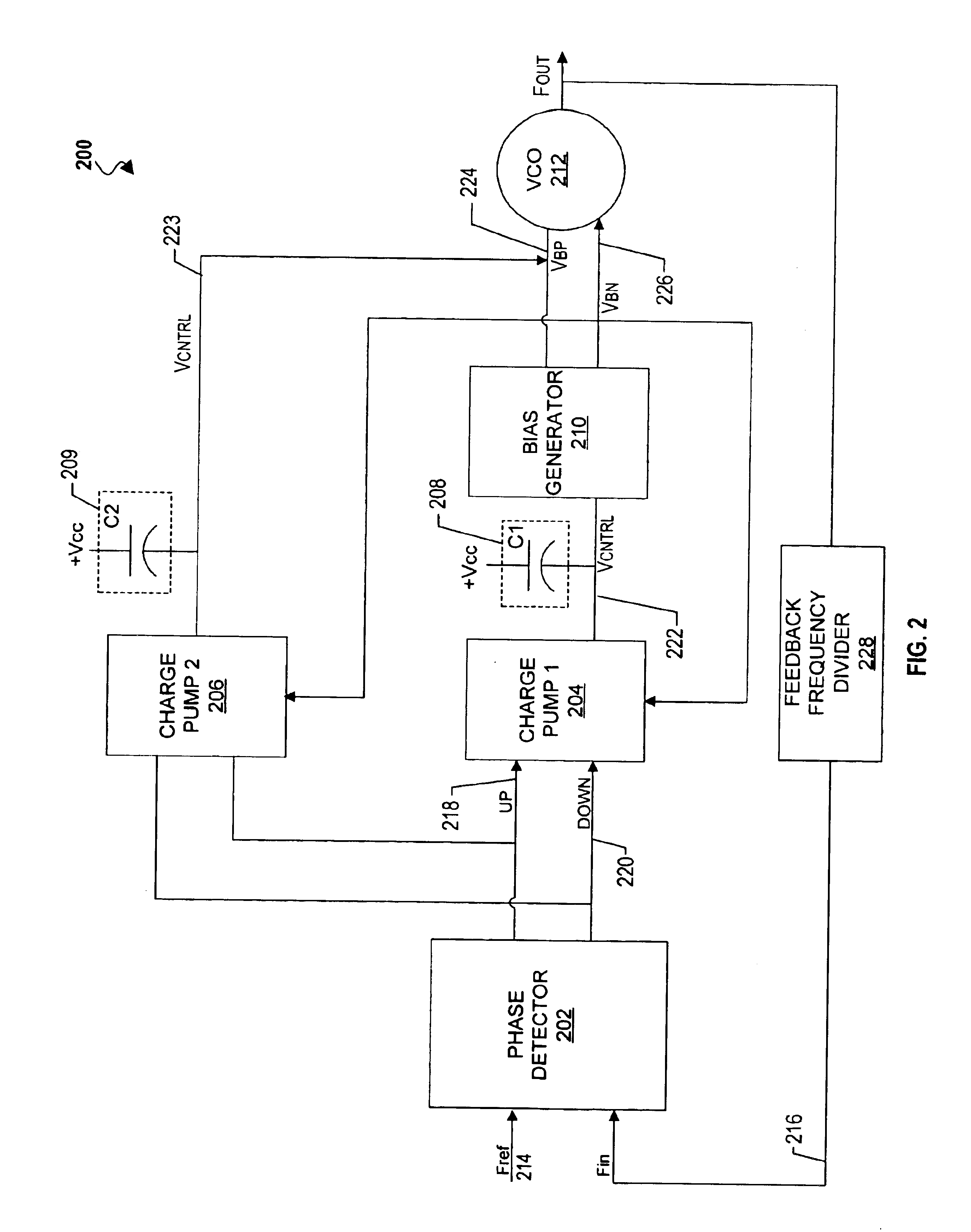

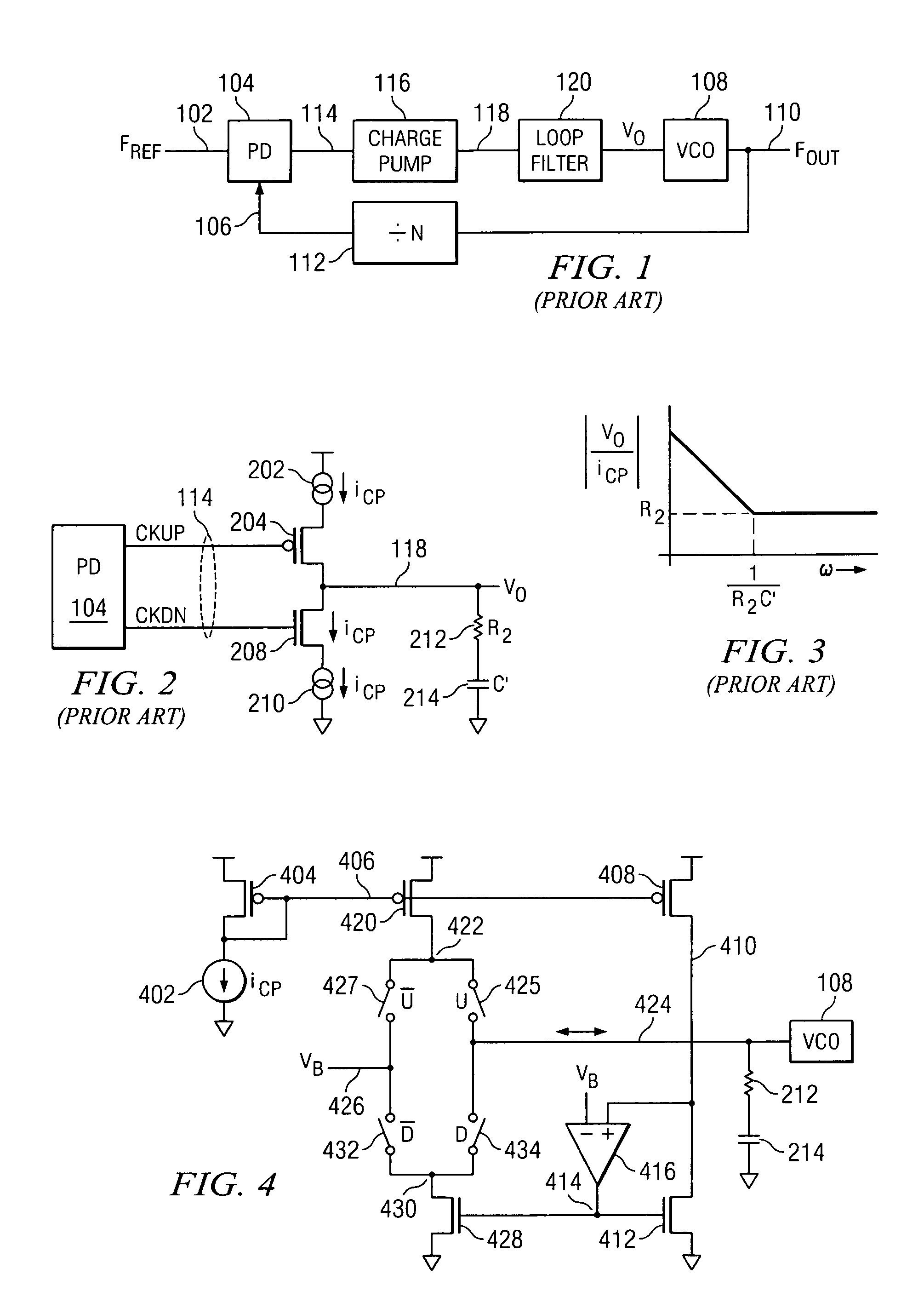

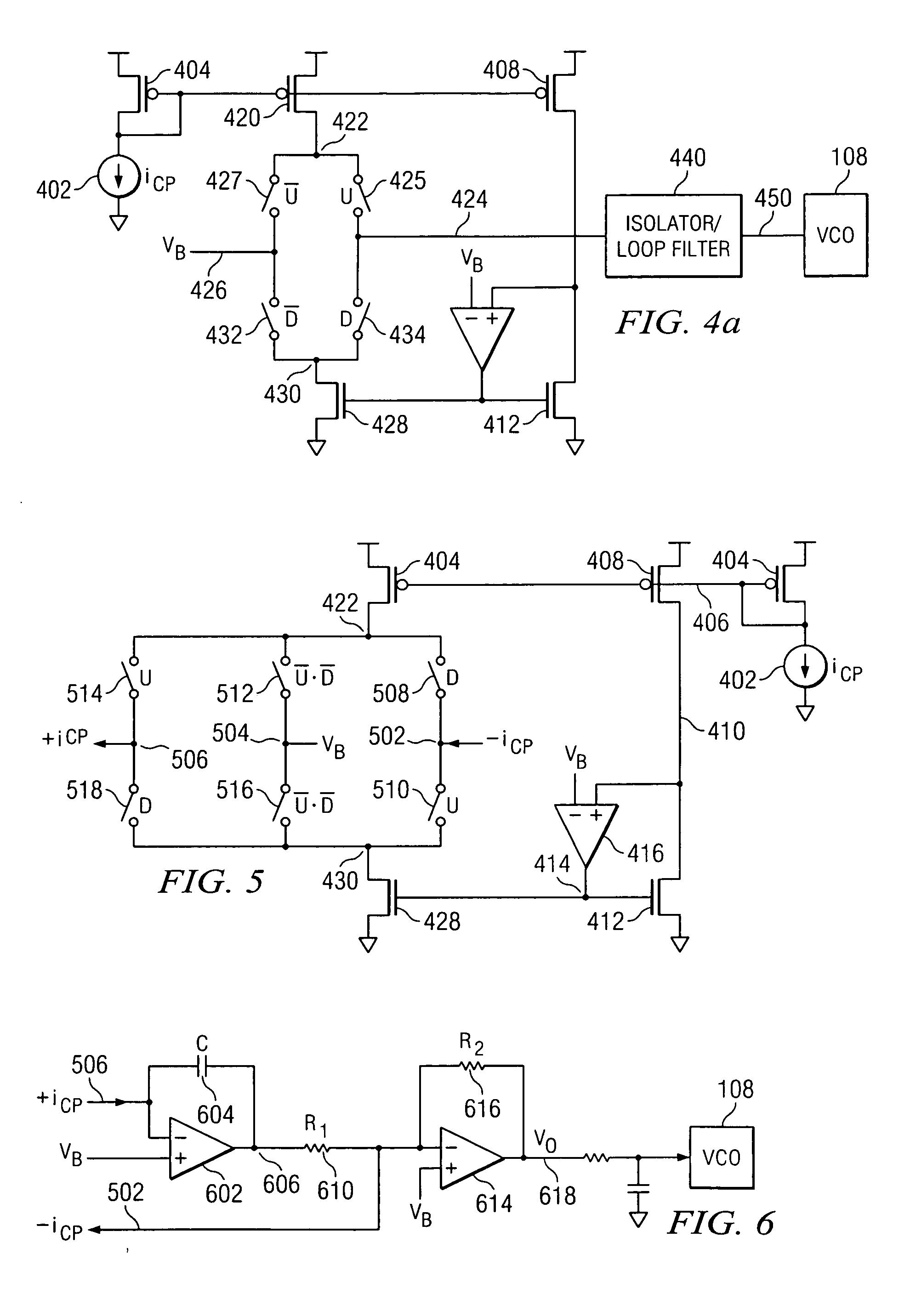

Integrated PLL loop filter and charge pump

A charge pumped phase locked loop circuit (PLL) is disclosed that includes a phase detector for detecting the phase error between a reference clock and an output clock to generate a phase error signal. A charge pump is provided that is controlled by the phase error signal to either source current to an intermediate control node or to sink current therefrom. An isolation circuit maintains the intermediate control node at a virtual AC reference voltage such that it remains at substantially the same voltage during the sourcing of current thereto or sinking of current therefrom, the isolation circuit generating a control voltage on the output thereof to control the frequency of the output clock. A loop filter is provided for filtering the control voltage.

Owner:SILICON LAB INC

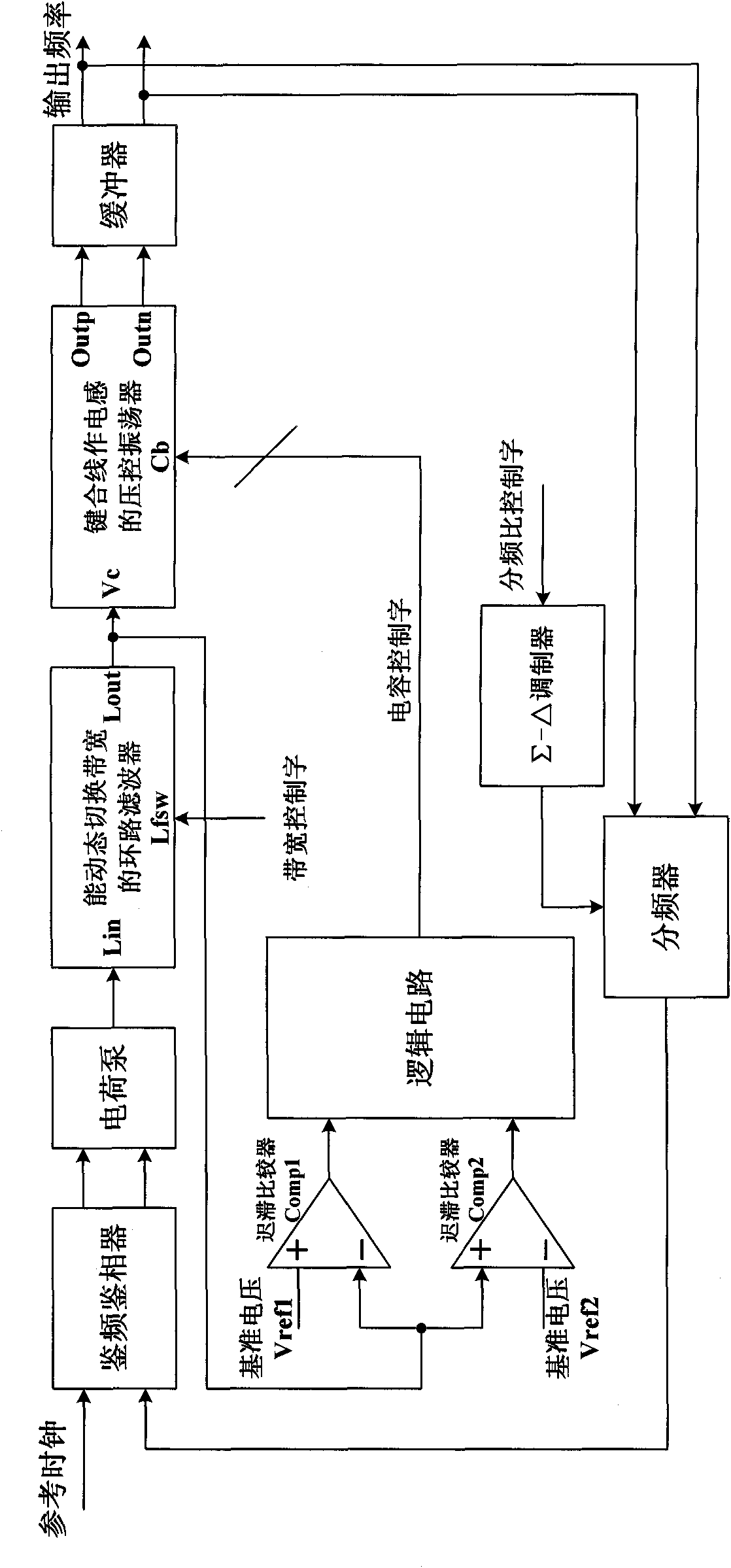

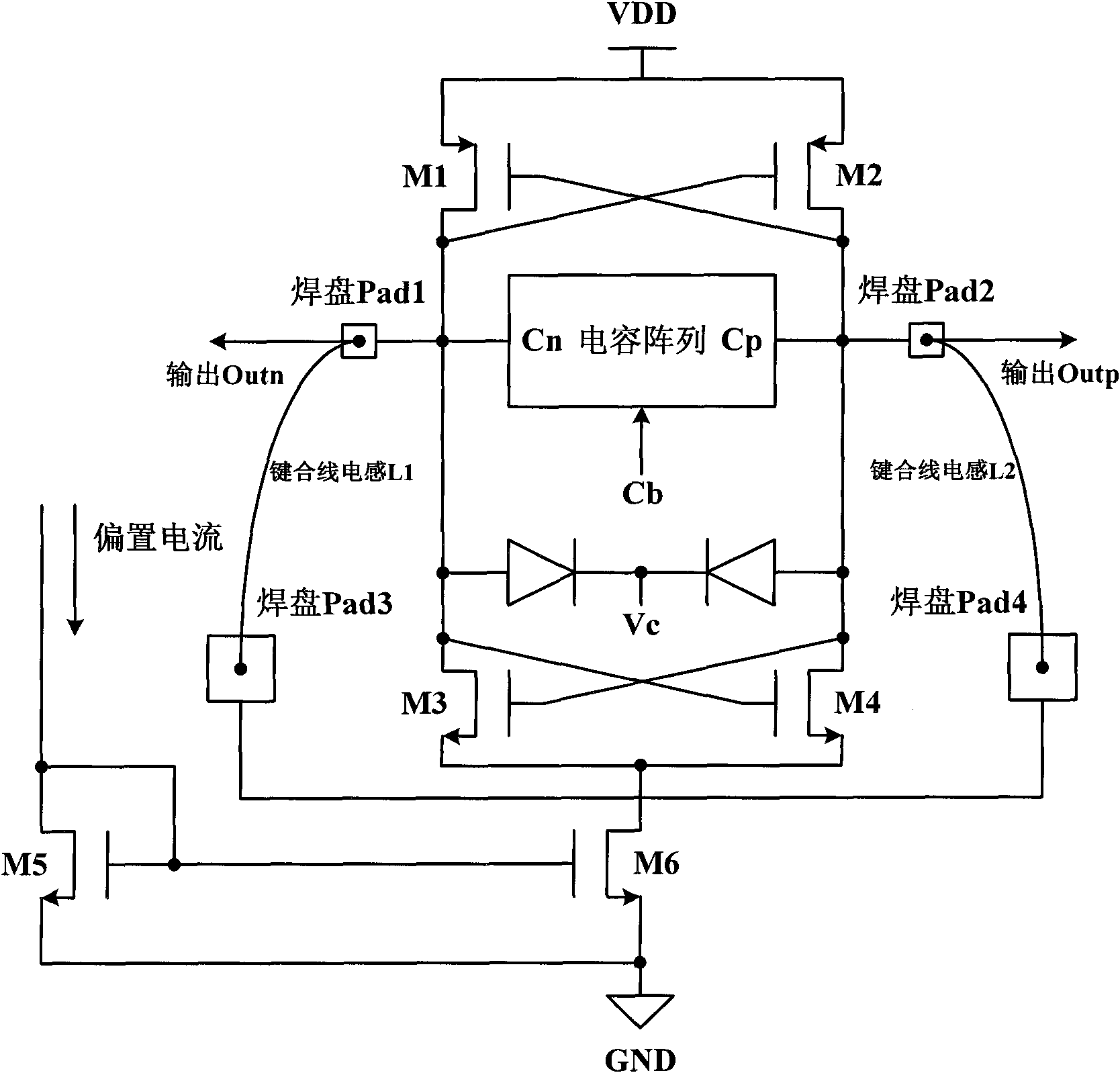

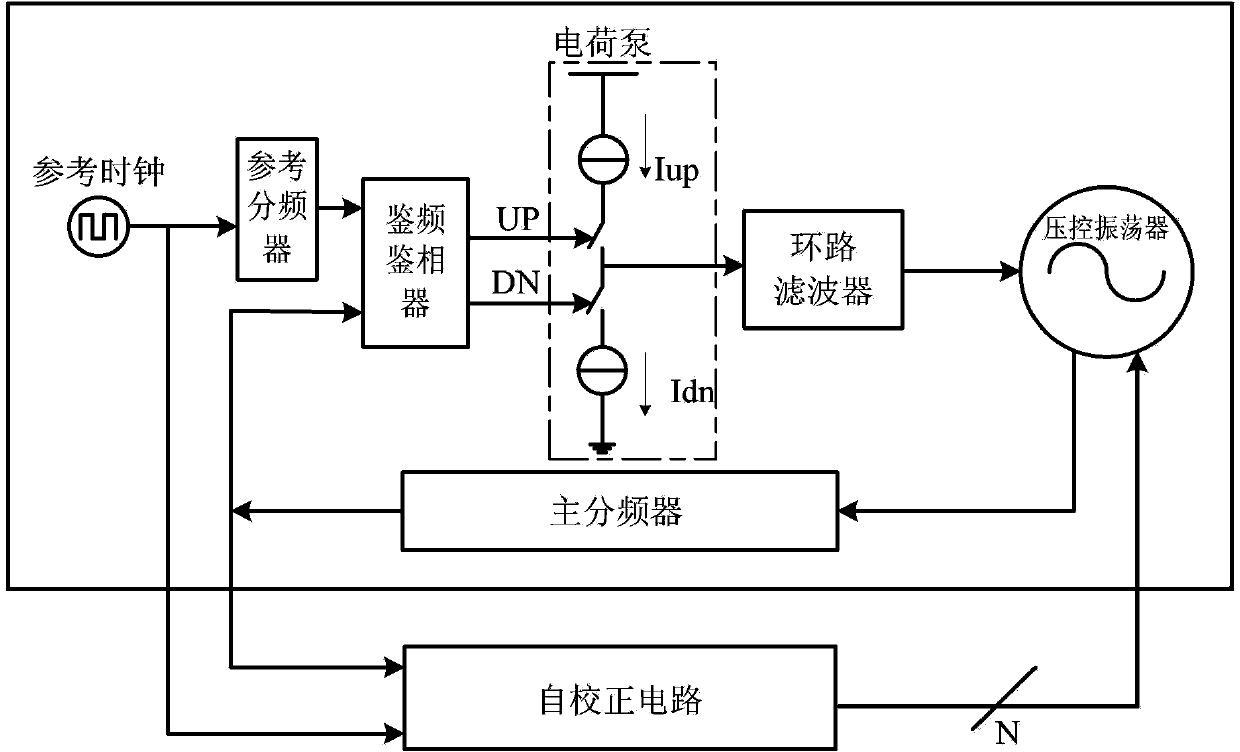

Frequency self-correction phase lock loop adopting bonding wire as electric inductance of oscillator

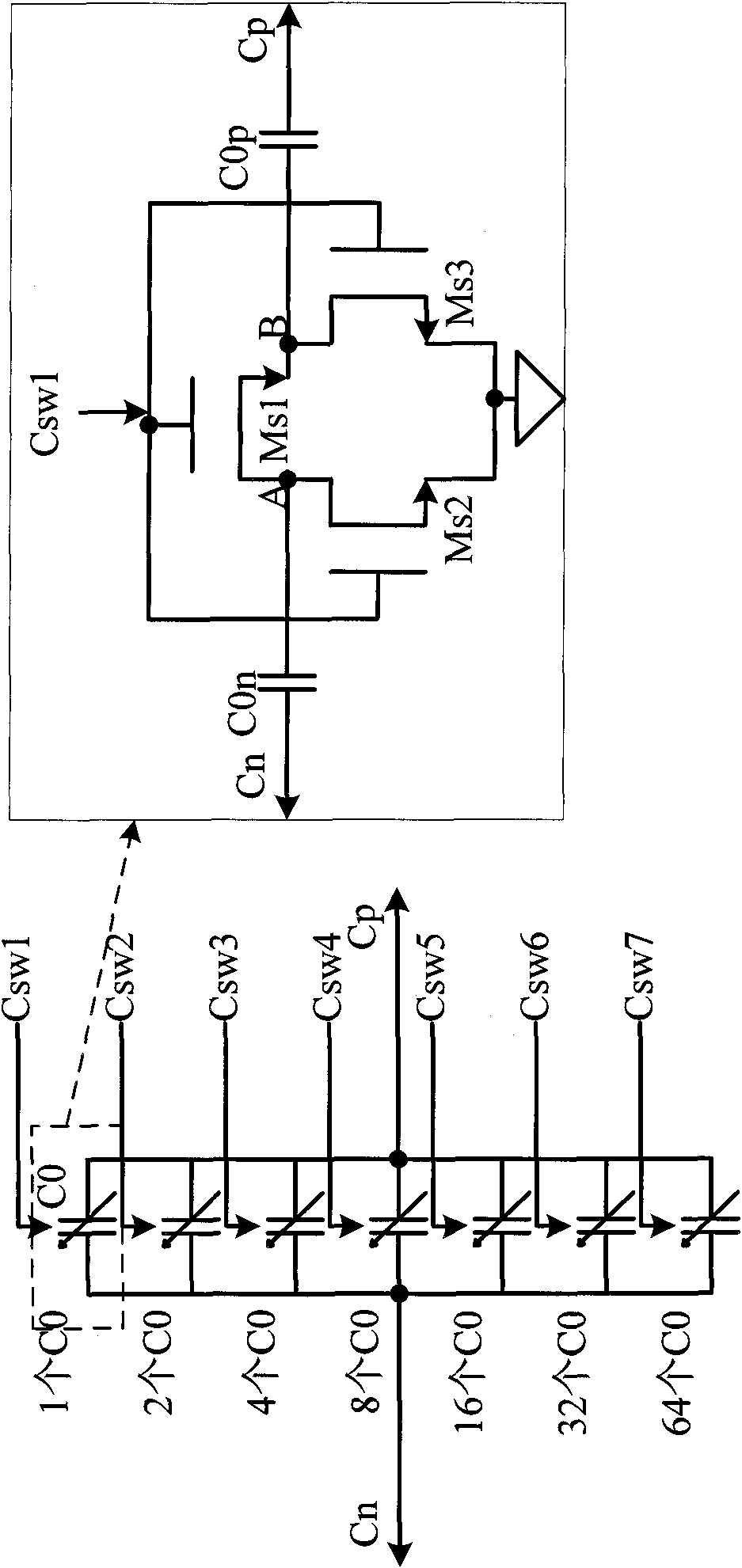

ActiveCN101807914AReduce power consumptionReduce phase noisePulse automatic controlCapacitanceLow noise

The invention discloses a charge pump phase lock loop which adopts a bonding wire as the electric inductance of an oscillator and has a frequency self-correction function. The phase lock loop adopts the bonding wire as the electric inductance of an electric inductance and capacitance resonant cavity type voltage-controlled oscillator and has the advantages of low power consumption, low noise and small area of chips; a frequency self-correction loop is connected between a control voltage input end of the voltage-controlled oscillator and a capacitance array of the voltage-controlled oscillator, thereby achieving the resonant frequency self-correction function and eliminating the problem of inaccurate resonant frequency caused by the bonding wire; the control voltage input end of the voltage-controlled oscillator is connected with a loop filter, and the loop filter carries out bandwidth dynamic switching by adopting a broadband loop filter and a narrow-band loop filter, thereby improving the speed for resonant frequency self-correction under the condition of not influencing the phase noise and the noise and spur performance of the phase lock loop.

Owner:TSINGHUA UNIV

Dual-mode self switching radiation hardening clock generation circuit based on phase-locked loops

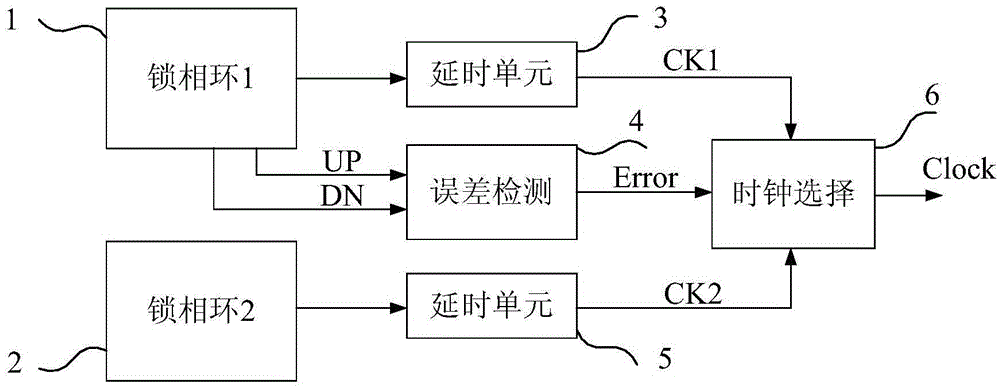

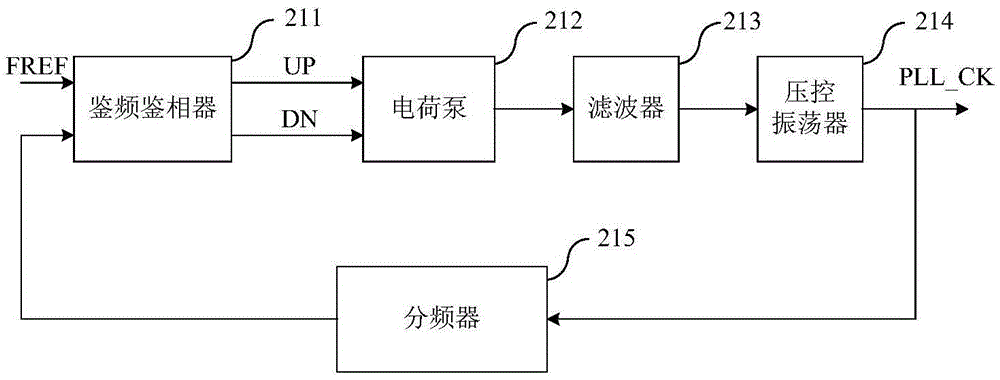

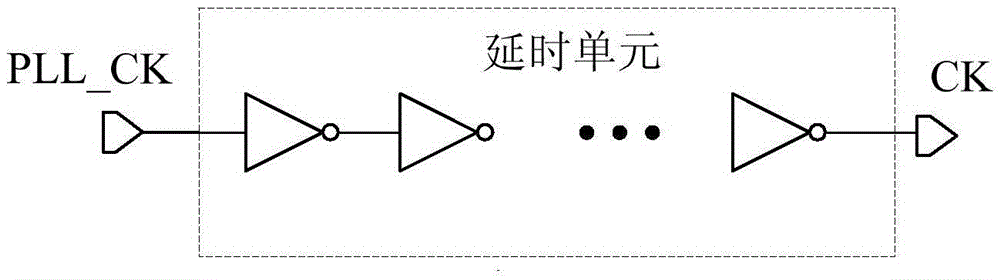

ActiveCN105610430AHigh immunity to single event transientsImprove immunityPulse automatic controlDual modePhase frequency detector

The invention provides a dual-mode self switching radiation hardening clock generation circuit based on phase-locked loops, which is mainly composed of two independent phase-locked loops, a delay unit, an error detection unit and a clock selection unit. The two independent phase-locked loops are charge pump phase-locked loops not subjected to radiation hardening, and used for providing corresponding clock output; the delay unit realizes the delay of output signals of the phase-locked loops; the error detection unit is used for detecting whether two output signals of a phase frequency detector in a main phase-locked loop are right and outputting corresponding indication signals; and the clock selection unit performs selective output on the delayed output of the two phase-locked loops as the final output. The dual-mode self switching radiation hardening clock generation circuit based on the phase-locked loops provided by the invention can eliminate interference of a single event effect in a radiation environment on a circuit working state to a great extent, ensure the stability of the phase-locked loops as clock signals, improve the reliability of the system, and has the advantages of being easy in implementation, small in area, low in power consumption and so on.

Owner:BEIJING MXTRONICS CORP +1

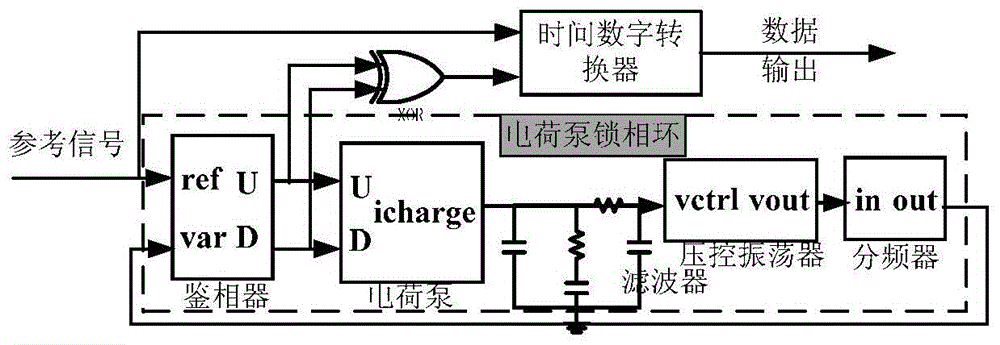

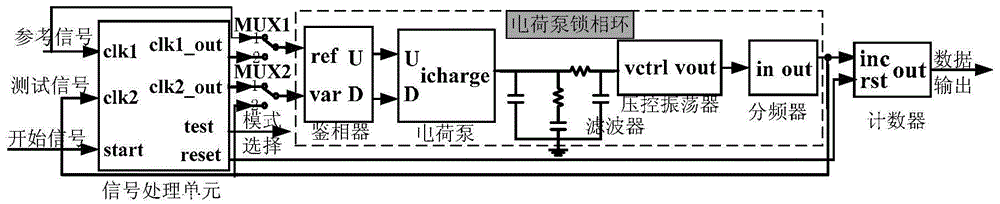

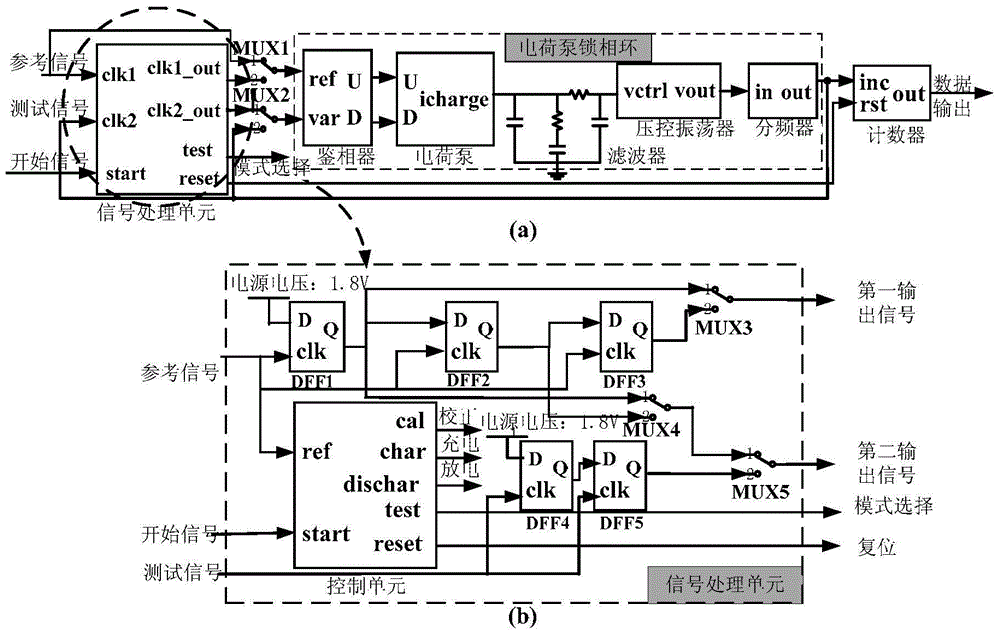

All-digital phase-locked loop built-in self-testing structure

The invention discloses an all-digital phase-locked loop built-in self-testing structure. The time difference between a reference signal and a test signal is converted into a digital signal to be output. The all-digital phase-locked loop built-in self-testing structure comprises a signal processing unit, a first dual-path switch MUX1, a second dual-path switch MUX2, a phase-locked loop to be tested and a counter. The phase-locked loop to be tested is a charge pump phase-locked loop. The reference signal and the test signal are connected to the input end of the phase-locked loop to be tested through the first dual-path switch MUX1 and the second dual-path switch MUX2 respectively, the time difference delta T of two input signals is converted into frequency variation delta f through the phase-locked loop to be tested, then the number of pulses is counted through the counter, and the frequency variation delta f is converted into count value variation delta N. The all-digital phase-locked loop built-in self-testing structure has the advantages of being fully digital, high in precision and low in cost.

Owner:SOUTHEAST UNIV

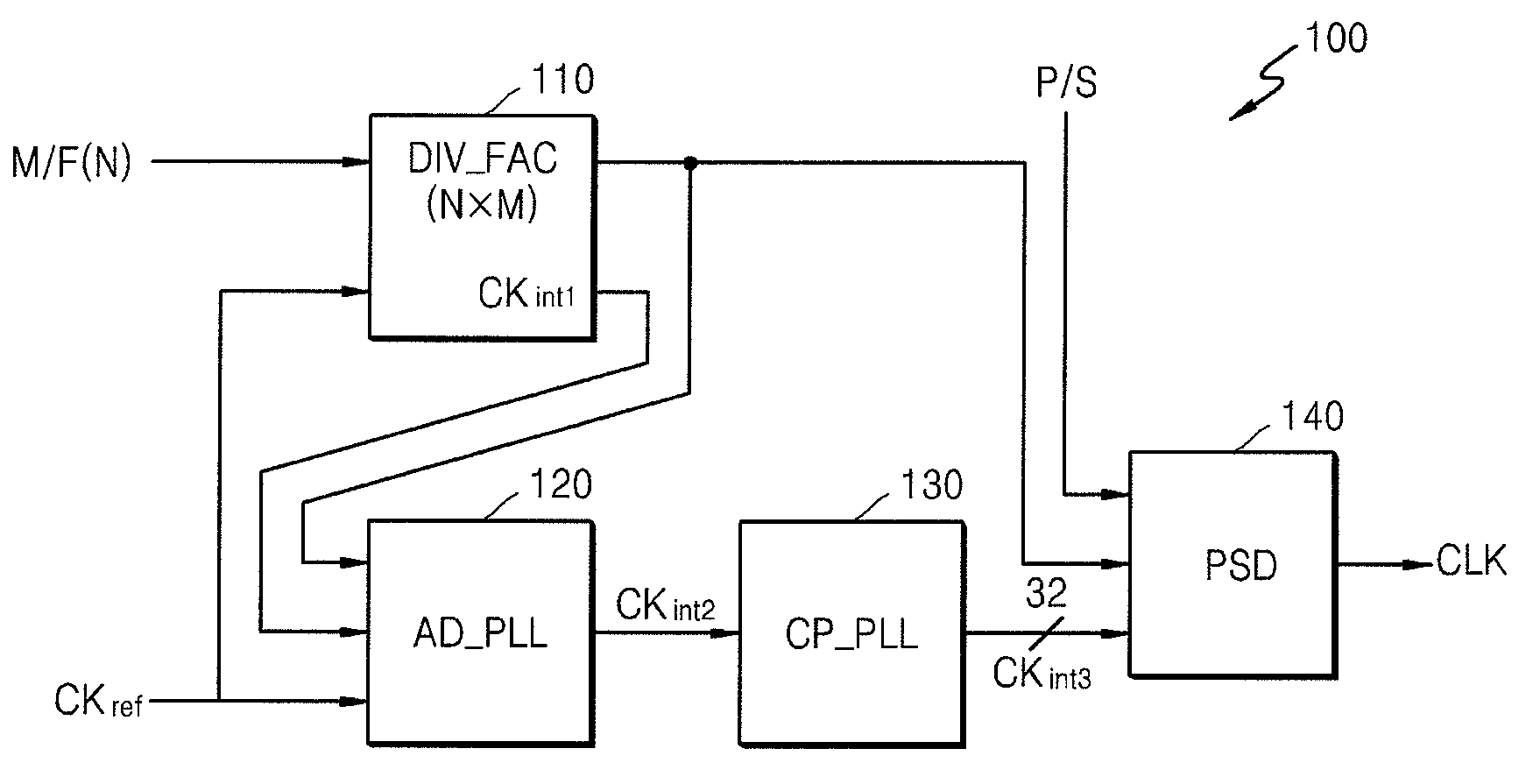

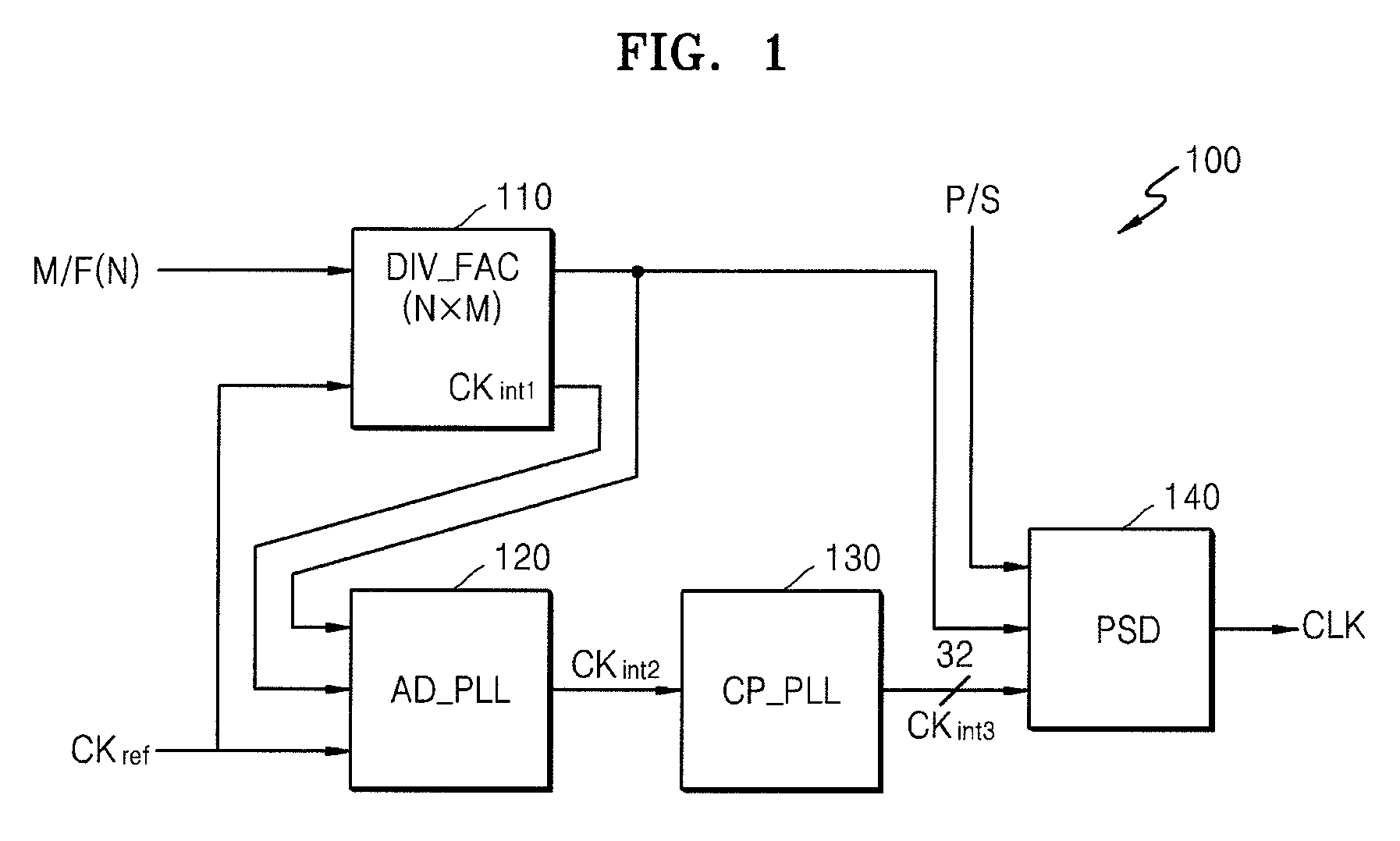

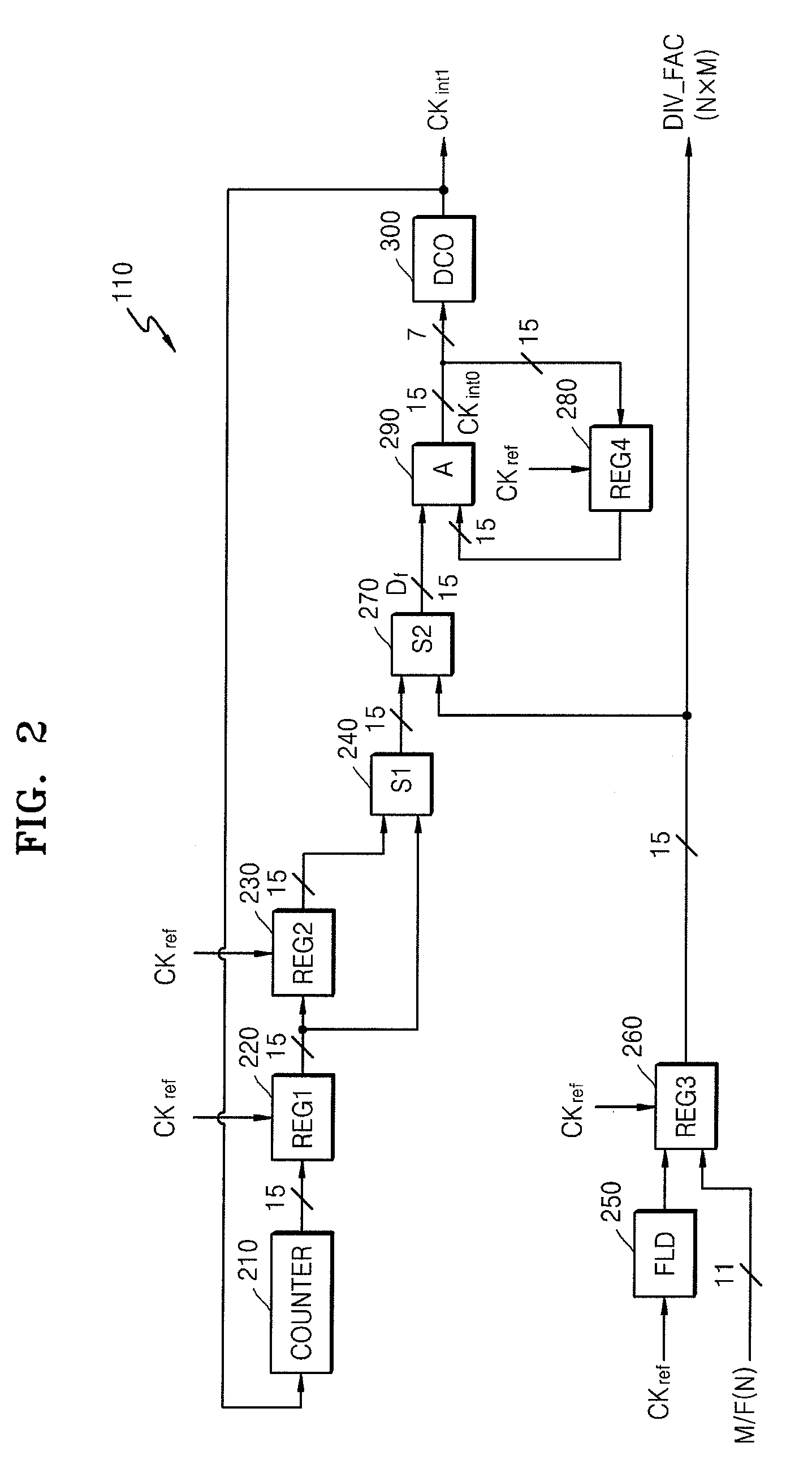

Clock generator to reduce long term jitter

A clock generator includes a controller, a digital phase locked loop (PLL) circuit, a charge pump phase locked loop (PLL) circuit and a divider. The controller generates a division factor and a first internal clock signal in response to a low-frequency reference clock signal and a multiplication factor. The digital PLL circuit generates a second internal clock signal in response to the reference clock signal, the division factor and the first internal clock signal. The charge pump PLL circuit generates a plurality of third internal clock signals by using the second internal clock signal. The divider generates a high-frequency clock signal in response to a phase selection signal, the division factor and the third internal clock signals.

Owner:SAMSUNG ELECTRONICS CO LTD +1

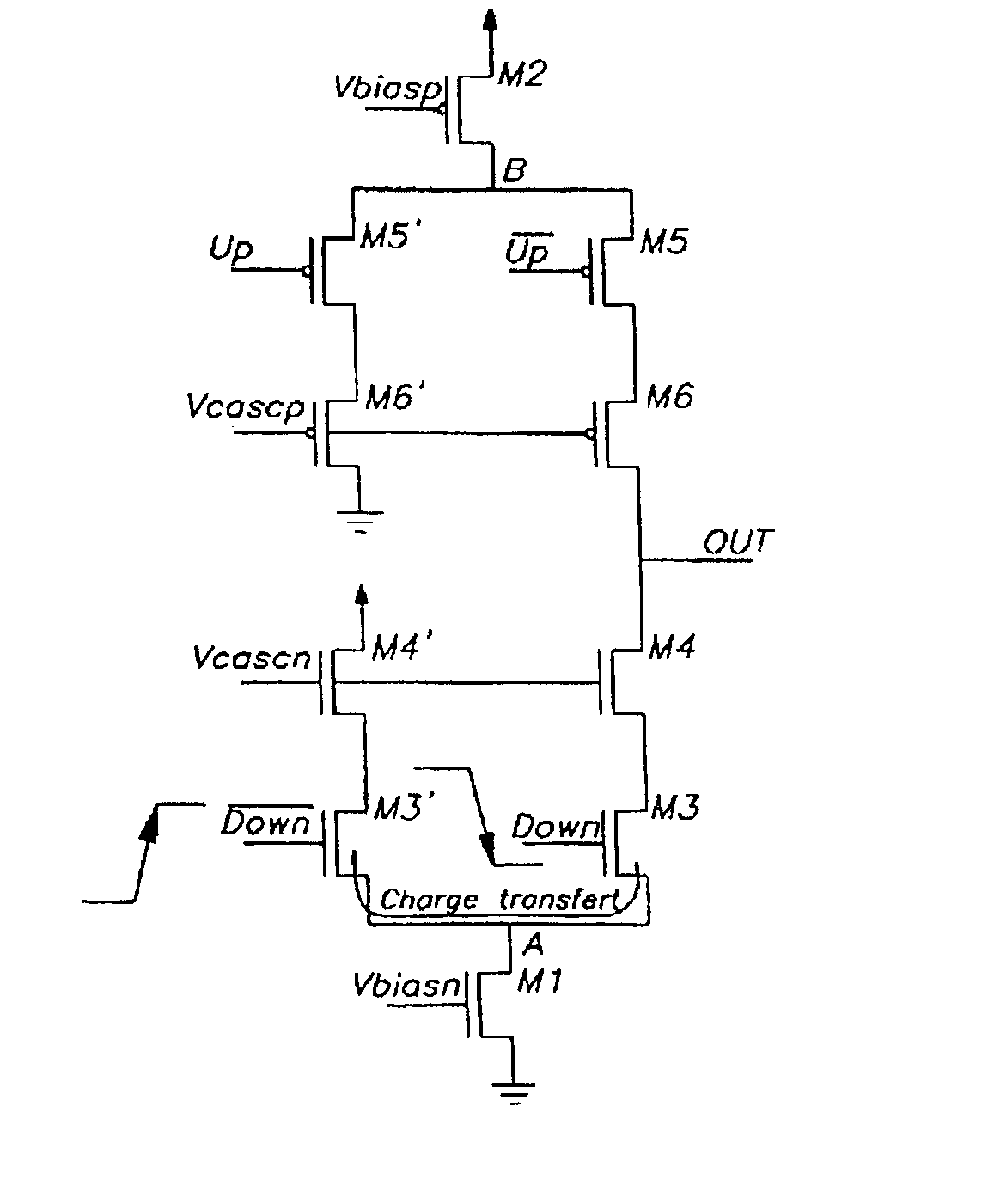

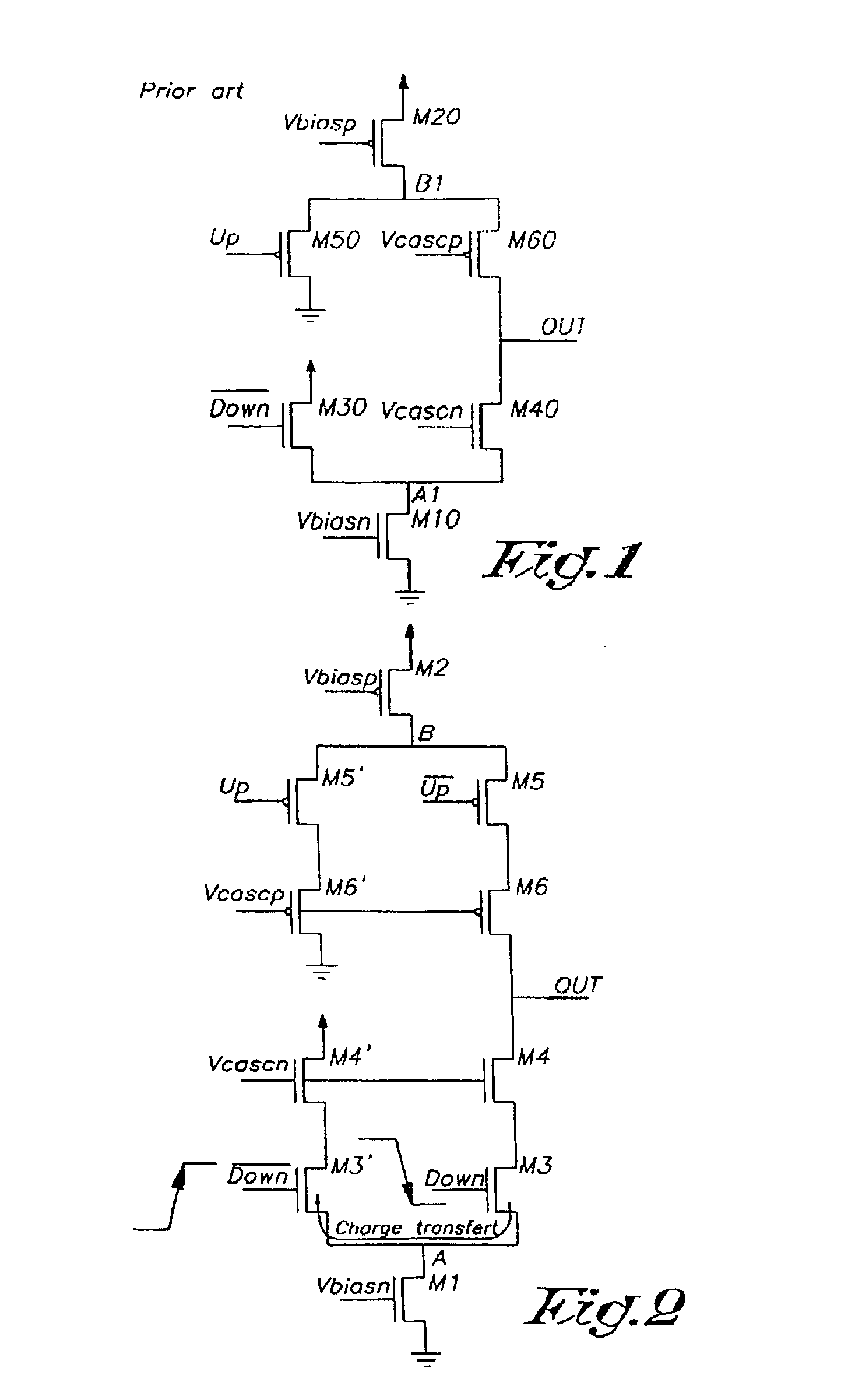

Low spurious charge pump

InactiveUS6885251B2Reduce stray currentLow spuriousPulse automatic controlElectronic switchingCascodeEngineering

Phase locked loop charge pump comprising a drain node (A, B) and at least a cascode transistor (M4, M6) for limiting the variation of the voltage of said drain node, characterized in that an intermediate switch transistor (M3, M5) is placed between the drain node (A, B) and the cascode transistor (M4, M6).

Owner:ALCATEL LUCENT SAS

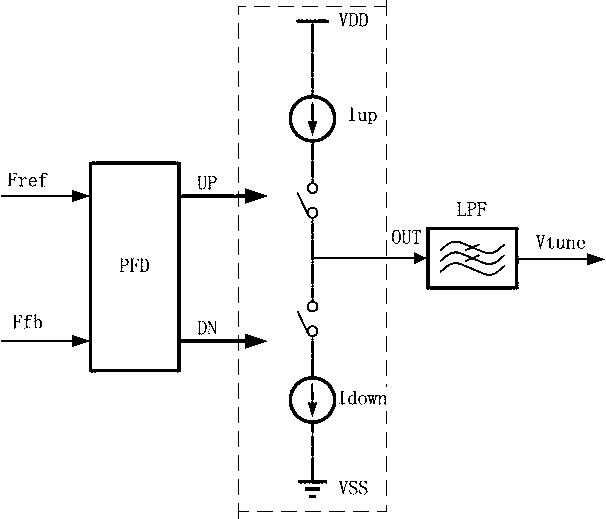

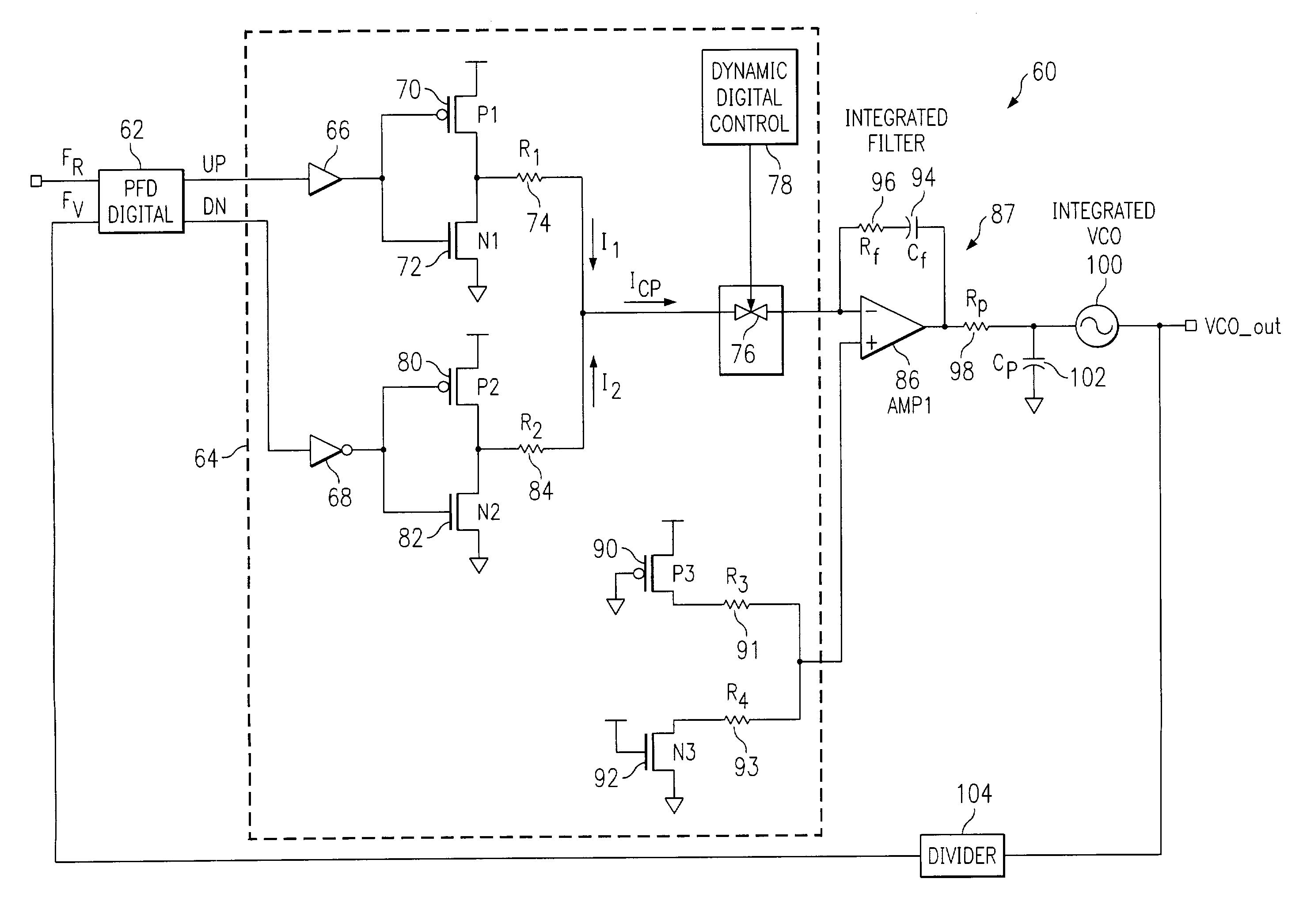

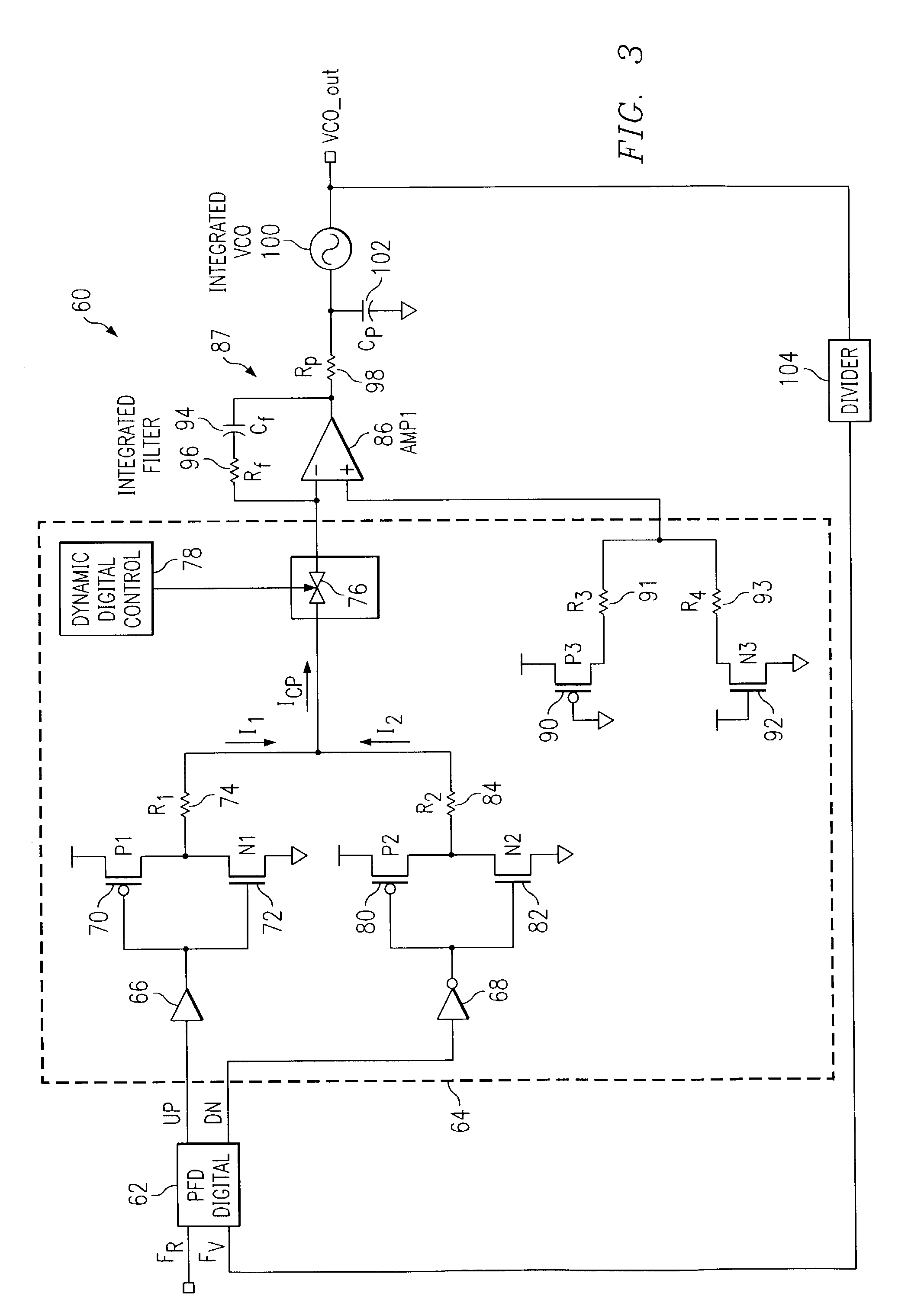

Charge pump phase locked loop

ActiveUS7158600B2Improve linearityLow spurious emissionPulse automatic controlModulated-carrier systemsPhase locked loop circuitEngineering

A phase lock loop circuit 60 has a phase frequency detector 62, a charge pump 64, an active filter 87 and a voltage-controlled oscillator 100. The phase detector generates UP and DN signals indicative of the relative frequency of FR, a reference signal, and FV, a signal controlled by the voltage-controlled oscillator. A charge pump using logic gates (buffer 66 and inverter 68) to produce a voltage drop over resistors 74 and 84 to generate a voltage at a node coupled to the input of transmission gate 76 according to the values of the UP and DN signals. When the transmission gate 76 is closed (low impedance) the charge pump may sink or source current to the inverting input of the operational amplifier 86 of the active filter 86. When the transmission gate is open (high impedance state) the inverting input is electrically isolated from the node.

Owner:TEXAS INSTR INC

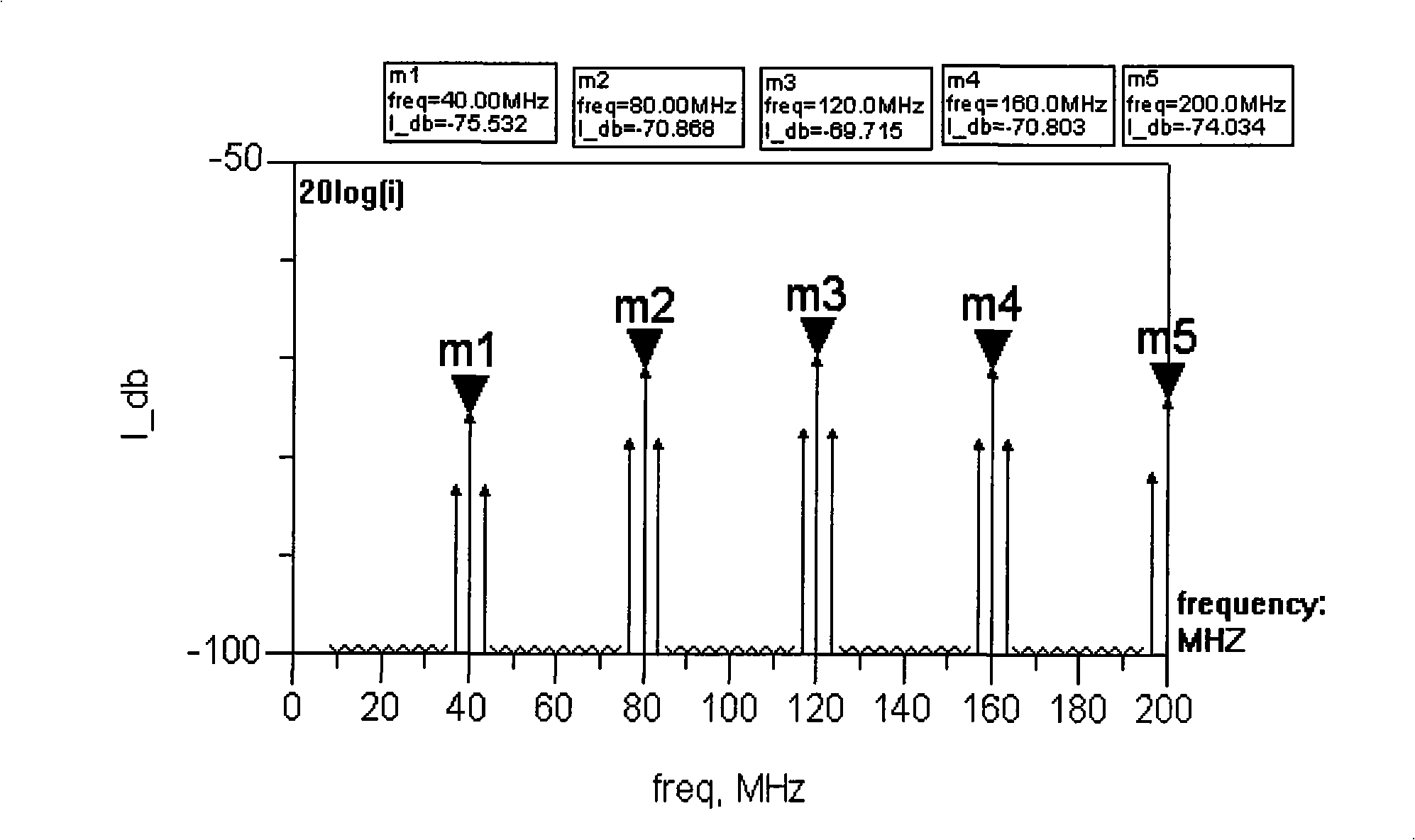

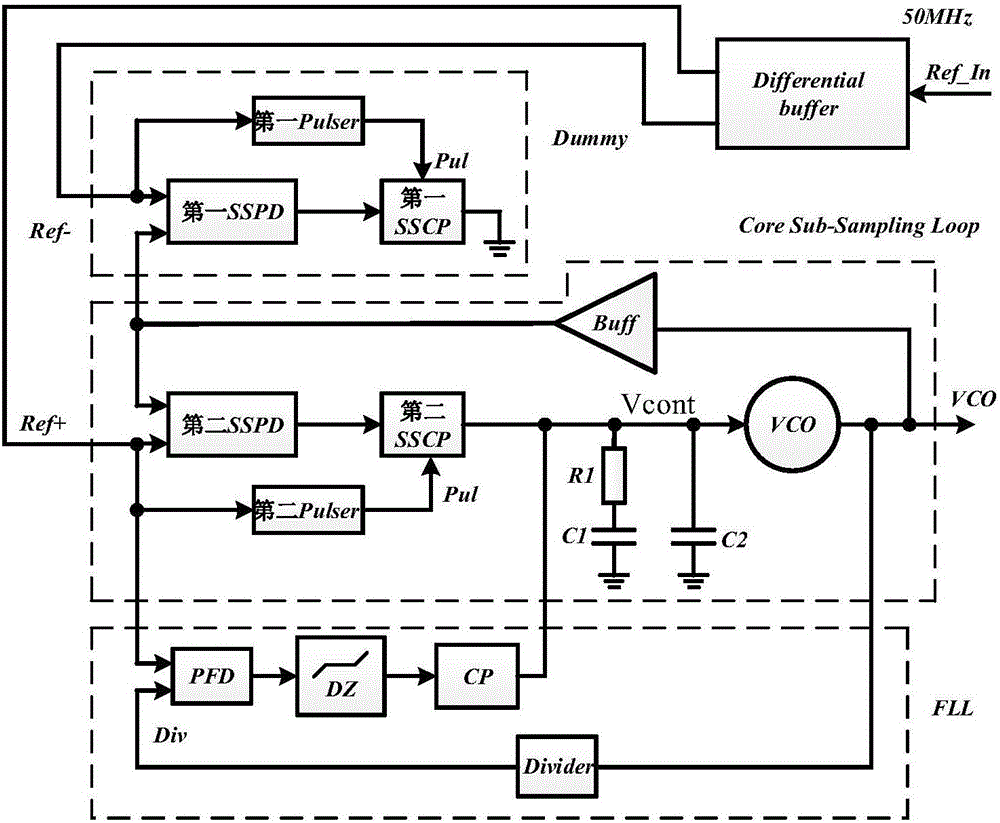

Phase-locked loop low in stray and quick in locking

ActiveCN106603070AEliminate spursReduce distractionsPulse automatic controlTransceiverPhase locked loop circuit

The invention discloses a phase-locked loop low in stray and quick in locking. The phase-locked loop eliminates strays caused by delayed mismatching of a phase frequency detector of a traditional charge pump phase-locked loop and current mismatching of the charge pump, and enables interference of adjacent channels of a radio communication transceiver system to be greatly reduced. Through adoption of a Dummy sampler circuit, reference strays are reduced to a great extent. Moreover, the locking speed can be increased through increases of the current of a phase-locked loop charge pump, so that the overall performance of the phase-locked loop can be improved comprehensively.

Owner:UNIV OF SCI & TECH OF CHINA

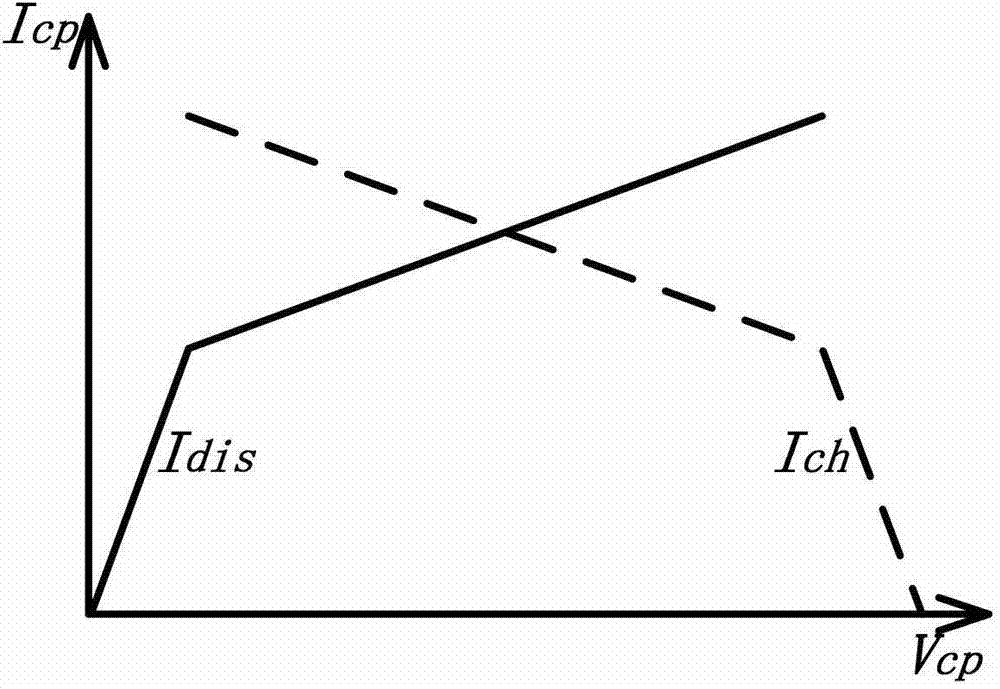

Phase-locked loop with quick response

InactiveCN101719767AImprove linearityGuaranteed featuresPulse automatic controlCharge currentPhase noise

The invention discloses a phase-locked loop with quick response, which comprises a circuit for converting charge pump charging impulse output by a phase frequency detector into slope voltage, a circuit for converting the slope voltage into slope current and a minimum pulse width detection circuit. The quick locking function is realized by linearly increasing the charge pump charging current during the charging of a charge pump. At the same time, when the pulse width is less than a certain value, the function of shielding the current of the slope charge pump ensures that the phase noise is not affected. In the phase-locked loop, the bandwidth of a loop is broadened by linearly increasing the charge pump charging current of the phase-locked loop of the charge pump; and the quick startup characteristics and the phase noise are well guaranteed by recovering the current to an original value in a locking state at the same time.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

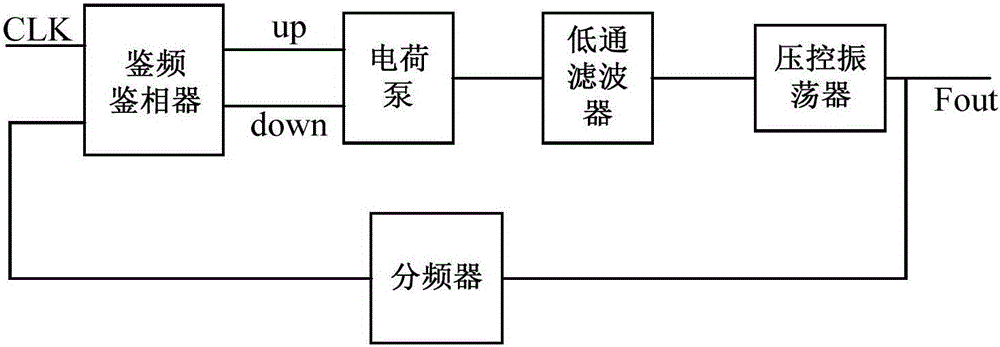

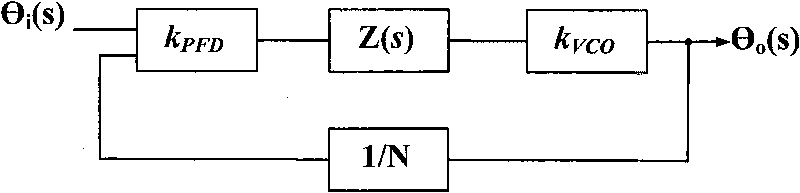

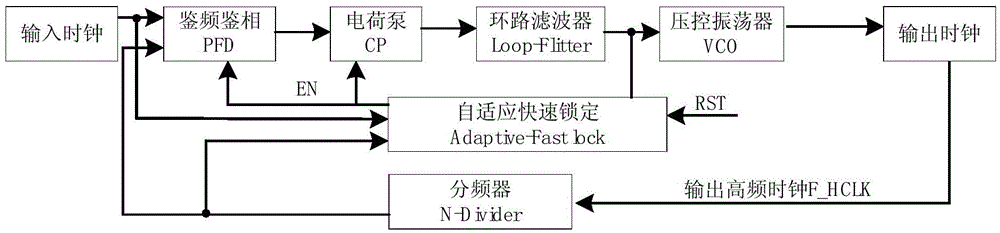

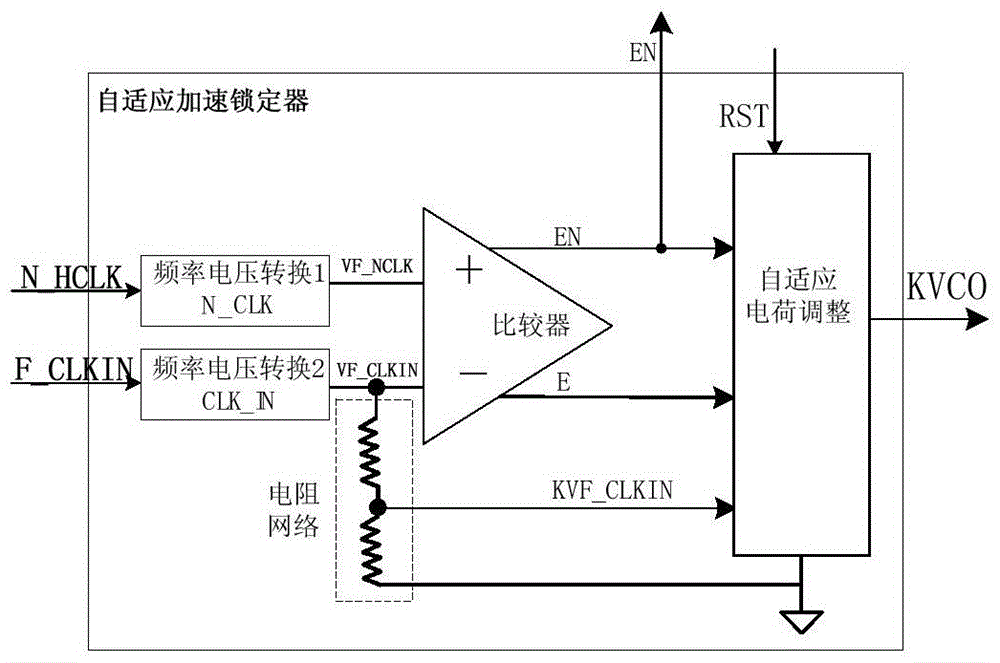

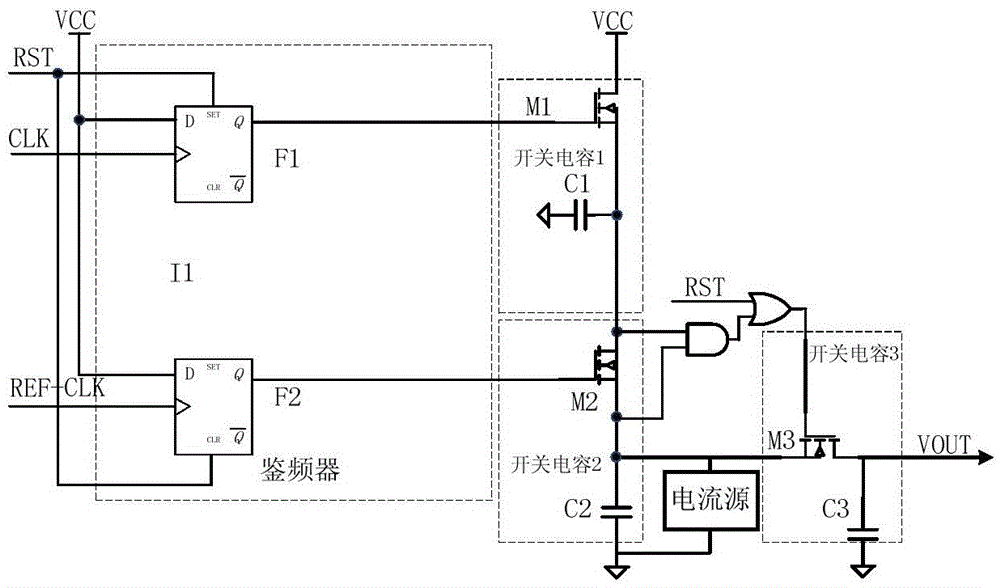

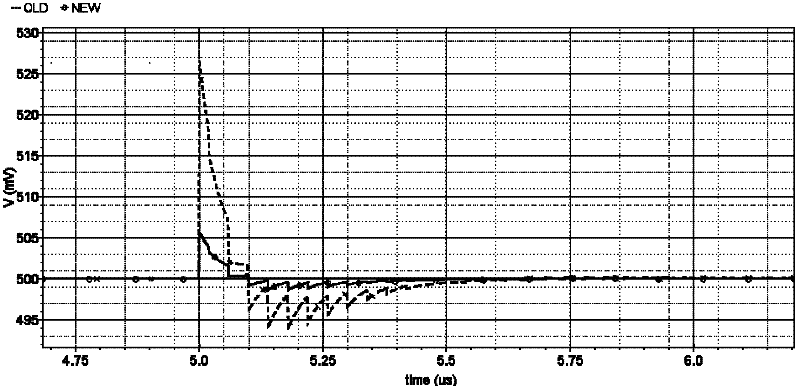

Charge pump phase-locked loop with adaptive acceleration locking structure

InactiveCN105610436AQuick lockAvoid extra jitter injectionPulse automatic controlStable stateCharge pump phase locked loop

The invention discloses a charge pump phase-locked loop with an adaptive acceleration locking structure. The charge pump phase-locked loop with the adaptive acceleration locking structure comprises a frequency and phase discrimination module, a charge pump module, a loop filter module, a voltage-controlled oscillation module and a frequency division module of the conventional charge pump phase-locked loop, and a special adaptive acceleration lock. Such structure can remarkably improve locking speed of the phase-locked loop, and also cannot generate additional jitter for output of the locked phase-locked loop at the same time, and meanwhile, in case of loss of lock caused by external environment, the structure starts by itself to make the loop recover to a steady state quickly.

Owner:XIDIAN UNIV +1

Apparatus to remove the loop filter resistor noise in charge-pump PLL

An improved charge pump based phase locked loop where the loop filter resistor noise is reduced by about an order is presented. The voltage controlled oscillator generates a clock signal, and this is input to the phase detector, which, compares the oscillator clock with the reference clock and using the charge pump it generates a current output proportional to the phase difference. The loop filter converts this proportional current to a voltage and connects it to the oscillator input. The loop filter consists of a capacitor, resistor and the apparatus that bypasses most of the resistor noise.

Owner:TEXAS INSTR INC

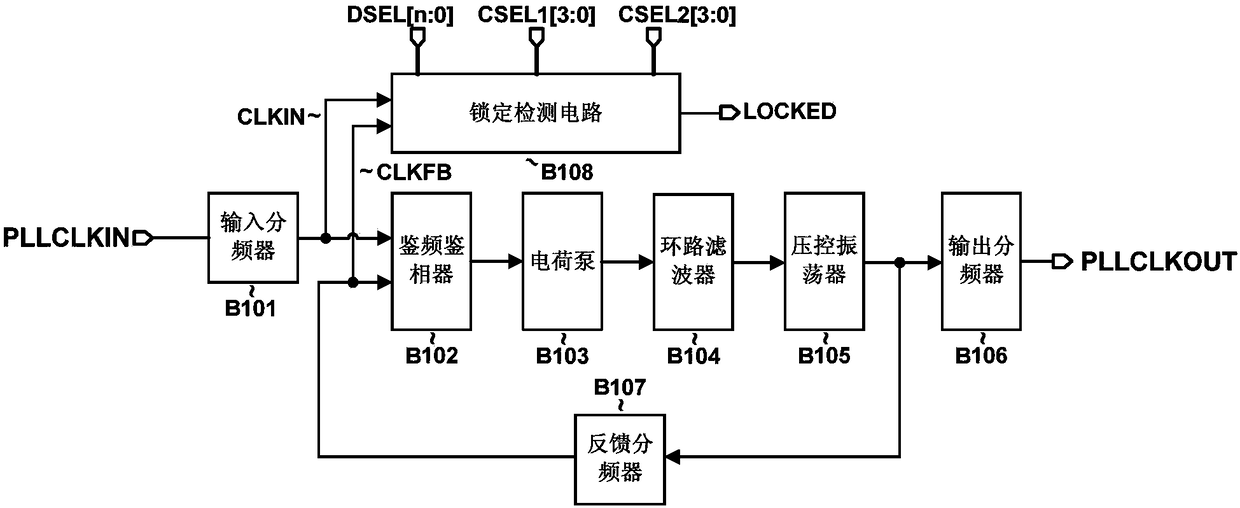

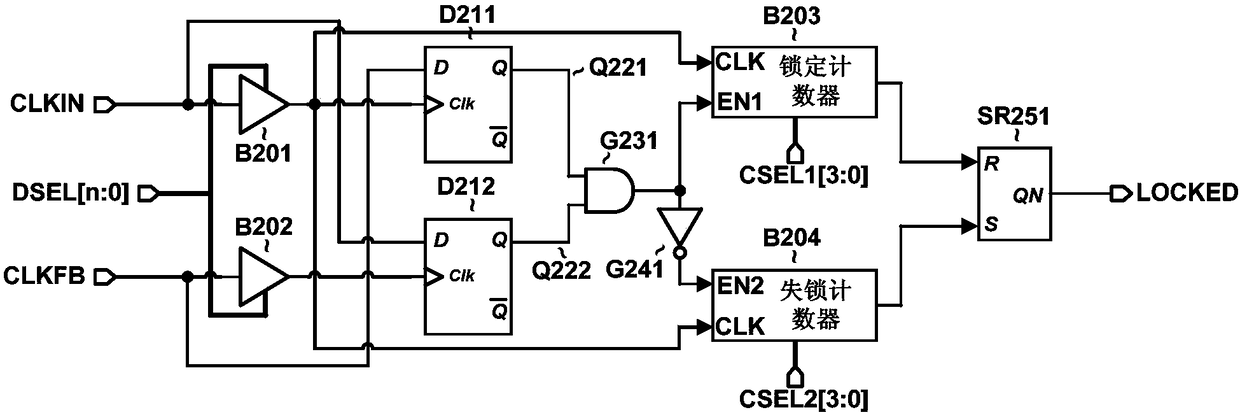

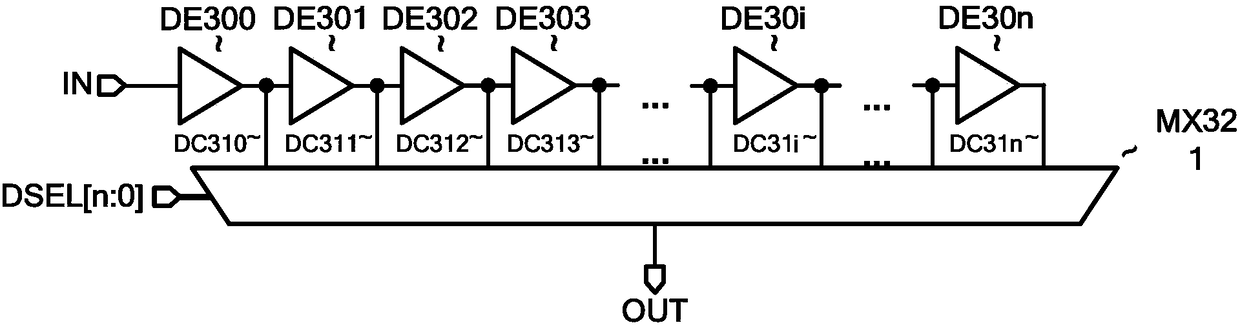

Configurable locking detection circuit applicable to charge pump phase-locked loop

ActiveCN108306638AImprove reliabilityIncrease flexibilityPulse automatic controlPhase differenceEngineering

The invention provides a configurable locking detection circuit applicable to a charge pump phase-locked loop. The configurable locking detection circuit comprises a clock phase difference comparisoncircuit, a locking counter B203, an unlocking counter B204 and an SR latch SR251; the clock phase difference comparison circuit receives two clock signals input from outside and performs phase difference comparison; when the phase difference absolute value is less than or equal to the time window length, the locking counter B203 is enabled; the unlocking counter B204 is reset and forbidden; otherwise, the unlocking counter B204 is enabled; the locking counter B203 is reset and forbidden; the output ends of the locking counter B203 and the unlocking counter B204 are connected to the R end and the S end of the SR latch SR251; and the output end of the SR latch SR251 is the locking indication signal of the configurable locking detection circuit. By means of the circuit provided by the invention, the false unlocking probability can be reduced; and the reliability of the locking detection circuit is improved.

Owner:BEIJING MXTRONICS CORP +1

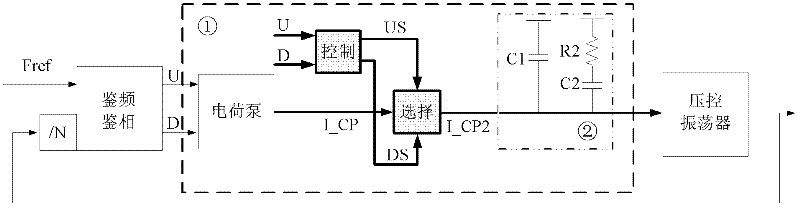

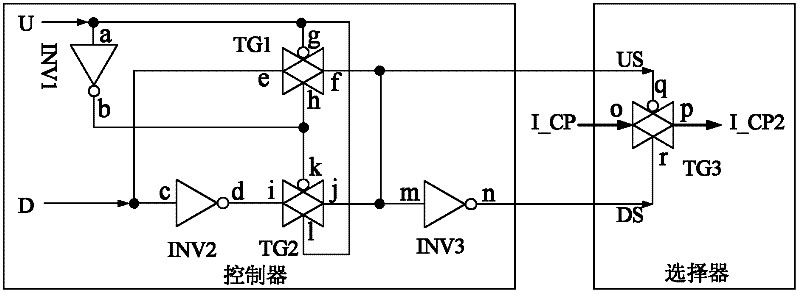

Charge pump and low-pass filter component with anti-single particle radiation circuit

InactiveCN102291128AReduce power consumptionSimple structurePulse automatic controlNumerical controlPhase locked loop circuit

The invention belongs to the field of microelectronic chip designing and manufacturing, and discloses a charge pump and low-pass filter component with an anti-single particle radiation circuit. The component comprises a charge pump, a low-pass filter and a numerical control suppression circuit, wherein the numerical control suppression circuit is arranged between the charge pump and the low-pass filter, comprises a controller and a selector, and can suppress current interference pulses generated by single particle radiation in real time. The whole charge pump phase-locked loop (CPPLL) circuitworks normally when the single particle radiation does not exist, and is controlled to be intercepted when the single particle radiation exists, to prevent the influence of the radiation current interference pulses on a post circuit when the single particle radiation exists. Therefore, the component is easy to integrate and has the characteristics of effectively improving the overall output jitter performance and single particle radiation resistance of the phase-locked loop circuit, reducing a control voltage peak value by about 80 percent, shortening stabilization time by about 50 percent, along with simple circuit structure, low power consumption, small area, high working speed, high compatibility and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

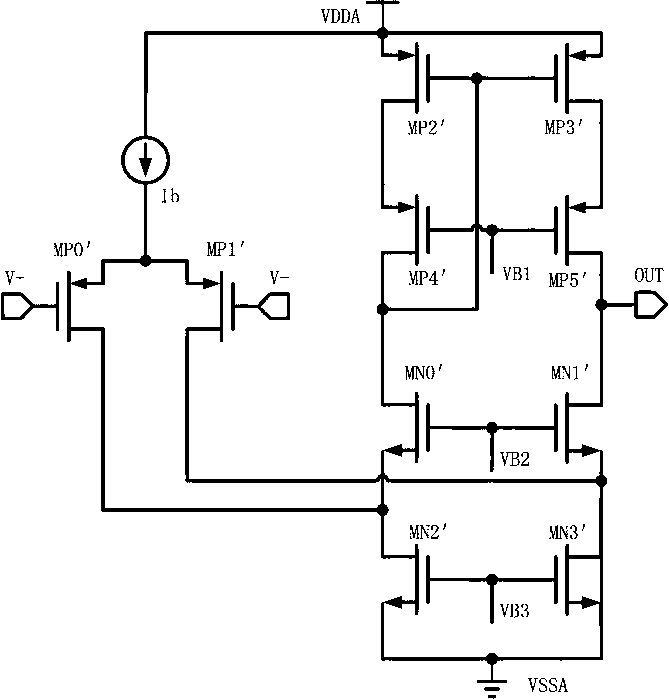

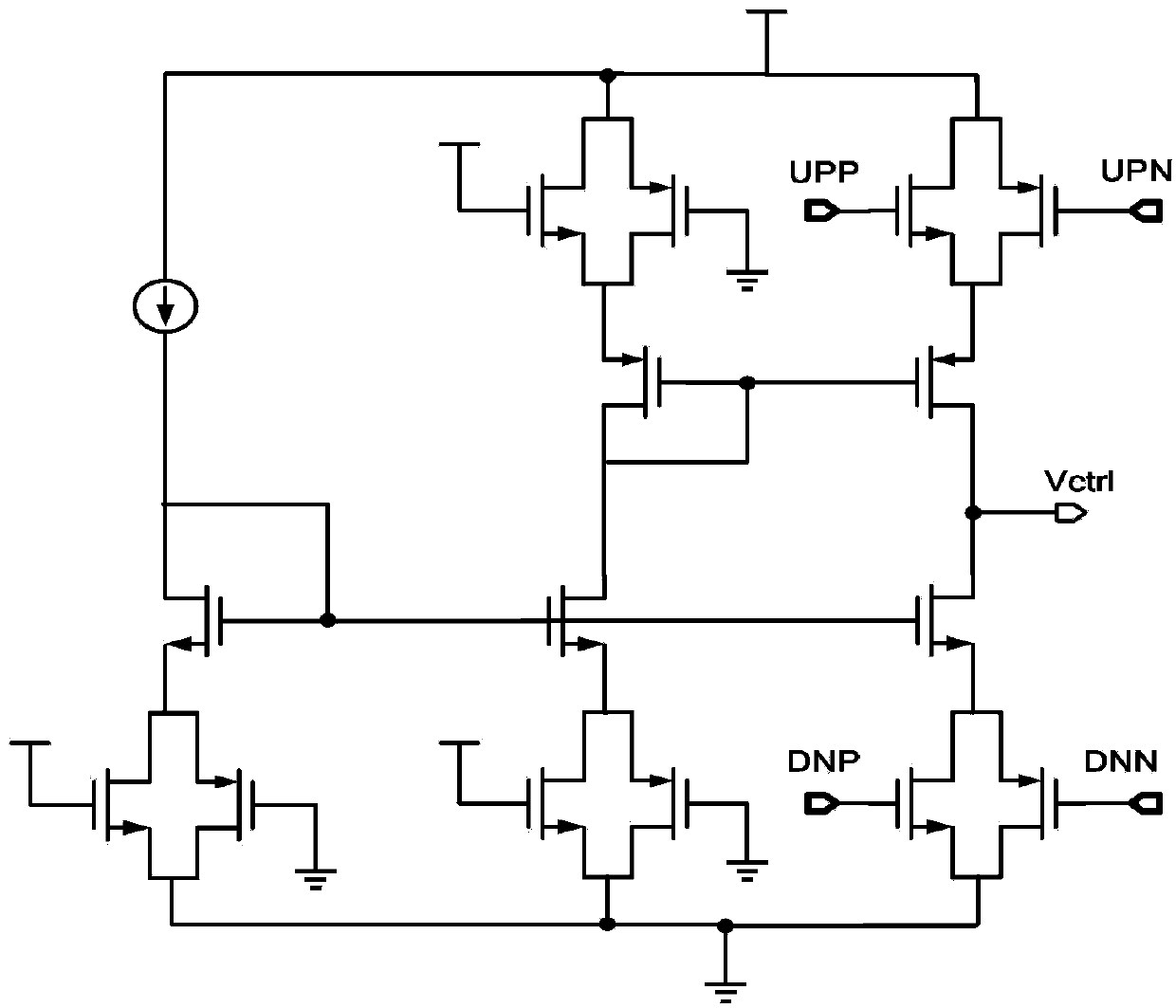

High-performance charge pump circuit in low-voltage charge pump phase-locked loop

ActiveCN103390998ASuperior static matching performanceImprove stabilityApparatus without intermediate ac conversionAudio power amplifierLow voltage

The invention relates to a high-performance charge pump circuit in a low-voltage charge pump phase-locked loop. The high-performance charge pump circuit comprises a charge-discharge circuit and a current duplicate circuit, wherein a first current duplicate branch circuit, a second current reproduce branch circuit, a first charge-discharge branch circuit and a second charge-discharge branch circuit are connected with a bias circuit; the second current duplicate branch circuit and the first charge-discharge branch circuit are connected with a first rail-to-rail operational amplifier; the first current duplicate branch circuit and the second charge-discharge branch circuit are connected with a second rail-to-rail operational amplifier; an output end of the first rail-to-rail operational amplifier is connected with a non-inverting input end through a first Miller compensating circuit; an output end of the second rail-to-rail operational amplifier is connected with a non-inverting input end through a second Miller compensating circuit; and the current ratio of the second charge-discharge branch circuit to the first current duplicate branch circuit and the current ratio of the first charge-discharge branch circuit and the second current duplicate branch circuit are equal. According to the high-performance charge pump circuit in the low-voltage charge pump phase-locked loop, the current matching range can be expanded, the dynamic current matching performance is good, the stability is high, and the circuit is safe and reliable.

Owner:杭州中科微电子有限公司

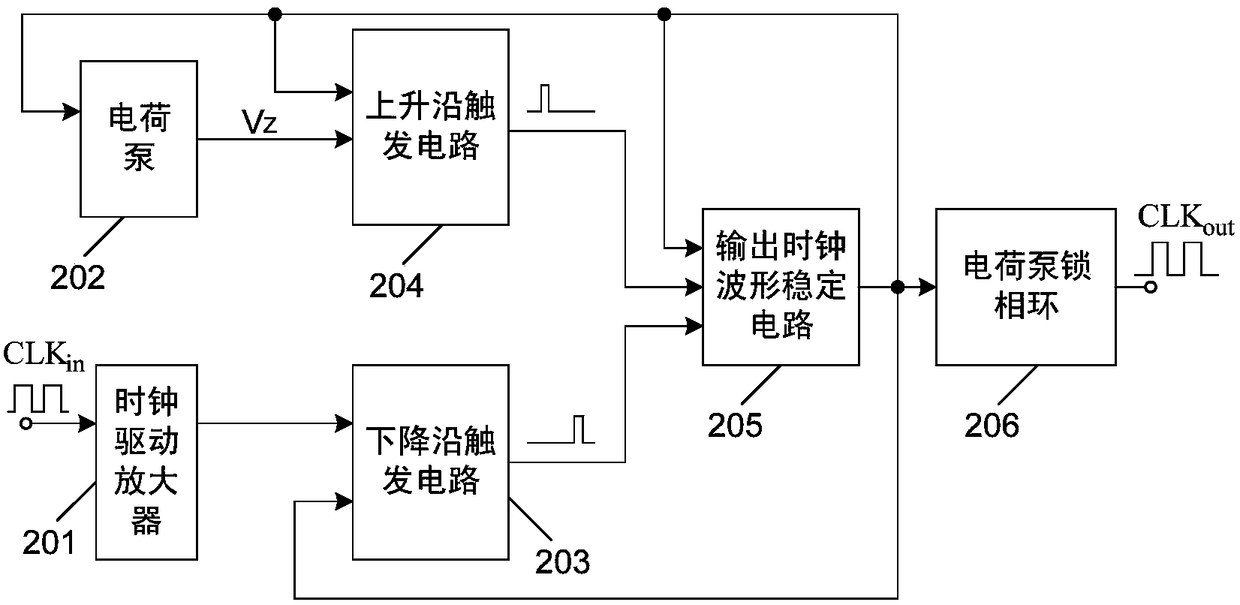

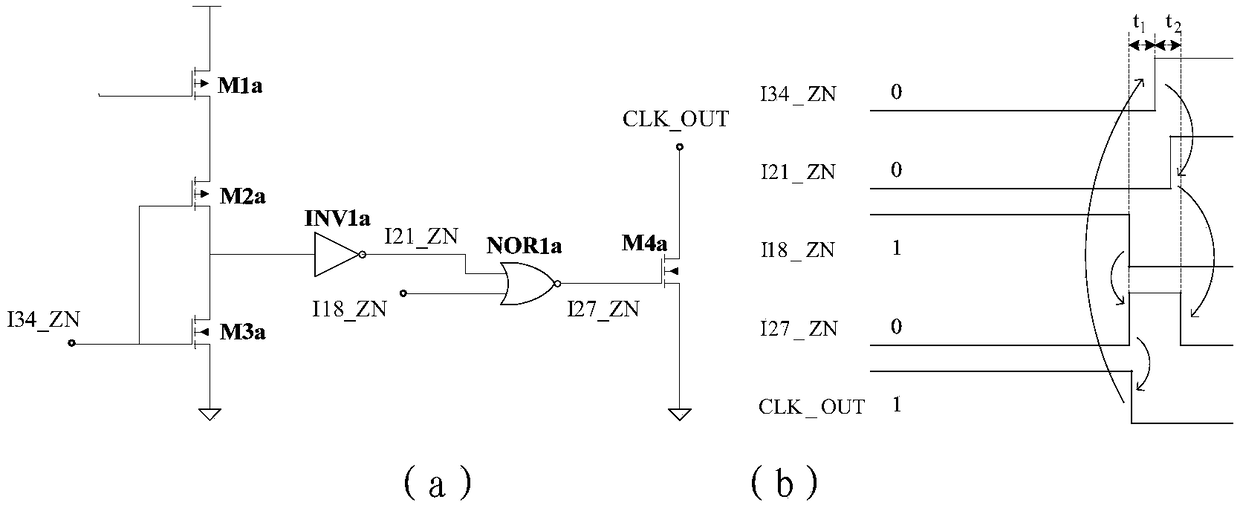

Clock circuit with stable duty ratio and low jitter

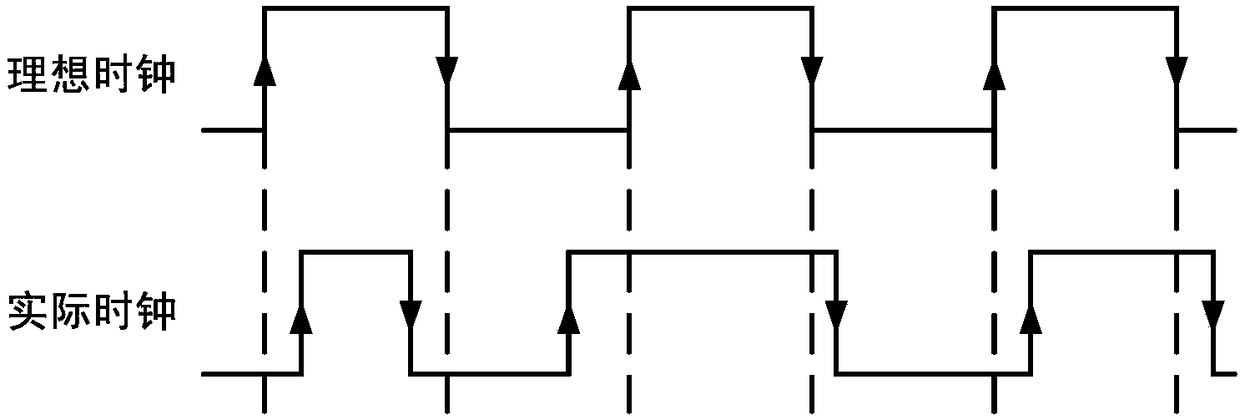

ActiveCN108199699AStable duty cycleMeet demanding requirementsContinuous to patterned pulse manipulationPulse shapingAudio power amplifierLow jitter

The invention discloses a clock circuit with a stable duty ratio and low jitter. The whole clock circuit comprises a clock driving amplifier module, a charge pump module, an output clock falling edgetriggering circuit module, an output clock rising edge triggering circuit module, an output clock waveform stabilization circuit module and a charge pump phase-locked loop module. The clock waveform stabilization circuit generates a complete output clock according to edge control pulses generated by rising edge and falling edge control circuits; the falling edge triggering circuit enables a falling edge of an output clock and a falling edge of an input clock to maintain consistent; the rising edge triggering circuit can take the output clock falling edge as a reference to adjust the output clock rising edge position according to a duty ratio detection result of the input clock, so that the duty ratio of the output clock is finally stabilized to 50%; and the charge pump phase-locked loop receives the output clock of the output clock waveform stabilization circuit module and generates a high-speed low-jitter clock signal. The clock circuit can meet a rigorous requirement for a clock signal in high-frequency application.

Owner:BEIJING MXTRONICS CORP +1

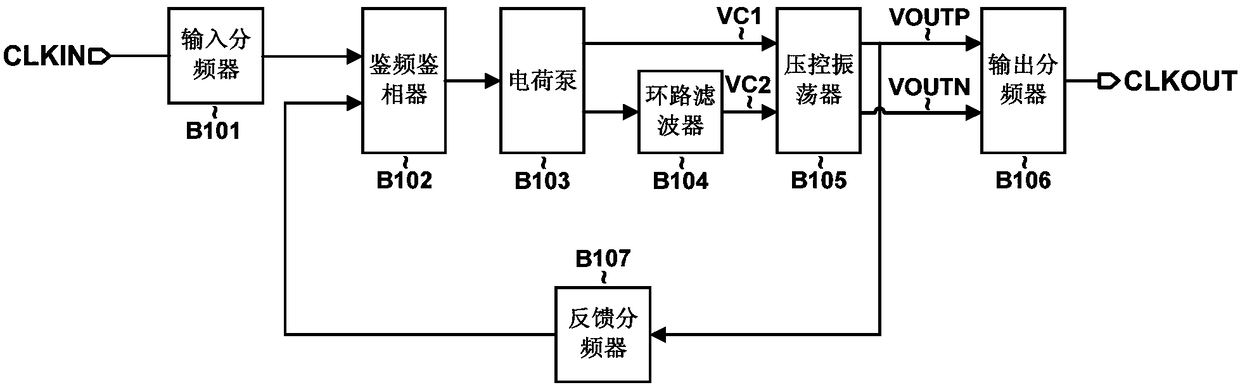

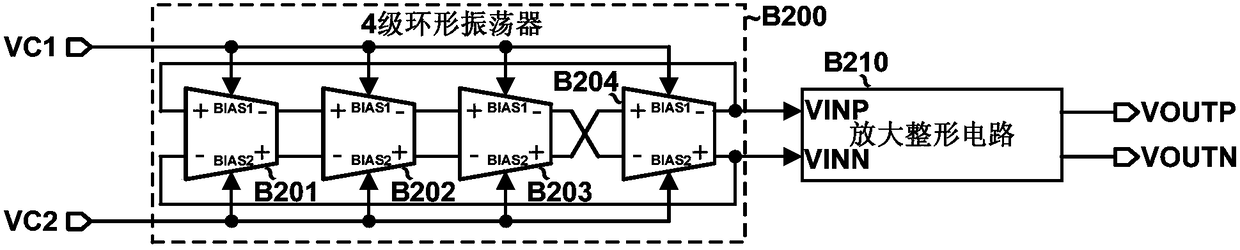

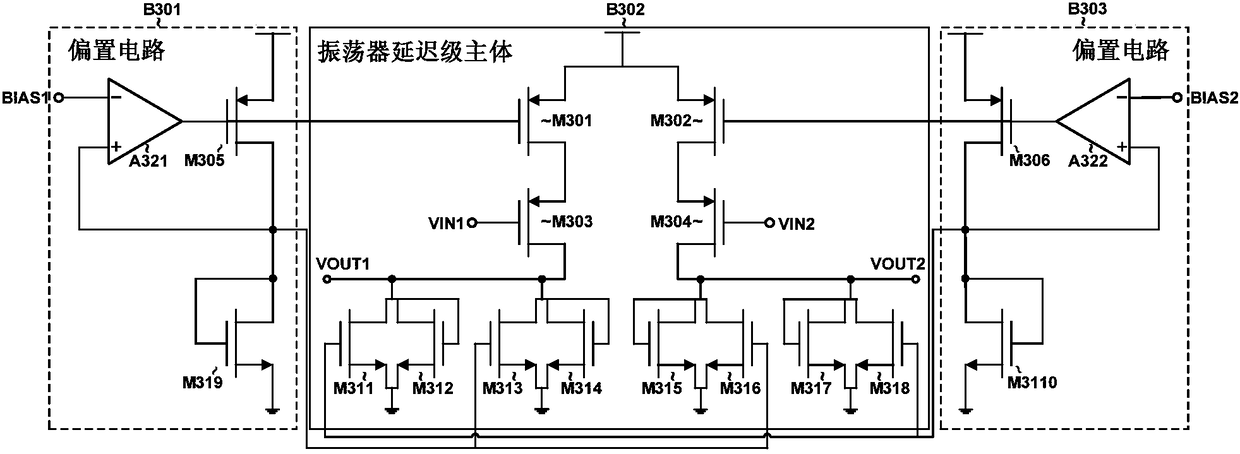

Charge pump phase locking loop adopting two voltages for control of voltage-controlled oscillator

ActiveCN108306637AGuaranteed Oscillating Signal-to-Noise PerformanceIncrease changePulse automatic controlSignal qualityEngineering

The invention provides a charge pump phase locking loop adopting two voltages for control of a voltage-controlled oscillator. The phase locking loop comprises an N-stage ring oscillator B200 and an amplifying and shaping circuit B201; the N-stage ring oscillator receives two control voltages respectively generated by a charge pump and a loop filter of the charge pump phase locking loop, and generates sine-wave oscillation signals at a certain frequency according to the control voltages; and the sine-wave oscillation signals are shaped into square-wave oscillation signals which serve as input signals of a digital frequency divider of the charge pump phase locking loop. Compared with the traditional voltage-controlled oscillator, the charge pump phase locking loop provided by the invention has the advantages that the two control voltages VC1 and VC2 serve as tuning voltages, VC1 serves as a coarse tuning voltage, and VC2 serves as a fine tuning voltage, so that both a high tuning speed and a high oscillation signal quality can be guaranteed, and the locking of the charge pump phase locking loop can be effectively accelerated.

Owner:BEIJING MXTRONICS CORP +1

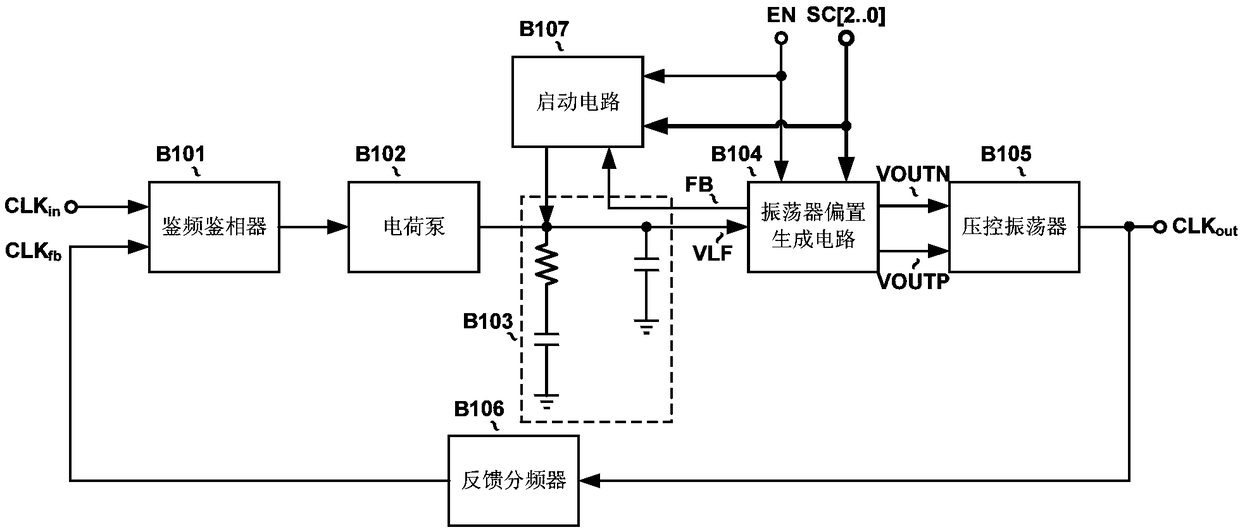

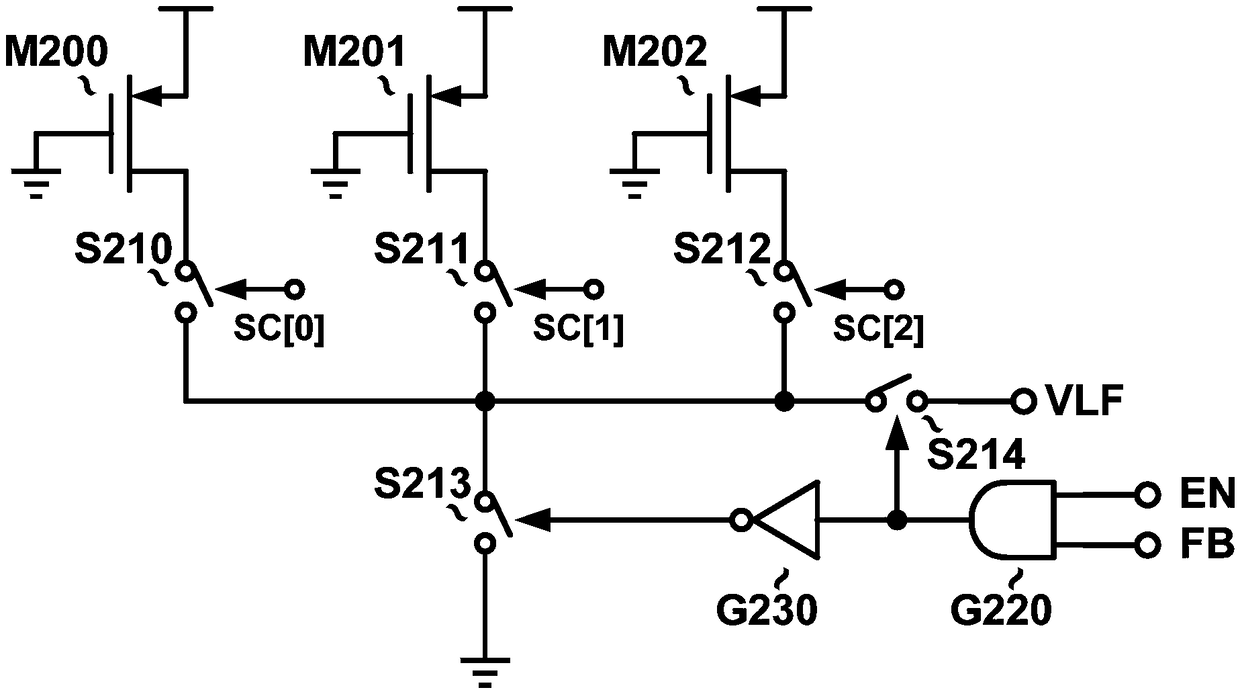

Charge pump phase-locked loop of configurable start-up circuit

ActiveCN108718195AShorten lock timeLatency overheadPulse automatic controlEngineeringBiological activation

The invention discloses a charge pump phase-locked loop of a configurable start-up circuit. The charge pump phase-locked loop charges a loop filter B103 through the configurable start-up circuit B107before the phase-locked loop operates, generates a start-up voltage, drives an oscillator bias generation circuit B104 to generate a bias voltage, and controls a voltage-controlled oscillator B105 tooscillate, so that the voltage-controlled oscillator starts to oscillate at a specific frequency close to a target frequency, and the activation of the phase-locked loop is completed. Compared with aconventional charge pump phase-locked loop, a user can operate the voltage-controlled oscillator at the specific frequency by a configuring signal before the phase-locked loop starts to work accordingto actual needs, thereby accelerating the locking process of the phase-locked loop after the phase-locked loop starts to work.

Owner:BEIJING MXTRONICS CORP +1