Phase-locked loop low in stray and quick in locking

A fast locking and phase-locked loop technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of large CP current mismatch of the charge pump, affecting system stability and locking time, etc., to achieve overall performance improvement, reference miscellaneous Dispersion reduction, interference reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

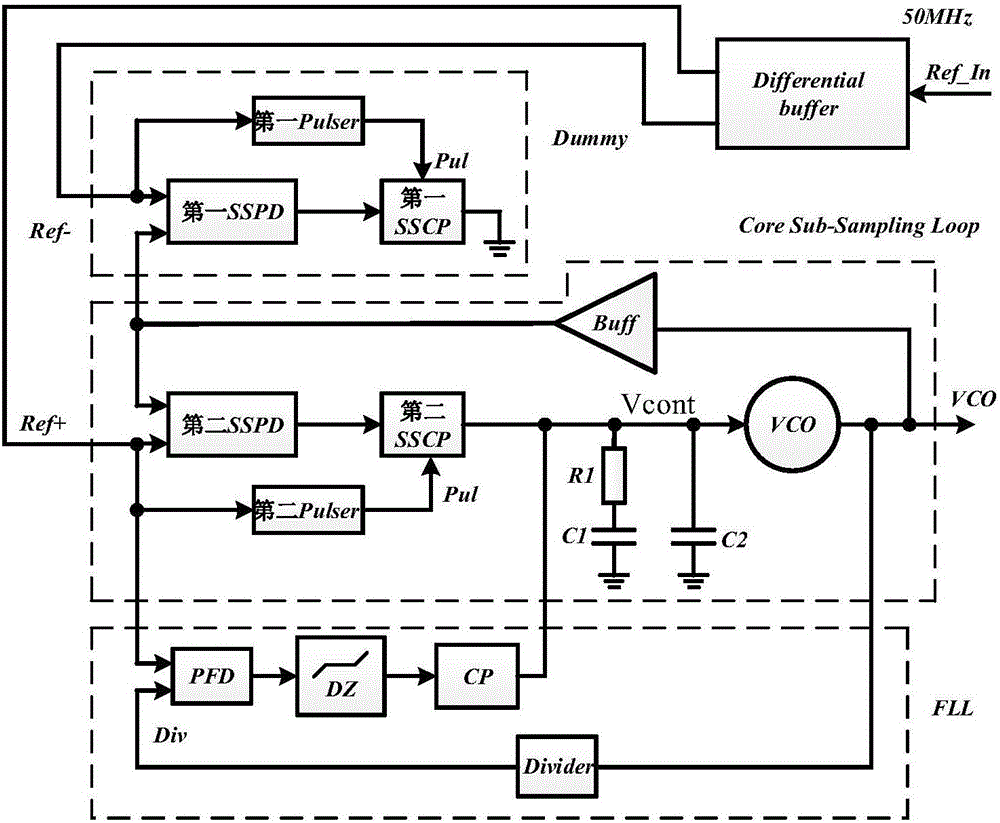

[0044] image 3It is a schematic structural diagram of a phase-locked loop circuit with low spurious fast locking provided by the embodiment of the present invention. Such as image 3 As shown, it mainly includes: differential buffer (Differential buffer), Dummy sampler circuit, sub-sampling loop (Core Sub-Sampling Loop) and frequency-locked loop FLL (Frequency-locked Loop); wherein,

[0045] The differential buffer converts the reference signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More