A kind of synchronous clock reference source and synchronous clock reference generation method

A technology for synchronizing clocks and generating methods, applied in the direction of electrical components, automatic power control, etc., can solve the problems of logic driver noise, complex circuits, complex peripheral circuits, etc., to reduce device costs, eliminate harmonic noise, and reduce the number of devices. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

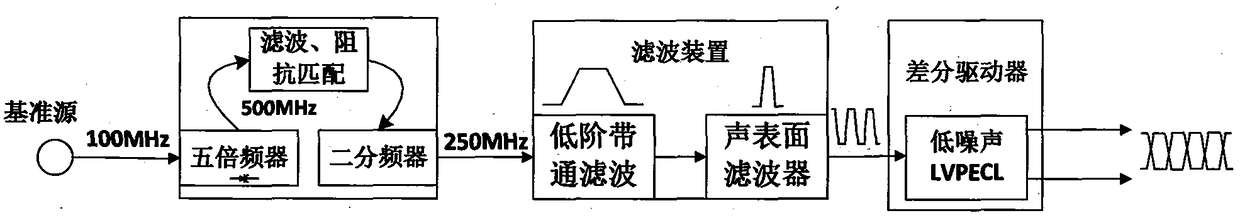

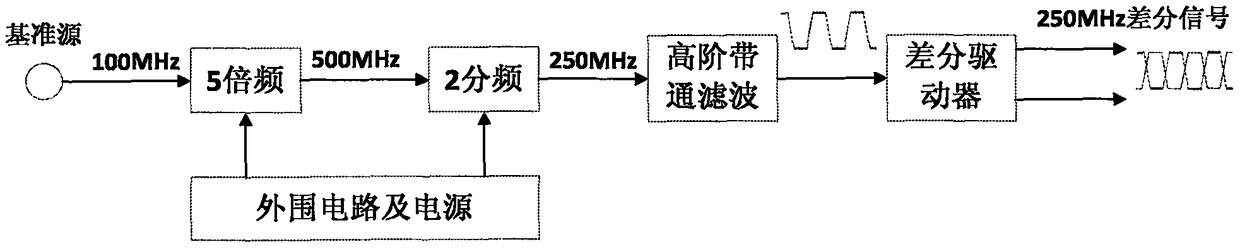

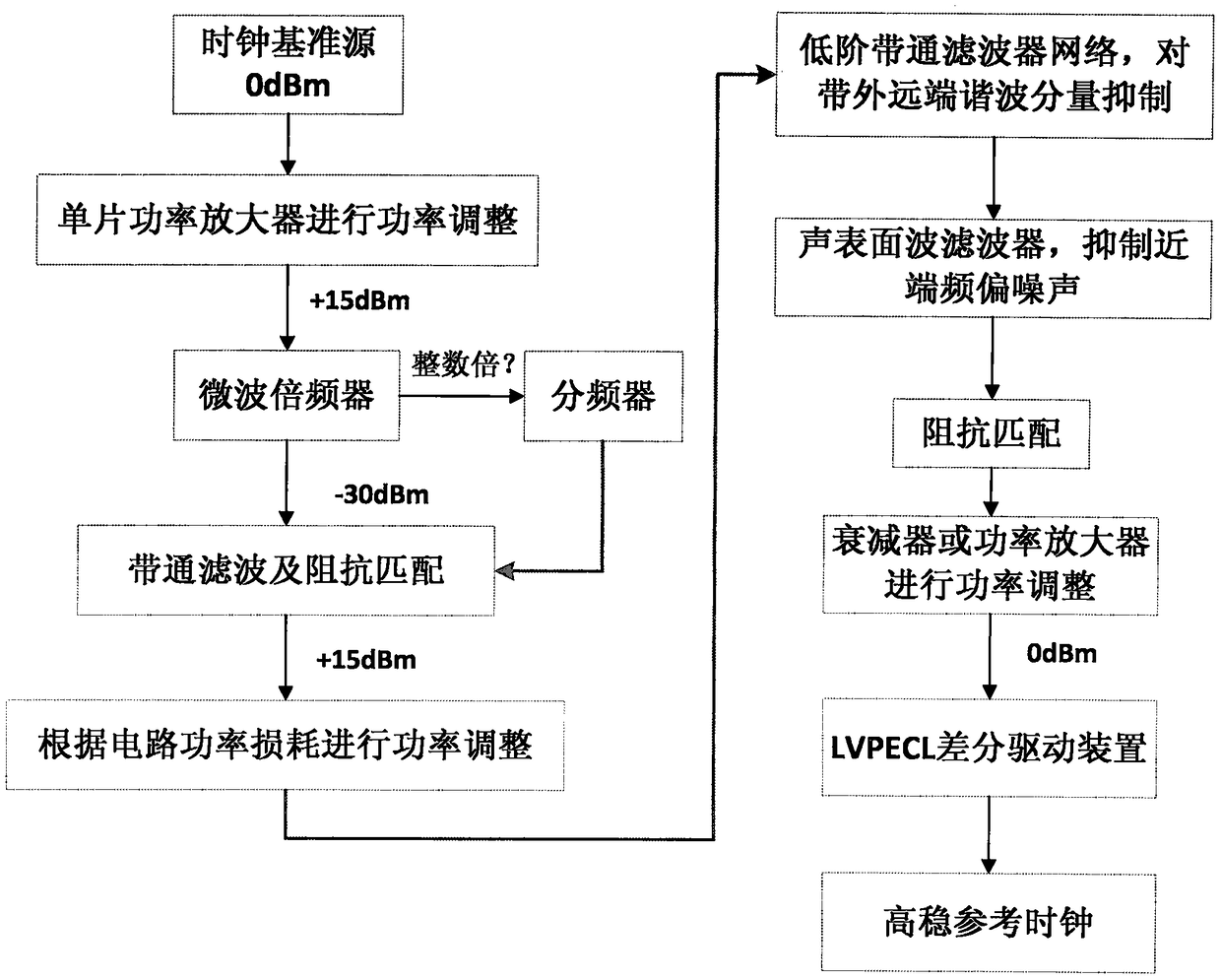

[0044]In the field of electronic measurement, measuring instruments need to provide a stable and reliable high-performance clock reference source when converting analog signals and digital signals (A / D, D / A), and the clock frequency can reach up to several hundred MHz. In general, the time base reference frequency provided by the whole machine has a high performance index and a low frequency, so it needs to be multiplied or divided to generate a clock source. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More