Symmetric charge pump replica bias detector

a charge pump and bias detector technology, applied in the direction of automatic control, process and machine control, instruments, etc., can solve the problems of asymmetric and long turn-off decay, switching transients still not optimally reduced, and low cost, and small siz

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

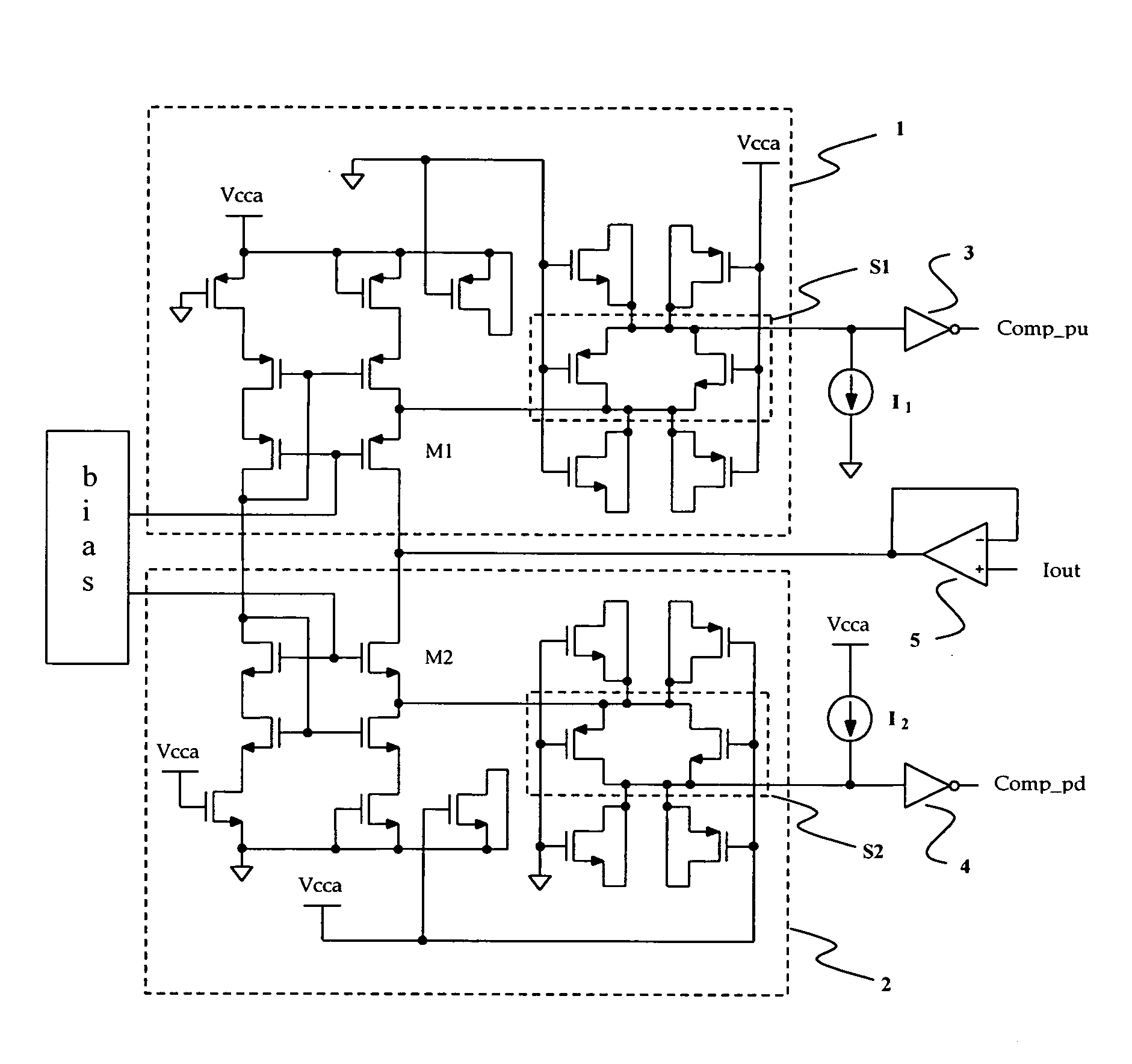

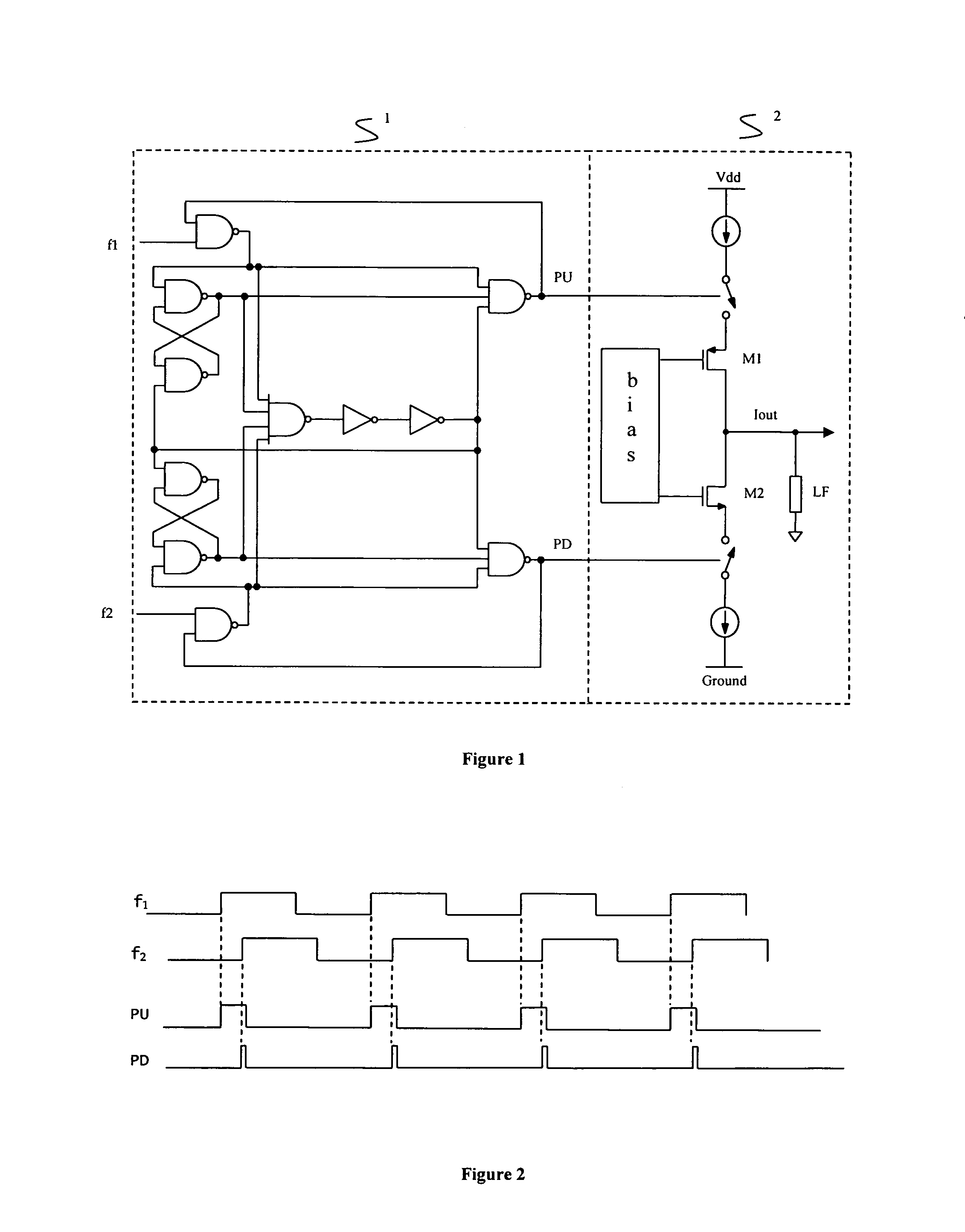

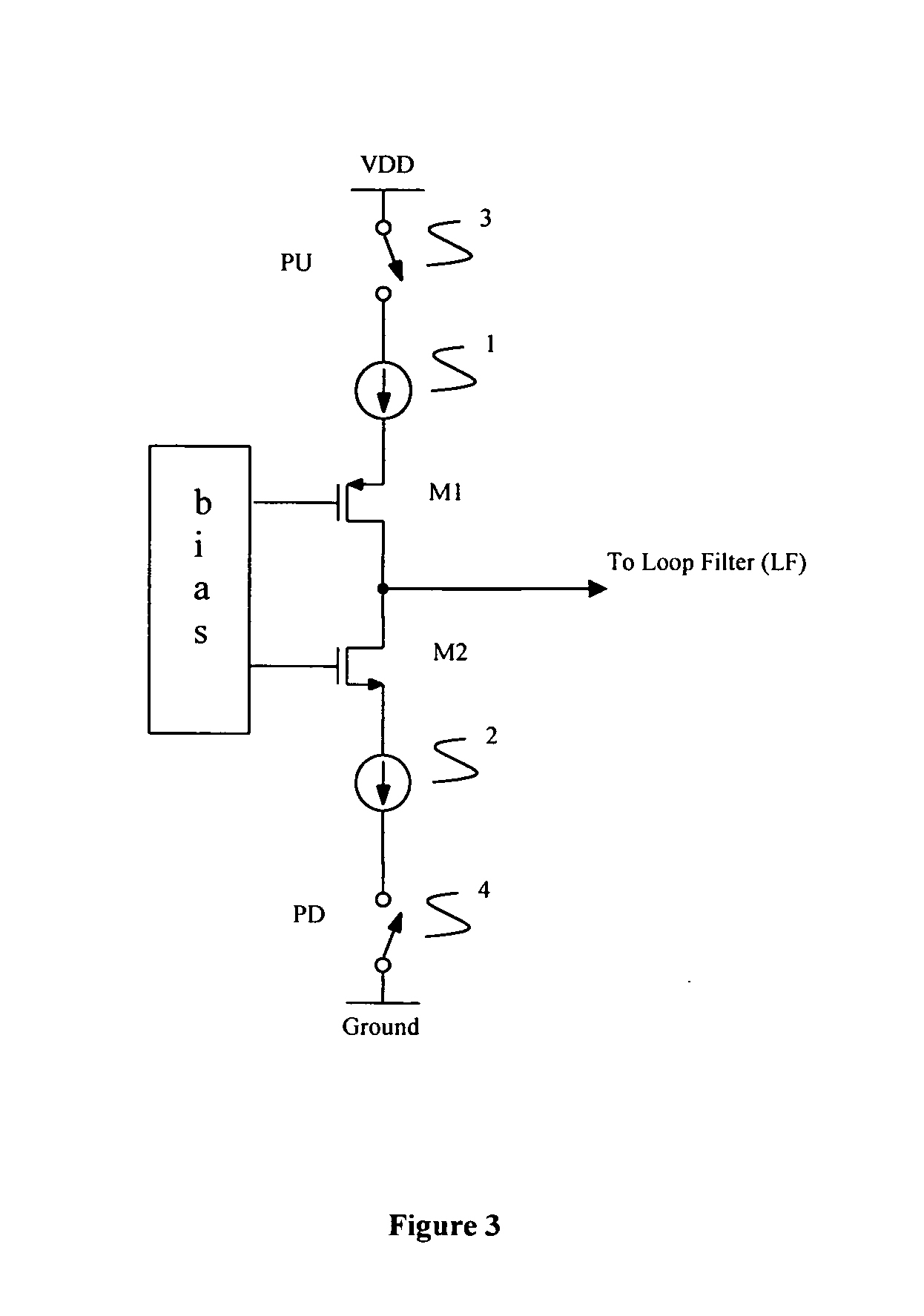

[0043]FIG. 4 is a schematic of the top-side PMOS current source of a charge pump constructed in accordance with the principles of the present invention. The charge pump theory of operation is common between the top-side PMOS current source and bottom-side current sink circuits. Therefore the explanation on the PMOS top-side circuit is sufficient for the total charge pump section. This embodiment is for a new Charge Pump architecture and design for use in a PLL frequency synthesizer for radio frequency applications including but not limited GSM standard with a very symmetrical charge pump current drive. This novel architecture permits the symmetrical turn-on time, rise time and fall time to be independent in the design and optimization process. The generation of differential output phases for both pump-up, PU and pump-down, PD is synchronized by a PFD and charge pump driver and buffer. All current source and sink cells are identical and should track very well over manufacturing proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More