Idle percent adjustable N-time frequency division circuit of pulse mixing mode

A technology of pulse synthesis and frequency division circuit, applied in the direction of synchronous pulse counter, continuous cycle pulse counter, electrical components, etc., can solve the problem that it is difficult to achieve odd or arbitrary order, and achieve strong PVT change ability, strong resistance and stability Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

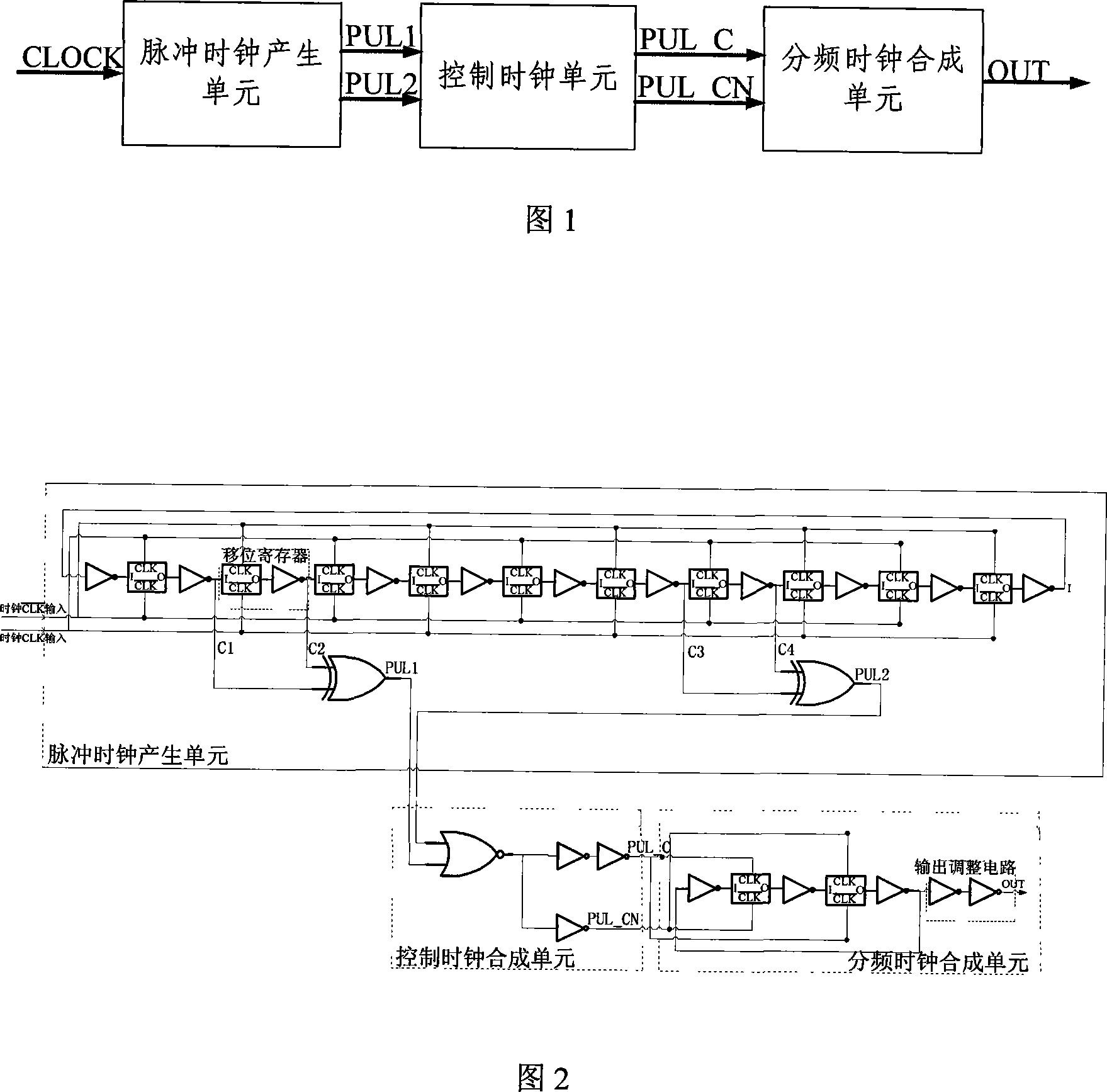

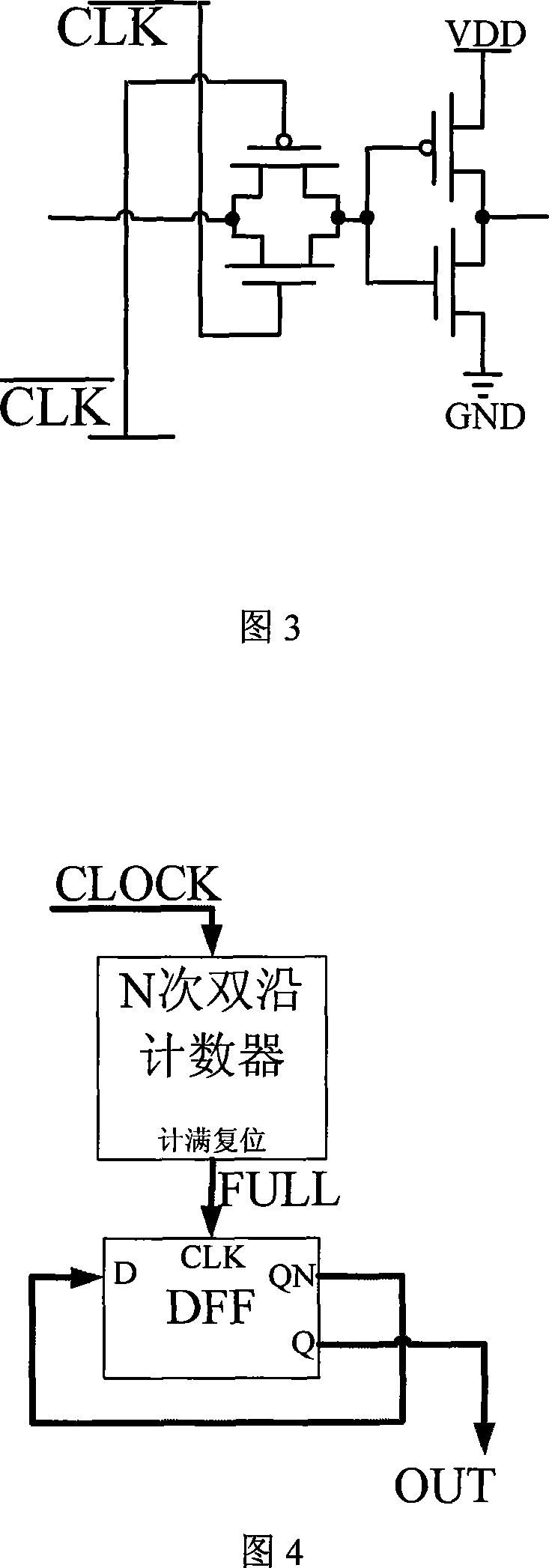

[0019] The invention adopts a dynamic edge trigger register, utilizes the phase difference of the clock signal to generate a double pulse signal with two positive edge / negative edge jumps every N input clock signal cycles, and uses the double pulse signal to obtain N times of frequency division output. As shown in Fig. 1 and Fig. 2, the duty cycle adjustable N times frequency division circuit of the pulse synthesis mode of the present invention comprises: the shift latch cascaded by N dynamic flip-flops in the pulse clock generating unit wherein N is the frequency division ratio of the input clock (10 stages in this embodiment), the control clocks of the odd-stage shift register and the even-stage shift register are reversely connected, and the output of the last stage shift register is passed through an inverted After the phase conve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More