Frequency divider

A frequency divider and frequency division technology, which is applied in pulse counters, synchronous pulse counters, counting chain pulse counters, etc., and can solve the problems of complex circuit combination.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

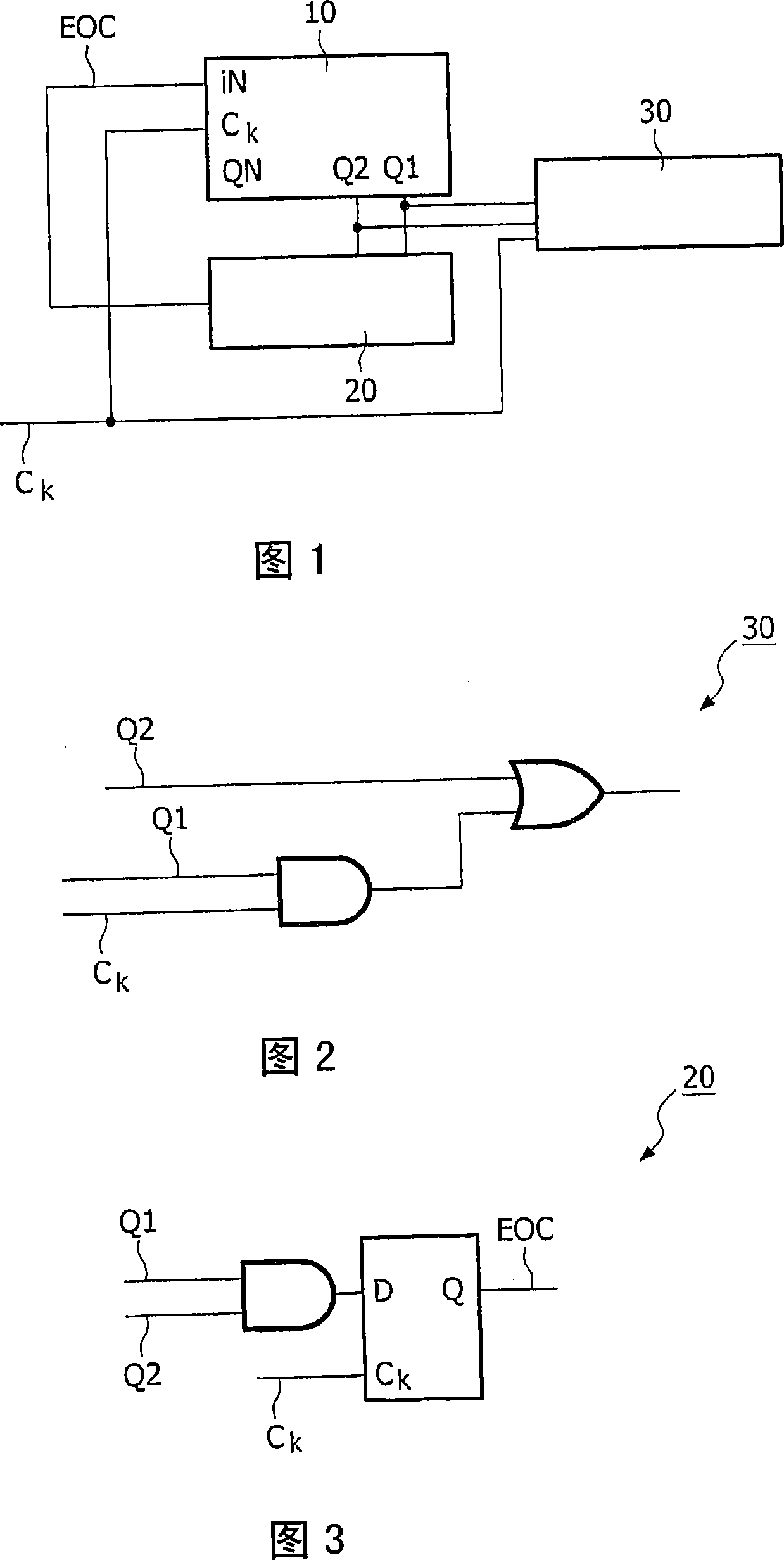

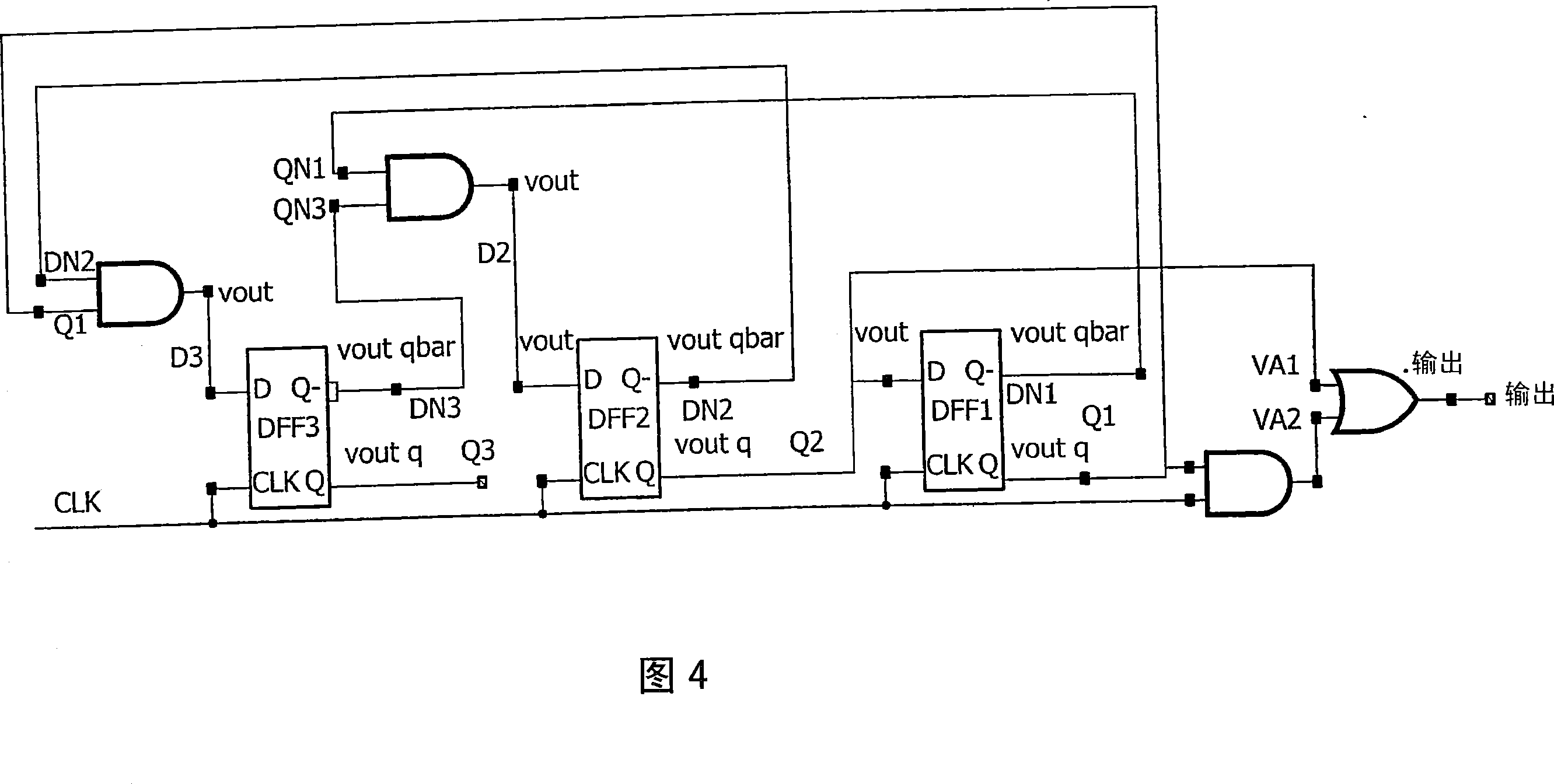

[0024] Fig. 1 shows a block diagram of a frequency divider according to an embodiment of the present invention. The frequency divider providing an odd frequency division factor comprises a binary counter 10 providing an even frequency division factor. This even frequency division factor is obtained by subtracting one from the odd frequency division factor. The binary counter has a clock input for receiving a periodic clock signal Ck having a frequency. The frequency divider also includes an end-of-count circuit 20 connected to the binary counter. The end-of-count circuit 20 generates an end-of-count signal EOC of a cycle of the clock Ck after every even cycle of the clock signal Ck. The count end signal EOC is input to the input terminal IN of the counter 10 . Described frequency divider also comprises the output generator 30 that is connected with binary counter and clock signal Ck, and output generator 30 produces output signal OUT, and the frequency of this signal and odd...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More