Patents

Literature

79 results about "Gmsk modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

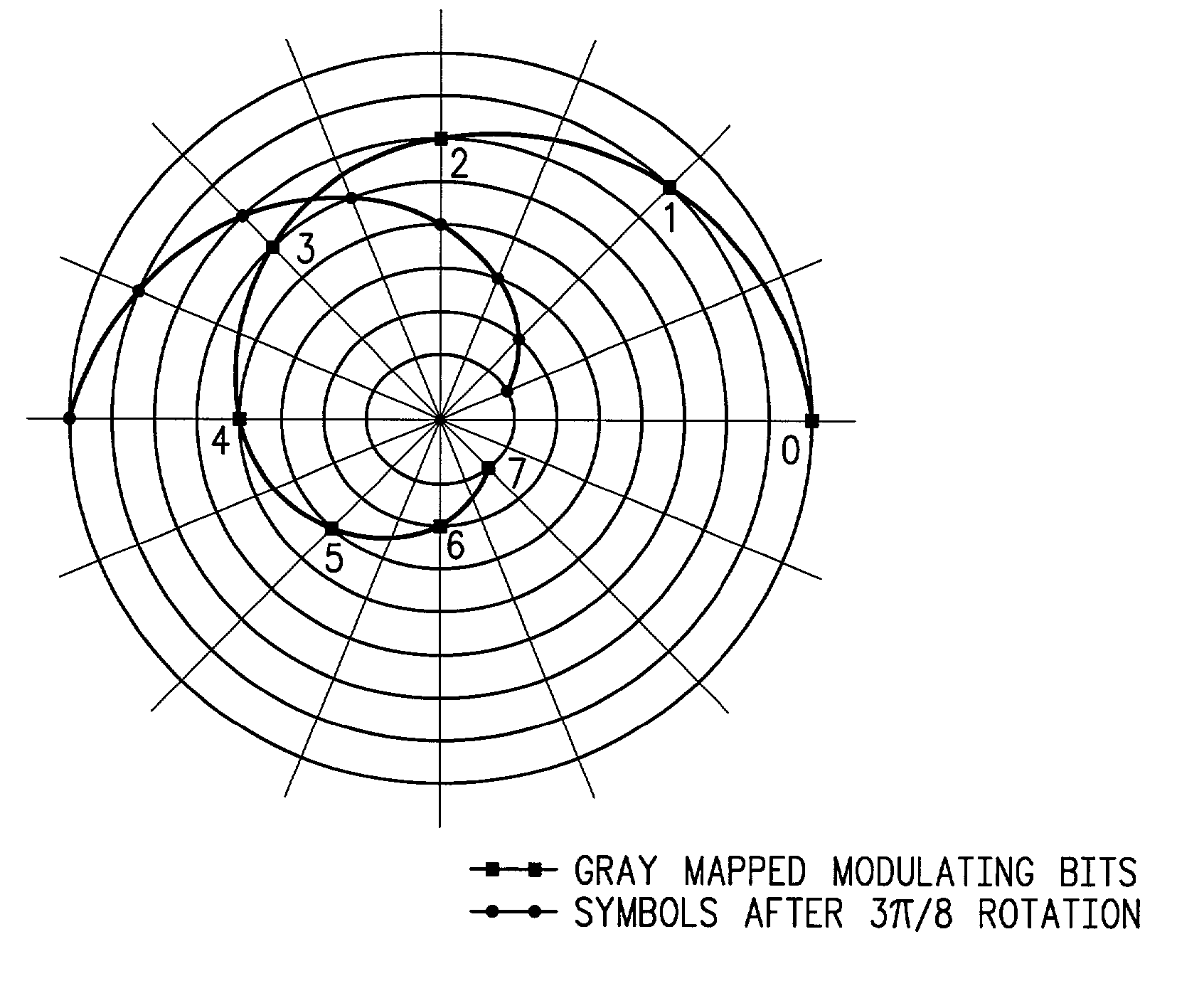

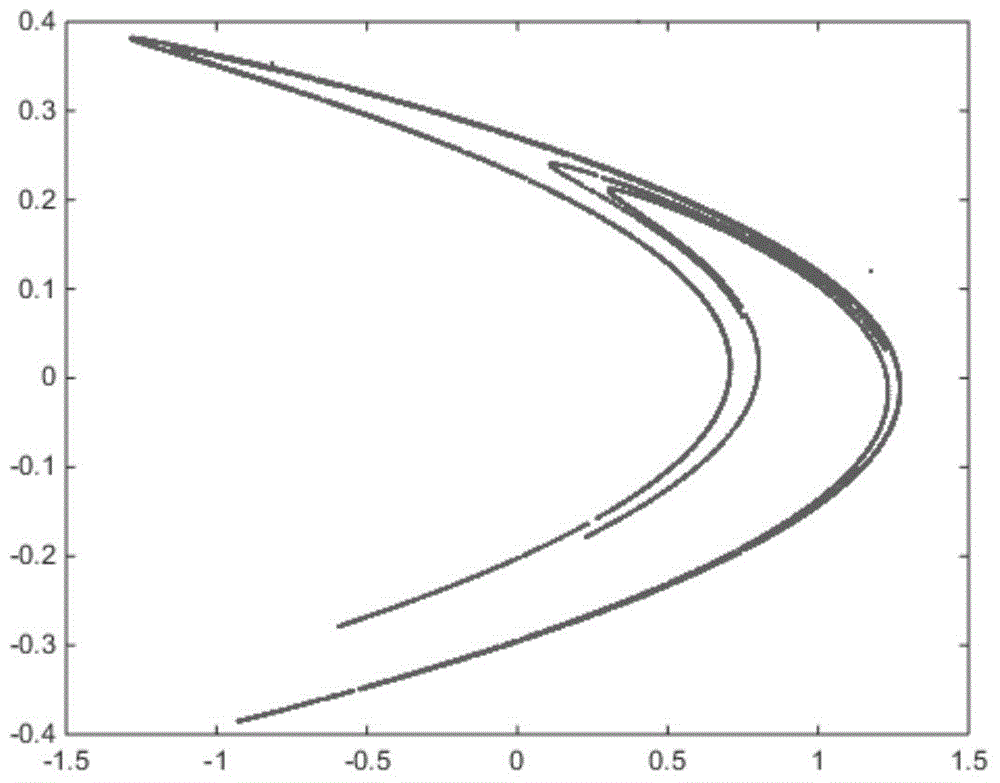

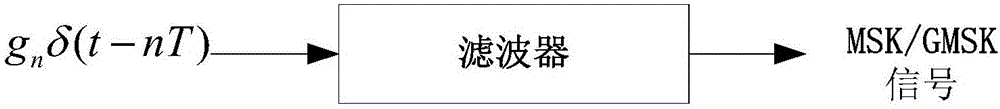

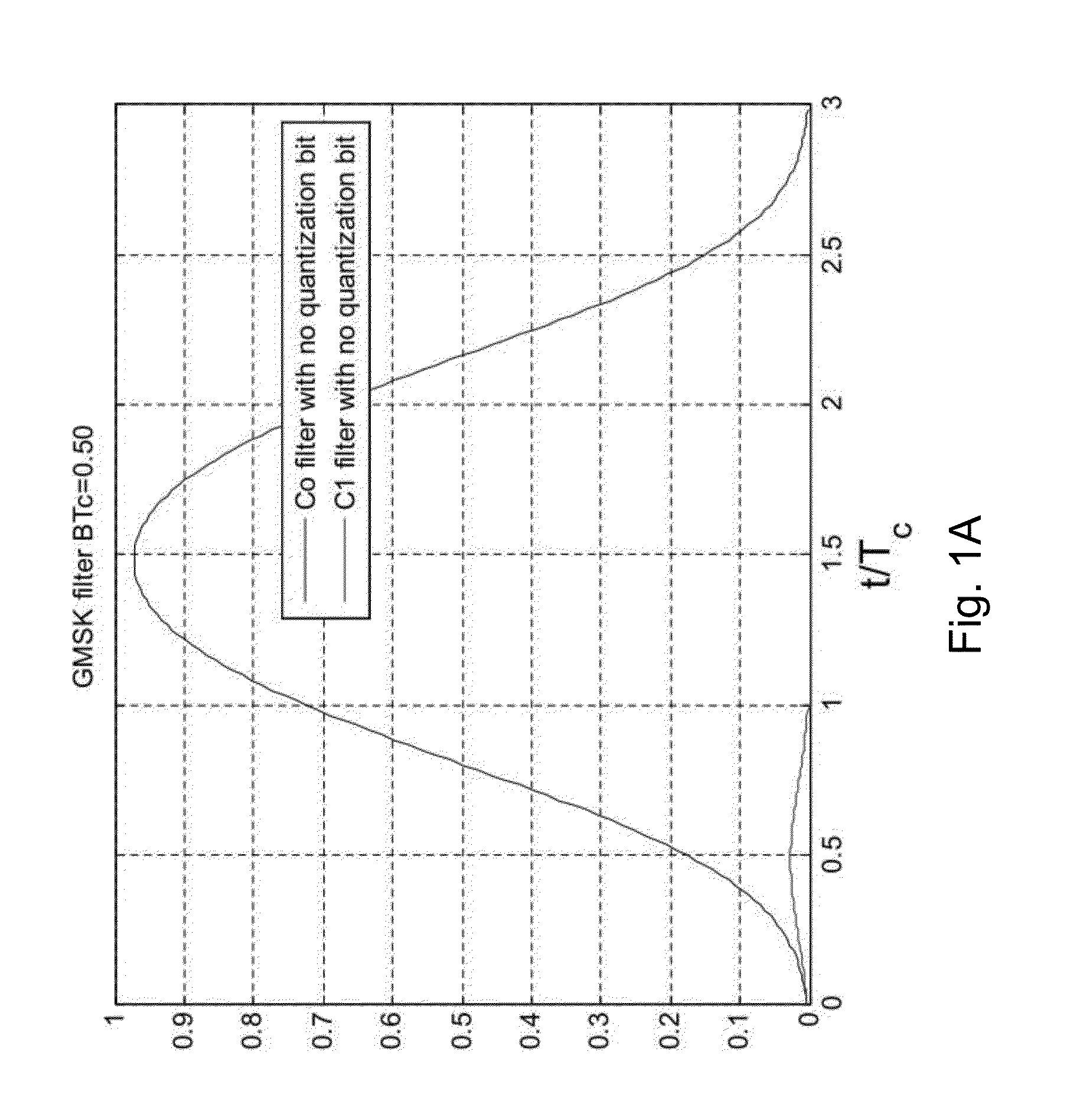

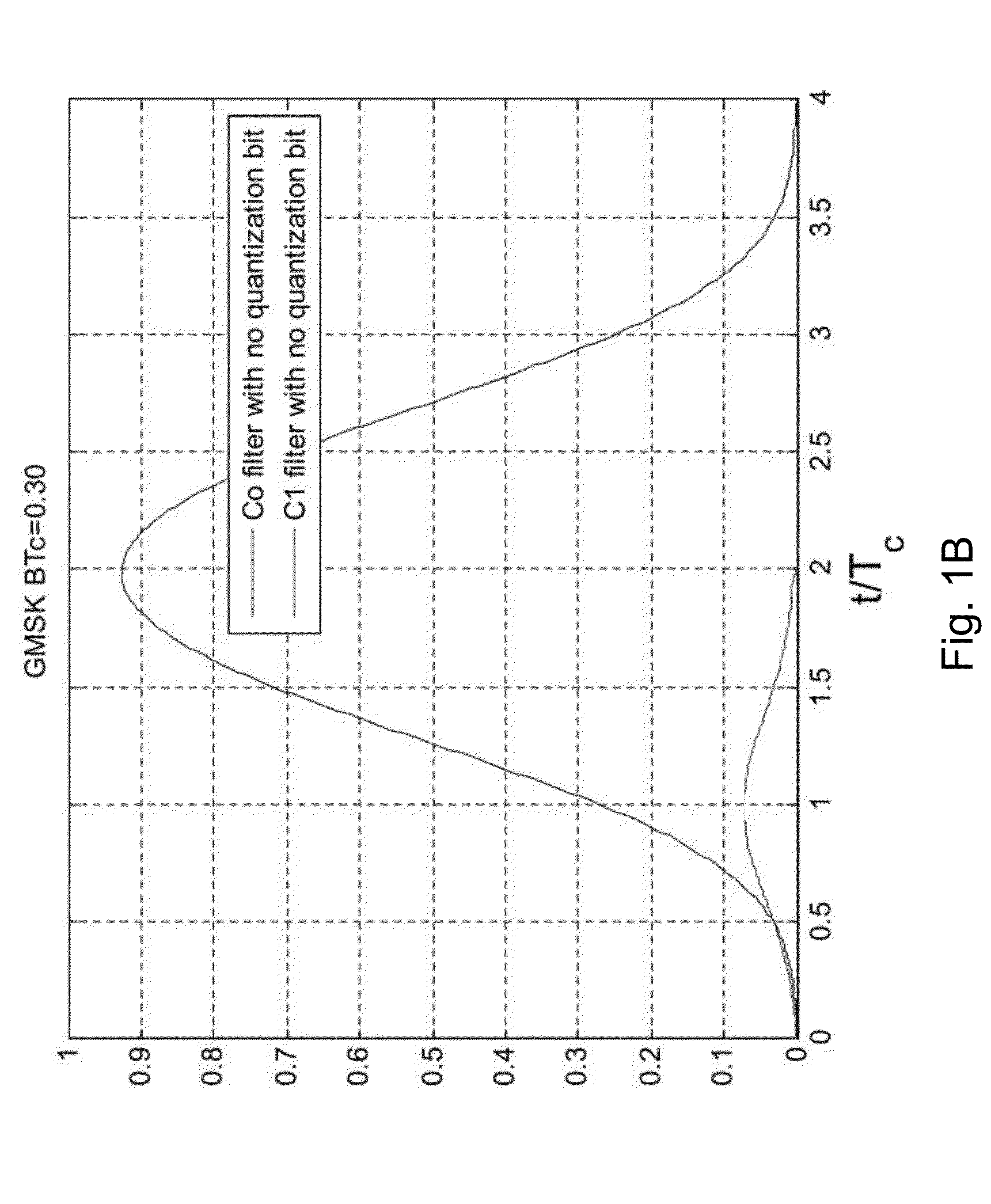

The Gaussian Minimum Shift Keying (GMSK) modulation is a modified version of the Minimum Shift Keying (MSK) modulation where the phase is further filtered through a Gaussian filter to smooth the transitions from one point to the next in the constellation.

Controlling transmission mode on basis of power in preceding time slot

InactiveUS7177607B2Good effectAvoid timeResonant long antennasPower amplifiersPower controllerAudio power amplifier

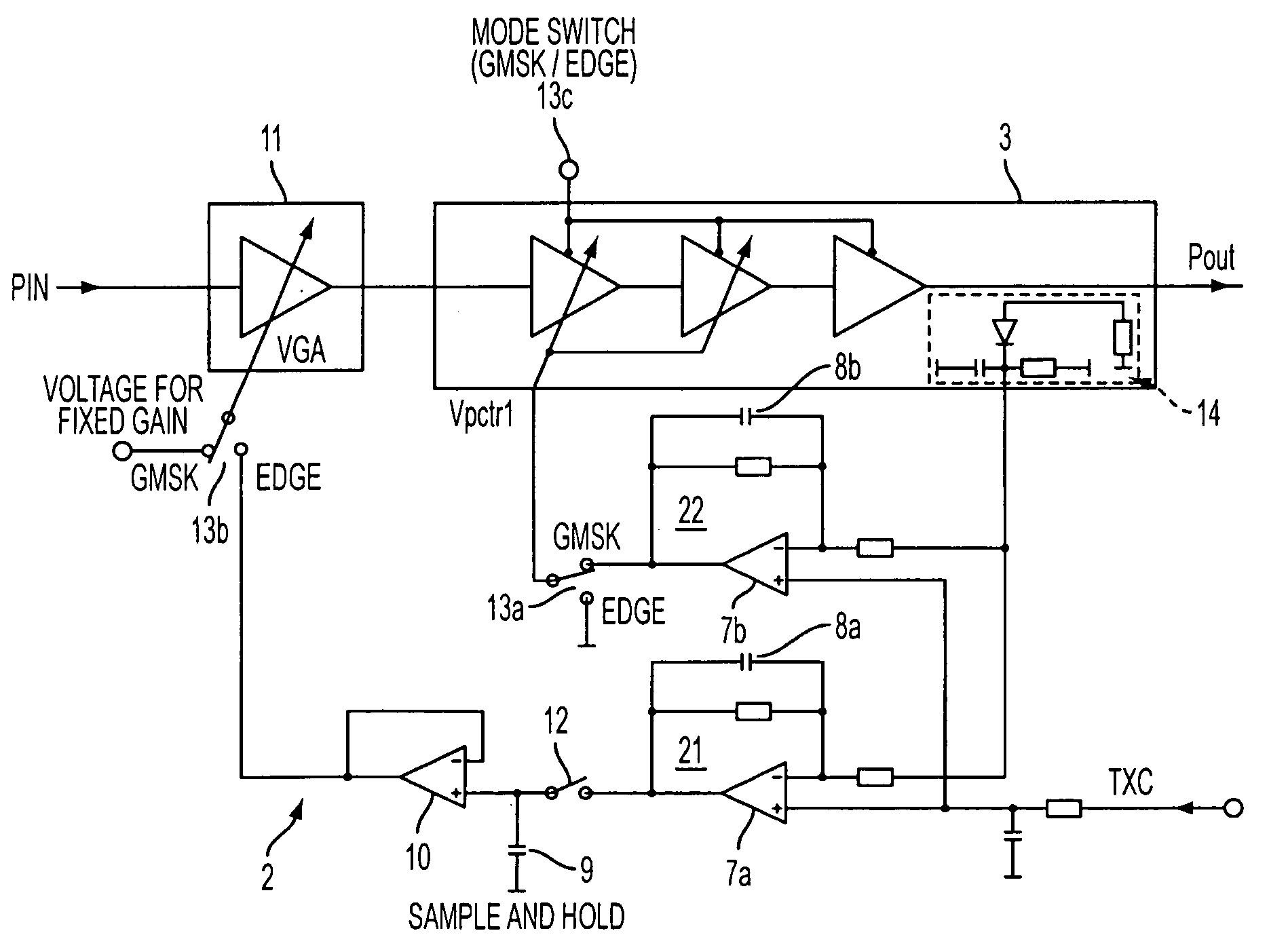

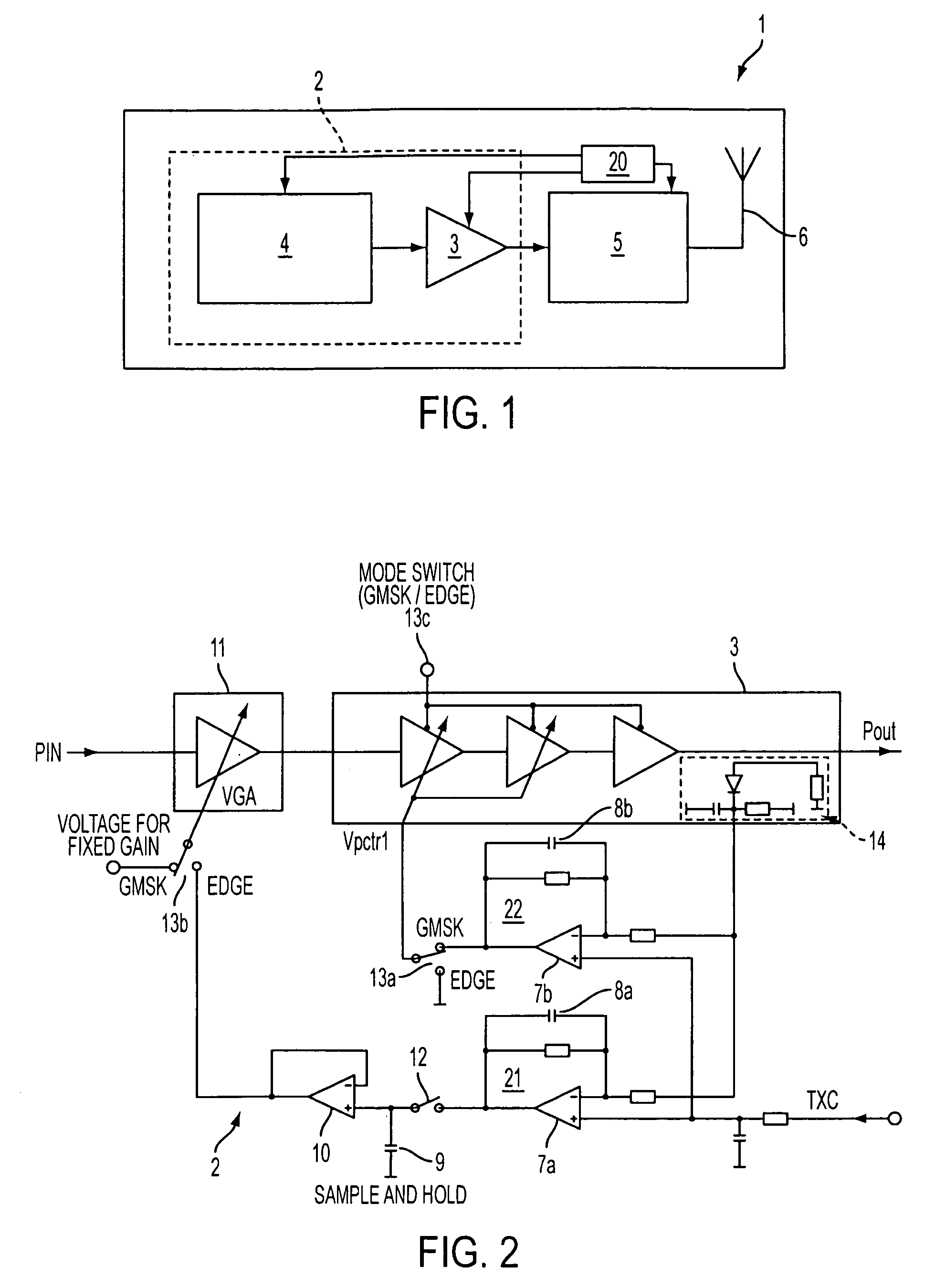

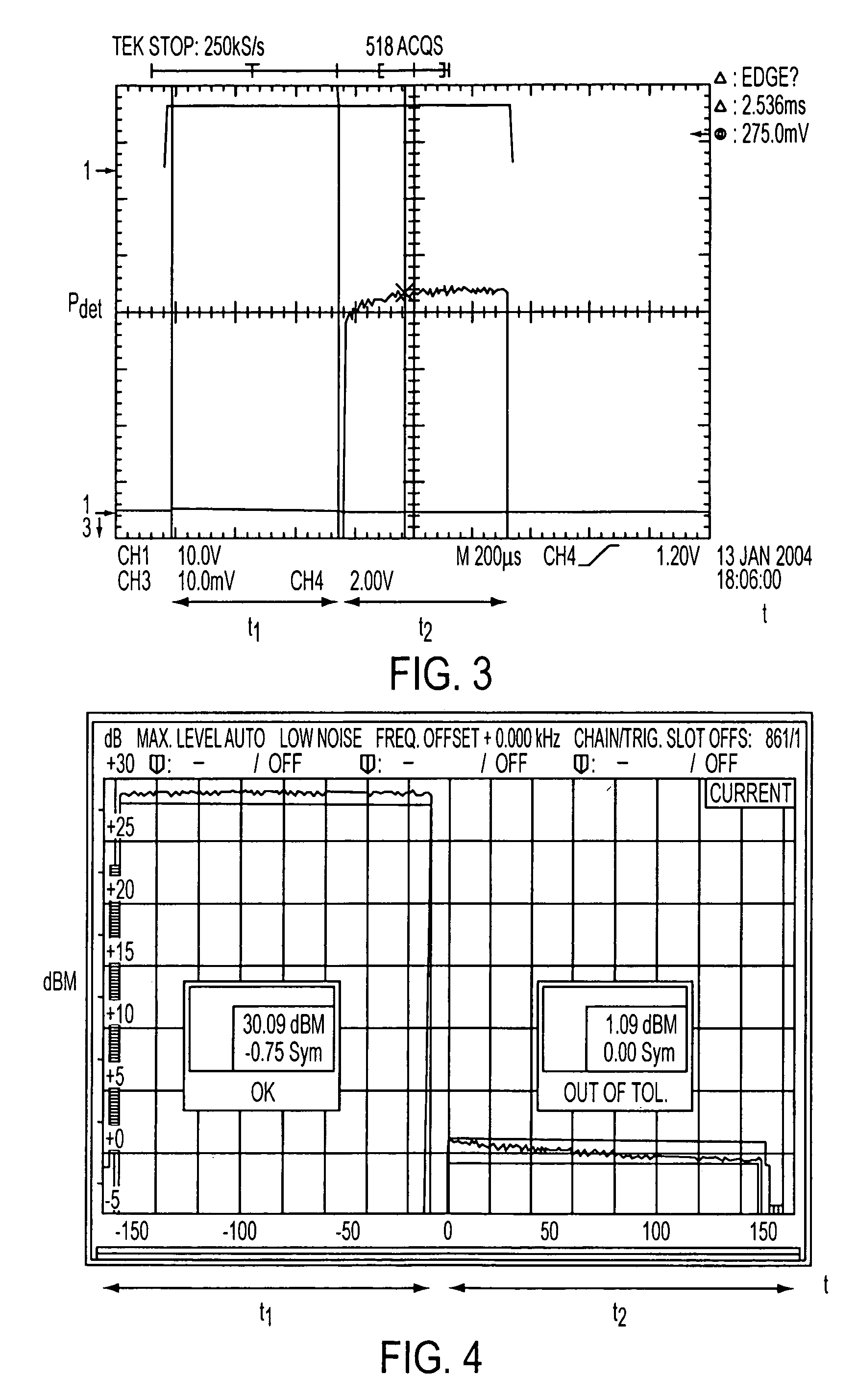

A transmitter 2 comprises a power amplifier 3 and power controller 4. The power amplifier 3 is capable of both linear and non-linear operation, and is controlled by a controller 20 and first and second control loops 21,22. The second control loop 22 is used with the transmission of GMSK modulated signals, which have no amplitude modulation, operating the power amplifier 3 in a non-linear mode. The first control loop 21 is used for the transmission of EDGE modulated signals, which have a substantial amount of amplitude modulation, operating the power amplifier 3 in a linear mode. The first control loop 21 is also used with GMSK time slots if the output power to be produced by the power amplifier 3 is low and the power of an immediately preceding time slot is high. In this case, a sample and hold circuit 9, 10 of the first control loop 21 is used when the power detector voltage in the power amplifier would change over the time slot by cooling, avoiding the possibility of the power level varying over the time slot.

Owner:NOKIA CORP

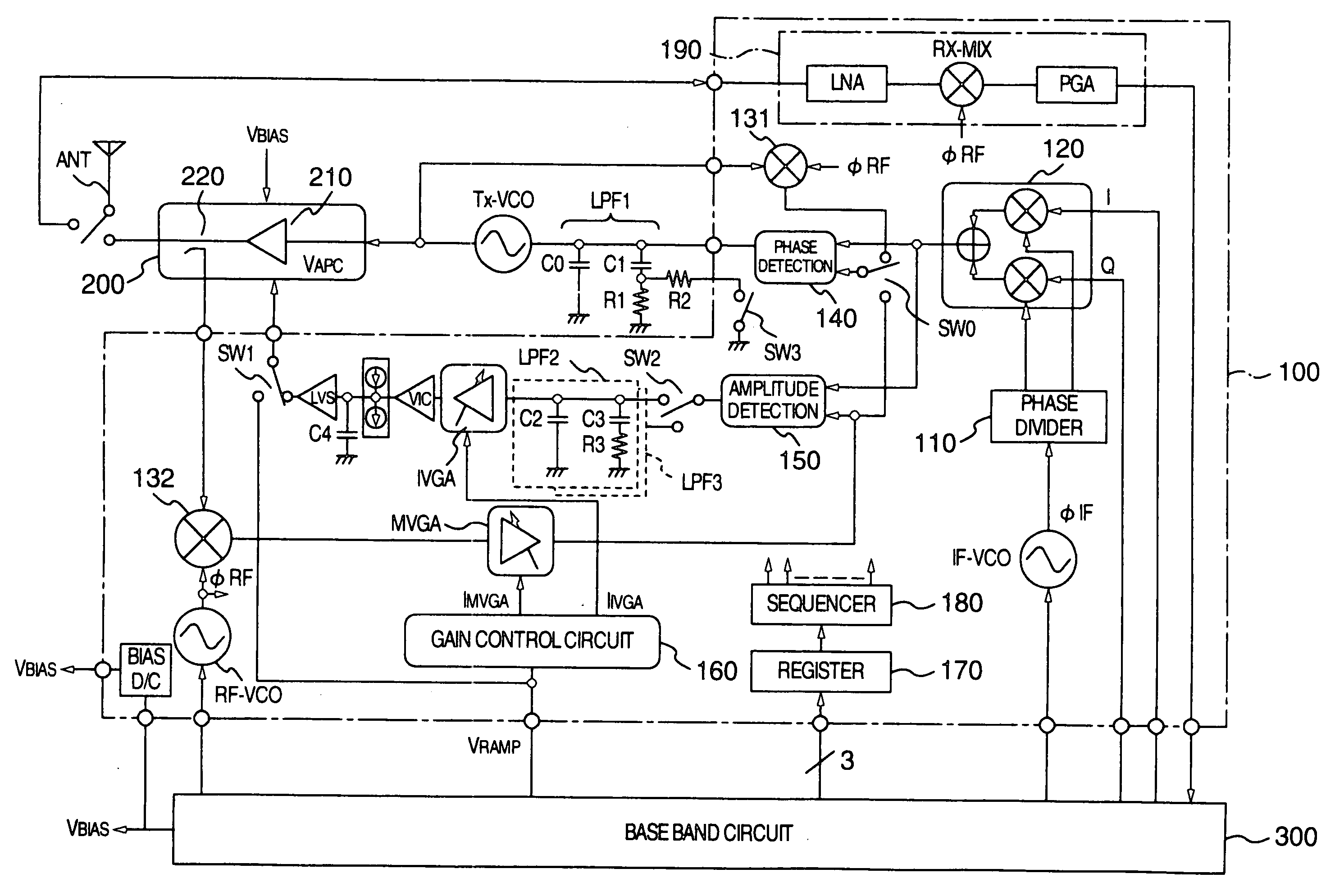

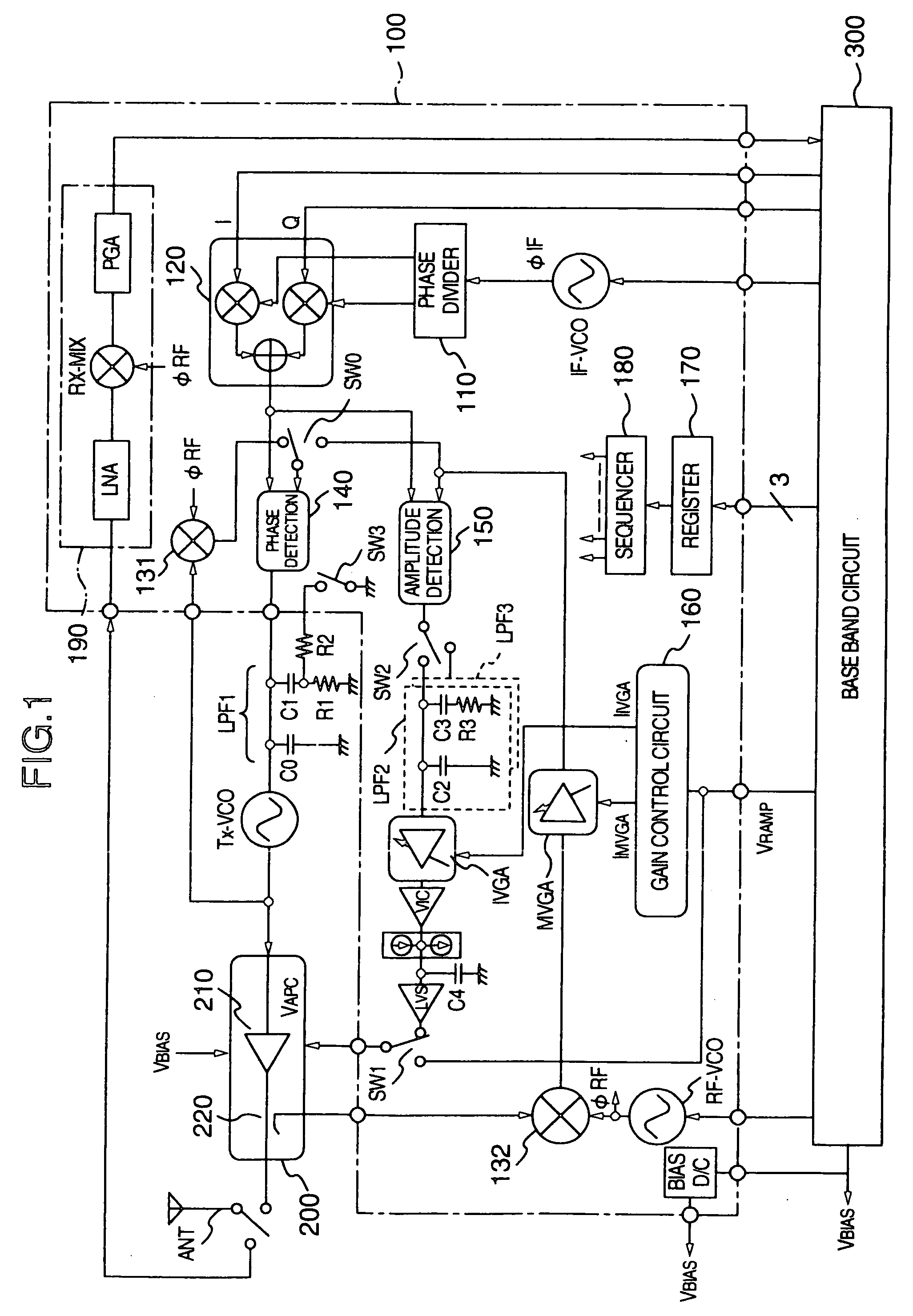

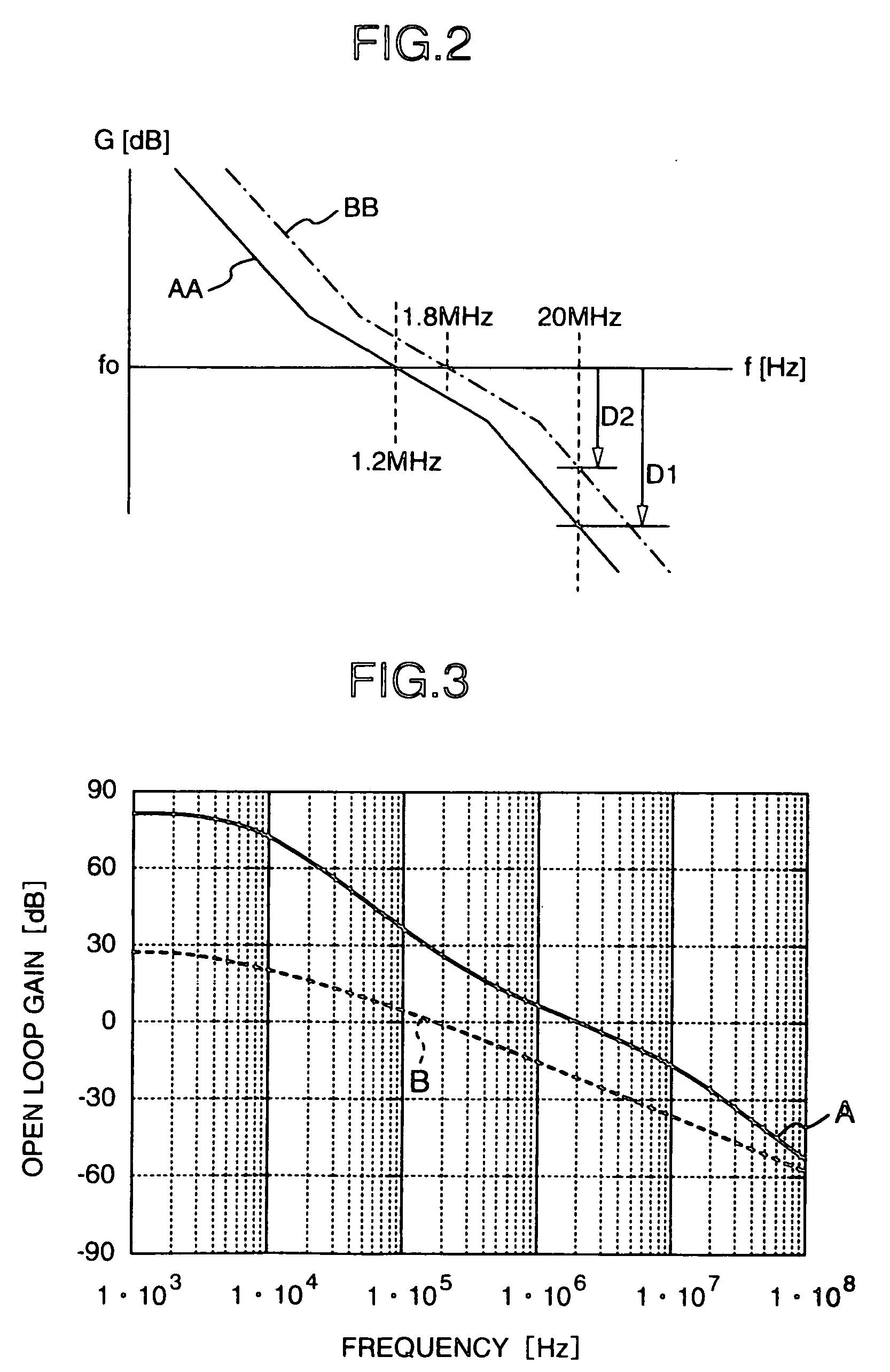

Transmitter having a phase control loop whose frequency bandwidth is varied in accordance with modulation modes

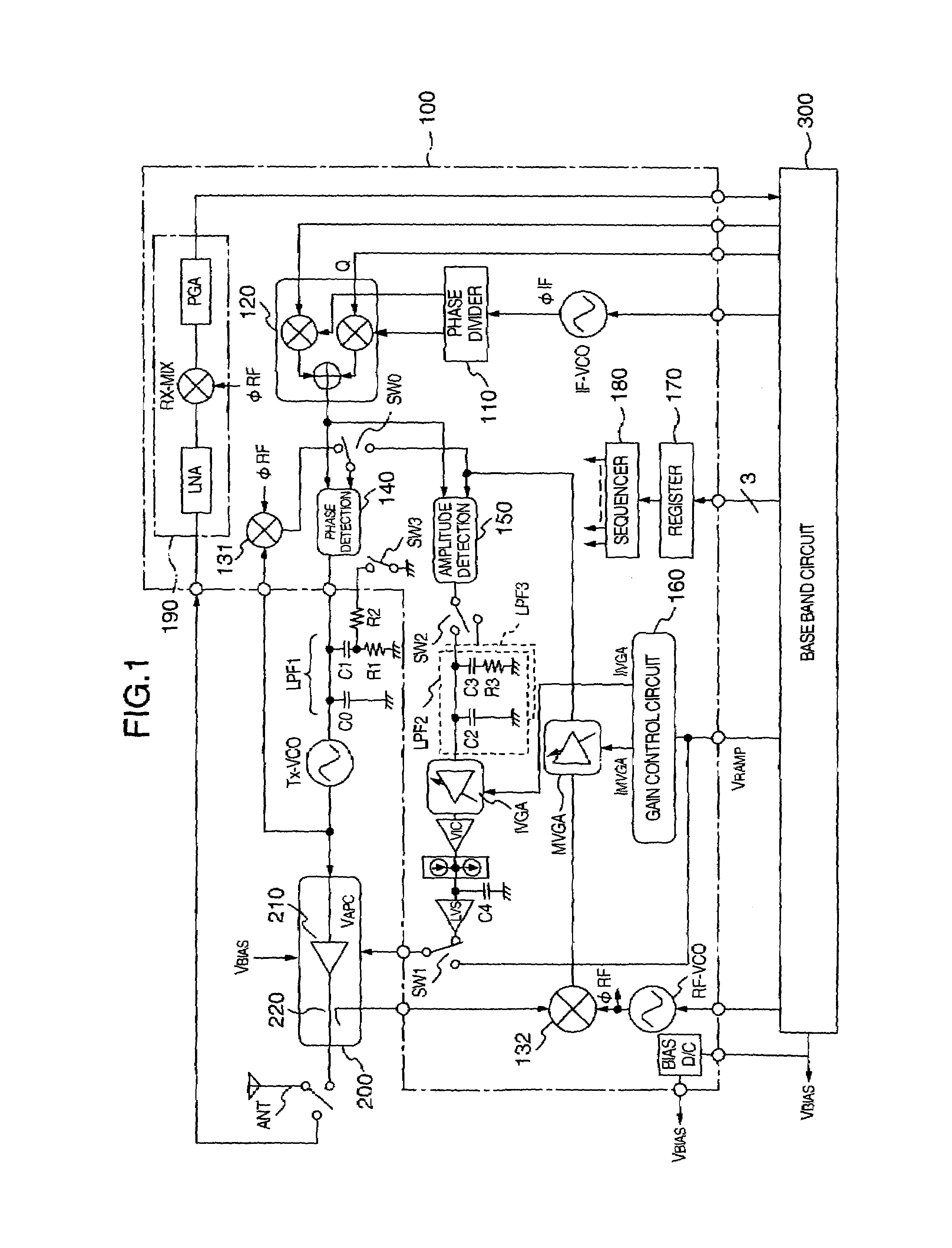

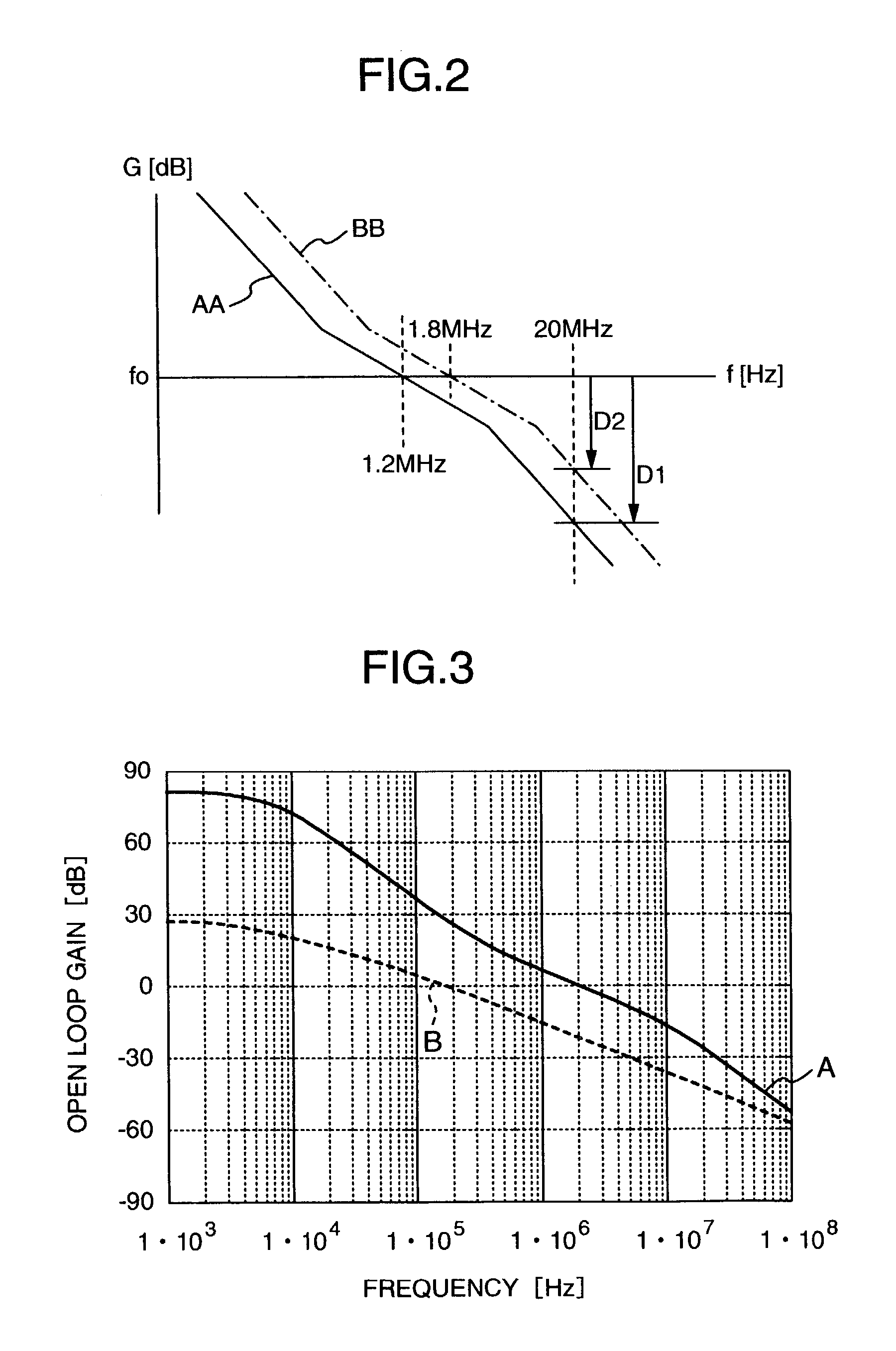

InactiveUS7085544B2Increase in error vector magnitudeSufficiently suppressPower amplifiersModulation with suppressed carrierLoop filterCarrier signal

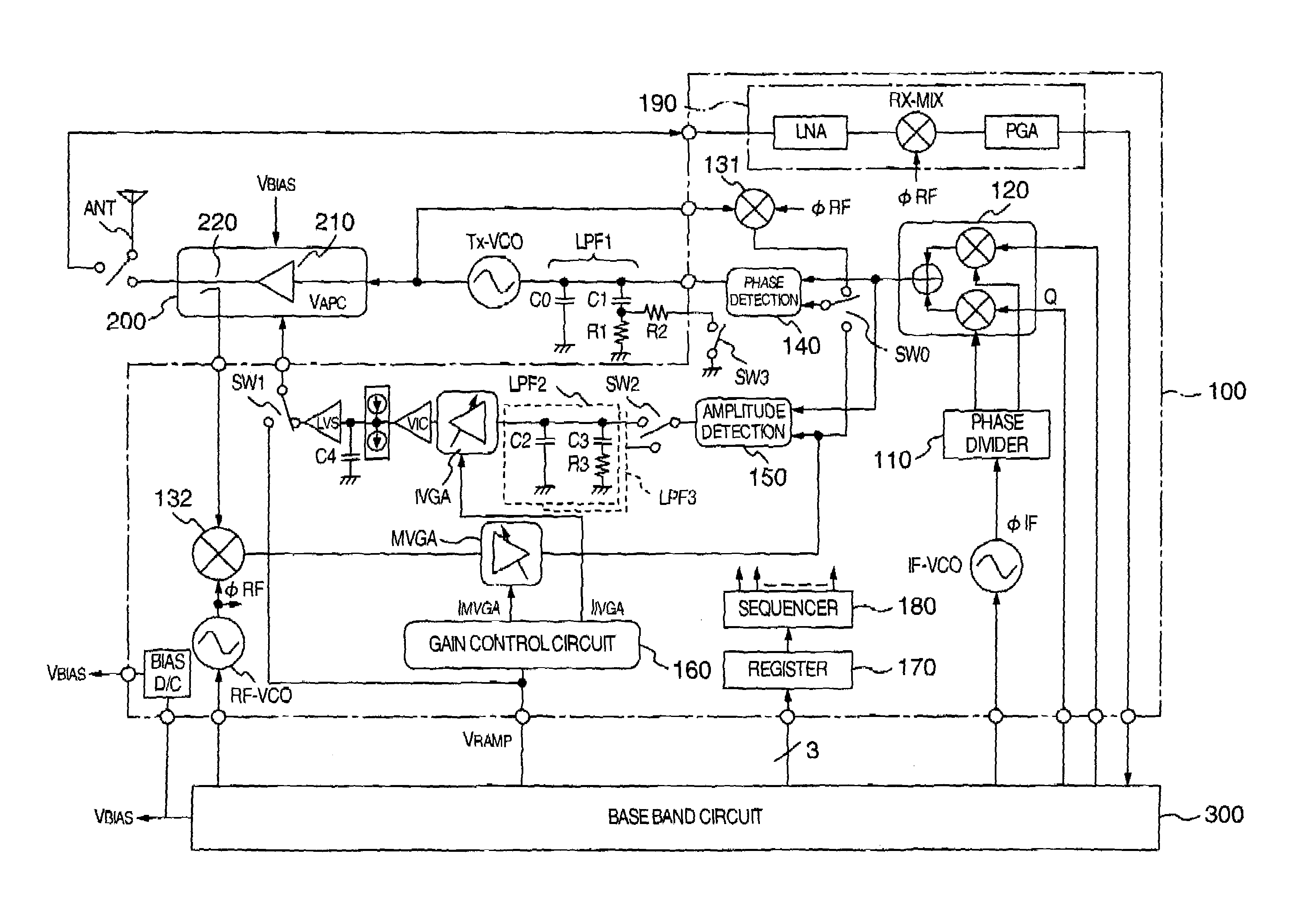

A transmitter adopting a polar loop system including a phase control loop for controlling the phase of a carrier signal outputted from a transmitting oscillator and an amplitude control loop for controlling the amplitude of a transmitting output signal outputted from a power amplification circuit, and designed to be capable of performing transmission using a GMSK modulation mode and transmission using an 8-PSK modulation mode. In the transmitter, the phase control loop is shared as a phase control loop for use in the GMSK modulation mode and a phase control loop for use in the 8-PSK modulation mode. A component similar to any one of components constituting a loop filter is provided in parallel therewith so that the component can be connected or disconnected in accordance with the modulation mode, for example, by use of a switching element.

Owner:RENESAS ELECTRONICS CORP +2

Single antenna interference suppression in a wireless receiver

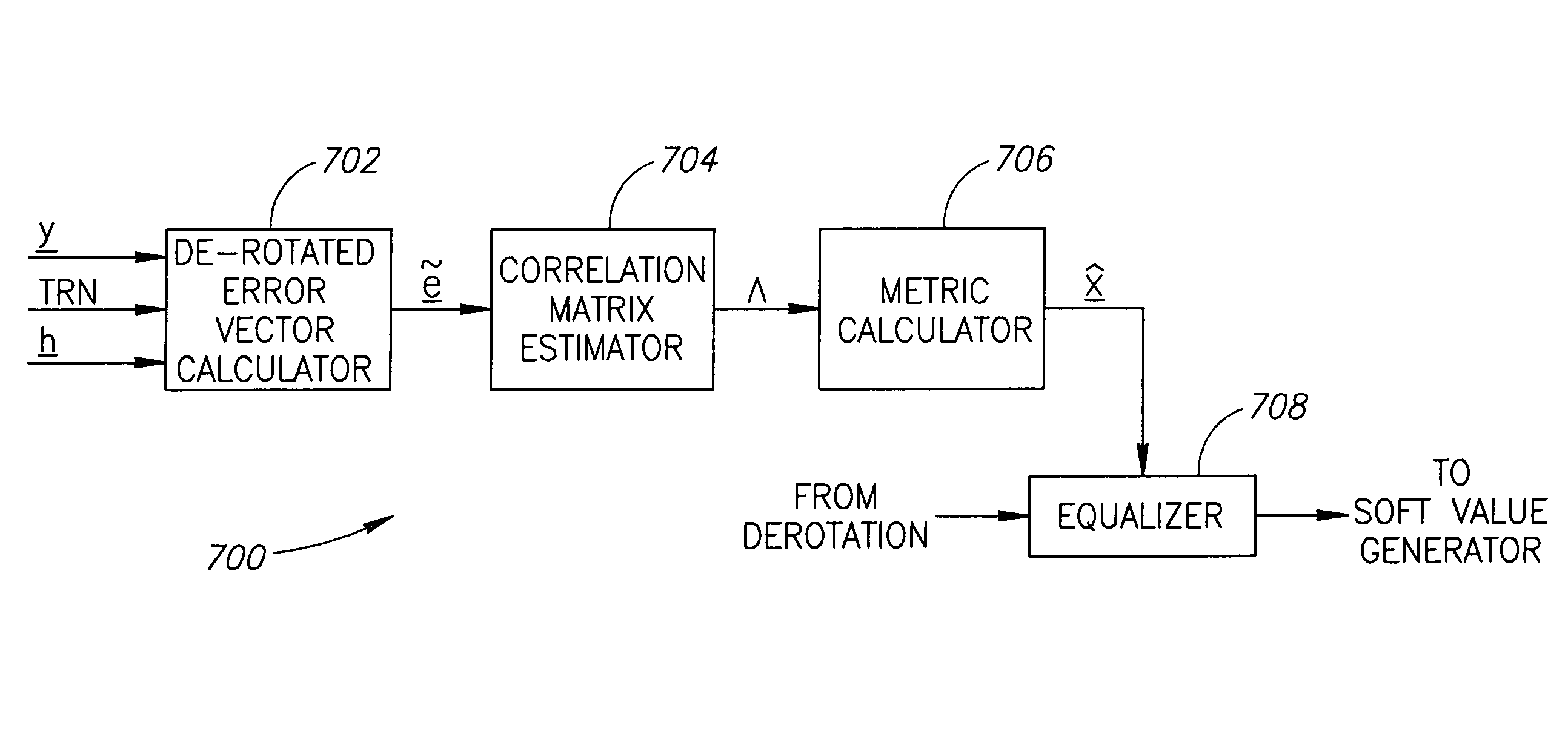

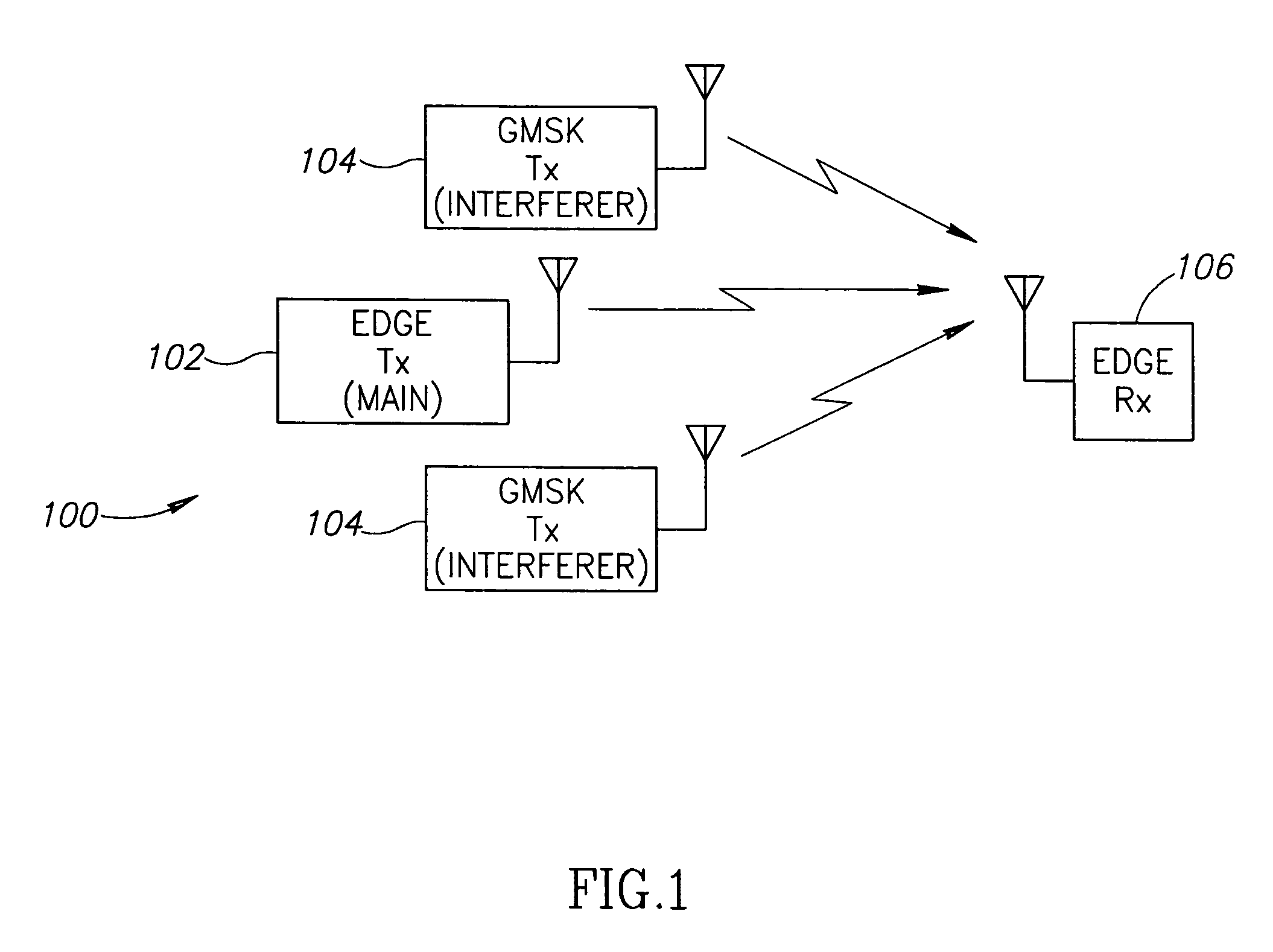

InactiveUS7567635B2Reduce impactReduce co-channel interferenceError preventionNetwork traffic/resource managementTime errorCommunications system

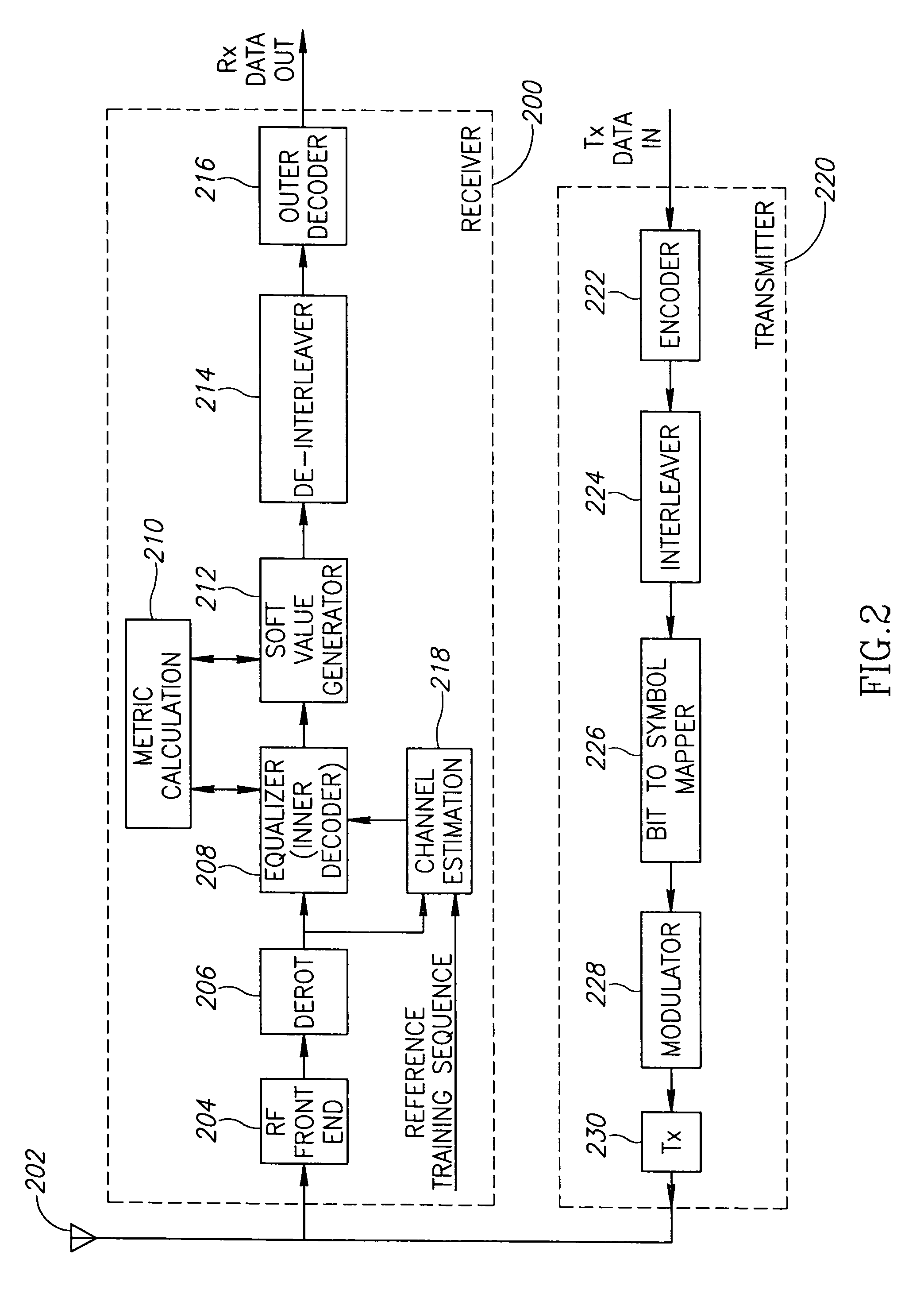

A novel and useful apparatus for and method of single antenna interference cancellation (SAIC) in a wireless communications system. A class of algorithms is disclosed for Downlink Advanced Receiver Performance (DARP) receivers based on a novel metric calculation used during equalization and optionally in other portions of the receiver as well, e.g., soft value generation. A DARP receiver for 8PSK EDGE modulation is presented wherein the interfering signals comprise GMSK modulated signals. The modified metric takes into account the rotation remaining in the noise component of the received signal after de-rotation of the 8PSK signal. Considering the interferer to be a GMSK signal, the I / Q elements of the noise are correlated and this fact is used to modify the decision rule for the received signal thus improving the performance of the equalizer. The model is further extended to take into account temporal error correlation.

Owner:COMSYS COMM & SIGNAL PROC

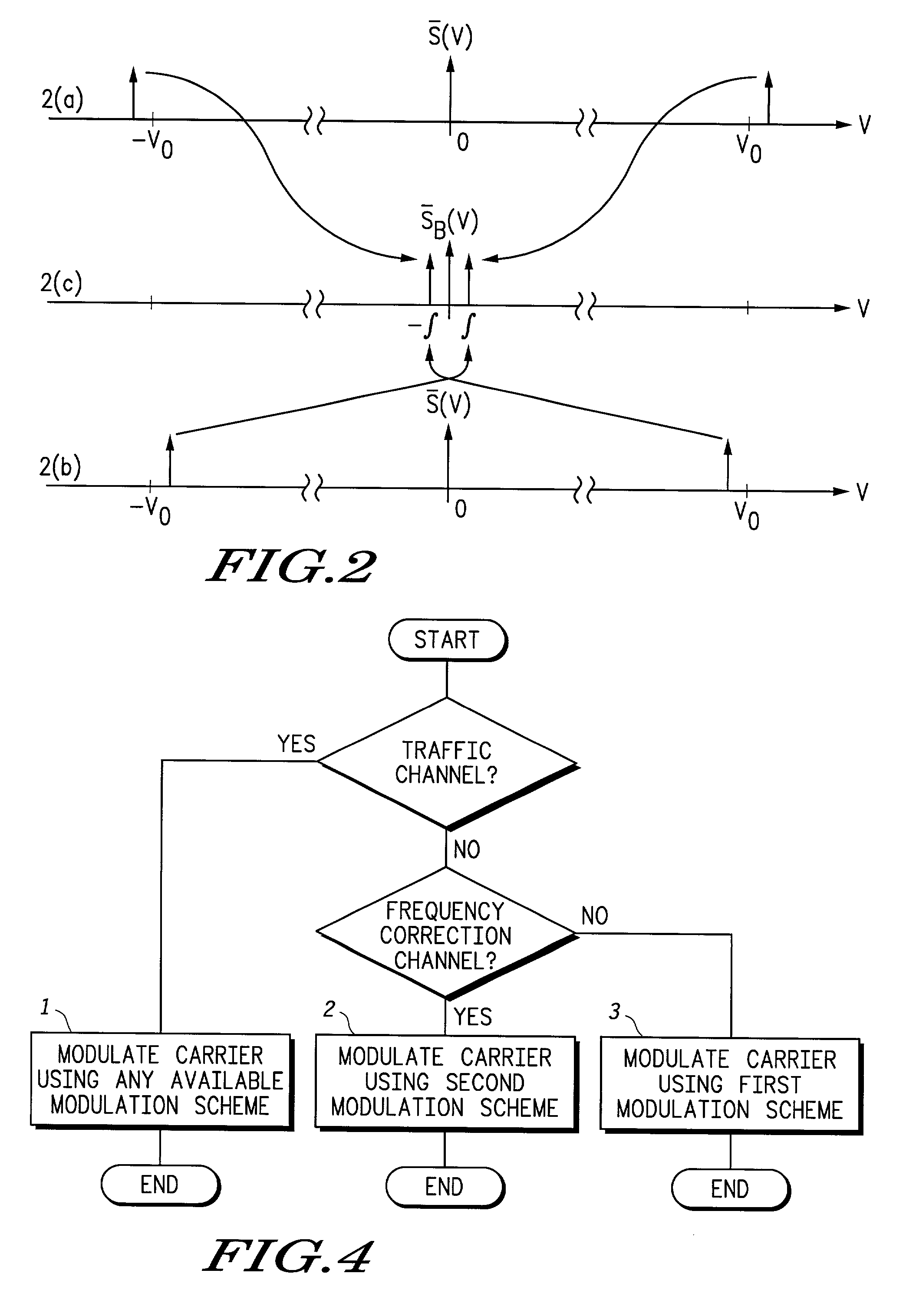

New improvement scheme about gaussian minimum shift keying (GMSK) modulation technology

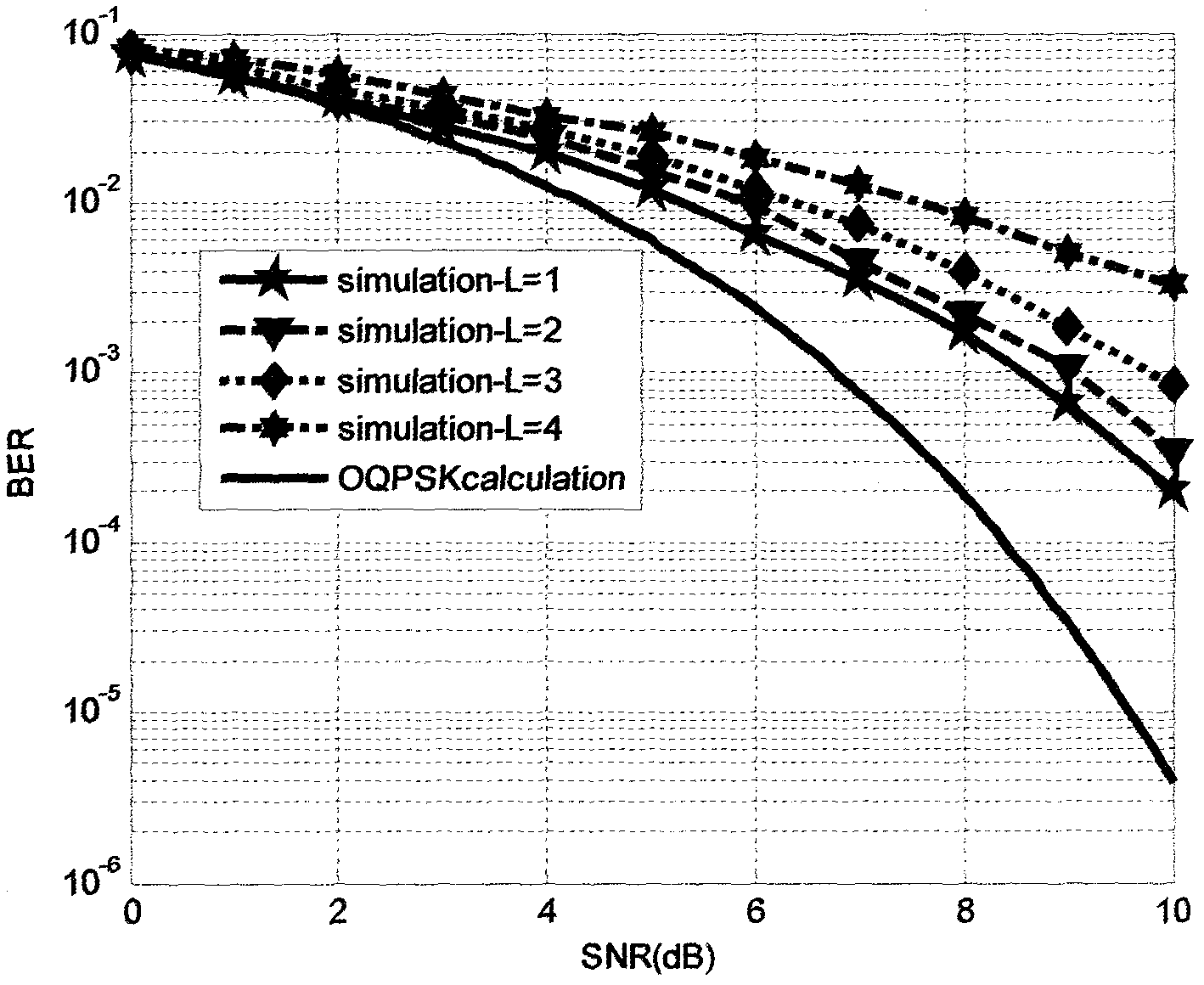

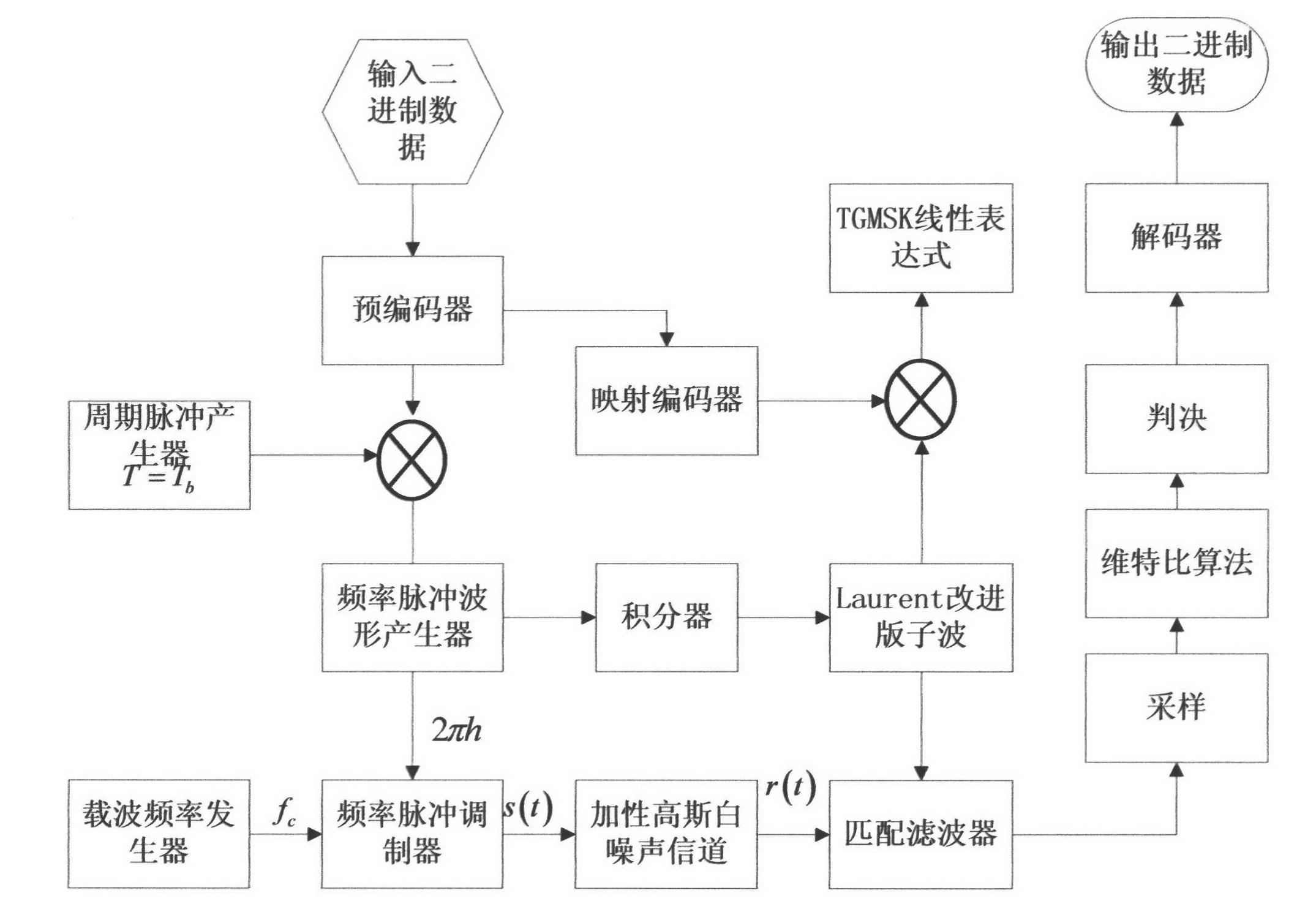

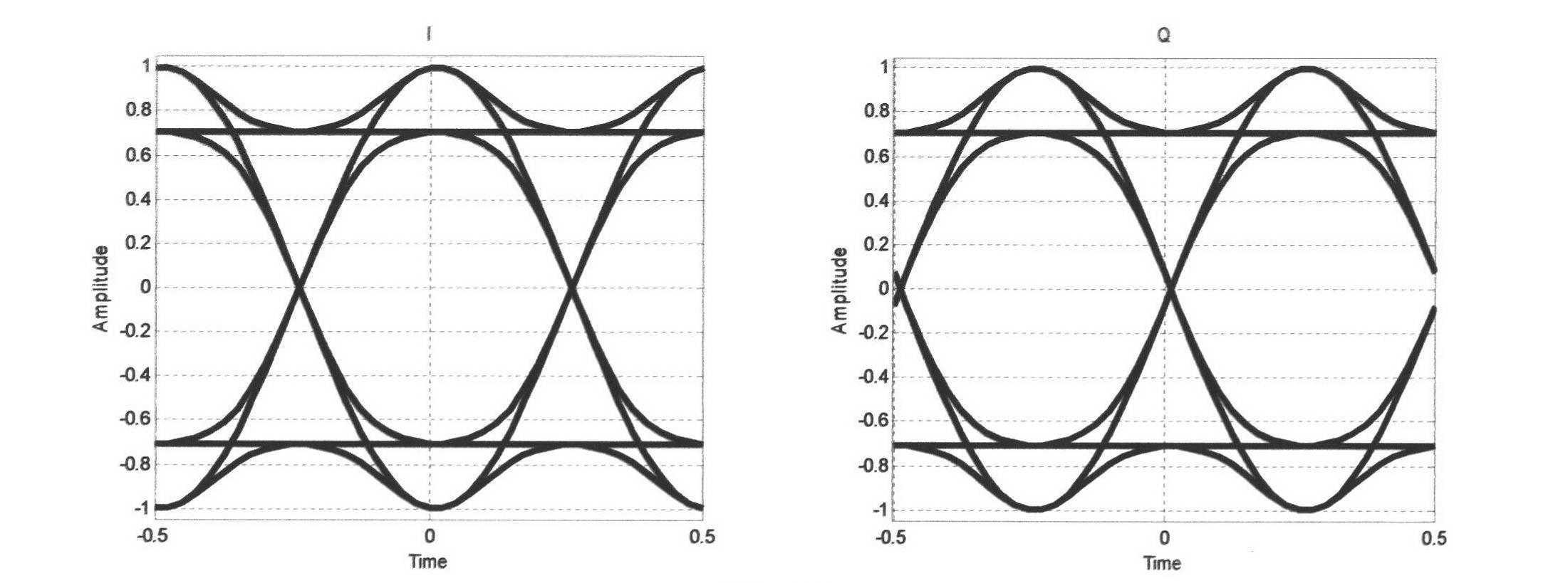

The invention relates to a digital modulation mode suitable for the wireless communication field. In the invention, firstly, a current existing gaussian minimum shift keying (GMSK) modulation technology is provided specifically. An insufficiency of the current existing GMSK modulation technology on a spectrum efficiency is analyzed. And then the new digital modulation mode based on the current existing GMSK modulation technology is provided. By using the modulation mode, contradiction between an error code function and the spectral efficiency can be fully considered to be solved. Binary information is converted into ternary data through precoding so that a transmission signal phase only has three kinds of hopping values. From aspects of emission and receiving, performance indexes of the frequency spectrum and the error code performance are measured. Using a matlab simulation platform can show that a frequency spectrum utilization rate and anti-interference performance of the modulation mode are higher and better than that of the GMSK modulation mode.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Transmitter and semiconductor integrated circuit for communication

InactiveUS20060217081A1Improve errorNoise reaching the reception frequency band can be suppressed sufficientlySimultaneous amplitude and angle modulationResonant long antennasLoop filterAmplitude control

A transmitter adopting a polar loop system including a phase control loop for controlling the phase of a carrier signal outputted from a transmitting oscillator and an amplitude control loop for controlling the amplitude of a transmitting output signal outputted from a power amplification circuit, and designed to be capable of performing transmission using a GMSK modulation mode and transmission using an 8-PSK modulation mode. In the transmitter, the phase control loop is shared as a phase control loop for use in the GMSK modulation mode and a phase control loop for use in the 8-PSK modulation mode. A component similar to any one of components constituting a loop filter is provided in parallel therewith so that the component can be connected or disconnected in accordance with the modulation mode, for example, by use of a switching element.

Owner:GOOGLE TECH HLDG LLC +1

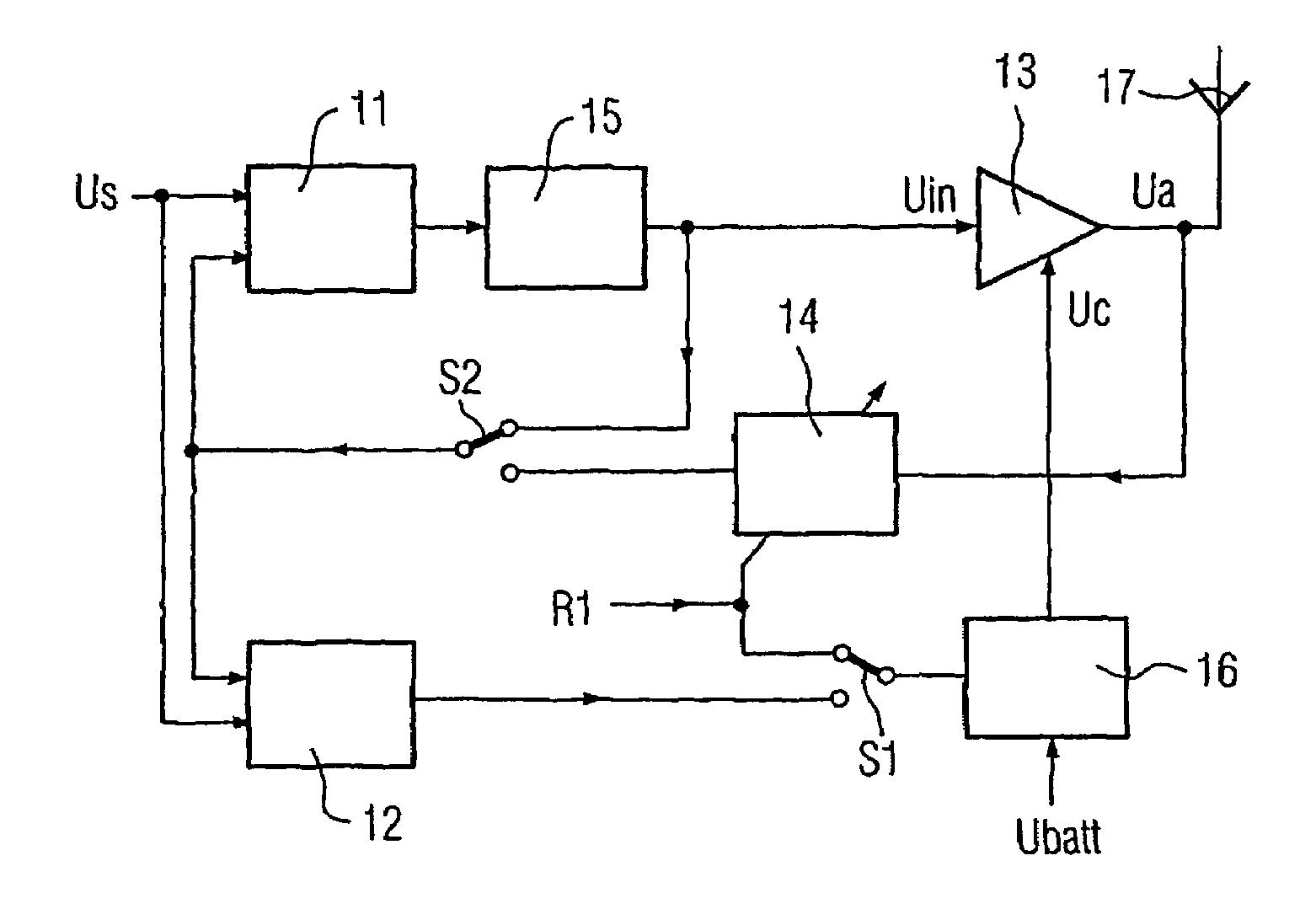

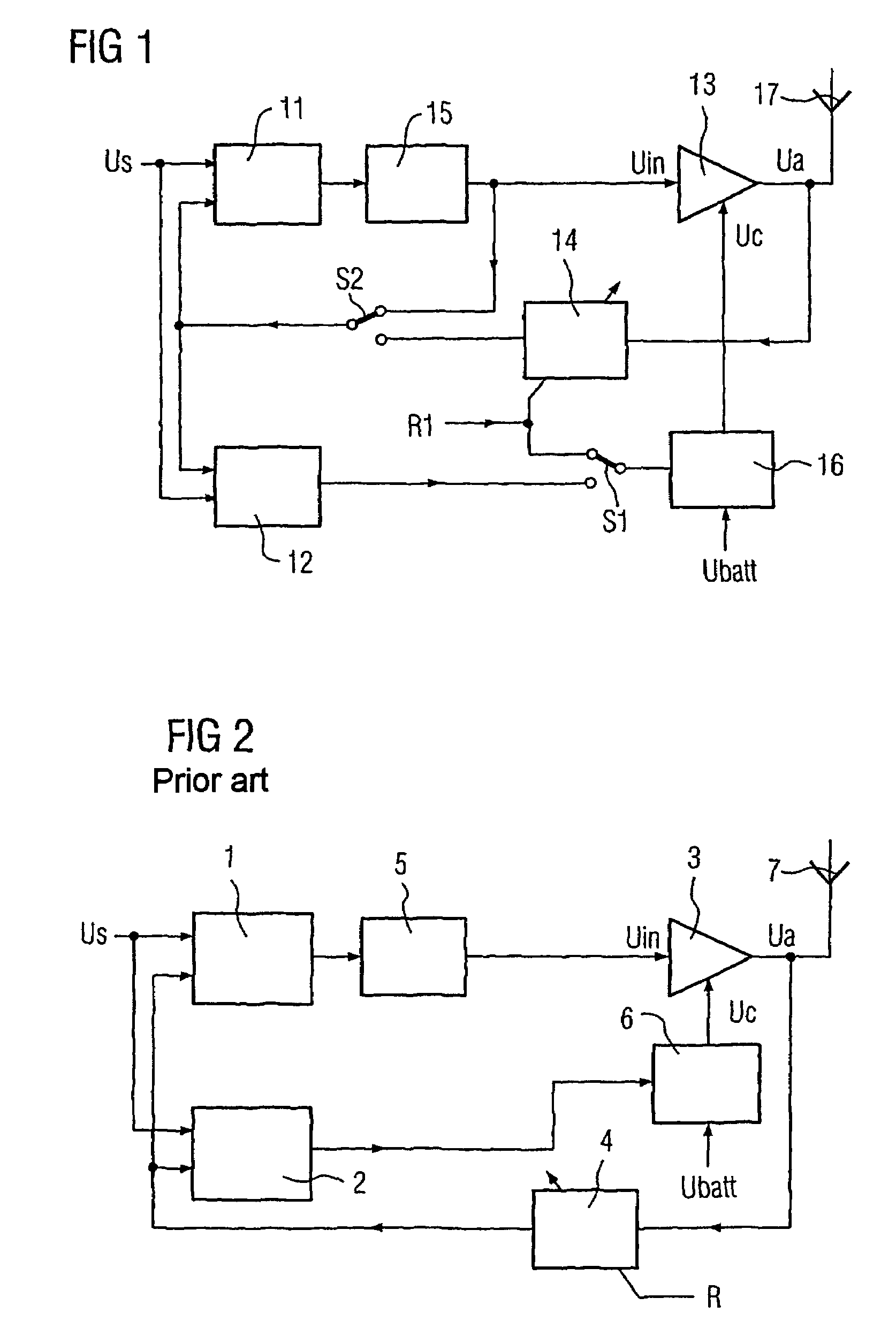

Circuit arrangement for switching a mobile radio transmitter between two modulation modes

ActiveUS7050772B2Resonant long antennasMultiple modulation transmitter/receiver arrangementsEngineeringVoltage modulation

A circuit is provided for regulating operation of a transmitter of a mobile communication terminal, which runs in the EDGE and GMSK modulation modes. The inventive circuit includes a power amplifier supplying an output signal for an antenna of the mobile communication terminal; a phase regulator that is provided with a phase comparator to which a setpoint signal for the output signal of the power amplifier is fed, and a voltage-controlled oscillator adjusting the phase position of the output signal of the power amplifier, the phase regulator regulating the phase position of the output signal of the power amplifier; an amplitude-regulating device that is provided with an amplitude comparator to which the setpoint signal for the output signal of the power amplifier is fed, and a battery-powered battery-voltage modulator adjusting the amplitude of the output signal of the power amplifier, the amplitude-regulating device regulating the amplitude of the output signal of the power amplifier; and a feedback line feeding an actual measured value for the output signal of the power amplifier back to the phase comparator and the amplitude comparator, the feedback line being provided with an adjustable amplifier which is controlled by a baseband chip and sets an output power of the antenna. The inventive circuit includes a changeover switch which is wired in such a way that it connects an input of the battery-voltage modulator to an output of the amplitude comparator in a first position for the EDGE mode while connecting an input of the battery-voltage modulator to an output of the power amplifier in a second position for the GMSK mode, the connection being made via the adjustable amplifier in both positions.

Owner:QUALCOMM INC

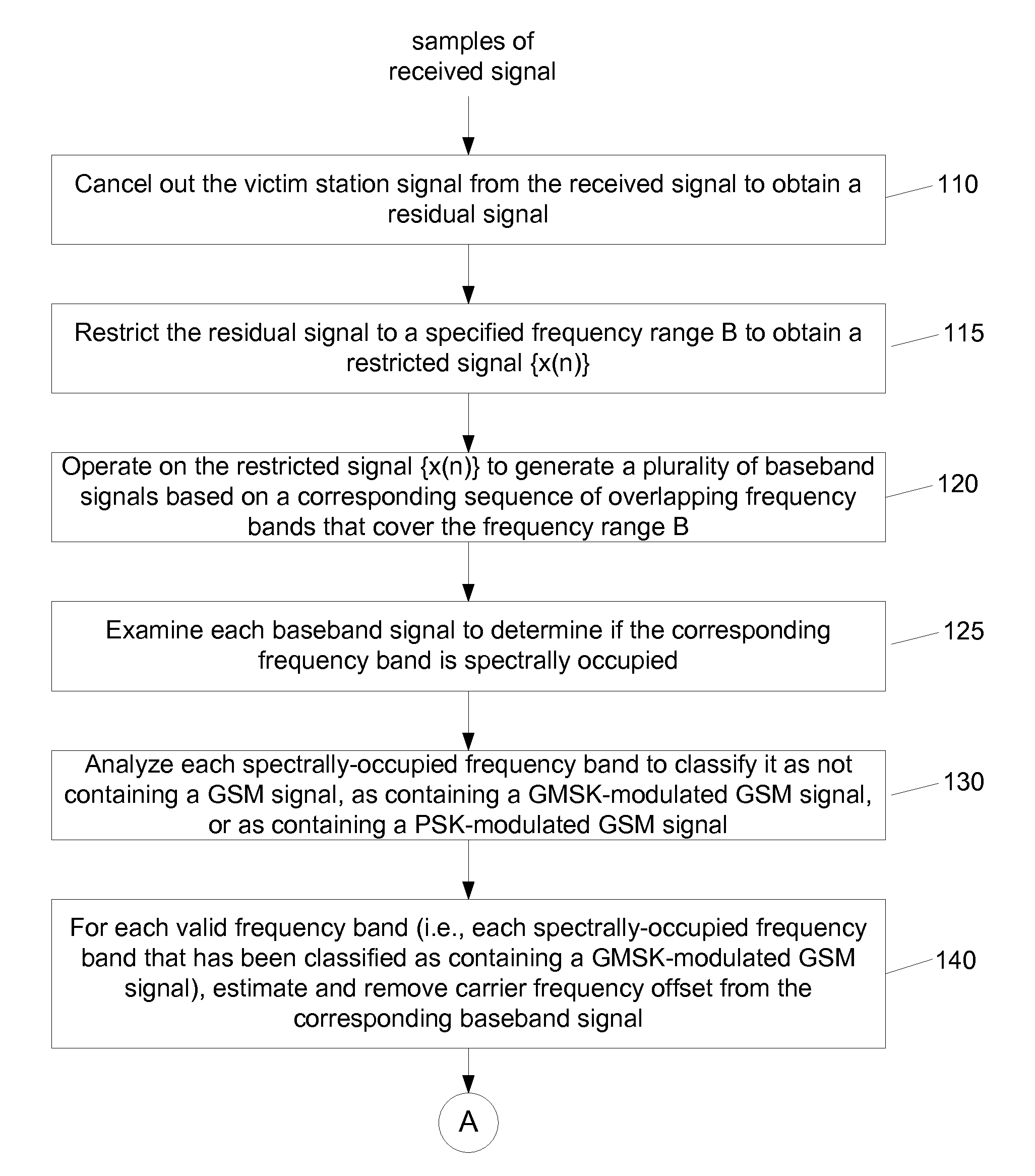

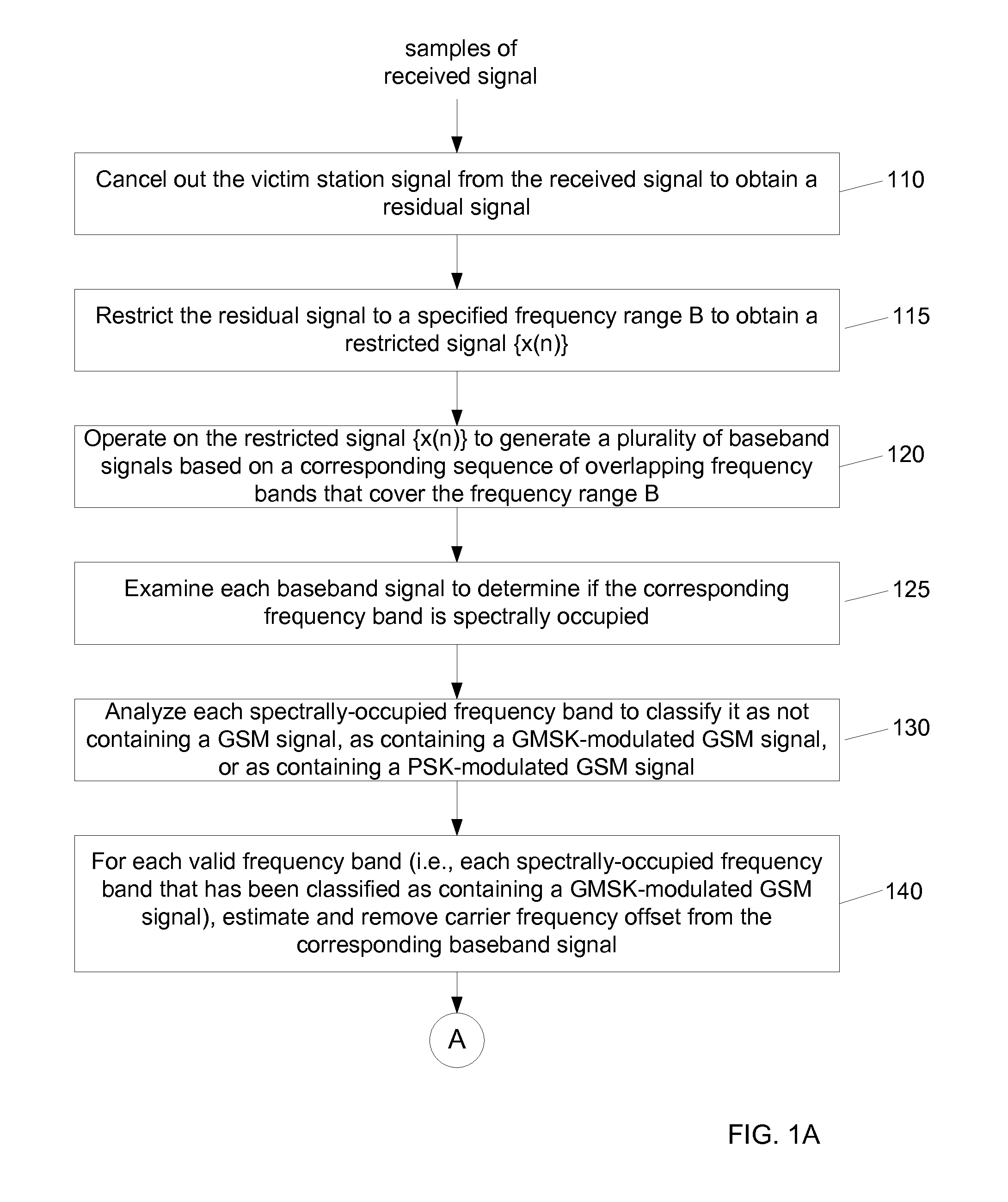

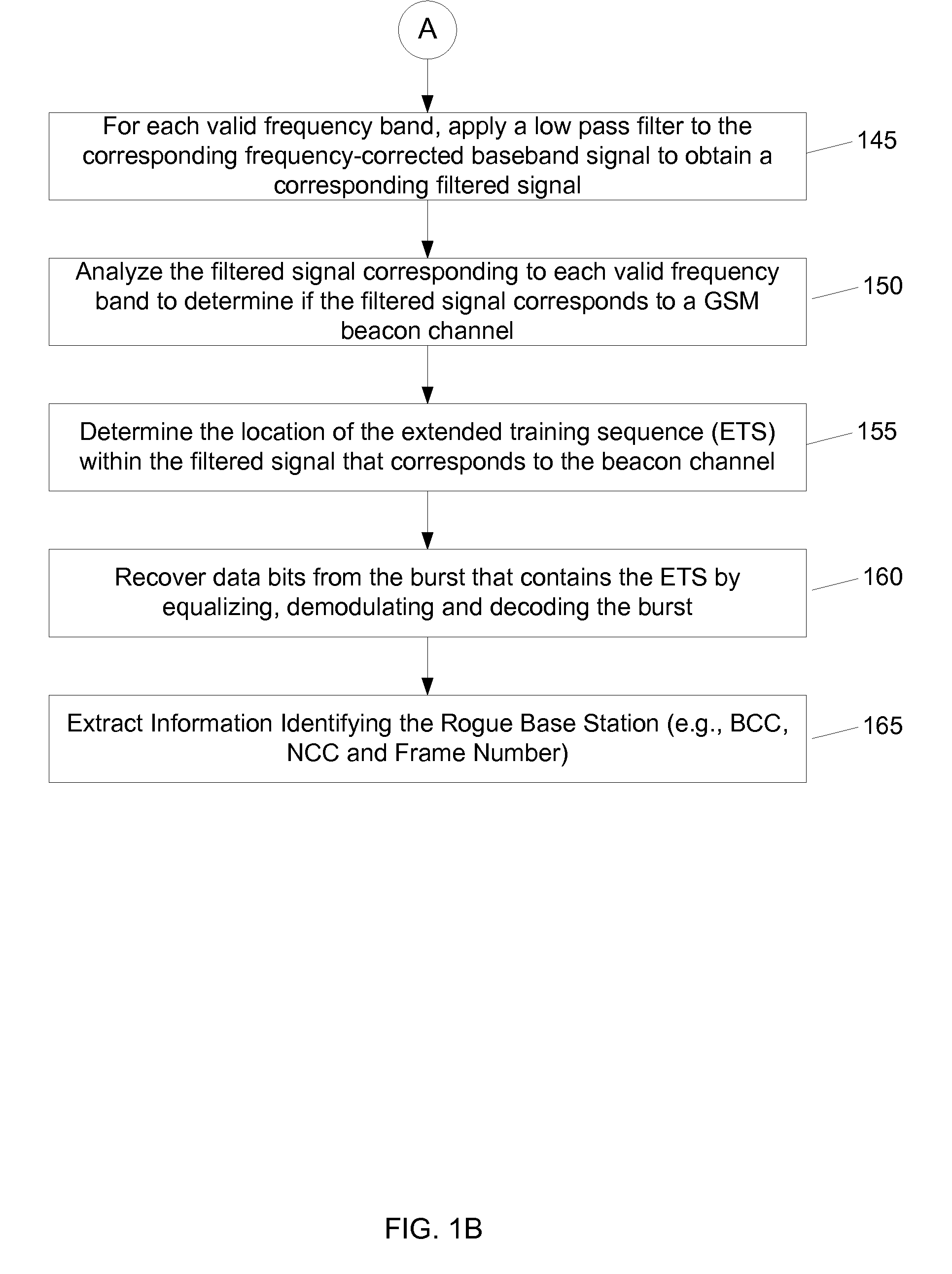

Identifying Rogue GSM Base Stations by Intercepting Downlink Beacon Channels

System and methods and memory media for identifying a rogue base station. A receiver captures an input signal that includes a mixture of the rogue station's transmission and the transmission of a victim base station. The victim station's transmission is removed from the mixture. A plurality of channel signals are extracted from the residual signal. The channel signals are analyzed which of them are “valid”, i.e., contain a GMSK-modulated GSM signal. The “valid” channel signals are low pass filtered and then analyzed to determine which of them corresponds to the beacon channel. Information identifying the rogue base station is extracted from the beacon channel.

Owner:NATIONAL INSTRUMENTS

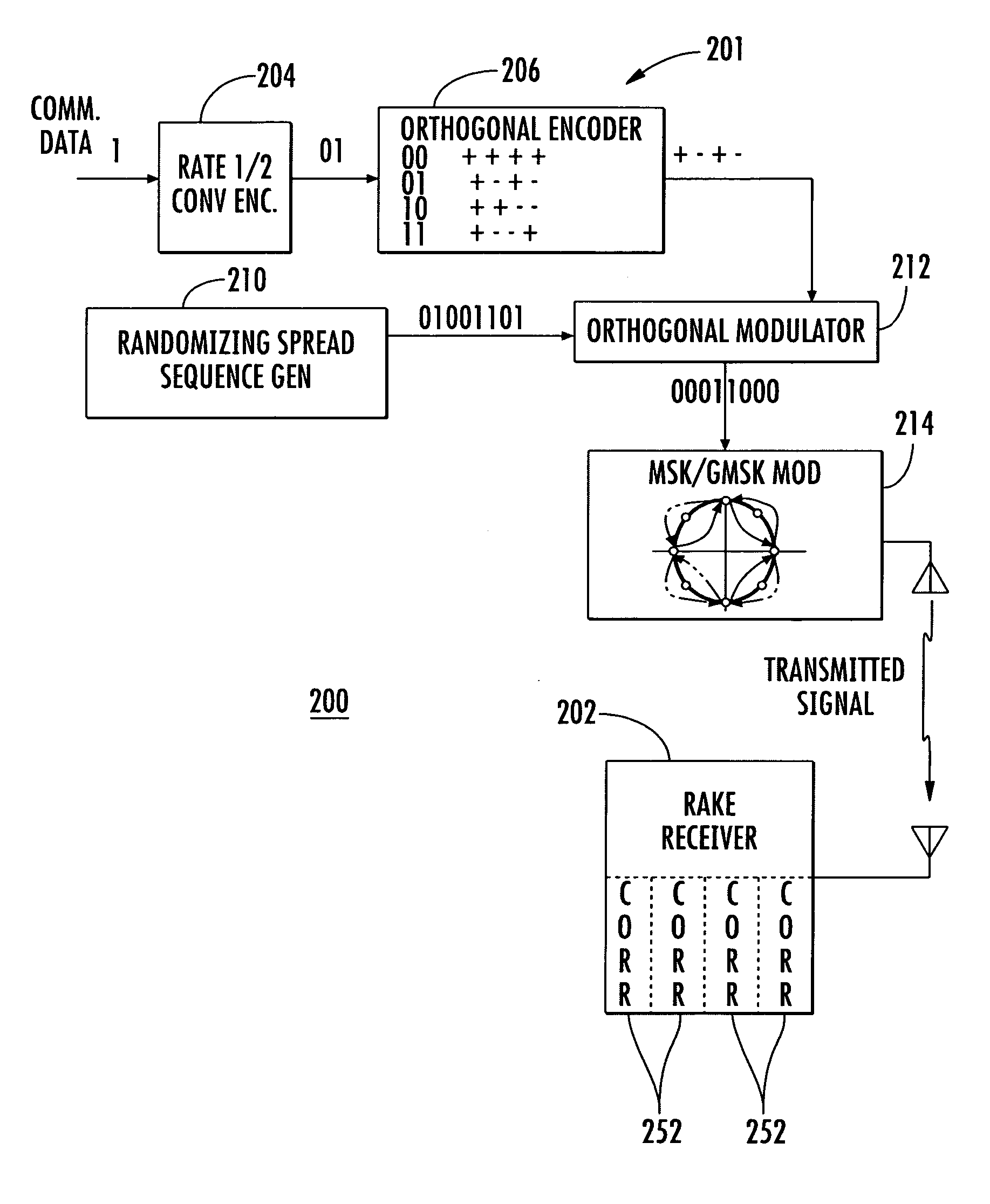

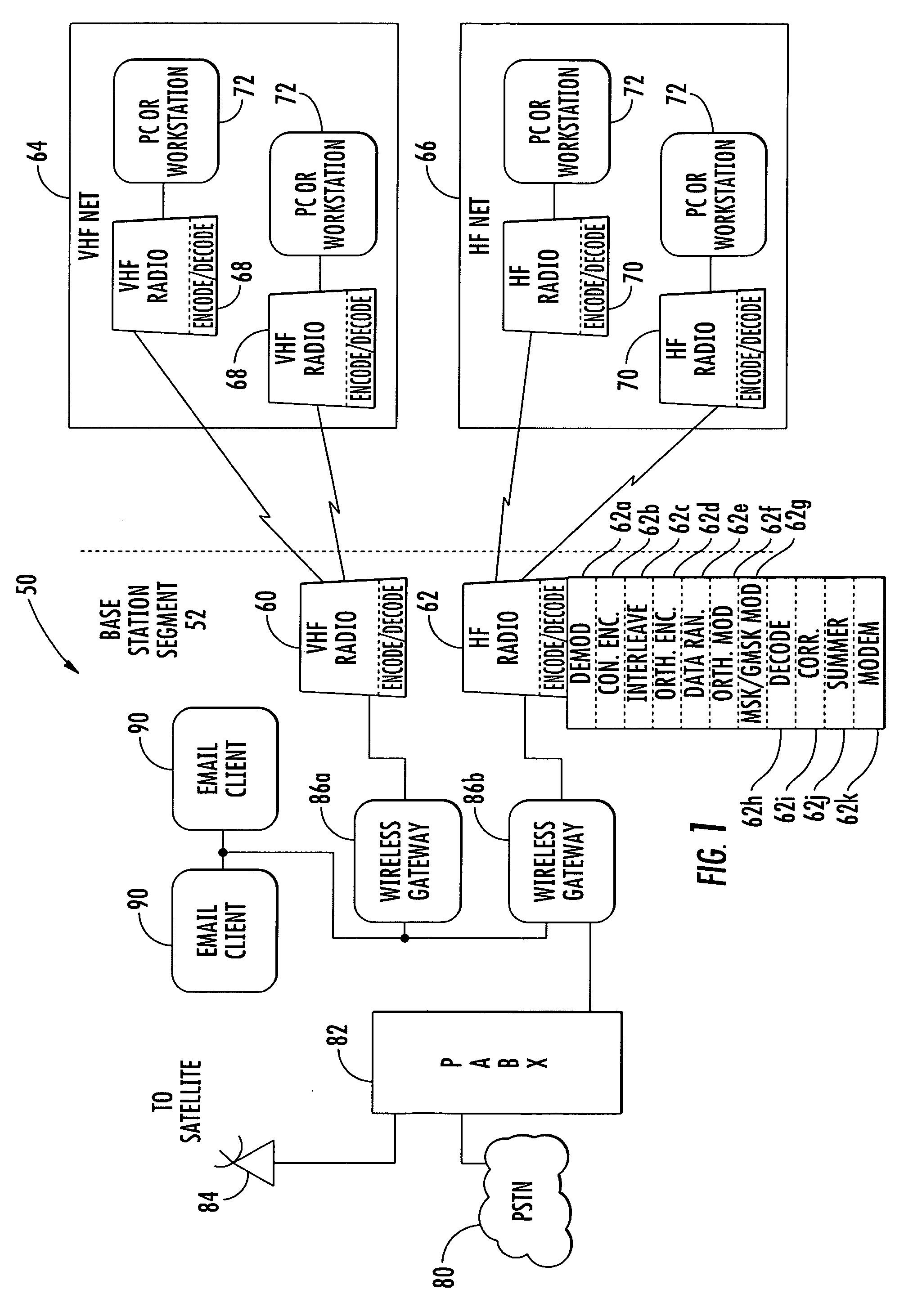

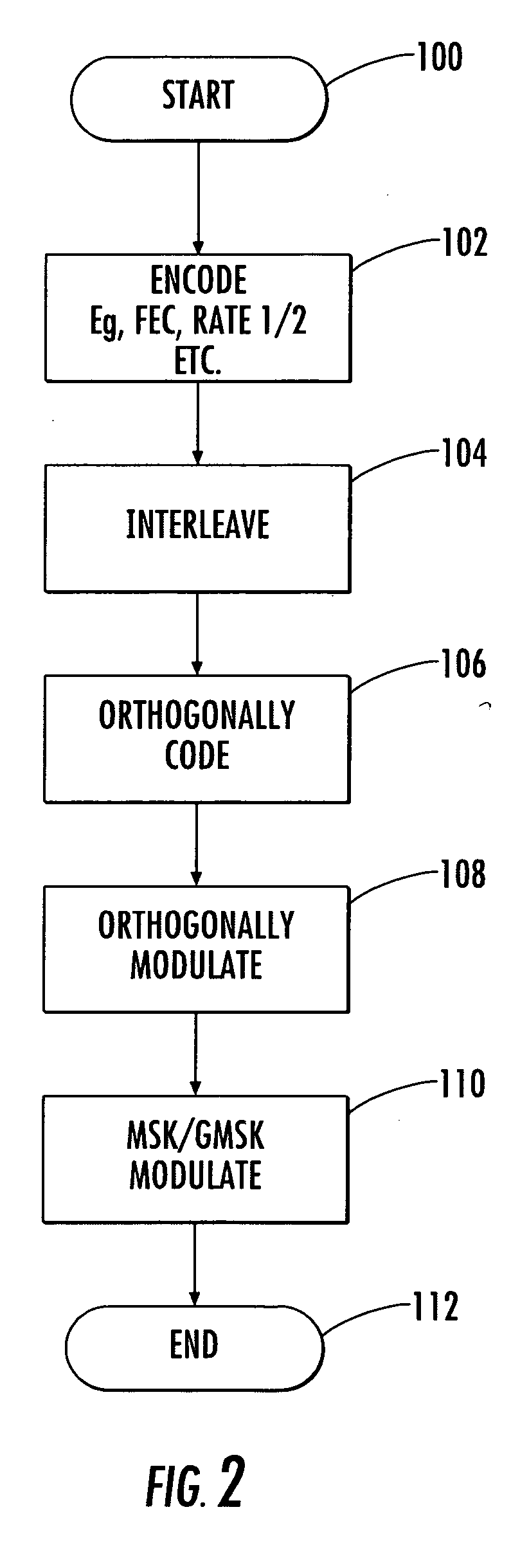

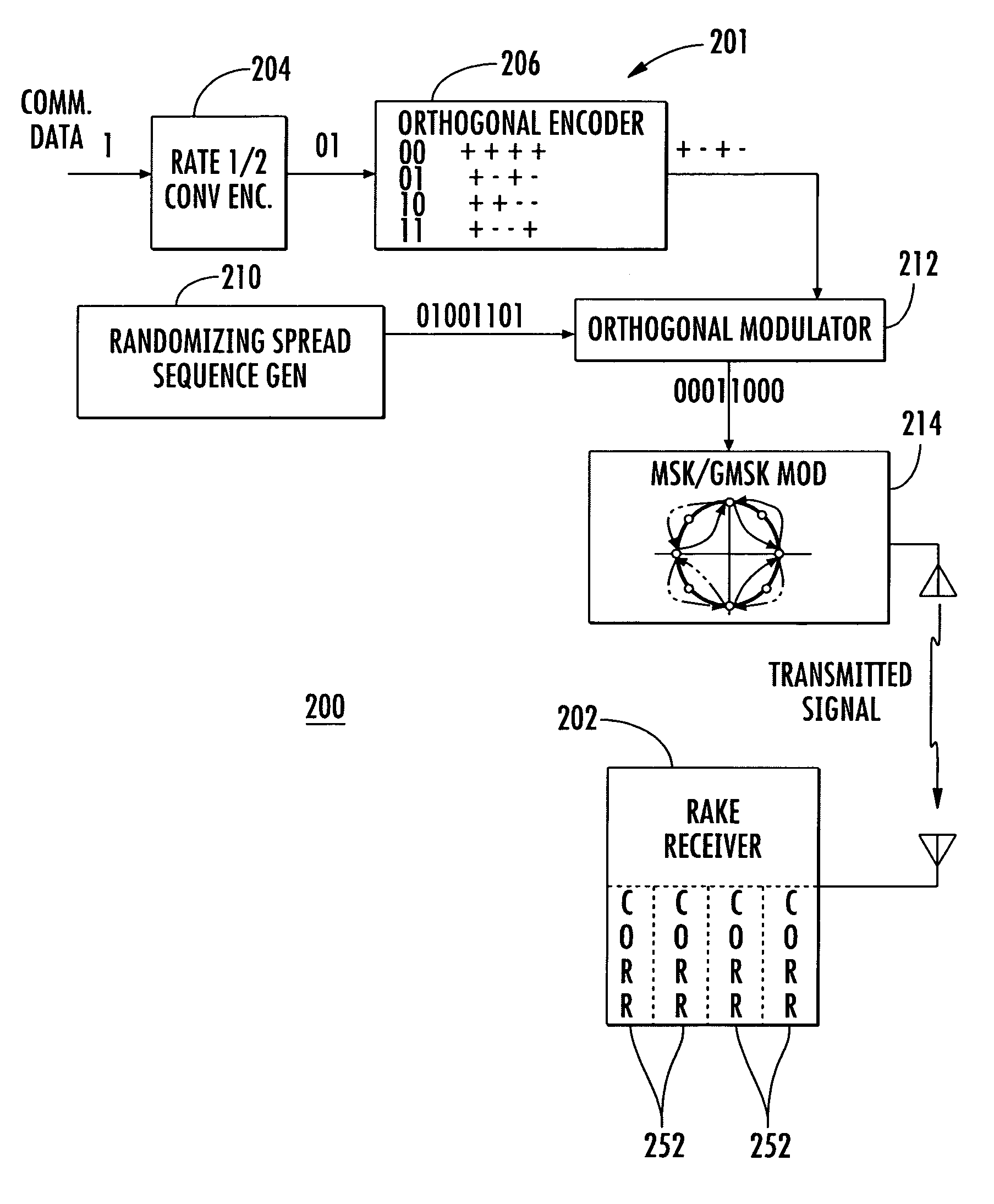

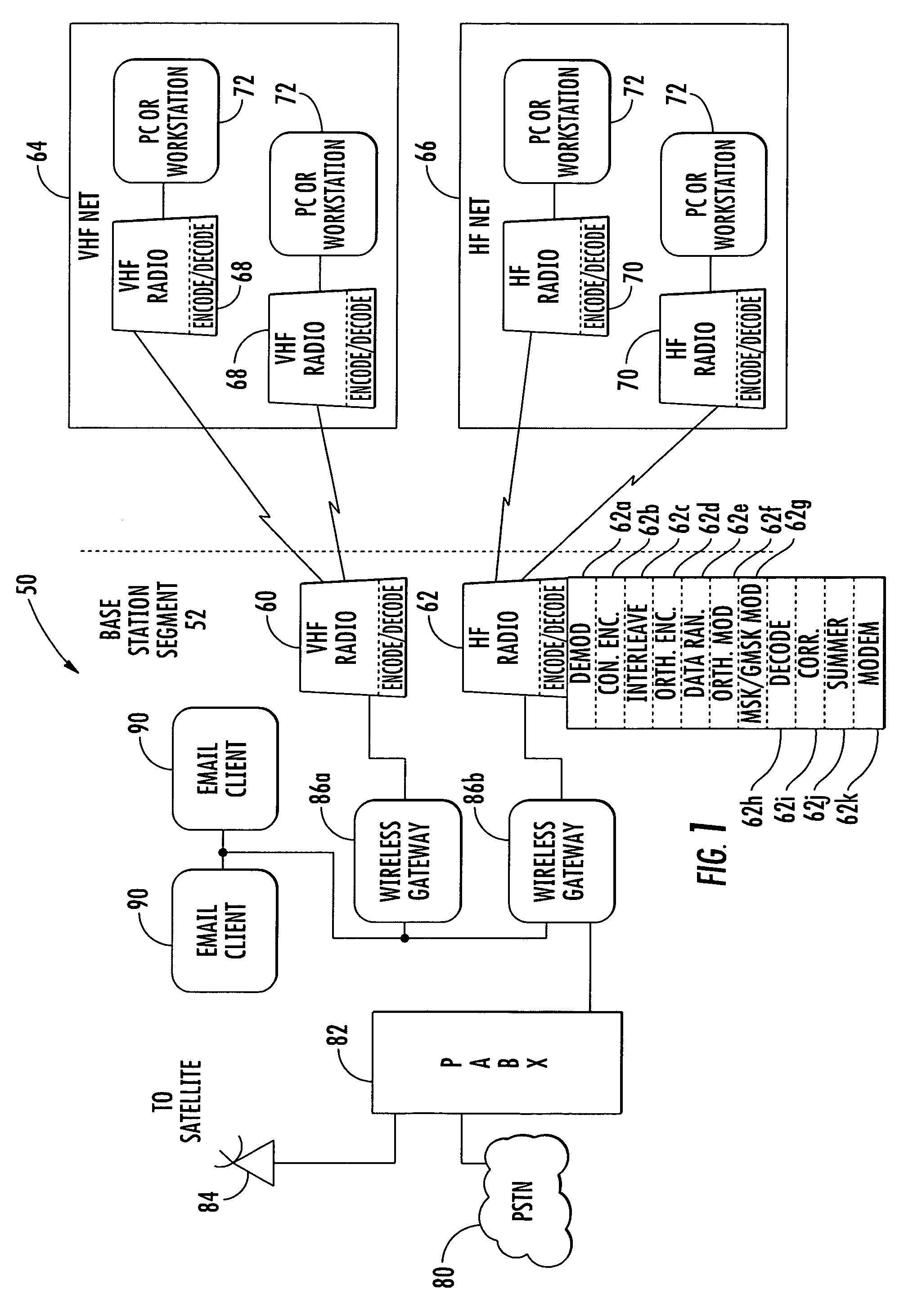

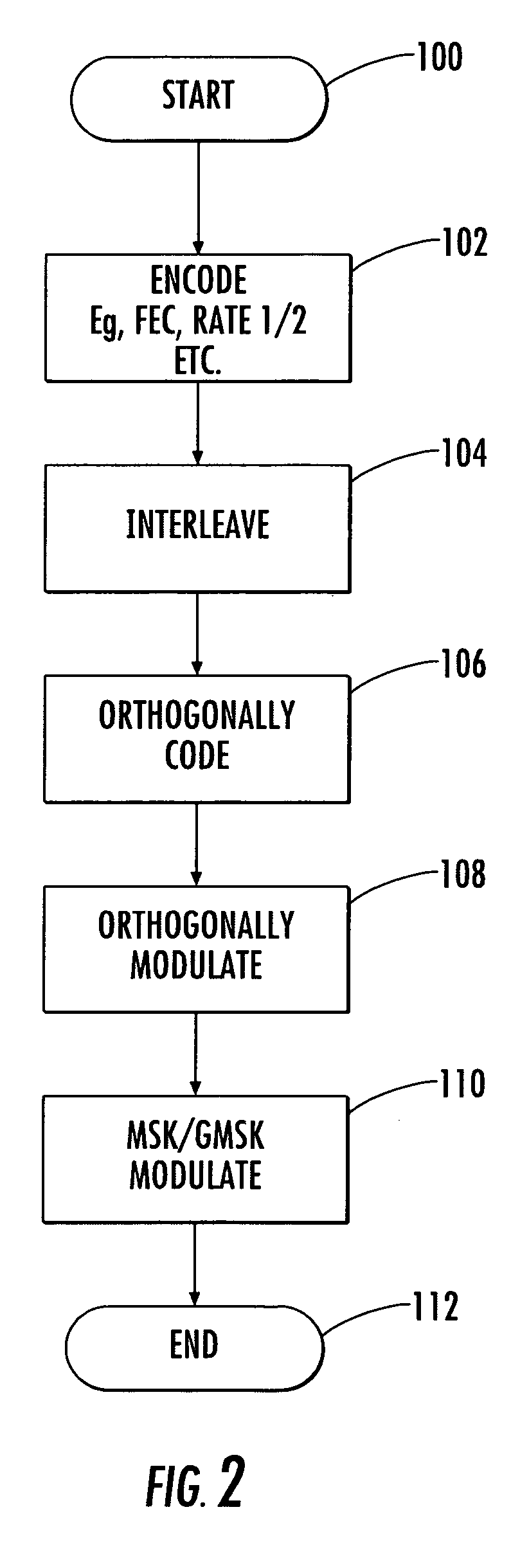

System and method for communicating data using constant amplitude waveform with hybrid orthogonal and MSK or GMSK modulation

ActiveUS20060251150A1Good spectral containmentConstant amplitudeError preventionAngle modulationCommunications systemRake receiver

A communications system of the present invention includes a transmitter that is operative for combining an orthogonal Walsh modulation with a minimum shift keying or Gaussian minimum shift keying waveform to form a hybrid communications signal that carries communications data over a constant amplitude waveform that is spread in time and frequency. This communications signal can be transmitted to a RAKE receiver that has a plurality of correlators with output weights formed for processing this hybrid communications signal.

Owner:HARRIS GLOBAL COMMUNICATIONS INC

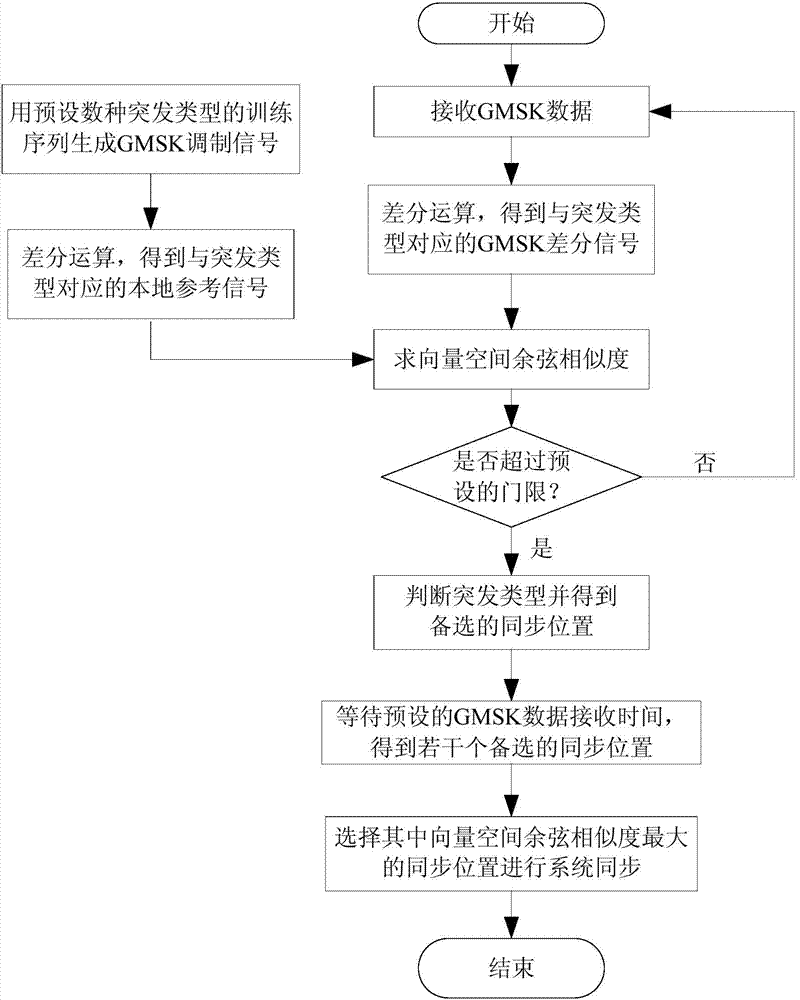

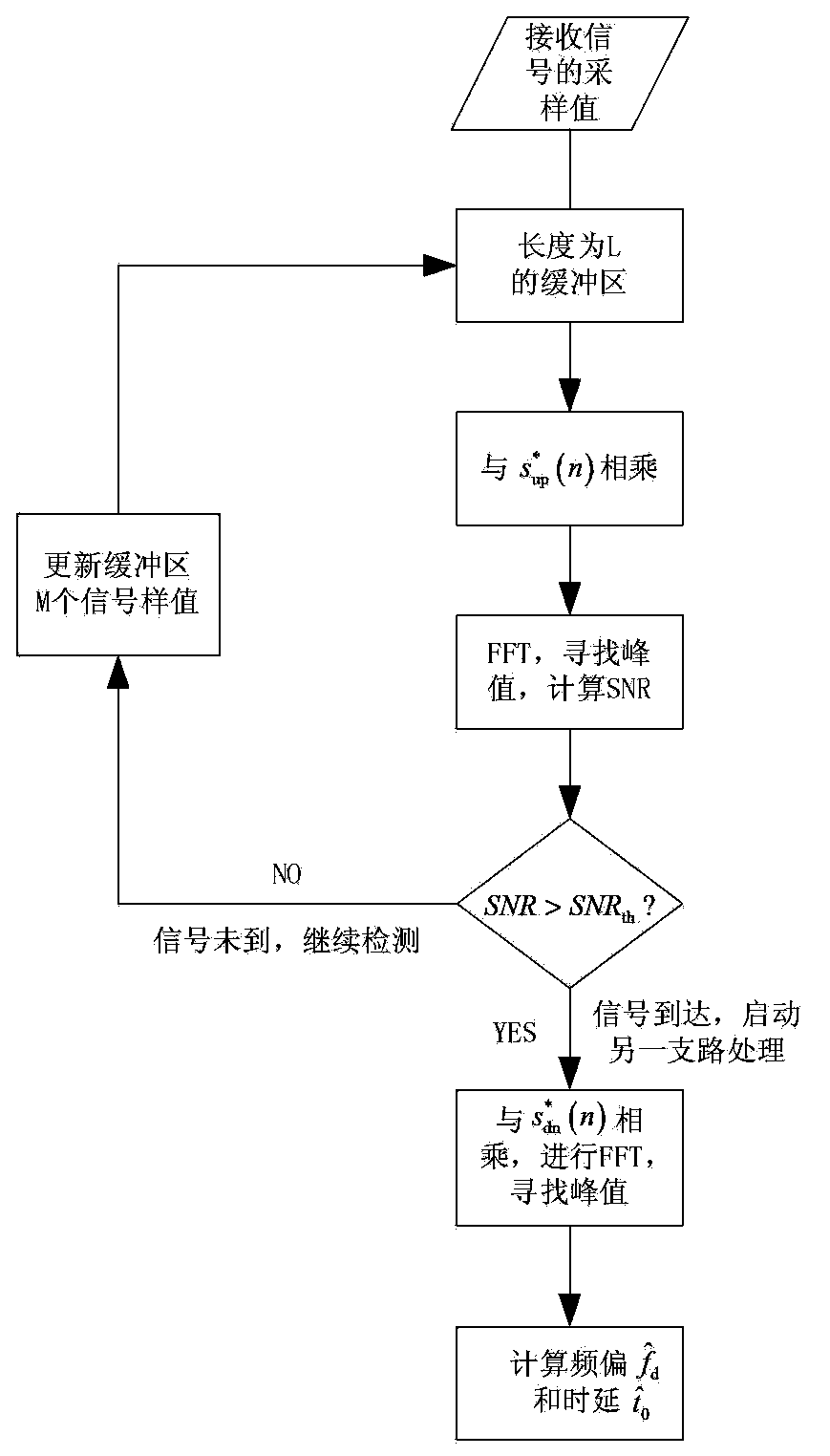

GMSK (Gaussian minimum shift keying) modulating system synchronization method

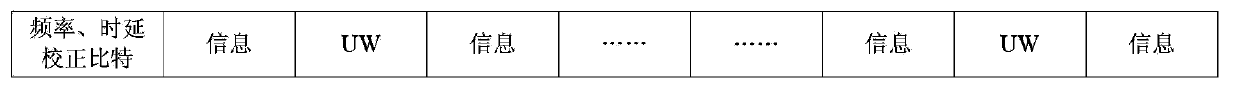

ActiveCN104333525ASuppress interferenceImprove robustnessModulated-carrier systemsCosine similarityData segment

The invention discloses a GMSK (Gaussian minimum shift keying) modulating system synchronization method which includes the steps: performing differential operation for GMSK modulating signals generated by a training sequence of preset numerous burst types to obtain a local reference signal; receiving GMSK data, marking current GMSK data receiving points as sampling points when the length of a received GMSK data segment is as same as that of the local reference signal, and performing differential operation for the current GMSK data segment to obtain a GMSK differential signal; gaining vector space cosine similarity according to the local reference signal and the GMSK differential signal in the same burst type; judging whether the vector space cosine similarity exceeds a threshold or not, continuing to receive the GMSK data if not, and then selecting one synchronization position from alternative synchronization positions to perform system synchronization within preset GMSK data receiving time. If the vector space cosine similarity exceeds the threshold, the burst type is the burst type of the currently received GMSK data, and the current sampling points are the alternative synchronization positions. Reliable synchronization can be realized, and the requirement of engineering application is more effectively met.

Owner:GUANGZHOU HAIGE COMM GRP INC

Gaussian minimum shift keying (GMSK) signal receiving method in satellite mobile communication

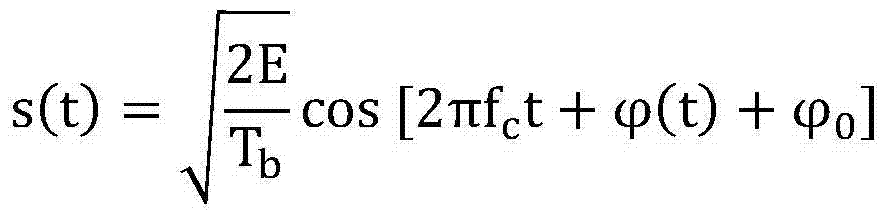

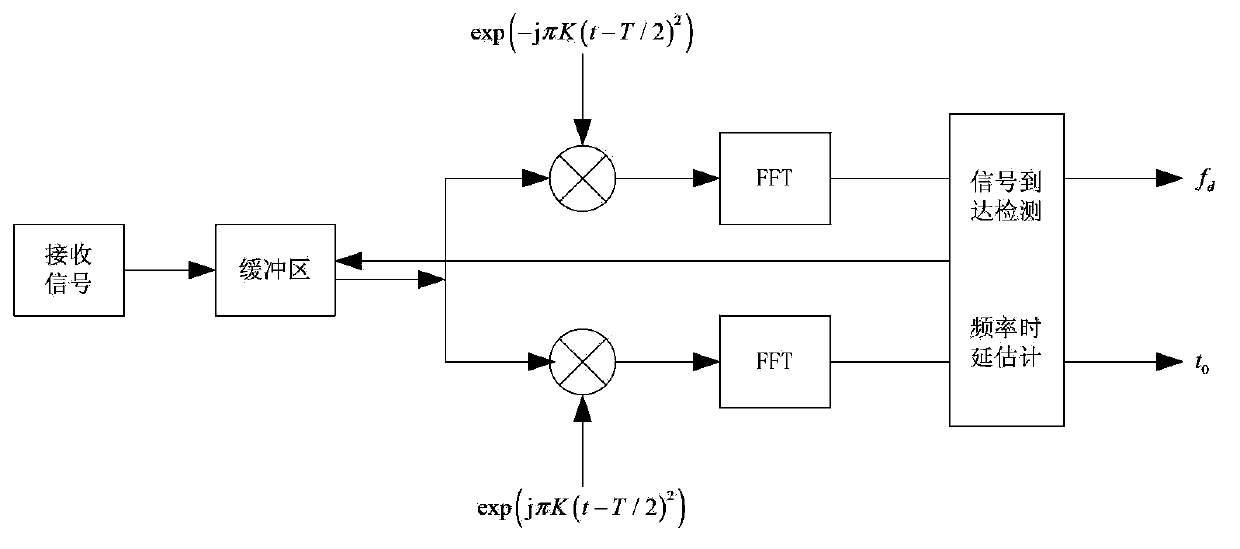

ActiveCN103428153ARapid implementation of arrival detectionSolve captured puzzlesSynchronisation signal speed/phase controlMulti-frequency code systemsChirpSatellite mobile communication

The invention discloses a GMSK signal receiving method in satellite mobile communication. The method comprises that firstly, double-Chirp signal assistance is conducted to perform system synchronization, by the aid of the method, the Doppler frequency and the time delay existing in a satellite mobile channel can be estimated quickly and accurately, and the system synchronization can be achieved; on the basis of completion of the system synchronization, a quasi-coherent algorithm is used for performing GMSK signal demodulation, according to the method, before the GMSK demodulation is performed at a transmitting end, 'precoding' is performed on raw information, and meanwhile, a 'de-rotation' module is added at a receiving end to simplify the design of timing synchronization greatly. The method is low in implementation complexity and low in performance loss. Performance test results of hardware implementation indicate that the relative loss of the bit error rate (BER) performance of the GMSK receiving method to the binary phase shift keying (BPSK) optimal coherent detection performance is about 0.7-0.8dB.

Owner:PLA UNIV OF SCI & TECH

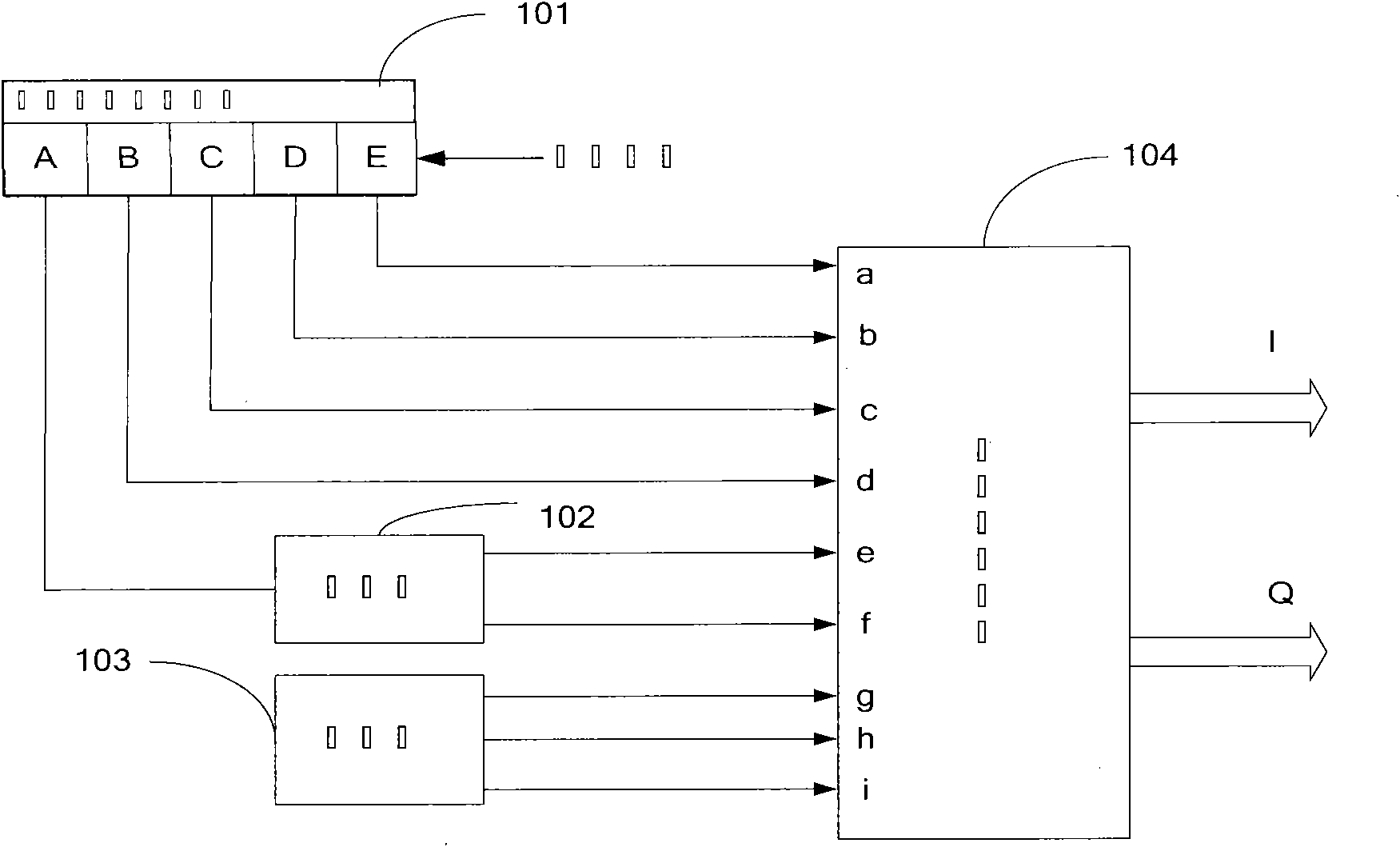

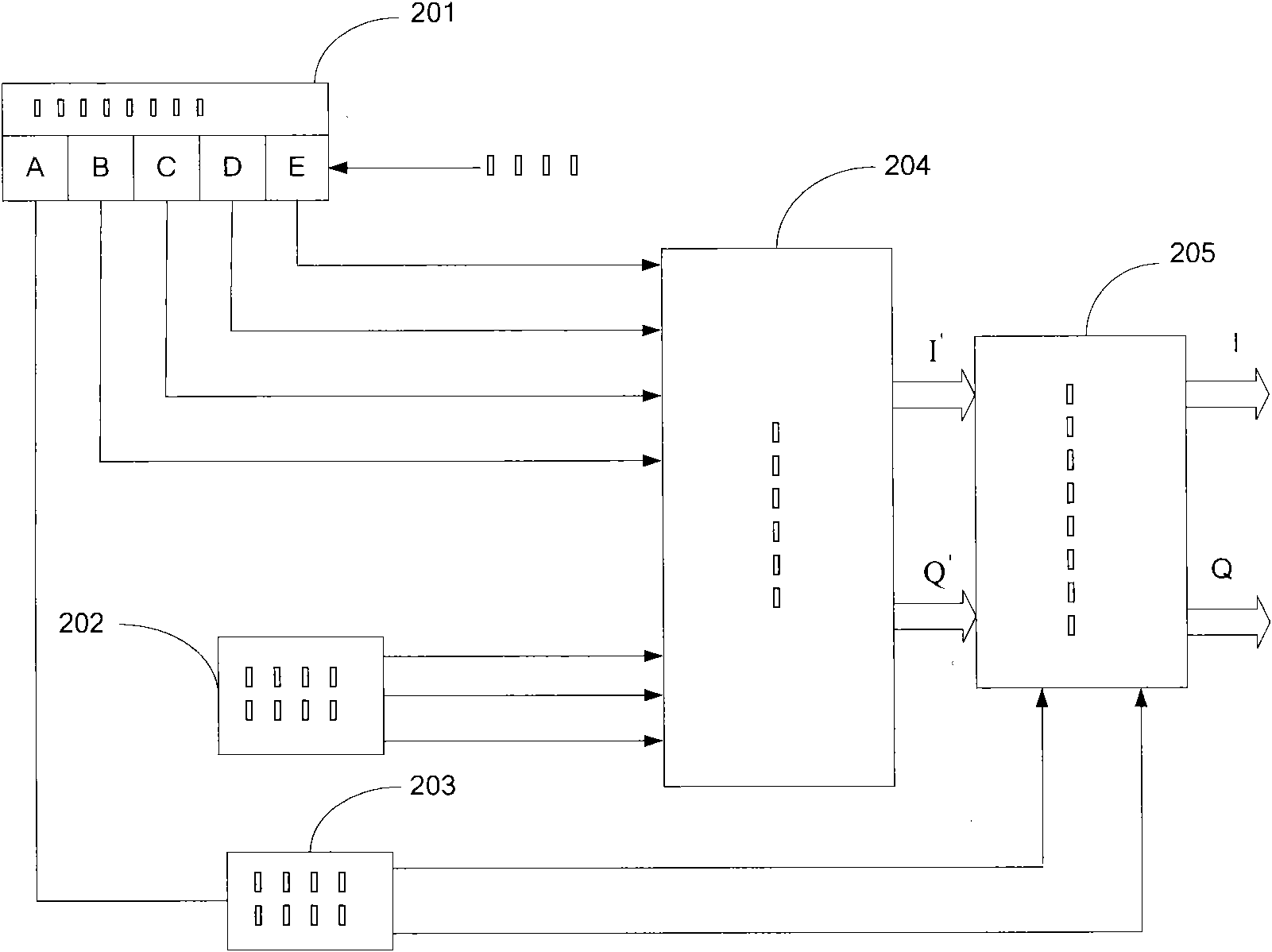

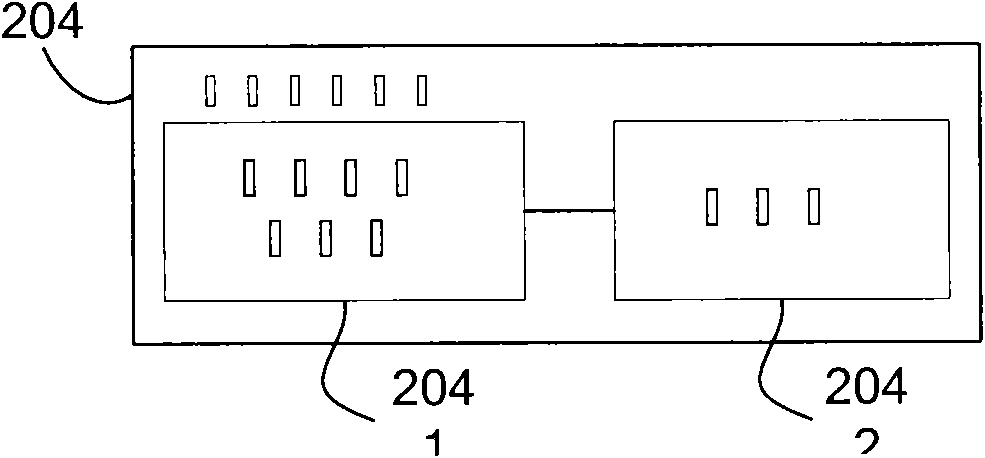

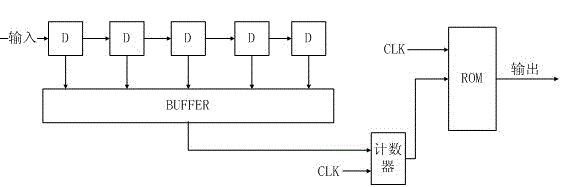

GMSK (Guassian Minimum Shift Keying) modulation device and method

InactiveCN101834818AReduce occupancyReduce areaPhase-modulated carrier systemsTransmitter/receiver shaping networksVery large scale integrated circuitsData acquisition

The invention discloses GMSK (Guassian Minimum Shift Keying) modulation device and method. The GMSK modulation device comprises a first data processing module, a first data generation module, a second data generation module, a data acquisition module and a second data processing module. Compared with the prior art, the GMSK modulation device provided by the embodiment of the invention does not use an accumulated phase bypass of a baseband signal as an address acquiring modulation signal data inside a lookup table, the lookup table only stores the modulation signal data related to the real-time phase information of the baseband signal, the final modulation signal data of the baseband signal is obtained by the modulation signal data looked up from the lookup table through angle rotation, therefore the ROM (Read Only Memory) occupying quantity of the lookup table is greatly reduced, the less capacity of the storage space of the ROM is, the smaller volume of the ROM is, and then the smaller area of an occupied chip is, thus the GMSK modulation device is more suitable for an super-large-scale integration.

Owner:广州市广晟微电子有限公司

System and method for communicating data using constant amplitude waveform with hybrid orthogonal and MSK or GMSK modulation

ActiveUS7352795B2Good spectral containmentConstant amplitudeError preventionAngle modulationCommunications systemRake receiver

A communications system of the present invention includes a transmitter that is operative for combining an orthogonal Walsh modulation with a minimum shift keying or Gaussian minimum shift keying waveform to form a hybrid communications signal that carries communications data over a constant amplitude waveform that is spread in time and frequency. This communications signal can be transmitted to a RAKE receiver that has a plurality of correlators with output weights formed for processing this hybrid communications signal.

Owner:HARRIS GLOBAL COMM INC

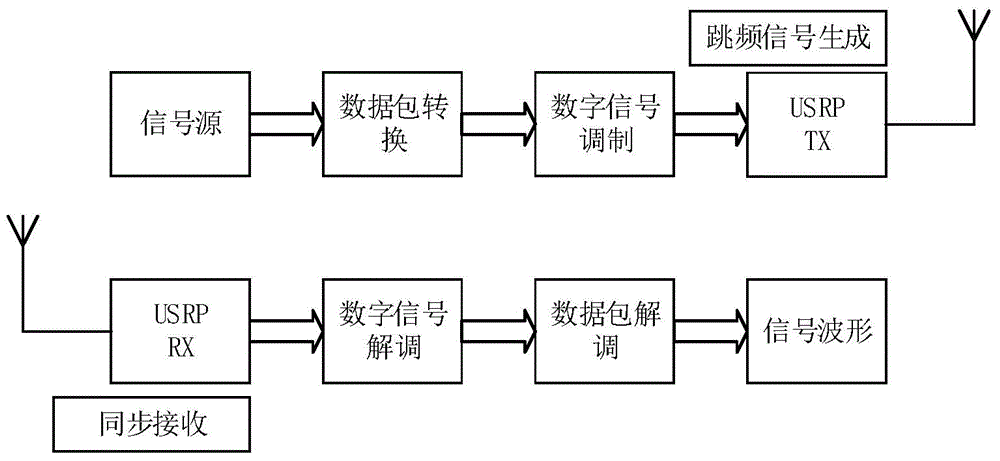

Radio communication system

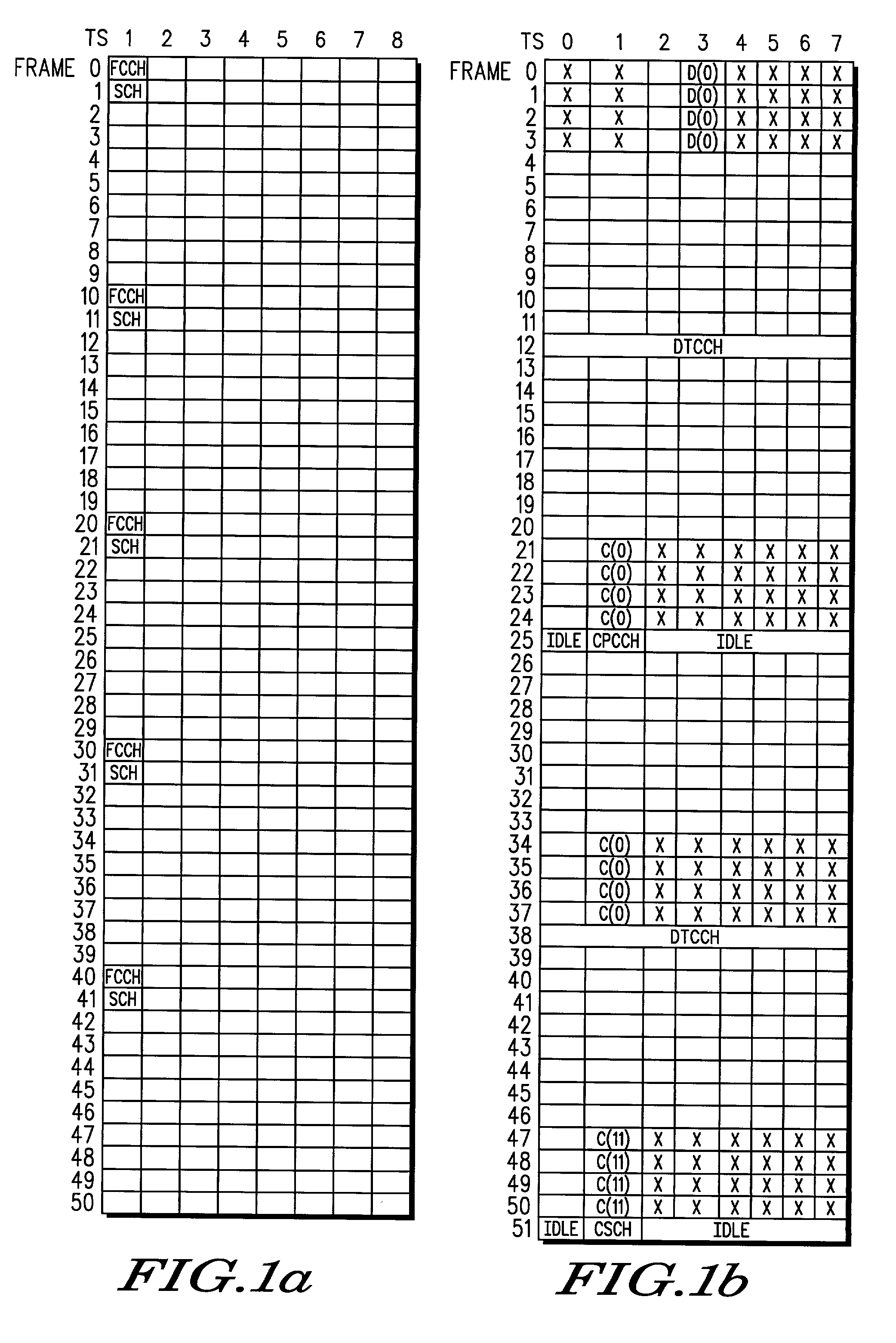

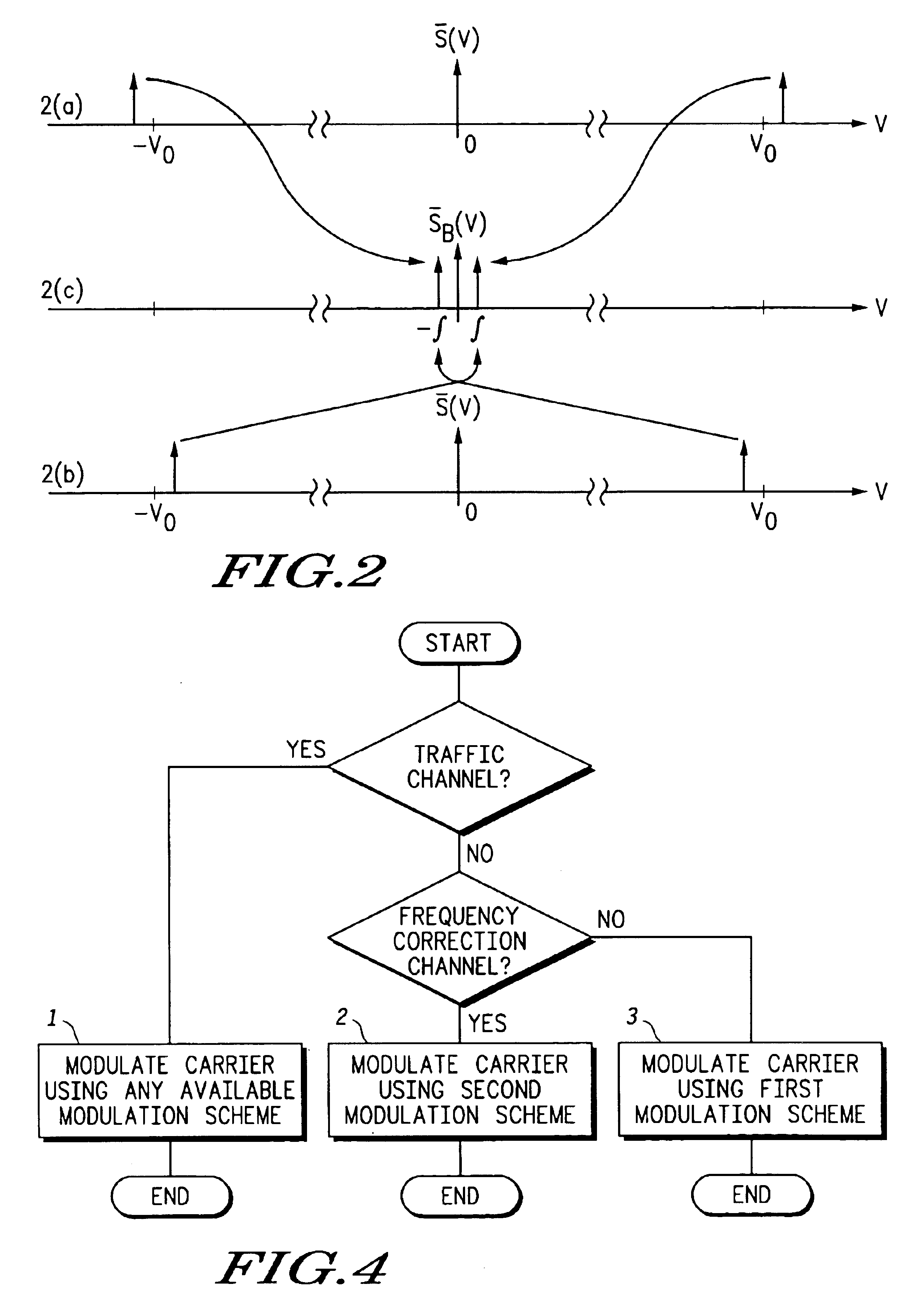

InactiveUS20030026238A1Time-division multiplexSynchronisation signal speed/phase controlCommunications systemEngineering

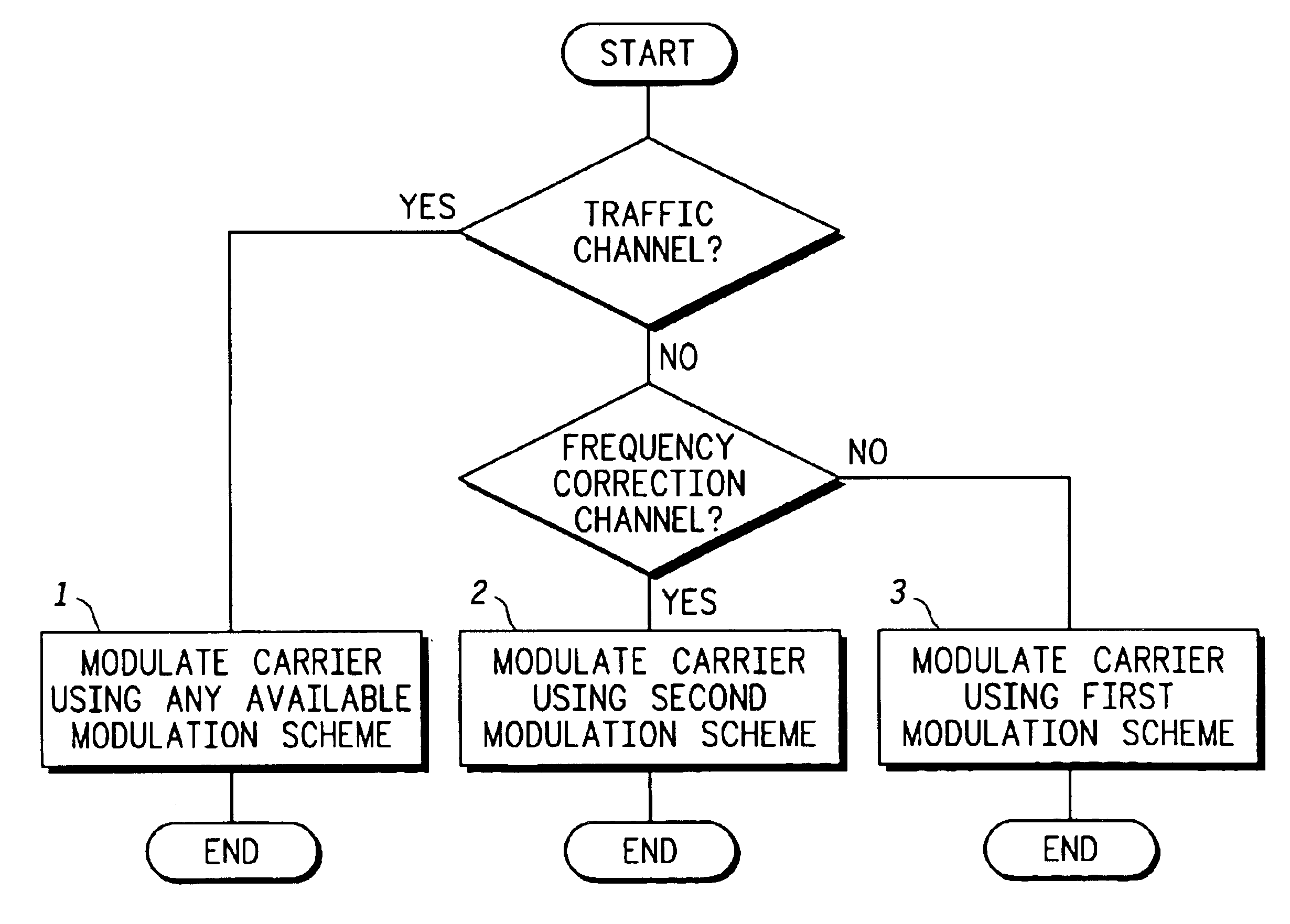

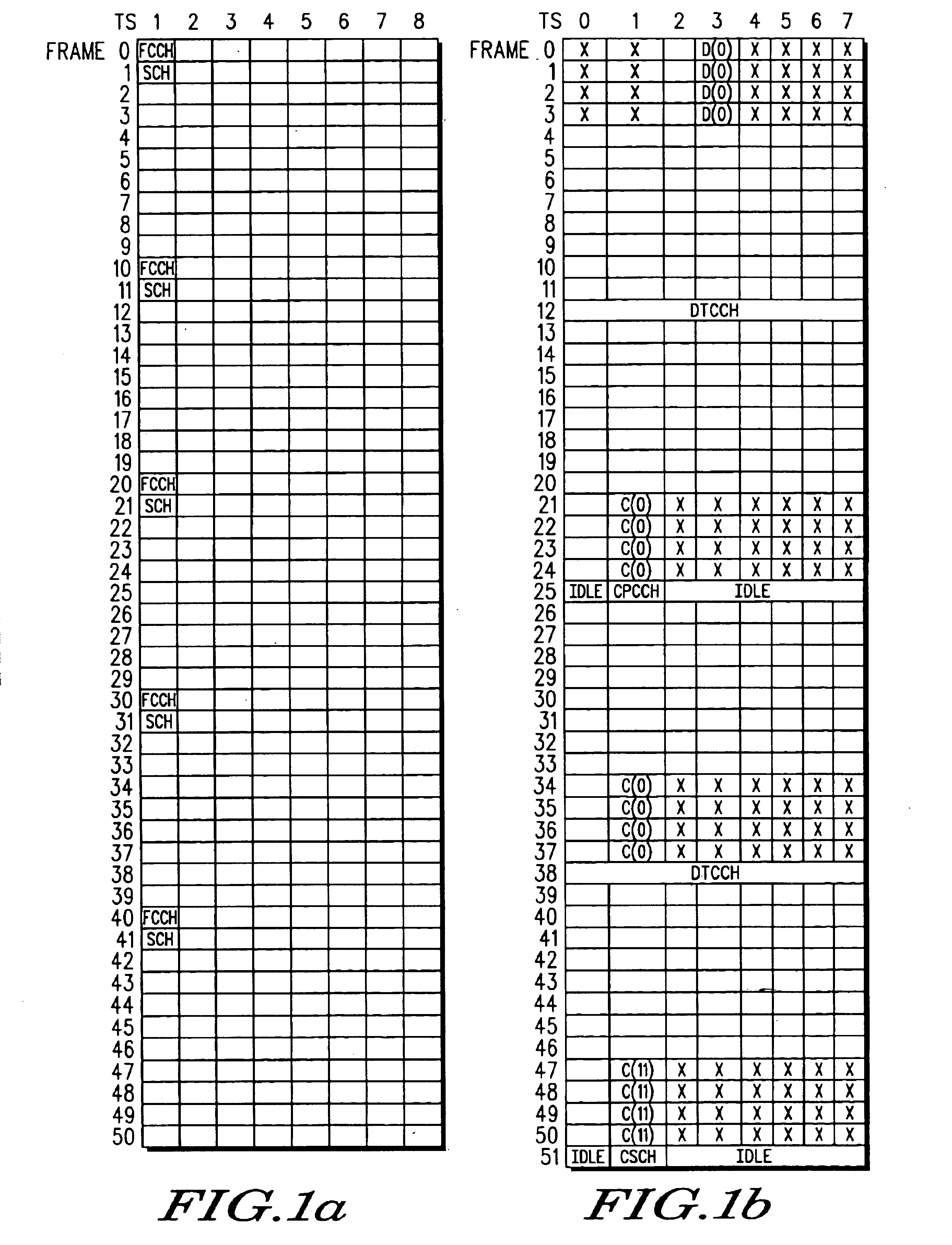

The invention relates to a radio communication system in which a time slot of a frame of a multiframe signal allocated to the frequency control channel is modulated using an 8PSK modulation scheme to contain a tone having a frequency which GMSK modulation is unsuited to generate. This enables COMPACT-format signals to be distinguished from GSM-format signals and ensures backwards compatibility with all existing GSM mobile stations.

Owner:GOOGLE TECH HLDG LLC

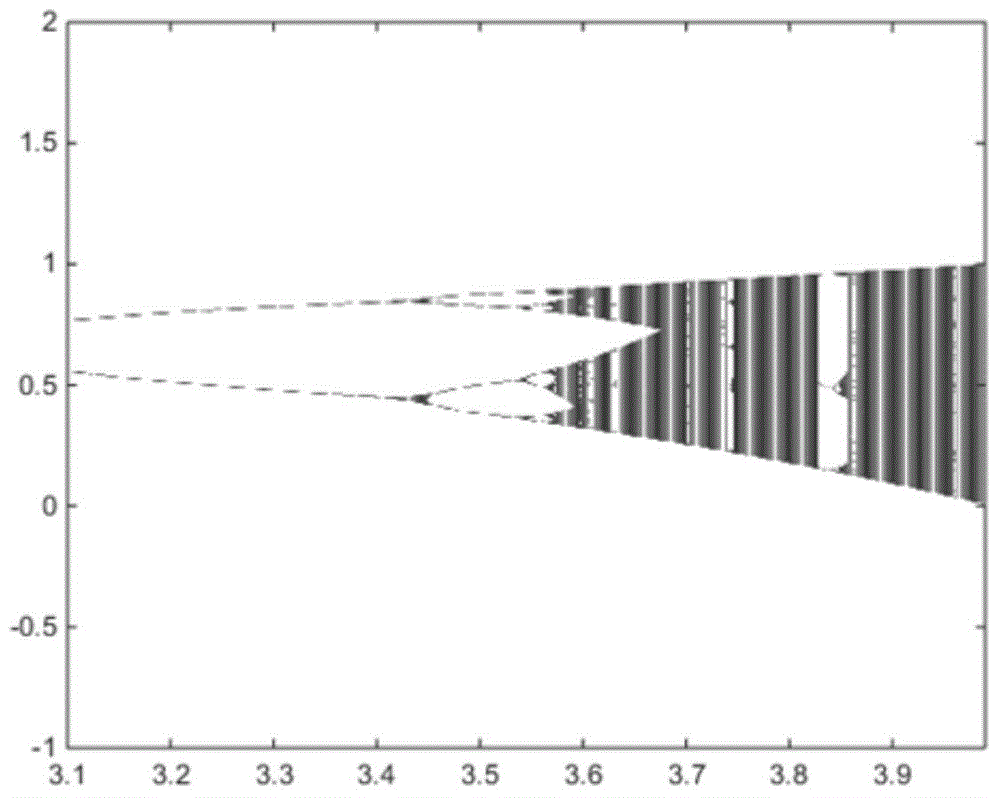

Short-wave frequency hopping communication system based on general software radio platform

A short-wave frequency hopping communication system based on a general software radio platform is disclosed. A signal emission module comprises a signal source module, a data packet conversion module, a digital signal modulation module and a USRP TX module, and the modules are successively connected. A signal receiving module comprises a USRP RX module, a digital signal demodulation module, a data packet demodulation module and a signal waveform module, and the modules are successively connected. On an emission module terminal, the signal source module emits a local signal; the data packet carries out data format conversion; GMSK modulation is performed; the USRP TX module carries out random emission at different time slots and different frequency points in a 3MHz-30MHz frequency range. On a receiving module terminal, a MIMO wire is used to connect a transmitter and a receiver; time synchronization is performed; an algorithm of emitting a same frequency hopping signal is used to carry out frequency hopping sequence synchronization; after the frequency hopping signals are received synchronously, the data format conversion is performed, the GMSK modulation is performed and a local signal is restored. By using the system of the invention, flexibility is high; equipment is simple; reconfiguration can be performed; a plurality of standards can be supported; rapid constructing can be performed and so on.

Owner:NANCHANG UNIV

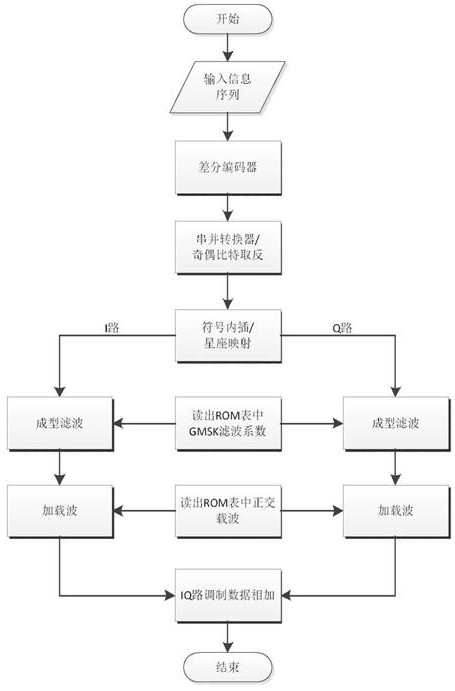

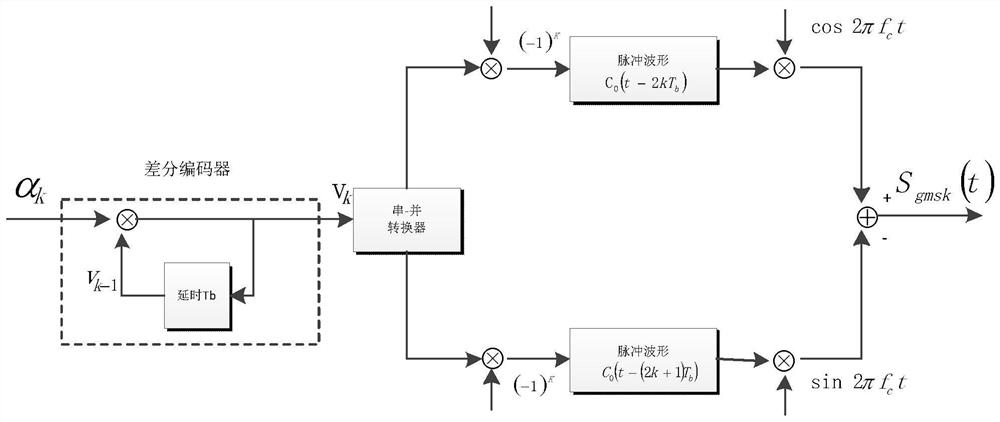

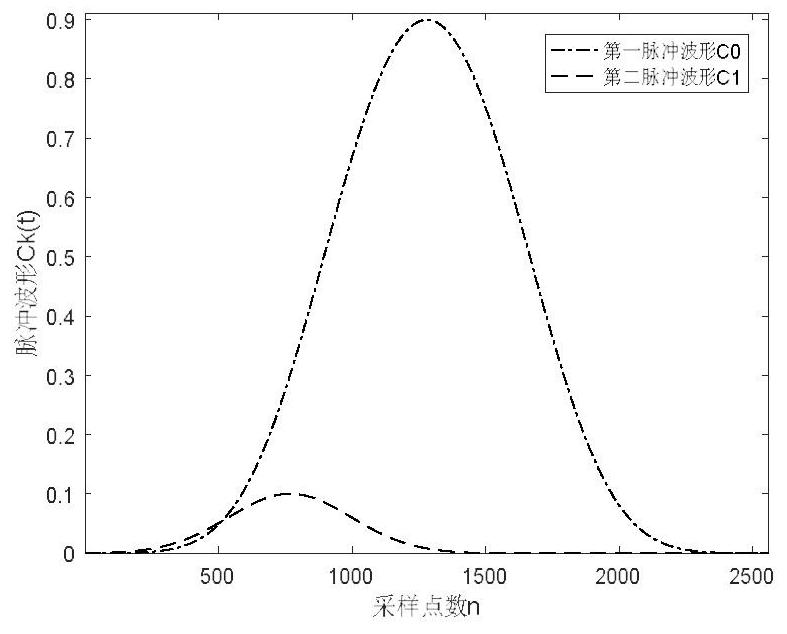

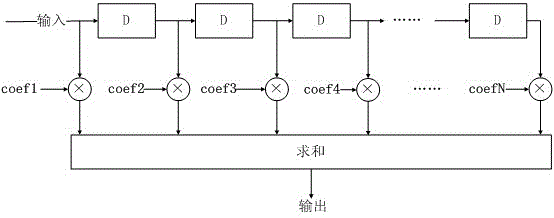

Hardware implementation method for GMSK modulation

ActiveCN111970087AGood demodulation performanceReduce computationFrequency-modulated carrier systemsMultiple carrier systemsComputer hardwareConverters

The invention provides a hardware implementation method for GMSK modulation, and aims to provide a method which is less in hardware resource consumption, convenient to expand and easy for hardware implementation. According to the technical scheme, the method comprises the following steps: sending an input information sequence into a differential encoder by a data processor for differential precoding, wherein the data processor is used for calculating according to Latent expansion; by a serial-to-parallel converter, performing serial-to-parallel conversion on the differentiated sequence, negating odd bits of the differential sequence subjected to serial-to-parallel conversion to obtain I and Q orthogonal baseband data before filtering forming corresponding to the pulse flow; by an interpolator, performing constellation mapping and shaping filtering on bit data obtained by symbol interpolation, reading a Gaussian minimum frequency shift keying (GMSK) filter coefficient prepared in advance from a ROM table; achieving convolution of the modulated data and data after constellation mapping through a multiplier, then multiplying carrier data in the ROM table by formed baseband data, and adding the I and Q modulated data to obtain final GMSK modulated signal data.

Owner:10TH RES INST OF CETC

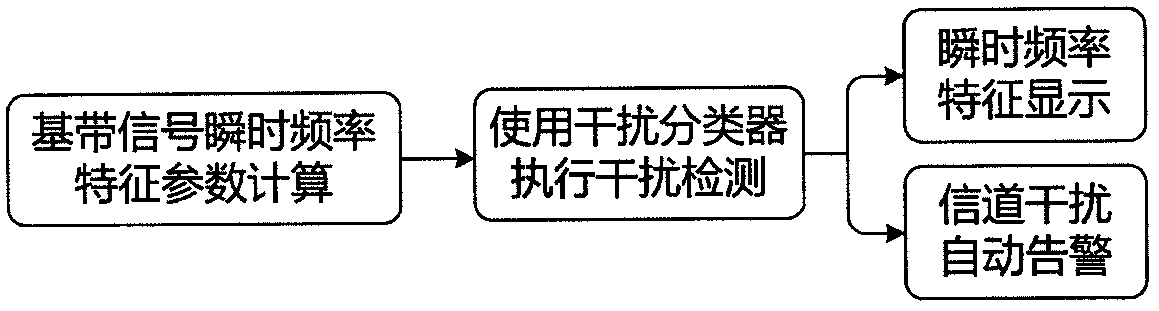

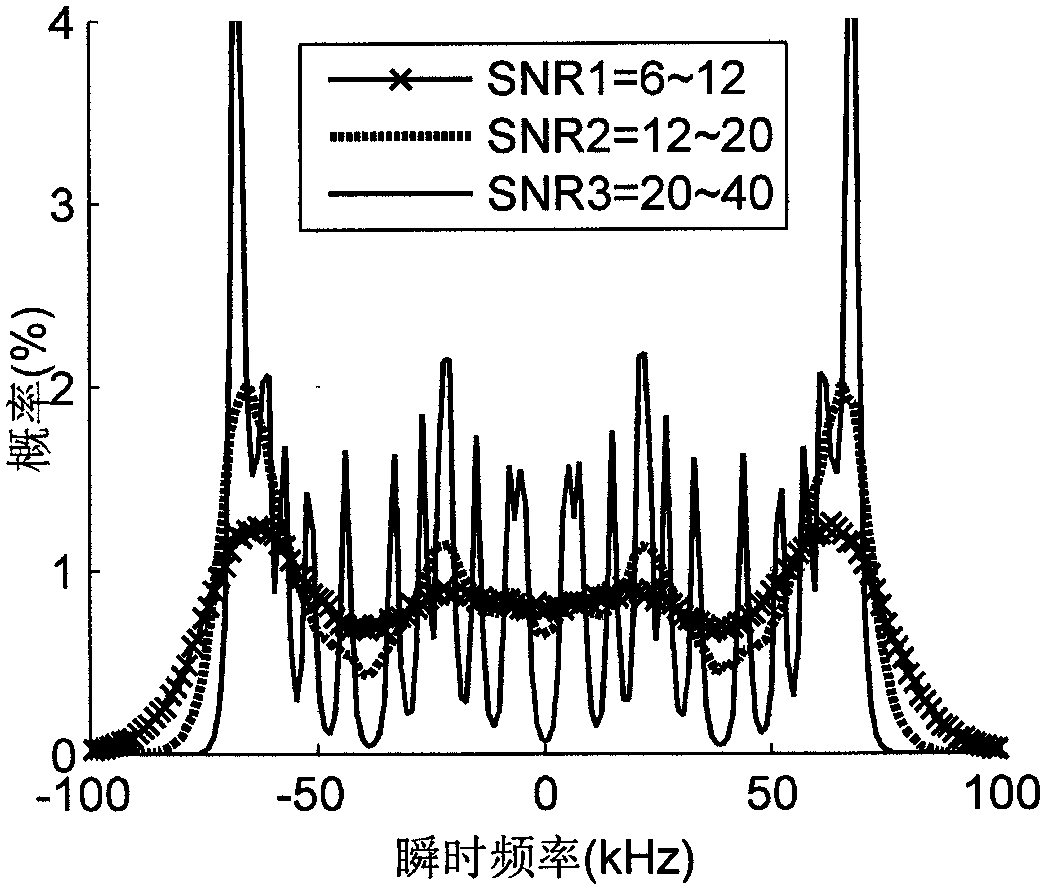

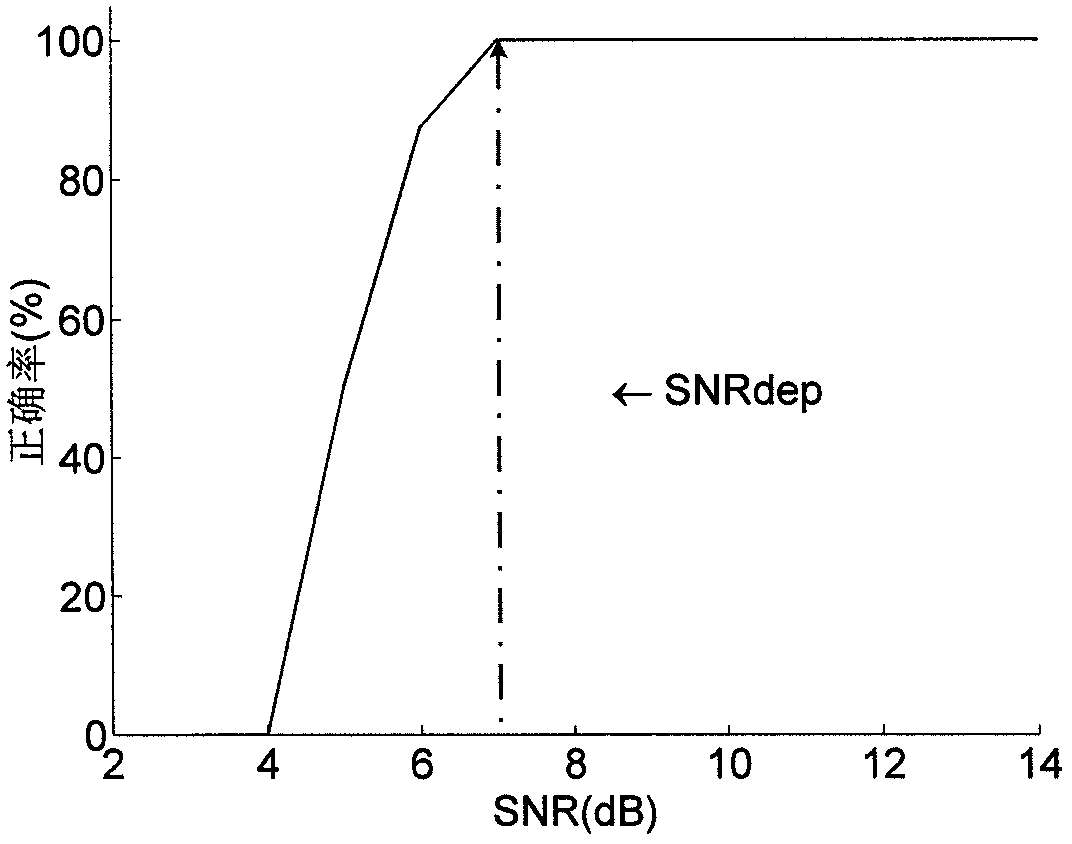

GMSK channel interference detection method

InactiveCN108631893AExcellent interference detection performanceTransmission monitoringTime domainComputation complexity

The invention provides a GMSK channel interference detection method. For the problems of co-frequency and adjacent-frequency interference detection in a GMSK channel, the special instantaneous frequency histogram distribution characteristics of GMSK modulation are used, a characteristic calculation interval and a characteristics threshold are obtained through learning and training, and an interference classifier based on characteristic parameters is established. In actual working, the special instantaneous frequency histogram distribution characteristics and the threshold are classified and determined by the interference classifier, and whether there is interference in the channel is detected. The method has a high detection probability for interference with unapparent spectrum characteristics and time domain amplitude characteristics in the GMSK channel and has the advantages of low computational complexity and low implementation cost.

Owner:CHENGDU UNIV OF INFORMATION TECH

Method for receiving a signal and receiver

InactiveCN101958859AImprove spectral efficiencyLimit distractionsModulated-carrier systemsCode division multiplexDecompositionPhason

A process for receiving a GMSK-modulated signal which, for simultaneously transmitting two services, has an in-phase signal with a pseudo-random code that differs from the quadrature signal. By means of a decomposition filter in a reference signal branch detects one service independently of the other during the correlating with the received signal.

Owner:ASTRIUM GMBH +1

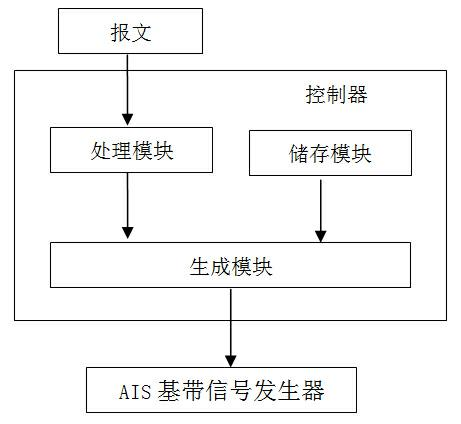

Automatic identification system (AIS) baseband signal communication equipment

InactiveCN102662160AReduce power consumptionExtended use timeWave based measurement systemsFrequency-modulated carrier systemsFloating pointComputer science

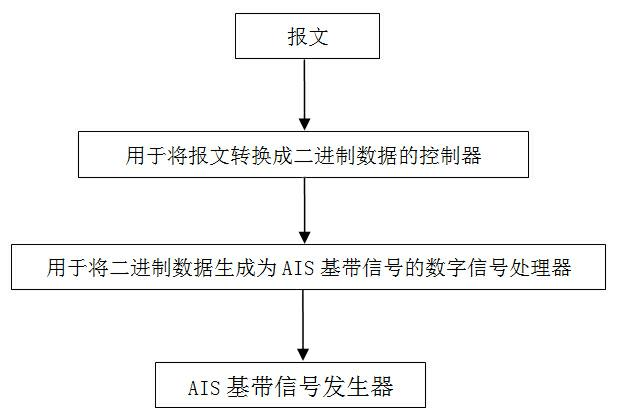

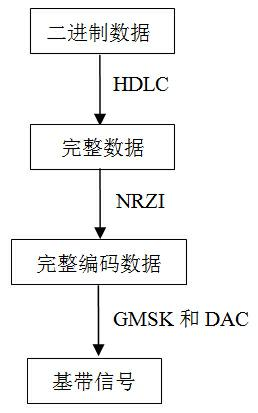

The invention relates to an automatic identification system (AIS) baseband signal communication equipment, which comprises a controller and an emitter, and is characterized in that the controller comprises a processing module for converting messages into binary data, a storage module for storing the binary data and the corresponding AIS baseband signal waveform, and a generation module for extracting the corresponding AIS baseband signal waveform from the storage module according to the binary data converted by the processing module and generating an AIS baseband signal; and the AIS baseband signal generated by the generation module is emitted by the emitter. The AIS baseband signal communication equipment has the advantages that by utilizing characteristics of the Guassian minimum shift keying (GMSK) modulated baseband signal, the controller extracts the corresponding AIS baseband signal waveform from the storage module according to the binary data to generate the AIS baseband signal, and complicated floating-point calculation is not required, so processors such as a digital signal processor (DSP) are not required; and therefore, the power consumption of the equipment is greatly reduced and the service time of the equipment is effectively prolonged.

Owner:WUHAN UNIV OF TECH

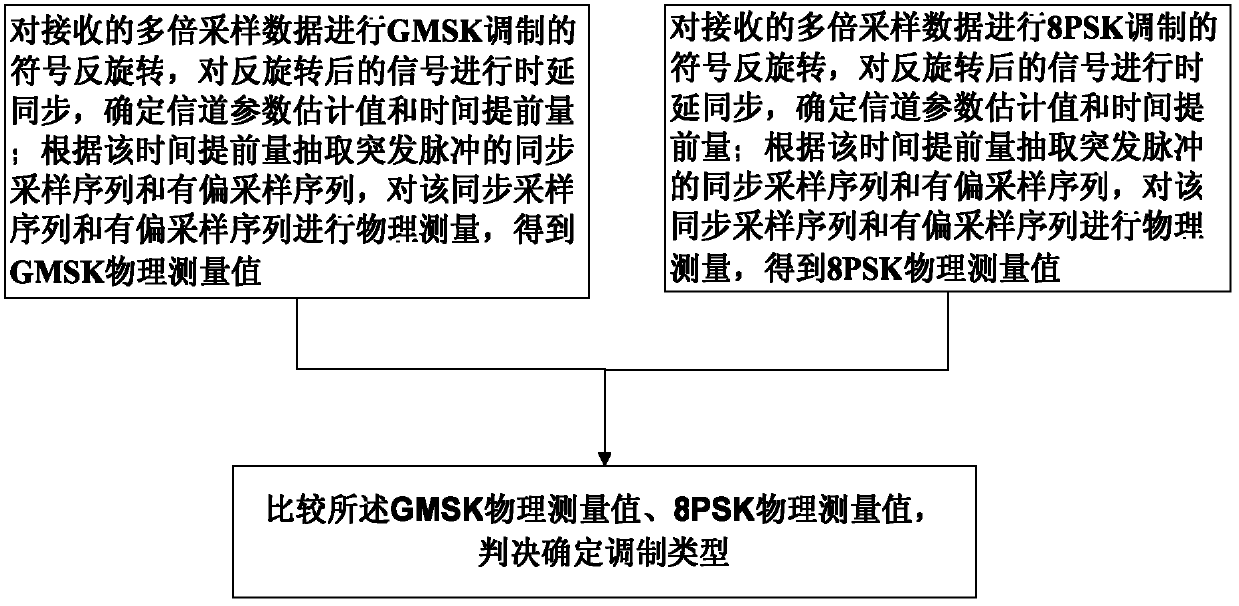

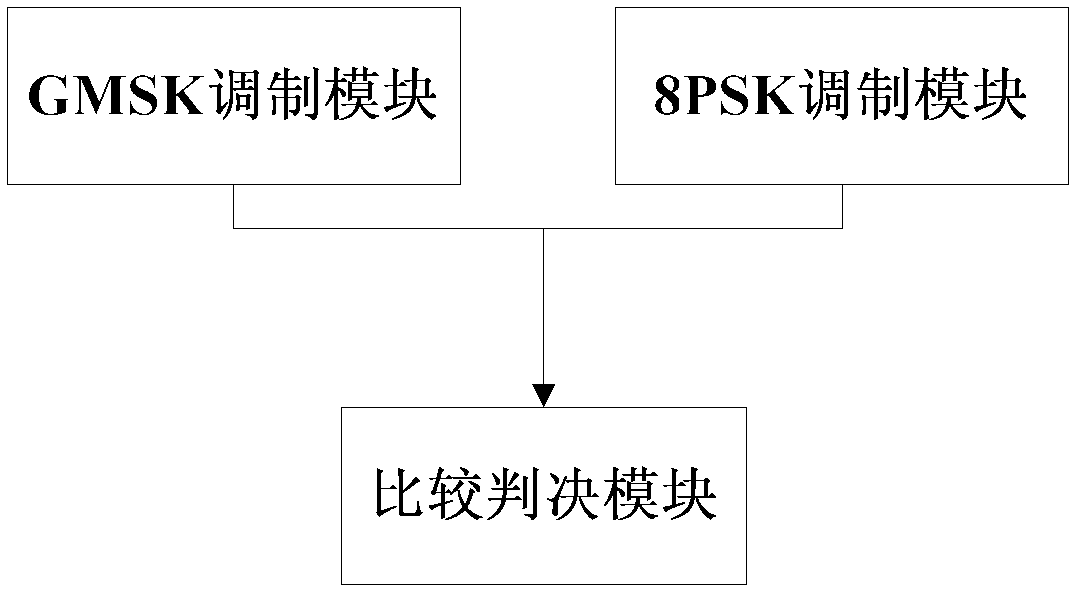

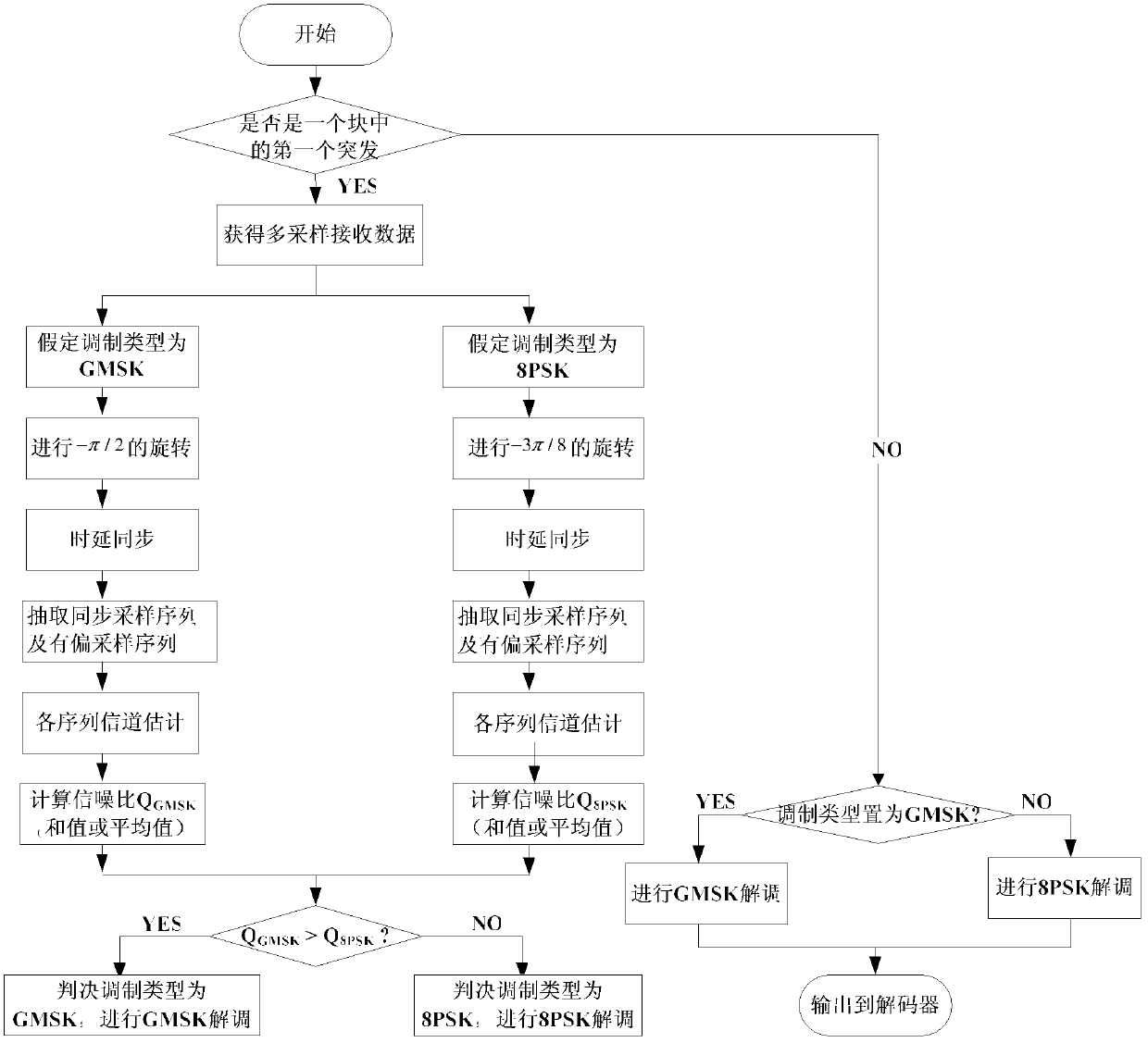

Method and device for detecting modulation type of EDGE communication system

InactiveCN102186197AImprove accuracyImprove the immunityBaseband system detailsFrequency-modulated carrier systemsCommunications systemInformation quantity

The invention provides a method and device for detecting the modulation type of a EDGE (Enhanced Data Rates for GSM Evolution) communication system, wherein the method comprises the following steps of: performing symbol counter-rotation of GMSK (Gaussian-filtered Minimum Shift Keying) modulation and 8PSK (8 Phase Shift Keying) modulation on received multiple sampling data respectively; performing time delay synchronization on counter-rotated signals to determine channel estimation values and time leads; extracting a synchronous sampling sequence and a biased sampling sequence of a burst pulse in accordance with various time leads; and performing physical measurement on the synchronous sampling sequence and the biased sampling sequence, comparing the physical measurement values obtained by calculation under two modulation types, and determining the modulation types by means of judgment. The method and the device provided by the invention greatly enhance the ability of judgment criteria in resisting channel distortion and noise owing to the consideration of asynchronous information quantity, effectively improve the correctness in detecting the modulation types, andare not high in complexity, simple, effective and great in application prospect.

Owner:COMBA TELECOM SYST CHINA LTD

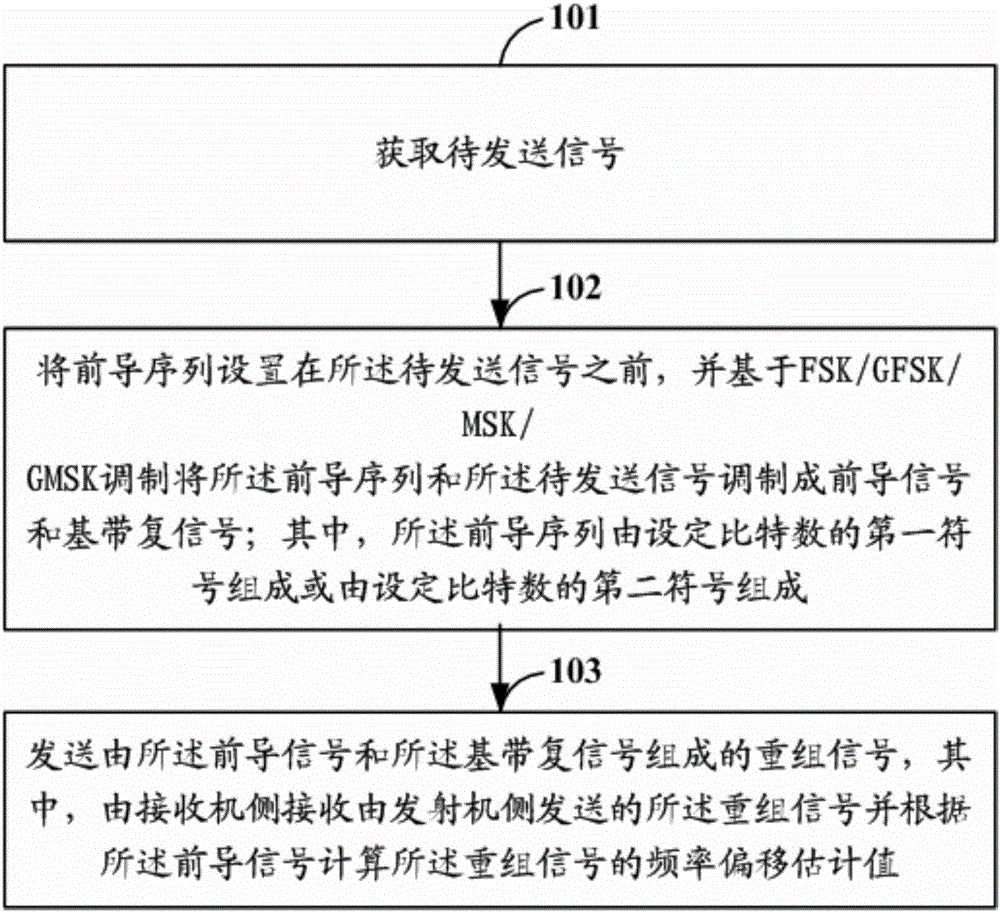

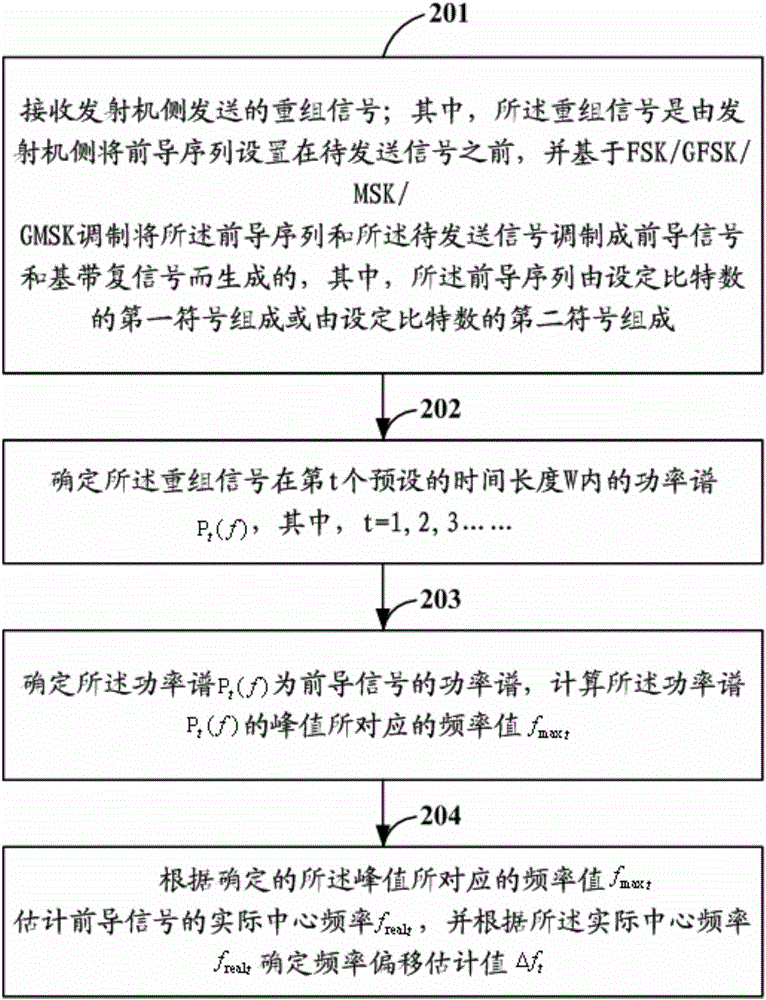

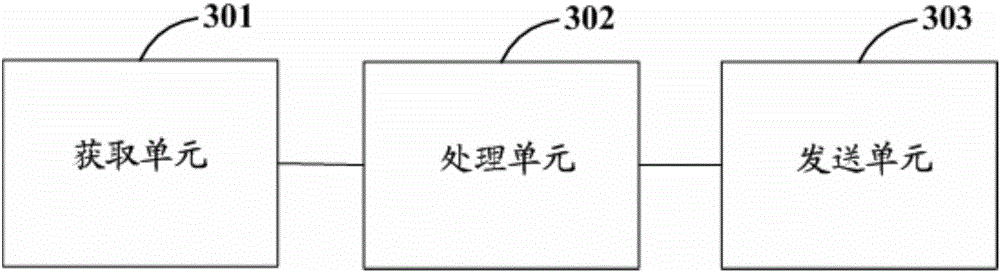

Frequency offset estimation methods, transmitter, receiver and communication system

ActiveCN106254289AIncrease redundancyImprove anti-interference abilityCarrier regulationMulti-frequency code systemsEngineeringFrequency shift

The present invention relates to frequency offset estimation methods based on frequency shift keying (FSK) / Gaussian FSK (GFSK) / minimum shift keying (MSK) / Gaussian MSK (GMSK) modulation, a transmitter, a receiver, and a communication system. A preamble sequence consisting of set symbols can be set as a preamble signal of a baseband complex signal, power spectrum analysis is performed on the preamble signal so as to estimate a frequency offset value of the baseband complex signal, and the receiver does not need to generate or pre-store the preamble signal, nor perform demodulation operation on the received preamble signal, so that the complexity of the algorithm and the communication system is lowered. In addition, the preamble sequence consisting of the same symbols improves the redundancy and anti-interference capability of the preamble signal, so that a frequency offset estimation result calculated according to the preamble signal is more accurate.

Owner:RUIJIE NETWORKS CO LTD

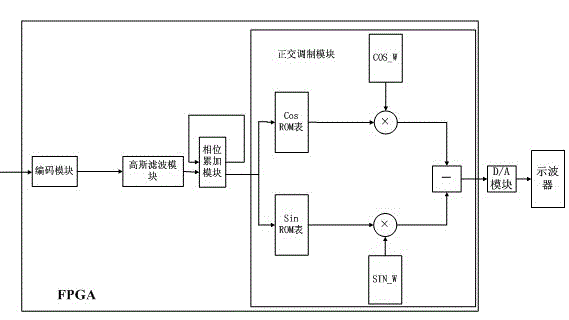

Method for realizing GMSK (Guassian Minimum Shift Keying) signal generator based on FPGA (Field Programmable Gate Array)

InactiveCN102983839AMeet the needs of full digitalizationFast implementationProgramme controlDigital technique networkInformation processingDigital signal processing

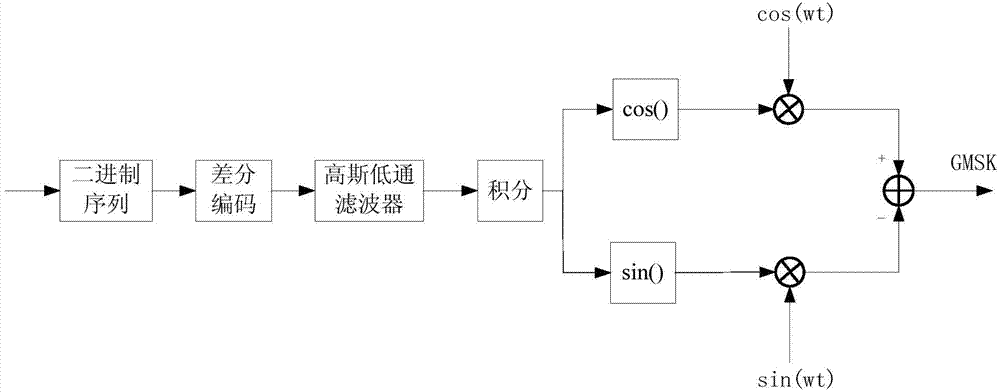

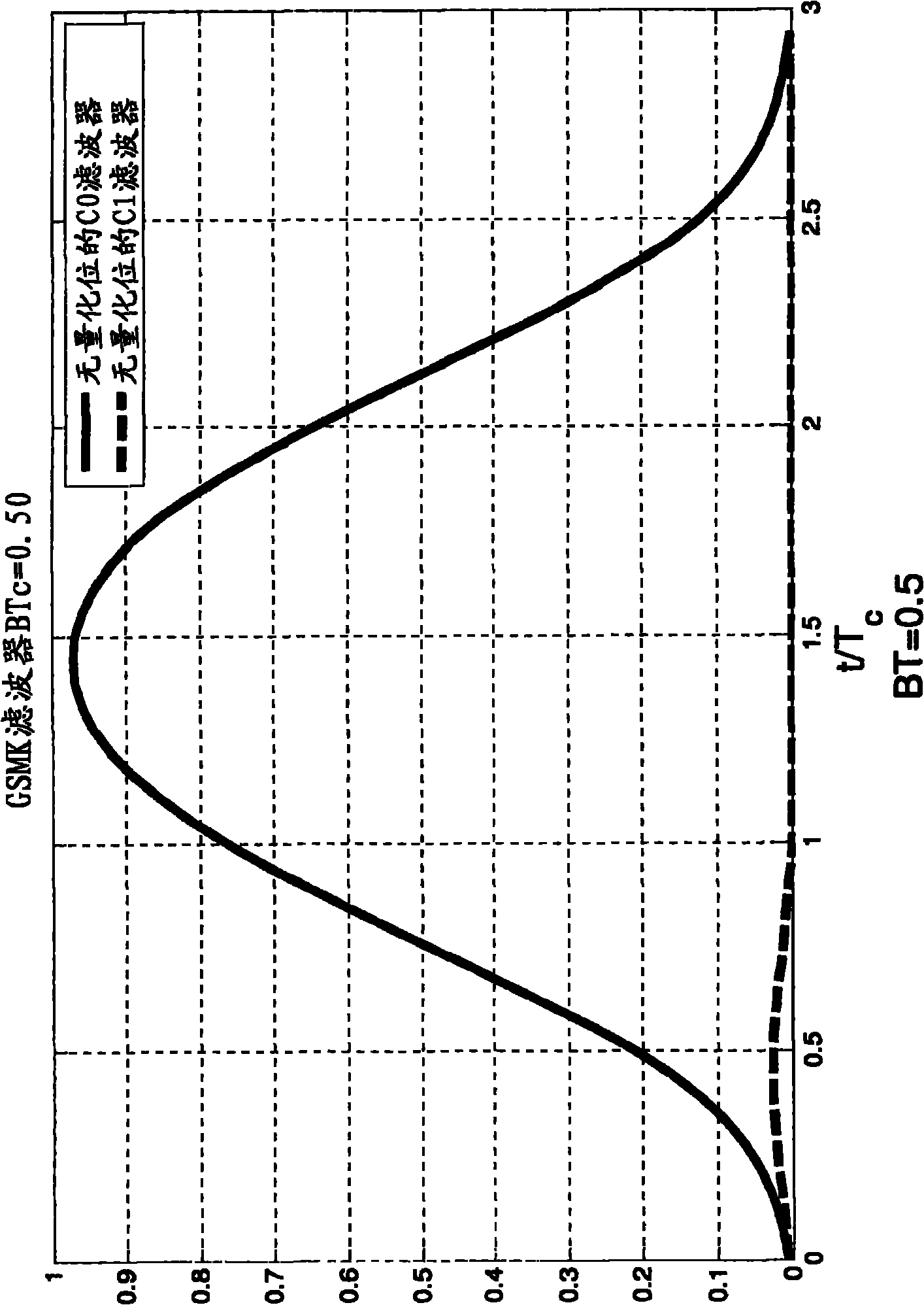

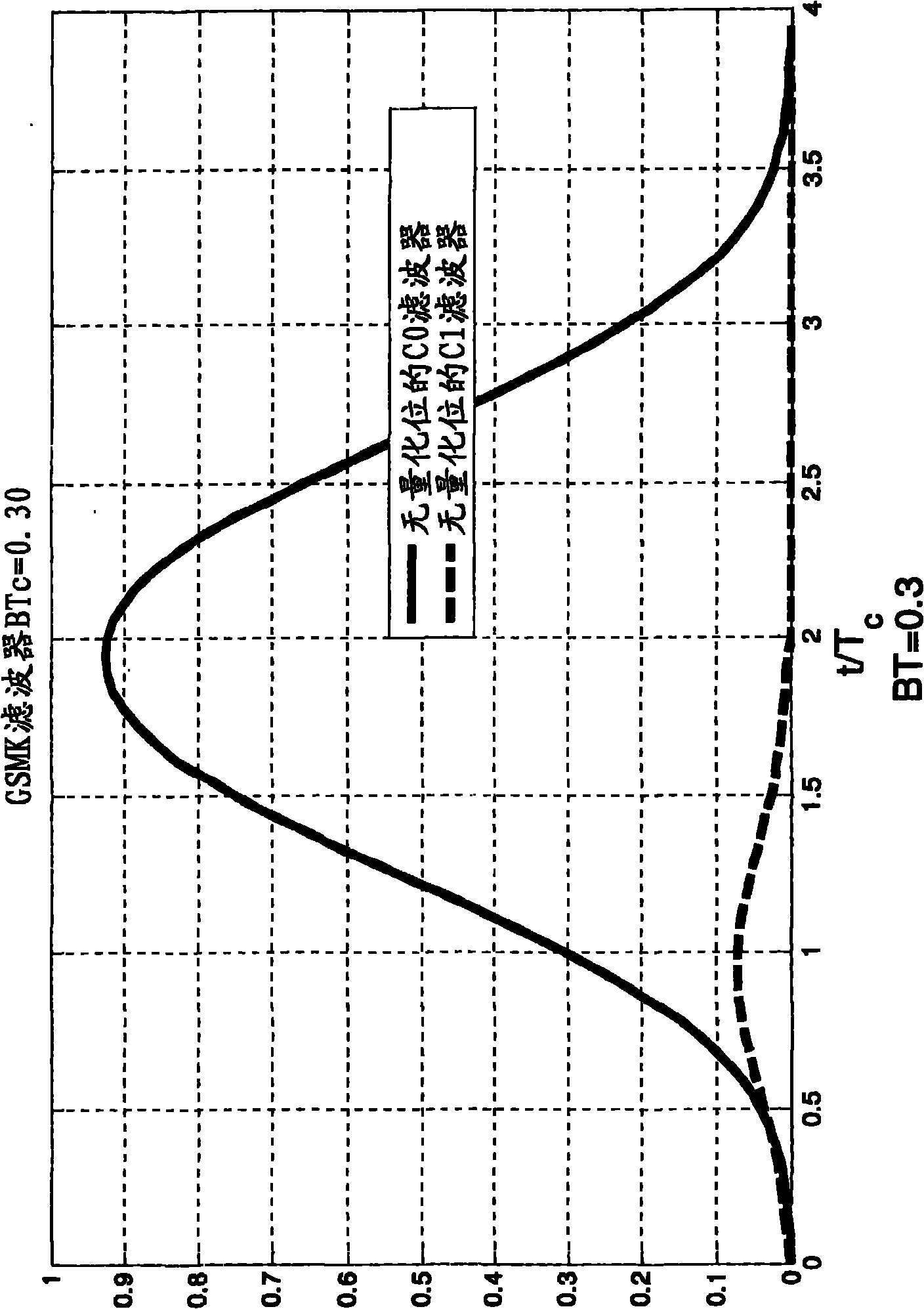

The invention relates to a method for realizing a GMSK (Guassian Minimum Shift Keying) signal generator based on an FPGA (Field Programmable Gate Array), which comprises the following steps: integrating an NRZ (Non-Return-to-Zero) coding module, a Gaussian filter module, a phase accumulation module, an orthogonal modulation module and a D / A (Digital to Analog) conversion module on an FPGA chip, filtering through NRZ coding and filtering mode selecting, accumulating a filtered signal into a phase value, carrying out two paths of ROM (Read Only Memory) table look-up on the phase value, multiplying a cosine value of one of the two paths by a coswt signal, multiplying a sine value of the other path by a sinwt signal and taking a difference between products of the two paths of signals as a generated GMSK modulation signal. The method has the beneficial effects that the signal modulated by the GMSK signal generator, which is realized by adopting the method, can select a filter with different filtering modes through flexibly controlling the switching of the filtering modes according to the filtering requirements of a system to realize the generation of a GMSK signal with different system bandwidth demands; and moreover, the method has the characteristics of high realization speed and less resources occupied, thereby satisfying the demand that the digital information processing system realizes the full digitalization of the GMSK signal generator.

Owner:TOEC TECH

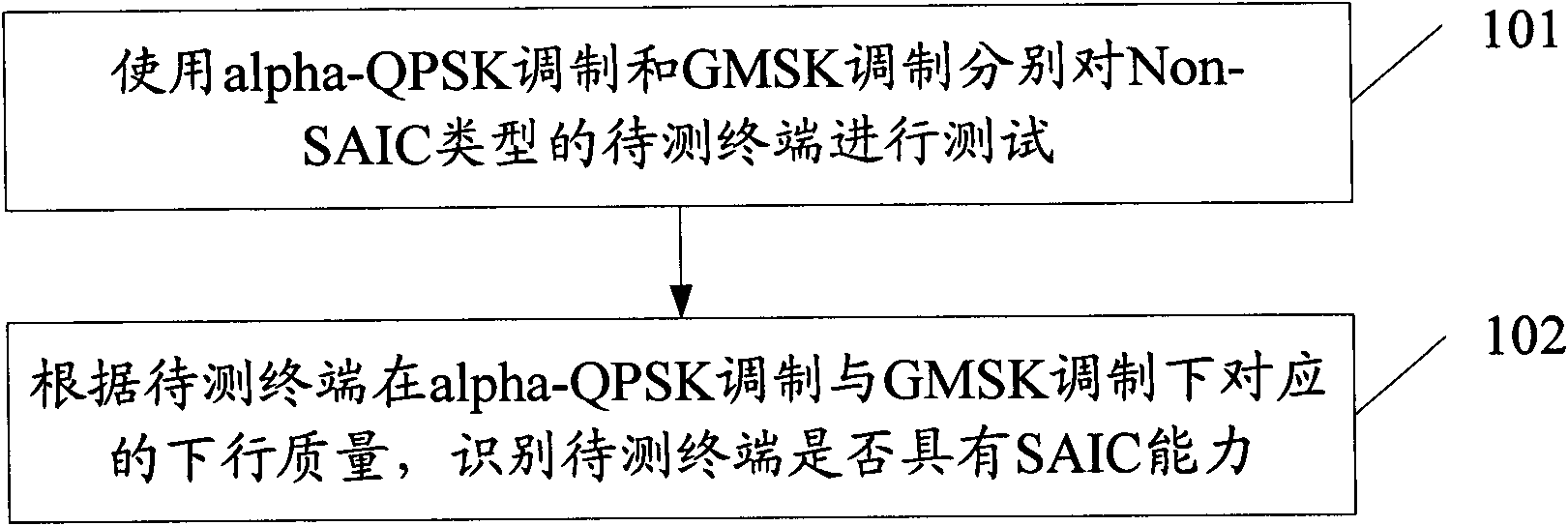

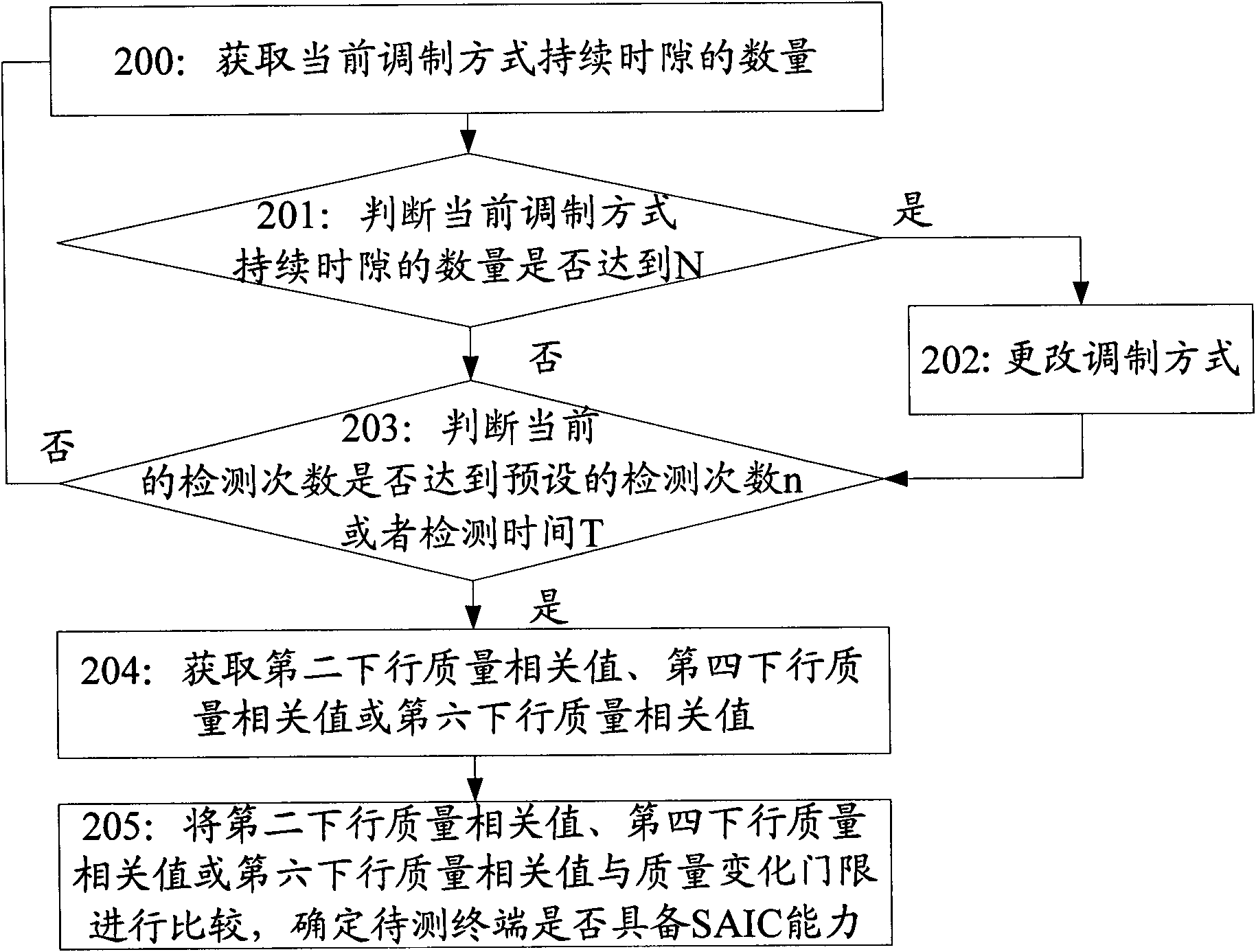

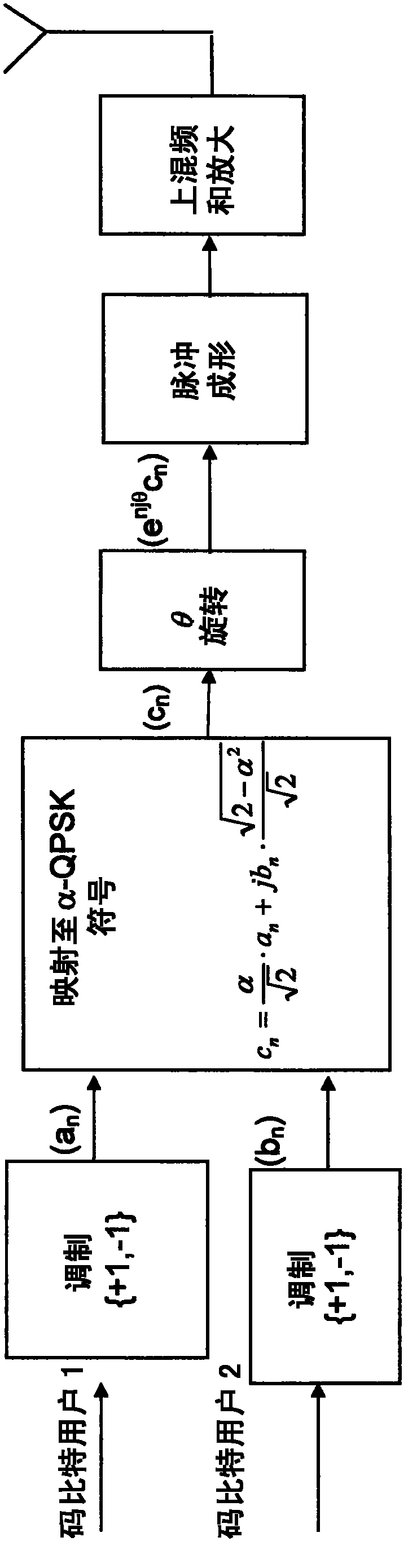

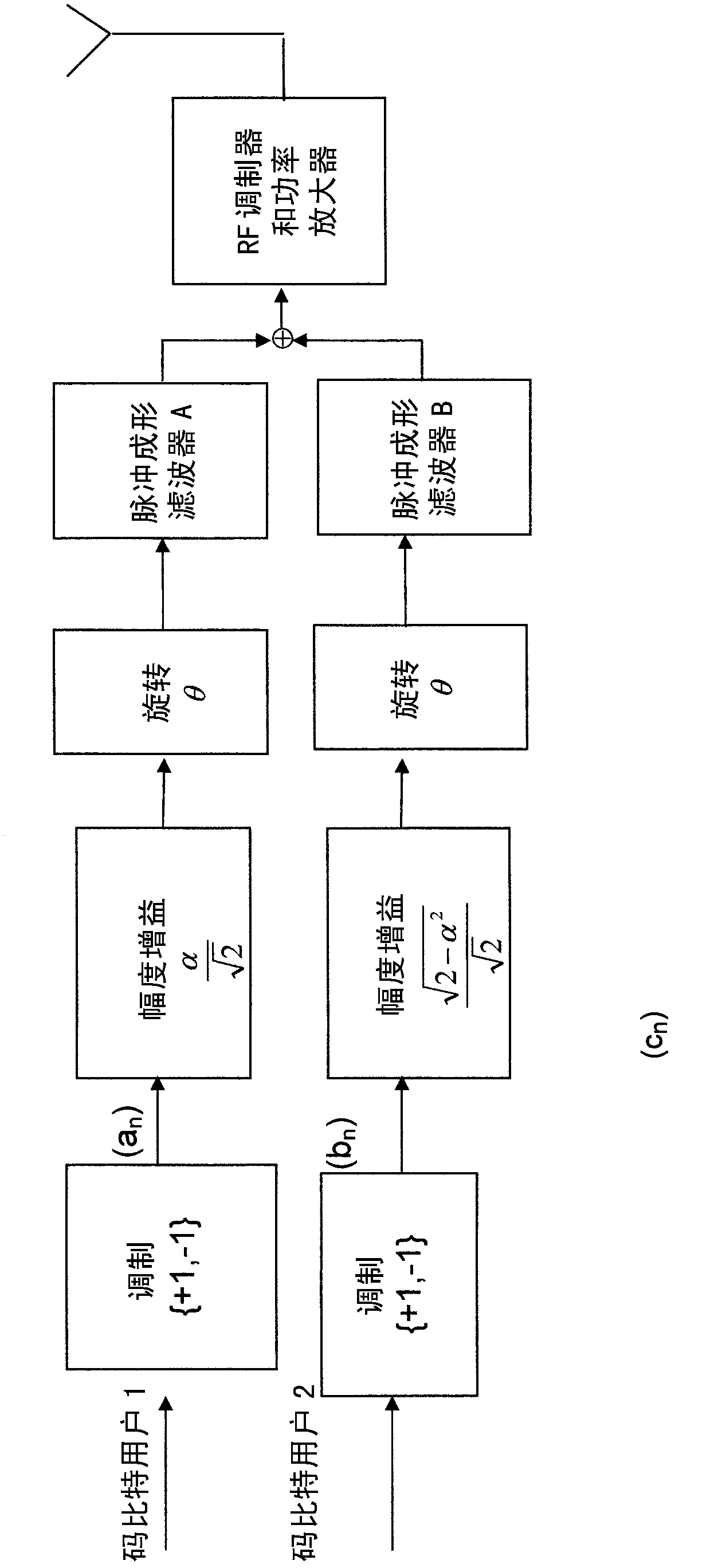

Single antenna interference cancellation (SAIC) capability recognizing method and device

ActiveCN101938437AImprove accuracyModulated-carrier systemsTransmission monitoringTelecommunicationsComputer module

The invention discloses single antenna interference cancellation (SAIC) capability recognizing method and device which belong to the field of wireless communication. The method comprises the following steps of: respectively testing Non-SAIC type terminals to be tested by using alpha-QPSK (Quadrature Phase Shift Keying) modulation and GMSK (Guassian Minimum Shift Keying) modulation; recognizing whether the terminals to be tested have SAIC capability or not according to the corresponding downlink quality of the terminals to be tested under the alpha-QPSK modulation and GMSK modulation; reporting the corresponding downlink quality information to an SAIC capability recognizing device under the alpha-QPSK modulation and the GMSK modulation by the terminals to be tested so that the SAIC capability recognizing device is used for obtaining the corresponding downlink quality under the alpha-QPSK modulation and the GMSK modulation according to the downlink quality information and recognizing whether the terminals to be tested have the SAIC capability or not. The device comprises a test module and a recognizing module. By the scheme, the invention can recognize a silence SAIC terminal with the SAIC capability and improve the accuracy of SAIC capability recognition.

Owner:HUAWEI TECH CO LTD

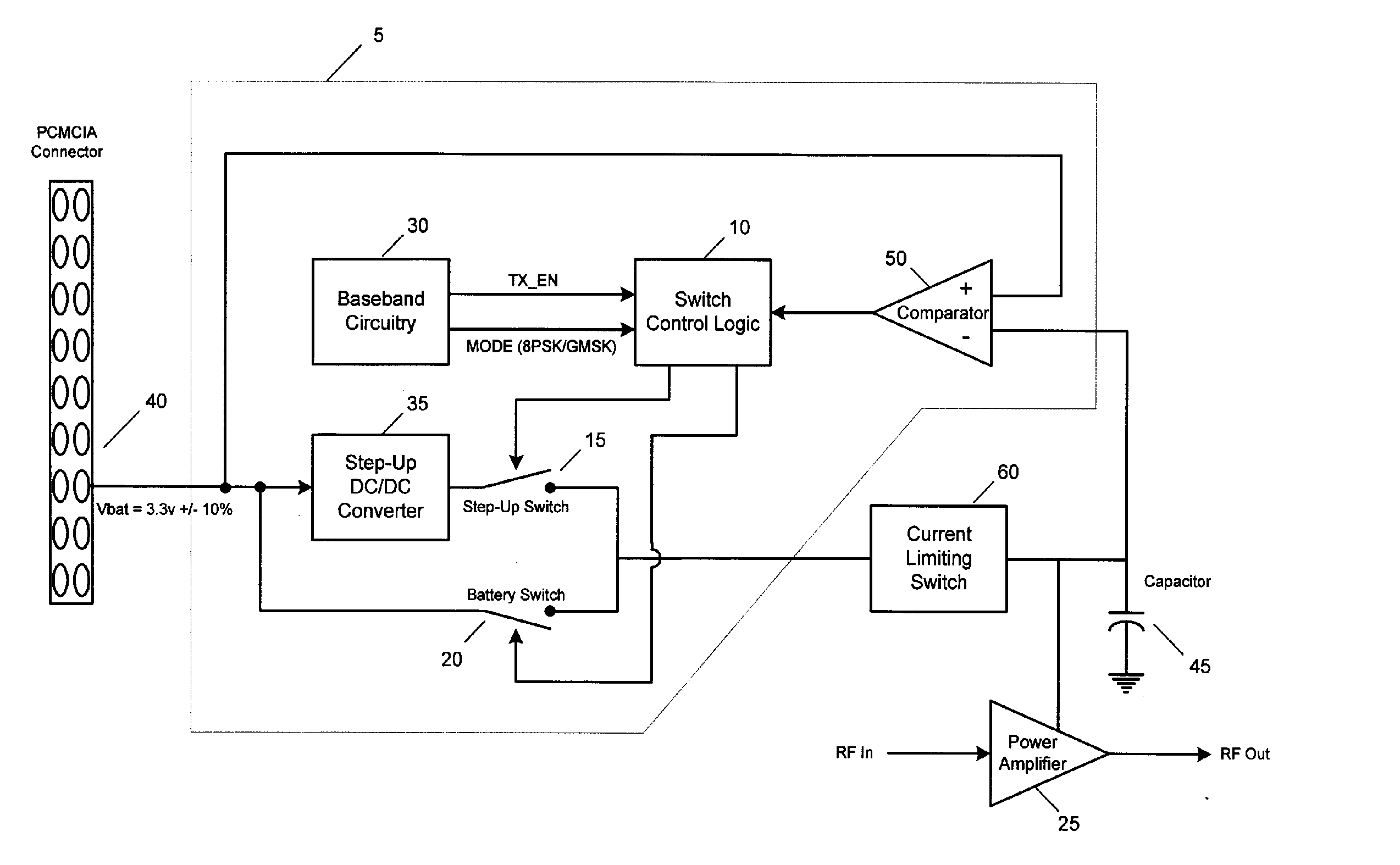

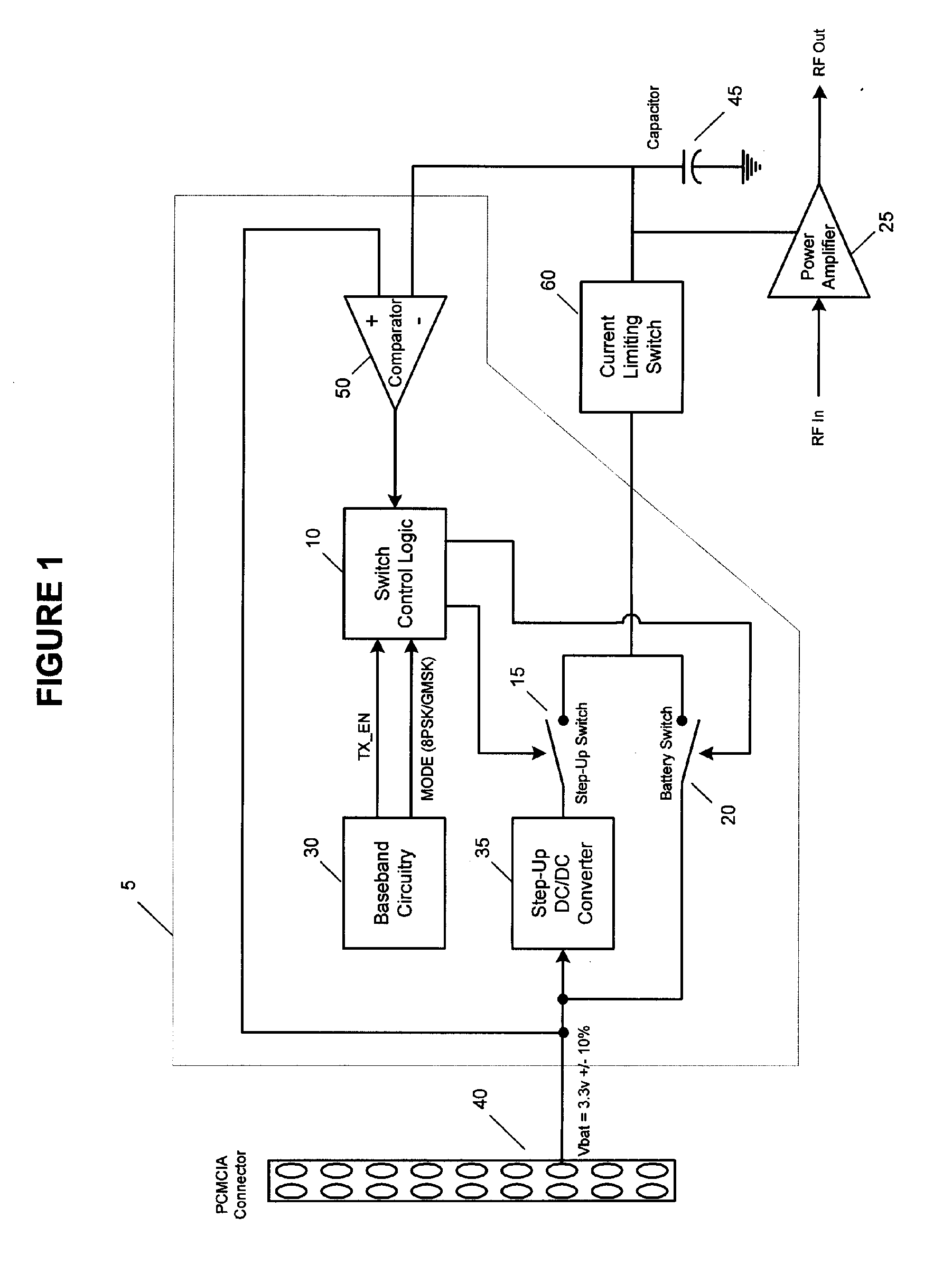

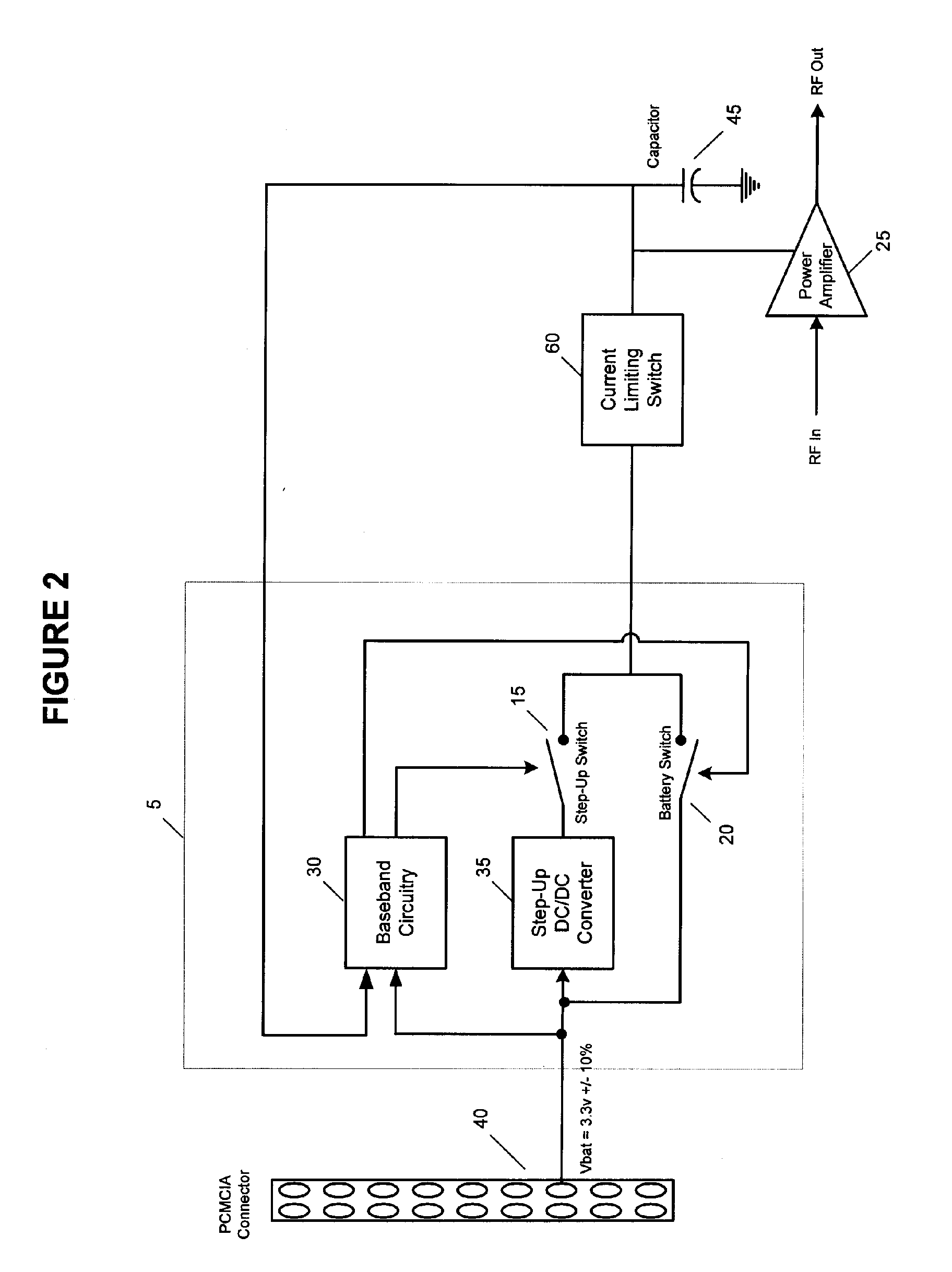

Intelligent RF power control for wireless modem devices

InactiveUS20070030712A1Avoid performance degradationResonant long antennasPower amplifiersAudio power amplifierModem device

A bypass circuit is disclosed for use with lower power supply voltage PC cards. The bypass circuit controls the power supply voltage fed to a power amplifier when switching between a lower power 8-PSK modulation mode and a higher power GMSK modulation mode. A step-up DC / DC converter provides a higher voltage to the power amplifier than can be supplied by an original power supply. Switch control logic controls a step-up switch and a battery switch. The step-up switch is turned on when operating in an 8-PSK modulation mode to provide a higher voltage to the power amplifier than the original power supply voltage. The battery switch is turned on when operating in the GMSK modulation mode to provide the original power supply voltage to the power amplifier.

Owner:SONY ERICSSON MOBILE COMM AB

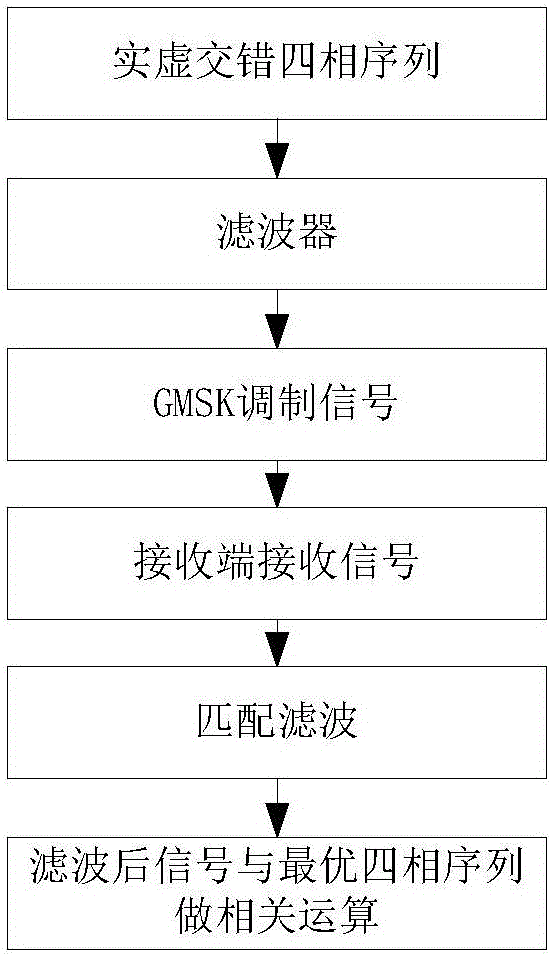

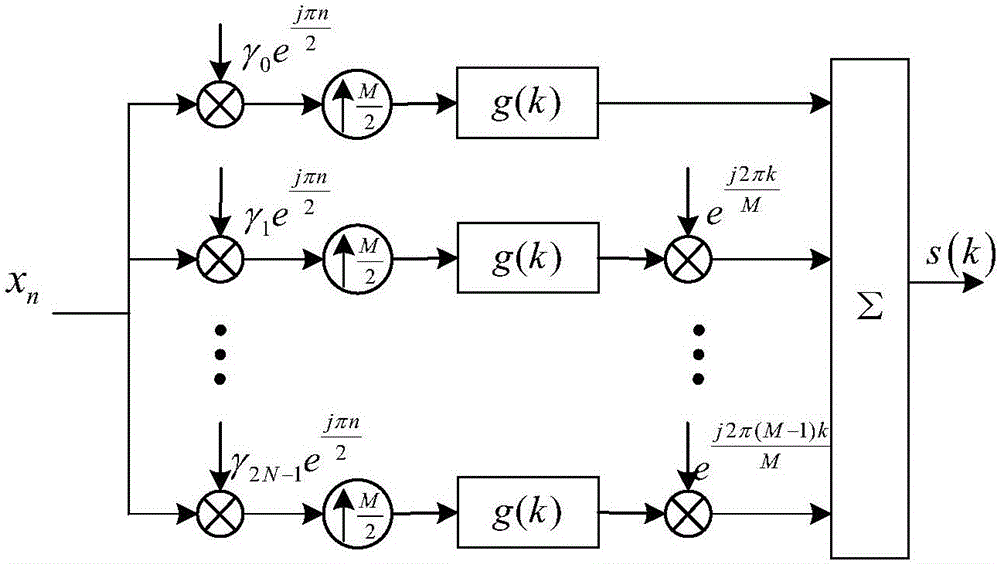

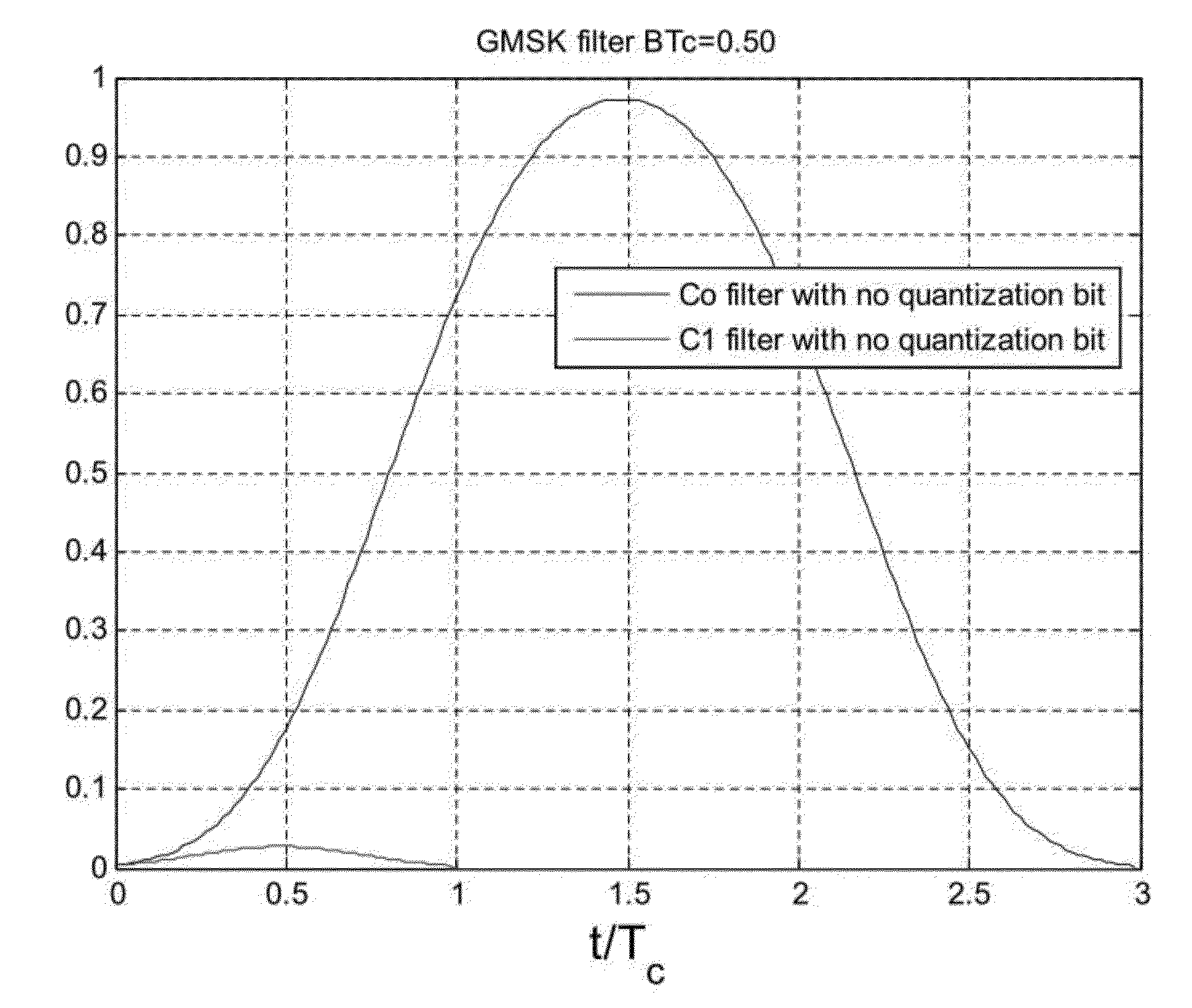

Establishment method for real virtual staggered quadriphase sequence, MSK/GMSK (Gaussian Minimum Shift Keying) synchronization method and spectrum spread system

ActiveCN106452501AExcellent autocorrelation propertyGood synchronizationChannel estimationMulti-frequency code systemsComputer scienceSpread spectrum

The invention discloses an establishment method for a real virtual staggered quadriphase sequence and a sequence set, an MSK / GMSK (Gaussian Minimum Shift Keying) synchronization method and an FBMC (Filter Bank Multicarrier)-OQAM spectrum spread system. The real virtual staggered quadriphase sequence and sequence set are established according to a binary sequence with high autocorrelation. The real virtual staggered quadriphase sequence can be generated by any binary sequence. The cycle of the generated real virtual staggered quadriphase sequence is two times of that of the original binary sequence. The maximum nontrivial autocorrelation function value of the generated real virtual staggered quadriphase sequence is two times of that of the original binary sequence. According to the real virtual staggered quadriphase sequence and sequence set obtained through adoption of above-mentioned establishment method, synchronization of a MSK / GMSK signal is realized; the optimum quadriphase sequence is applied to MSK / GMSK modulation, thereby obtaining the MSK / GMSK signal with an excellent autocorrelation characteristic; and the optimum quadriphase sequence can be applied to synchronization and channel estimation. The established real virtual staggered quadriphase sequence and sequence set also can be used as spectrum spread codes for spreading spectrum, a purpose of reducing a peak-to-average power ratio of an FBMC signal is achieved, a signal transmission rate is improved, and an FBMC-OQAM signal with the excellent autocorrelation characteristic is obtained.

Owner:HUAZHONG UNIV OF SCI & TECH

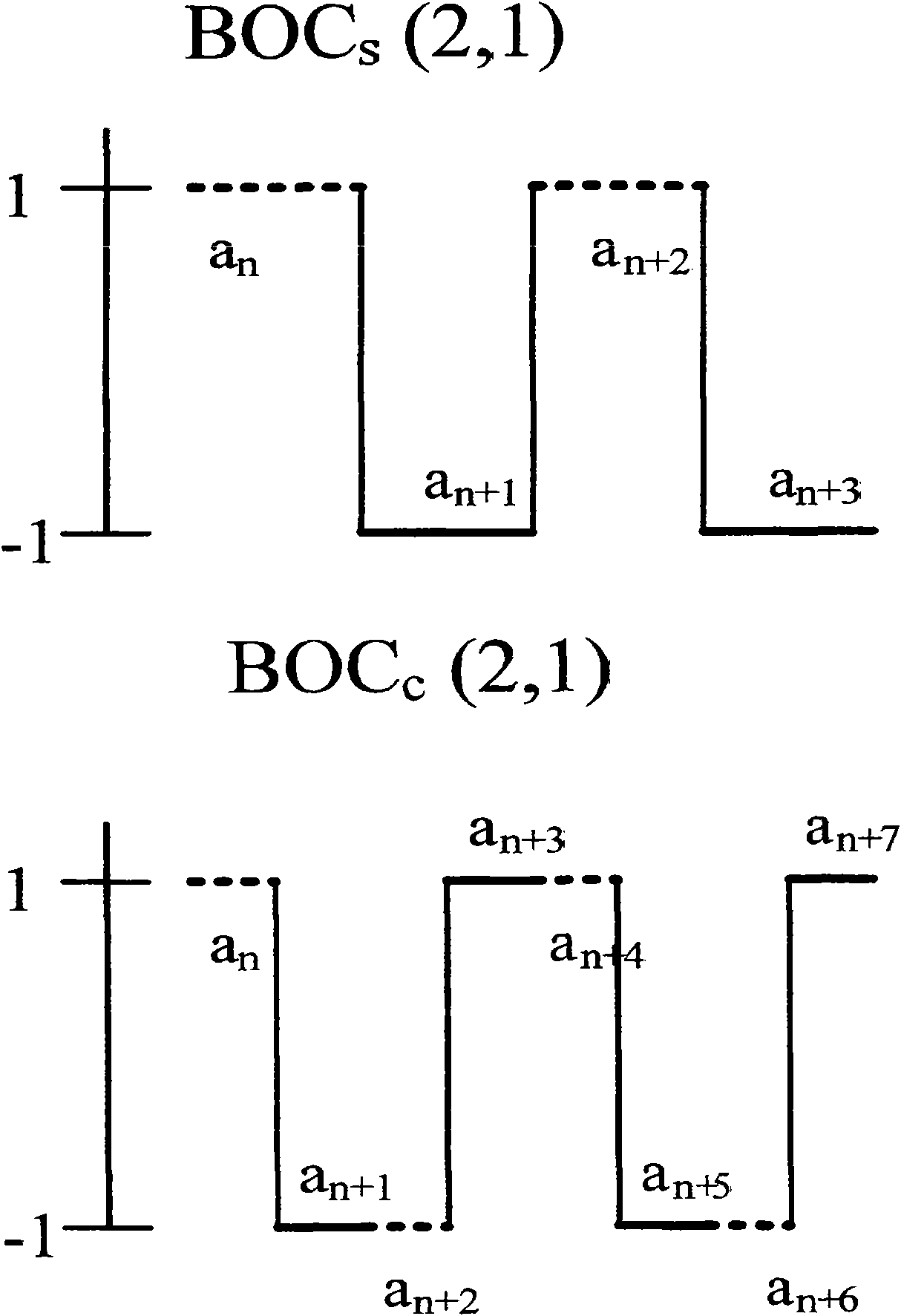

Spread Spectrum GMSK Signals

ActiveUS20160072546A1Reduce pruningEnhanced signalCode division multiplexFrequency-modulated carrier systemsTelecommunicationsTransmission channel

A method for generating a spread spectrum Gaussian Minimum Shift Keying (GMSK) signal includes obtaining a sequence of data symbols for a data channel, obtaining at least one first spread spectrum code comprising a first sequence of spread spectrum chips for the data channel, obtaining at least one second spread spectrum code comprising a second sequence of spread spectrum chips for a pilot channel, and generating a sequence of pre-modulation chips by combining the sequence of data symbols for the data channel with the spread spectrum chips of the first sequence of the at least one first spread spectrum code and data symbols for the pilot channel with the spread spectrum chips of the second sequence of the at least one second spread spectrum code to a combined sequence of chips. The method further includes assigning the chips of the combined sequence of chips to the transmission channels In-Phase I and Quadrature Q of the spread spectrum GMSK signal so that not more than two consecutive pre-modulation chips generated with the same spread spectrum code are transmitted in the same transmission channel I or Q, and performing GMSK modulation using the sequence of pre-modulation chips to generate a spread spectrum GMSK signal.

Owner:AIRBUS DEFENCE & SPACE

Radio communication system

InactiveUS6907027B2Time-division multiplexSynchronisation signal speed/phase controlCommunications systemControl channel

The invention relates to a radio communication system in which a time slot of a frame of a multiframe signal allocated to the frequency control channel is modulated using an 8PSK modulation scheme to contain a tone having a frequency which GMSK modulation is unsuited to generate. This enables COMPACT-format signals to be distinguished from GSM-format signals and ensures backwards compatibility with all existing GSM mobile stations.

Owner:GOOGLE TECH HLDG LLC

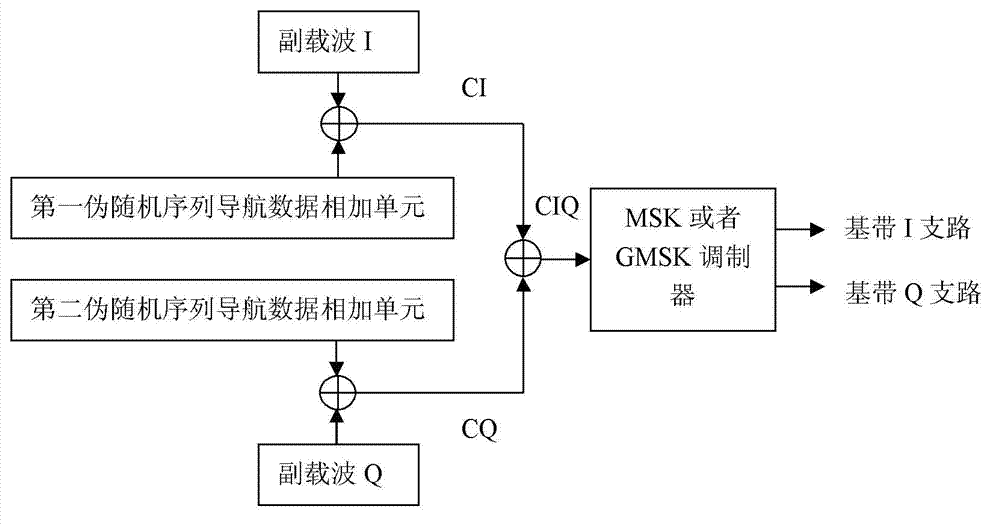

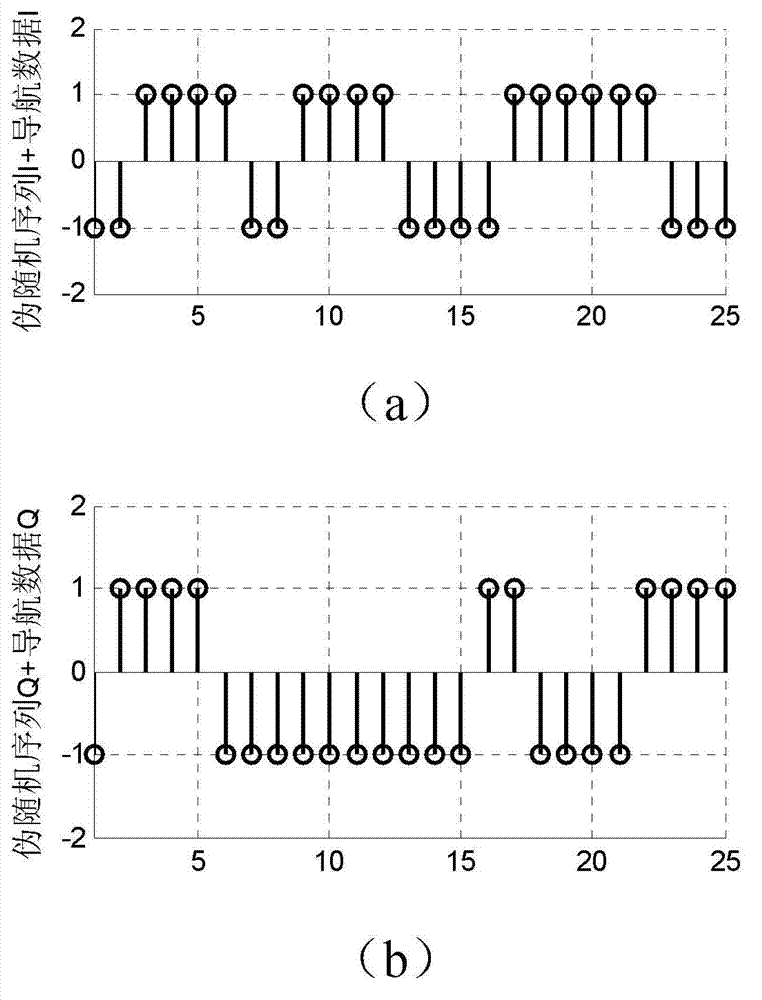

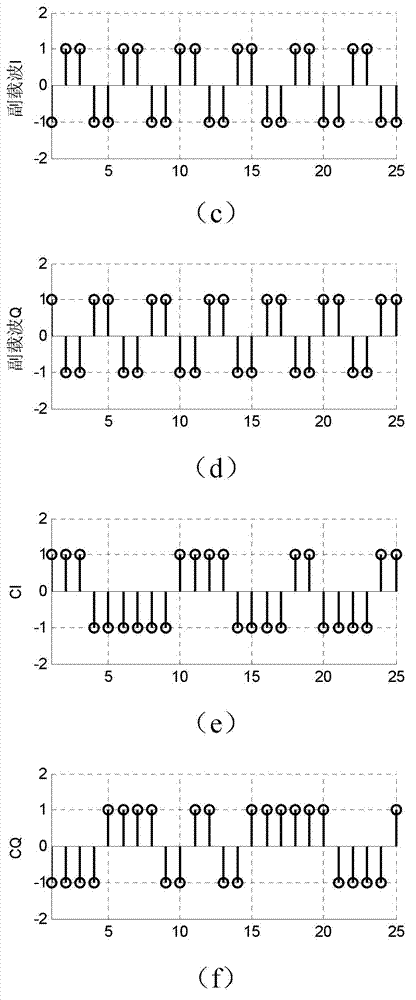

Method for generating satellite navigation signals in minimum shift keying (MSK) or Gaussian filtered minimum shift keying (GMSK) modulation mode

InactiveCN103197324ADoes not add much complexityEasy to useSatellite radio beaconingUltrasound attenuationAudio power amplifier

The invention discloses a system and a method for generating satellite navigation signals based on a minimum shift keying (MSK) or a Gaussian filtered minimum shift keying (GMSK) modulation mode. The system comprises a first pseudorandom sequence navigation data adding unit, a second pseudorandom sequence navigation data adding unit, a first subcarrier input unit, a second subcarrier input unit, a plurality of modulo two addition units and an MSK or GMSK modulator. The method comprises the steps of enabling a pseudorandom sequence I and navigation data I to form a sequence through modulo two addition and then to obtain a signal CI through the modulo two addition with a subcarrier I, enabling a pseudorandom sequence Q and navigation data Q to form a sequence through the modulo two addition and then to obtain a signal CQ through the modulo two addition with a subcarrier Q, and carrying out the modulo two addition on the signal CI and the signal CQ to obtain a signal CIQ for MSK or GMSK modulation. According to the system and the method for generating the satellite navigation signals based on the MSK or the GMSK modulation mode, the advantages that MSK or GMSK is rapid in power attenuation and constant in enveloping are remained, meanwhile a common binary phase shift keying (BPSK) mode receiver can be used for receiving, the method and the system are particularly suitable for navigation frequency ranges with limited bandwidth and facilitate utilization of a high-power amplifier by a satellite, and complexity of the receiver can not be greatly increased.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

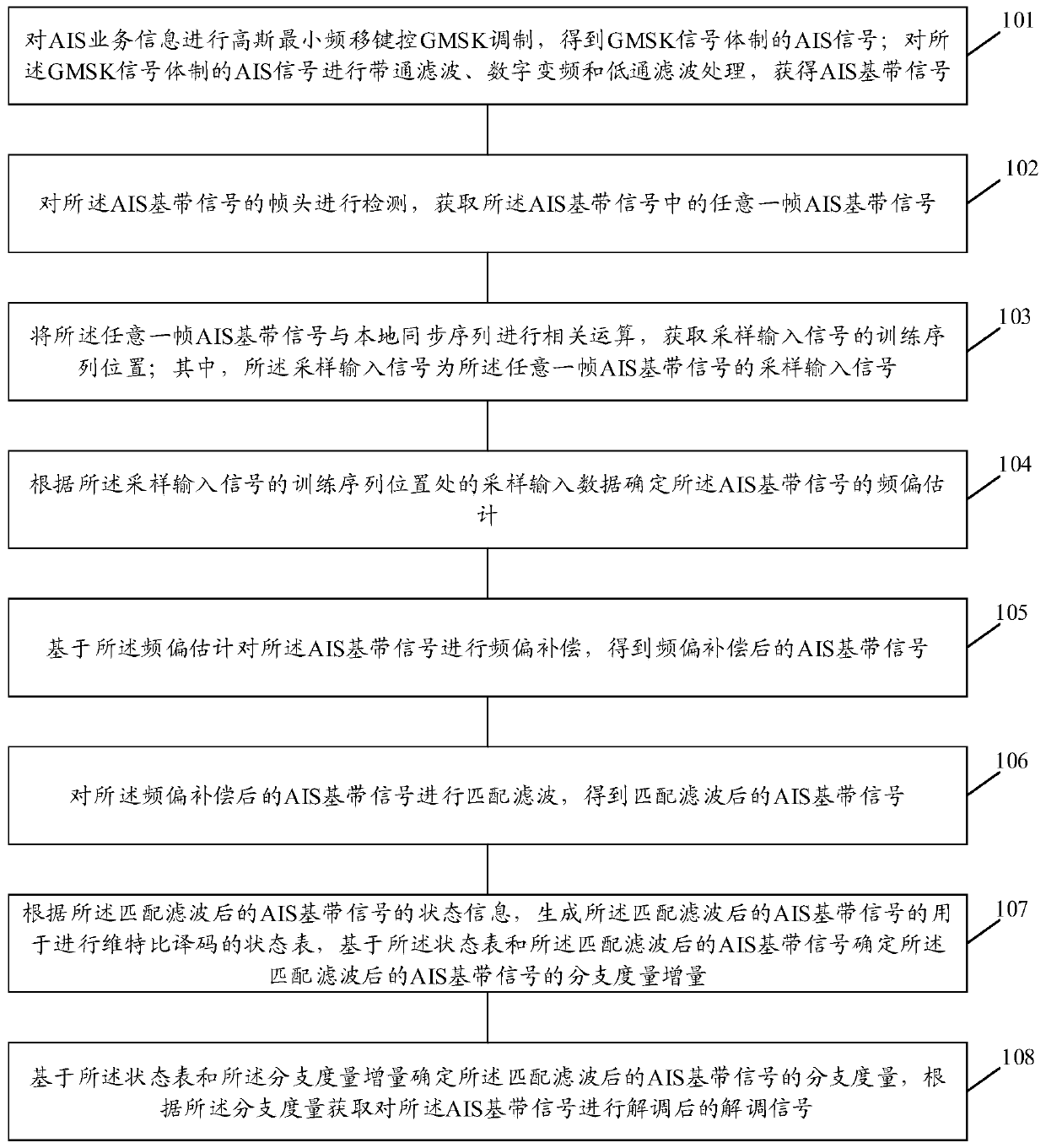

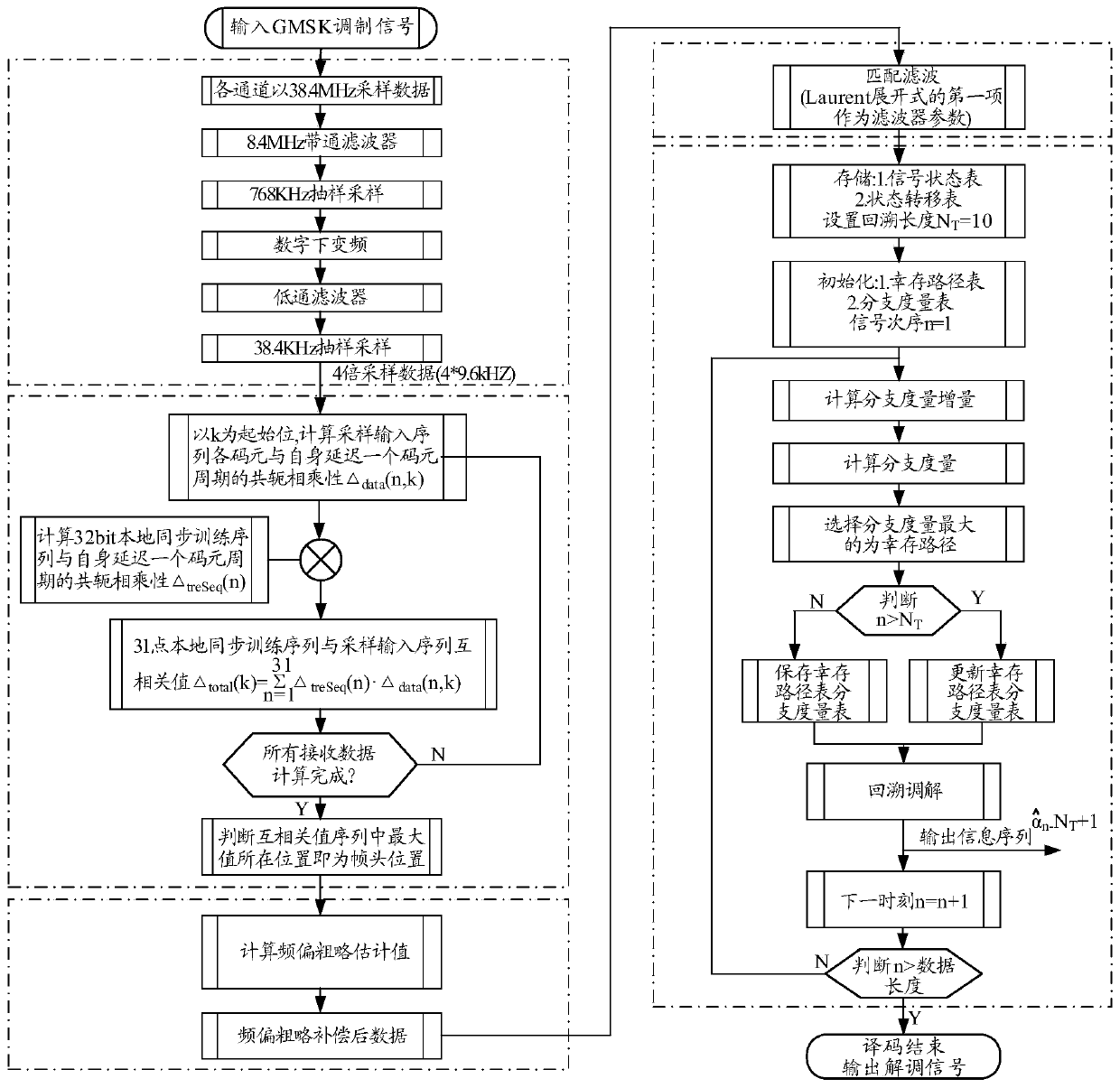

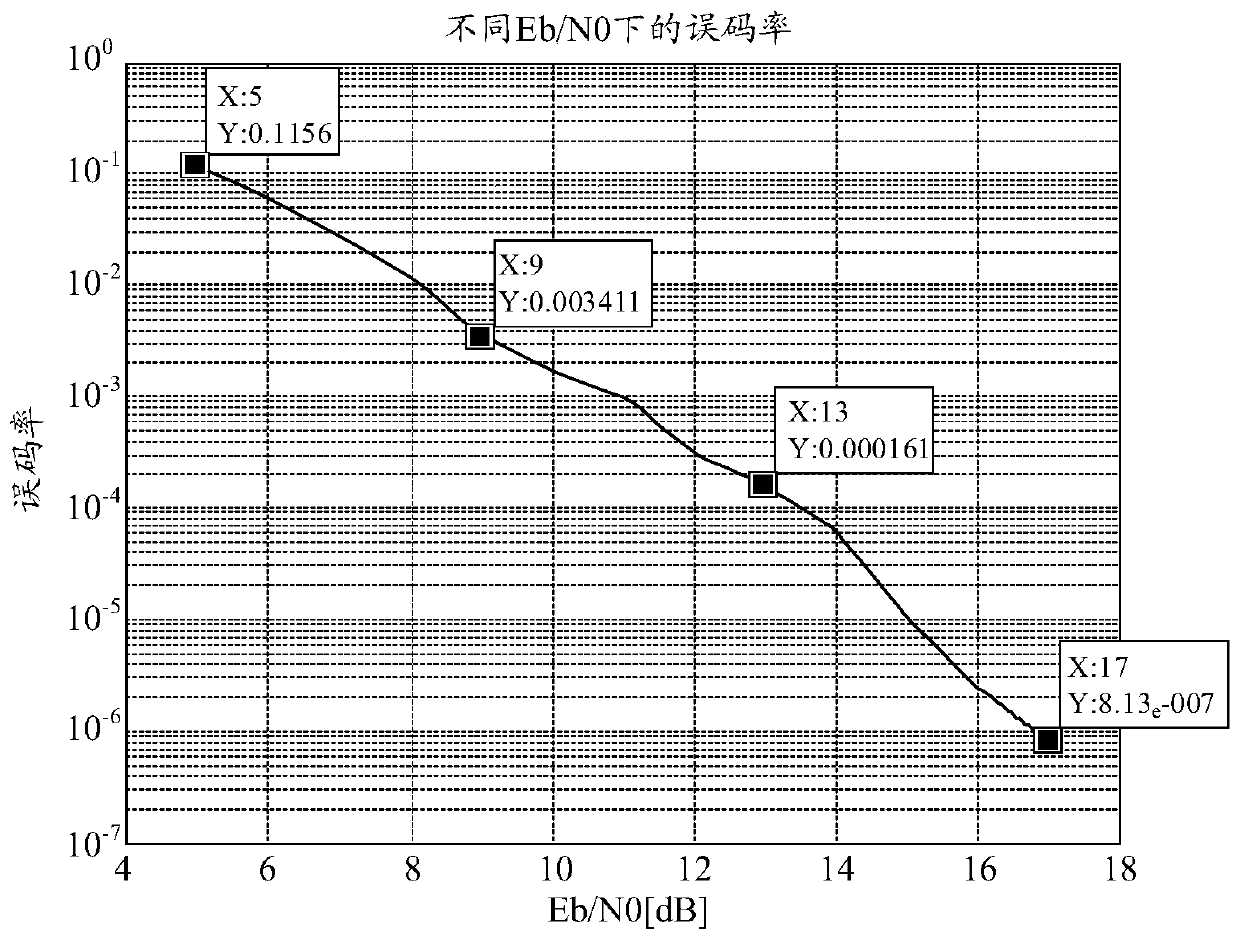

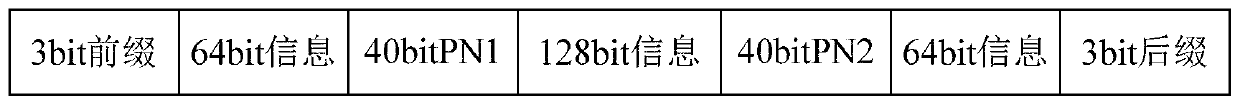

Signal demodulation method and system of satellite-borne automatic identification system (AIS)

ActiveCN110943956AImprove demodulation performanceThe implementation process is simpleMultiple carrier systemsBandpass filteringService information

The embodiment of the invention discloses a technical scheme. The method comprises the following steps: performing GMSK modulation on AIS service information; performing band-pass filtering, digital down-conversion and low-pass filtering on the modulated AIS signal to obtain an AIS baseband signal; performing the frame header detection, frequency offset estimation, frequency offset compensation, matched filtering and Viterbi decoding on an AIS baseband signal to obtain the demodulation signal of the AIS baseband signal. According to the invention, the good demodulation performance of a coherent demodulation algorithm is maintained, the problems of carrier recovery and phase blind bit estimation in coherent demodulation are avoided, and compared with the coherent demodulation algorithm, theimplementation process is simpler. The error rate and the packet error rate of the finally obtained demodulated AIS baseband signal are low, and the requirement for demodulating the AIS signal can bemet.

Owner:SPACE STAR TECH CO LTD

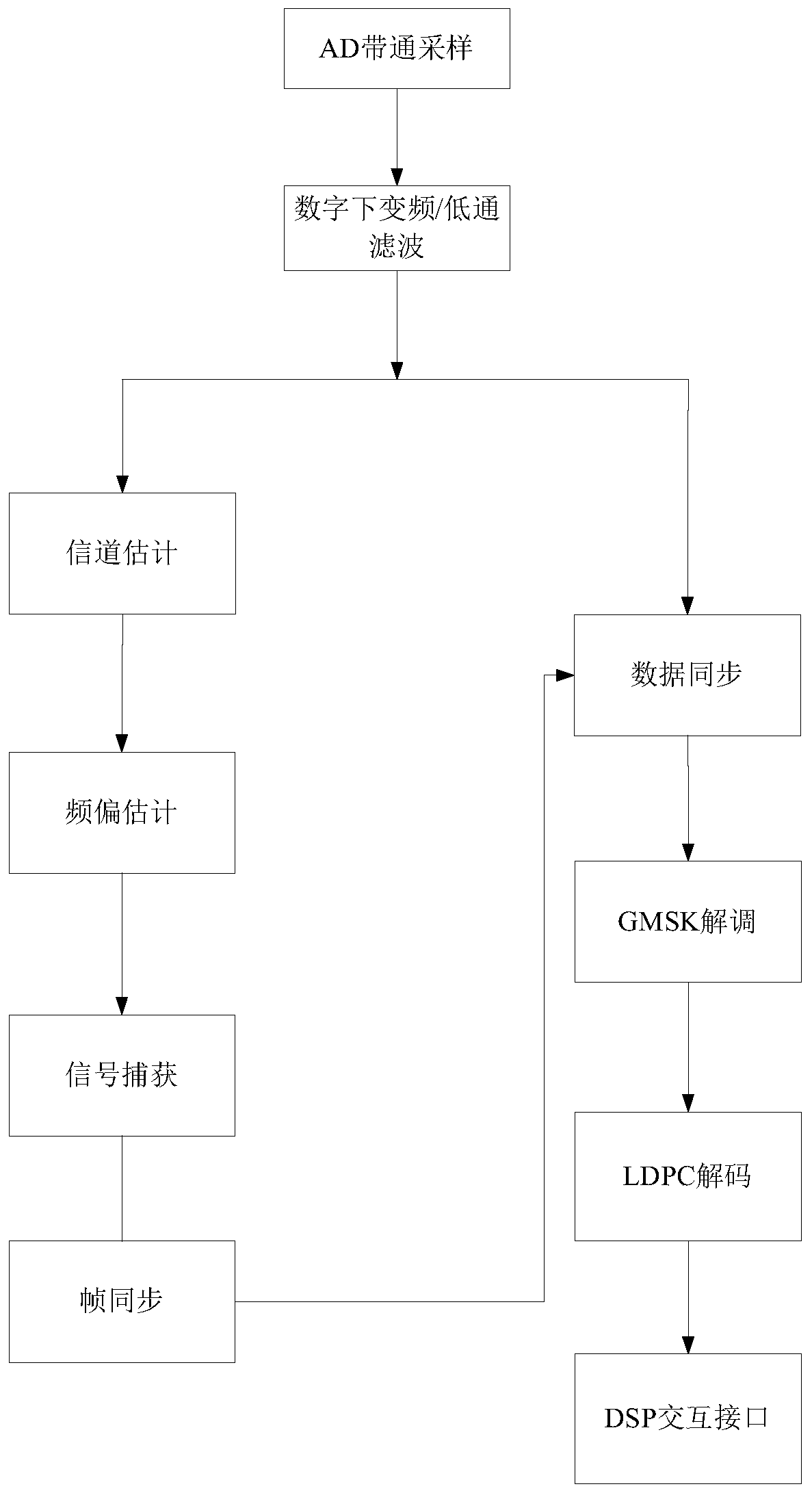

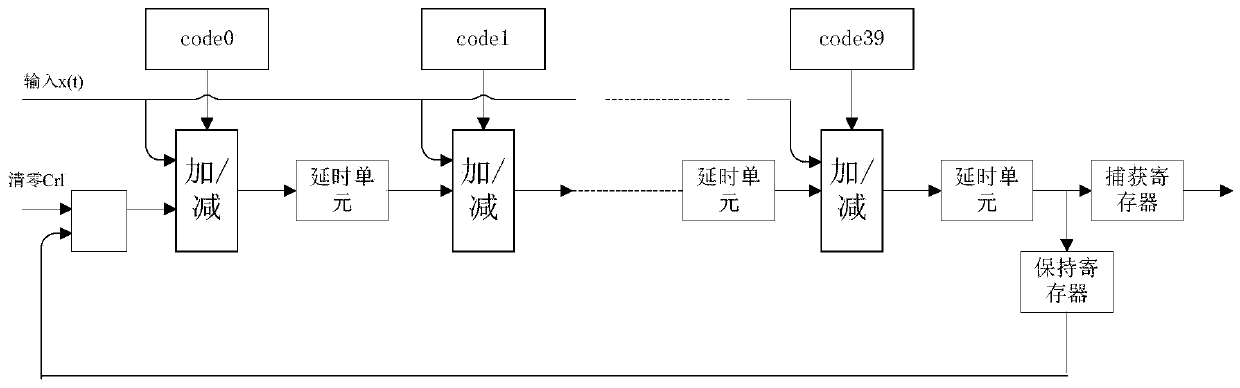

Rapid acquisition and synchronization method of wireless burst communication system

ActiveCN111371711AFully receivedReceived reliablyError preventionBaseband system detailsIntermediate frequencyMatched filter

The invention discloses a rapid capturing and synchronizing method of a wireless burst communication system, which comprises the following steps: step 1, an information sending end sends data, an information receiving end performs AD band-pass sampling and digital down-conversion processing, and a received signal is converted into a zero intermediate frequency signal; 2, channel estimation is carried out, and influence factors causing signal deformity are eliminated; step 3, frequency offset estimation: designing two groups of PNs at a fixed time interval, taking autocorrelation values generated by the two groups of PNs as two vector angles, and calculating an angle difference and a time difference to obtain frequency offset; 4, signal capture and frame synchronization, wherein signal capture and frame synchronization are completed by adopting a two-stage matched filter; and 5, carrying out GMSK demodulation and LDPC decoding to obtain information. According to the invention, a GMSK modulation and demodulation technology is adopted, and two independent PN short codes and LDPC coding are used to replace pilot frequency + frame header + check code, so that a receiver can receive datacompletely and reliably in an extremely short time.

Owner:TIANJIN JINHANG COMP TECH RES INST

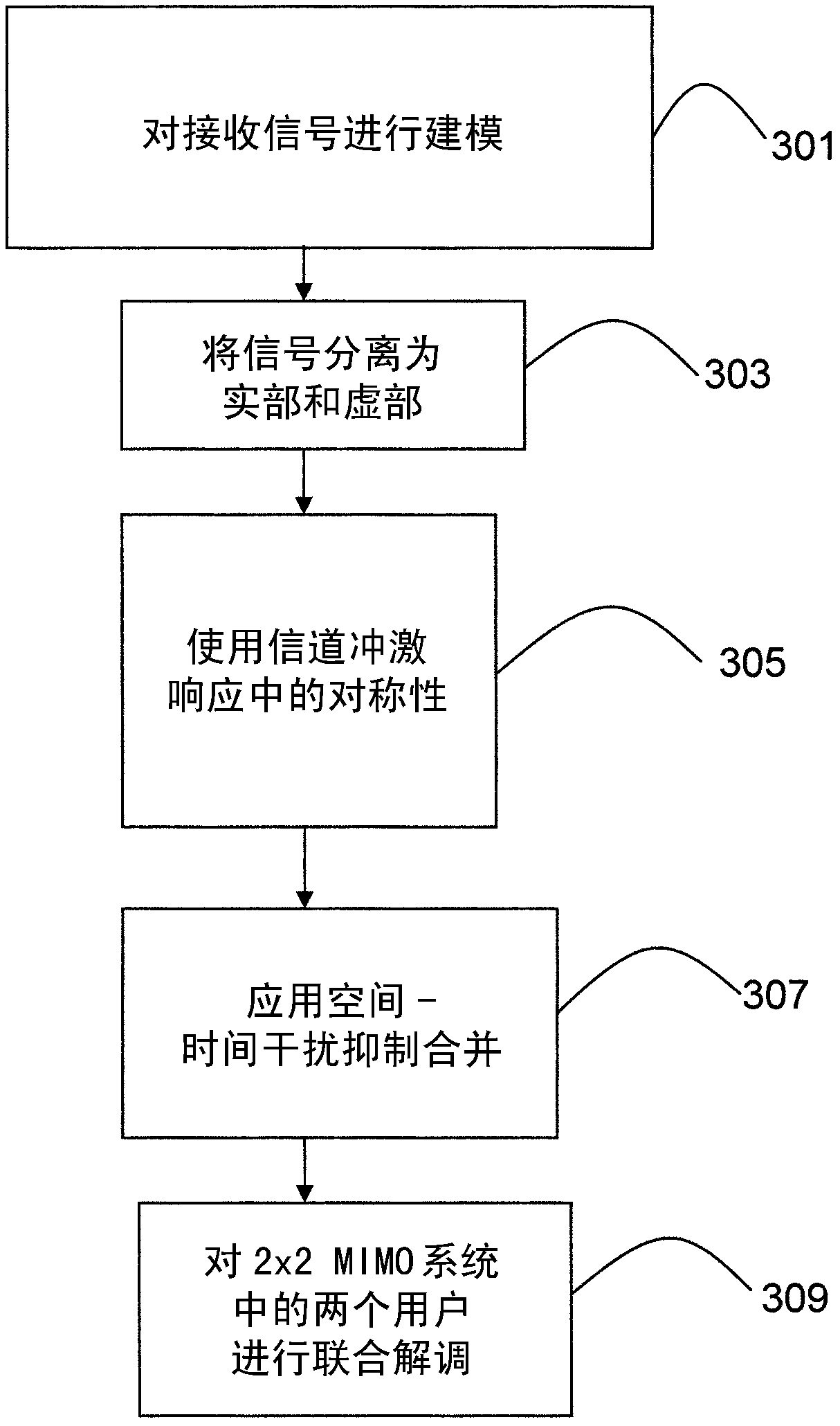

A receiver for voice services over adaptive multi-user channels on one slot

A receiver, in particular a VAMOS receiver, is provided. The receiver is adapted to split the complex-valued baseband signal into its real and imaginary parts. The two branch system thus created is modeled as a real-valued Multiple Input Multiple Output (MIMO) system. The receiver is further adapted to use correlations of the noise, both in time and between branches of a channel to suppress the noise for multi-users in the same channel. In accordance with one embodiment the receiver is adapted to take into account the known symmetries present in a symbol constellation when more than one user exists in the same channel. This is for example the case in adaptive symbol constellation such as an adaptive alpha - QPSK constellation. Using the receiver in accordance with the above can provide the same performance as a joint detection receiver in the presence of Gaussian white noise, while giving better interference suppression than either SAIC or joint detection in the presence of GMSK modulated interference.

Owner:TELEFON AB LM ERICSSON (PUBL)