Patents

Literature

205results about How to "High speed access" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Vertical Services Integration Enabled Content Distribution Mechanism

InactiveUS20070124488A1Increased cost-effectivenessHigh bandwidthMultiple digital computer combinationsData switching networksContent distributionNetwork link

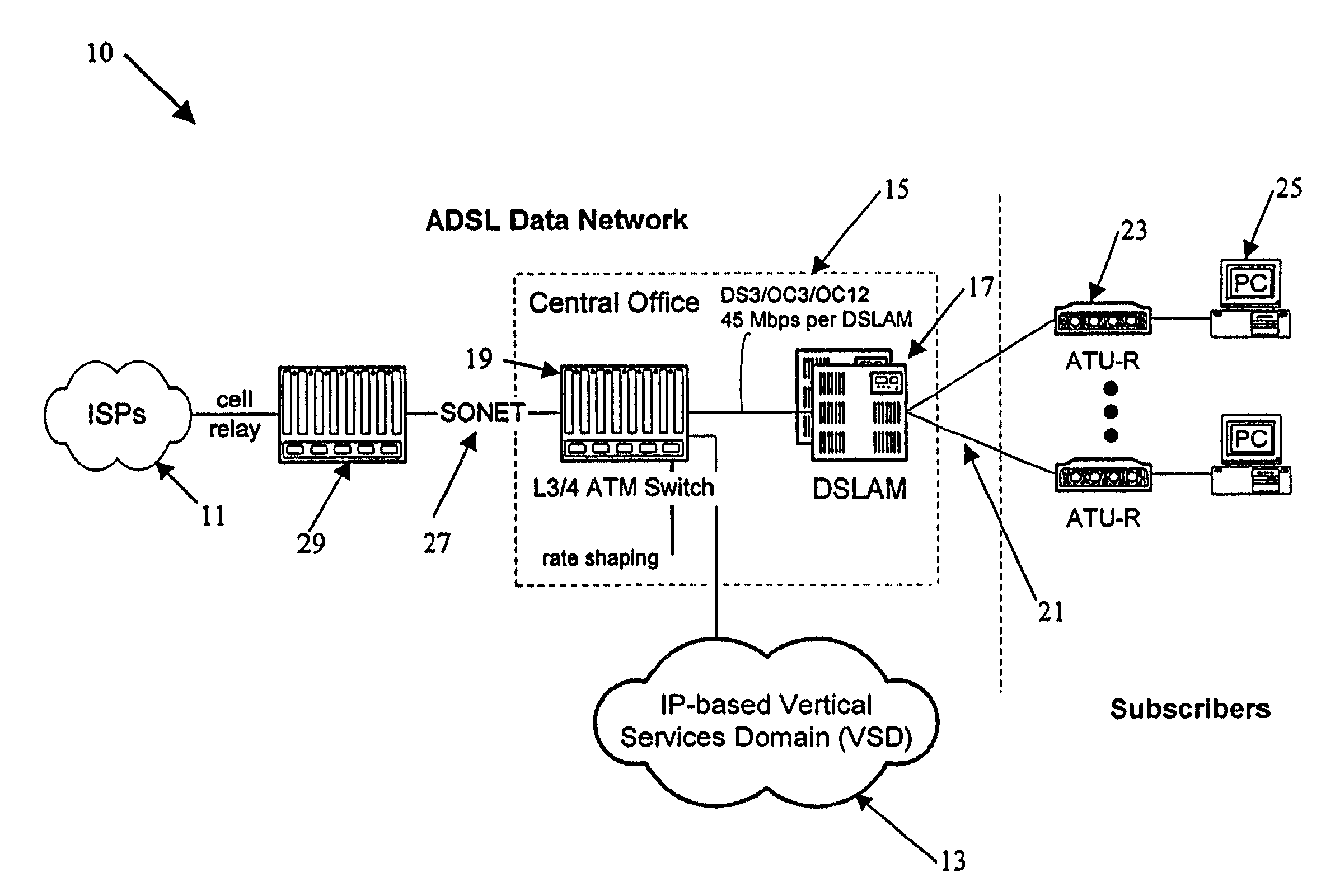

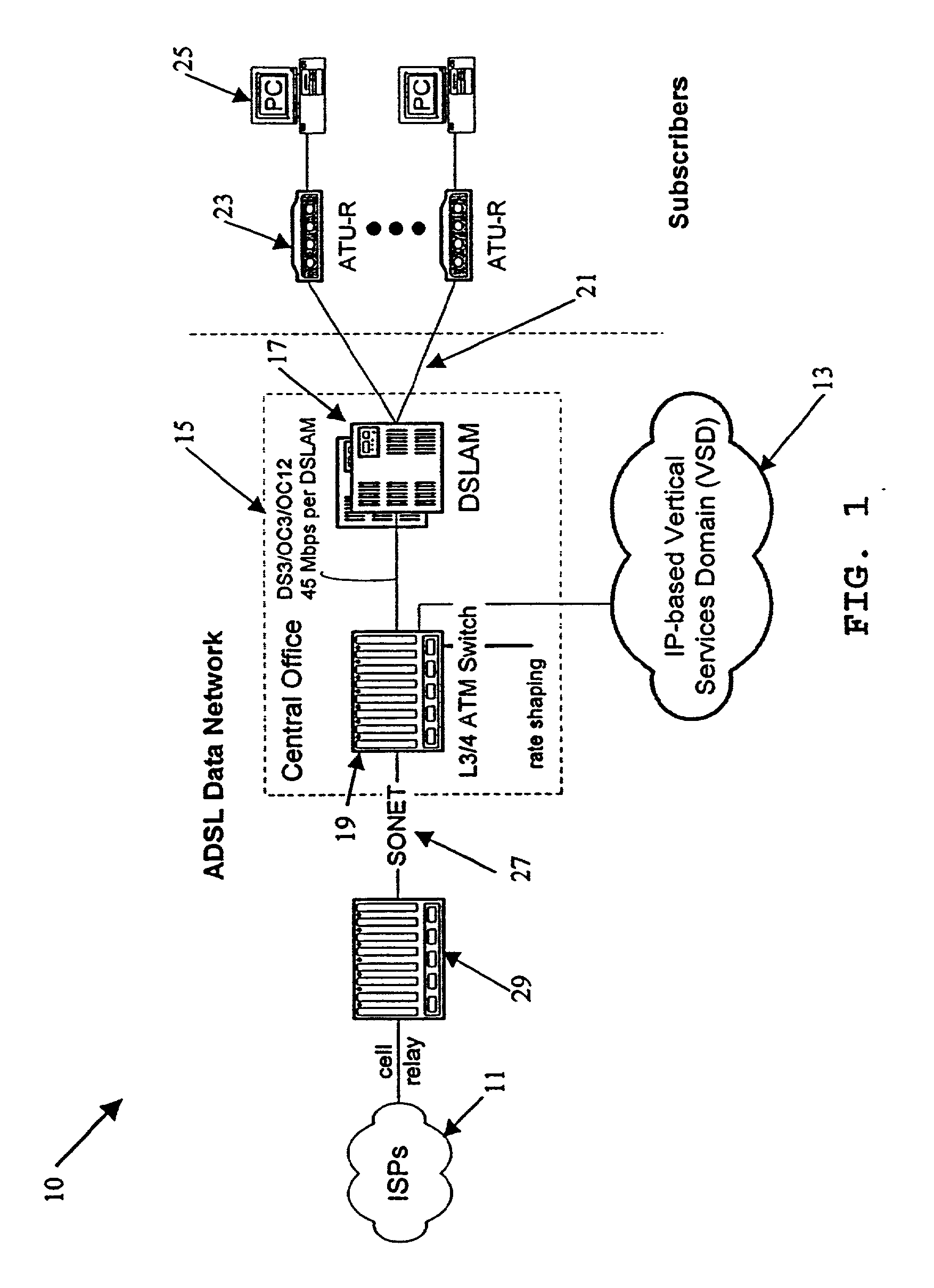

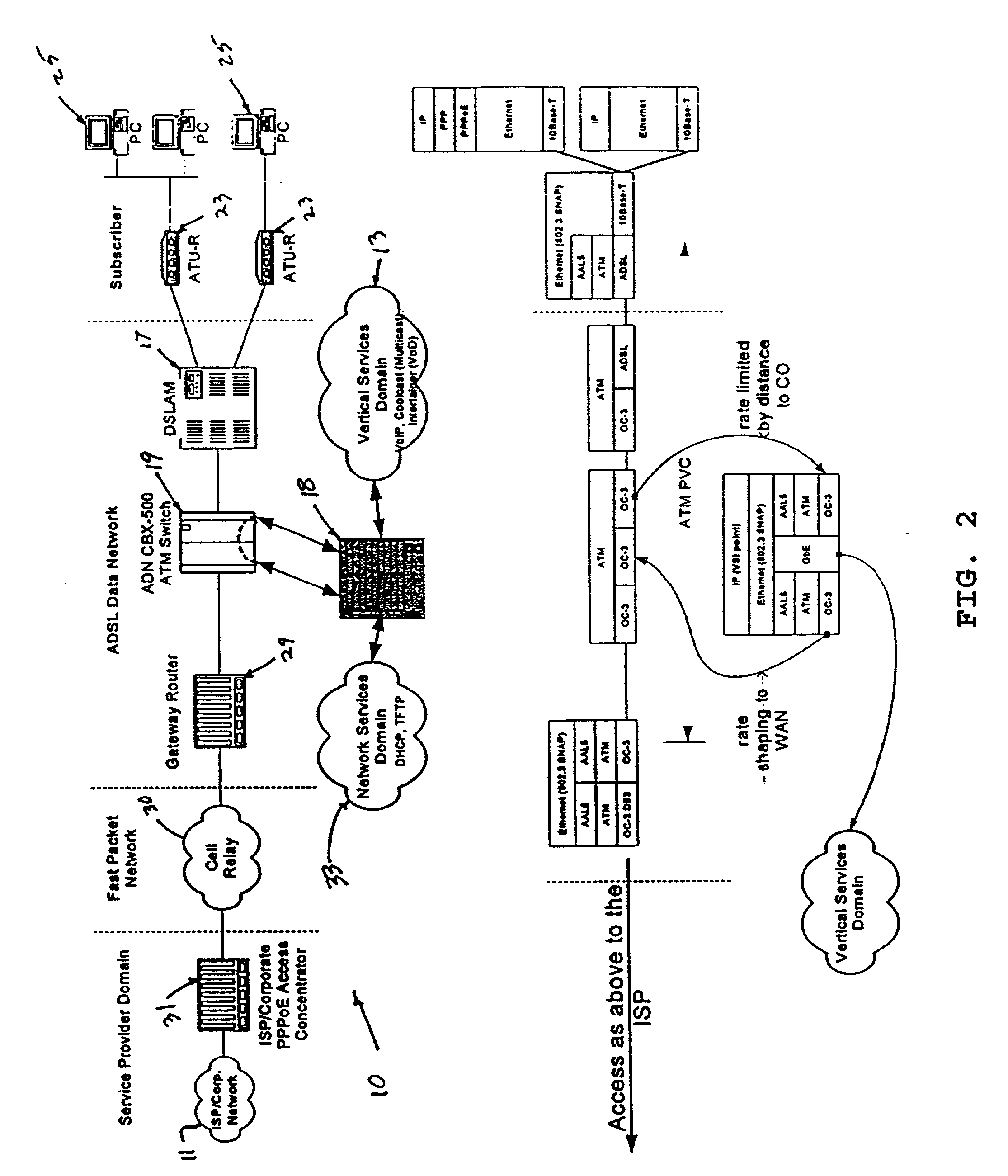

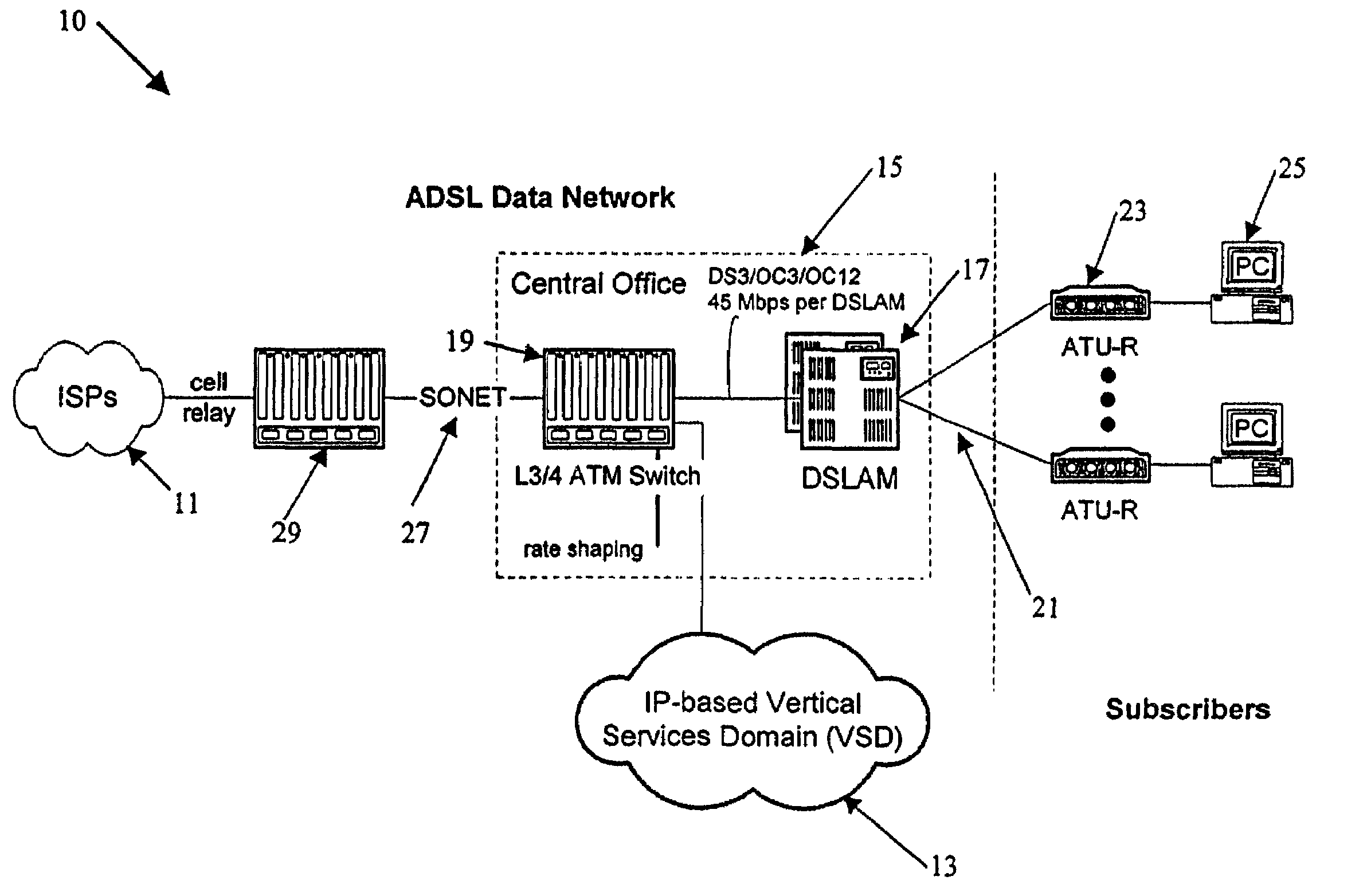

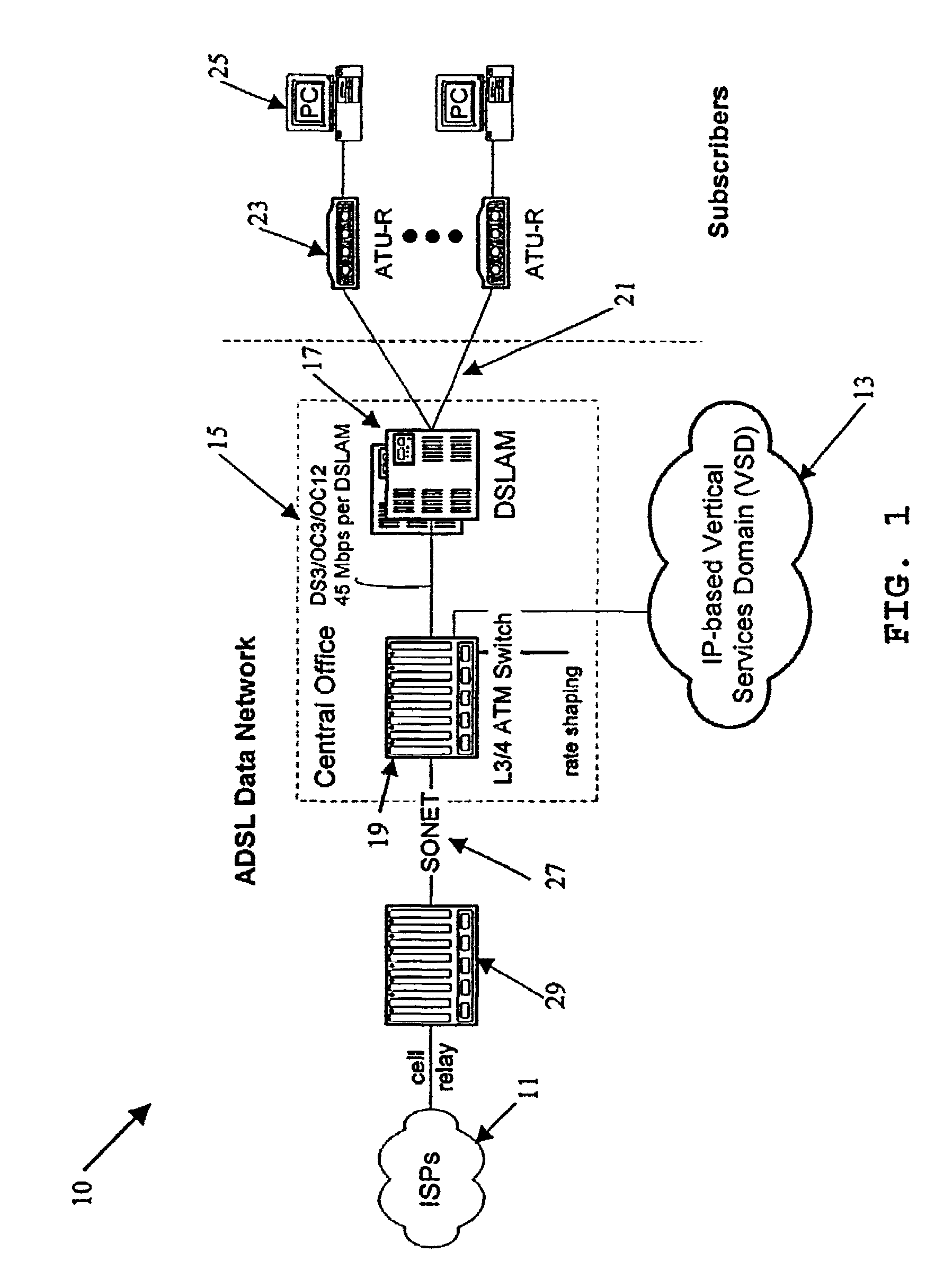

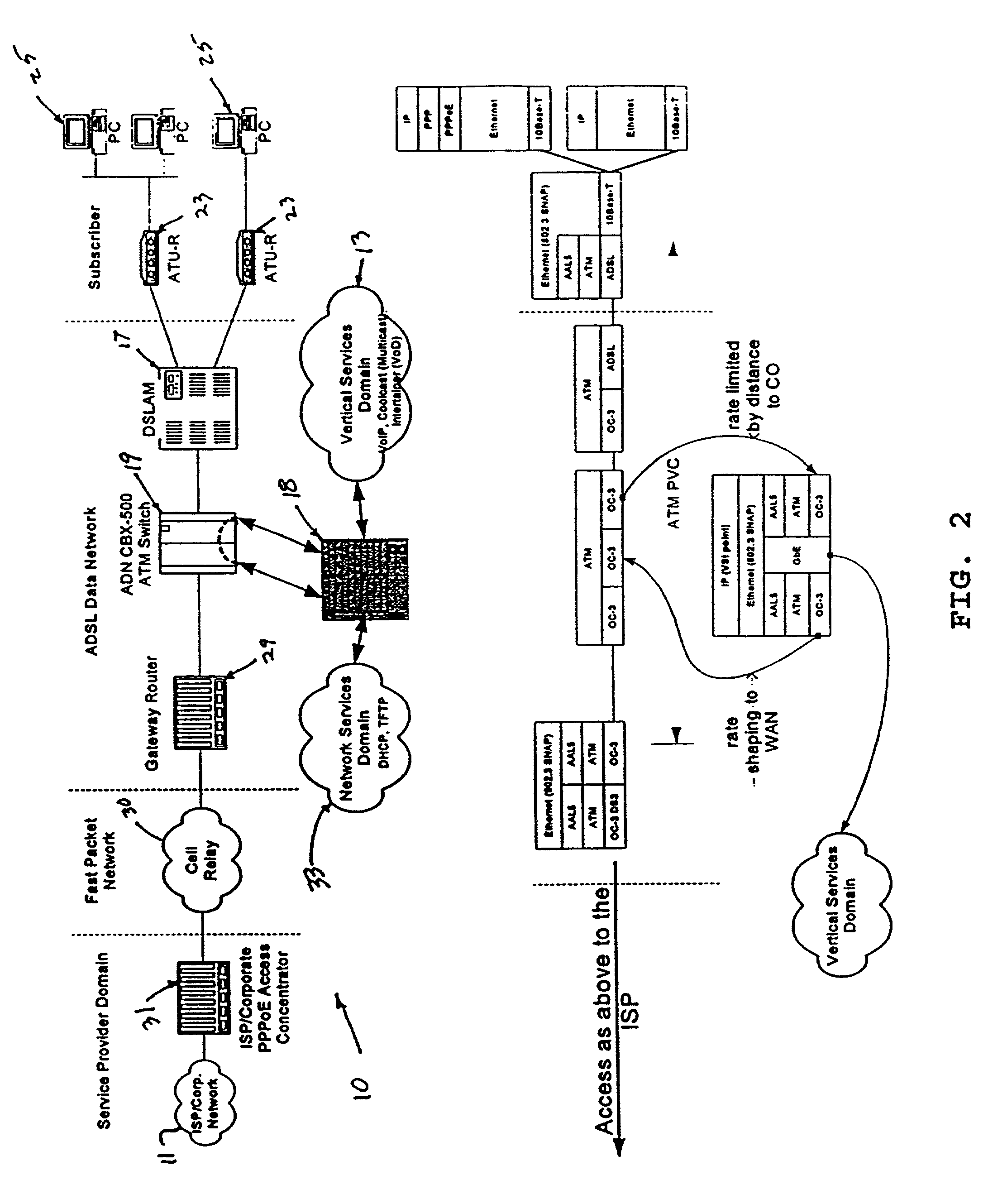

The invention relates to an enhanced ADSL Data Network (ADN) with vertical services capabilities. In general, vertical services capabilities are data services offered directly from a central office to an end user, without compromising the integrity of the user's guaranteed bit rate to the Internet through the ADN. One such vertical service is content downloadable at a high data rate from a content server located in or proximate to a central office that serves the end user. The content of the local server is updated and upgraded periodically and systematically from a central content server that distributes content to a number of remote central offices. The content is distributed between the central content server and the respective local content servers using available bandwidth, that is to say bandwidth on at least certain network links that is unused by subscriber traffic.

Owner:VERIZON PATENT & LICENSING INC

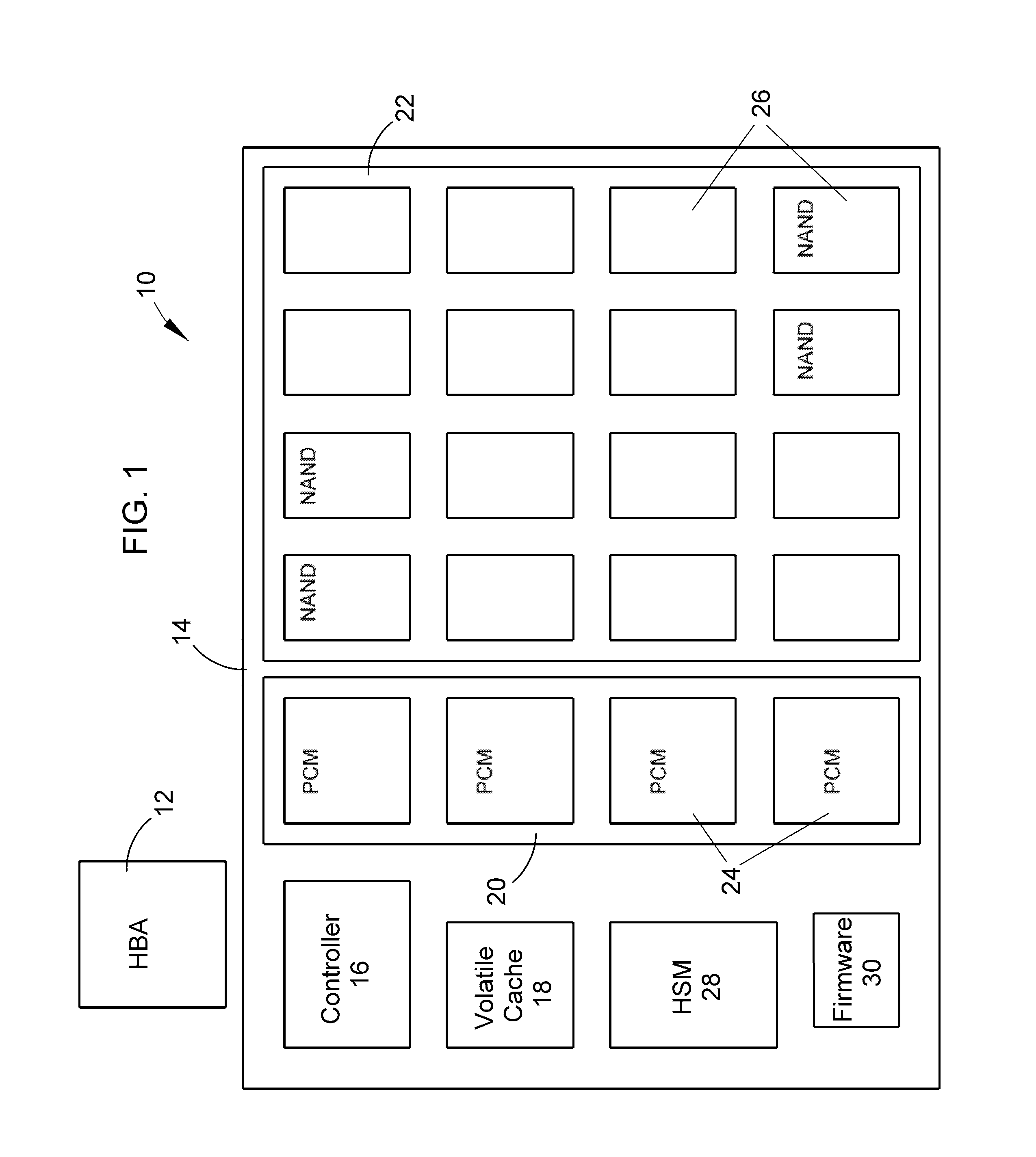

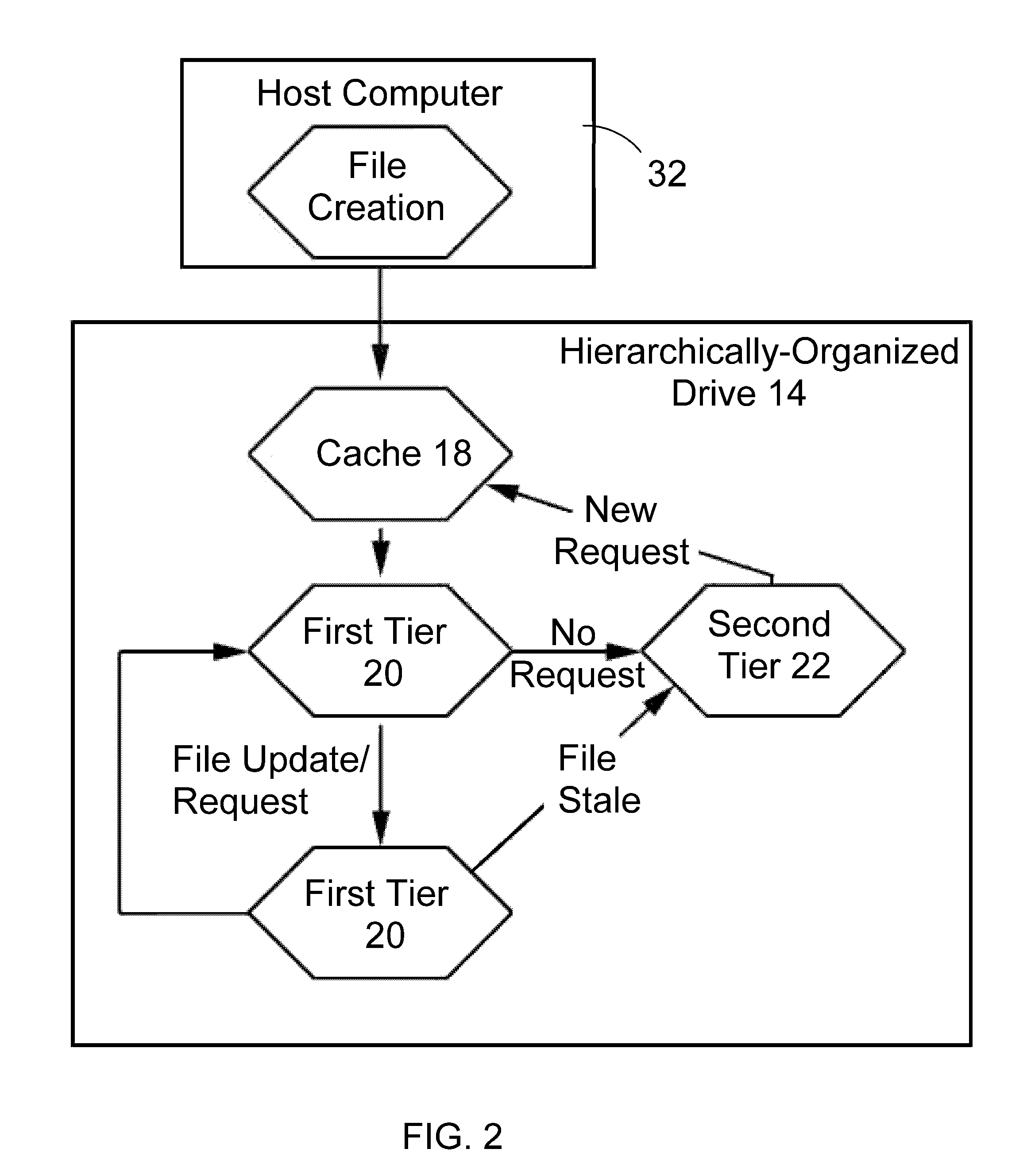

Hierarchically structured mass storage device and method

InactiveUS20100325352A1Faster access timeHigh write enduranceMemory architecture accessing/allocationMemory adressing/allocation/relocationAccess timeStorage management

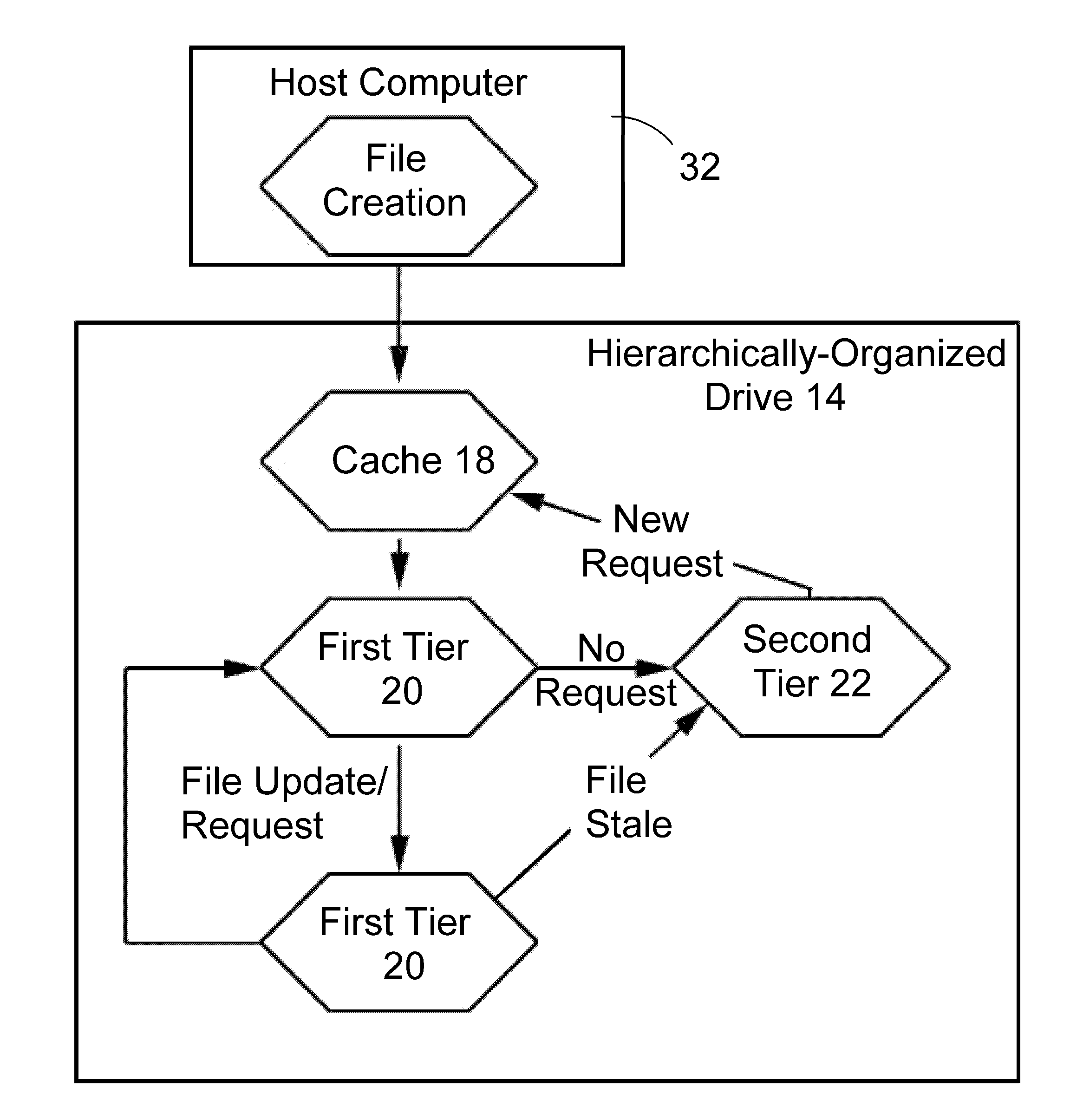

A hierarchically-structured computer mass storage system and method. The mass storage system includes a mass storage memory drive, control logic on the mass storage memory drive that includes a controller and one or more devices for executing a hierarchical storage management technique, a volatile memory cache configured to be accessed by the control logic, and first and second non-volatile storage arrays on the mass storage memory drive and comprising, respectively, first and second non-volatile memory devices. The first and second non-volatile memory devices have properties including access times and write endurance, and at least one of the access time and the write endurance of the first non-volatile memory devices is faster or higher, respectively, than the second non-volatile memory devices. Desired data storage localities on the storage arrays are determined through access patterns and selectively utilizing the properties of the memory devices to match the data storage requirements.

Owner:OCZ STORAGE SOLUTIONS

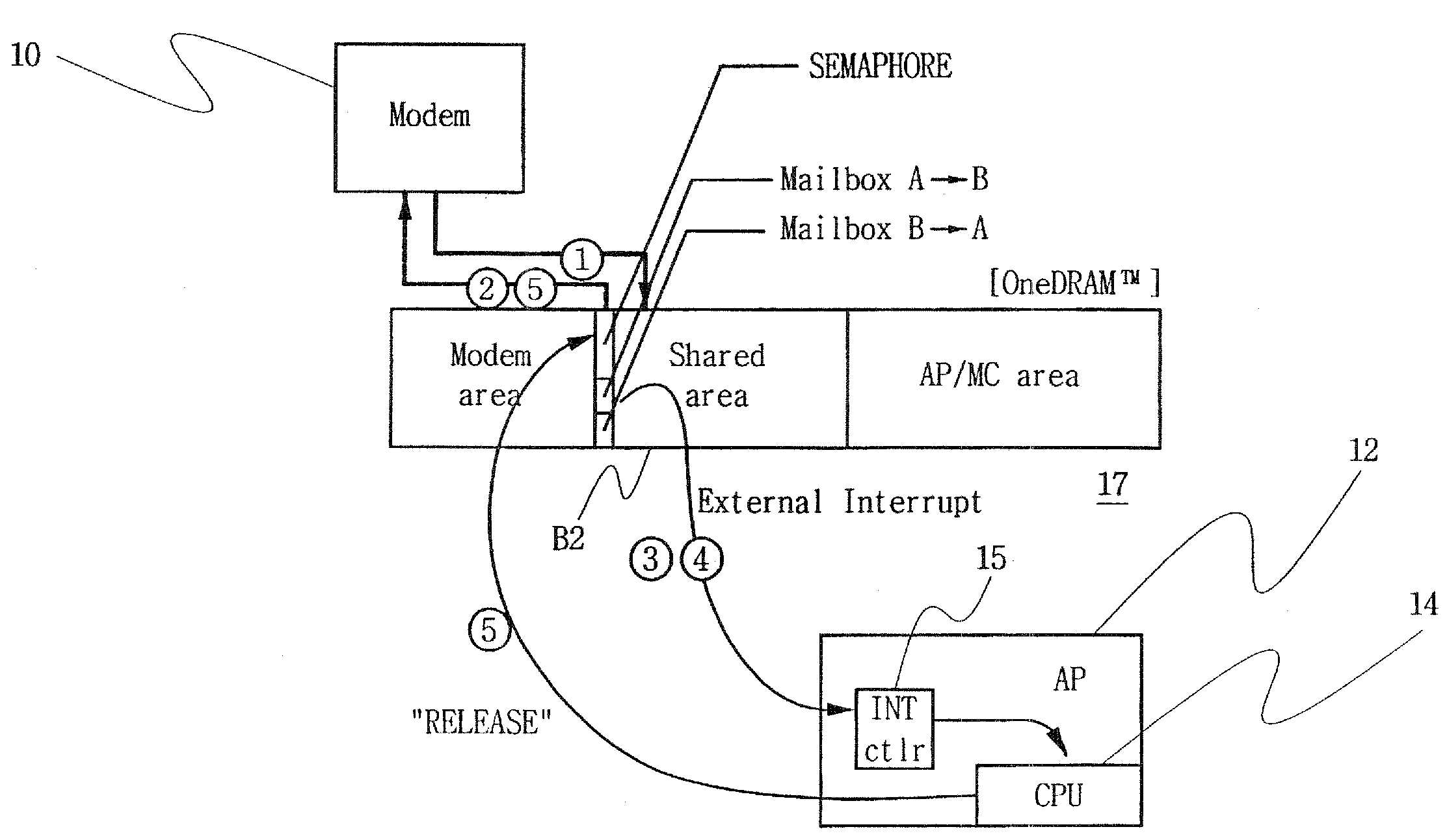

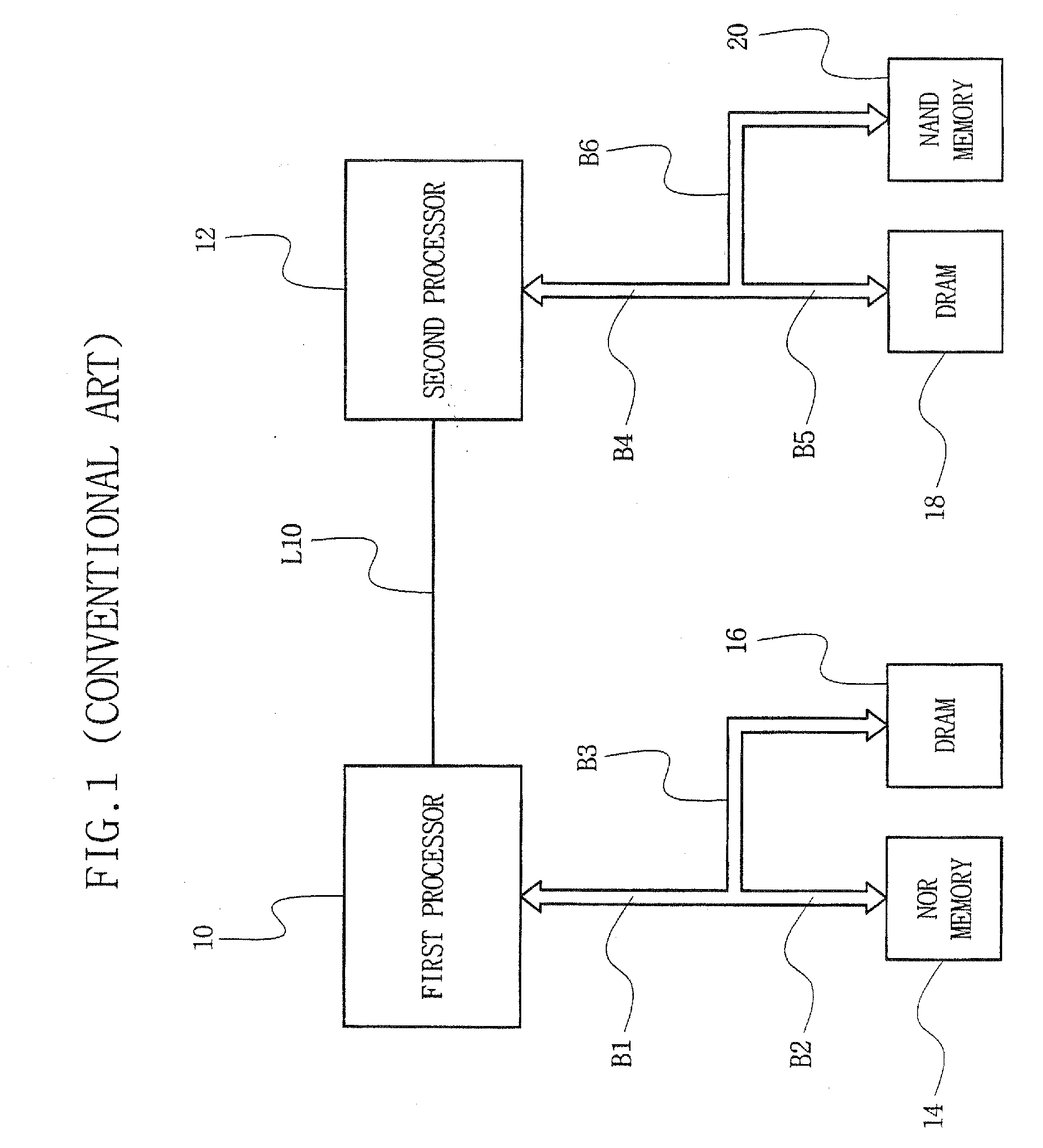

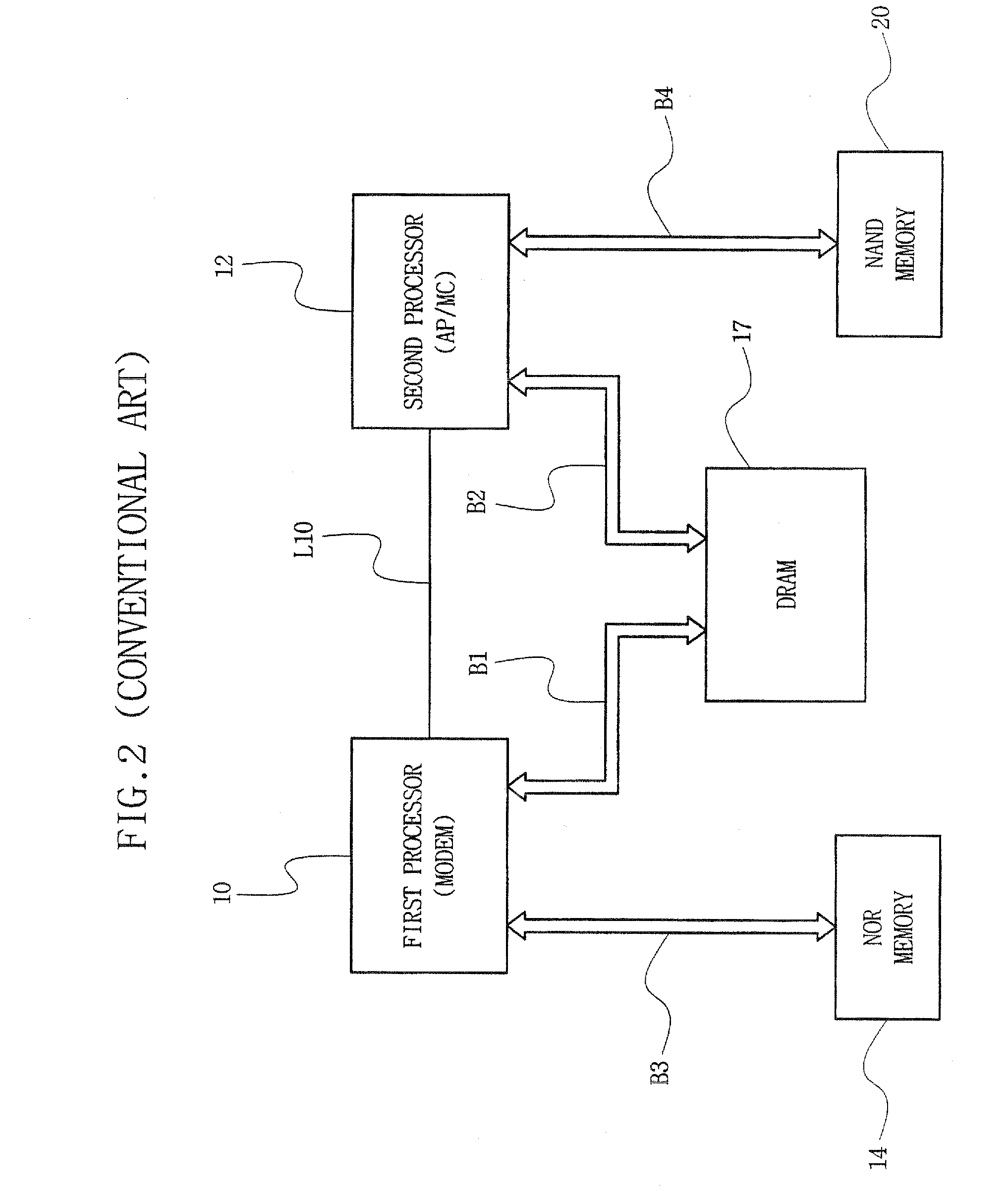

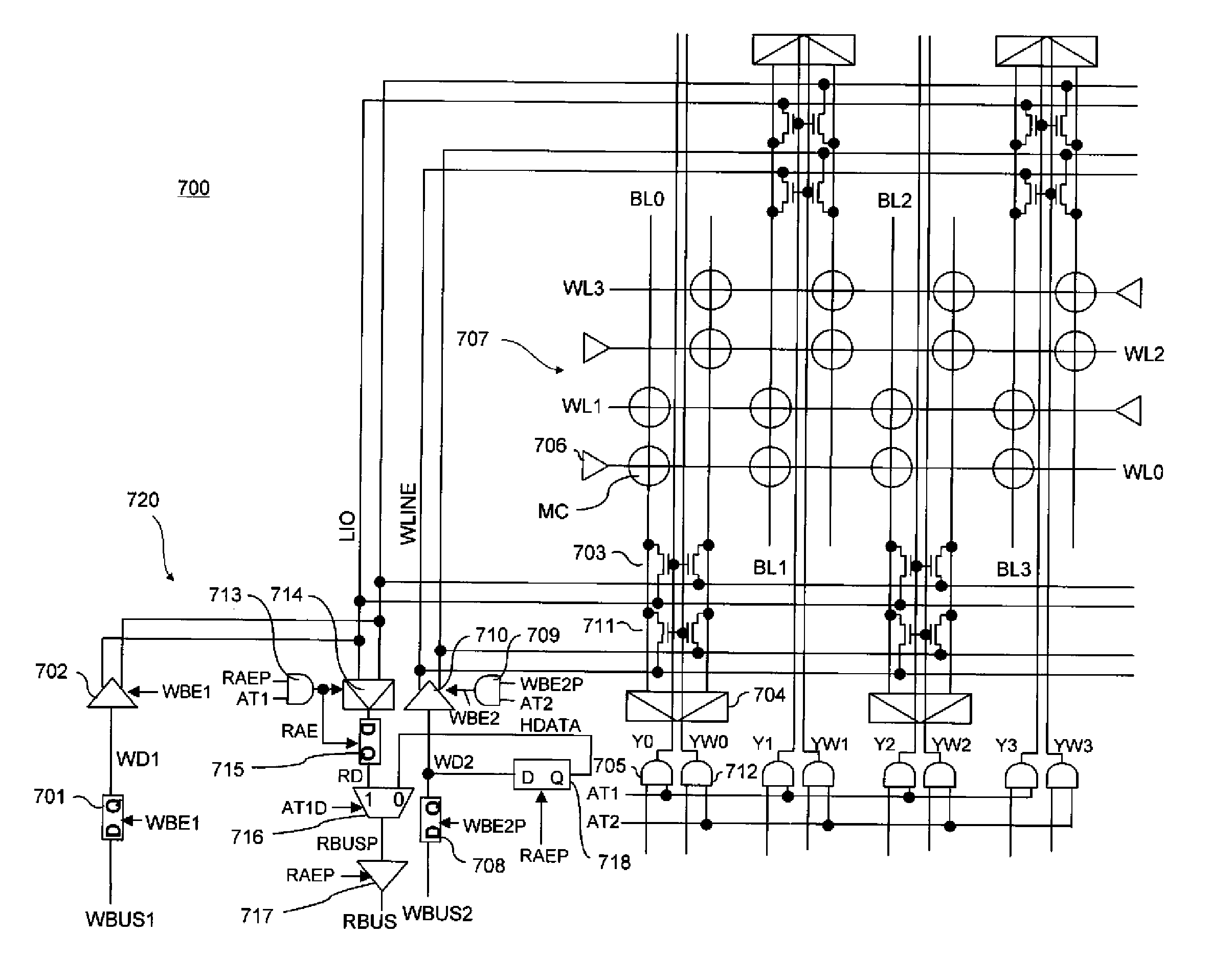

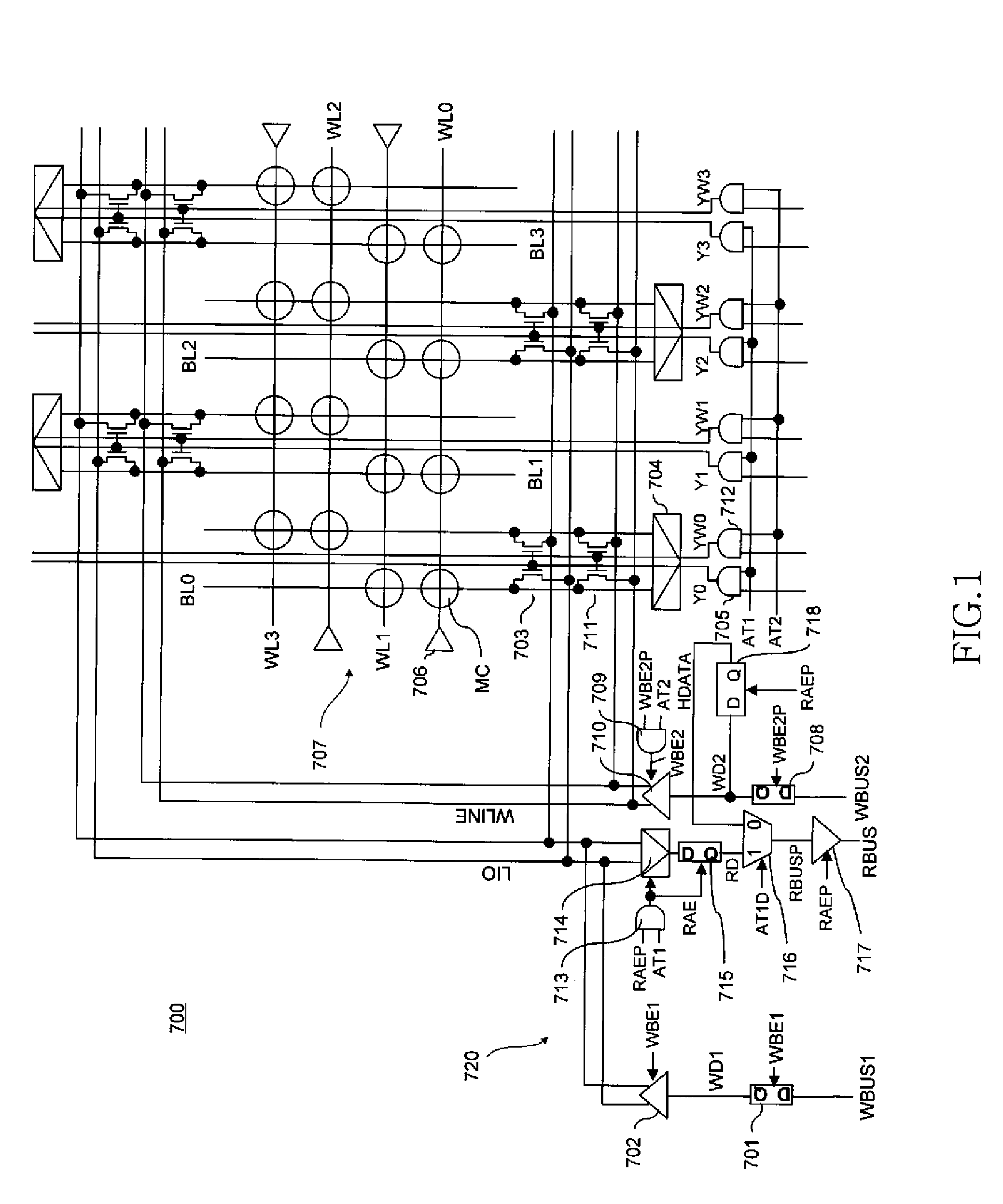

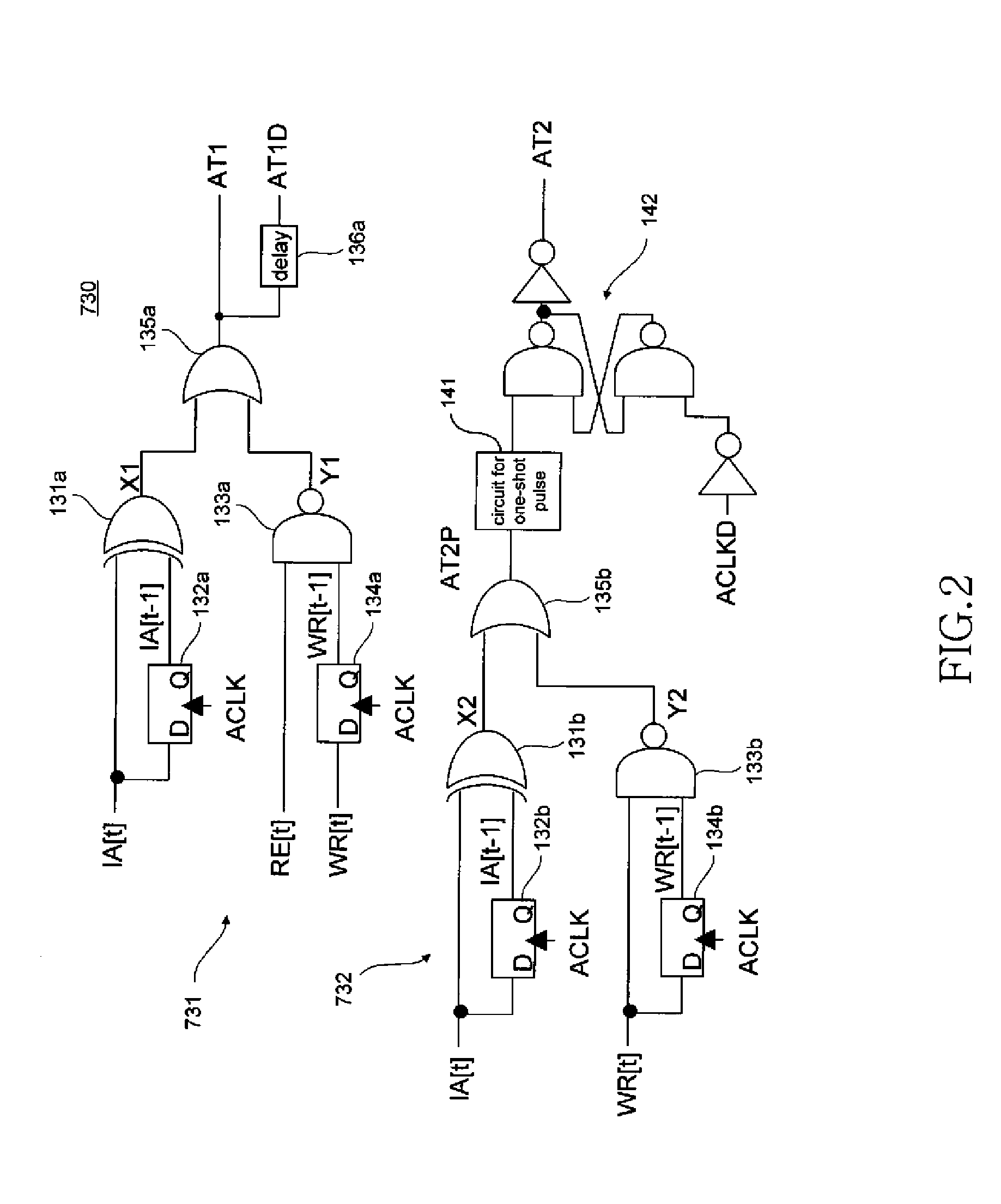

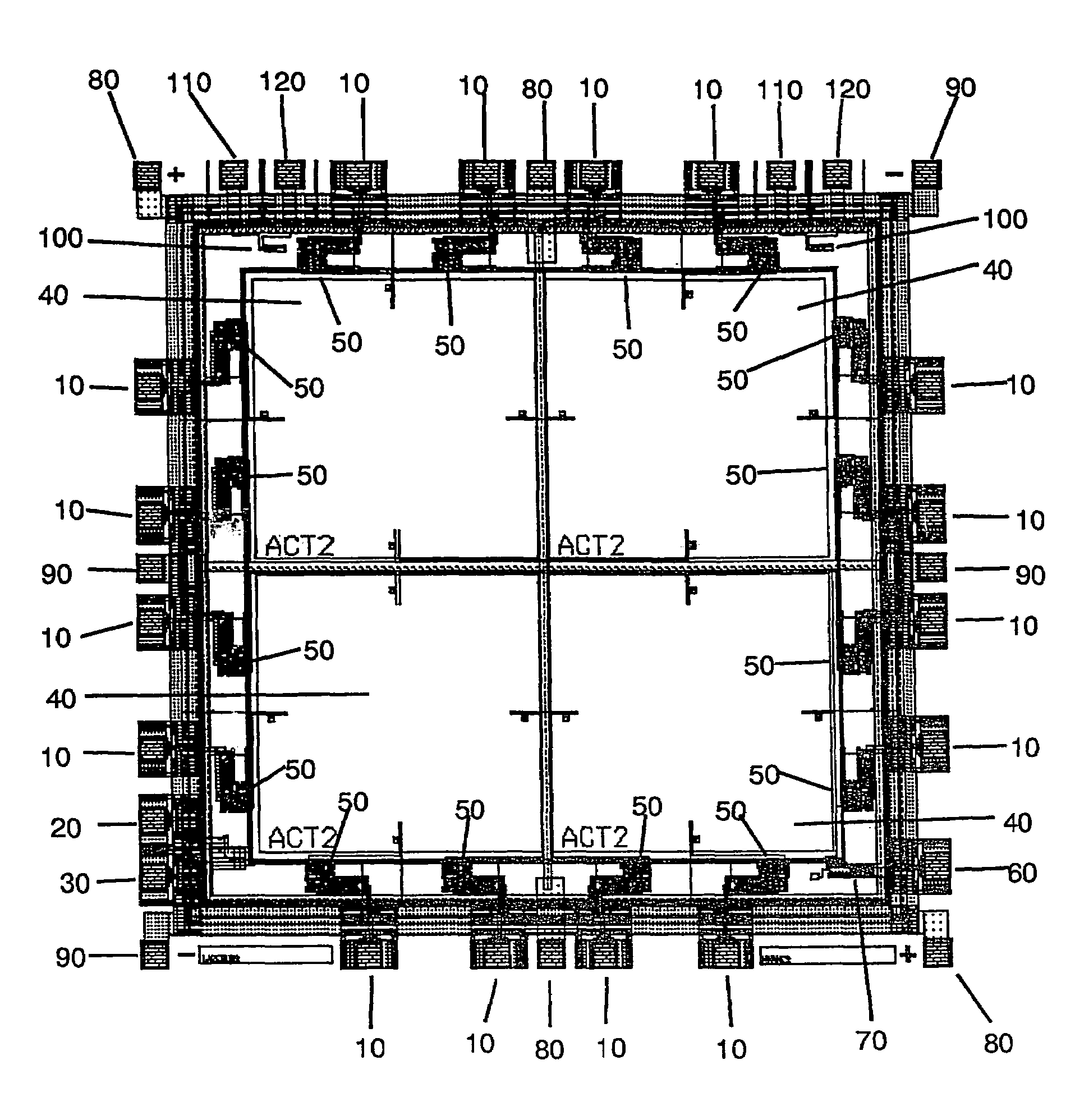

Multipath accessible semiconductor memory device with host interface between processors

ActiveUS20080077937A1Low costIncrease speedGeneral purpose stored program computerDigital storageMulti processorData access

A multipath accessible semiconductor memory device provides an interface function between processors. The memory device may include a memory cell array having a shared memory area operationally coupled to two or more ports that are independently accessible by two or more processors, an access path forming unit to form a data access path between one of the ports and the shared memory area in response to external signals applied by the processors, and an interface unit having a semaphore area and mailbox areas accessible in the shared memory area by the two or more processors to provide an interface function for communication between the two or more processors.

Owner:SAMSUNG ELECTRONICS CO LTD

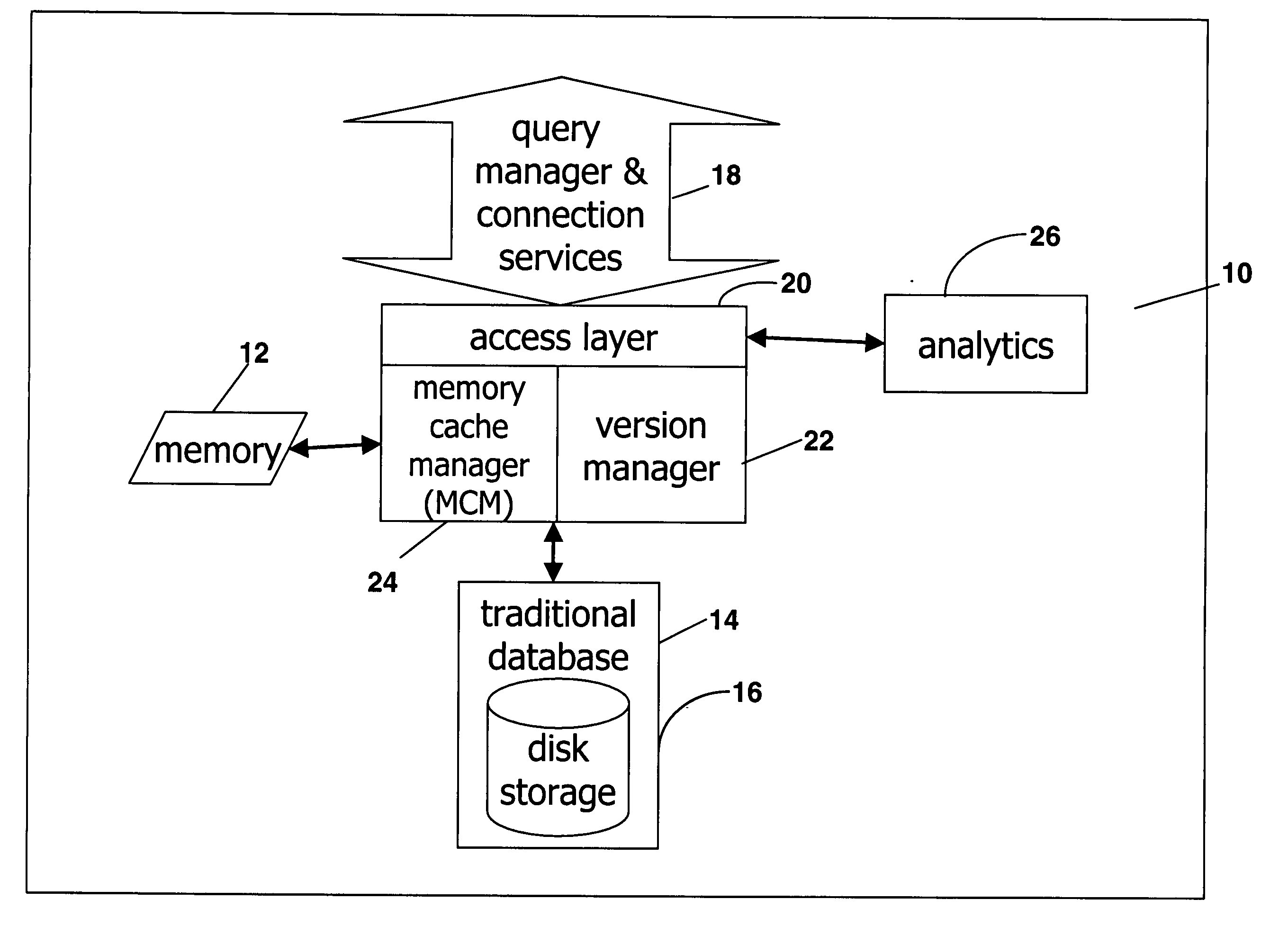

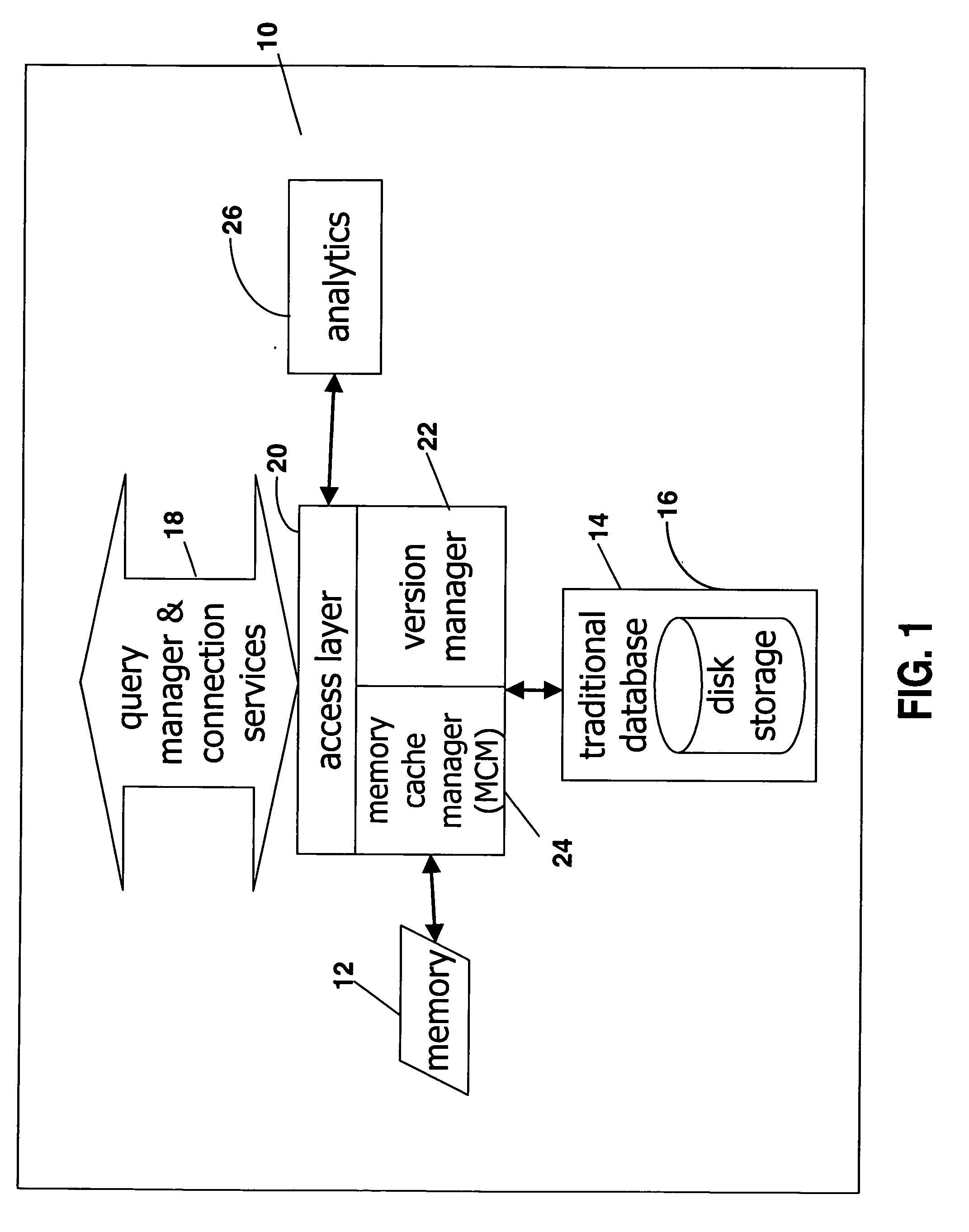

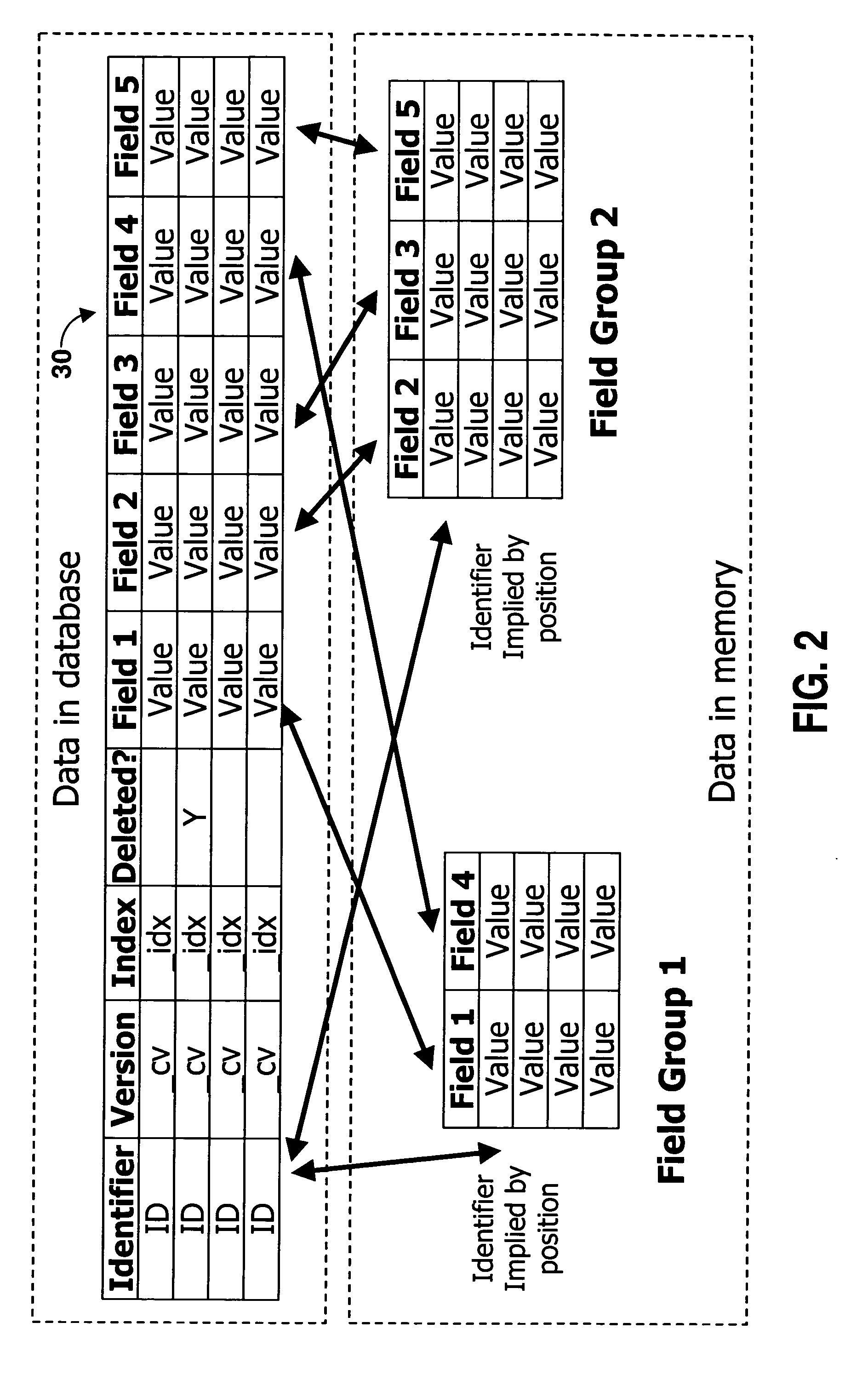

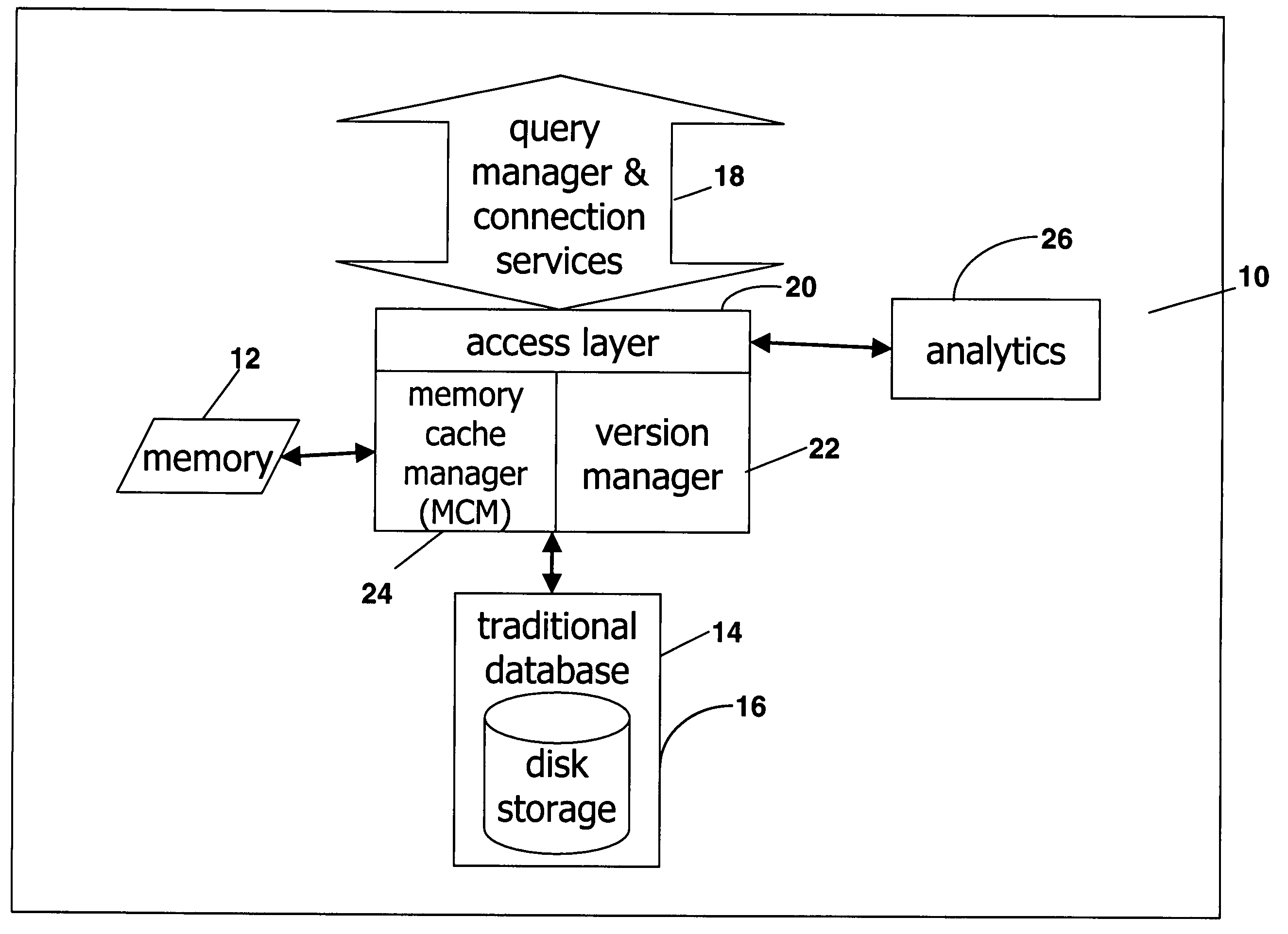

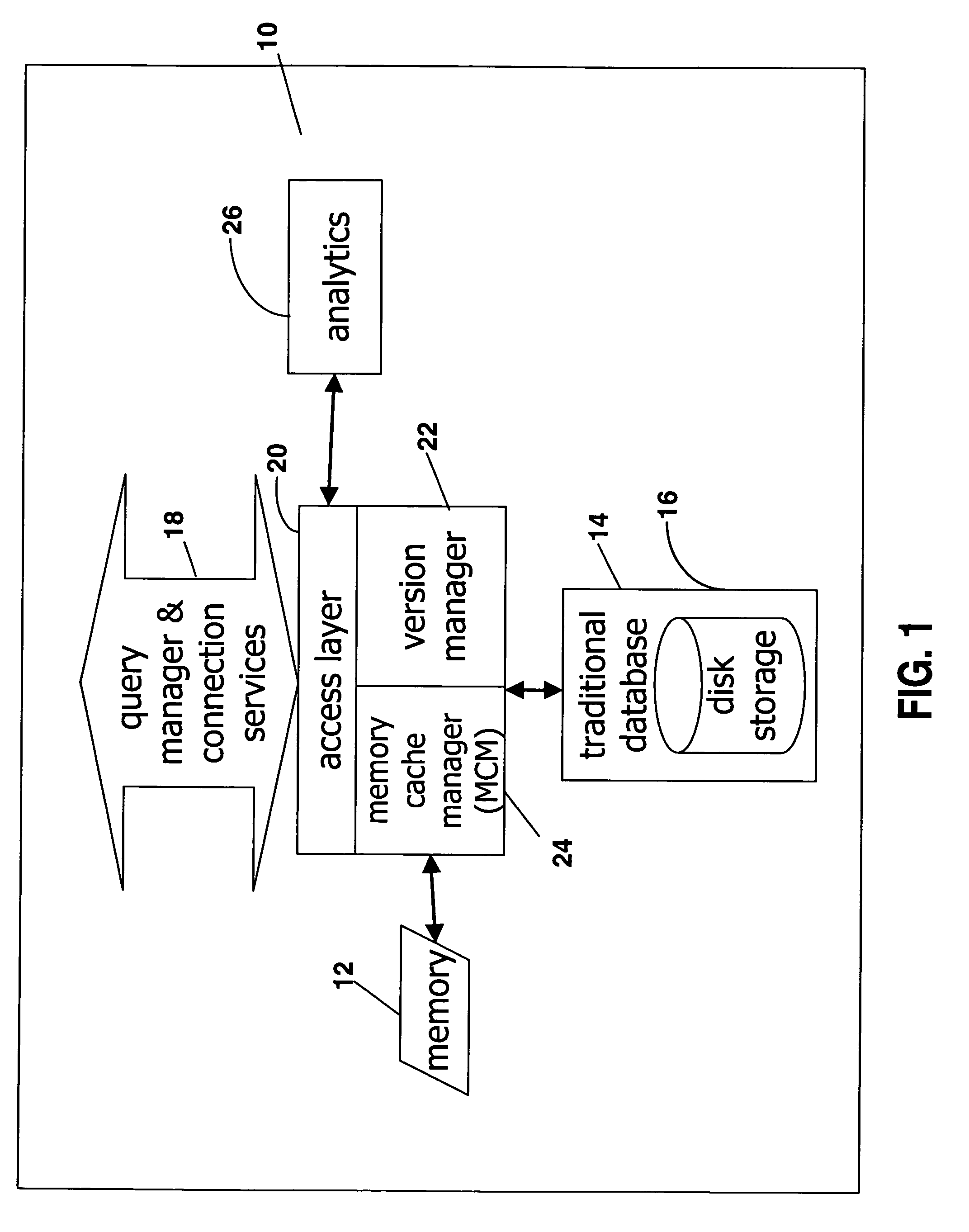

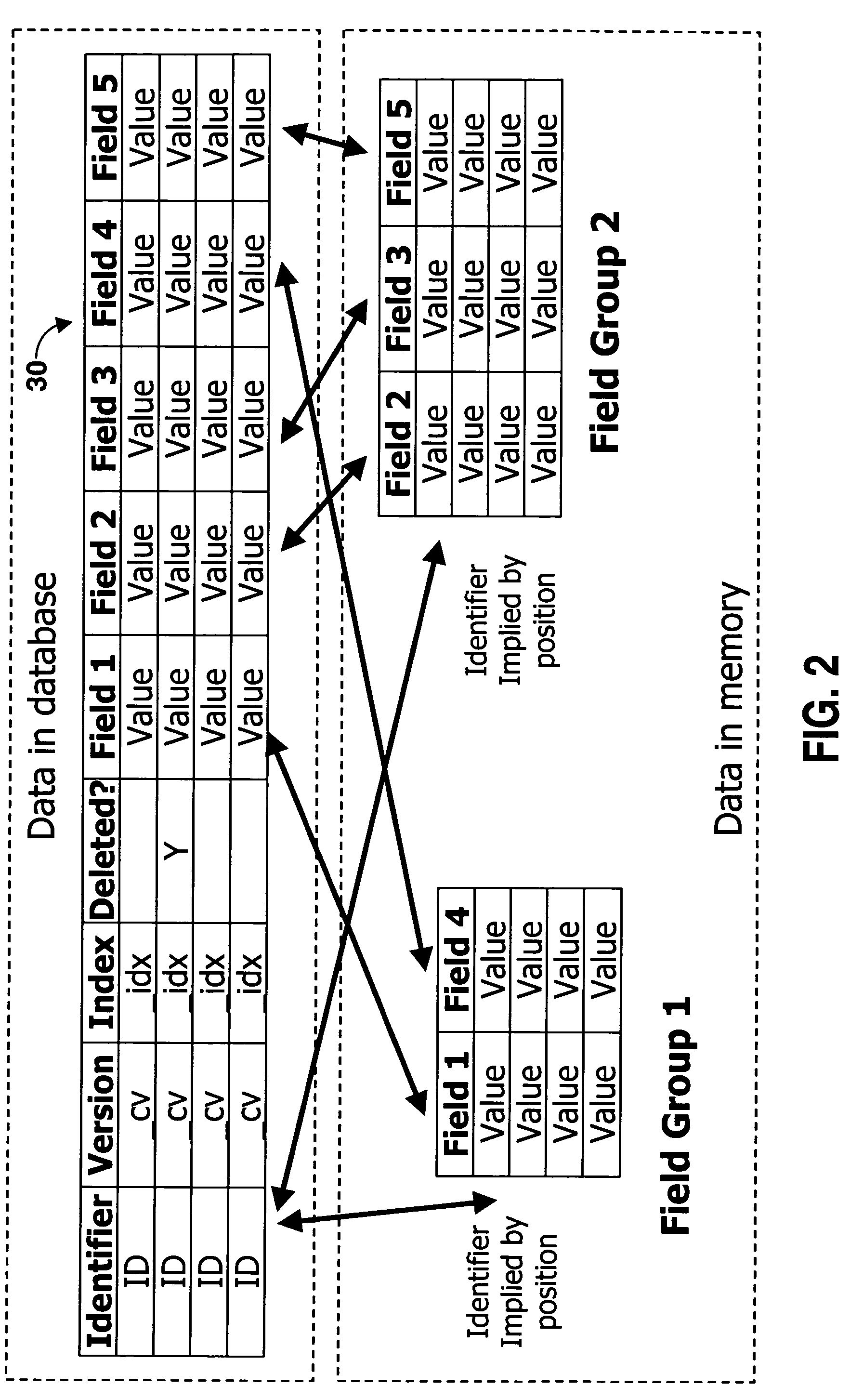

Extended database engine providing versioning and embedded analytics

ActiveUS20050138013A1Increase valueEfficient methodDigital data information retrievalDigital data processing detailsRelational databaseDatabase engine

A system for calculating analytics uses a relational database to store inputs, calculates results, and stores them in cache. The system also includes an access layer that provides a unified view of the data in server. A dynamic access layer is generated at runtime to run an analytic to provide a flexible framework for creating business logic.

Owner:KINAXIS INC

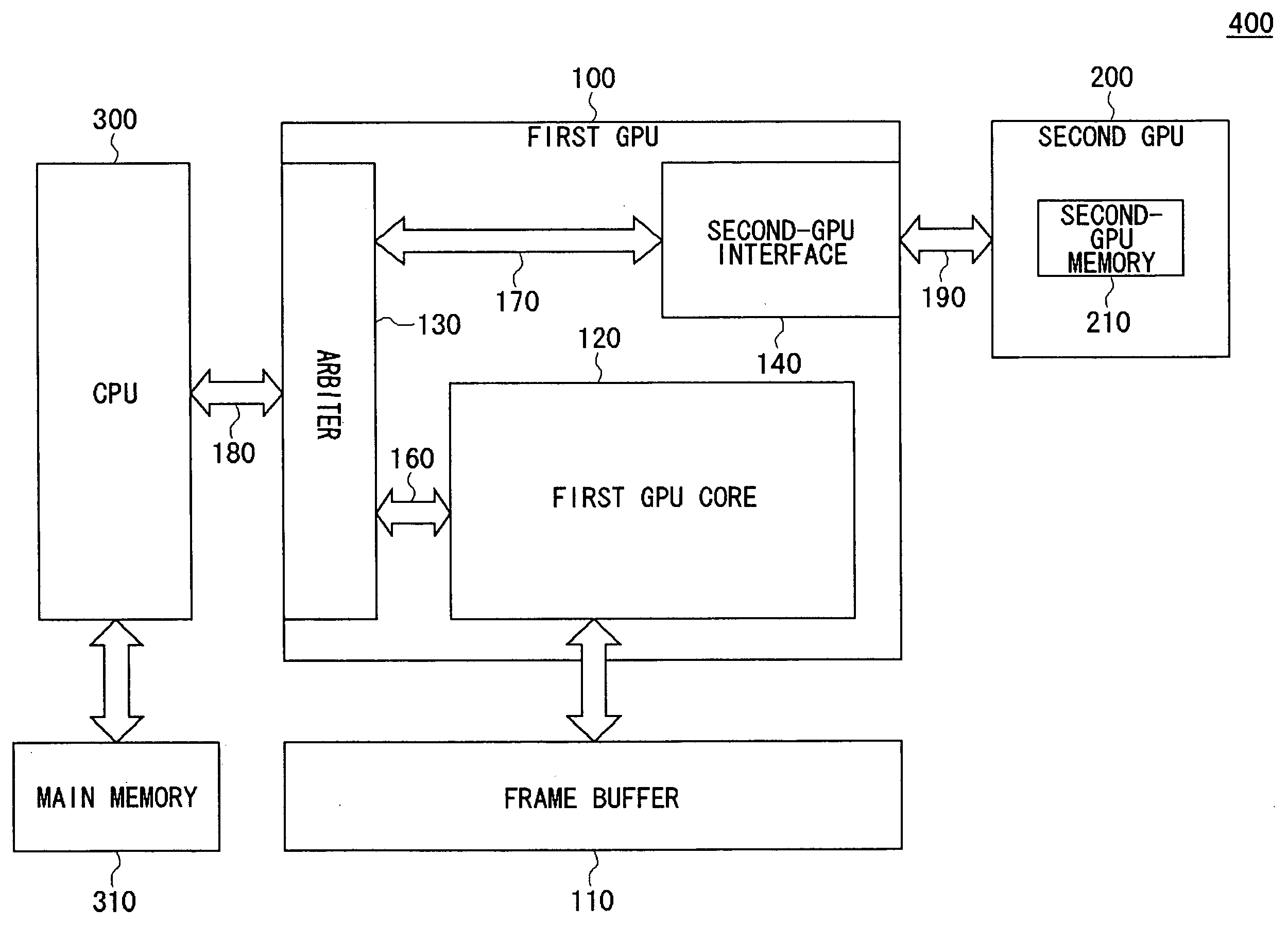

Multi-graphics processor system, graphics processor and data transfer method

ActiveUS20070273699A1Improve efficiencyImprove data transfer efficiencyMultiple digital computer combinationsProcessor architectures/configurationEmbedded systemData transmission

A multi-graphics processor system includes a CPU; a first GPU connected to the CPU via an input / output interface; and a second GPU connected to the first GPU via a second-GPU interface. The first GPU is provided with a second-GPU bus for communicating the CPU and the second GPU via the second-GPU interface. The CPU communicates with the second GPU via the second-GPU bus after receiving a signal indicating the timing of the data communication.

Owner:SONY COMPUTER ENTERTAINMENT INC

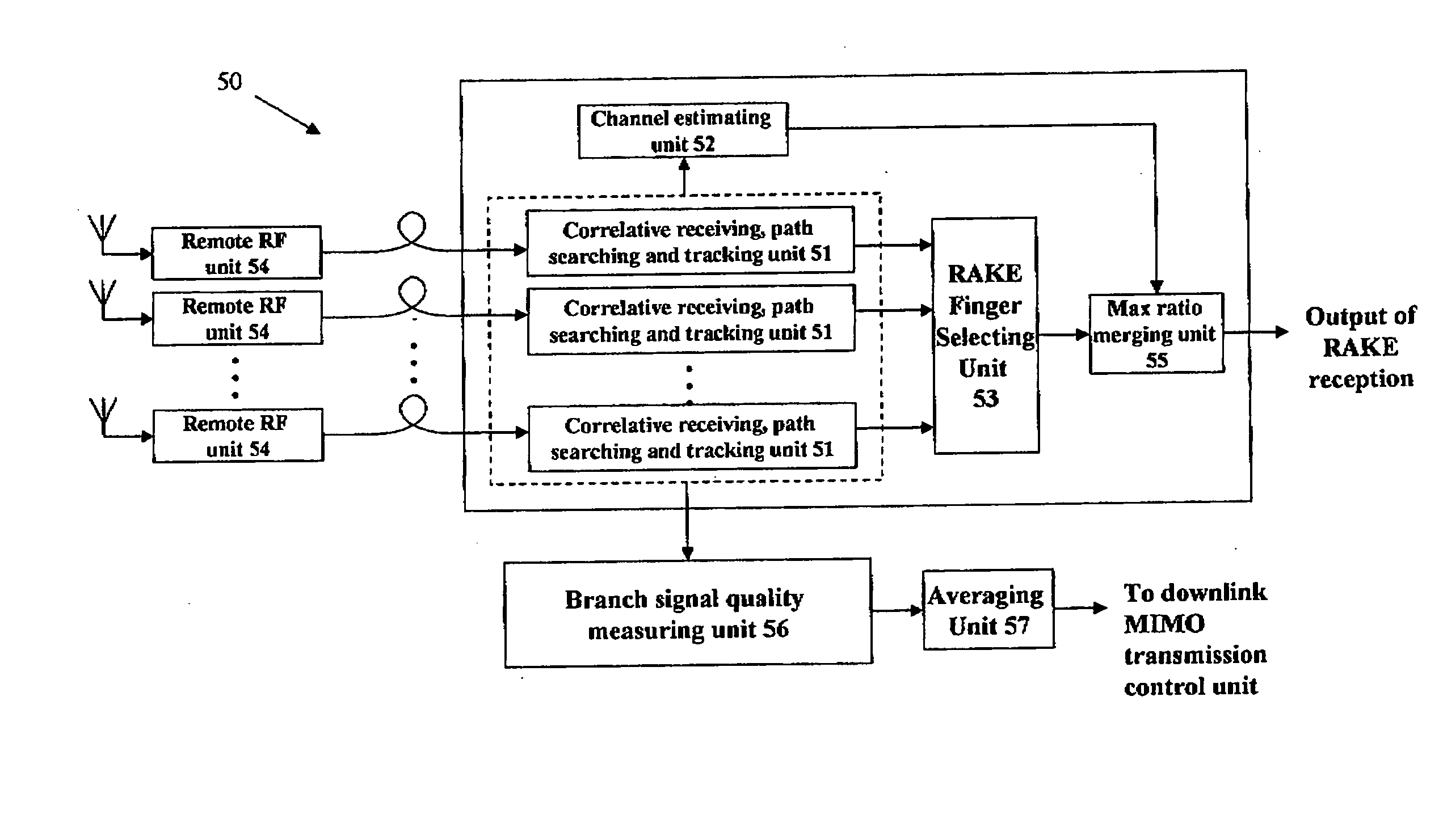

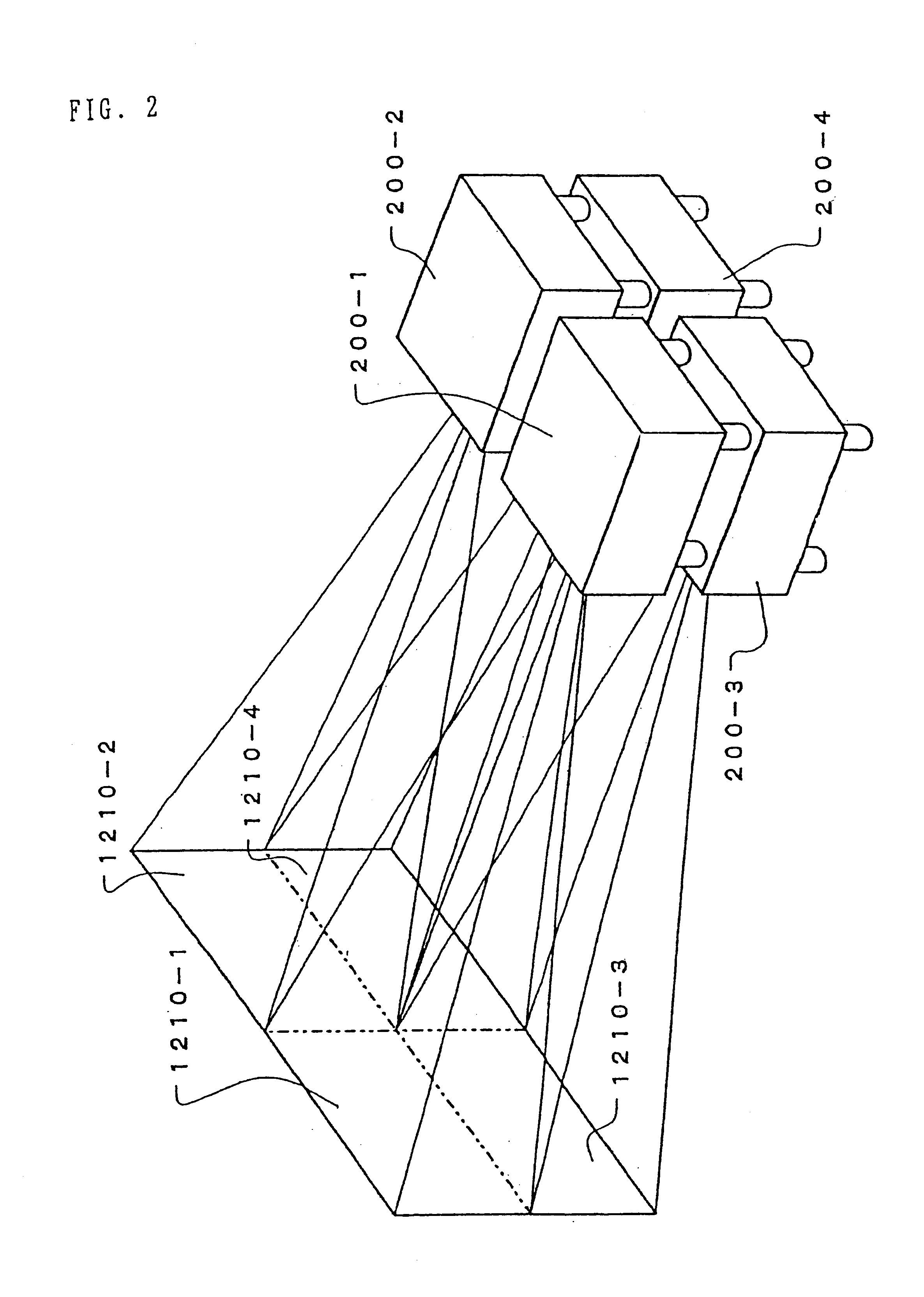

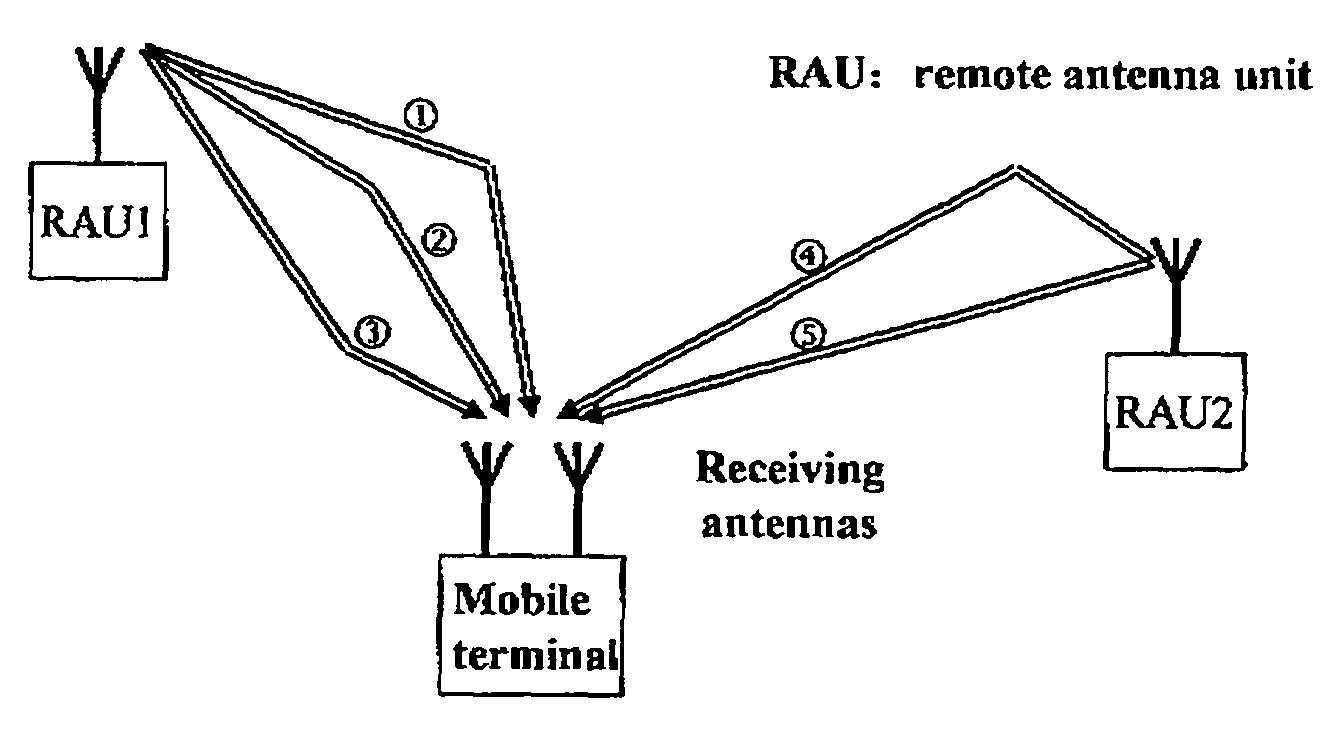

Multiple input/multiple output communication method based on distributed transmission sources

InactiveUS20070280370A1High speed downlink packet accessIncrease downlink speedSite diversitySpatial transmit diversitySignal qualityData stream

A MIMO method based on distributed transmission sources for transmitting a downlink data stream between M transmitting antennas and a mobile terminal having P receiving antennas, M and P>1, channels from at least two transmitting antennas to one of receiving antennas have different multipath distributions, said method comprises transmitting corresponding M substreams to the mobile terminal by using the same spreading code; estimating the multipath channel matrix; and processing the signal according to the multipath channel matrix to restore the downlink data stream, the estimating including measuring the total number of actual multipath received components having different delays in the transmitted signals; constructing the multipath channel matrix by taking the number as the multipath number, so that if the signal transmitted by one of the transmitting antennas to the receiving antenna has no multipath component corresponding to one of the delays, the channel parameter corresponding to the transmitting antenna, the receiving antenna and the delay is set as 0, the transmitting comprises adjusting the gain of said M sub-data streams based on the average signal quality measurement of uplink signals from the mobile terminal to said M transmitting antennas, so that average path losses of respective downlink channels are substantially equal.

Owner:UTSTARCOM TELECOM CO LTD

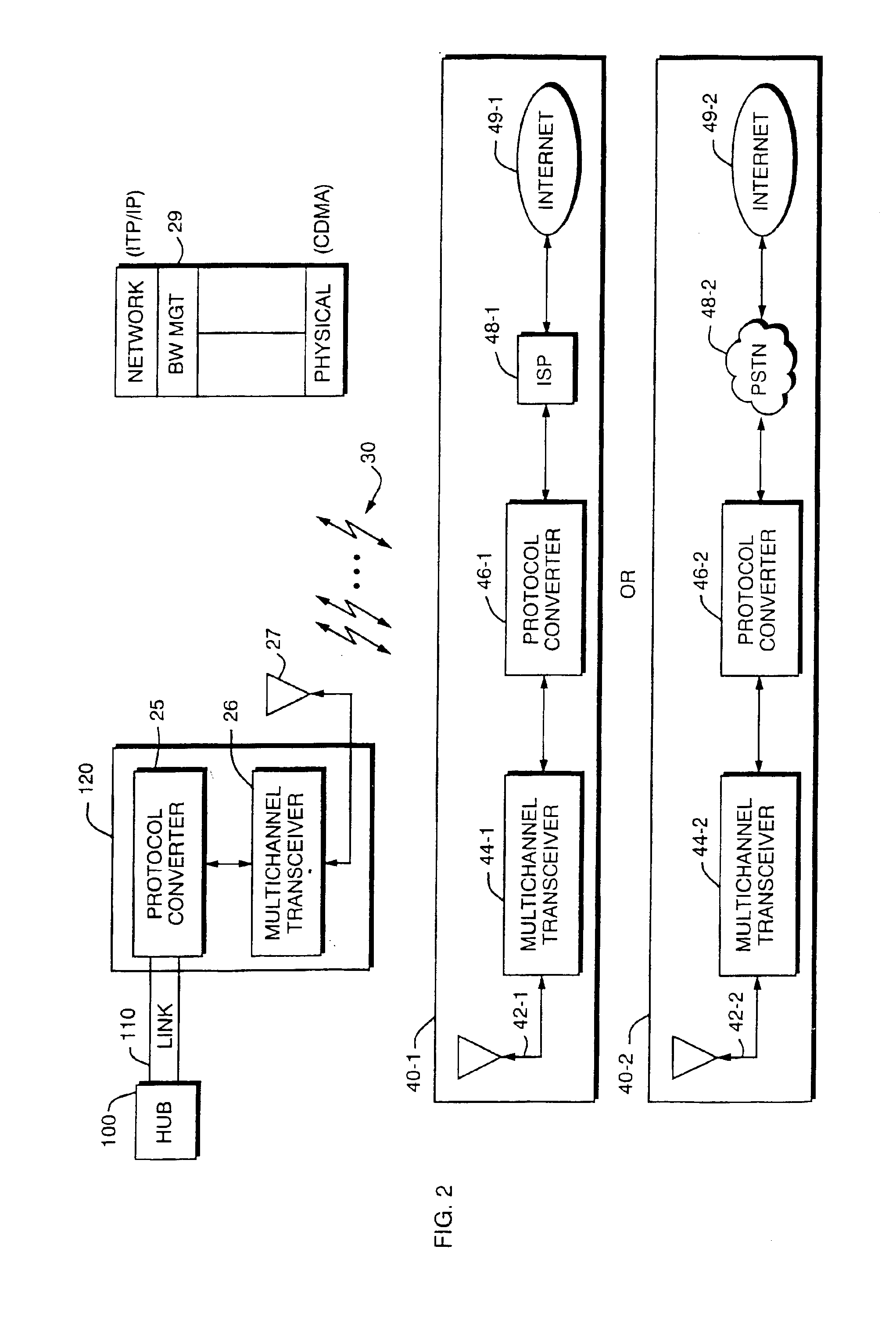

Two tier hi-speed wireless communication link

InactiveUS6850512B1Communication link costCost prohibitiveError prevention/detection by using return channelFrequency-division multiplex detailsTransceiverTelecommunications link

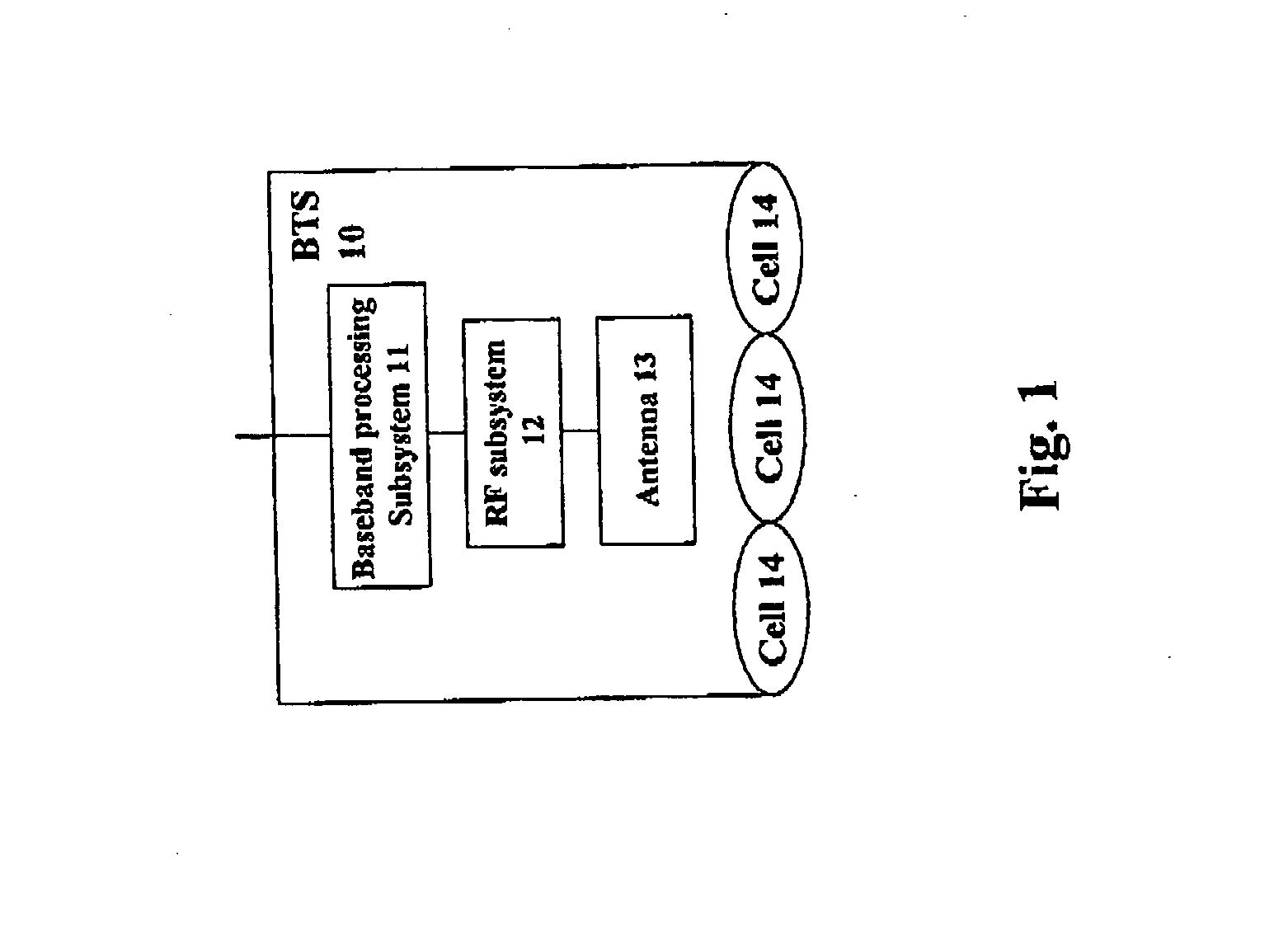

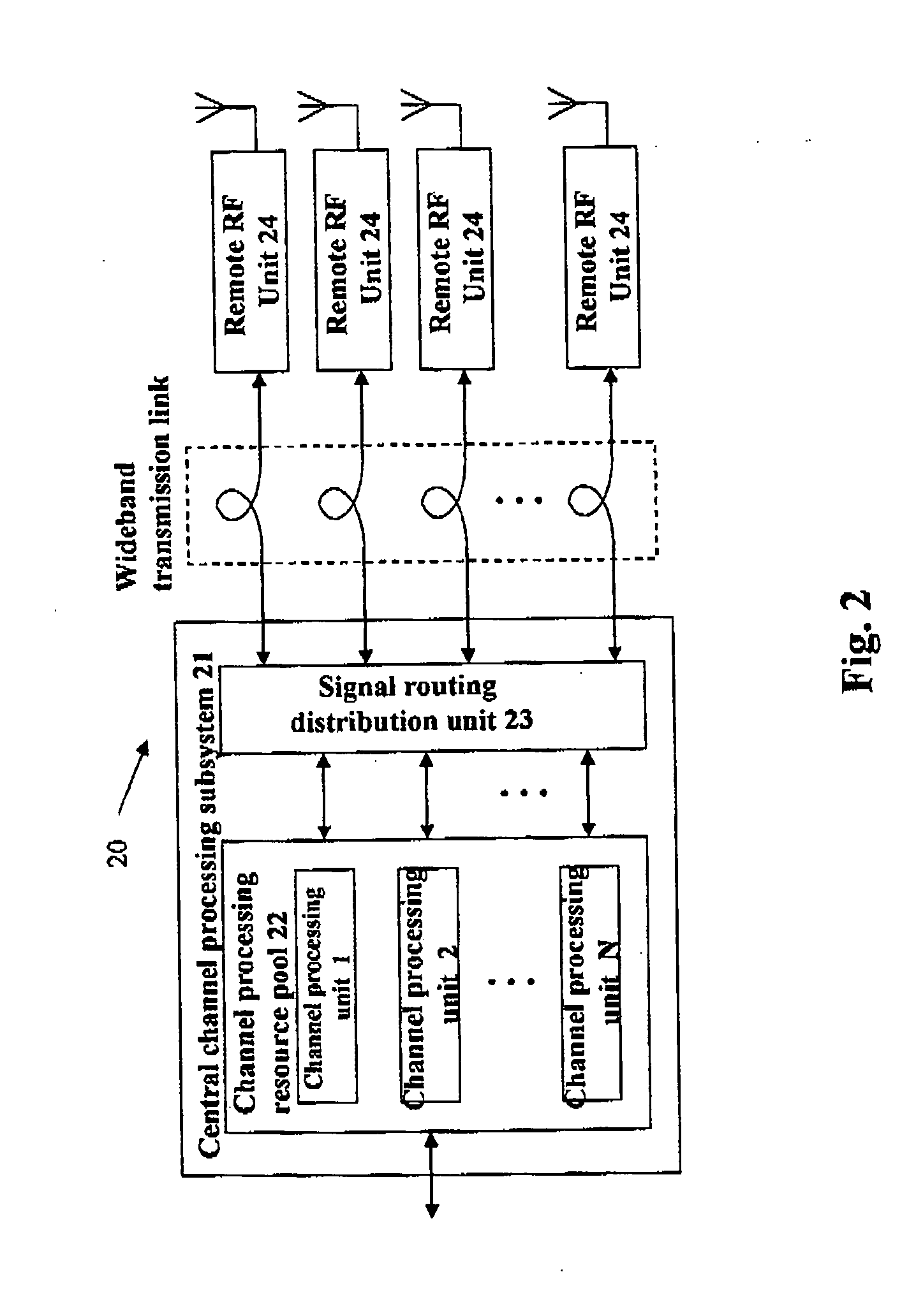

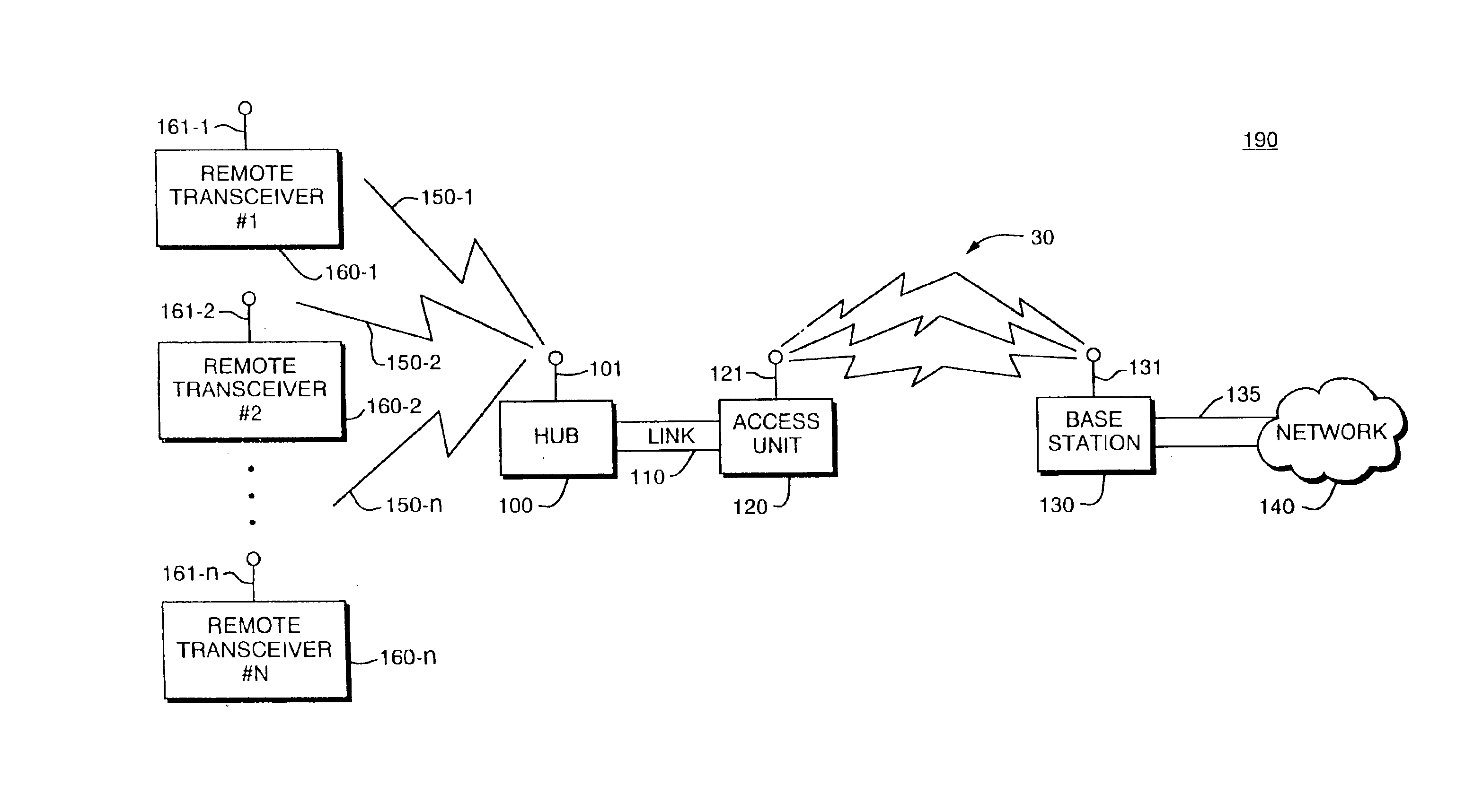

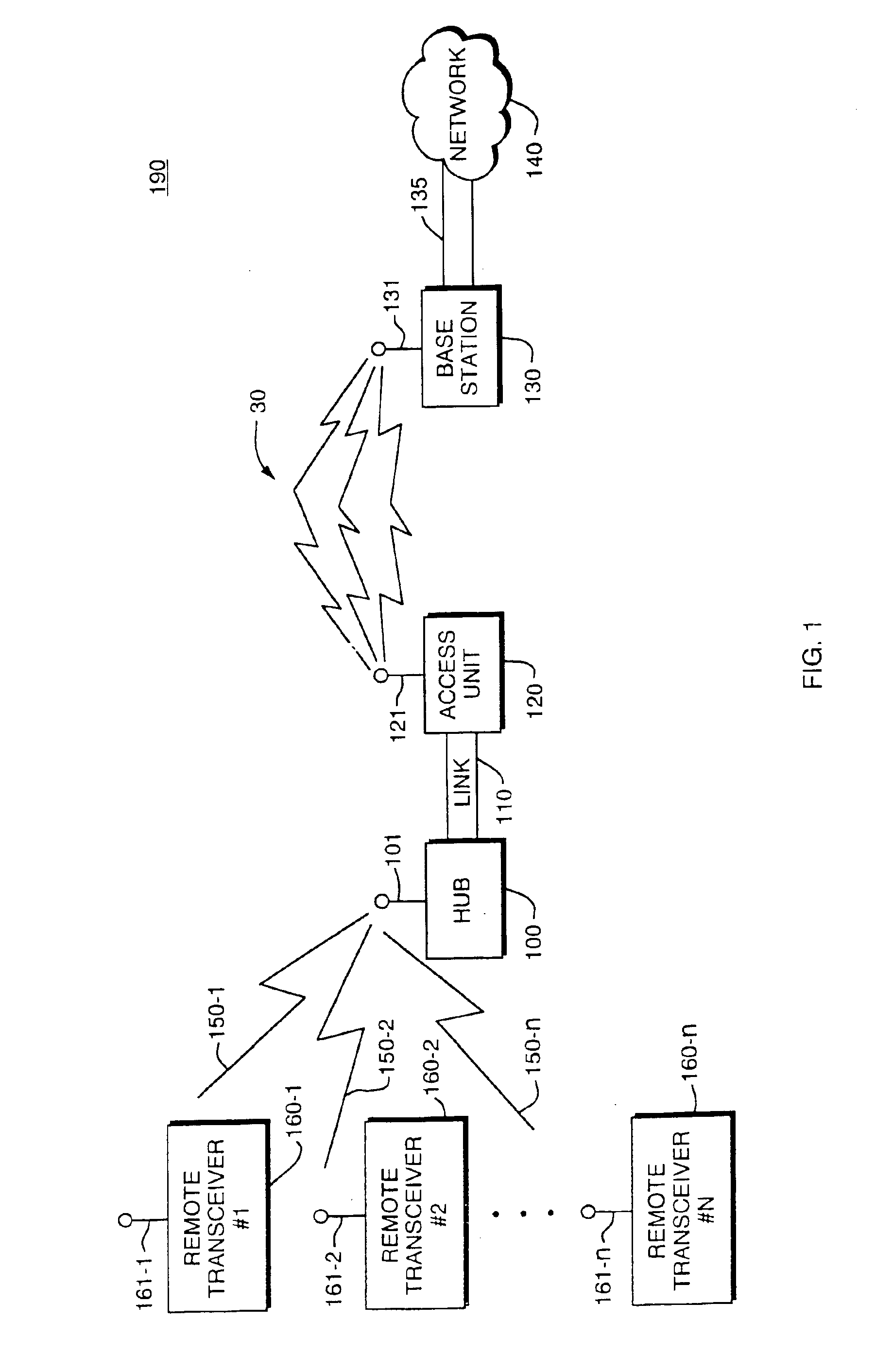

A system and method for communicating between a plurality of remote transceivers and a network is discussed including multiple types of serially-connected communication links, upon which data flows are established to communicate information between the remote transceivers and network. A hub is coupled to one end of a hardwired communication link while an access unit is coupled to the other end. In addition to supporting communications on the hardwired link, the hub supports communication with the plurality of remote transceivers over a wireless link of a first type. The access unit at the other end of the hardwired link is in further communication with a base station over a wireless communication link of a second type, while the base station is in further communication with the network. Based on this topology, data flows over this string of interconnected communication media support information transfers between the plurality of remote transceivers and the network.

Owner:IPR LICENSING INC

Vertical services integration enabled content distribution mechanisms

InactiveUS7170905B1Increased cost-effectivenessReduce demandTime-division multiplexData switching by path configurationTraffic capacityContent distribution

The invention relates to an enhanced ADSL Data Network (ADN) with vertical services capabilities. In general, vertical services capabilities are data services offered directly from a central office to an end user, without compromising the integrity of the user's guaranteed bit rate to the Internet through the ADN. One such vertical service is content downloadable at a high data rate from a content server located in or proximate to a central office that serves the end user. The content of the local server is updated and upgraded periodically and systematically from a central content server that distributes content to a number of remote central offices. The content is distributed between the central content server and the respective local content servers using available bandwidth, that is to say bandwidth on at least certain network links that is unused by subscriber traffic.

Owner:RAKUTEN INC

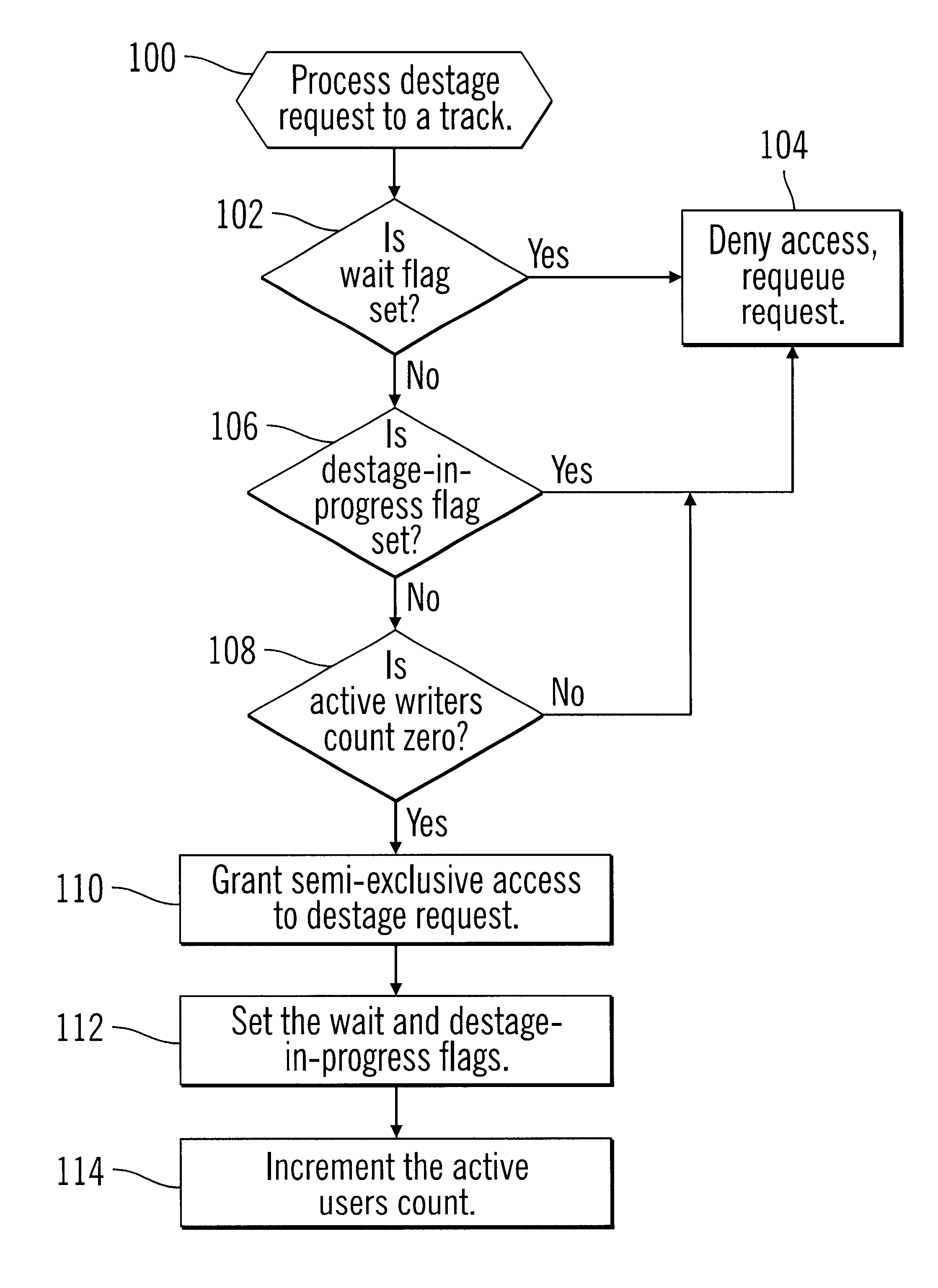

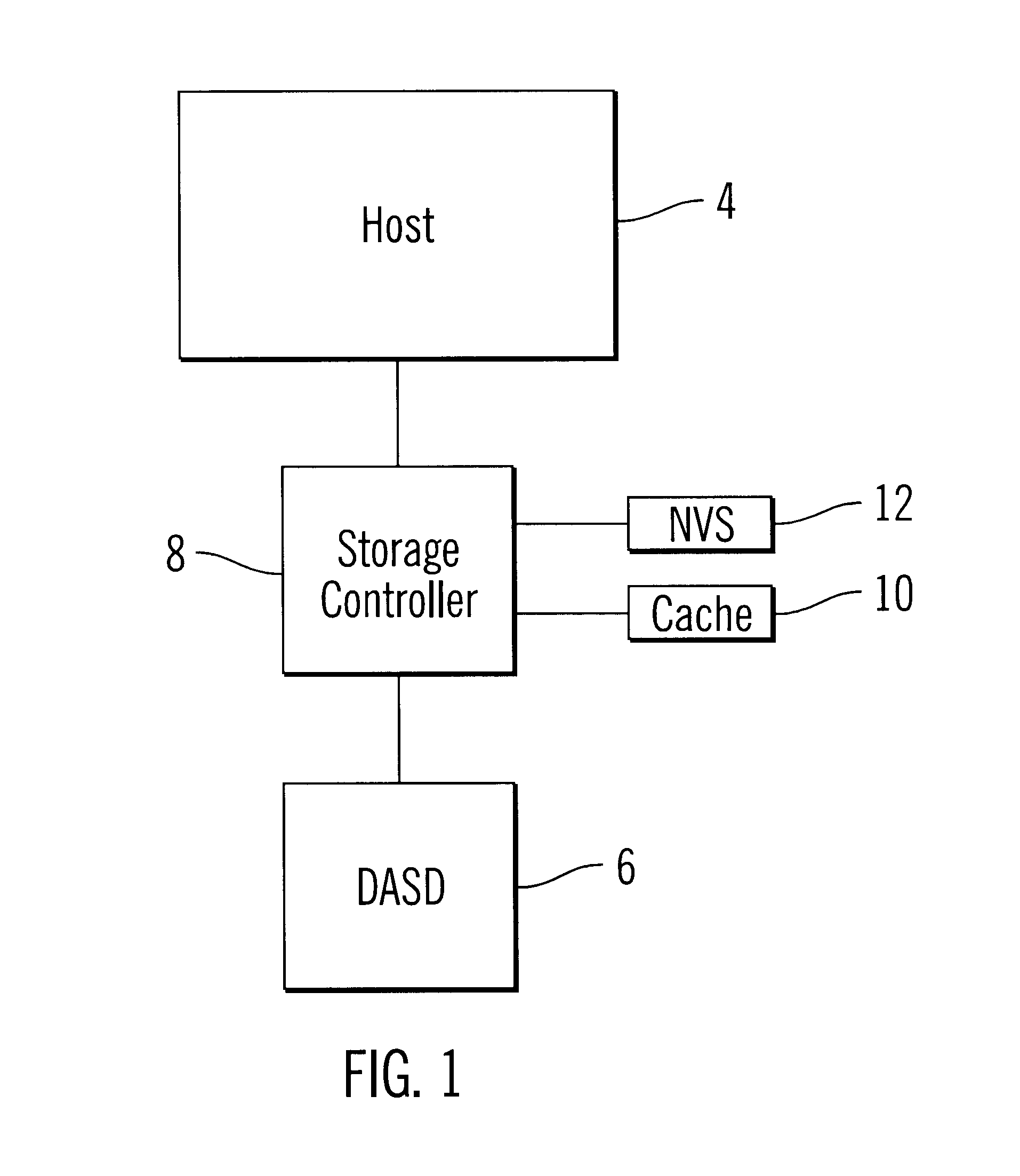

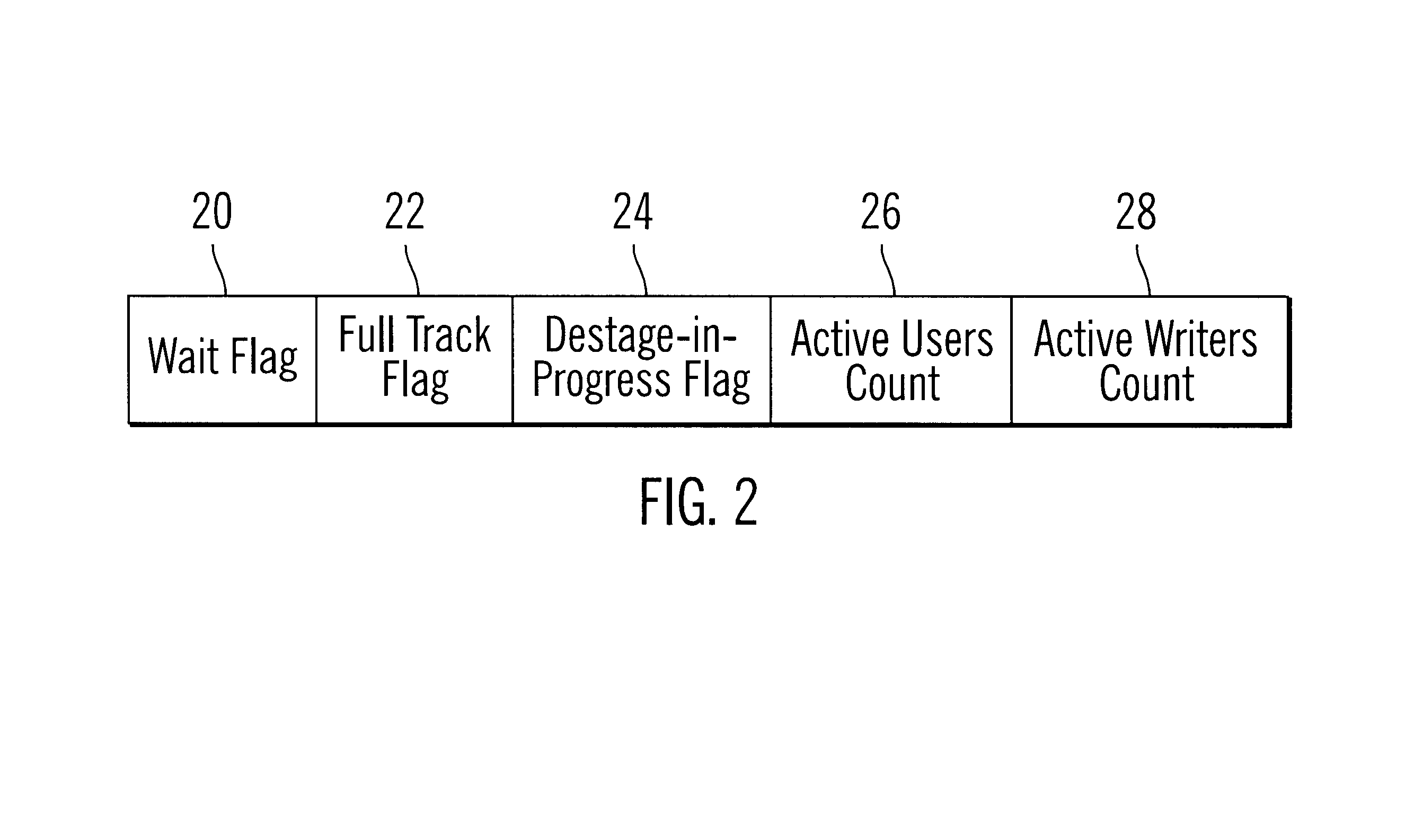

Method, system, and program for performing read operations during a destage operation

InactiveUS6425050B1Minimize destage bottlenecksHigh speed accessError detection/correctionMemory adressing/allocation/relocationData accessStorage area

Disclosed is a method, system, and program for processing data access requests, such as read requests, to a storage location maintained in both a first storage, such as a cache, area and second storage area, such as a disk drive, during a destage operation. A destage operation is granted access to the storage location to destage data from the storage location in the first storage area to the second storage area. During the destage operation, a data access request is granted access to the storage location.

Owner:IBM CORP

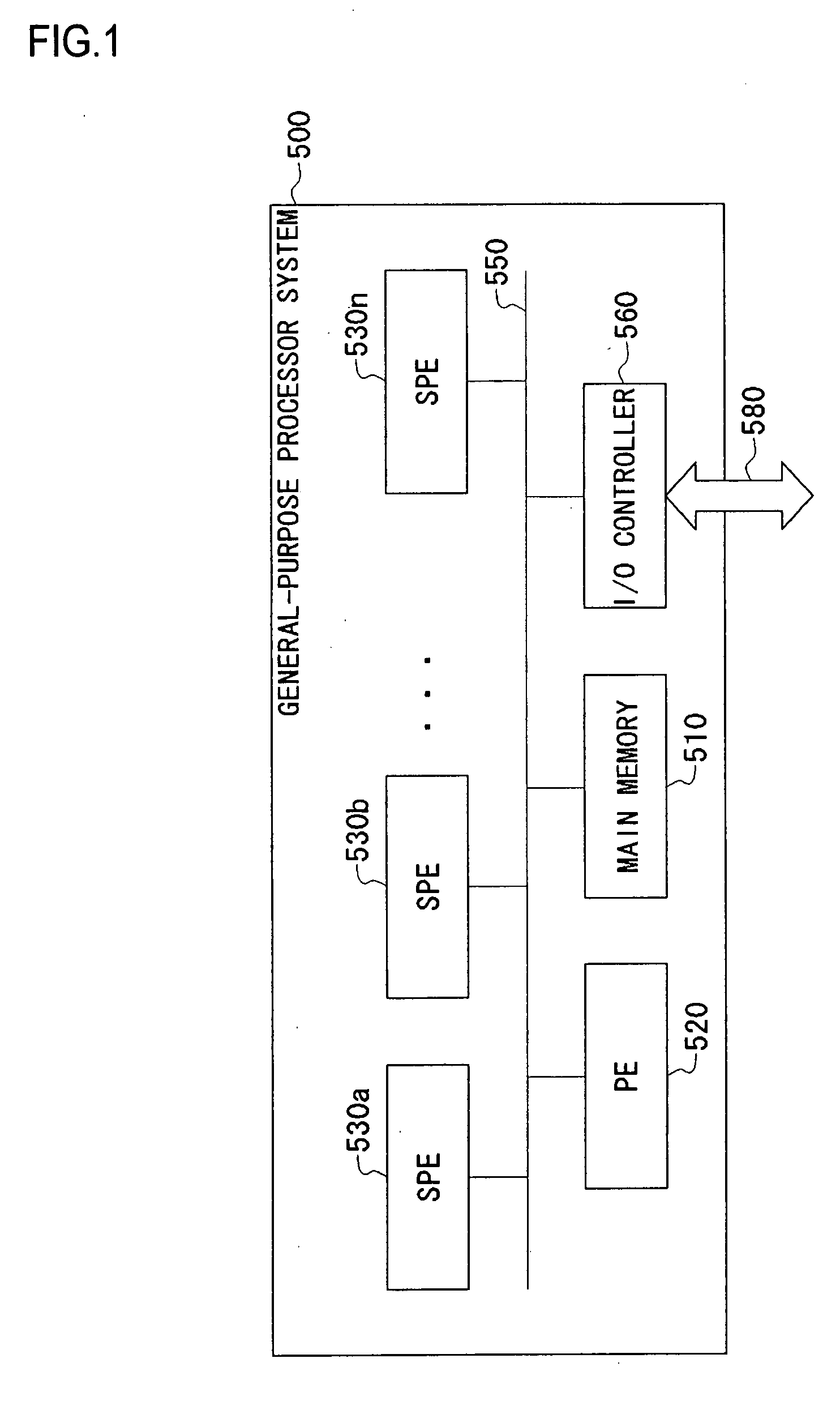

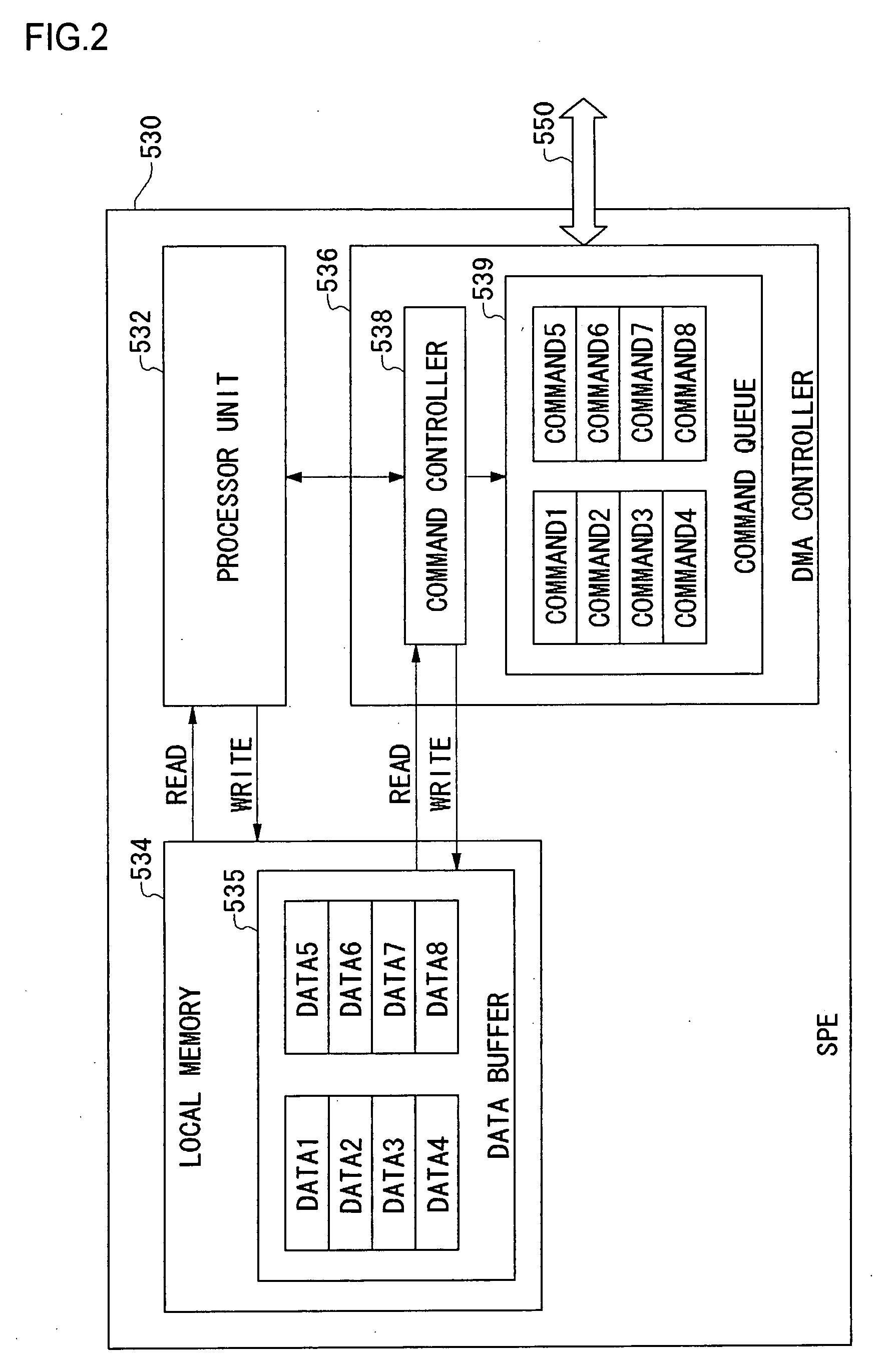

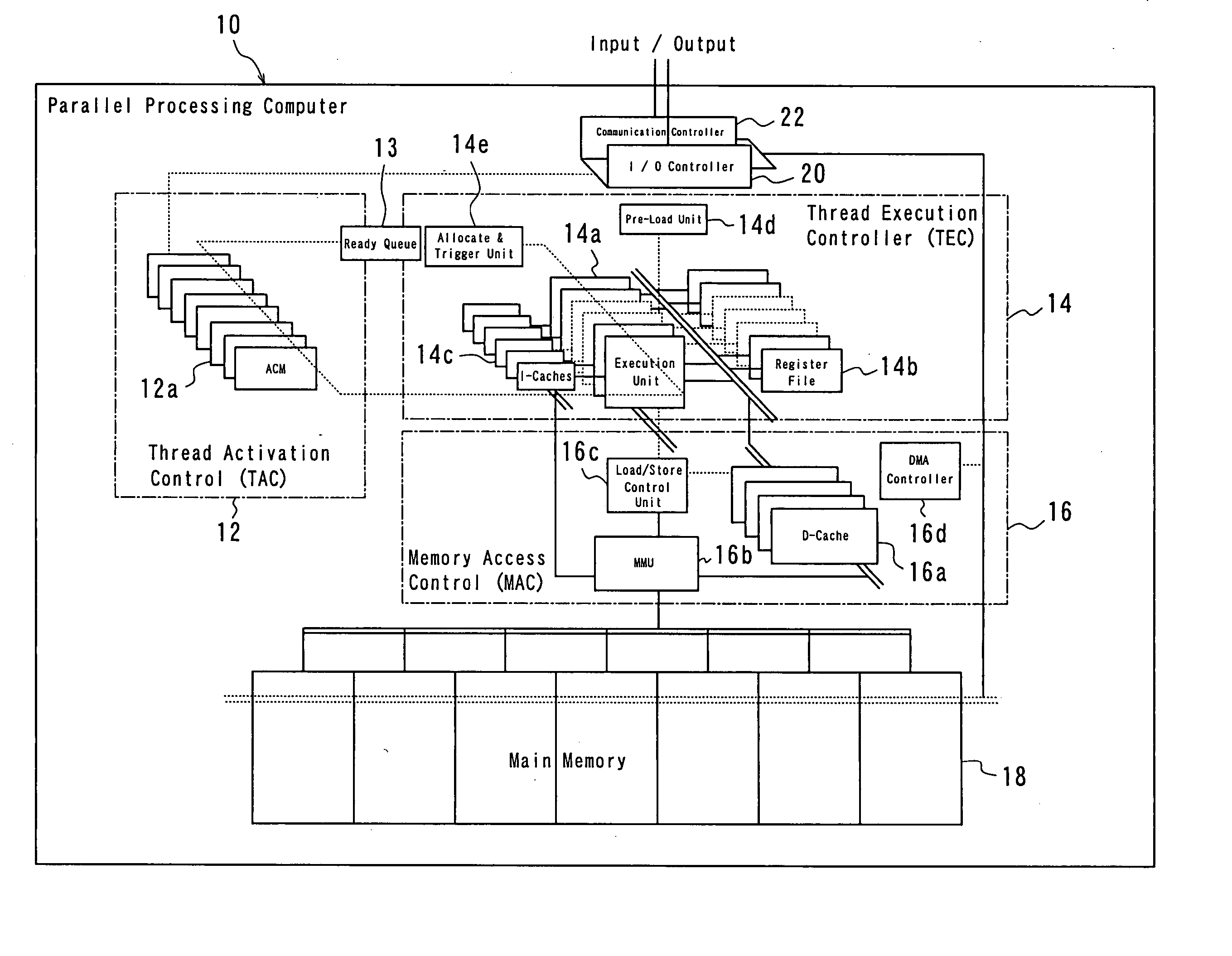

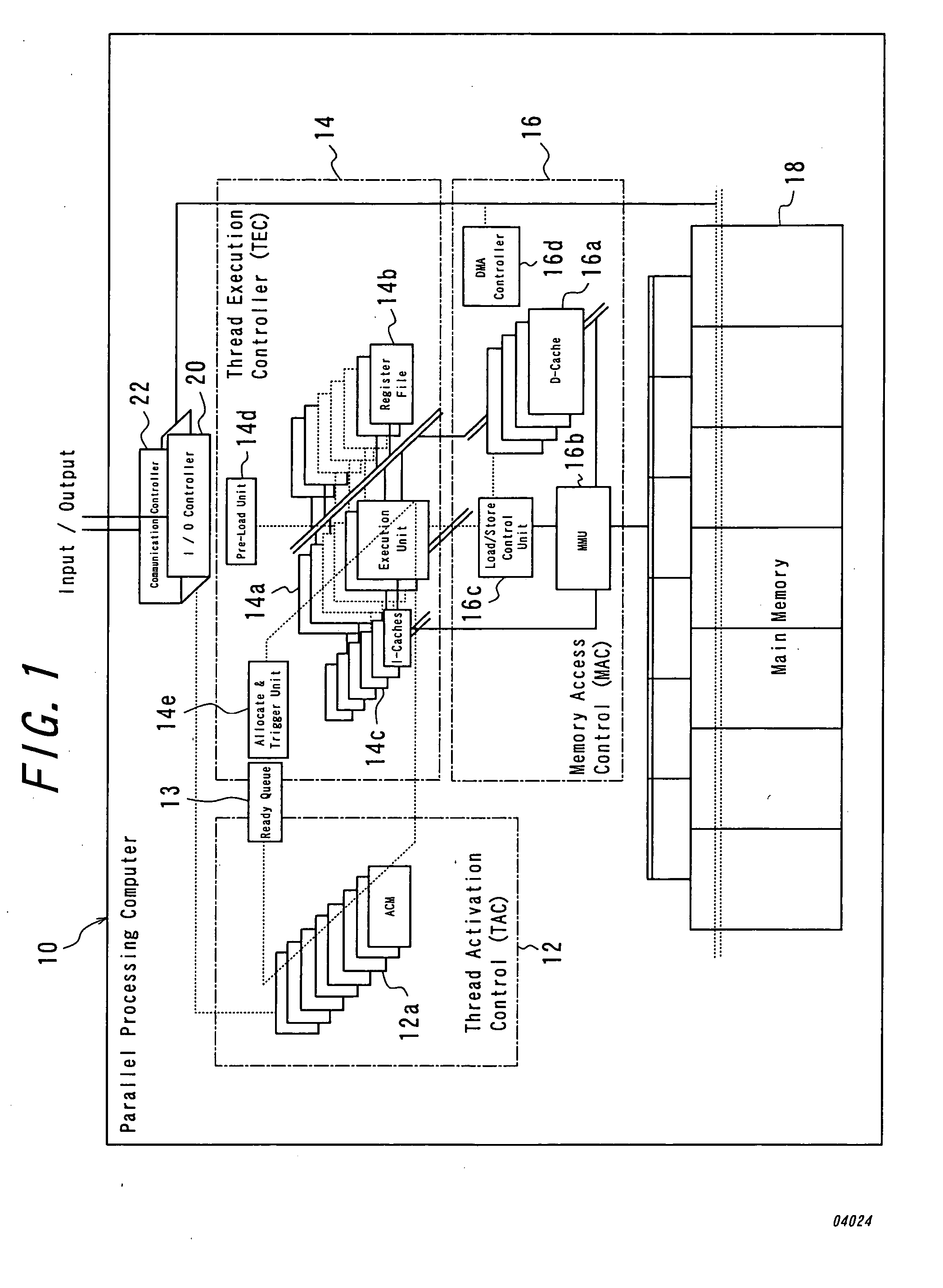

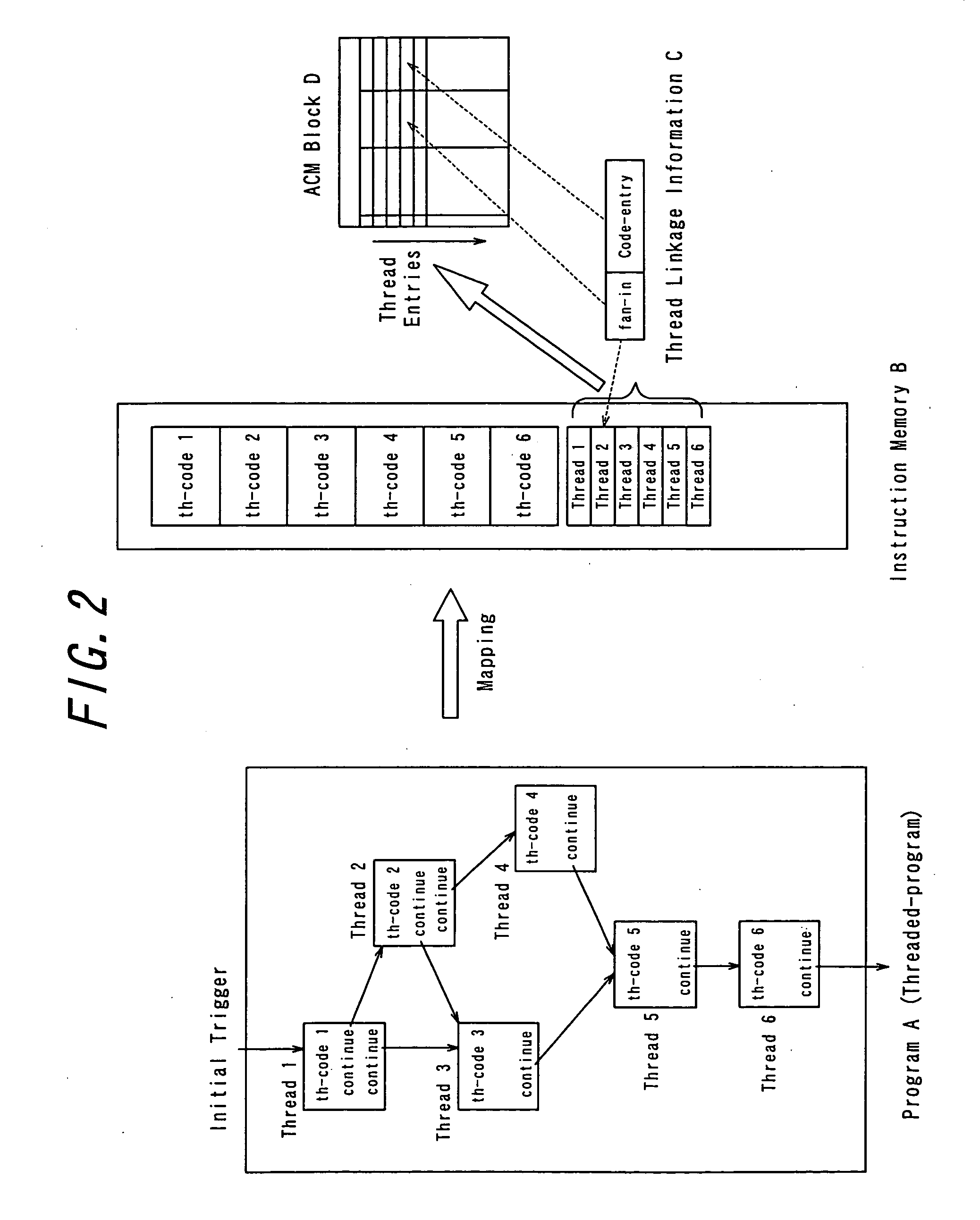

Parallel processing computer

InactiveUS20050240930A1Efficient executionImprove throughputProgram initiation/switchingRegister arrangementsProgram fragmentFile allocation

There is provided a parallel processing computer for executing a plurality of threads concurrently and in parallel. The computer includes: a thread activation controller for determining whether or not each of threads, which are exclusively executable program fragments, is ready-to-run, to put the thread determined ready-to-run into a ready thread queue as ready-to-run thread; and a thread execution controller having a pre-load unit, an EU allocation and trigger unit, a plurality of thread execution units and a plurality of register files including a plurality of registers, and the pre-load unit, prior to when each ready-to-run thread in the ready thread queue is executed, allocates a free register file of the plurality of register files to the each ready-to-run thread, to load initial data for the each ready-to-run thread into the allocated register file, and the EU allocation and trigger unit, when there is a thread execution unit in idle state of the plurality of thread execution unit, retrieves ready-to-run thread from the top of the ready thread queue, and to allocate the retrieved ready-to-run thread to the thread execution unit in idle state, and to couple the register file loaded the initial data for the ready-to-run thread with the allocated thread execution unit in idle state, and to trigger the ready-to-run thread. The plurality of thread execution units execute the triggered threads concurrently in parallel.

Owner:KYUSHU UNIV

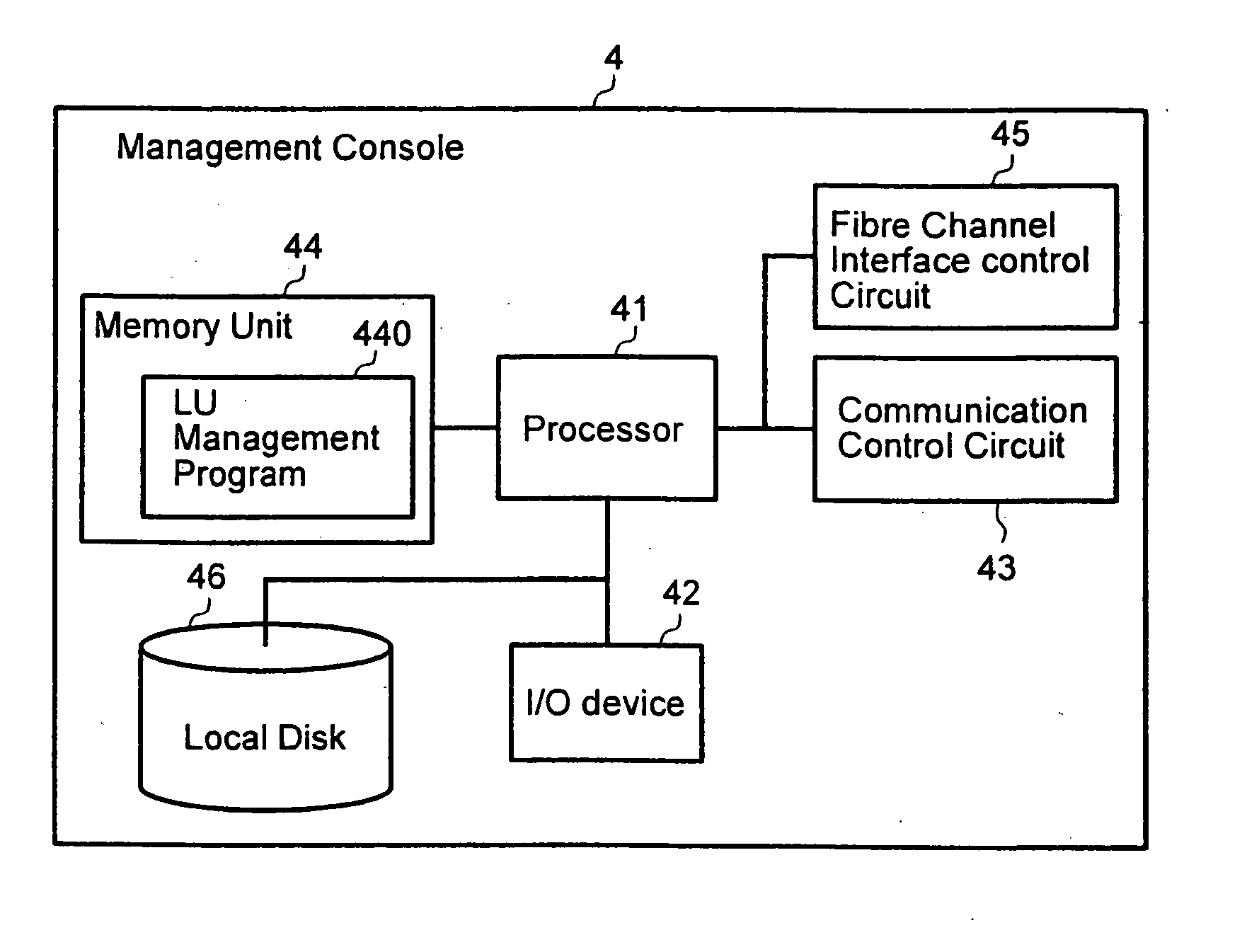

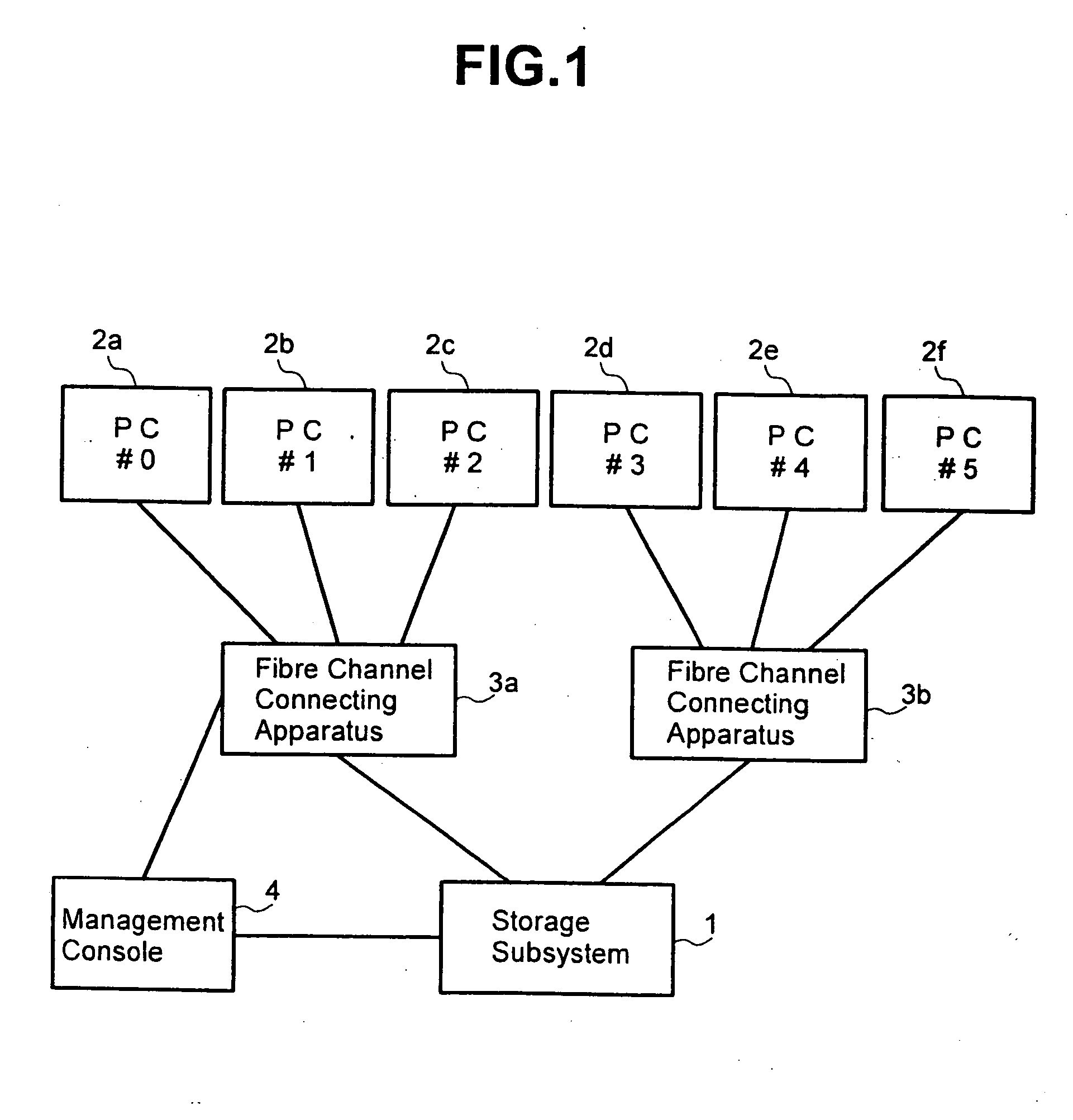

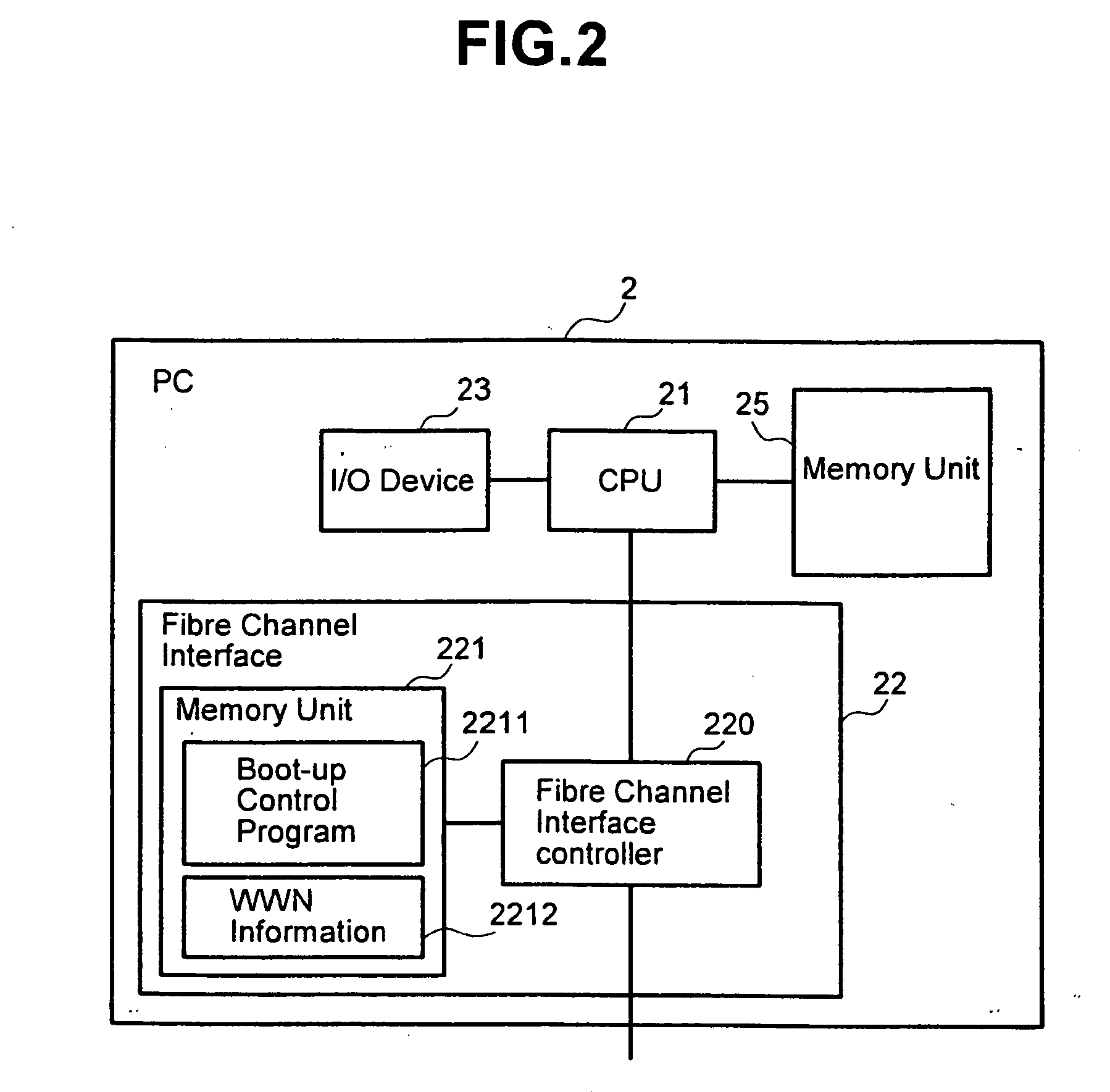

Computer system

InactiveUS20050021727A1Reduce overheadHigh speed accessInput/output to record carriersComputer security arrangementsInformation controlComputerized system

The Computer System consists of components including more than one Computer and Storage Subsystem to which more than one Computer are connected. The Storage Subsystem is equipped with more than one Storage Unit, Management Table registering information to manage Storage Units accessible by each of the Computers and Controller to control accesses by more than one Computer to more than one Storage Unit. The controller controls the accesses according to the information set in the Management Table when the Storage Unit is accessed by the Computer.

Owner:HITACHI LTD

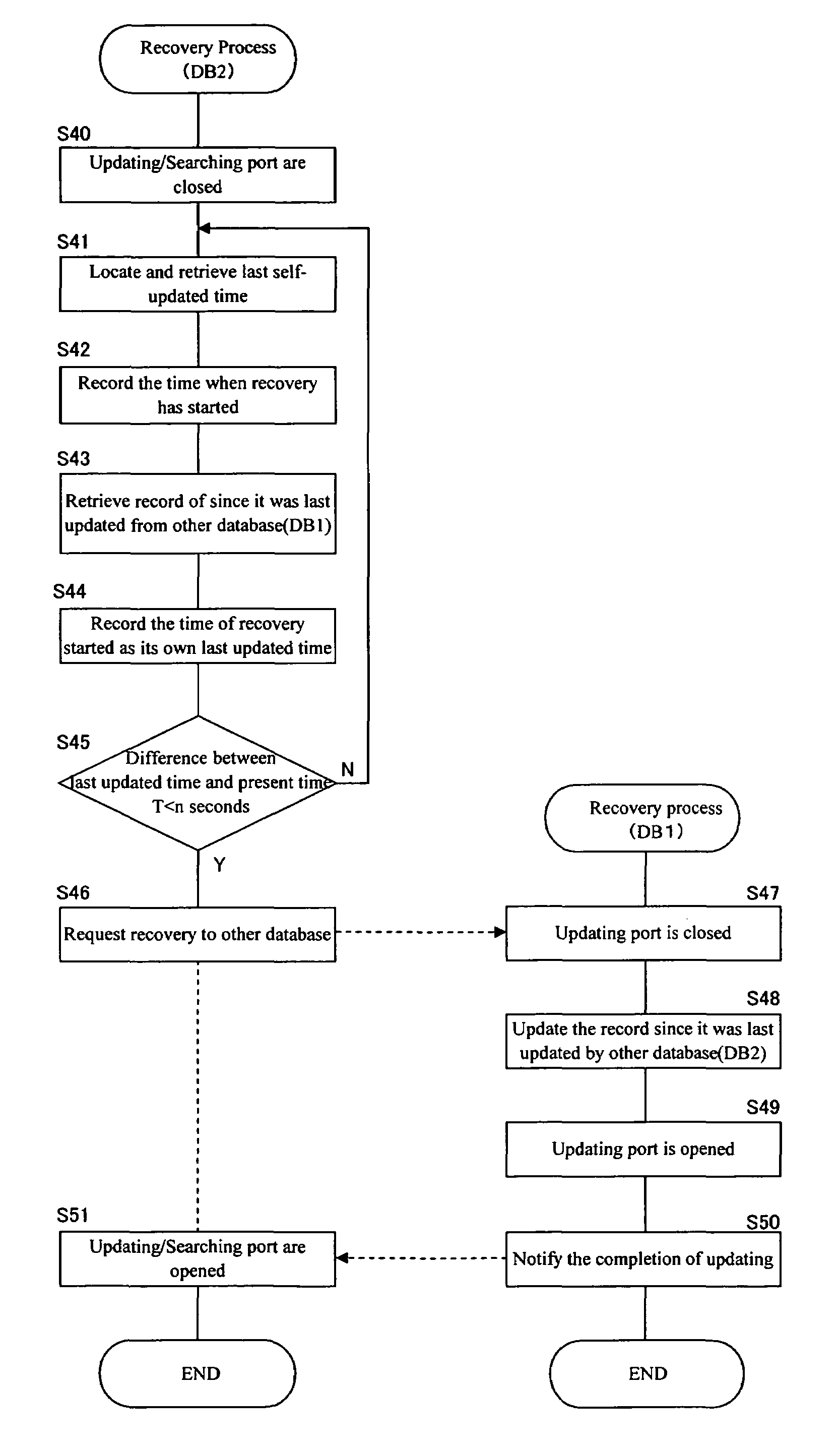

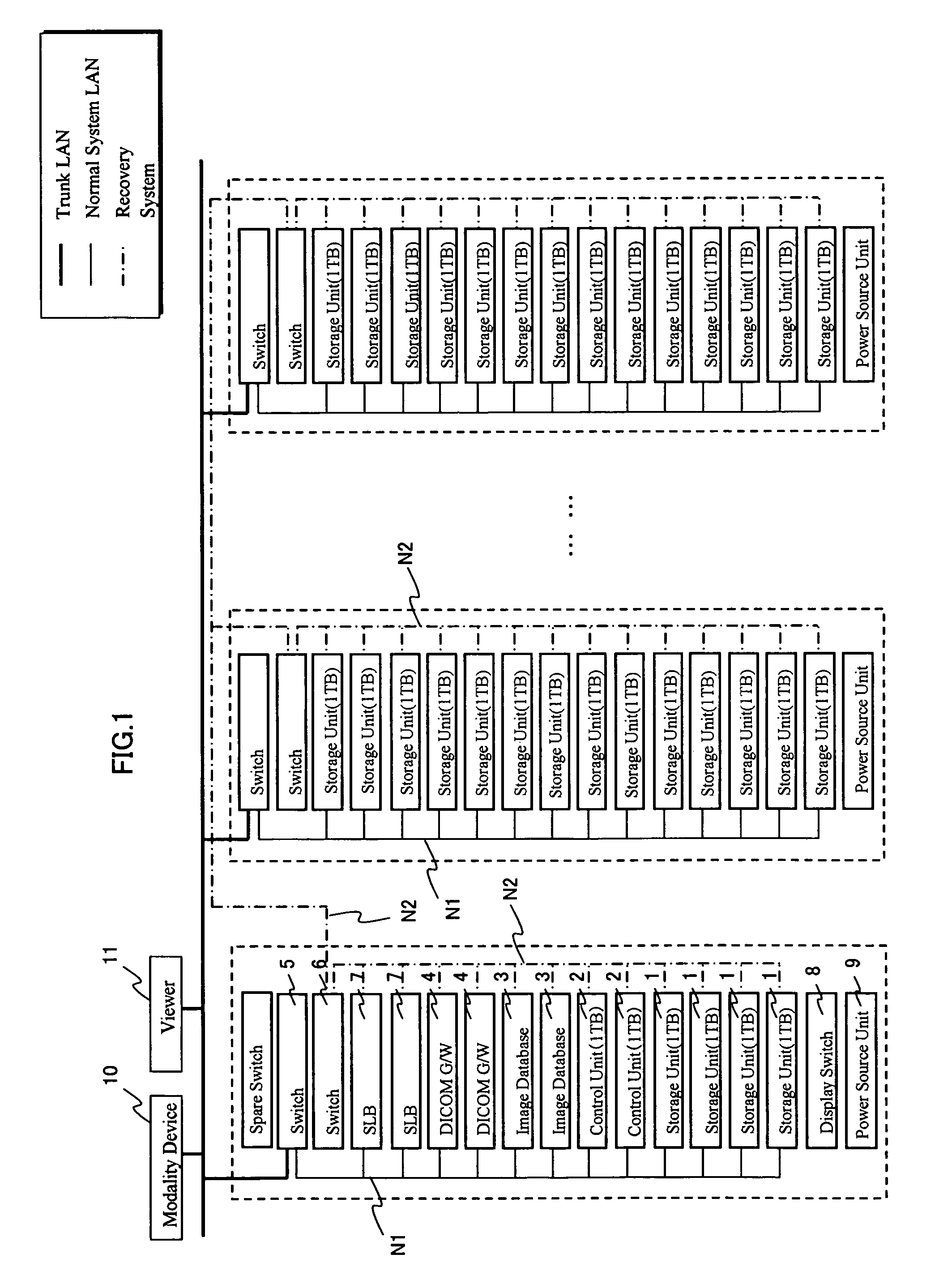

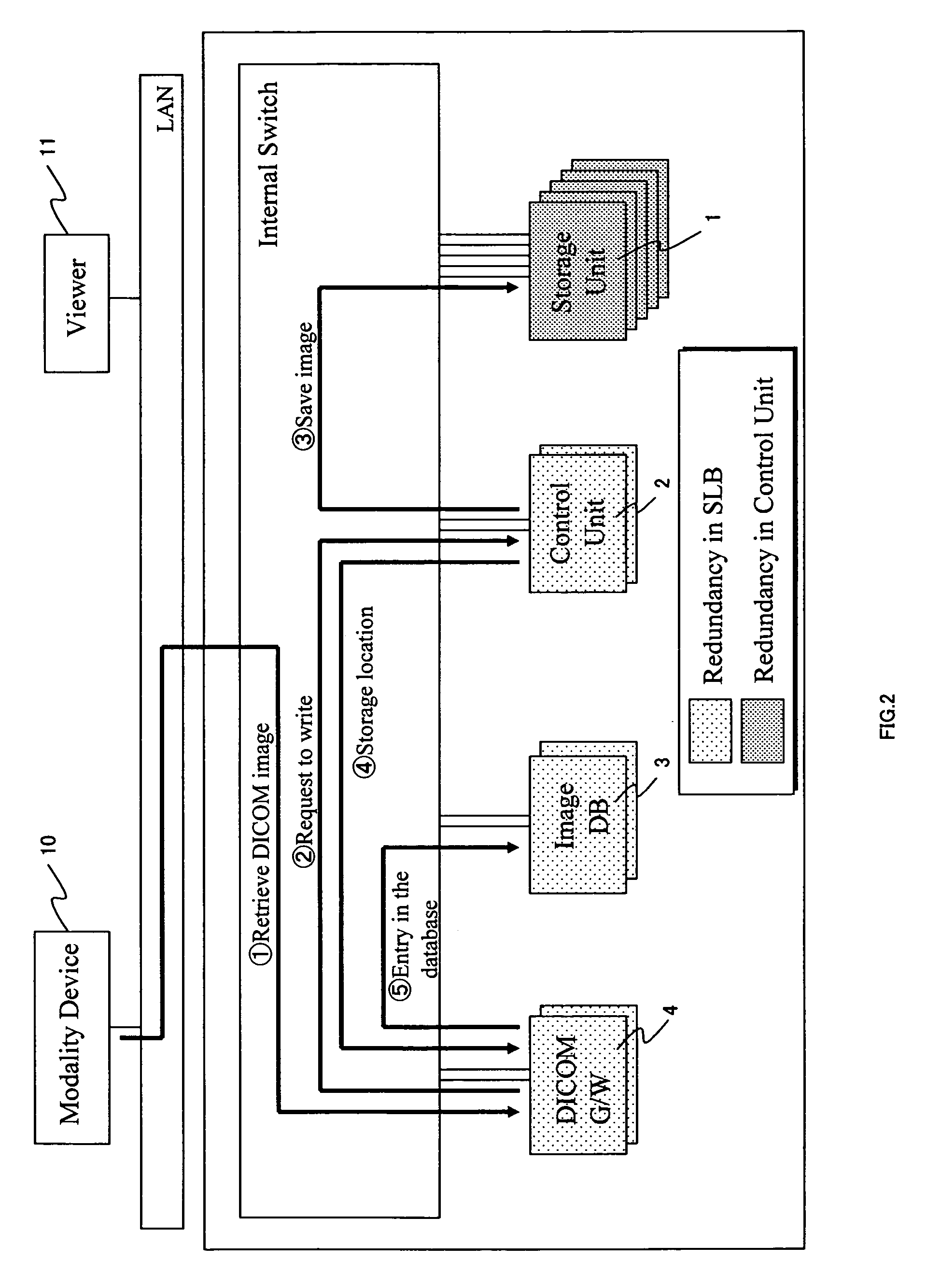

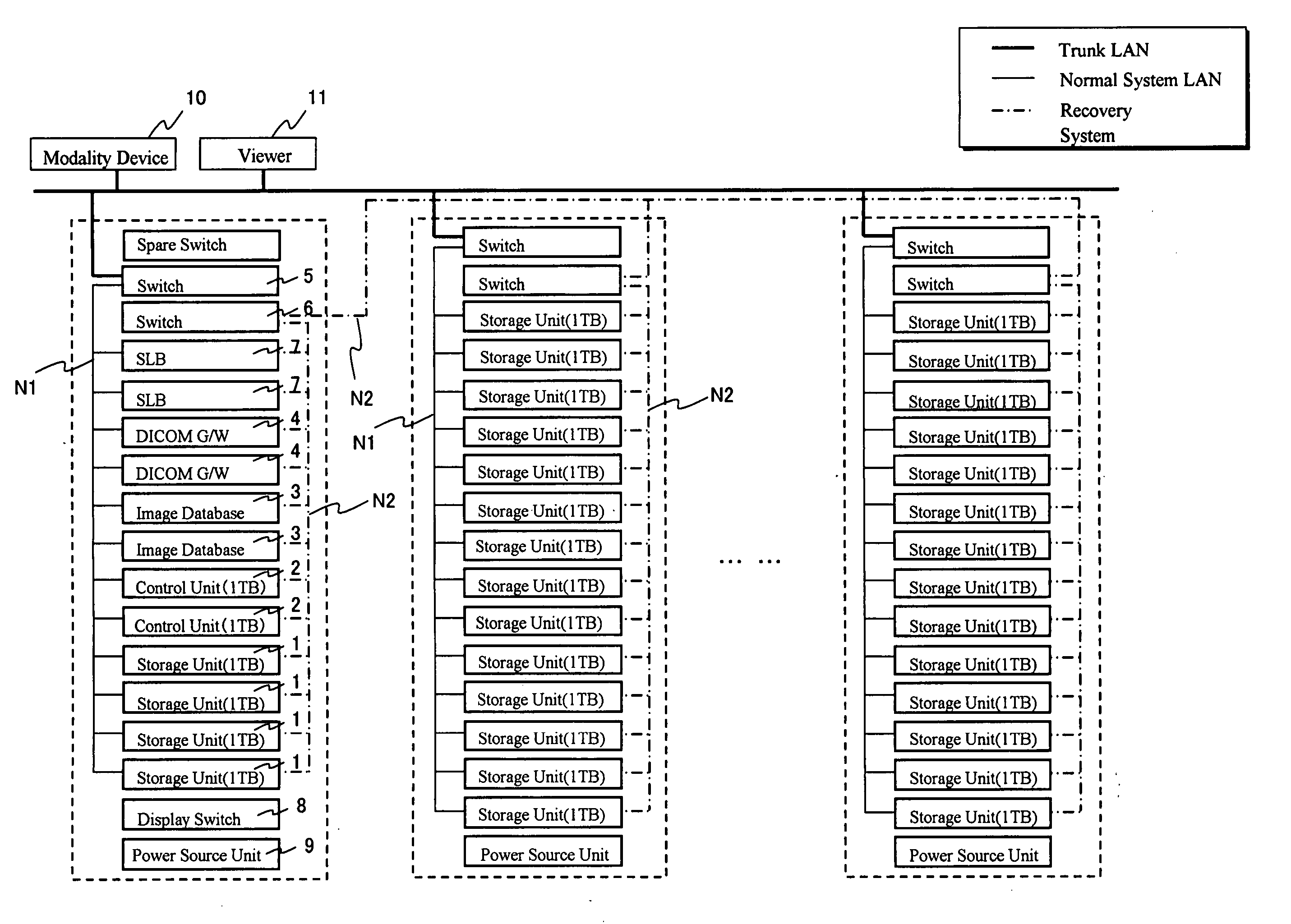

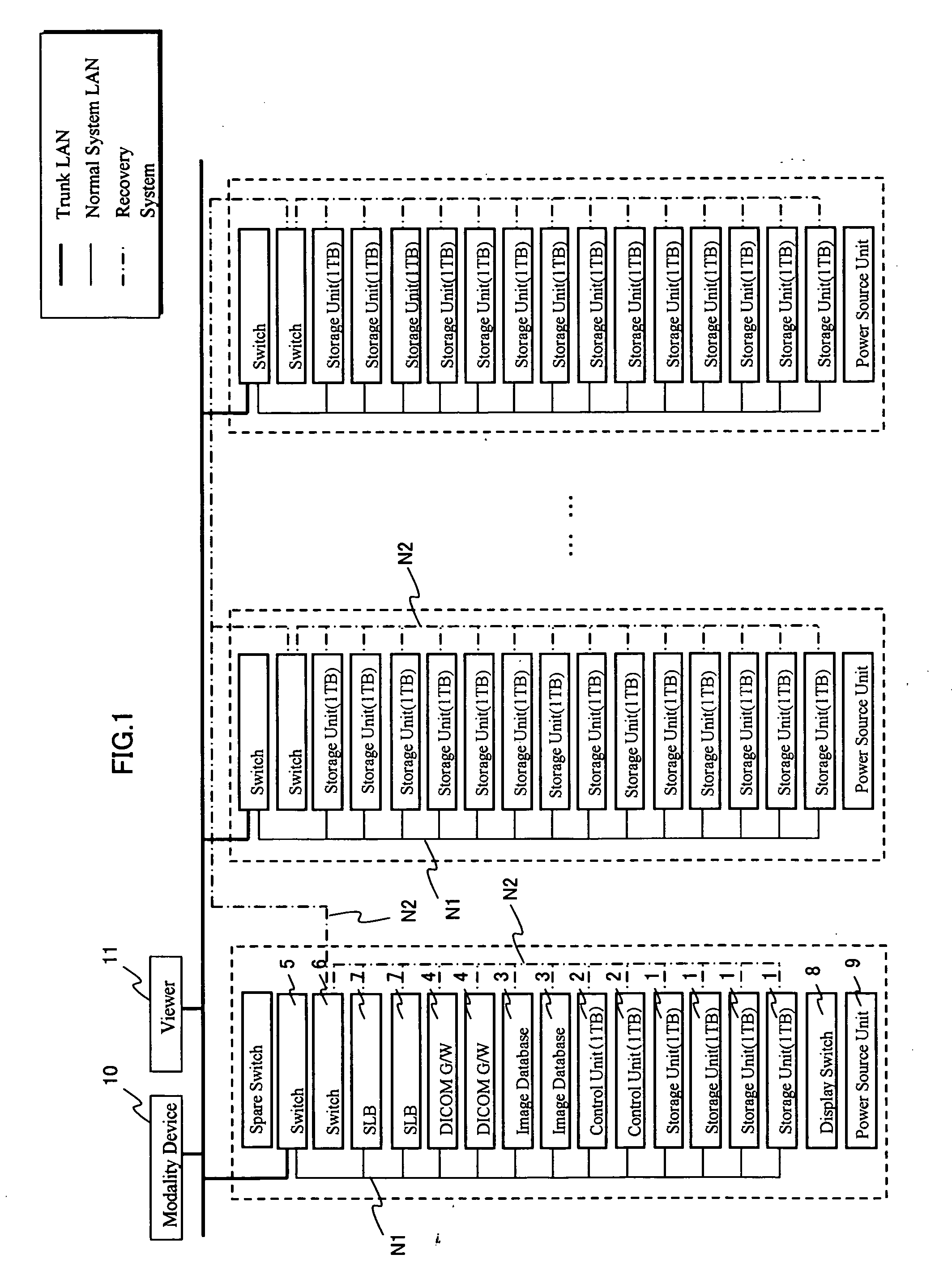

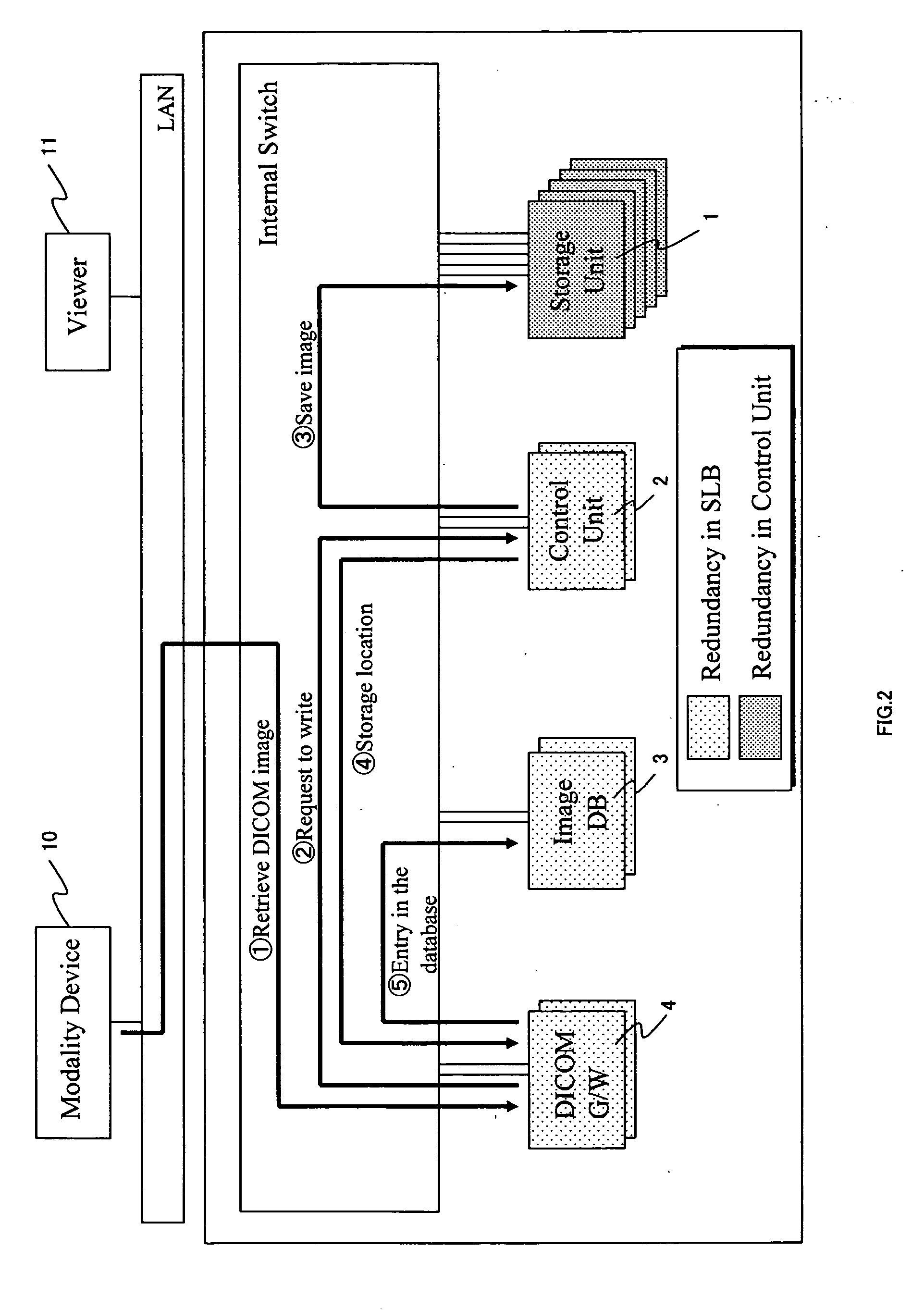

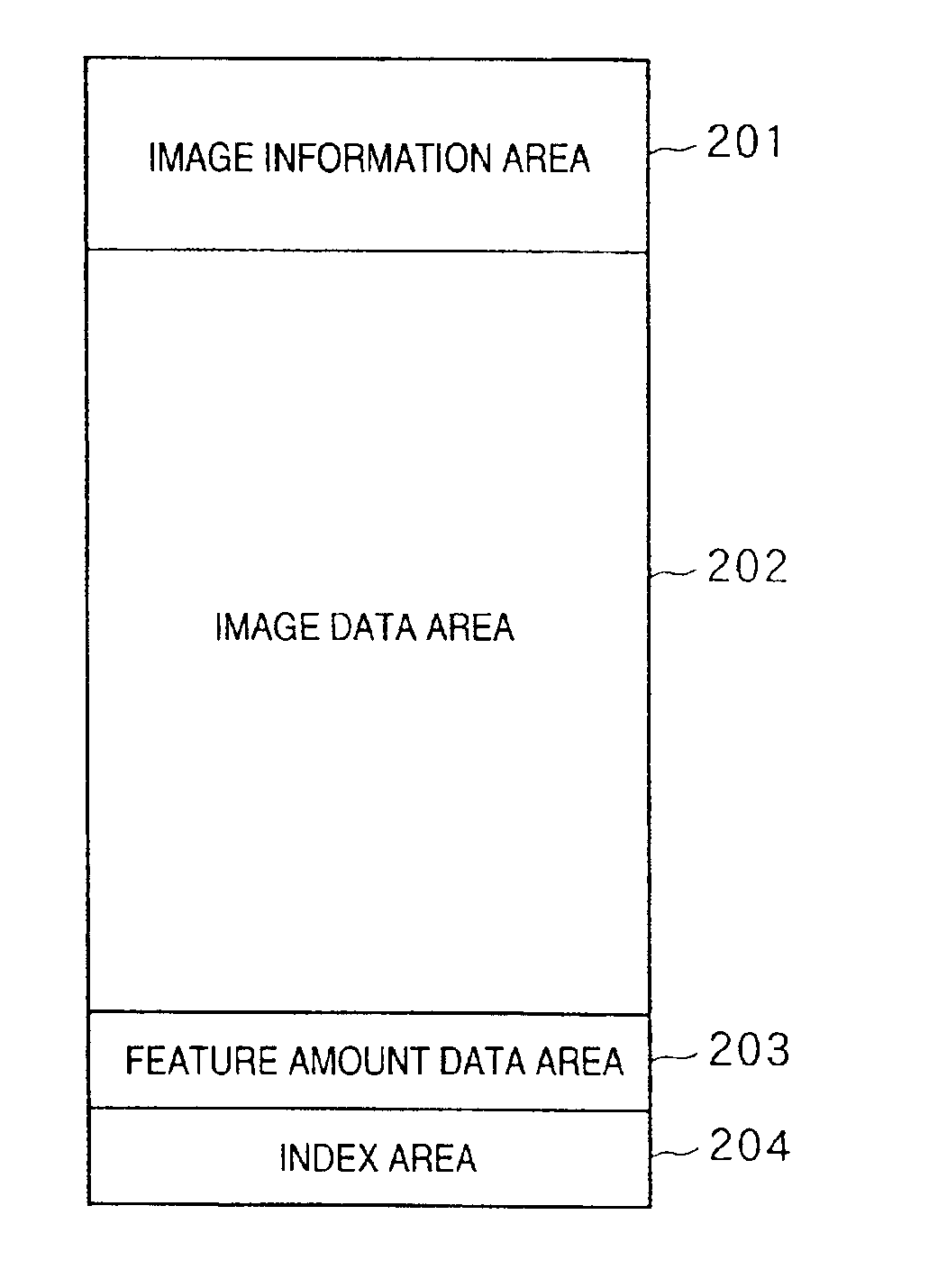

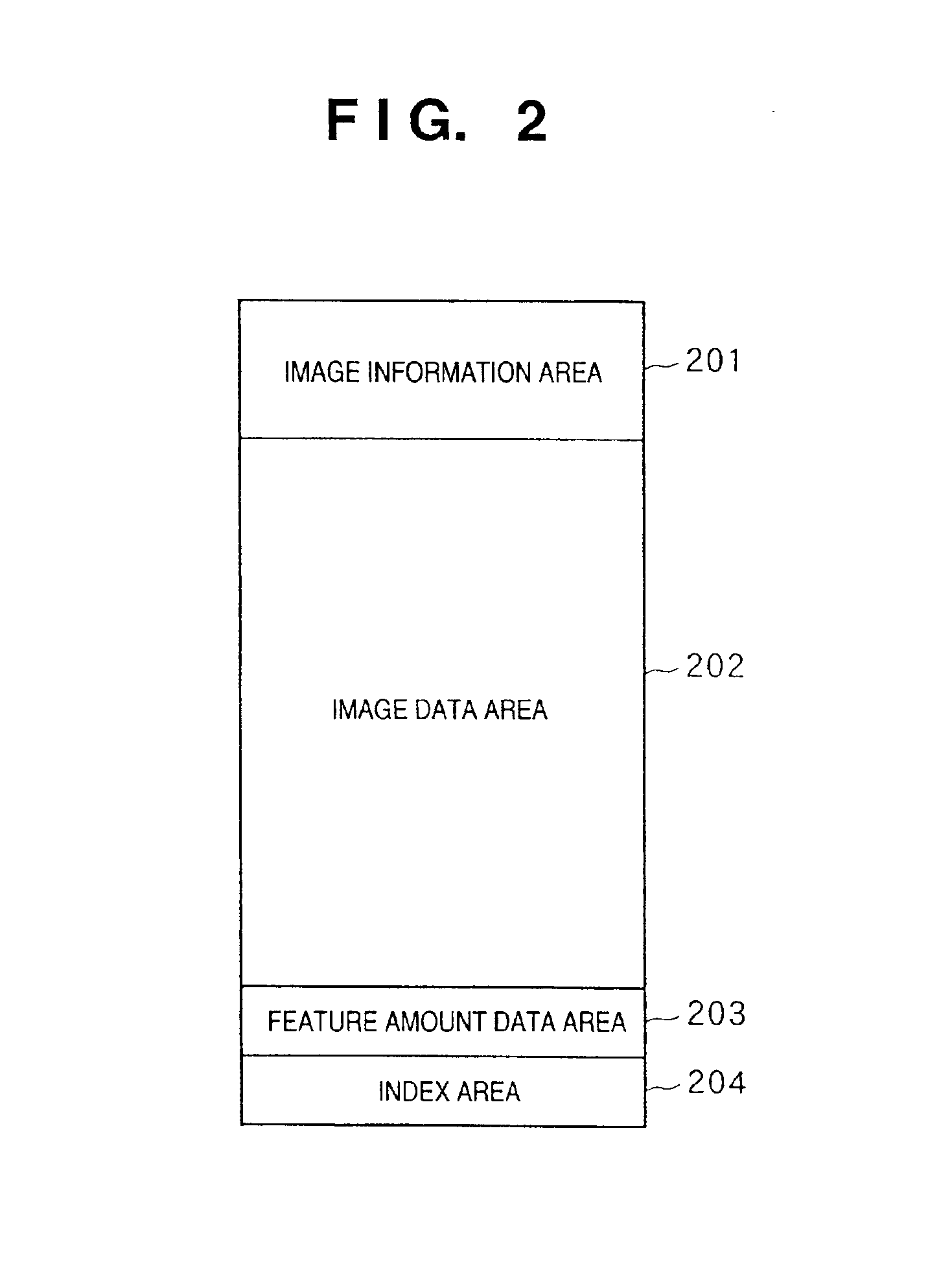

Image database system

InactiveUS7716277B2Improve reliabilityIncrease speedData processing applicationsDigital data processing detailsDICOMNetwork connection

It is an object of the present invention to provide a highly reliable image database system capable of accessing image data at high speed regardless of the increase of the image data and capable of controlling the image data as a whole. A storage unit 1, a control unit 2, an image database server 3 and a DICOM gateway 4 are subjected with each other to network connection. The storage unit 1 stores medical image data. The control unit 2 controls the storage unit. The image database server 3 stores key information associated with the image data stored and applies relay processing between an externally connected viewer and the image database server. The DICOM gateway 4 applies relay processing via a DICOM protocol between a plurality of modality devices externally connected with the image database server and the DICOM gateway. A control unit group, an image database server group, and a DICOM gateway group are constituted by providing at least a plurality of control units, a plurality of image database servers and a plurality of DICOM gateways, and a load balancer for executing load distribution control of every group is provided for every group based on header information of a request.

Owner:YAMATAKE SATOSHI

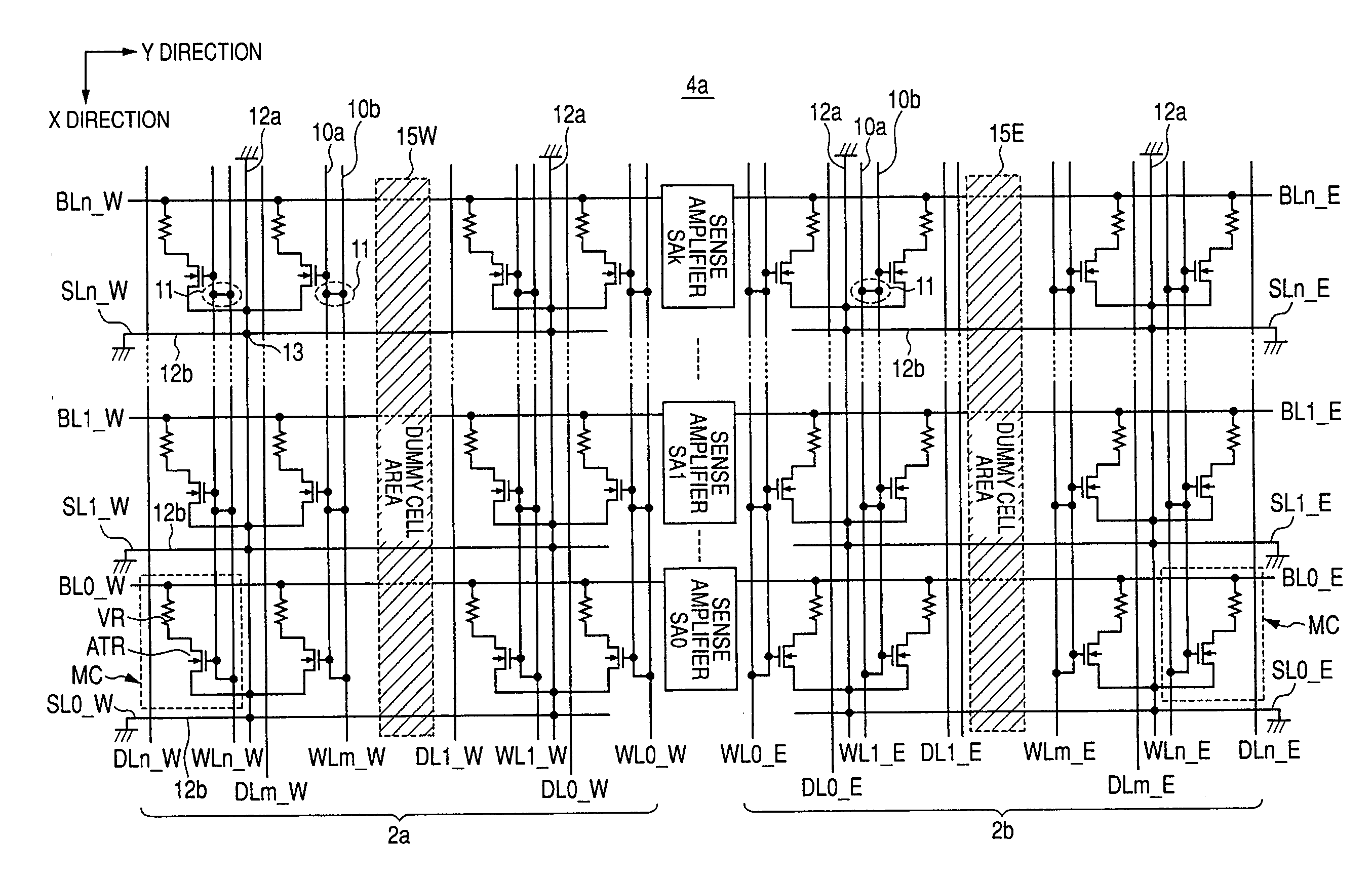

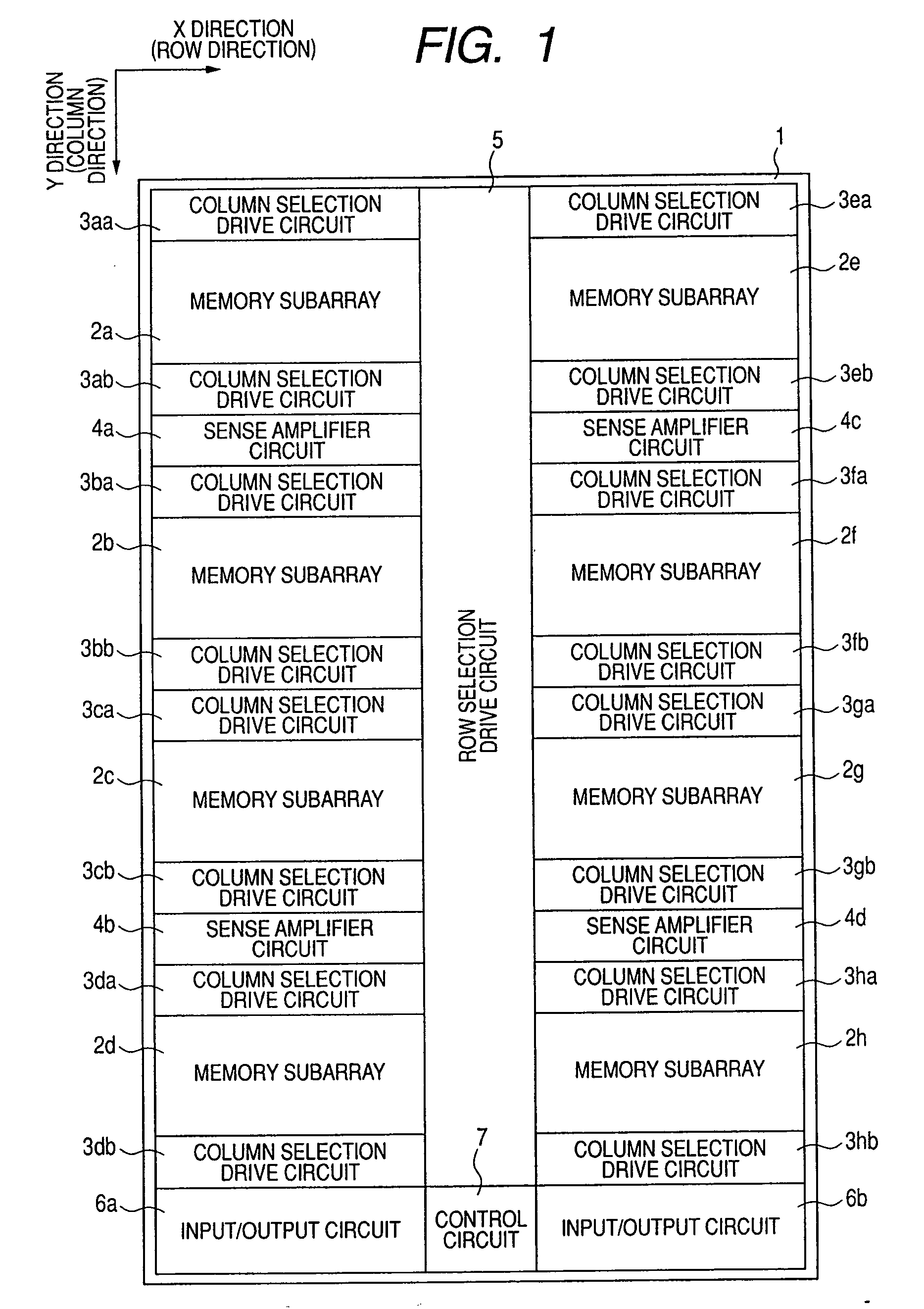

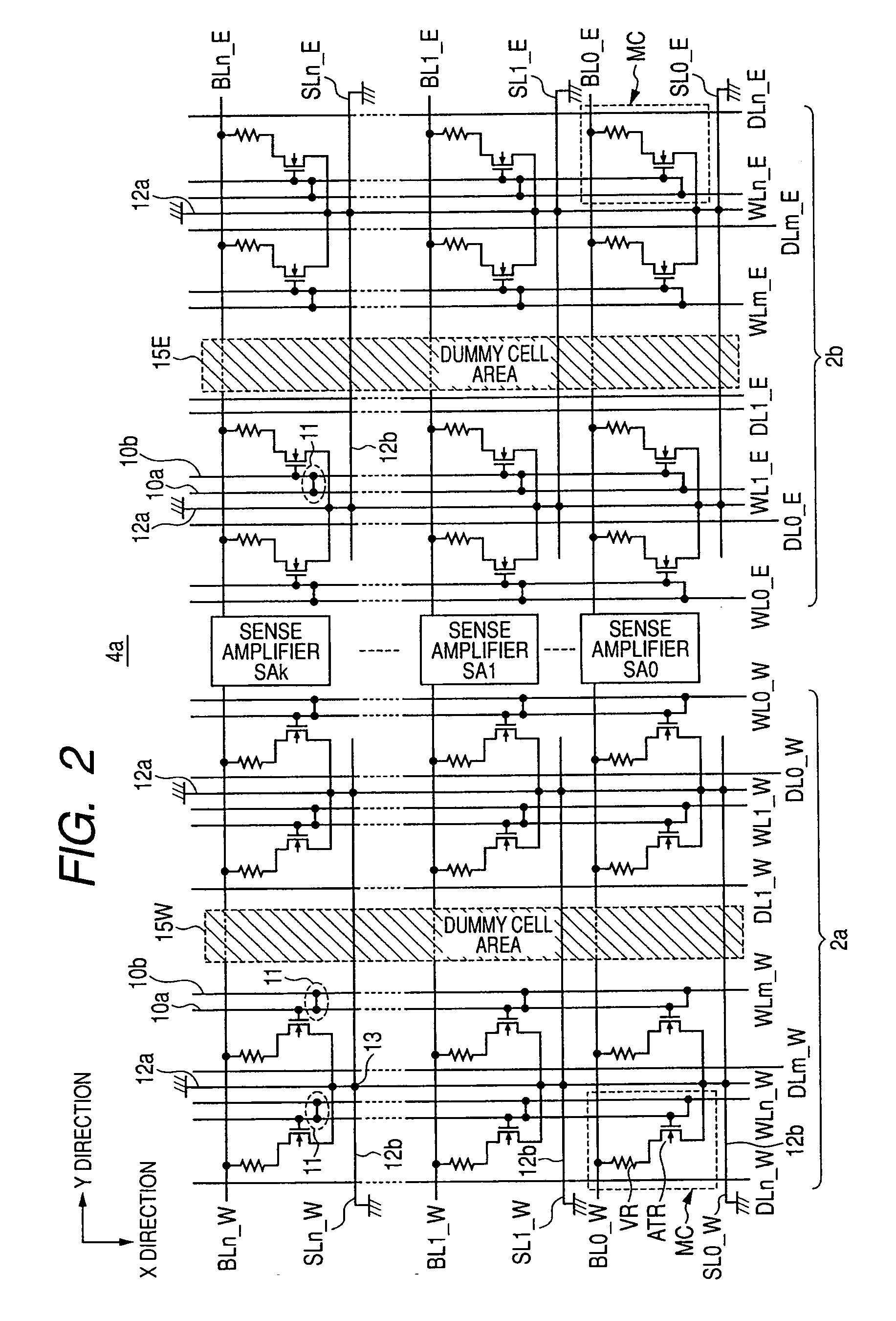

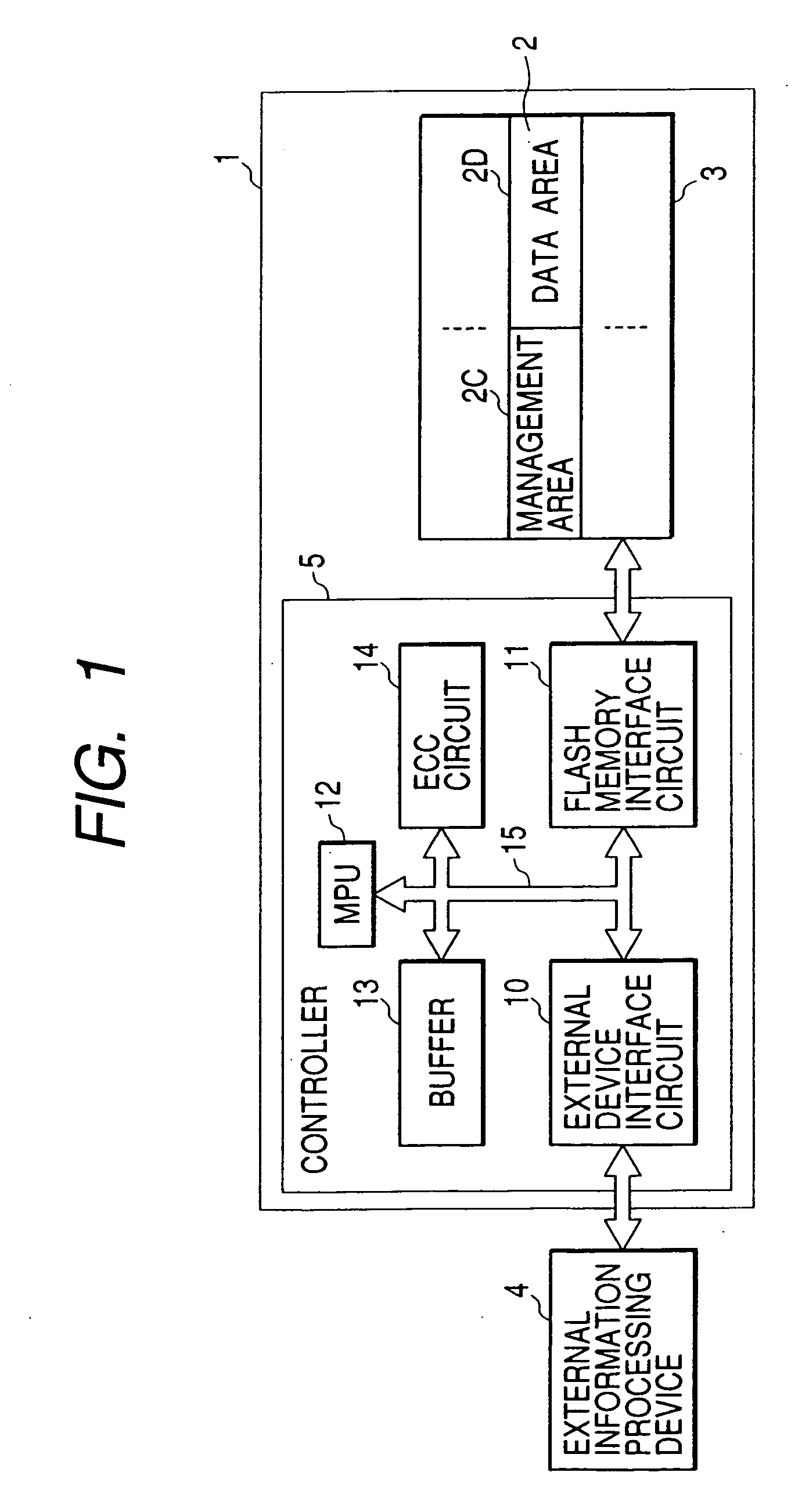

Semiconductor memory device and control method thereof

InactiveUS20100124090A1Increase speedReduce power consumptionDigital storageAudio power amplifierPhase-change memory

To provide data lines connected via column switches to a plurality of sense amplifiers and an input / output circuit that, in response to a write request, supplies pre-write data through the data line to selected phase change memory cells and then write data through the data line to the selected phase change memory cells. Thus, a pre-write operation and an actual write operation according to the write data can be performed at high speed. Because only the memory cells selected by a column address are subject to write, consumption power is reduced and lives of the memory cells are not shortened.

Owner:ELPIDA MEMORY INC

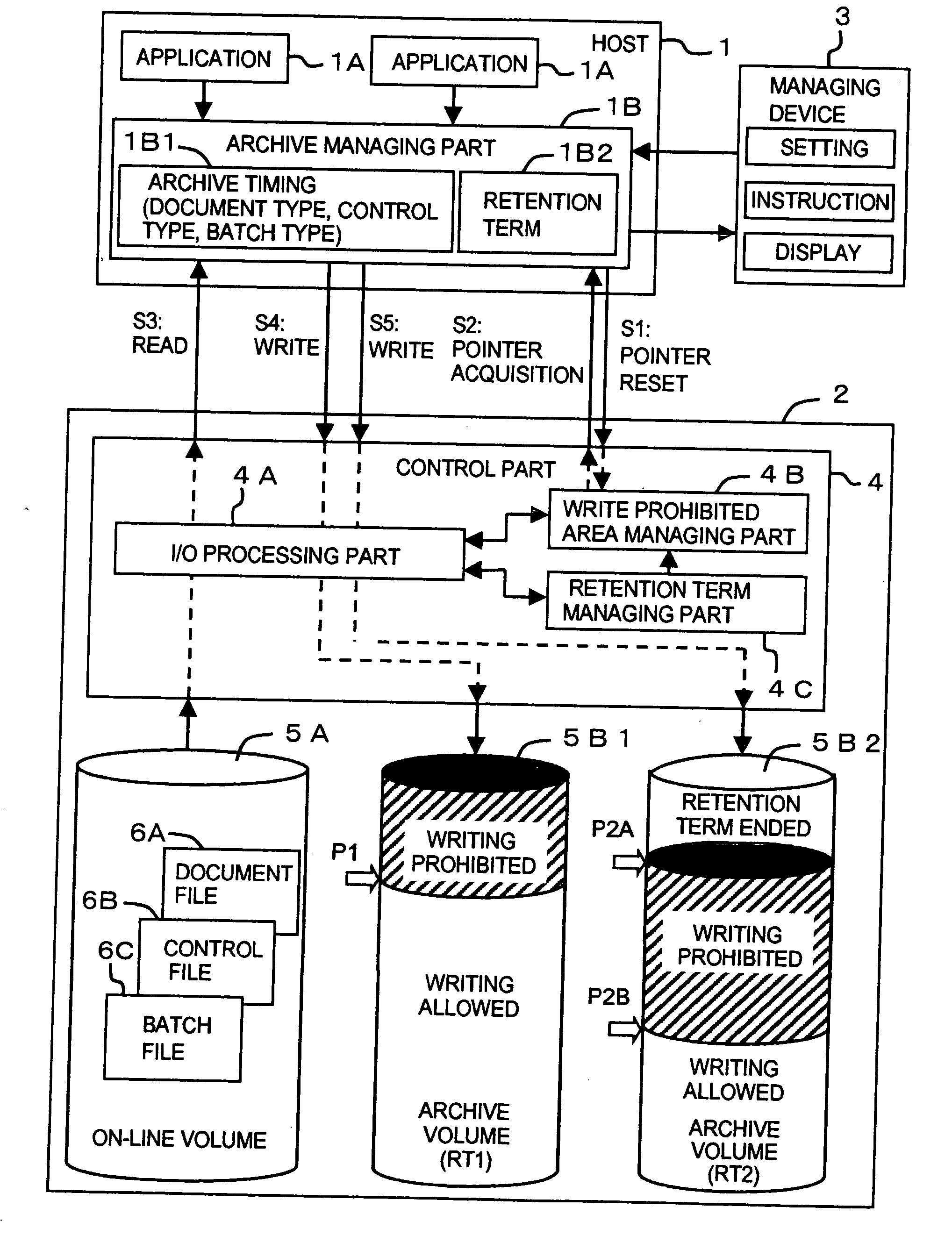

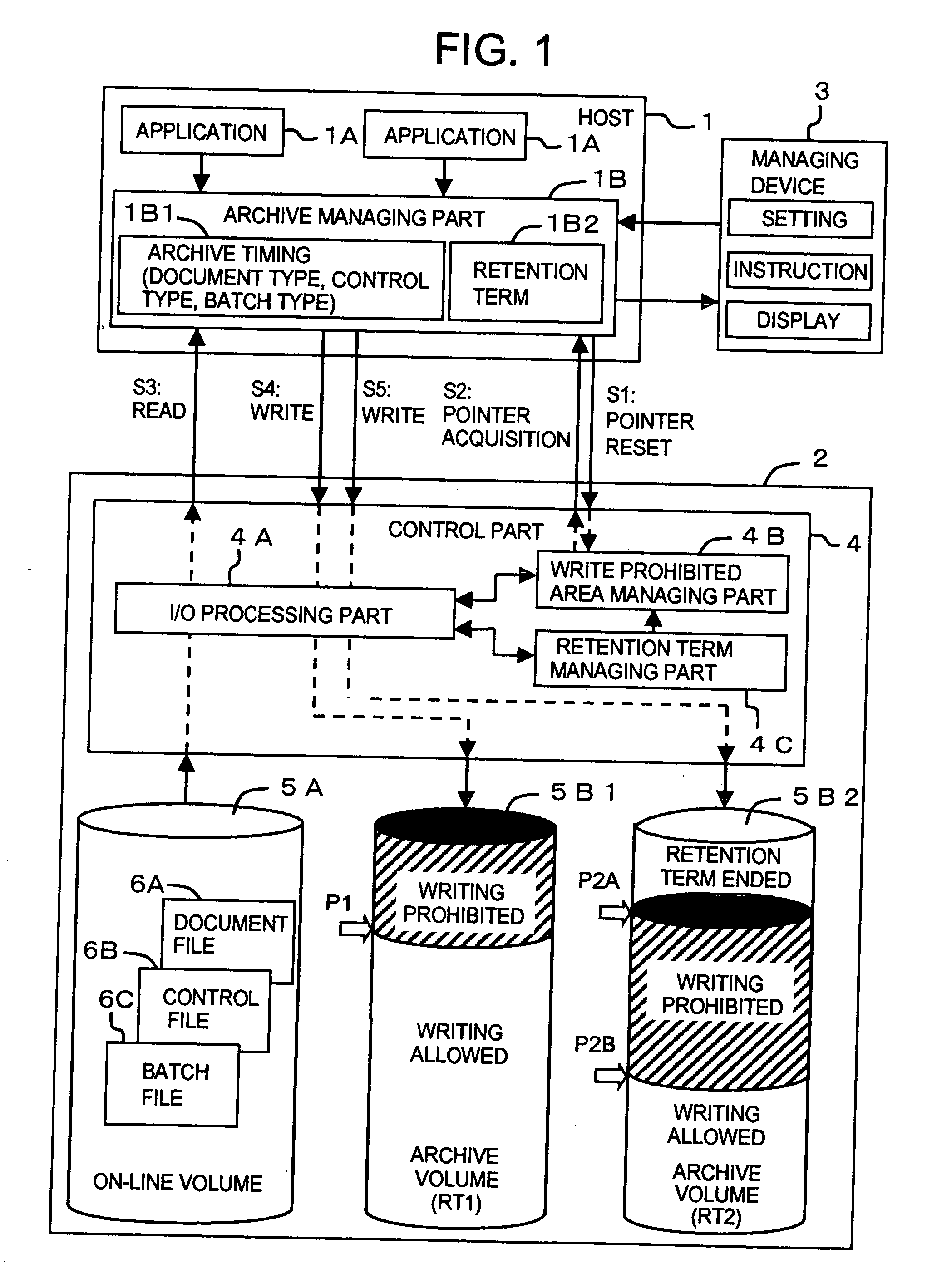

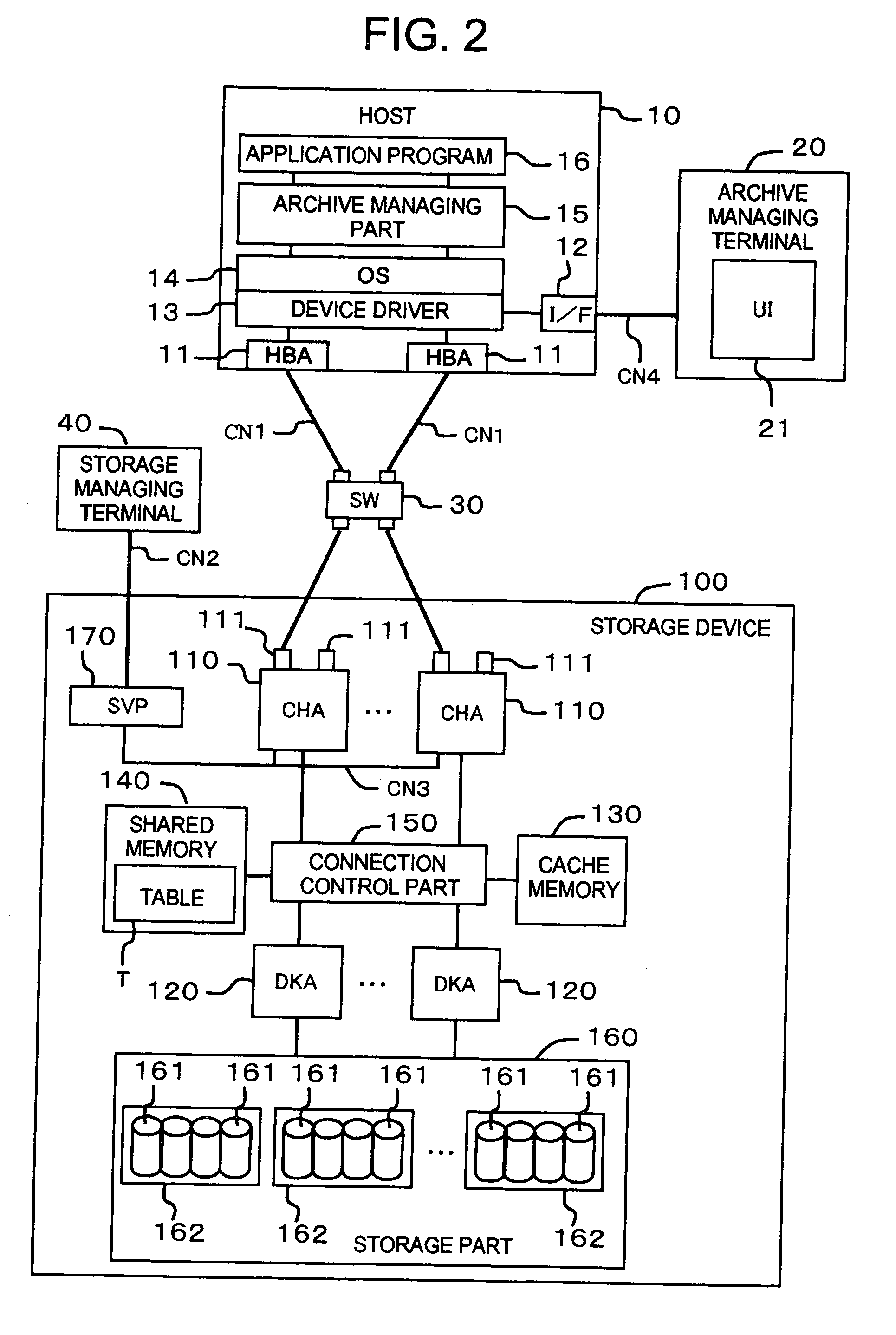

Storage system and storage device archive control method

InactiveUS20060179087A1Avoid dataImprove future data utilizabilityDigital data protectionInternal/peripheral component protectionRetention periodEngineering

The present invention performs appropriate archive management using a device that allows random access. An archive managing part 1B reads out files stored in an on-line volume 5A at a timing determined by the respective file type, and stores these files in a specified volume among archive volumes 5B1 and 5B2. A retention term is designated for each set of file data, and respective retention terms are also set for the respective volumes 5B1 and 5B2. The file data is stored in a volume having a retention term that matches the retention term of the file data. The respective volumes 5B1 and 5B2 are set in a device that allows random access such as a hard disk or the like. The areas in which data is written into the respective volumes 5B1 and 5B2 are managed as write prohibited areas by means of pointers P. As a result, the respective volumes 5B1 and 5B2 are used as a so-called WORM device.

Owner:HITACHI LTD

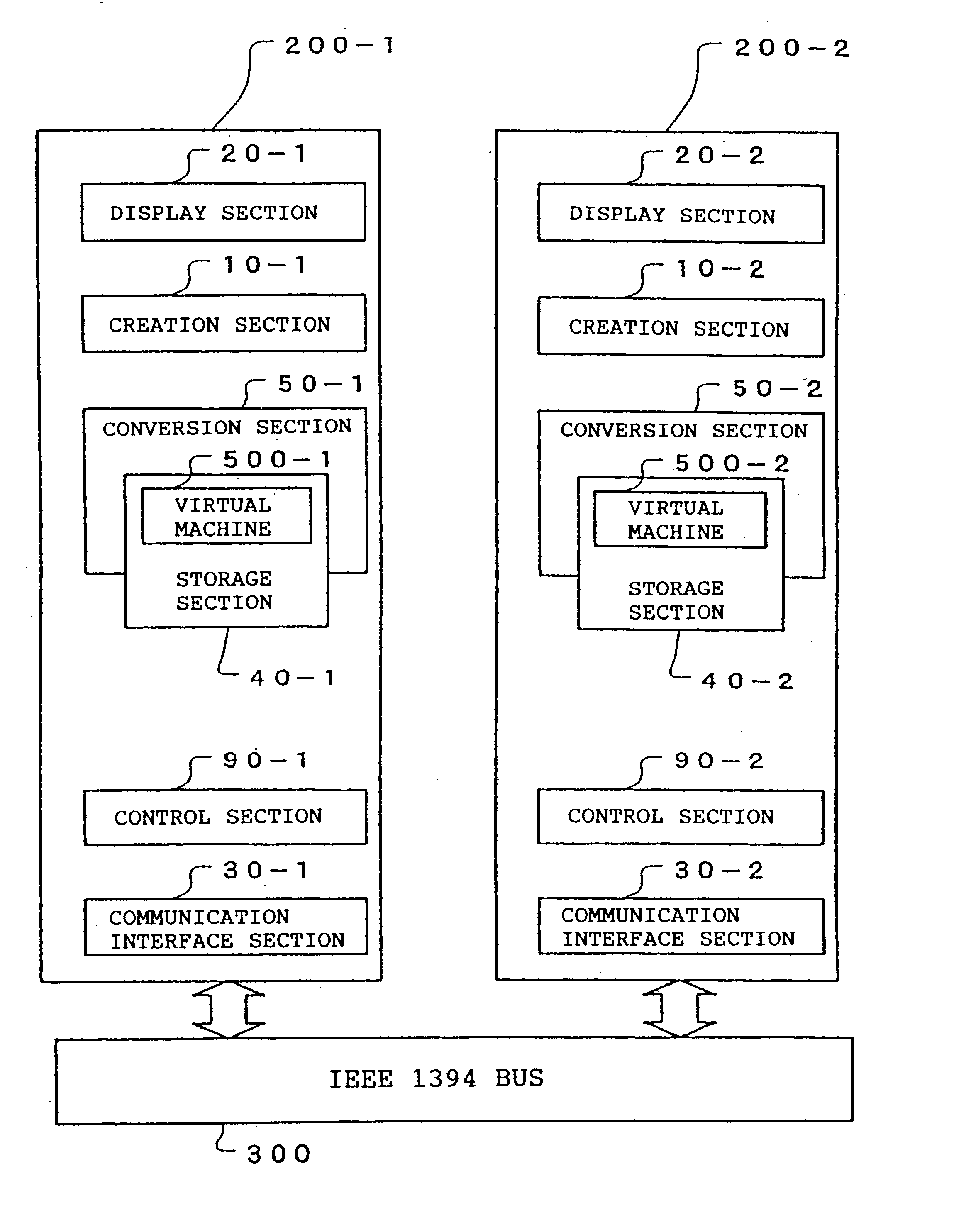

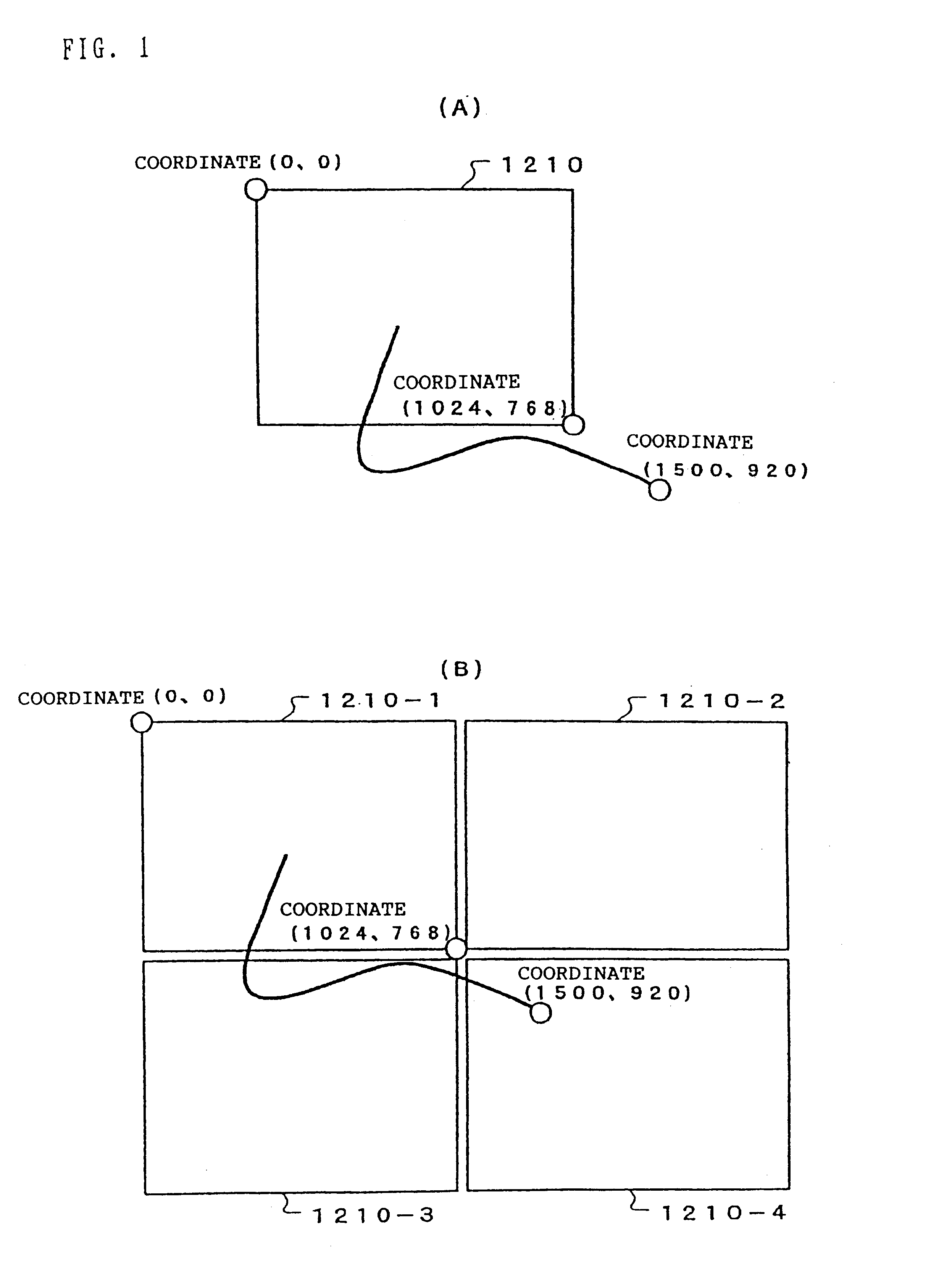

Image display system and information storage medium

InactiveUS6839061B1Improve processing speedHigh speed accessCosmonautic condition simulationsHybrid switching systemsCommunication interfaceDisplay device

An image display system transmits and receives supplied data which can be converted by a virtual machine among plural processing devices which are connected via a transmission line, and creates and displays an image. At least two processing devices among the plural processing devices each includes an image display device. At least one of the image display devices includes a conversion device, in which a virtual machine is provided, that converts the supplied data into a data format in which an image can be displayed, a communication interface section that receives the supplied data from another processing device, and a storage device in which created images are stored and which can be accessed from another processing device via the communication interface section. Each of the at least one of the image display device and the other image display device reads some of the images from the storage device and display the images in a shared manner, the other image display device having the conversion device and the communication interface section.

Owner:SEIKO EPSON CORP

Multiple input/multiple output communication method based on distributed transmission sources

InactiveUS7809073B2Increase downlink speedHigh speed accessSite diversitySpatial transmit diversityData streamMultipath channels

Owner:UTSTARCOM TELECOM CO LTD

Magnetic memory device

InactiveUS20100118581A1Reduce resistanceEfficient disposalDigital storageMagnetic memoryBoundary region

The present invention provides a magnetic memory device capable of providing high-speed access without increasing an array area. Gate word lines are respectively linearly disposed between source impurity regions and drain impurity regions within a memory cell array area. Gate word line protrusions are respectively provided at boundary regions of memory cell forming regions. Contacts relative to the gate word line protrusions are respectively provided at boundary regions of memory cells at adjacent columns. The drain impurity regions are respectively disposed with being shifted from the centers of the memory cell forming regions in such a manner that spaces between the drain impurity regions become large in the regions in which the protrusions are disposed.

Owner:RENESAS ELECTRONICS CORP

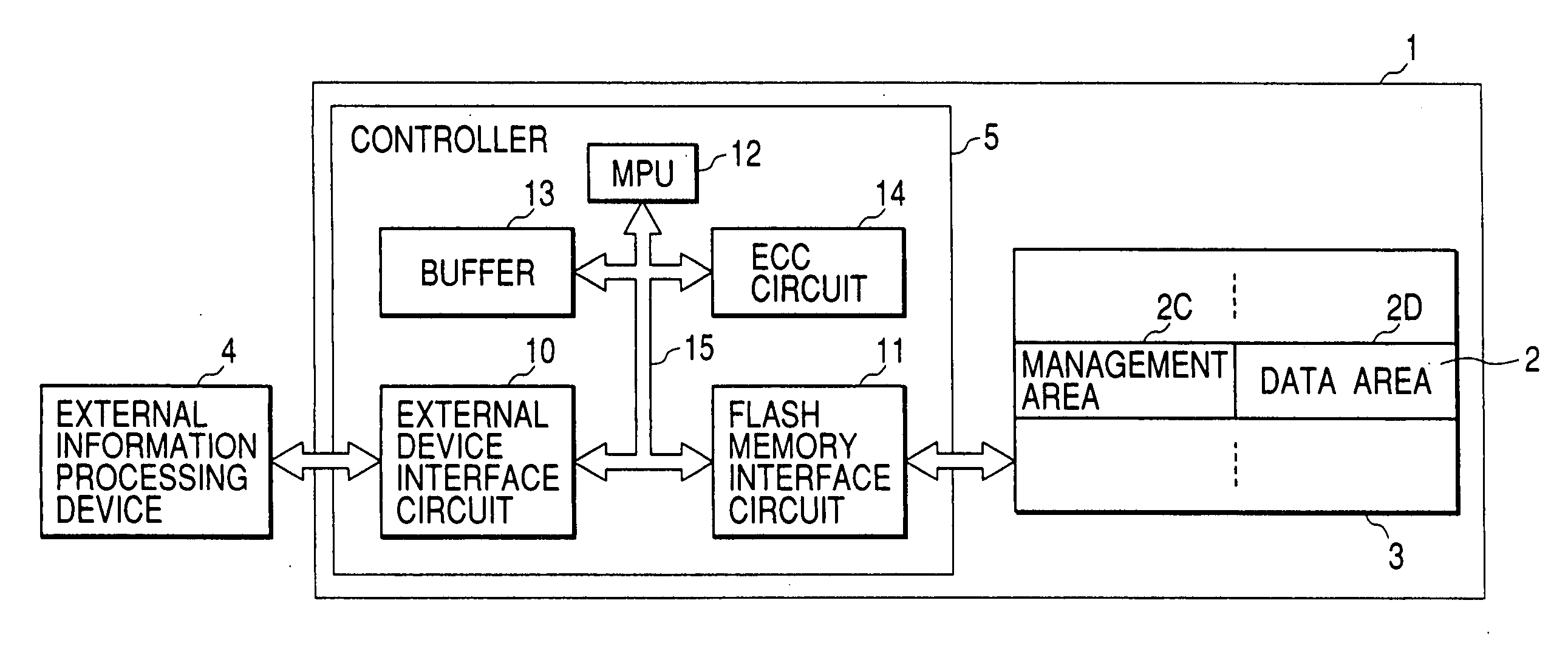

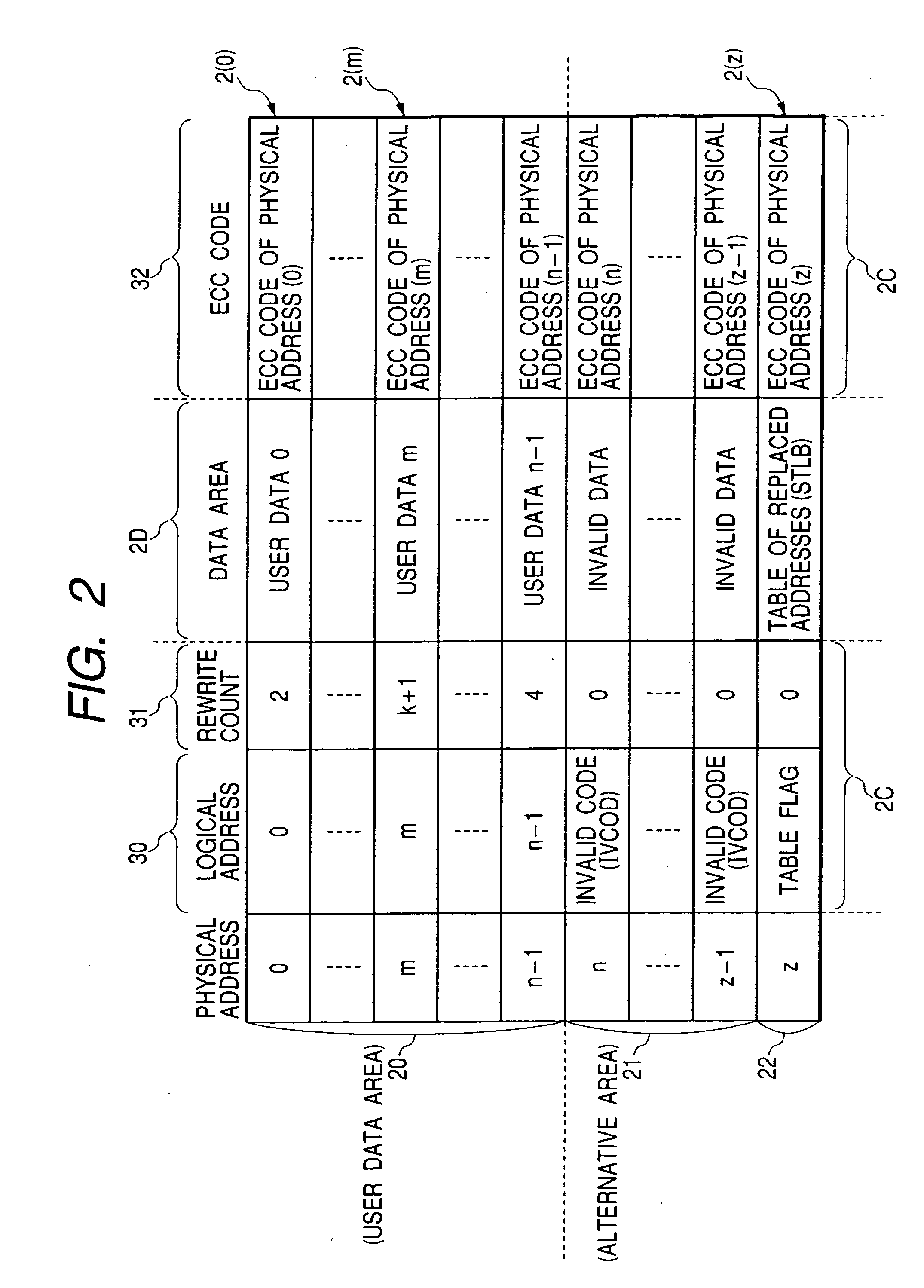

Nonvolatile memory system

InactiveUS20070038901A1Reliable informationPerformance deteriorationMemory loss protectionError detection/correctionError checkPhysical address

A memory system permitting a number of alternative memory blocks to be made ready in order to extend the rewritable life and thereby contributing to enhanced reliability of information storage is to be provided. The memory system is provided with a nonvolatile memory having a plurality of data blocks in predetermined physical address units and a controller for controlling the nonvolatile memory in response to an access request from outside. Each of the data blocks has areas for holding a rewrite count and error check information regarding each data area. The controller, in a read operation on the nonvolatile memory, checks for any error in the area subject to the read according to error check information and, when there is any error, if the rewrite count is greater than a predetermined value, will replace the pertinent data block with another data block or if it is not greater, correct data in the data block pertaining to the error.

Owner:RENESAS ELECTRONICS CORP

Image database system

InactiveUS20050244082A1Improve reliabilityIncrease speedData processing applicationsError detection/correctionDICOMDistribution control

It is an object of the present invention to provide a highly reliable image database system capable of accessing image data at high speed regardless of the increase of the image data and capable of controlling the image data as a whole. A storage unit 1, a control unit 2, an image database server 3 and a DICOM gateway 4 are subjected with each other to network connection. The storage unit 1 stores medical image data. The control unit 2 controls the storage unit. The image database server 3 stores key information associated with the image data stored and applies relay processing between an externally connected viewer and the image database server. The DICOM gateway 4 applies relay processing via a DICOM protocol between a plurality of modality devices externally connected with the image database server and the DICOM gateway. A control unit group, an image database server group, and a DICOM gateway group are constituted by providing at least a plurality of control units, a plurality of image database servers and a plurality of DICOM gateways, and a load balancer for executing load distribution control of every group is provided for every group based on header information of a request.

Owner:YAMATAKE SATOSHI

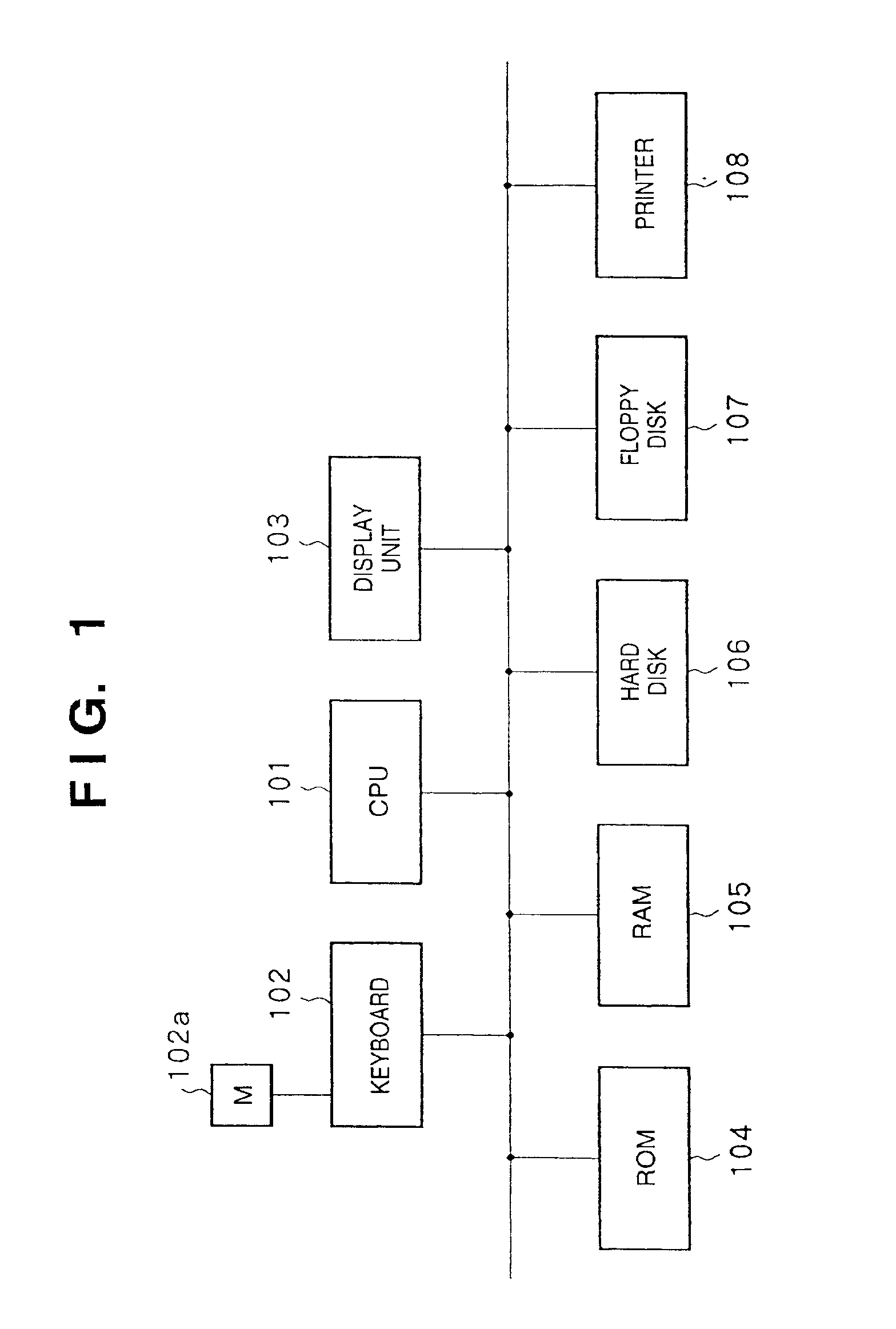

Image storage method and apparatus

InactiveUS6912531B1Easy to handleImprove image qualityData processing applicationsCharacter and pattern recognitionAcquired characteristicComputer graphics (images)

Owner:CANON KK

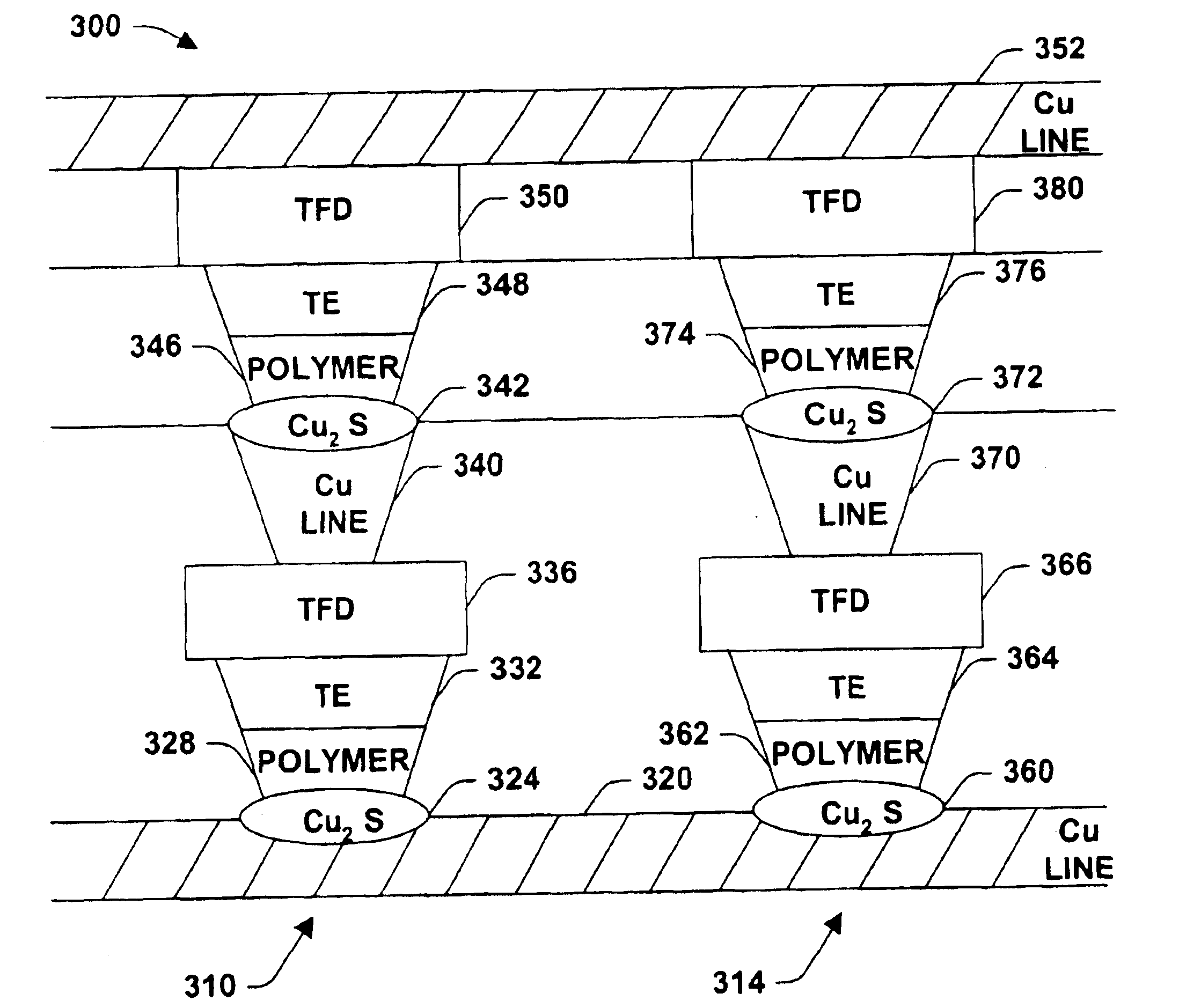

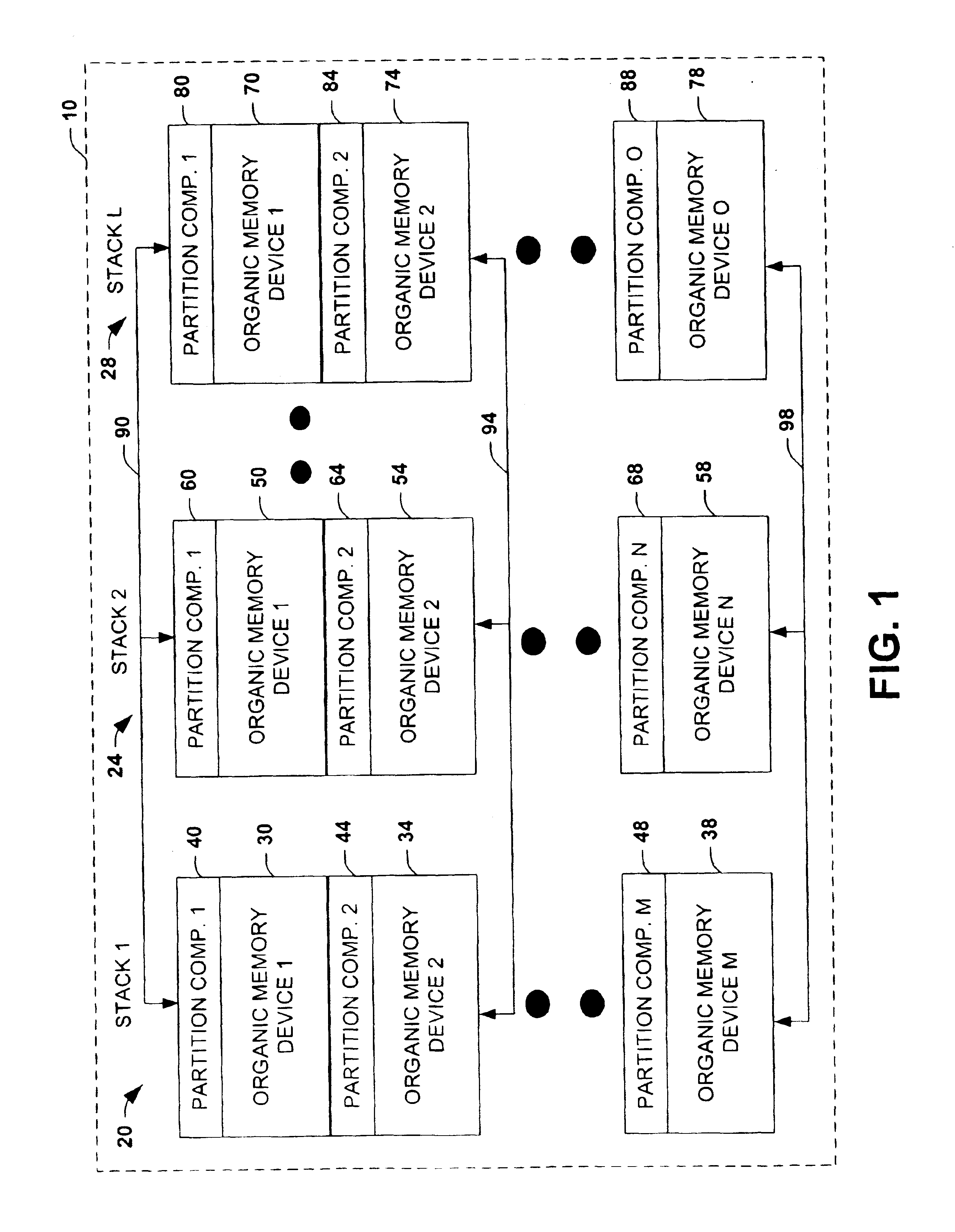

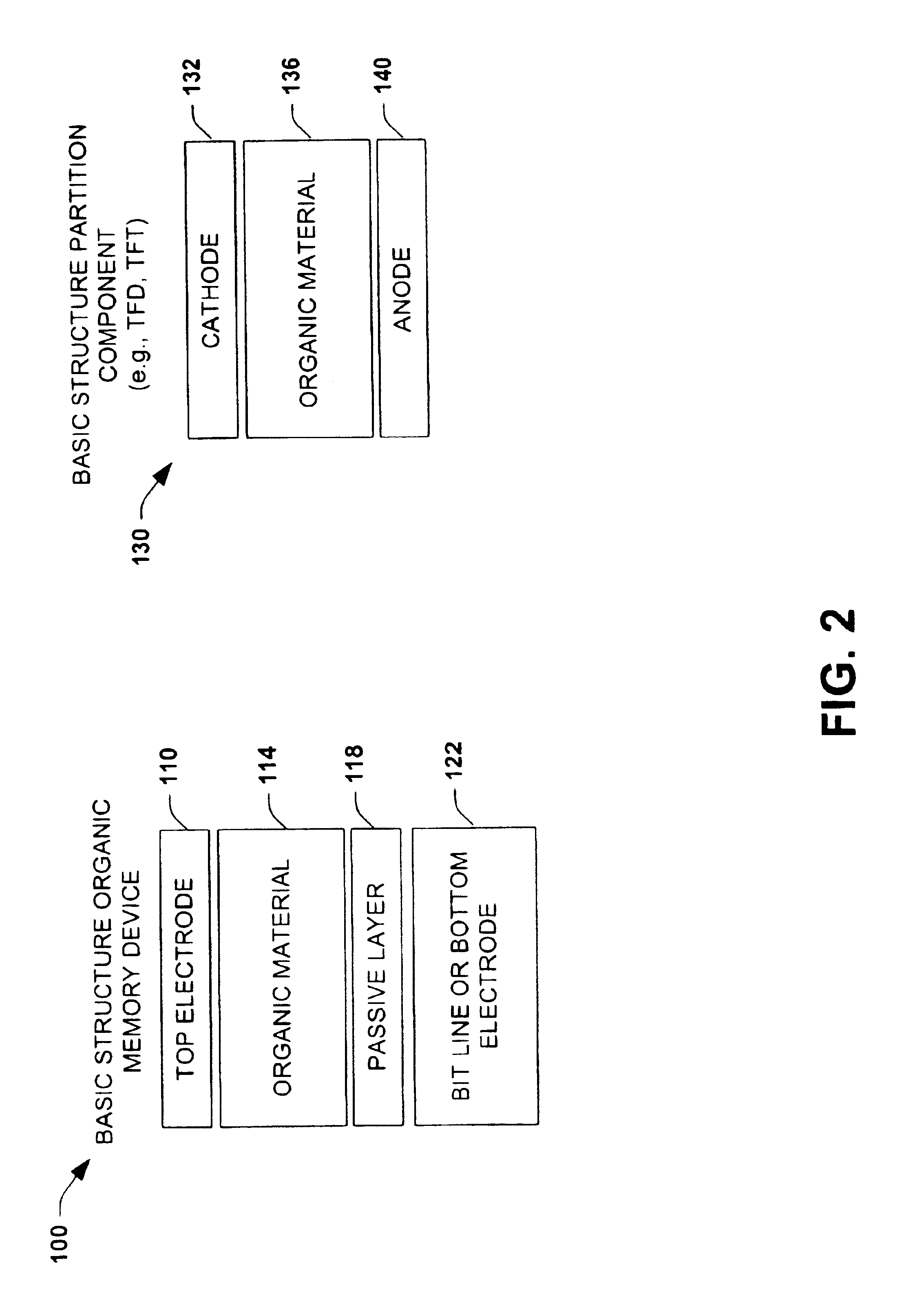

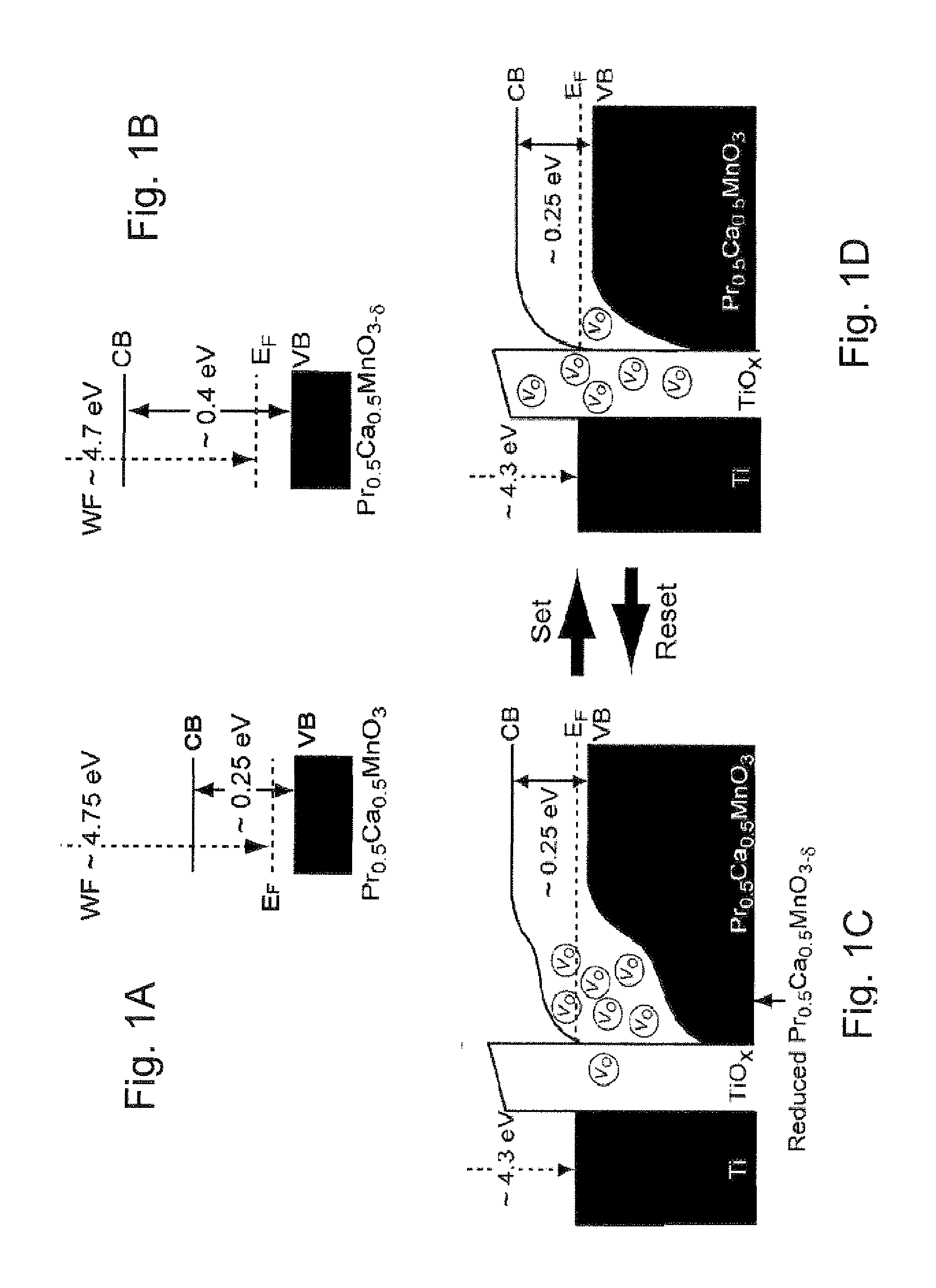

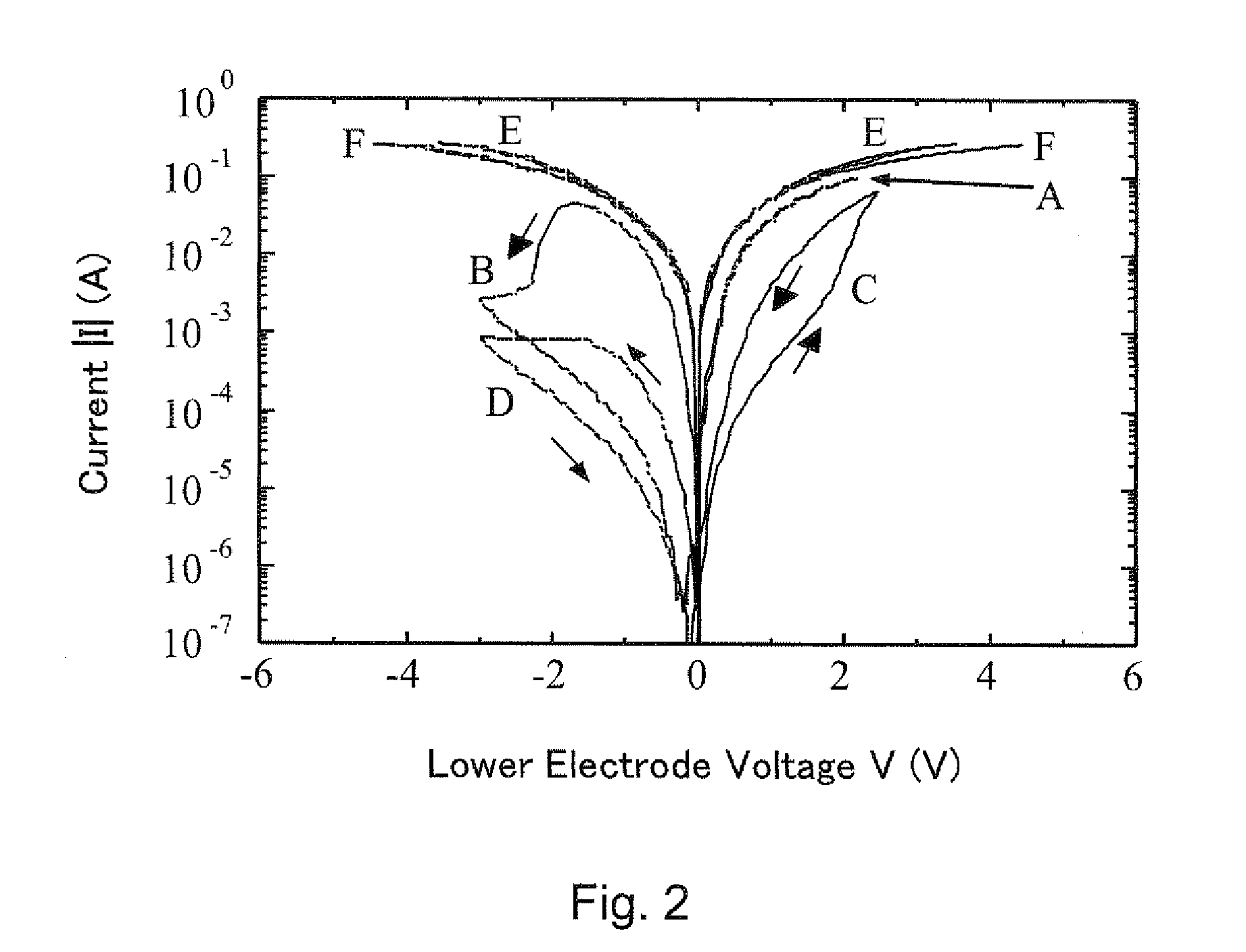

Stacked organic memory devices and methods of operating and fabricating

InactiveUS6870183B2Facilitate charge transferShort resistance/impedance switch timeNanoinformaticsSolid-state devicesOrganic memoryHigh density

The present invention provides a multi-layer organic memory device that can operate as a non-volatile memory device having a plurality of stacked and / or parallel memory structures constructed therein. A multi-cell and multi-layer organic memory component can be formed with two or more electrodes having a selectively conductive media between the electrodes forming individual cells, while utilizing a partitioning component to enable stacking of additional memory cells on top of or in association with previously formed cells. Memory stacks can be formed by adding additional layers—respective layers separated by additional partitioning components, wherein multiple stacks can be formed in parallel to provide a high-density memory device.

Owner:MONTEREY RES LLC

Nonvolatile semiconductor memory device

InactiveUS20110317472A1High-speed accessLow costSolid-state devicesDigital storageResistive elementStorage cell

A memory cell array having a 1R structure is composed of nonvolatile variable resistive elements each including a variable resistor formed of a metal oxide film whose resistance changes depending on an oxygen concentration in the film, and first and second electrodes sandwiching the variable resistor. The first electrode and the variable resistor form a rectifier junction through a rectifier junction layer composed of an oxide layer and a layer (oxygen depletion layer) of the metal oxide film having an oxygen concentration lower than a stoichiometric composition. The oxygen moves between the first electrode and the metal oxide film when a voltage is applied, and a thickness of the oxygen depletion layer changes, so that the resistance of the metal oxide film changes and the rectifying properties are provided. A thickness of the oxygen depletion layer is set to allow the variable resistive element to show the sufficient rectifying properties.

Owner:SHARP KK +1

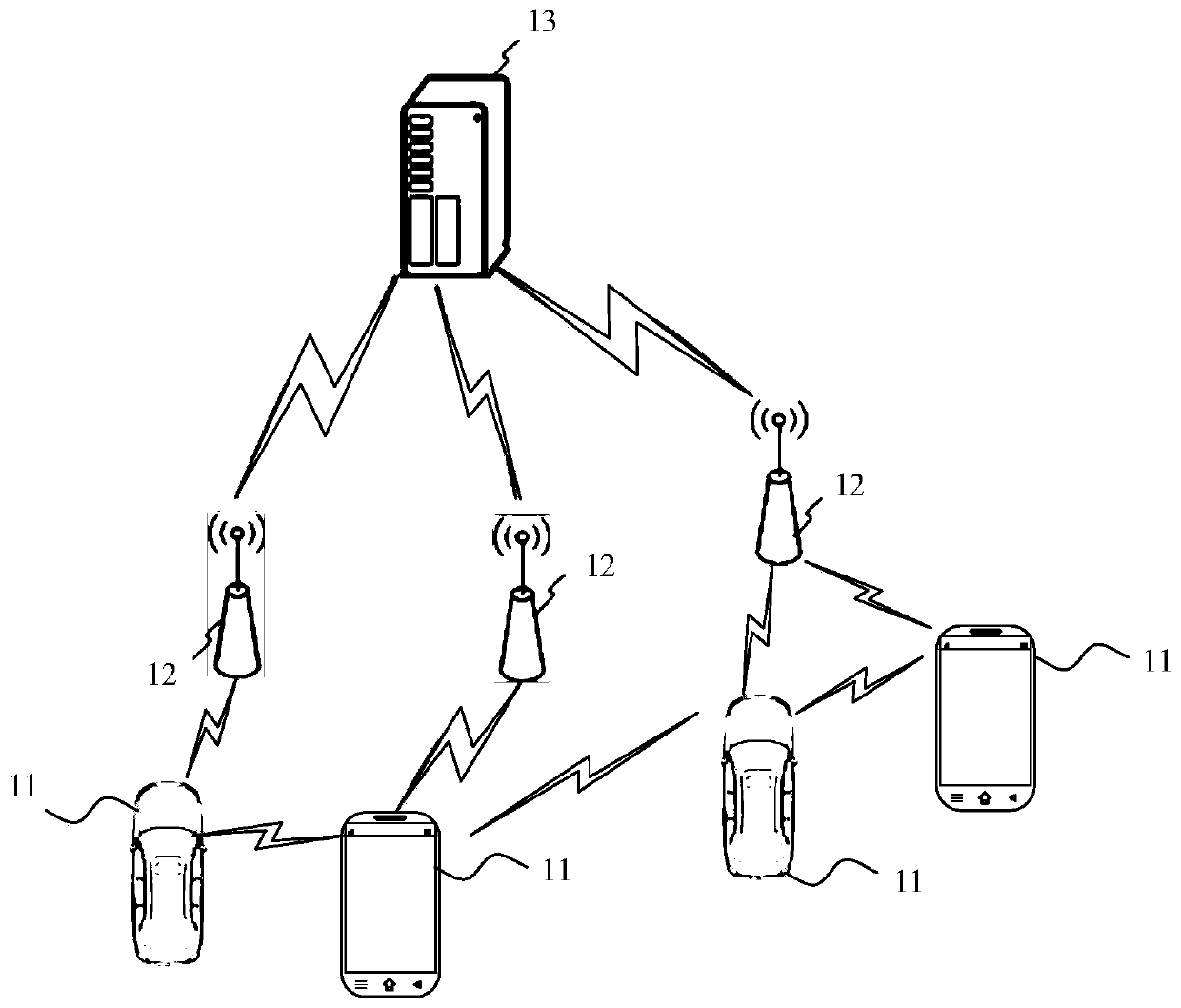

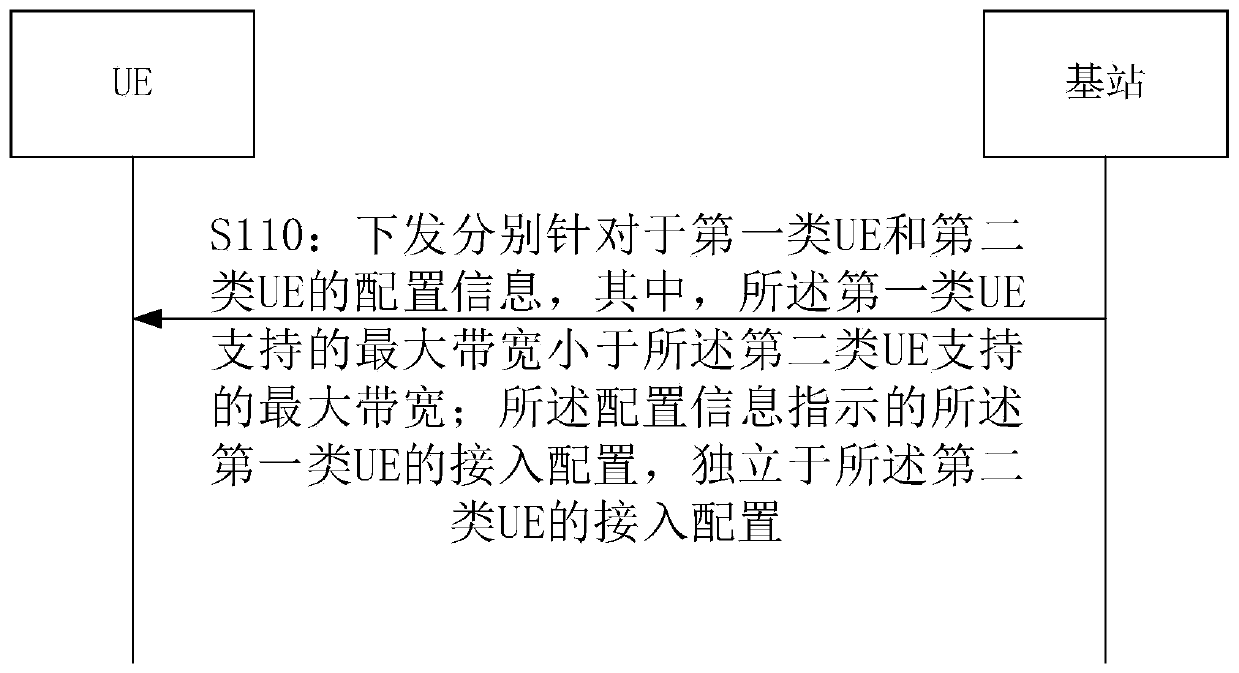

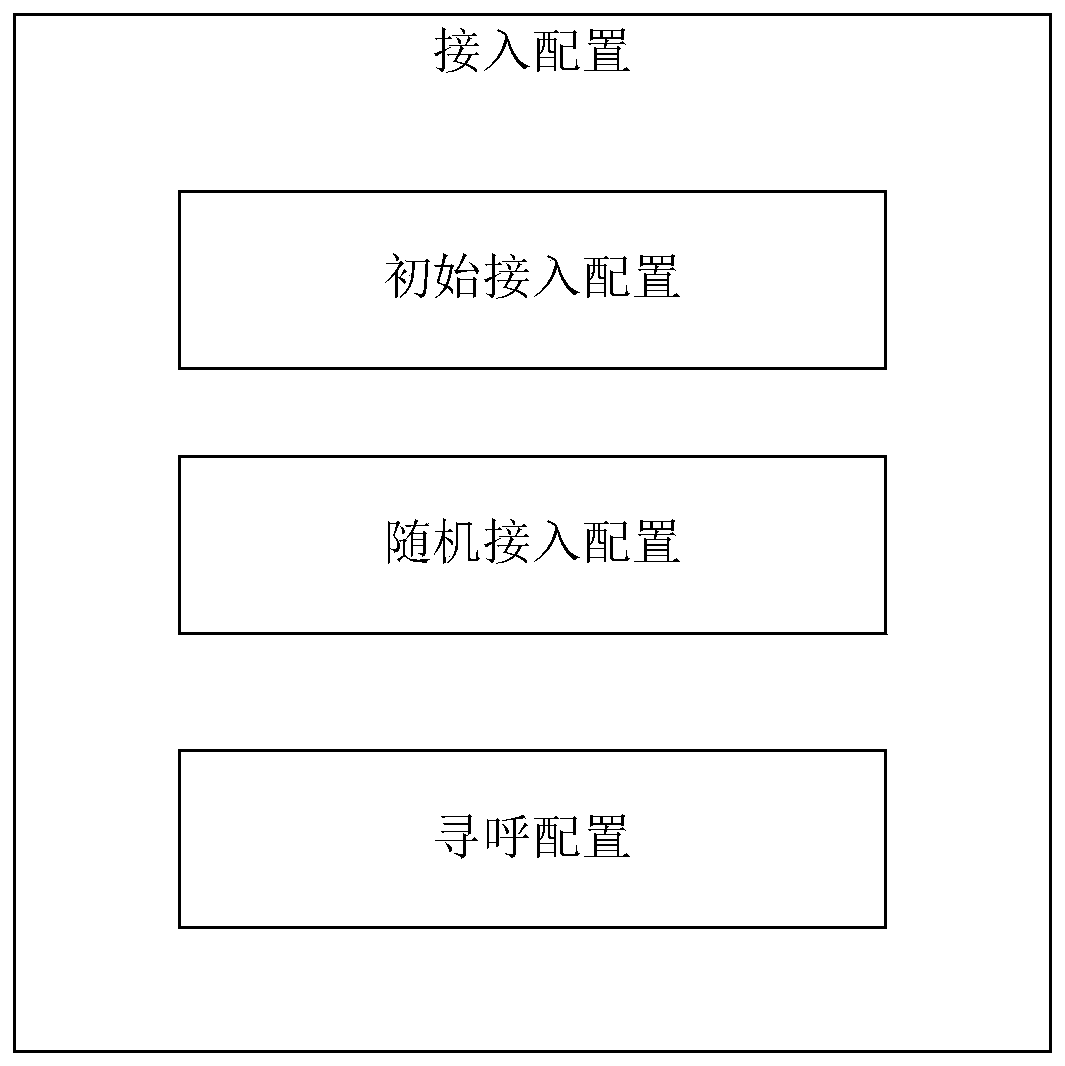

Configuration information transmission method and device, communication equipment and storage medium

ActiveCN111567126AReduce power consumptionReduce complexityAssess restrictionHigh level techniquesAccess networkInformation transmission

The embodiments of the application disclose an information transmission method and device, communication equipment, and a storage medium. The configuration information transmission method includes: issuing configuration information respectively for UE of the first type and UE of the second type, wherein the maximum bandwidth supported by the UE of the first type is less than the maximum bandwidthsupported by the UE of the second type. The access configuration of the UE of the first type indicated by the configuration information is independent of the access configuration of the UE of the second type; the access configuration of the UE of the first type is used for the UE of the first type to access the network; the access configuration of the UE of the second type is used for the UE of the second type to access the network.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

Extended database engine providing versioning and embedded analytics

ActiveUS7698348B2Efficient methodIncrease valueDigital data information retrievalDigital data processing detailsRelational databaseDatabase engine

A system for calculating analytics uses a relational database to store inputs, calculates results, and stores them in cache. The system also includes an access layer that provides a unified view of the data in server. A dynamic access layer is generated at runtime to run an analytic to provide a flexible framework for creating business logic.

Owner:KINAXIS INC

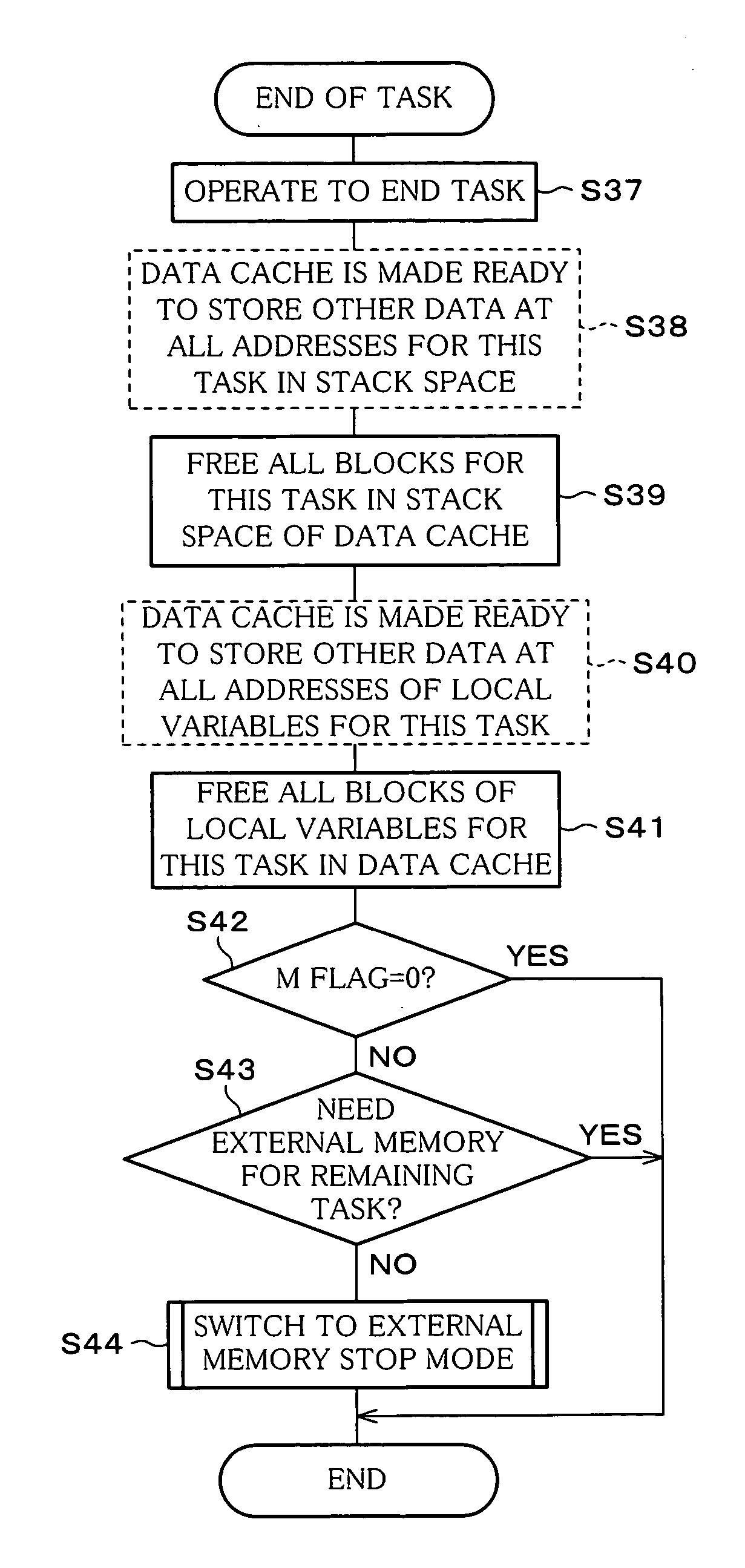

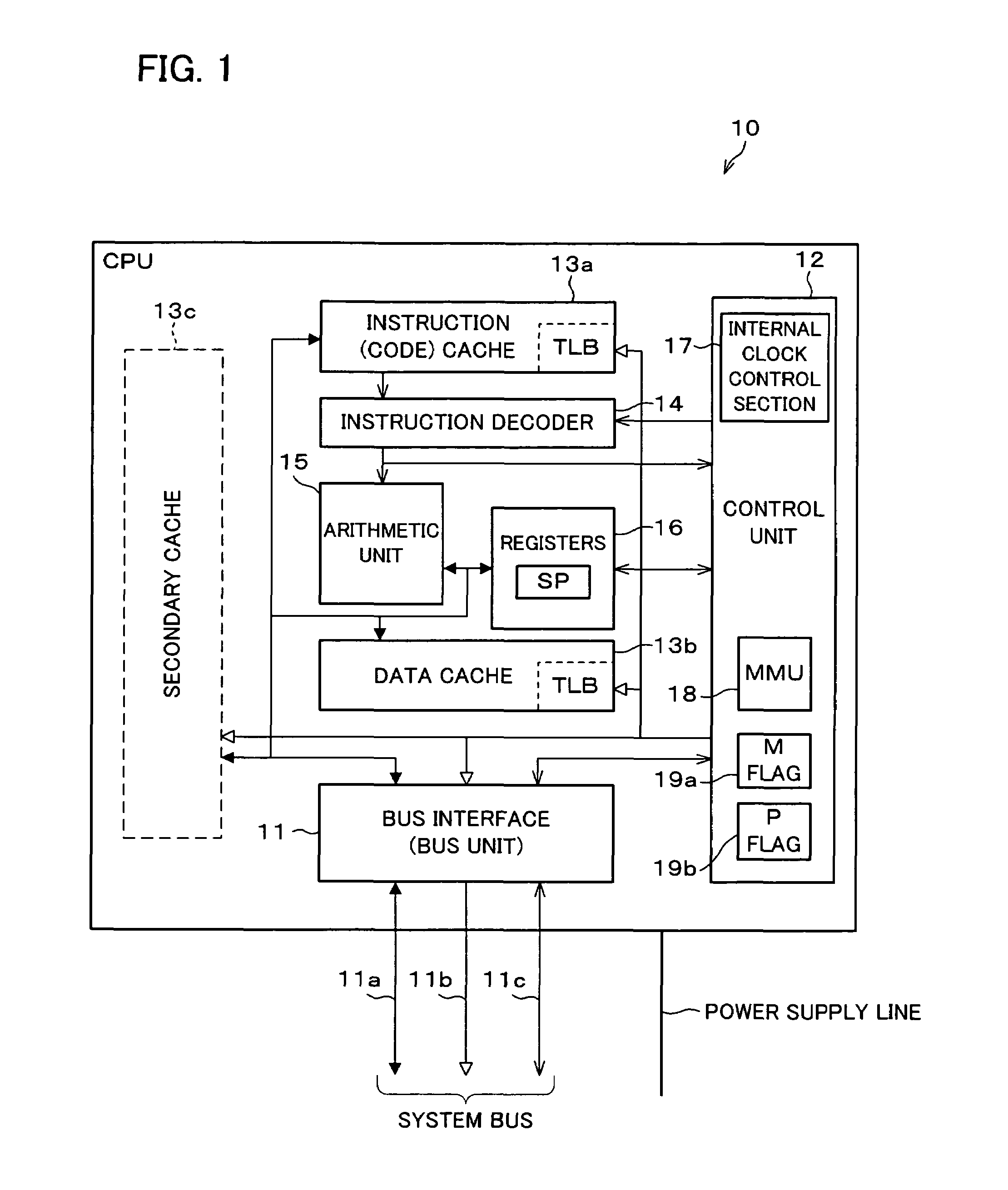

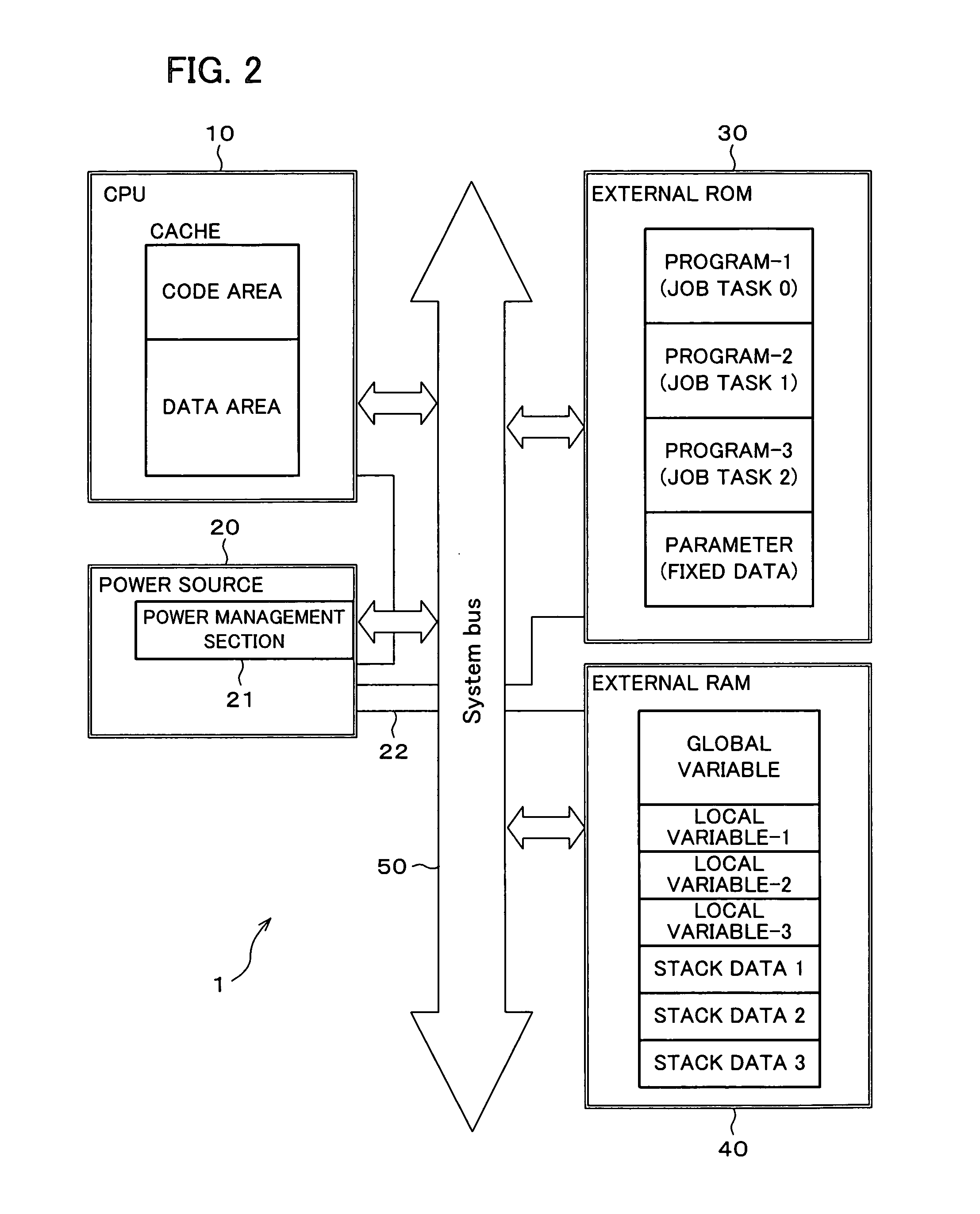

CPU, information processing device including the CPU, and controlling method of CPU

ActiveUS7266641B2Easy to handleReduce power consumptionEnergy efficient ICTVolume/mass flow measurementInformation processingExternal storage

A CPU includes a bus interface, a control unit, an instruction cache, a data cache, a secondary cache, an instruction decoder, an arithmetic unit, and registers. When operations can be performed only with the cache, the CPU inhibits access to external memory and stops power supply to the external memory. With this arrangement, by performing operations in the CPU without using the external memory, it is possible to realize a speedy processing and to stop power supply to the external memory, thus allowing for reduction in power consumption.

Owner:SHARP KK

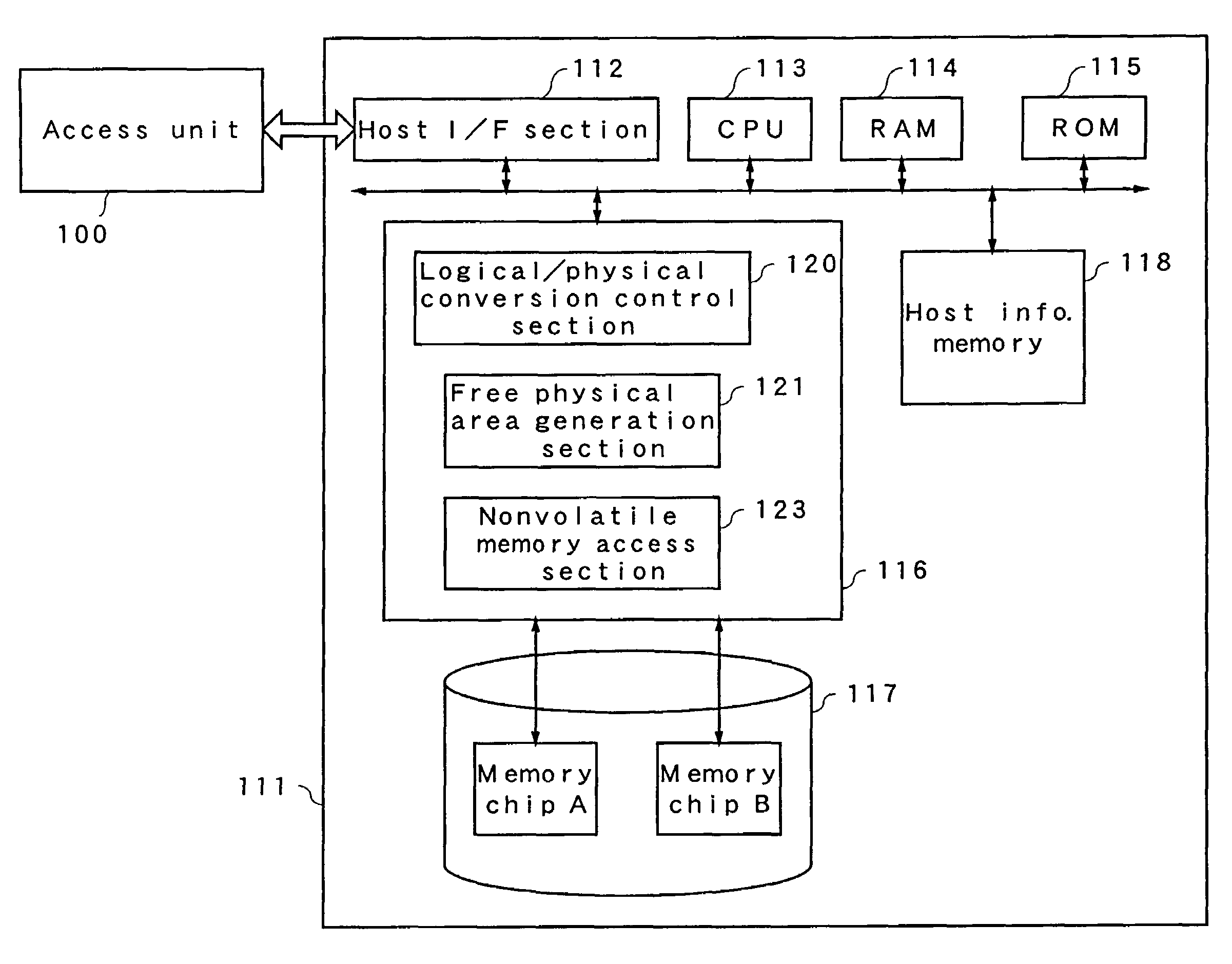

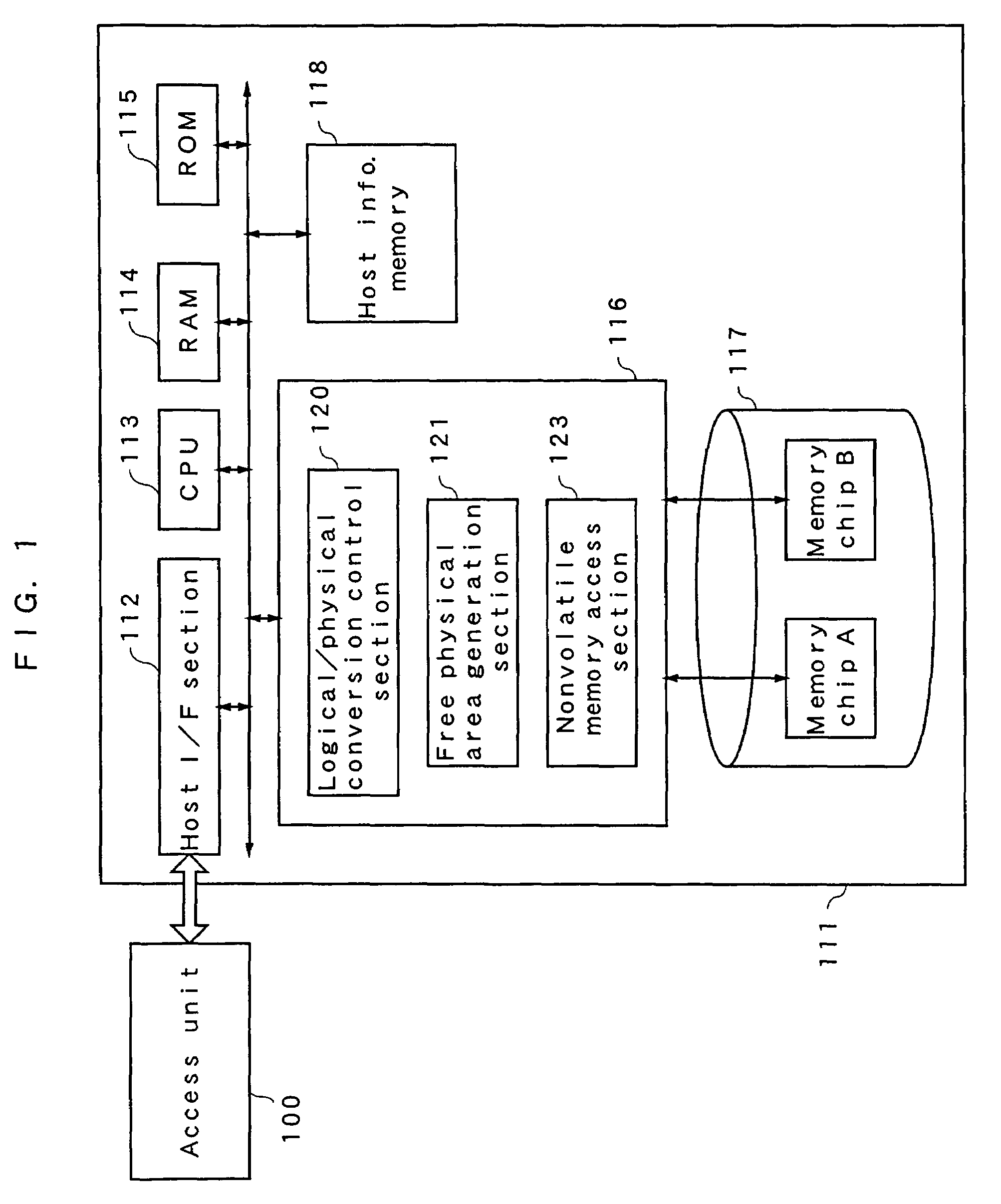

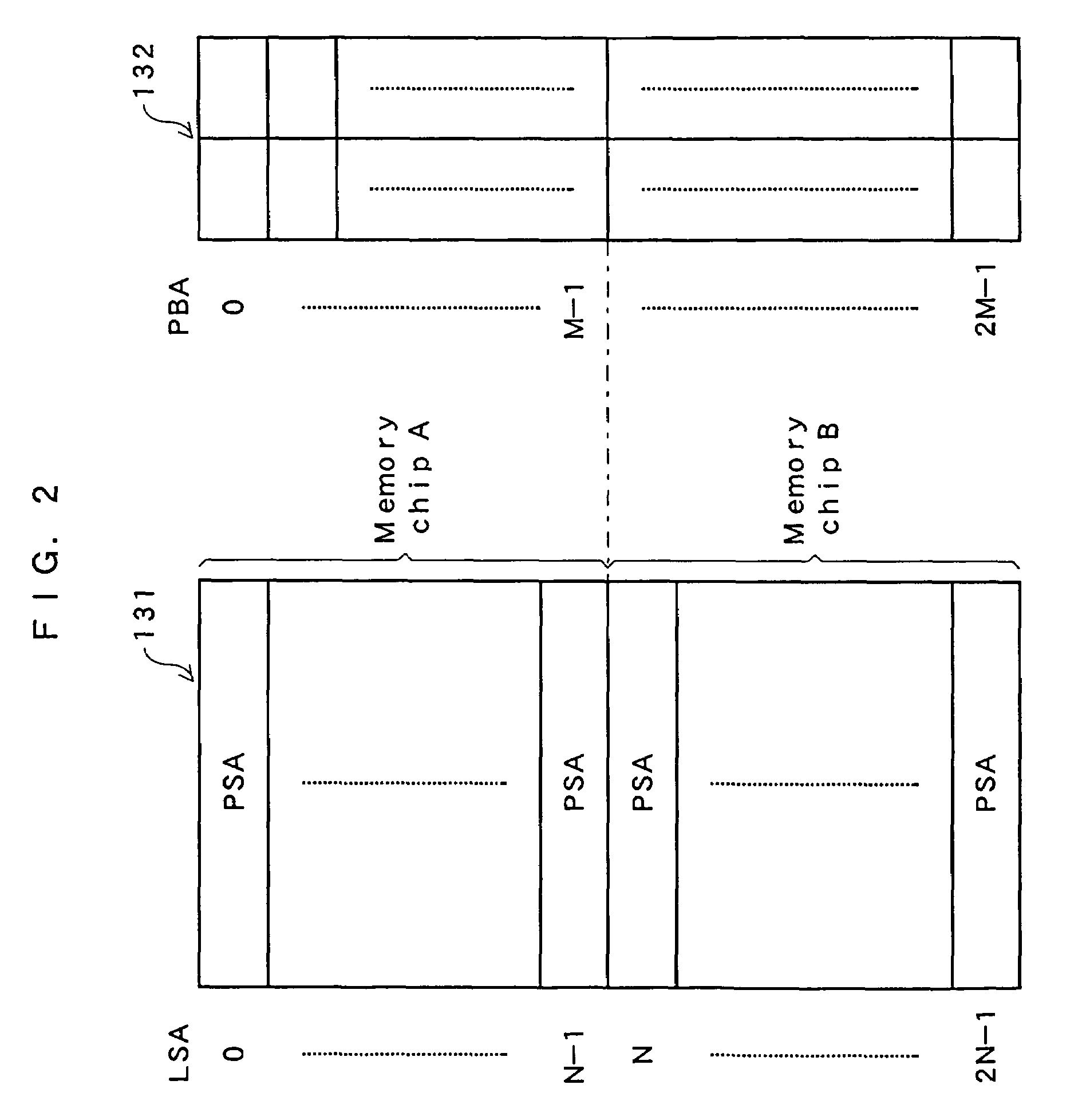

Semiconductor memory card, semiconductor memory control apparatus, and semiconductor memory control method

ActiveUS7654466B2Lower performance requirementsFree block can be increasedEnergy efficient ICTInput/output to record carriersMemory chipSemiconductor

A host information memory is provided in a semiconductor memory card and a data write start address and a data size supplied by an access unit are stored. A free physical area generation section determines whether or not to perform erasing of an invalid block of a nonvolatile memory when writing of data based on the data write start address and data size, and determines the number of blocks to be erased. When erasing, writing of data and erasing of invalid blocks are simultaneously performed with respect to different memory chips. Erase process of data, herewith, can be optimized and high speed access from the access unit to a semiconductor memory card can be realized.

Owner:PANASONIC CORP

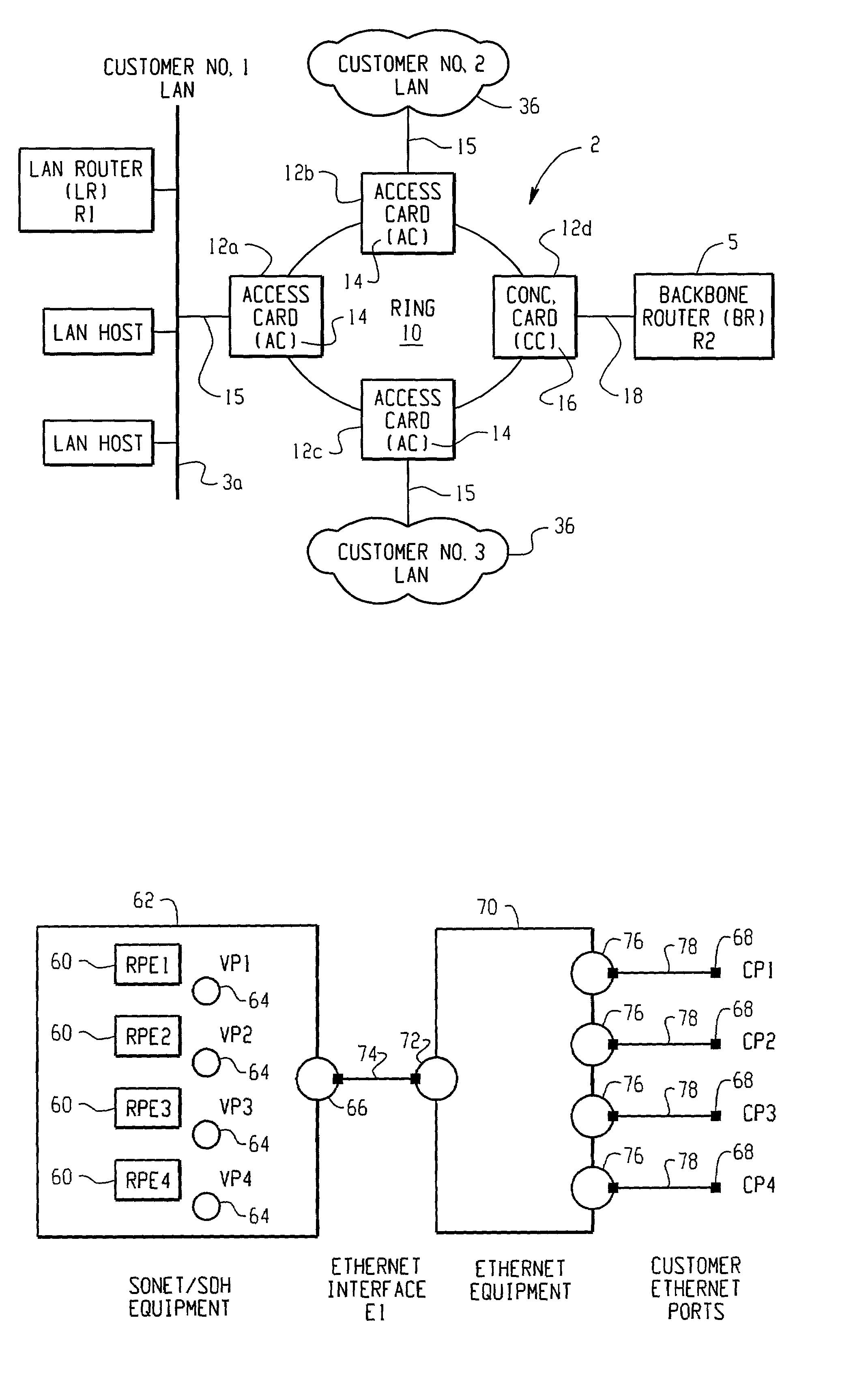

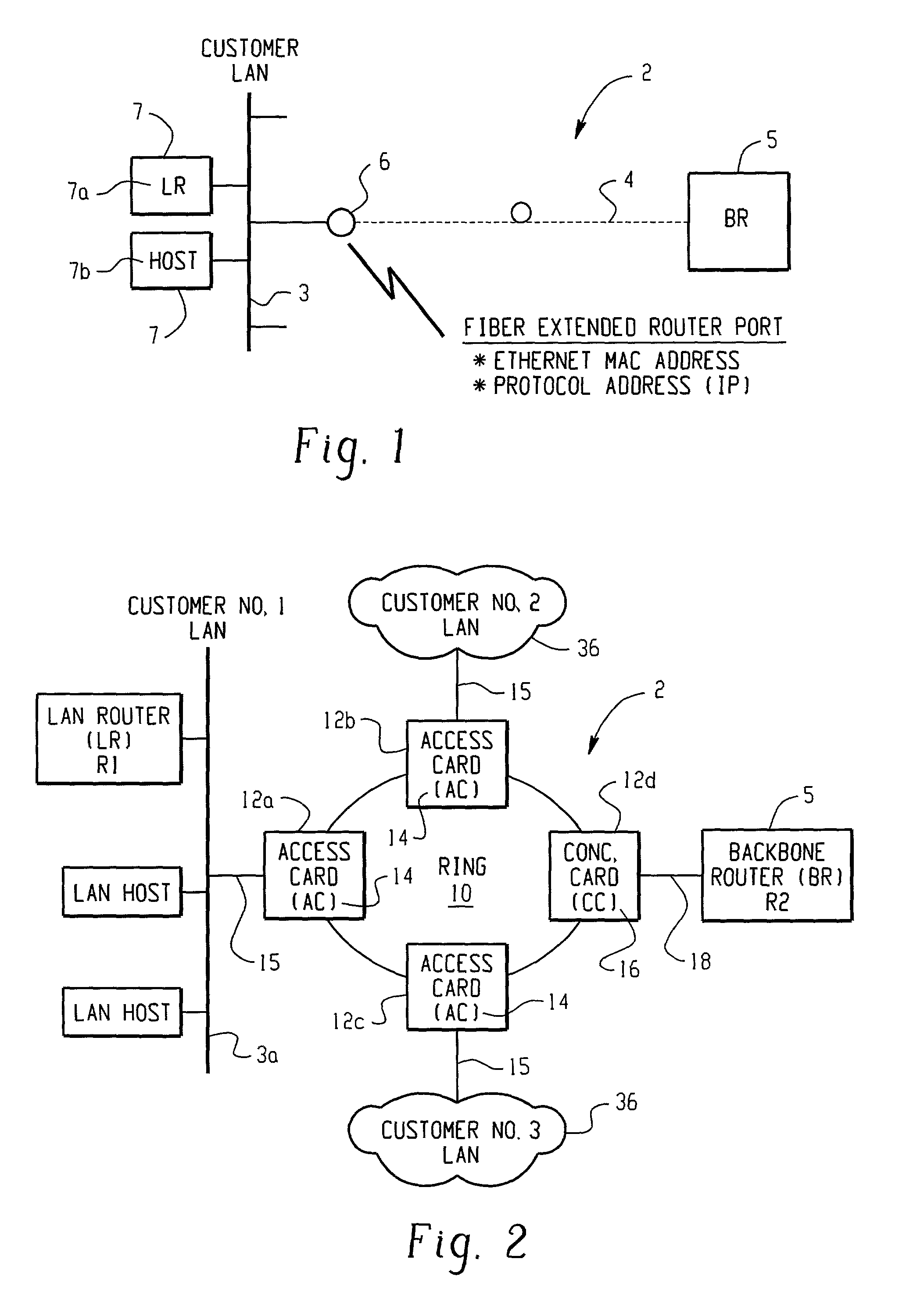

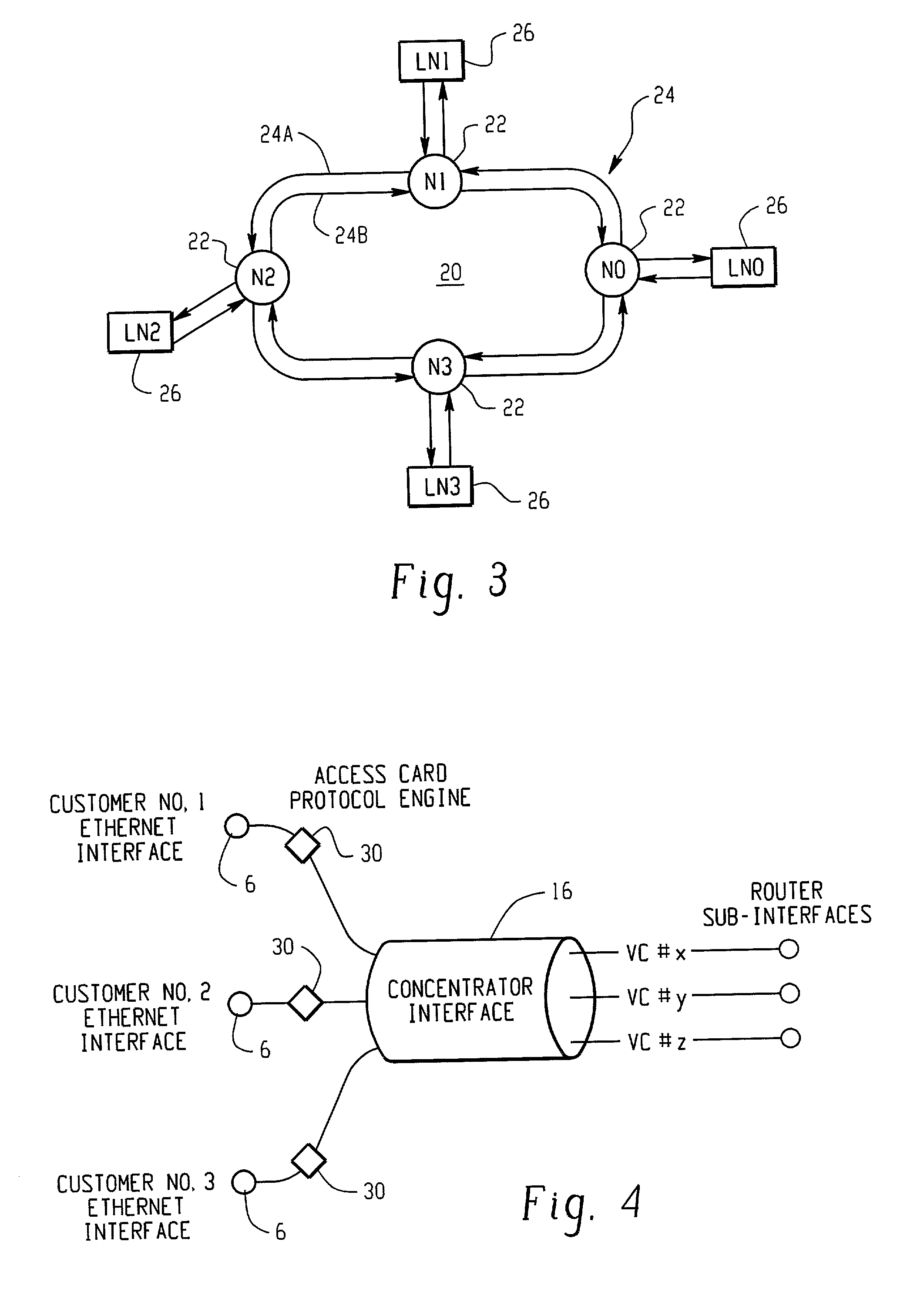

Virtual ethernet ports with automated router port extension

ActiveUS7002976B2Increase valueMinimize interfaceTime-division multiplexData switching by path configurationEncapsulated dataAutomatic routing

A method and system for extending a plurality of sub-interfaces of a router port of a wide area network access device to a plurality of user networks using a transport network is provided. The transport network comprises a plurality of network nodes coupled together by one or more data communication paths wherein at least one of the network nodes comprises an access device. The access device includes a plurality of router port extension functional units wherein each router port extension functional unit is coupled to one of the user networks. Each router port extension functional unit comprises a virtual channel agent and a LAN agent. Each router port extension functional units has an associated virtual port, and all of the virtual ports are multiplexed to a single LAN communication port. The method comprises the steps of receiving a first upstream data packet from a first user LAN, decapsulating the received first data packet so that the LAN encapsulation format is removed from said received first data packet, encapsulating the first decapsulated data packet into the transport network encapsulation format, transmitting the first transport network encapsulated data packet onto the transport network, and repeating the foregoing steps with a second user LAN using a second router port extension functional unit.

Owner:TELEFON AB LM ERICSSON (PUBL)

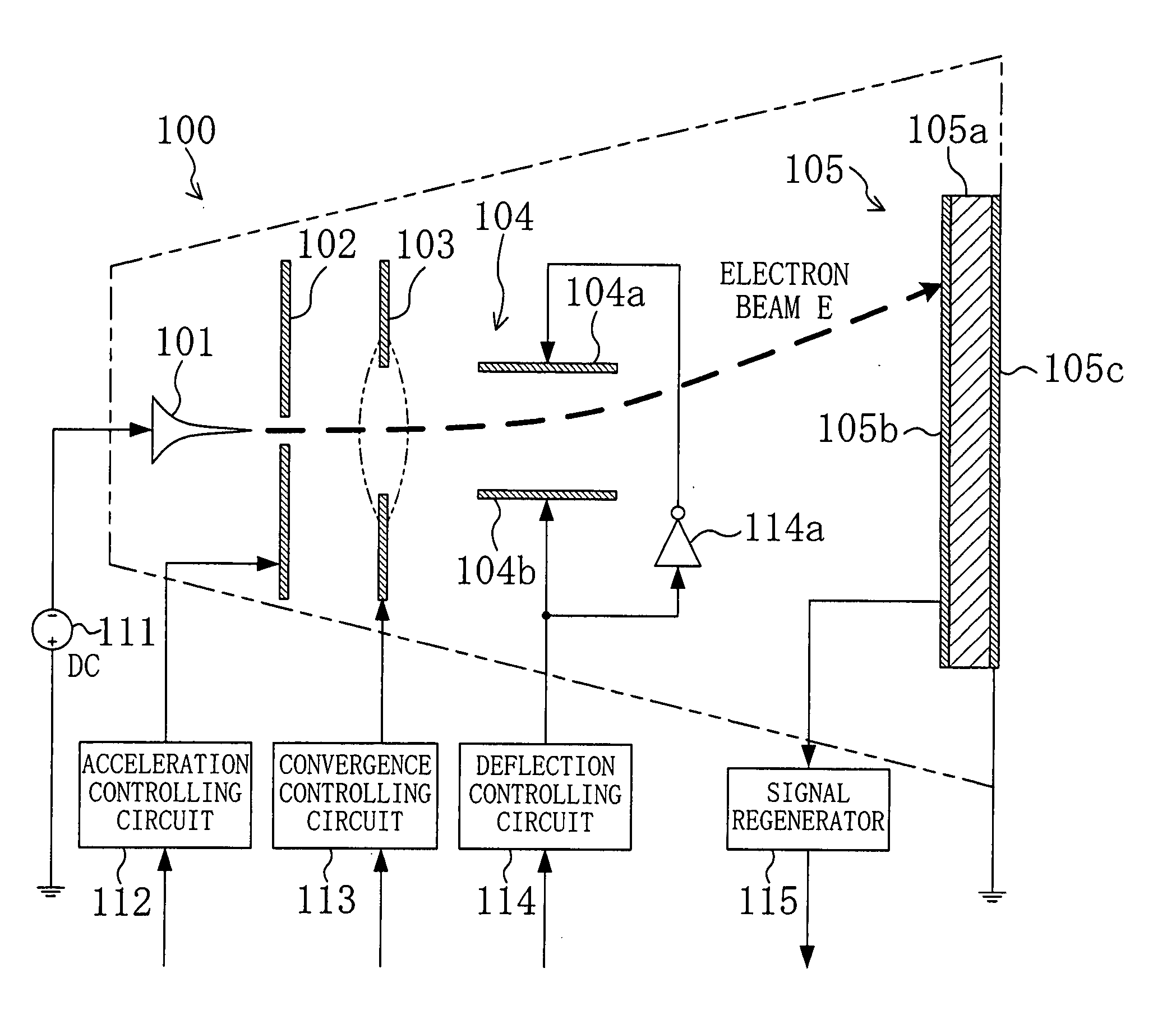

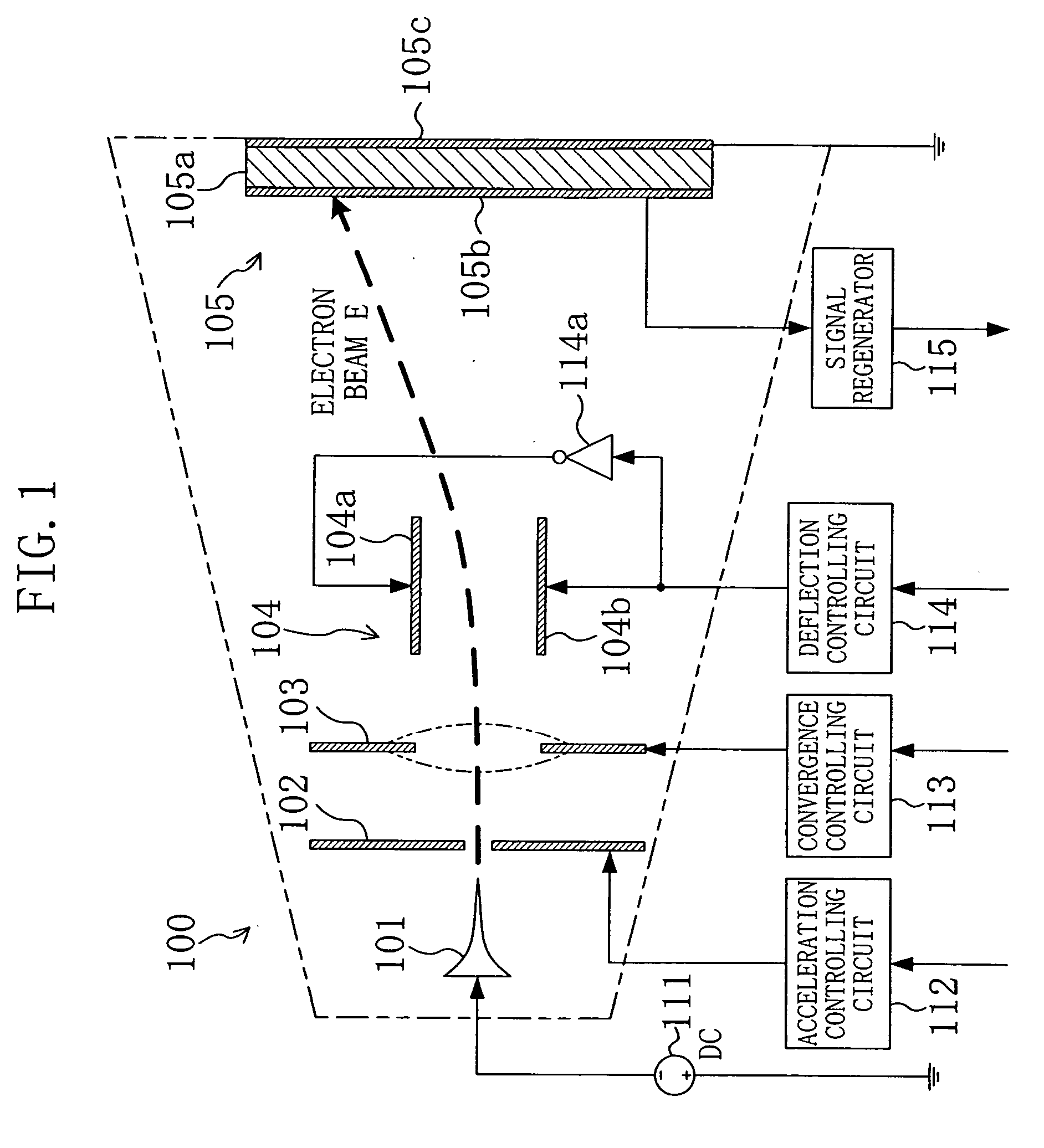

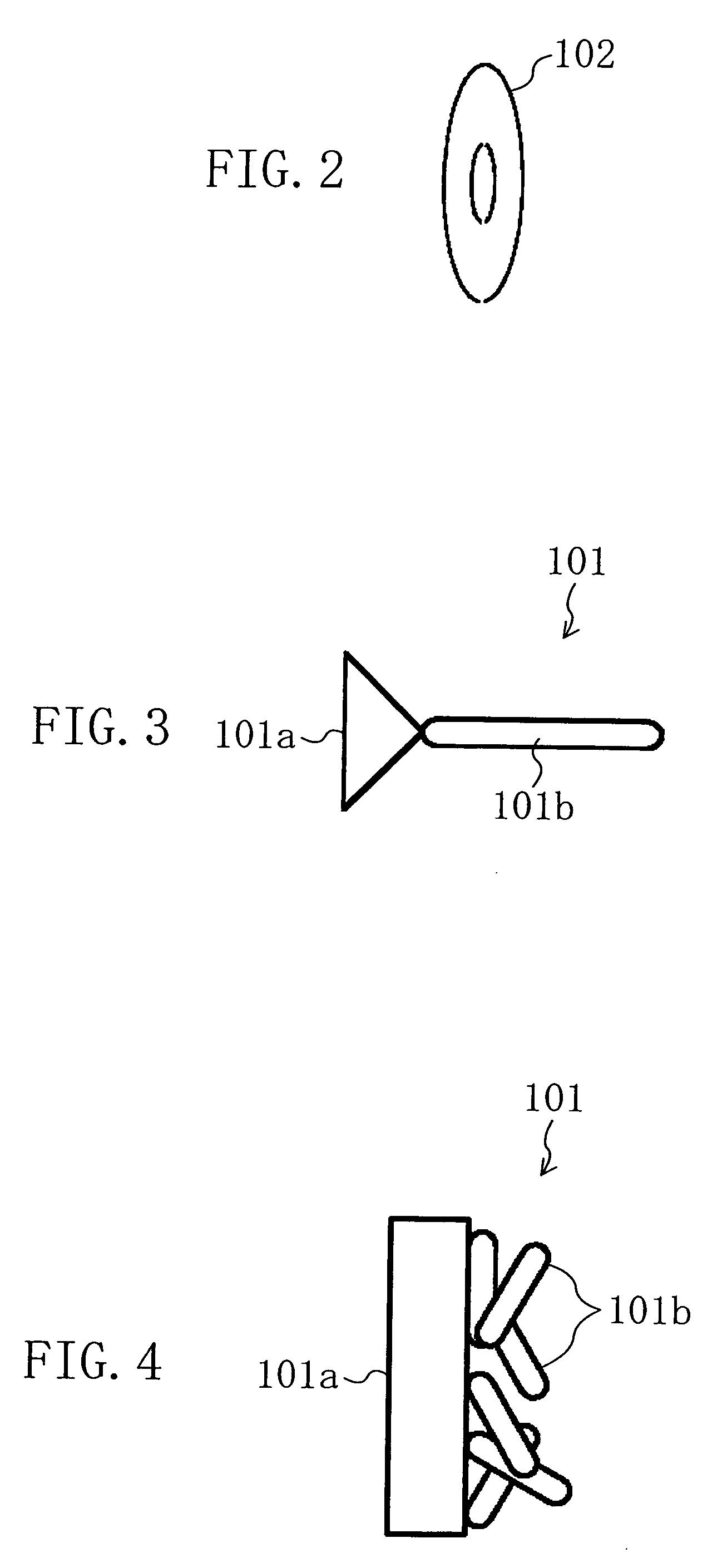

Information storage

InactiveUS20060072427A1Increase speedImprove accuracyRead-only memoriesRecord information storageHigh energyPotential difference

To greatly increase the storage density of a storage apparatus, an electron beam E emitted from a cold cathode 101 is accelerated by an accelerating electrode 102, caused to converge by a convergence electrode 103, deflected by a deflection electrode 104 and applied to a minute region of a storage film 105. The storage film 105 includes, for example, a phase change film 105a. The film is rapidly heated and cooled to change into an amorphous state upon irradiation with an electron beam E with high energy, while being gradually cooled to change into a crystallized state upon irradiation with an electron beam E with approximately intermediate energy, thereby storing data. Upon irradiation with an electron beam E with low energy, the potential difference between a detection electrode 105b and an anode 105c is detected depending on the state, i.e., the amorphous or crystallized state, thereby reading stored data.

Owner:PANASONIC CORP

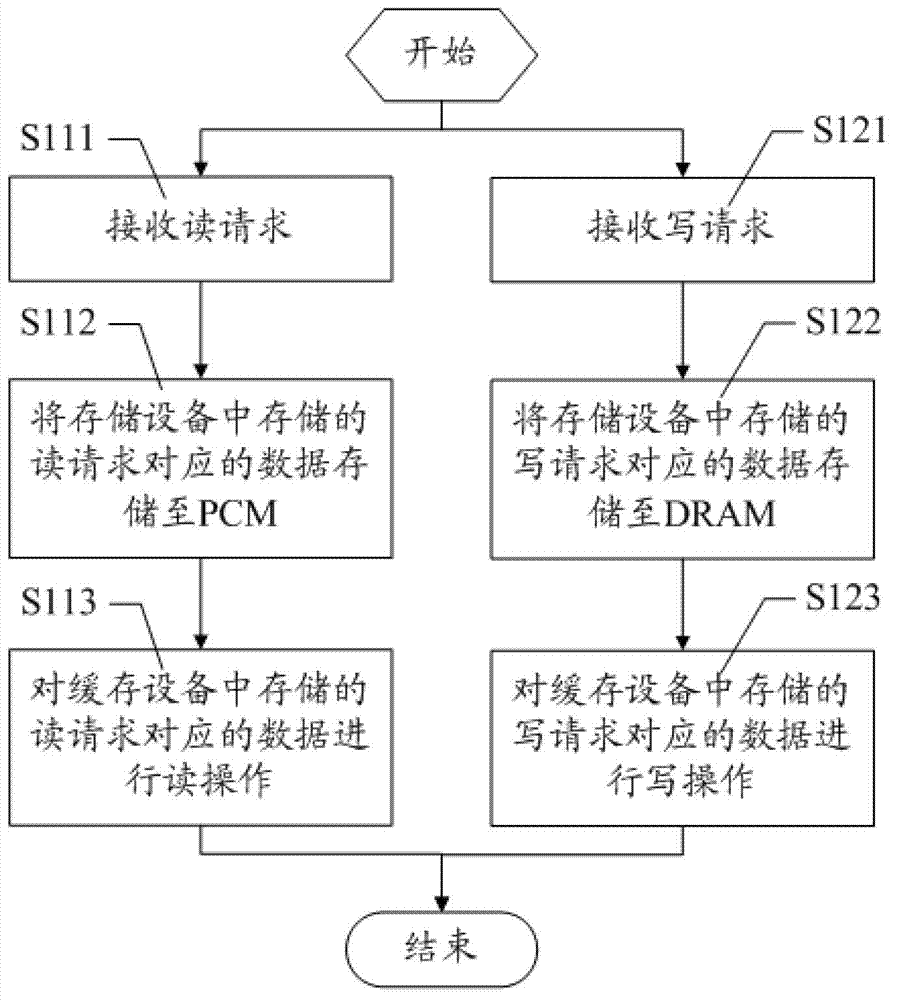

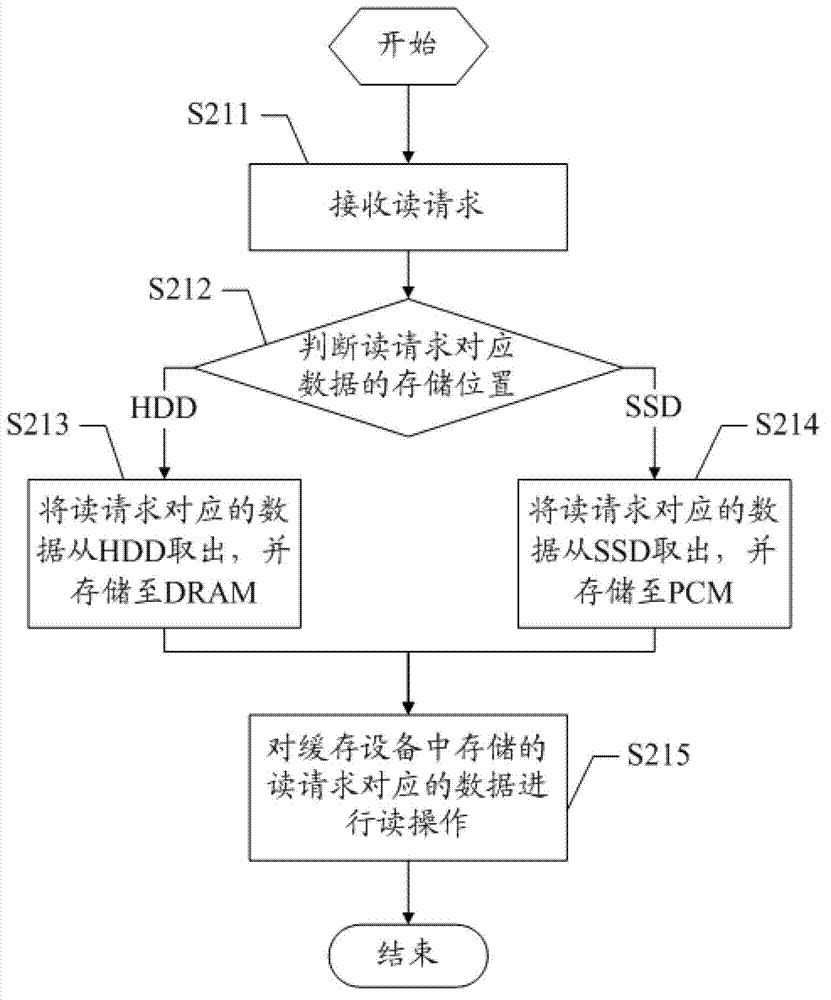

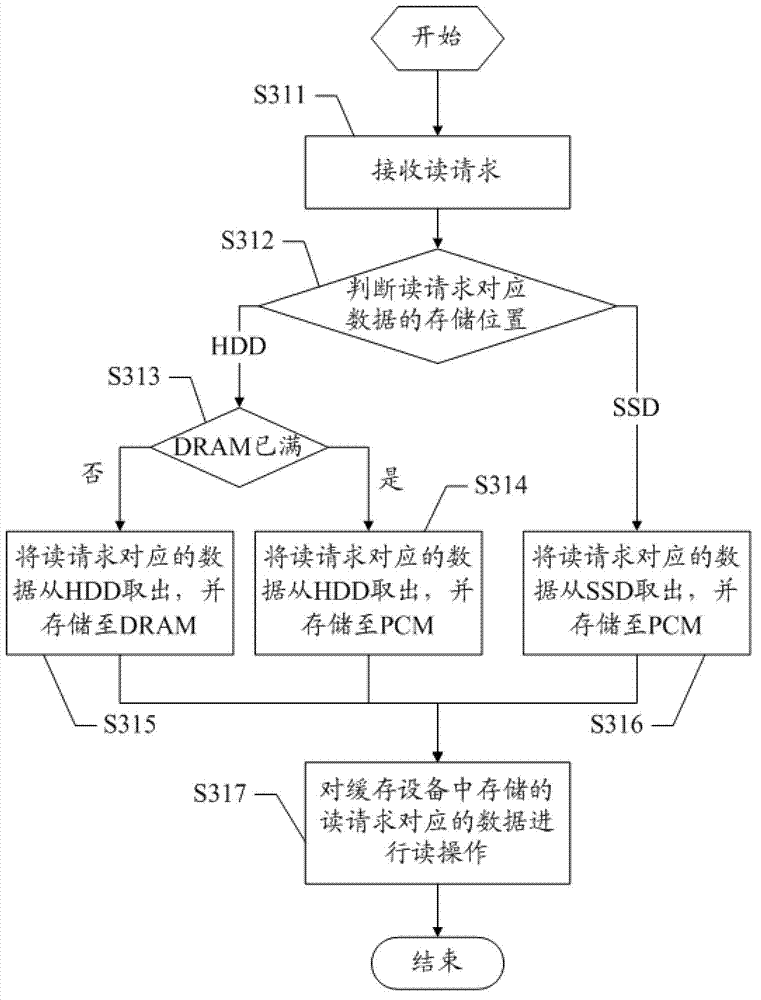

Data reading-writing processing method and device based on mixing memory

ActiveCN102831087AHigh densityHigh speed densityElectric digital data processingPhase-change memoryOperating system

The invention discloses a data reading-writing processing method and a data reading-writing processing device based on a mixing memory. The method comprises the following steps: receiving a reading request or a writing request; storing the data corresponding to the reading request stored in a storage device to a phase change memory PCM (Phase Change Memory) of a cache device, or storing the data corresponding to the writing request stored in the storage device to a dynamic random access memory DRAM (Dynamic Random Access Memory) of the cache device; carrying out reading operation on the data corresponding to the reading request stored in the cache device, or carrying out writing operation on the data corresponding to the writing request stored in the cache device. According to the data reading-writing processing method and the data reading-writing processing device, the high-speed access, high capacity and low cost is achieved, the PCM loss is effectively reduced, and the service life of the whole mixing memory is improved.

Owner:国家超级计算深圳中心(深圳云计算中心)

Molecular memory medium and molecular memory integrated circuit

InactiveUS7260051B1Reduce quality problemsFast accessNanoinformaticsRecord information storagePhase shiftedComputer science

A molecular memory media having a media surface and a platform with read / write heads. The platform and media are moved to allow one of addition, removal, and repositioning of atoms, electrons, and charges on a surface of the media. The media is a material capable of storing data written to it, and detectable using a vibrating tip sensor that resonates at a free space value which is phase shifted when charges or anomalies on a surface of the media are present. Other methods of reading and writing to the media are presented. The media may be enhanced by augmenting grain boundaries of the media vis deposition and removal of PMMA materials. Servo trenches and sync bits identify positions of the read / write heads and maintain alignment during memory operations.

Owner:NANOCHIP