Power and signal line bussing method for memory devices

a memory device and signal line technology, applied in the field of power and signal line bussing method for high density and high speed memory devices, can solve the problems of large signal delay, conventional bussing arrangement, and ineffective reduction of the frequency response of the peripheral circuit 4, so as to reduce the noise generated by the chip, fast access time, and the effect of not increasing the size of the chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

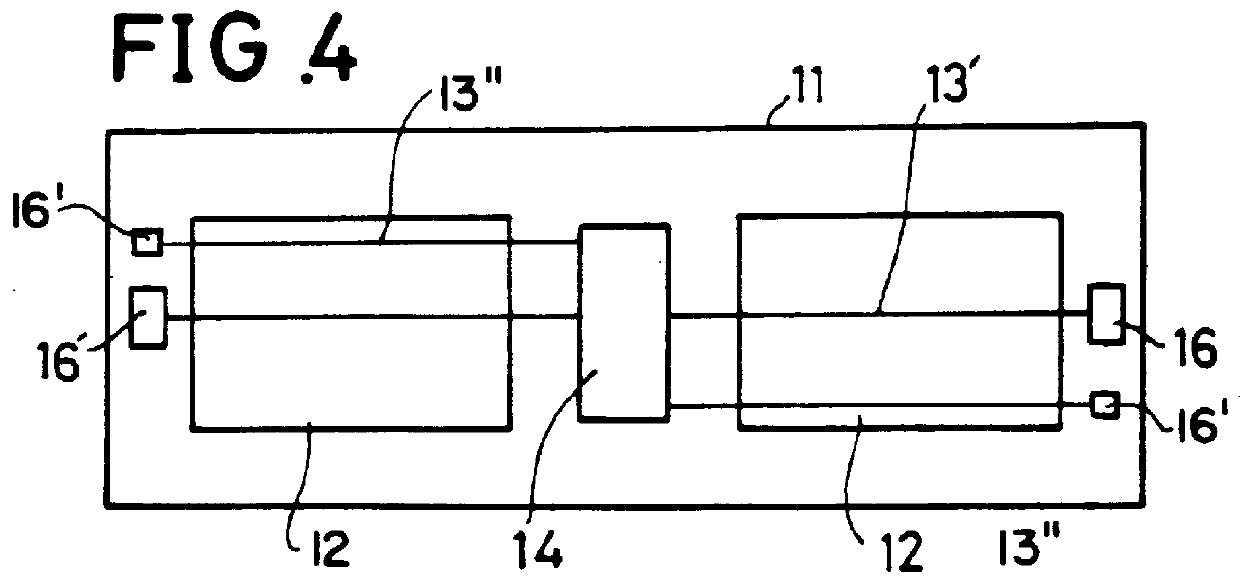

FIG. 3 shows a power line bussing arrangement according to the present invention. Chip 11 comprises two memory cell arrays 12 centered around peripheral circuitry 14. Power lines 13a, formed above memory cell arrays 12 and peripheral circuitry 14, supplies power from Vcc pad 15 to peripheral circuitry 14. Ground lines 13b, formed above memory cell arrays 12 and peripheral circuitry 14, connects peripheral circuitry 14 to GND pad 15'. Both power lines 13a and ground lines 13b are separated parallel lines traversing end-to-end chip 11. All power lines 13a are connected to Vcc pad 15 and all ground lines 13b are connected to GND pad 15'. Ground lines 13b and power lines 13a are formed in an adjacent alternating pattern such that a power line 13a is positioned adjacent to ground line 13b, which is positioned adjacent another power line 13a, and so on.

Accordingly, Vcc power is supplied through Vcc pad 15 and power lines 13 to each circuit in the peripheral circuitry 14. By coupling a pow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More