Memory system and method having selective ECC during low power refresh

a memory system and low power refresh technology, applied in error detection/correction, error avoidance, instruments, etc., can solve the problem that data retention errors can be expected to occur during refresh, and achieve the effect of reducing power rate, reducing power rate, and reducing power ra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

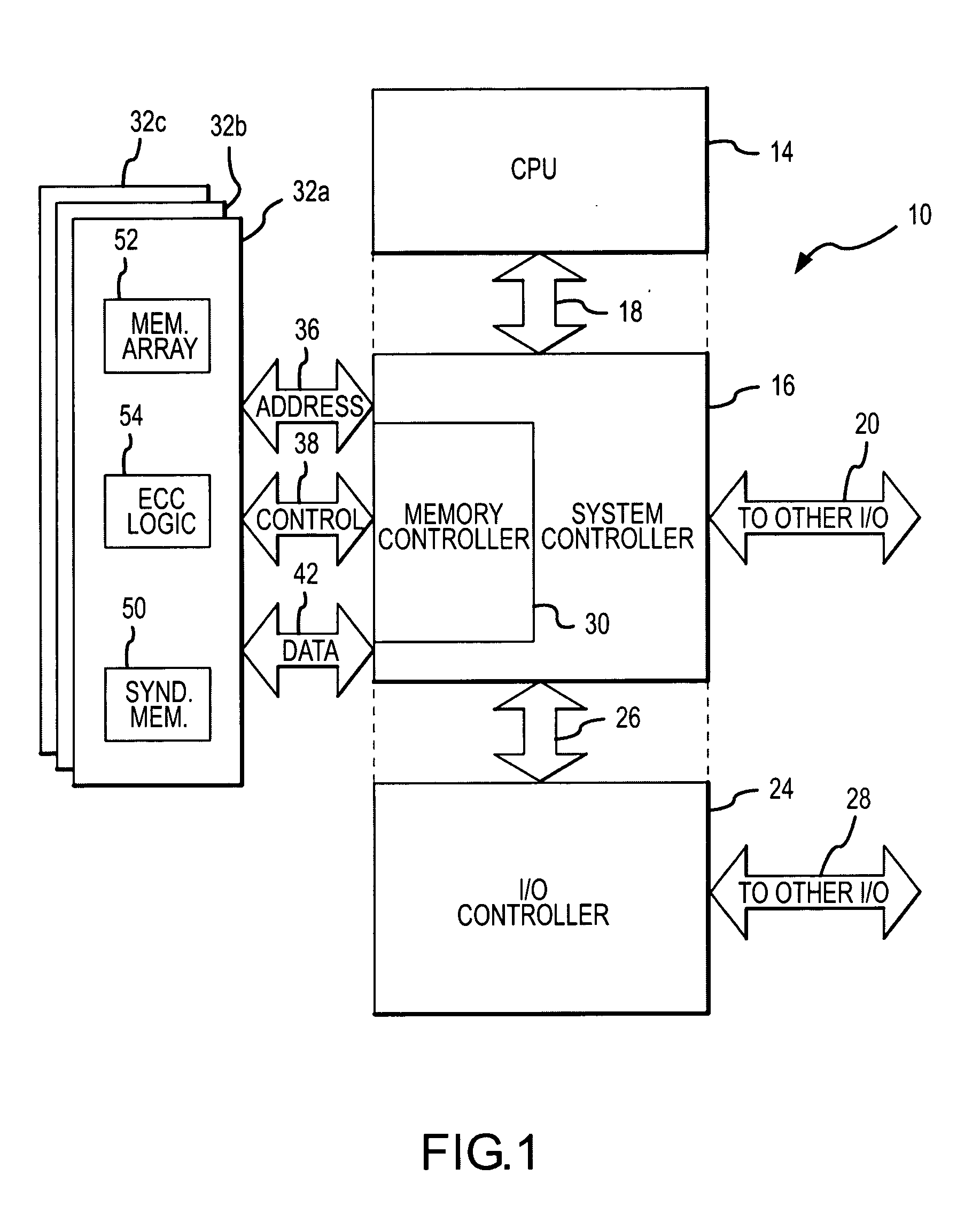

[0017] A computer system 10 according to one embodiment of the invention is shown in FIG. 1. The computer system 10 includes a central processor unit (“CPU”) 14 coupled to a system controller 16 through a processor bus 18. The system controller 16 is coupled to input / output (“I / O”) devices (not shown) through a peripheral bus 20 and to an I / 0 controller 24 through an expansion bus 26. The I / O controller 24 is also connected to various peripheral devices (not shown) through another I / 0 bus 28.

[0018] The system controller 16 includes a memory controller 30 that is coupled to several dynamic random access memory (“DRAM”) device 32a-c through an address bus 36, a control bus 38, and a data bus 42. The locations in each of the DRAMs 32a-c to which data are written and data are read are designated by addresses coupled to the DRAMs 32a-c on the address bus 36. The operation of the DRAMs 32a-c are controlled by control signals coupled to the DRAMs 32a-c on the control bus 38.

[0019] In oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More