Apparatus, system, and method for bus link width optimization

a technology of bus link width and system, applied in the field of apparatus, system and method for bus link width optimization, can solve the problems achieve the effects of reducing bus power requirements, high bandwidth, and reducing bandwidth requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

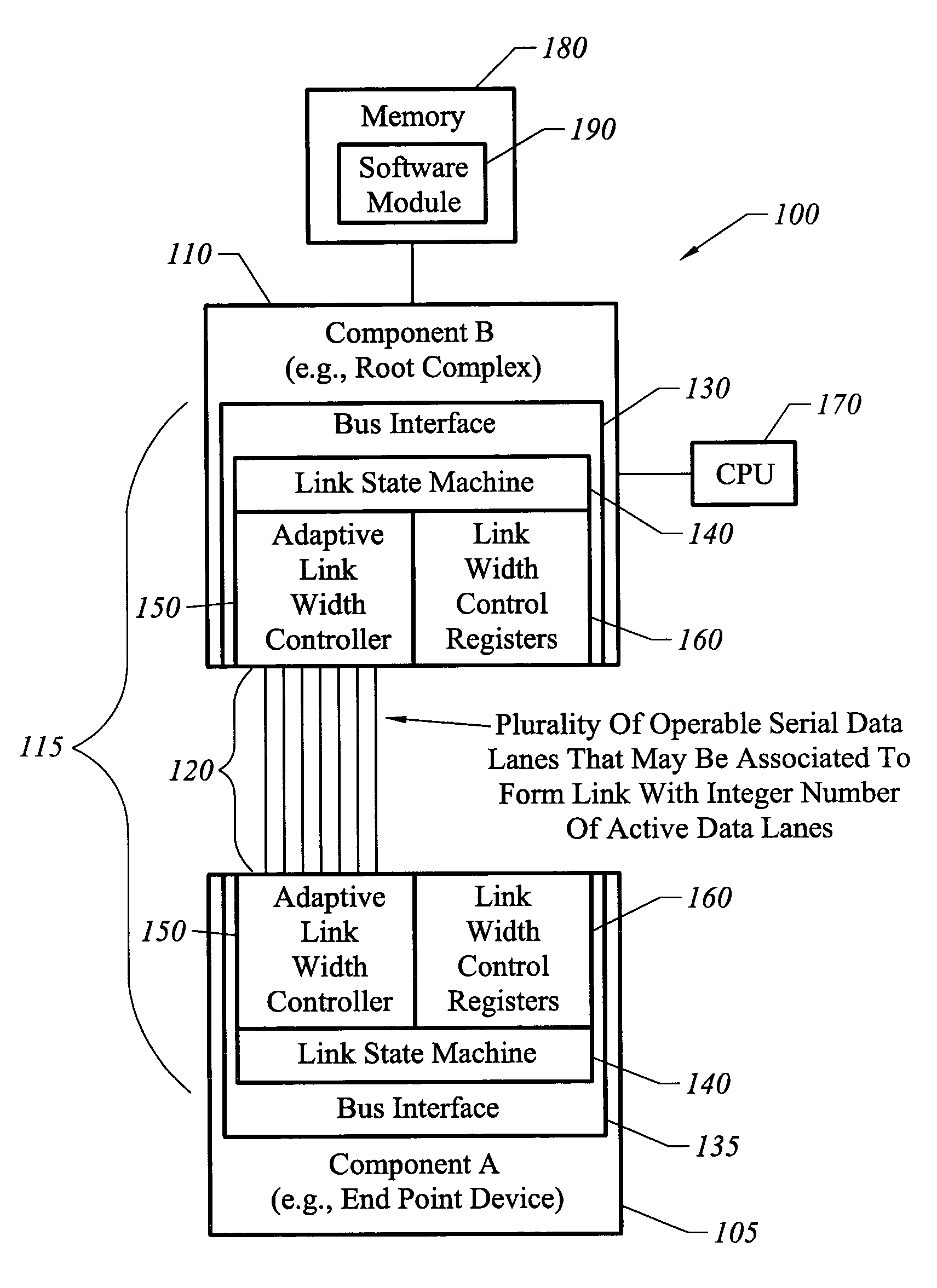

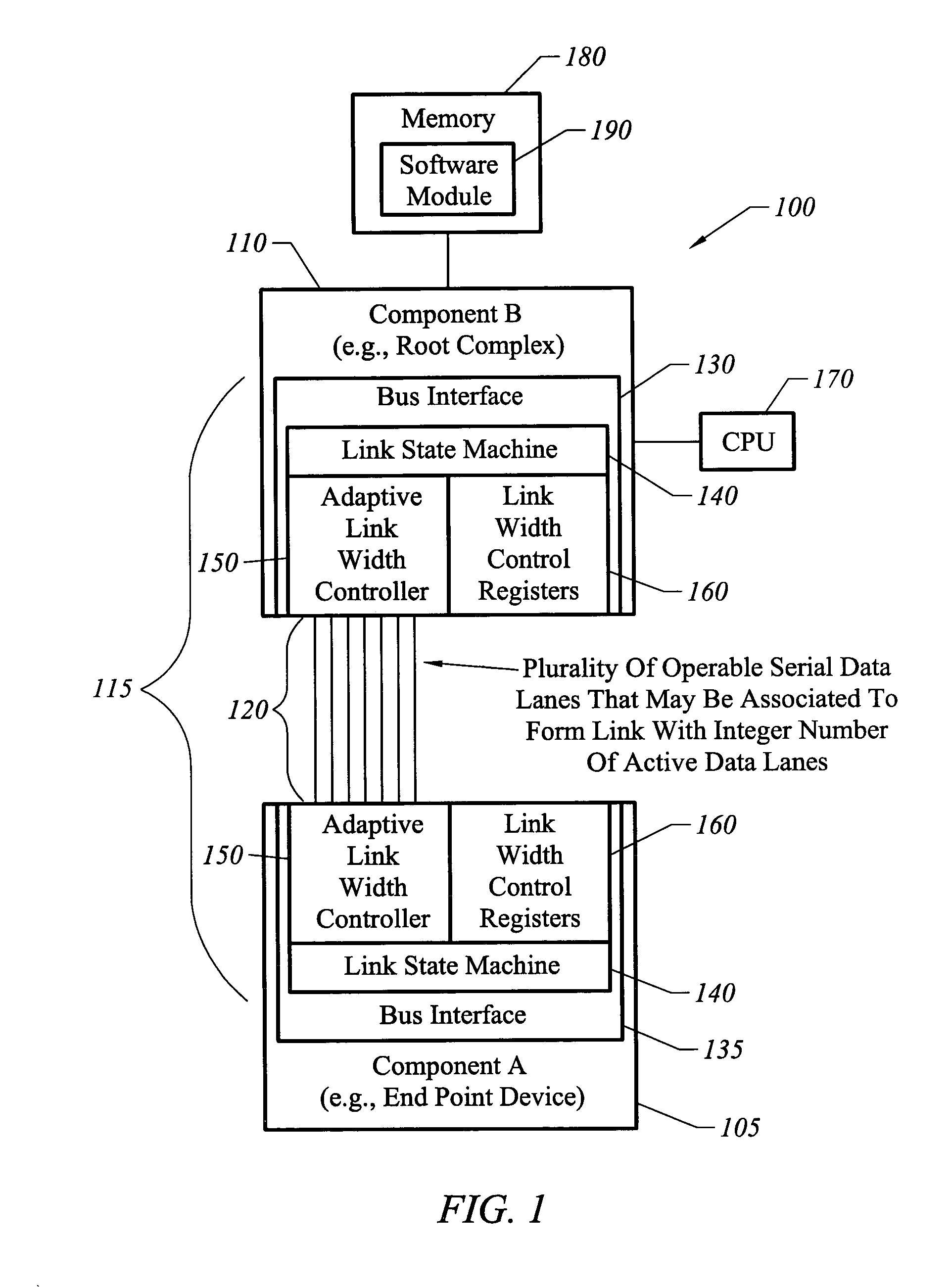

[0026]The present invention is directed towards an apparatus, system, and method for adaptively adjusting bus bandwidth. FIG. 1 is an illustrative block diagram of a system 100 in accordance with one embodiment of the present invention. Referring to FIG. 1, system 100 includes two components 105 and 110 that are communicatively coupled by a data bus 115 comprised of a plurality of serial data lanes 120 and bus interfaces 130 and 135.

[0027]In some embodiments, bus 115 is part of a system in which a first component 105 is an end-point device, such as a graphical processing unit (GPU). The other component 110 may correspond to a bridge, such as a root complex for peripheral devices. A CPU 170 and memory 180 having executable software instructions 190 may be coupled to component 110. However, it will be understood in the following description that bus 115 may be utilized in a variety of systems other than that illustrated in FIG. 1.

[0028]In one embodiment, each of the serial data lanes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More