Patents

Literature

56results about How to "Secure characteristic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

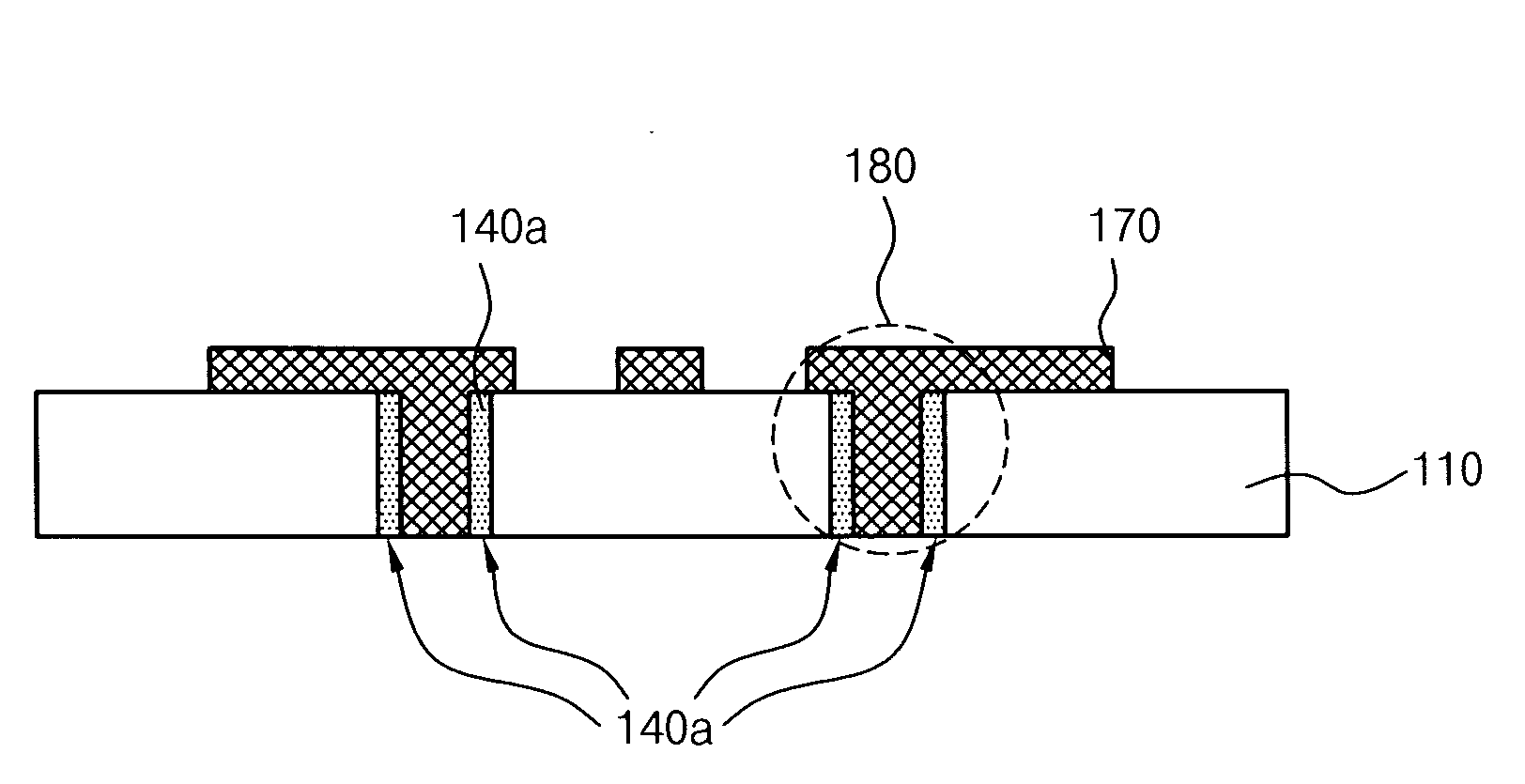

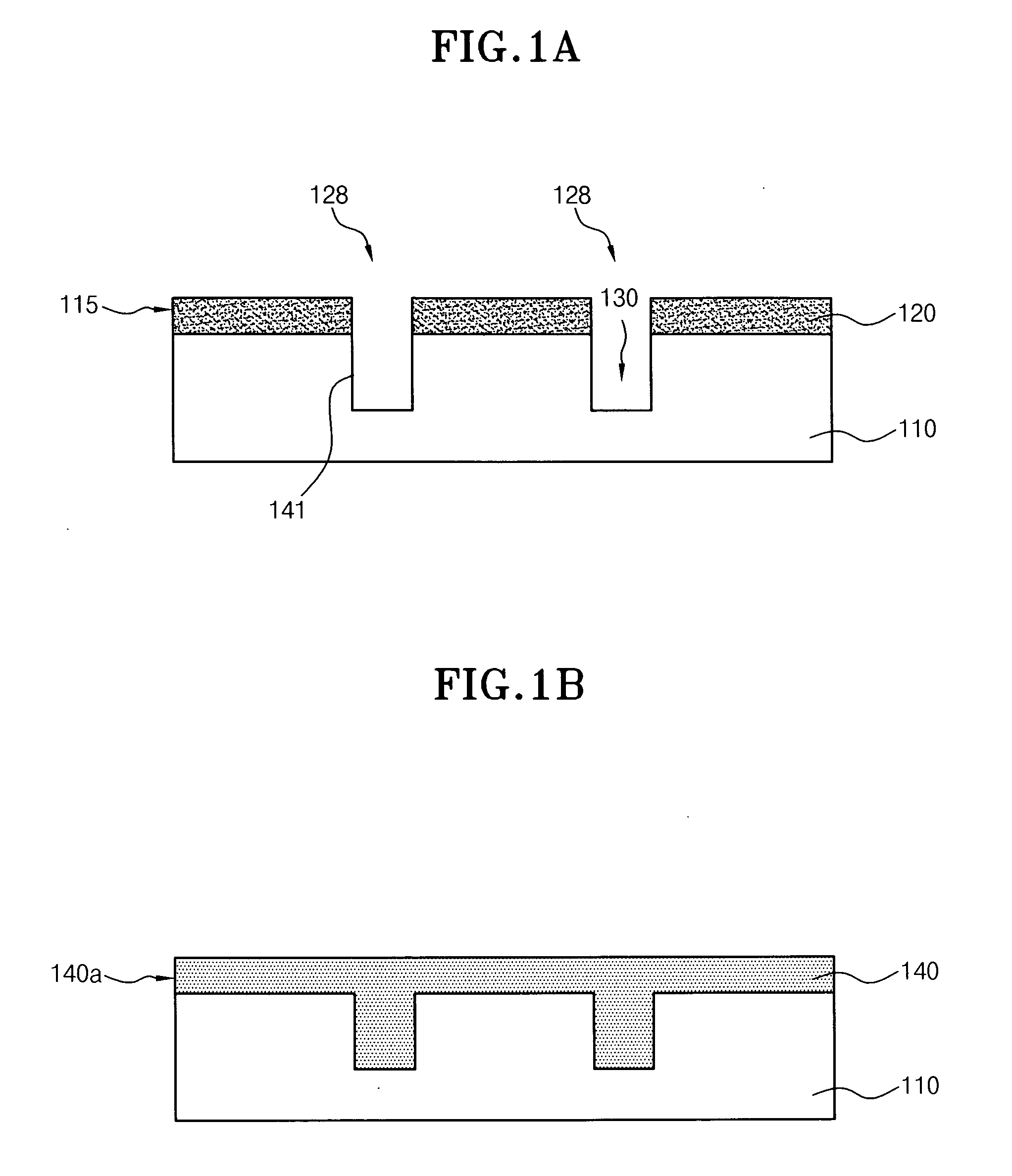

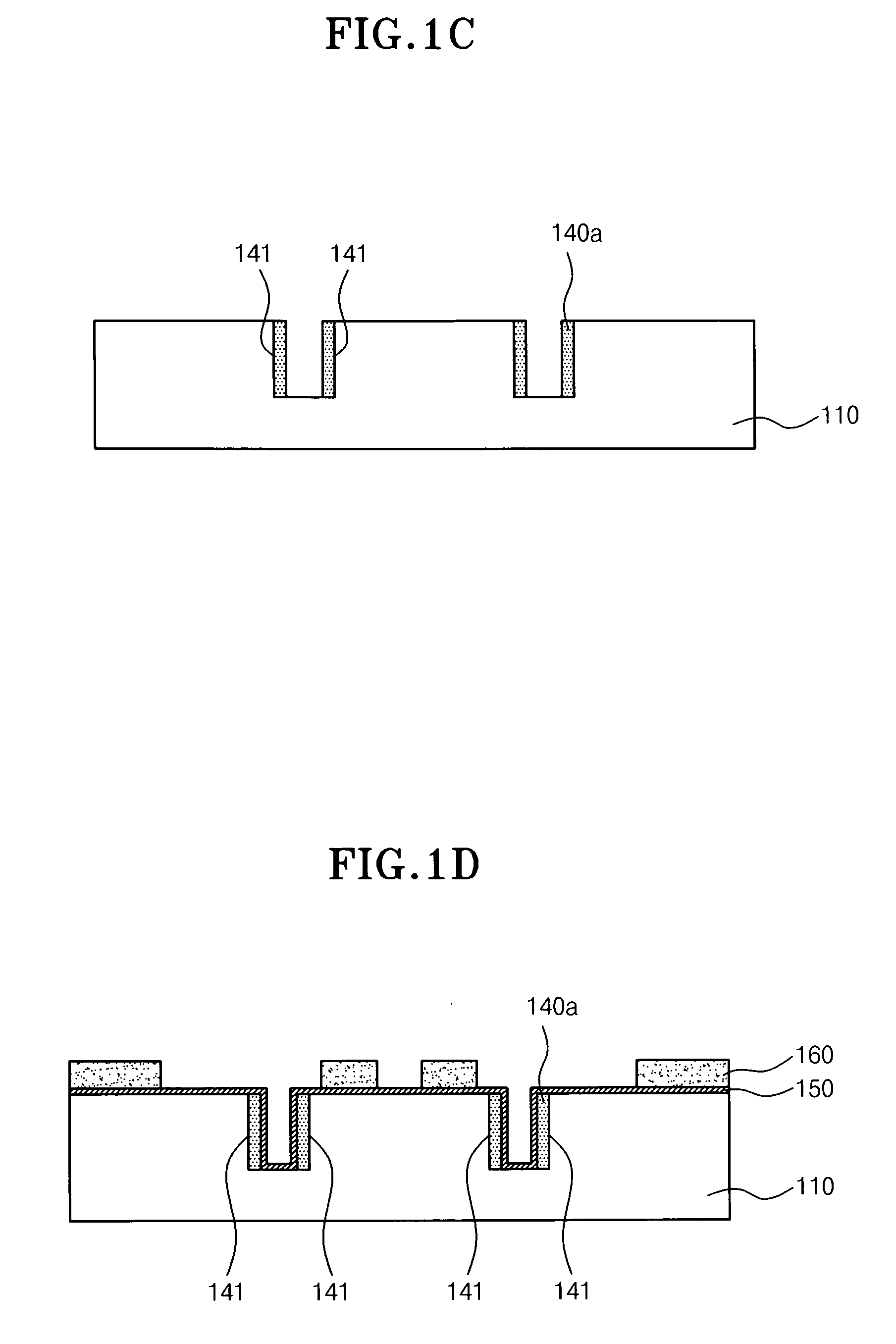

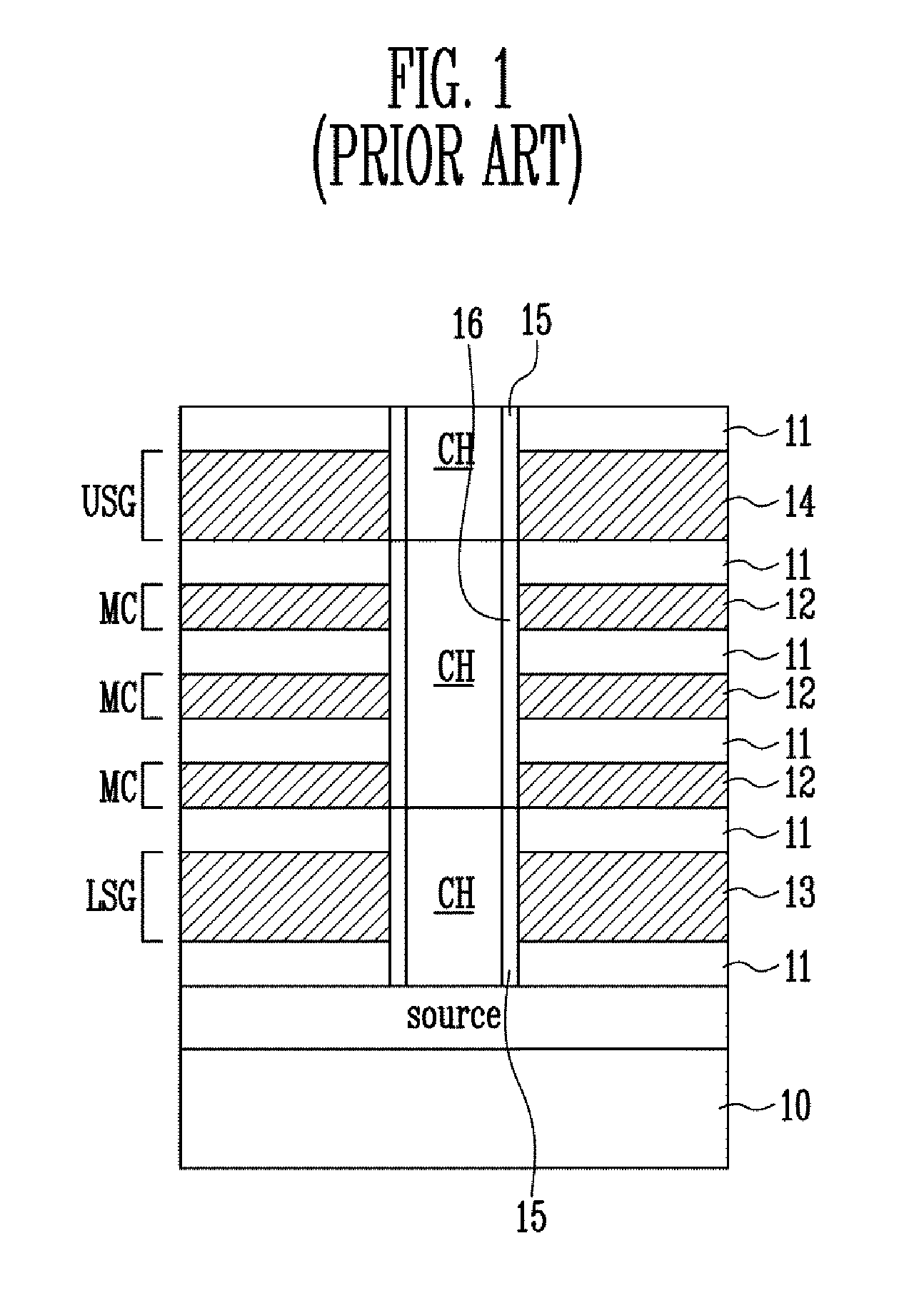

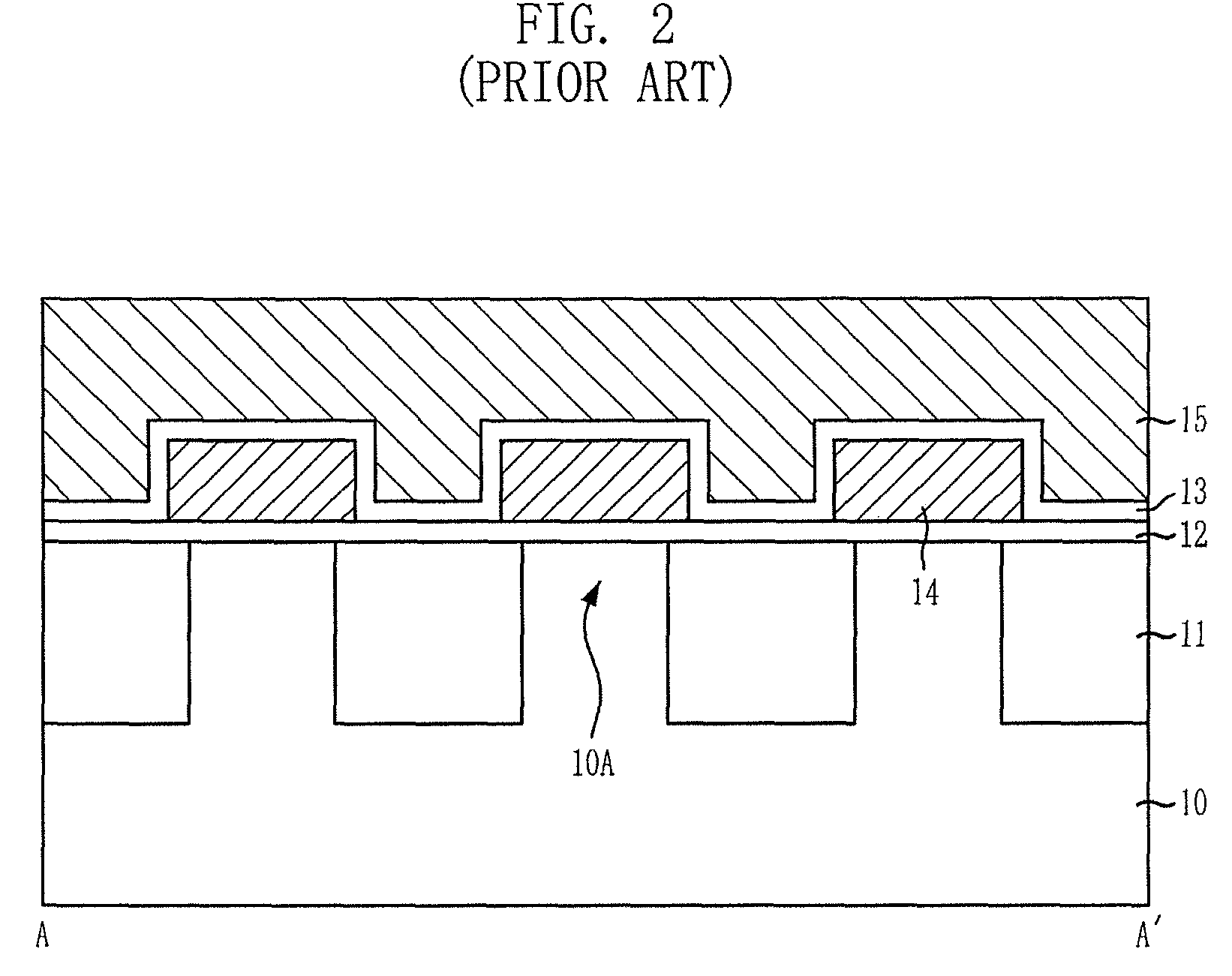

Through-silicon via and method for forming the same

InactiveUS20080079121A1Low costSecure characteristicSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

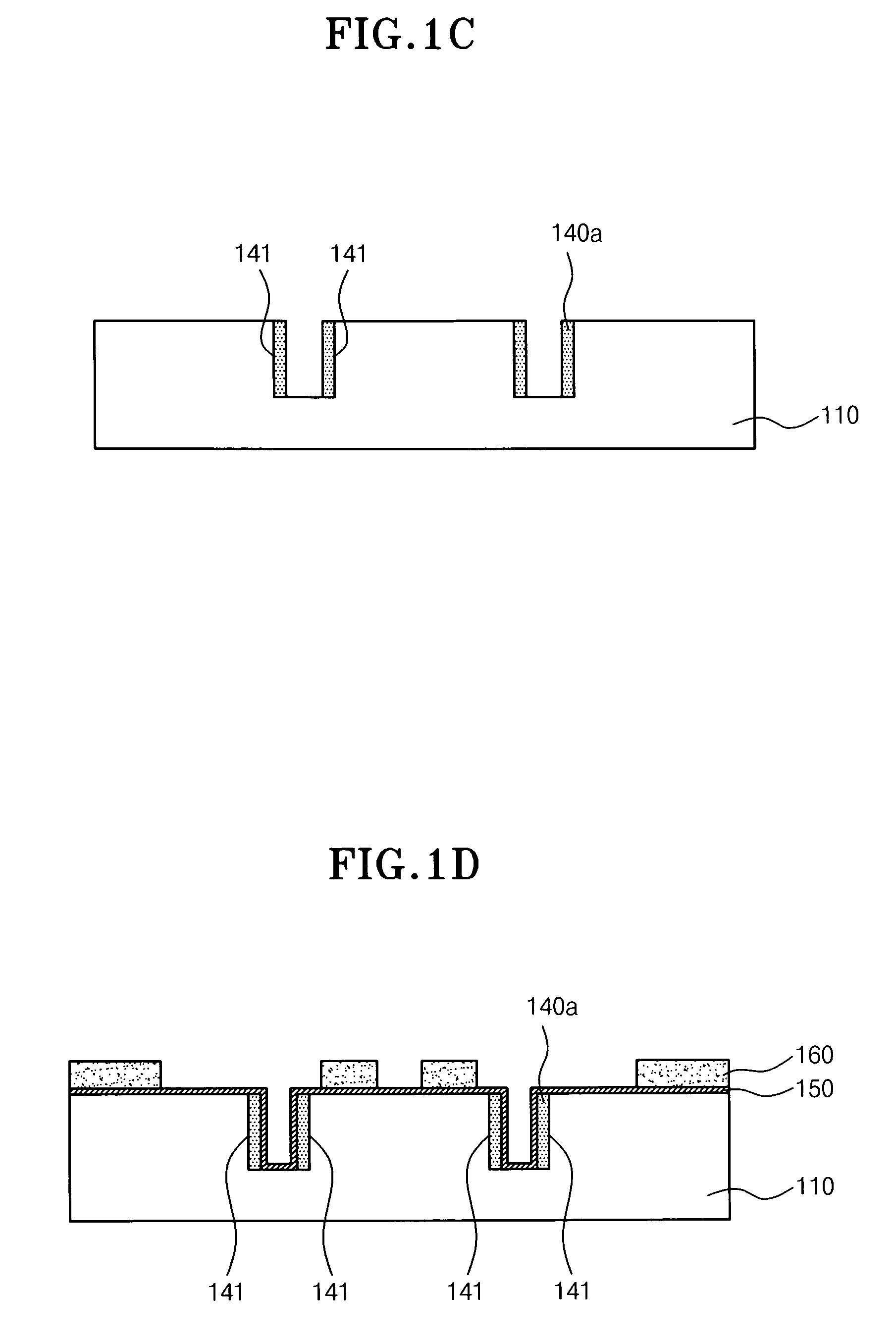

A method for forming a through-silicon via includes the steps of defining a groove in each chip of a wafer which has a plurality of semiconductor chips; applying liquid polymer on the wafer to fill the groove; forming an insulation layer on a sidewall of the groove through patterning the polymer; forming a metal layer to fill the groove which is formed with the insulation layer on the sidewall thereof; and back-grinding a backside of the wafer to expose the metal layer filled in the groove.

Owner:SK HYNIX INC

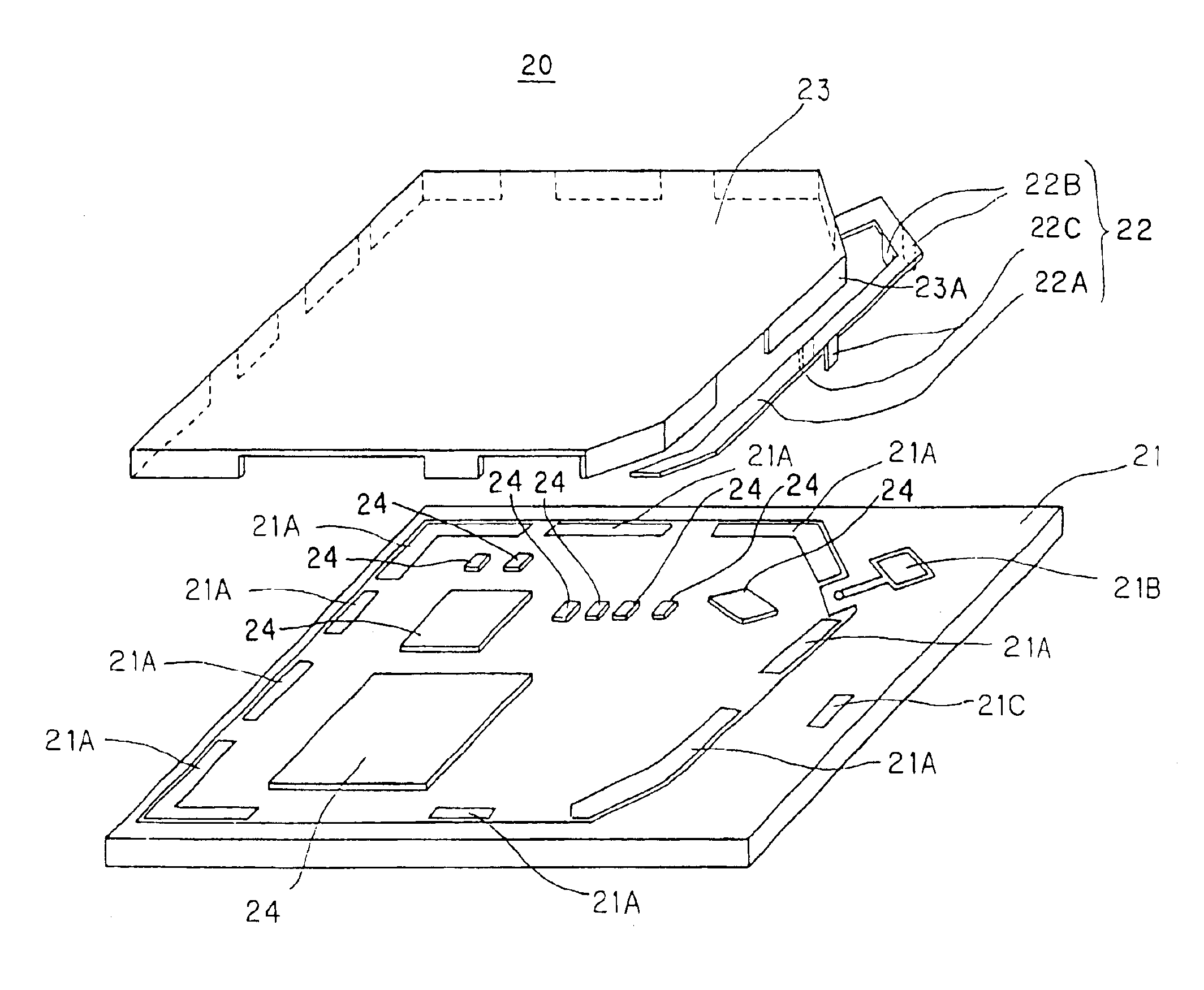

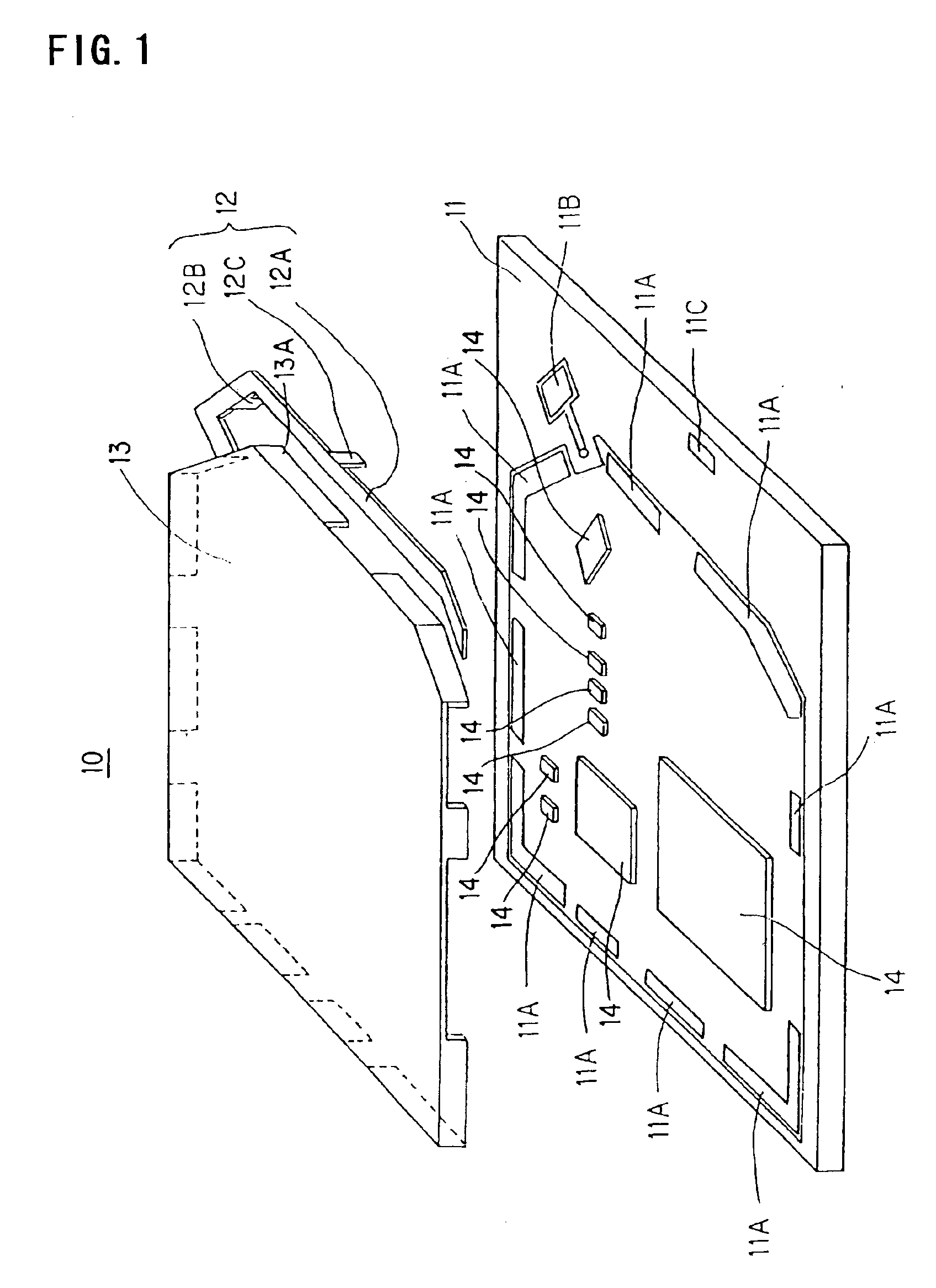

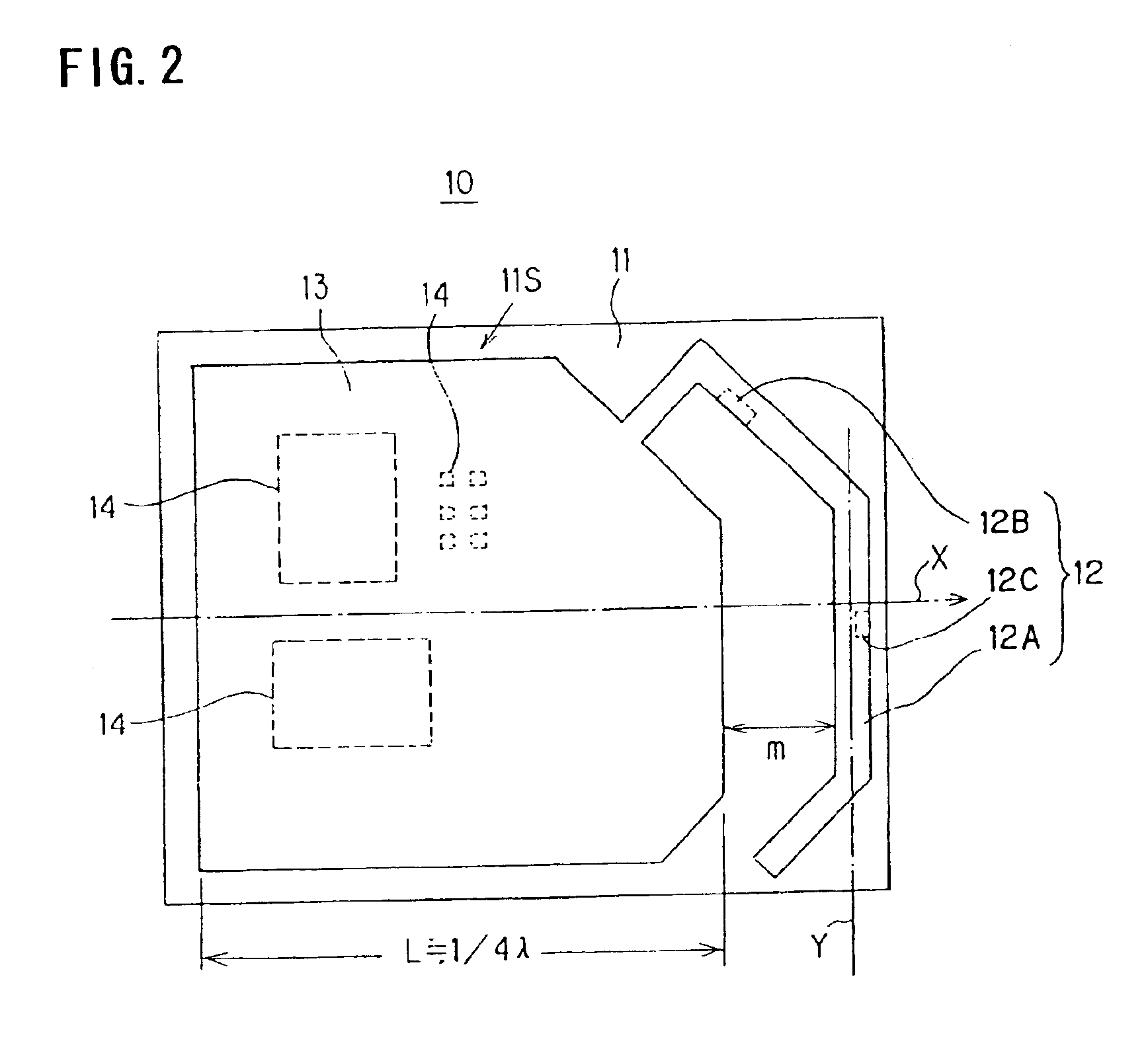

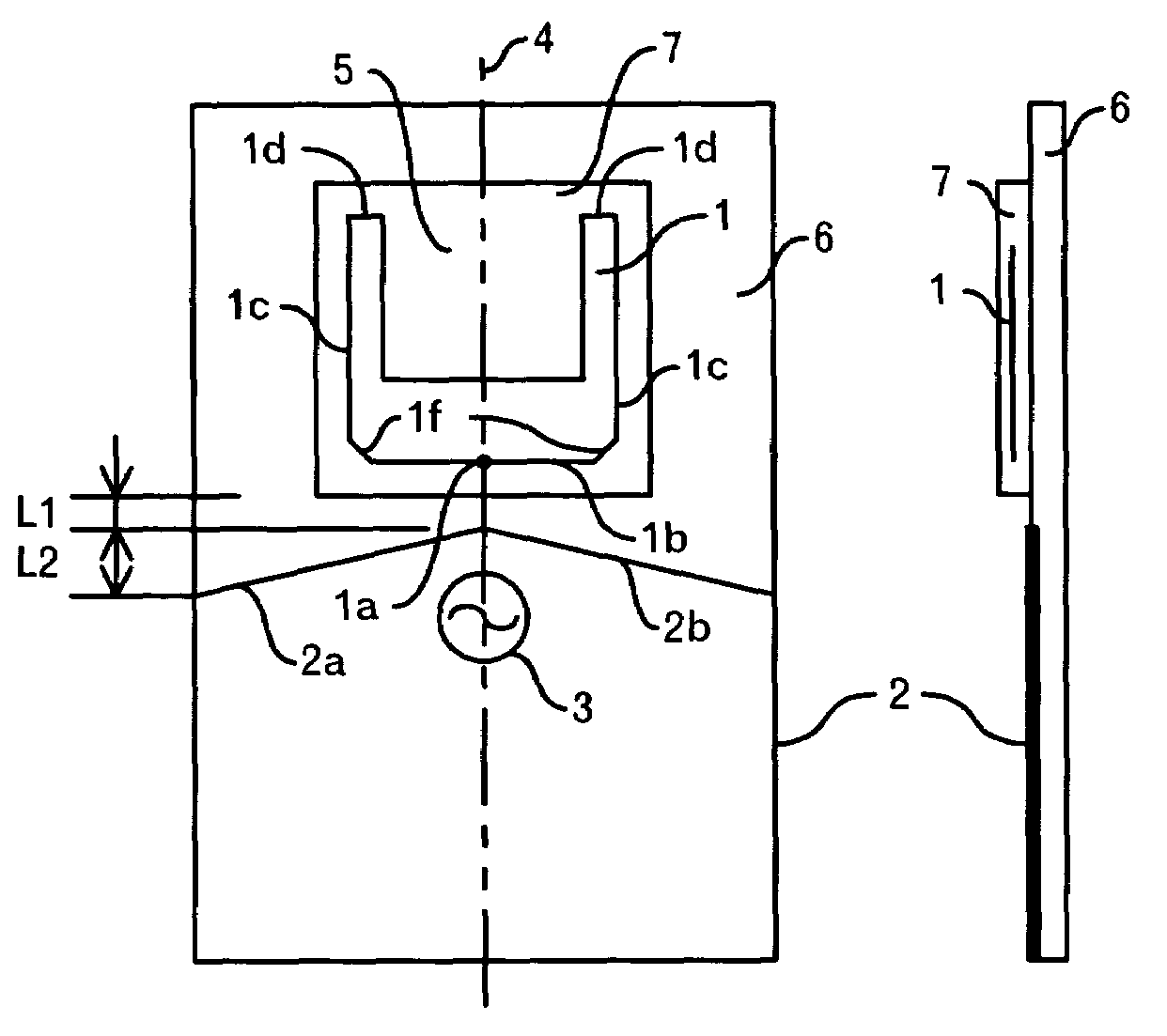

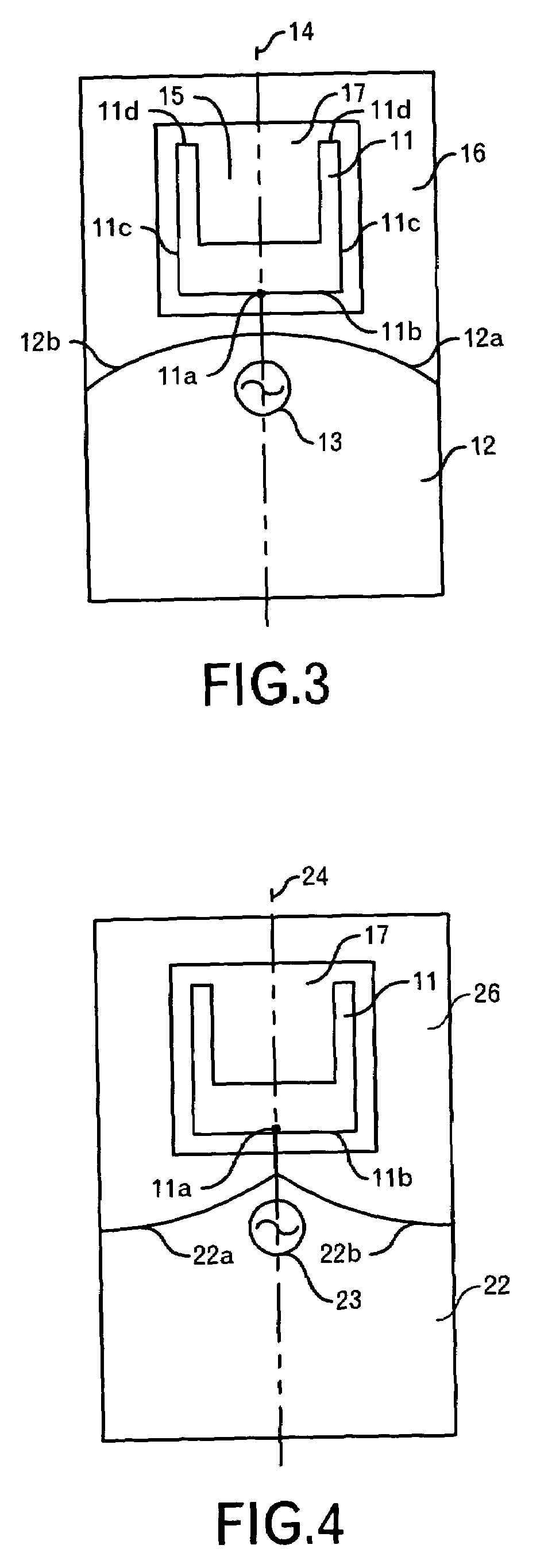

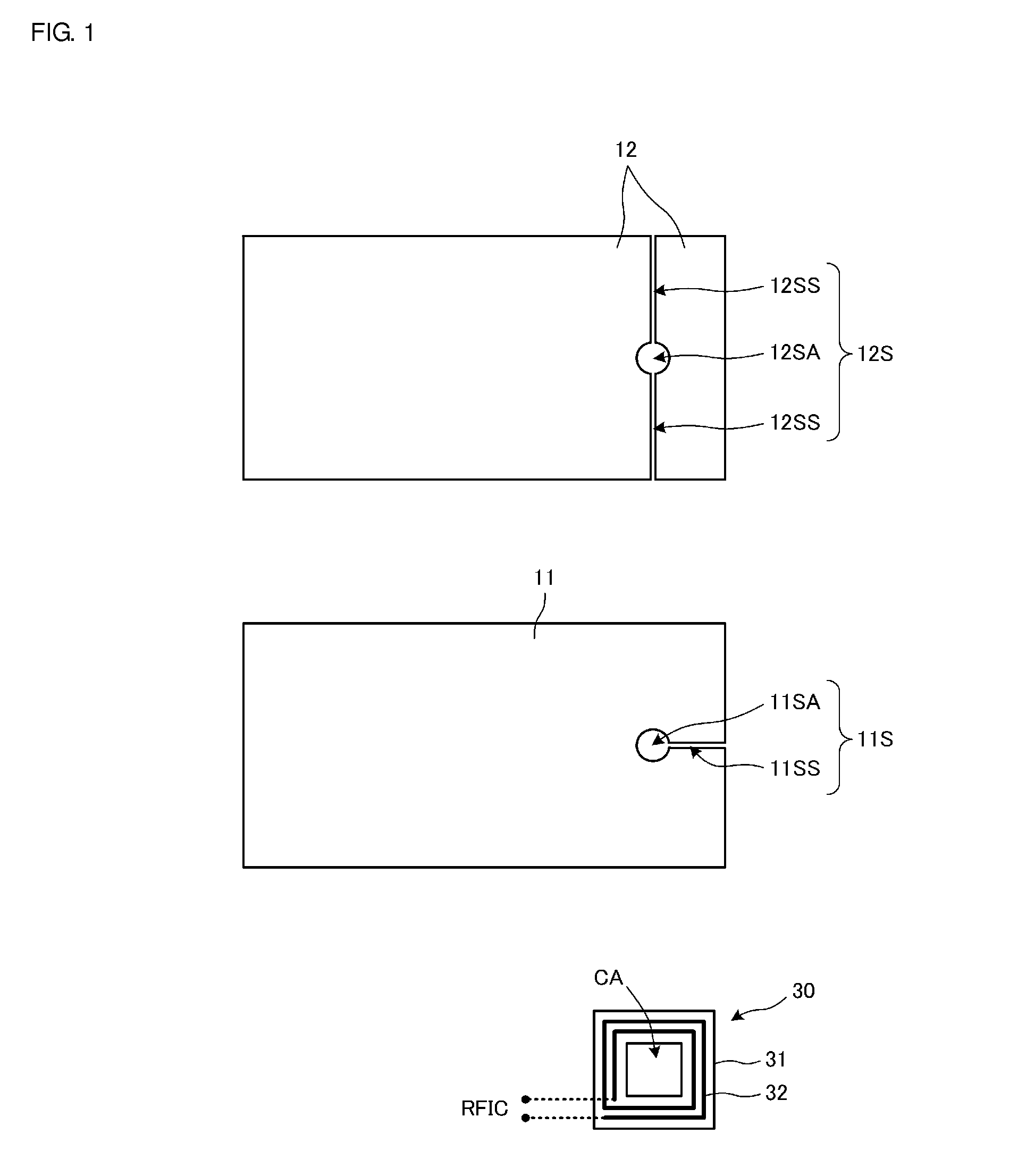

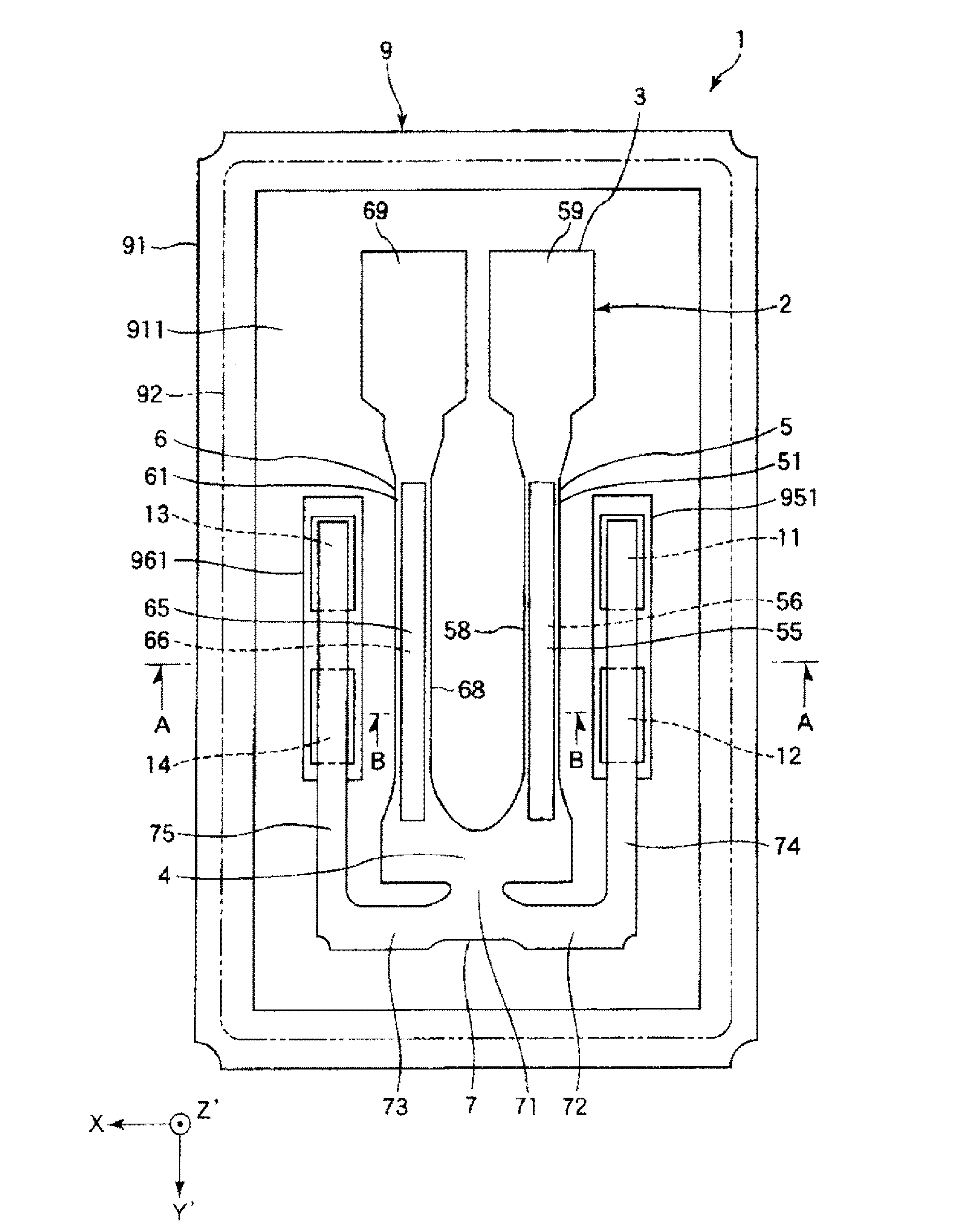

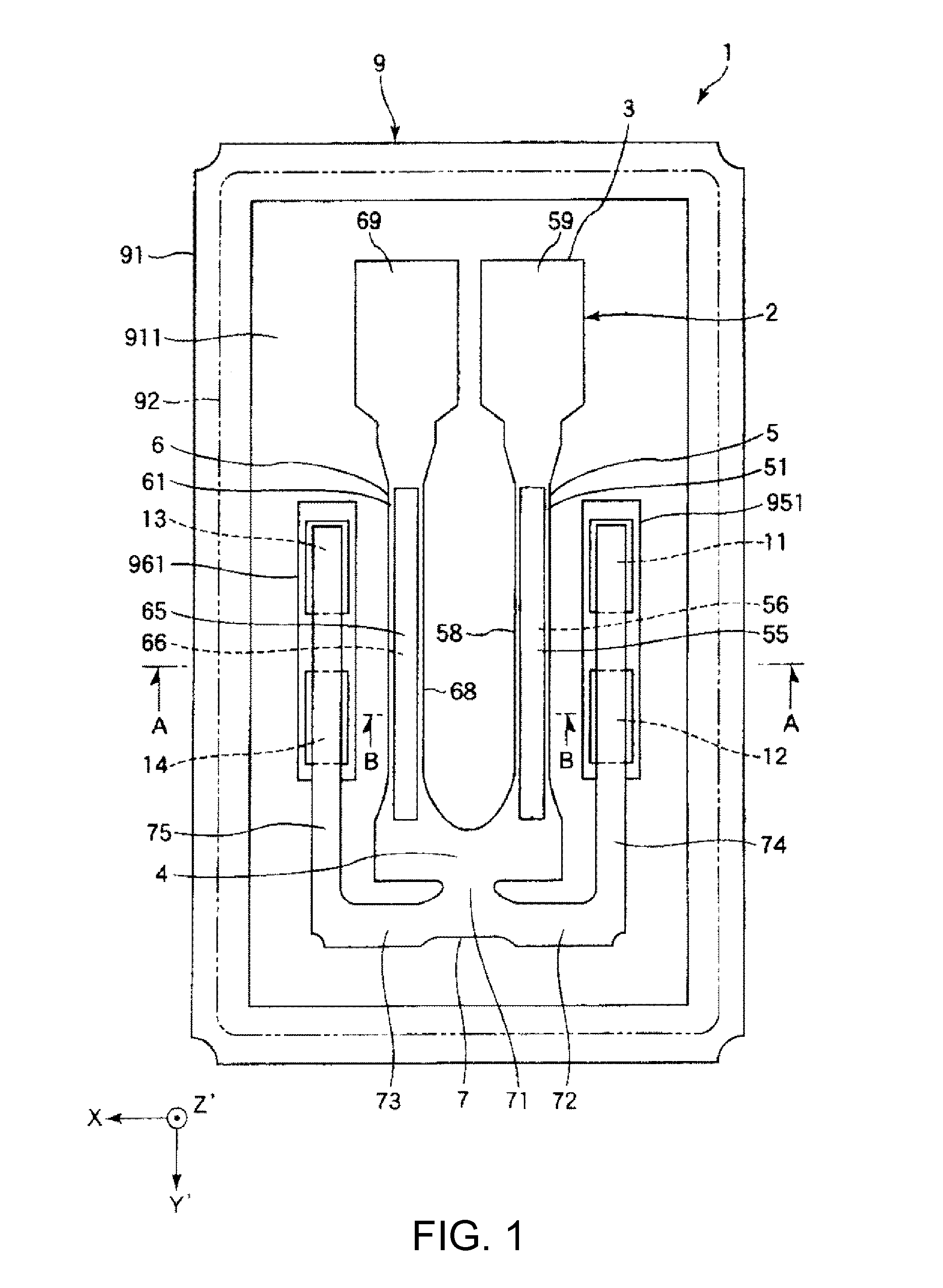

Antenna apparatus, printed wiring board, printed circuit board, communication adapter and portable electronic equipment

ActiveUS6946996B2Improve installation densitySmaller printed wiringSimultaneous aerial operationsAntenna supports/mountingsLength waveElectronic component

An antenna apparatus is provided that includes a printed wiring board, electronic components disposed on the printed wiring board, a shielding member (ground member) that is disposed on the printed wiring board. The shielding member has a length along a predetermined directional axis X set substantially to ¼λ or more, the wavelength of an electromagnetic wave used for communication being λ. An antenna element extends in a direction crossing the directional axis X and is grounded to the shielding member (ground member).

Owner:SEIKO EPSON CORP

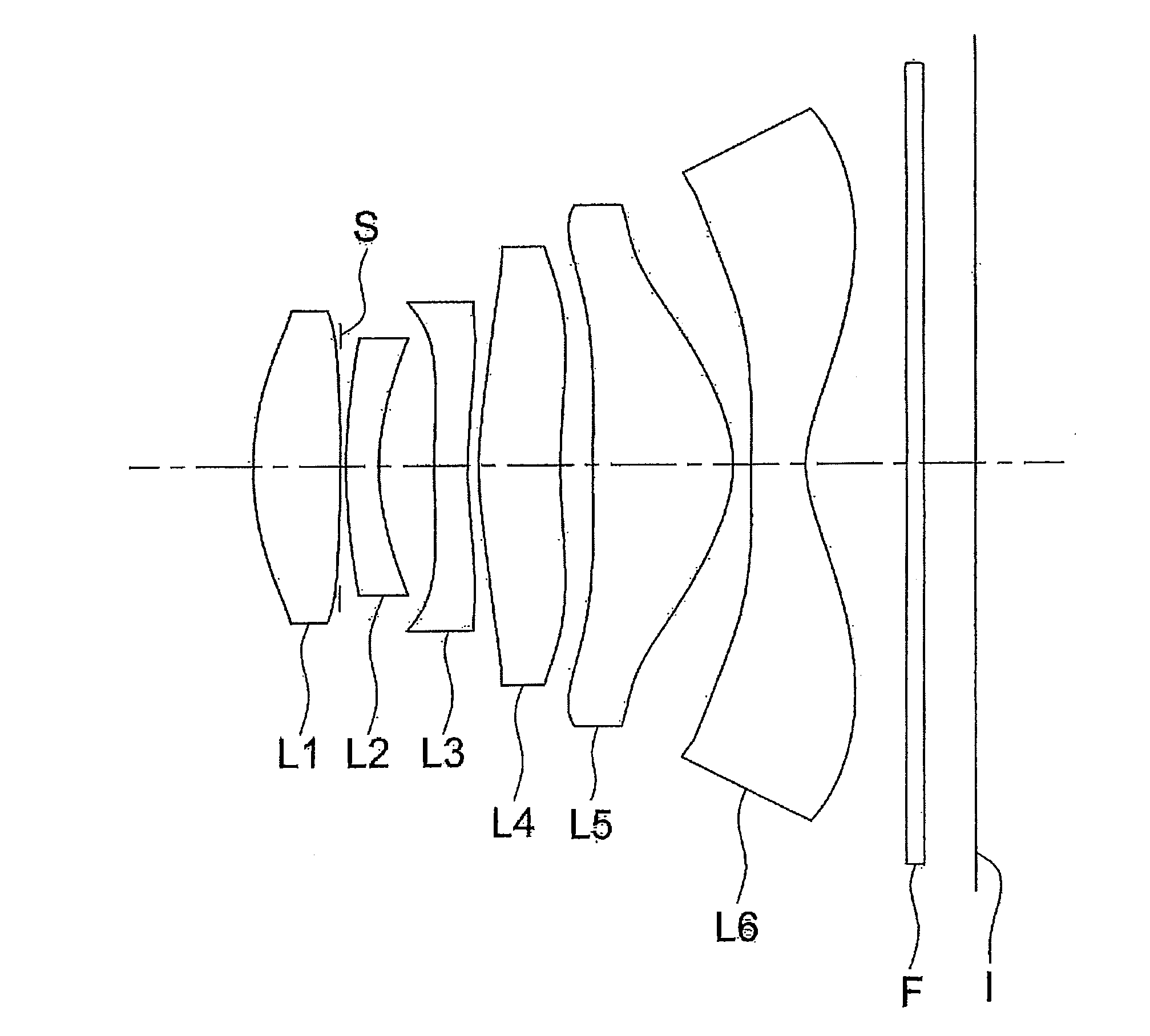

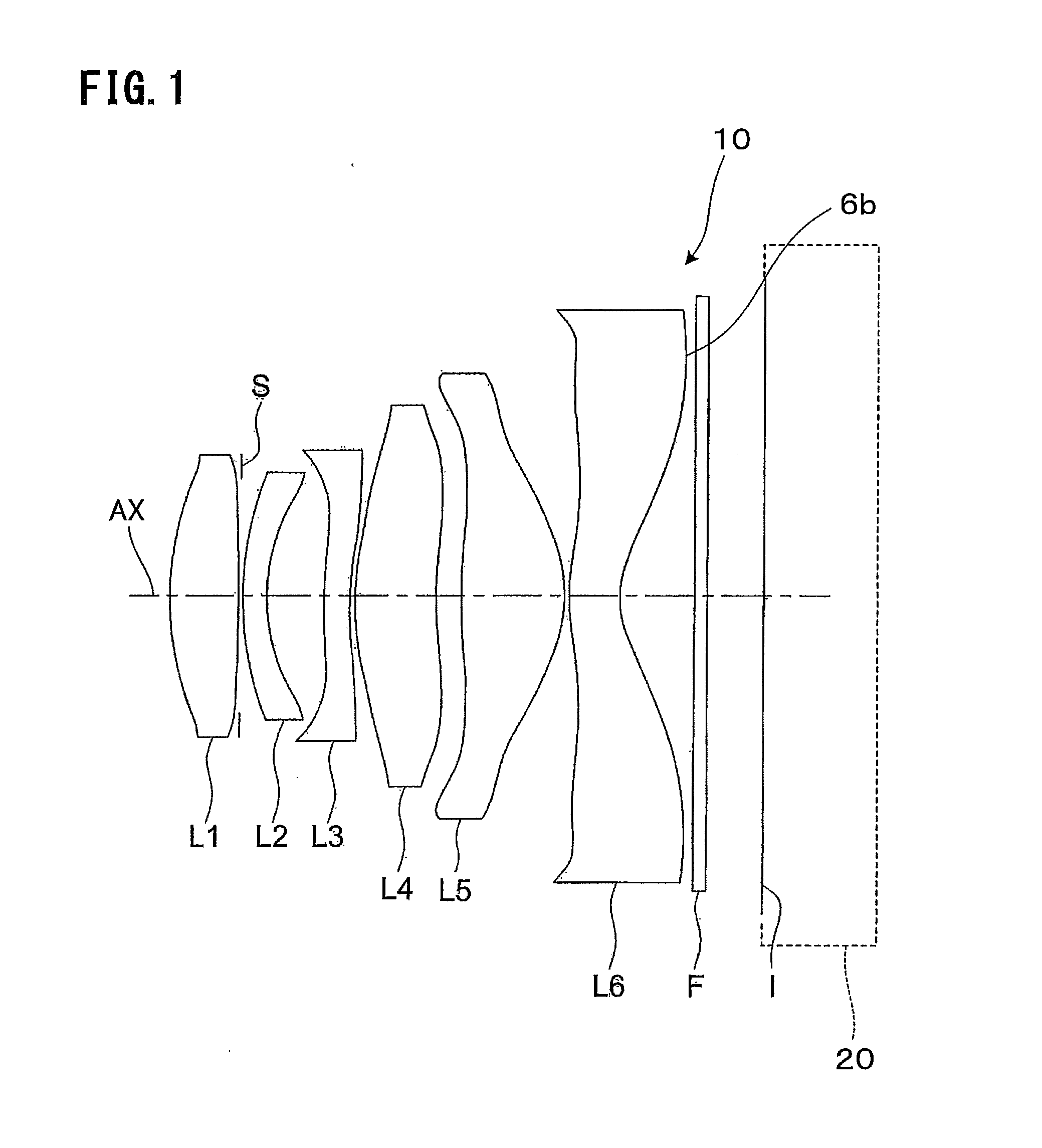

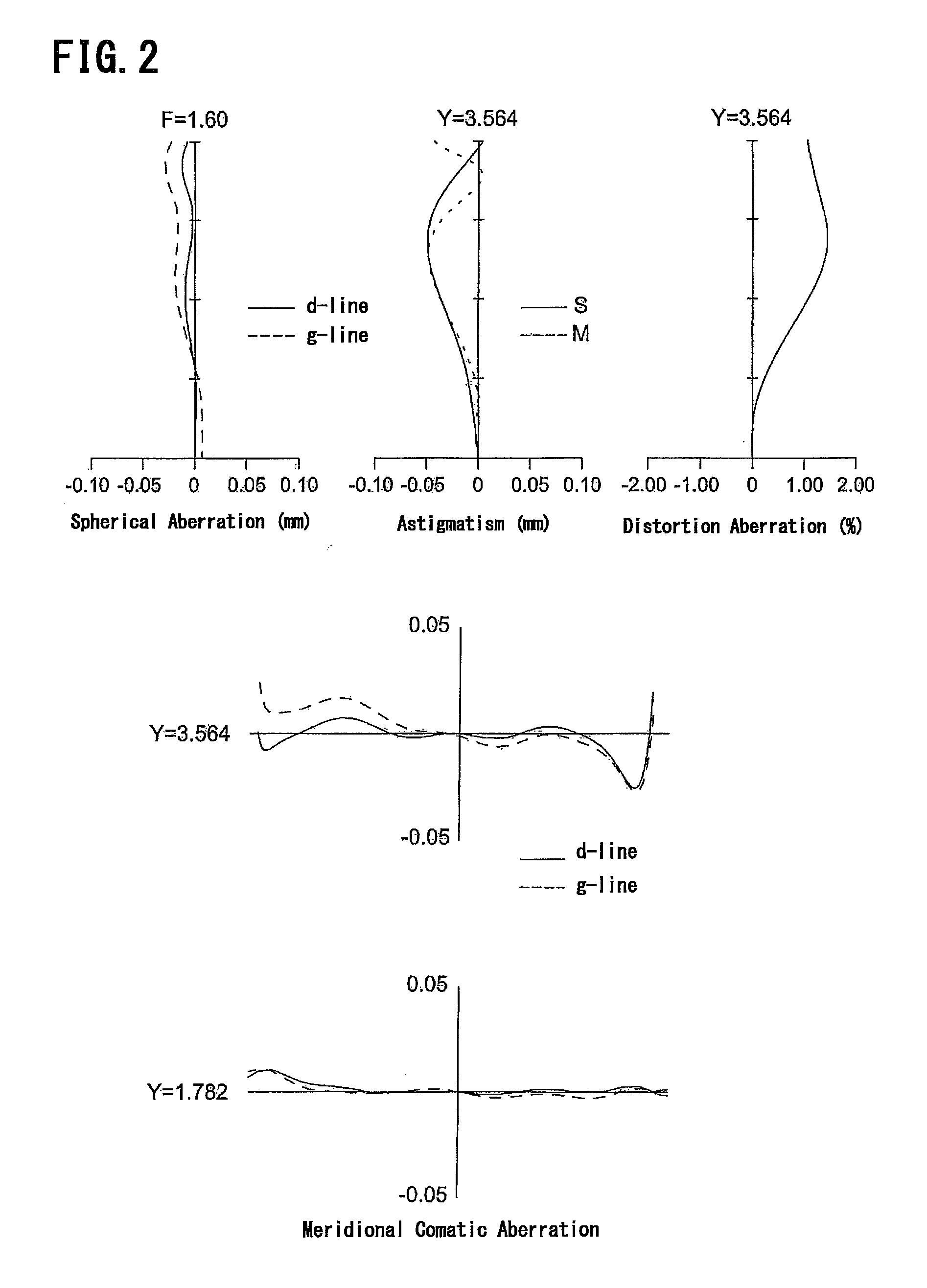

Image Capture Lens

There is provided an image pickup lens having a 6-element structure which has a small size and a sufficiently lens speed of F / 2 or less and in which various aberrations are corrected favorably. This image pickup lens includes a first lens having a positive refractive power and comprising a convex surface directed to the object side; a second lens having a negative refractive power and comprising a concave surface directed to the image side; a third lens having a positive or negative refractive power; a fourth lens having a positive refractive power; a fifth lens having a positive refractive power and comprising a convex surface directed to the image side; and a sixth lens having a negative refractive power and comprising a concave surface directed to the image side, in this order from the object side, wherein the image side surface of the sixth lens has an aspherical shape and an inflection point at a position other than an intersection point with the optical axis, and the image pickup lens satisfies the following conditional expressions.ν1>50ν2≦30where,ν1 is an Abbe number of the first lens, andν2 is an Abbe number of the second lens.

Owner:KONICA MINOLTA OPTO

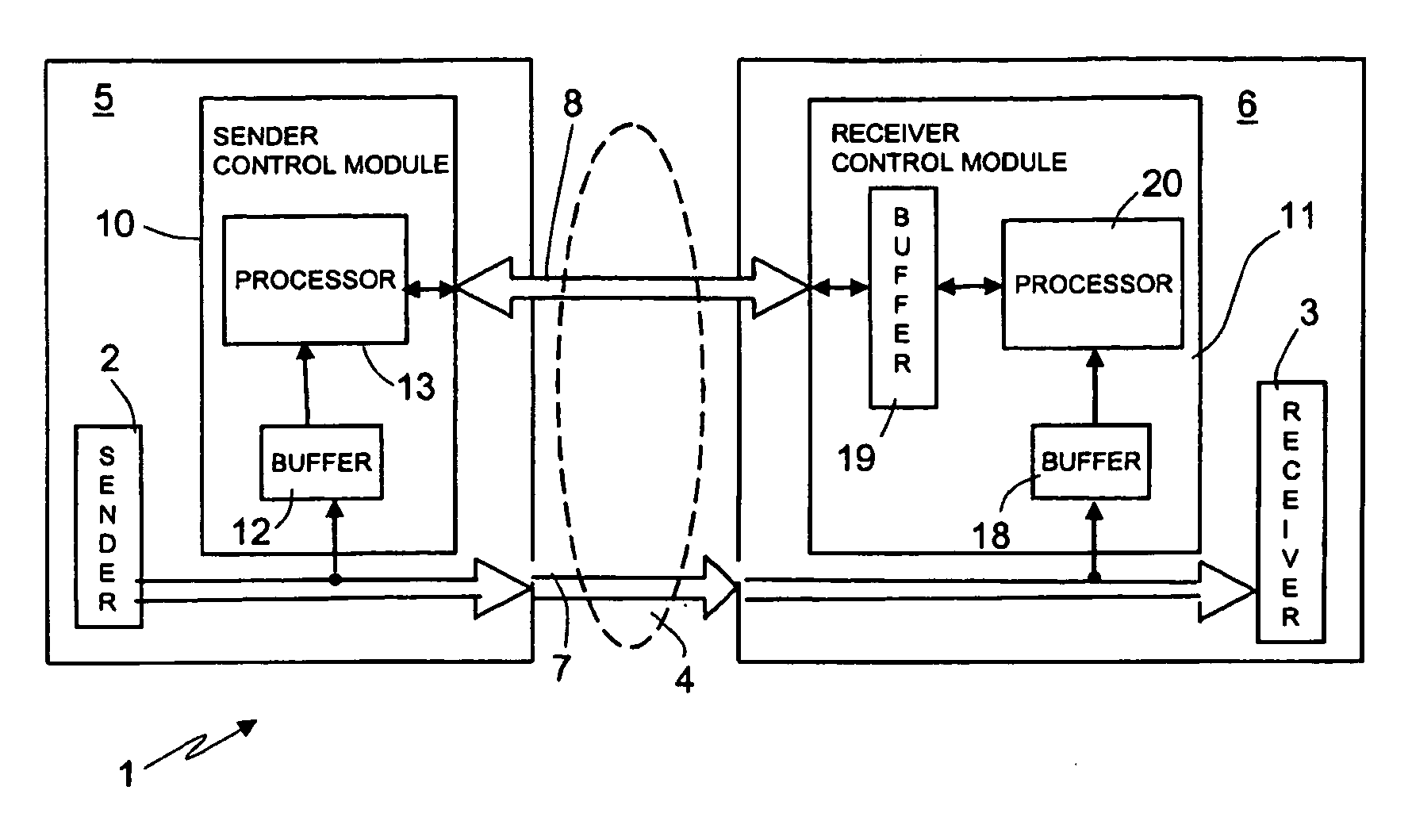

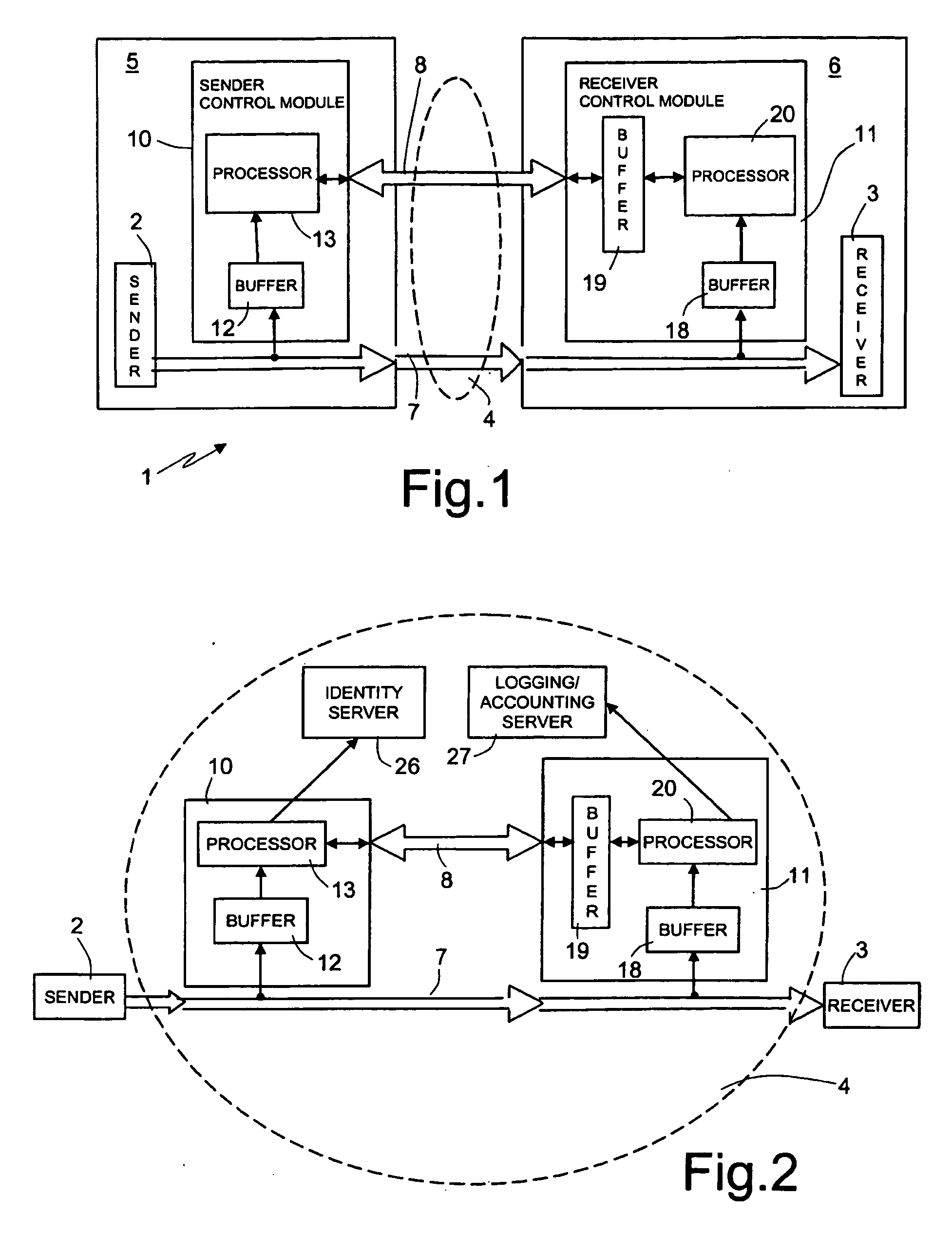

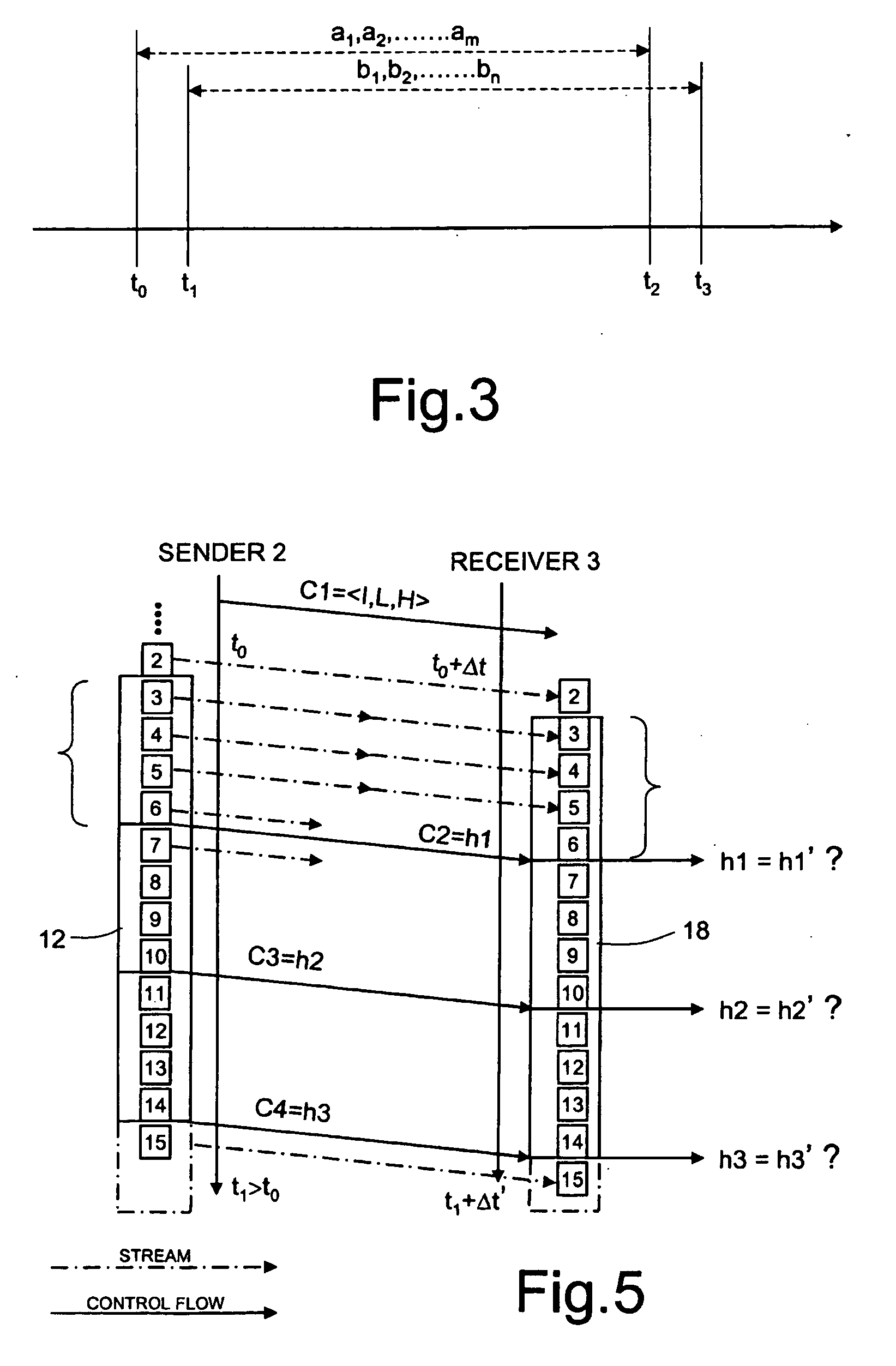

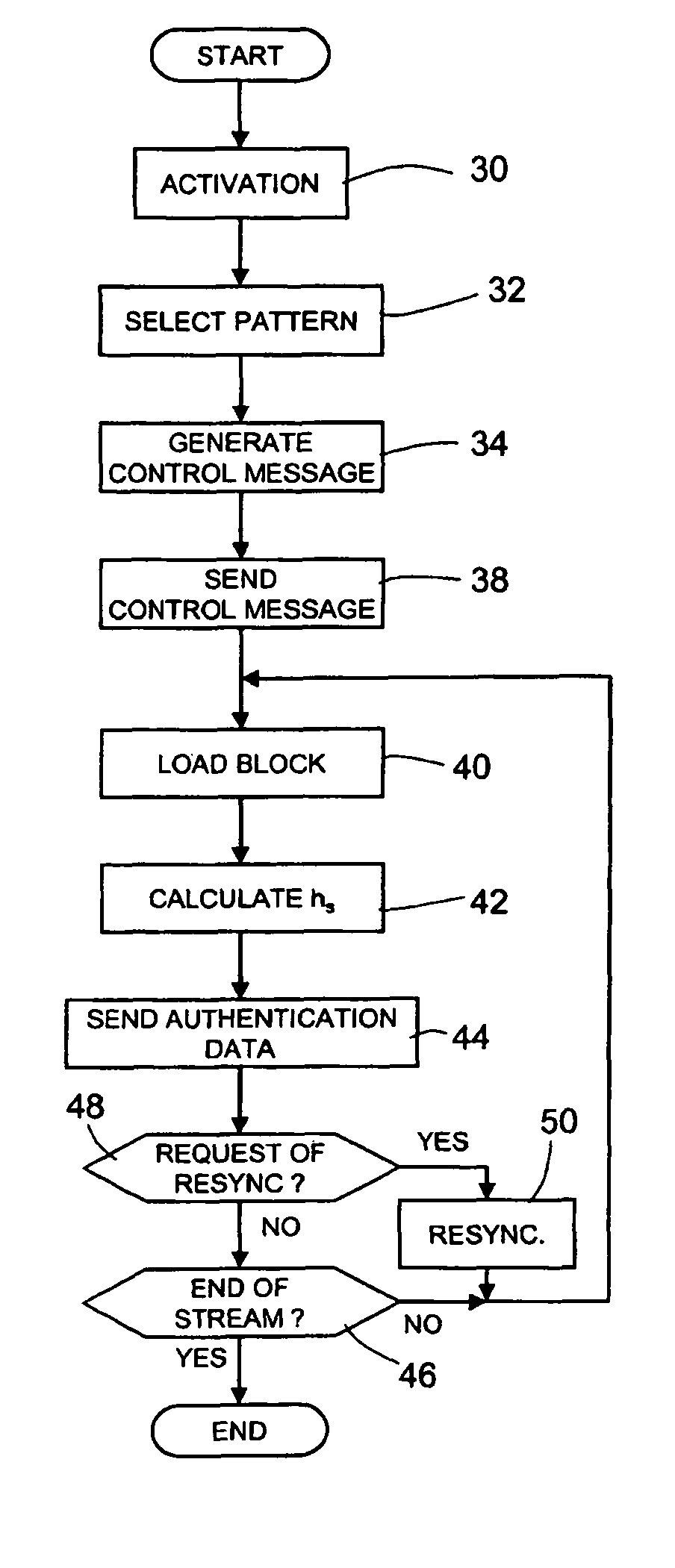

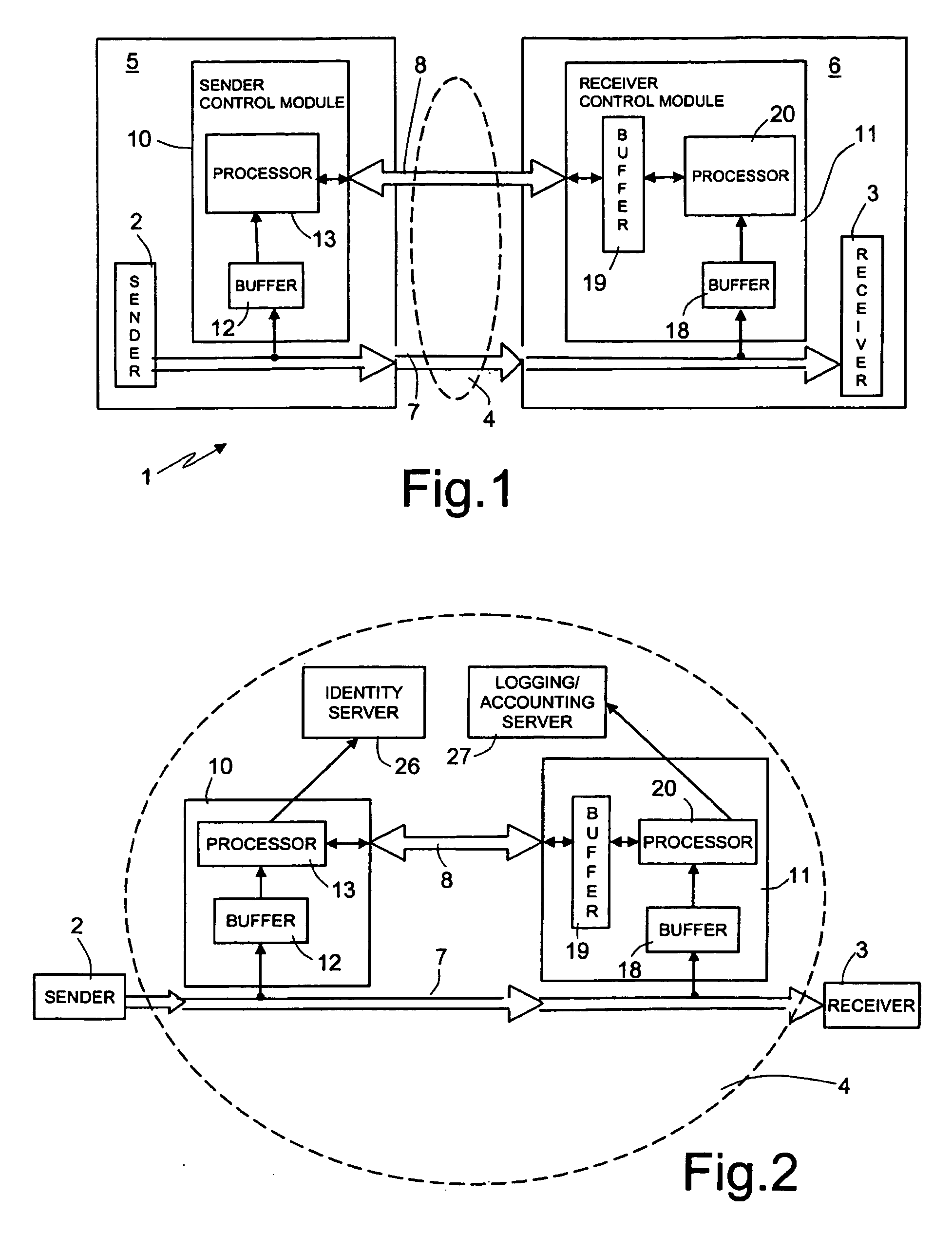

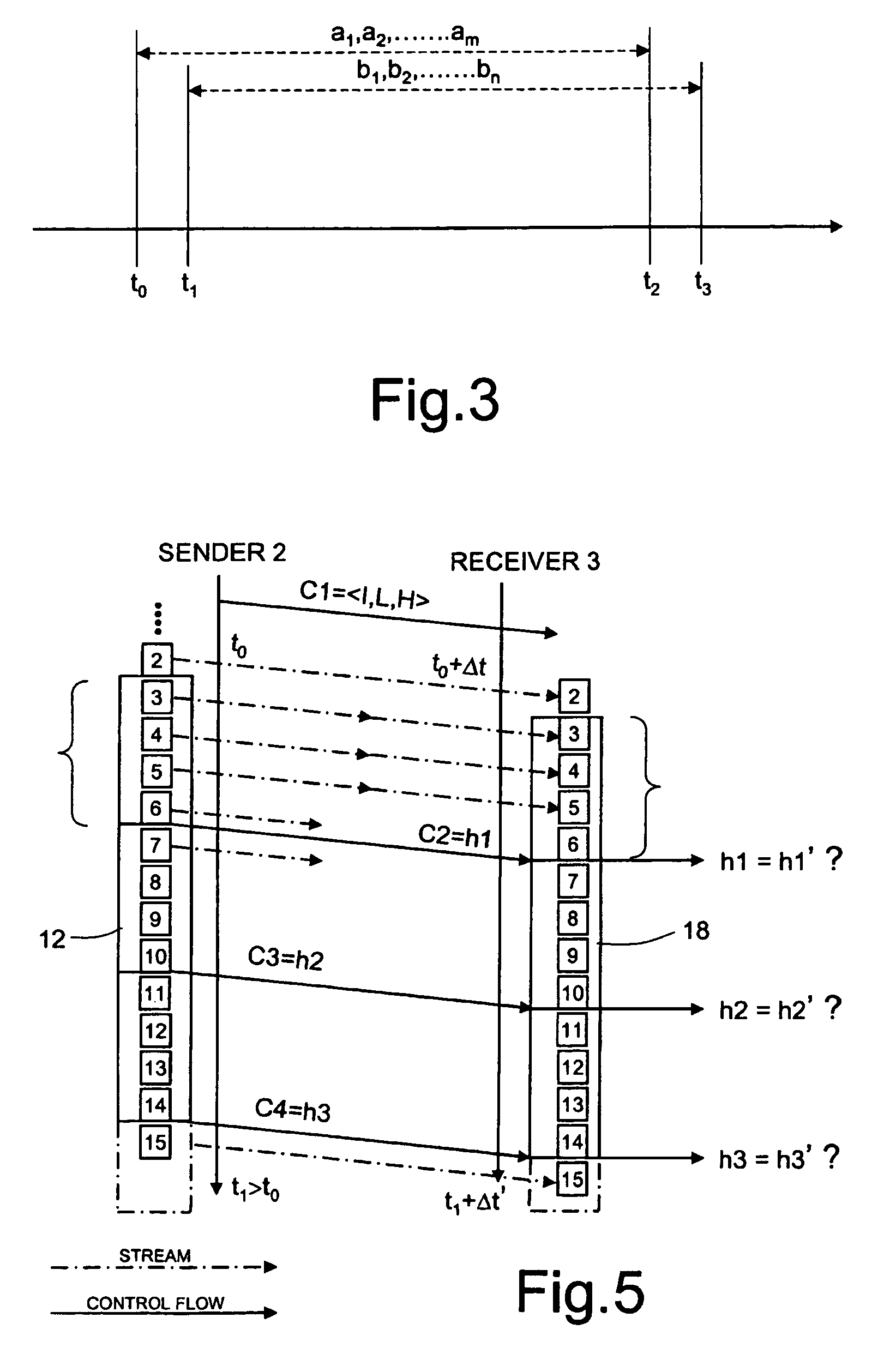

Out-of Band Authentication Method and System for Communication Over a Data Network

ActiveUS20090210707A1Overcomes drawbackSecure characteristicMemory loss protectionError detection/correctionData streamTransmitter

A method and system for out-of-band authentication of messages transmitted, e.g. as packets, on a communication network, whereby a first stream of data is received by a sender control module from a sender; the first stream of data is transmitted over a first channel, e.g. a non-secure data channel, toward a receiver control module; the sender control module generates authentication data of the first stream of data; the authentication data are transmitted from the sender control module to the receiver control module on a second channel, e.g. a secure data channel, distinct from the first channel; and a stream of data received by the receiver control module is checked using the authentication data. Before sending the authentication data, the sender control module transmits a control message including synchronization data to the receiver control module over the second channel.

Owner:TELECOM ITALIA SPA

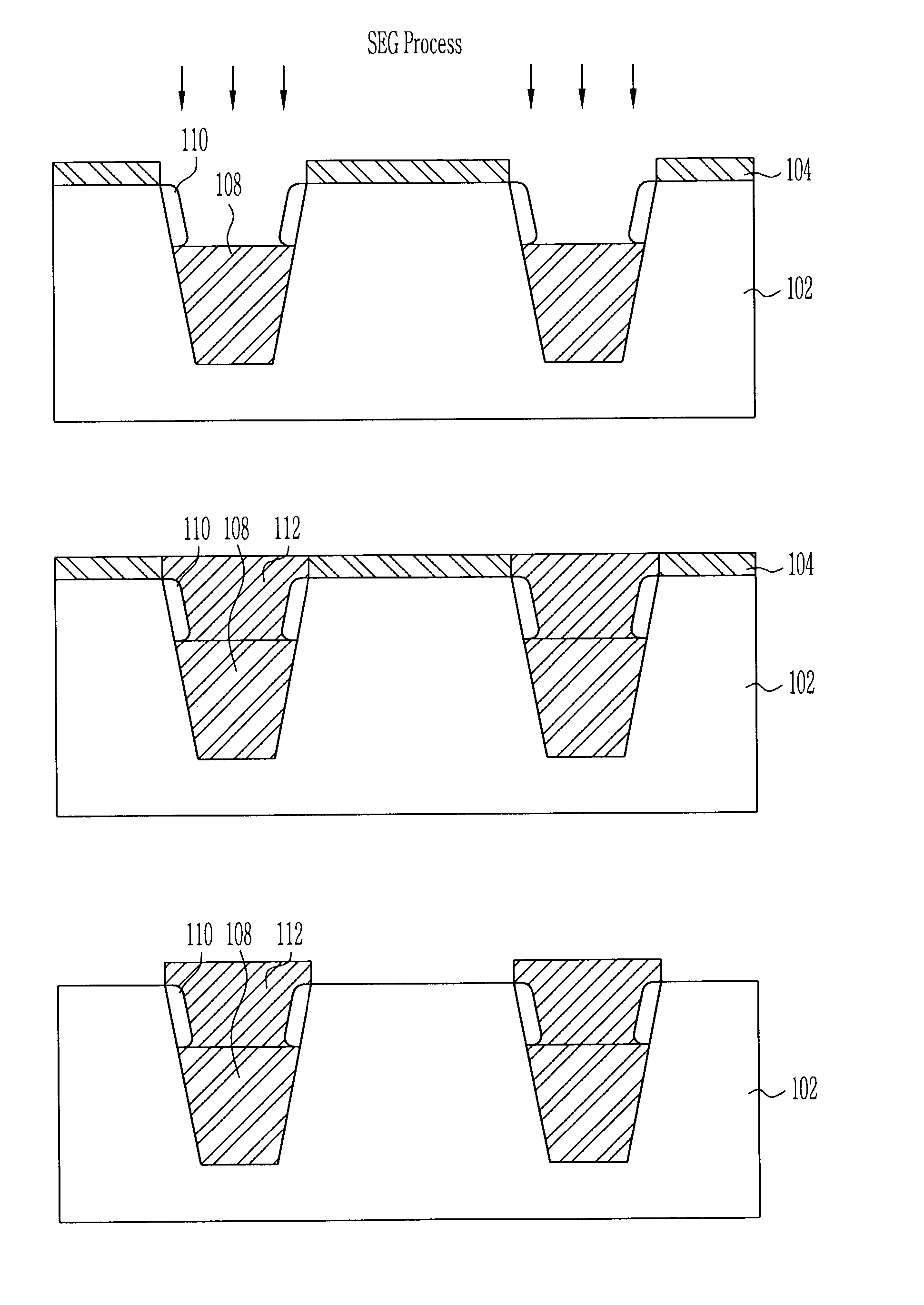

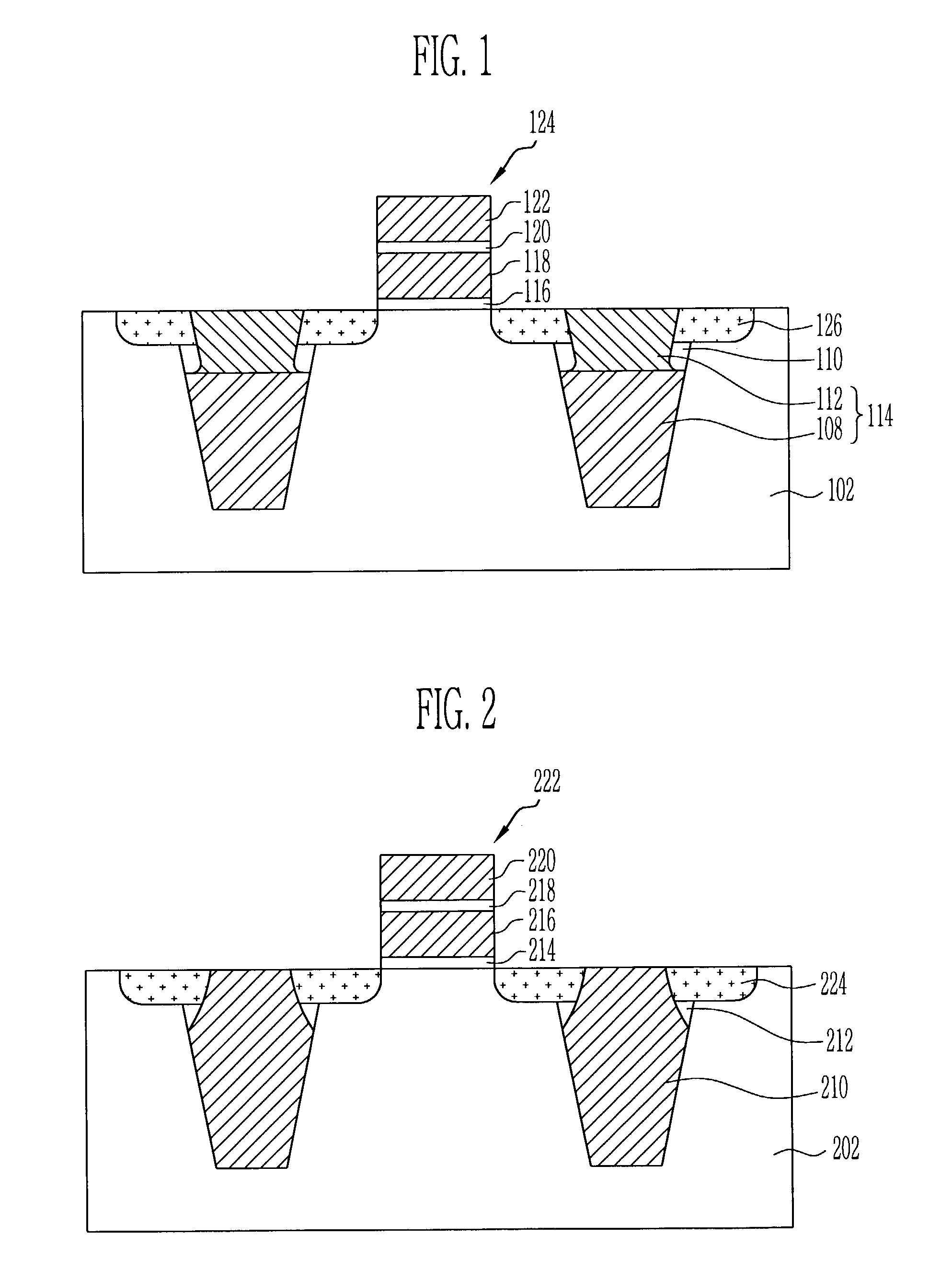

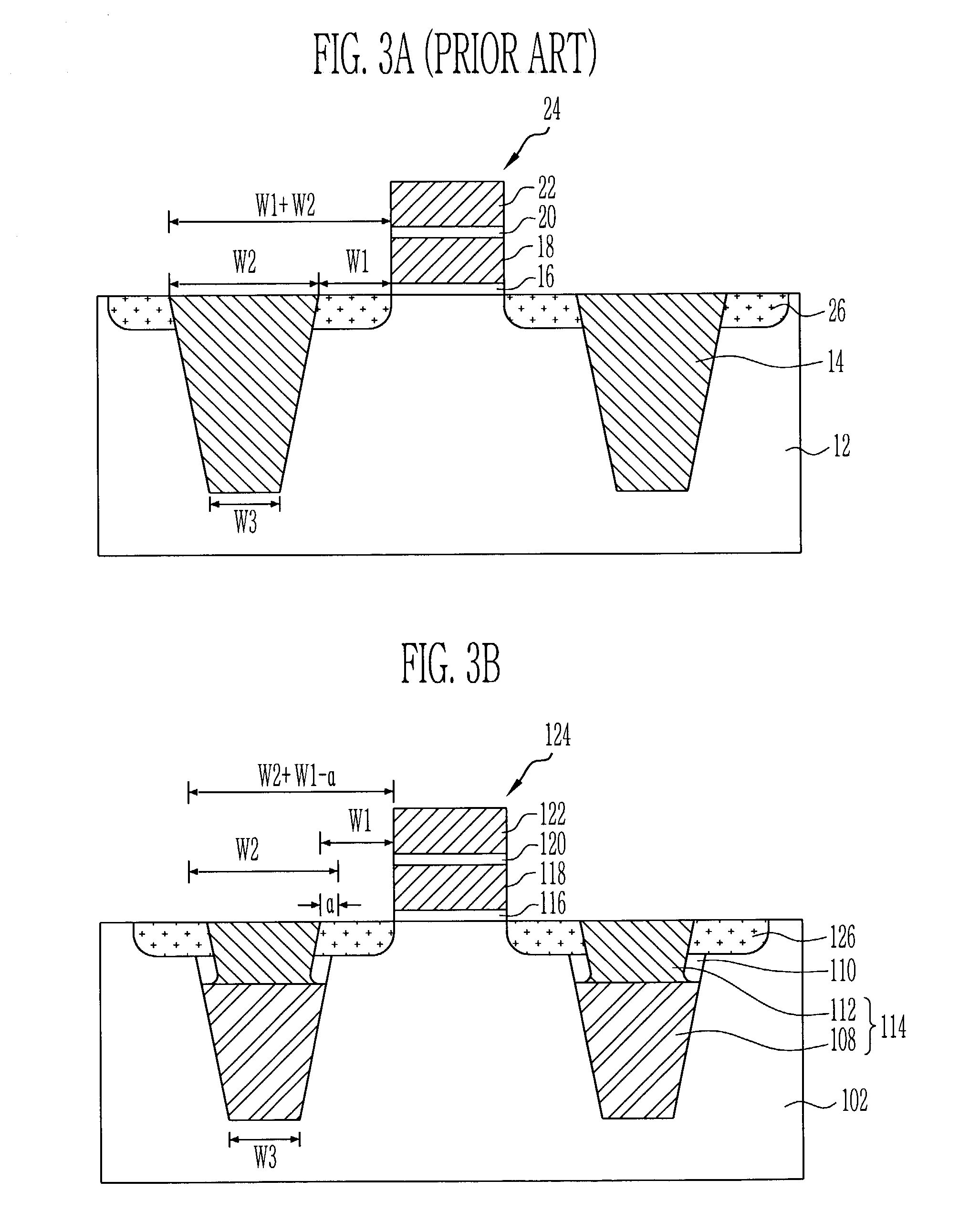

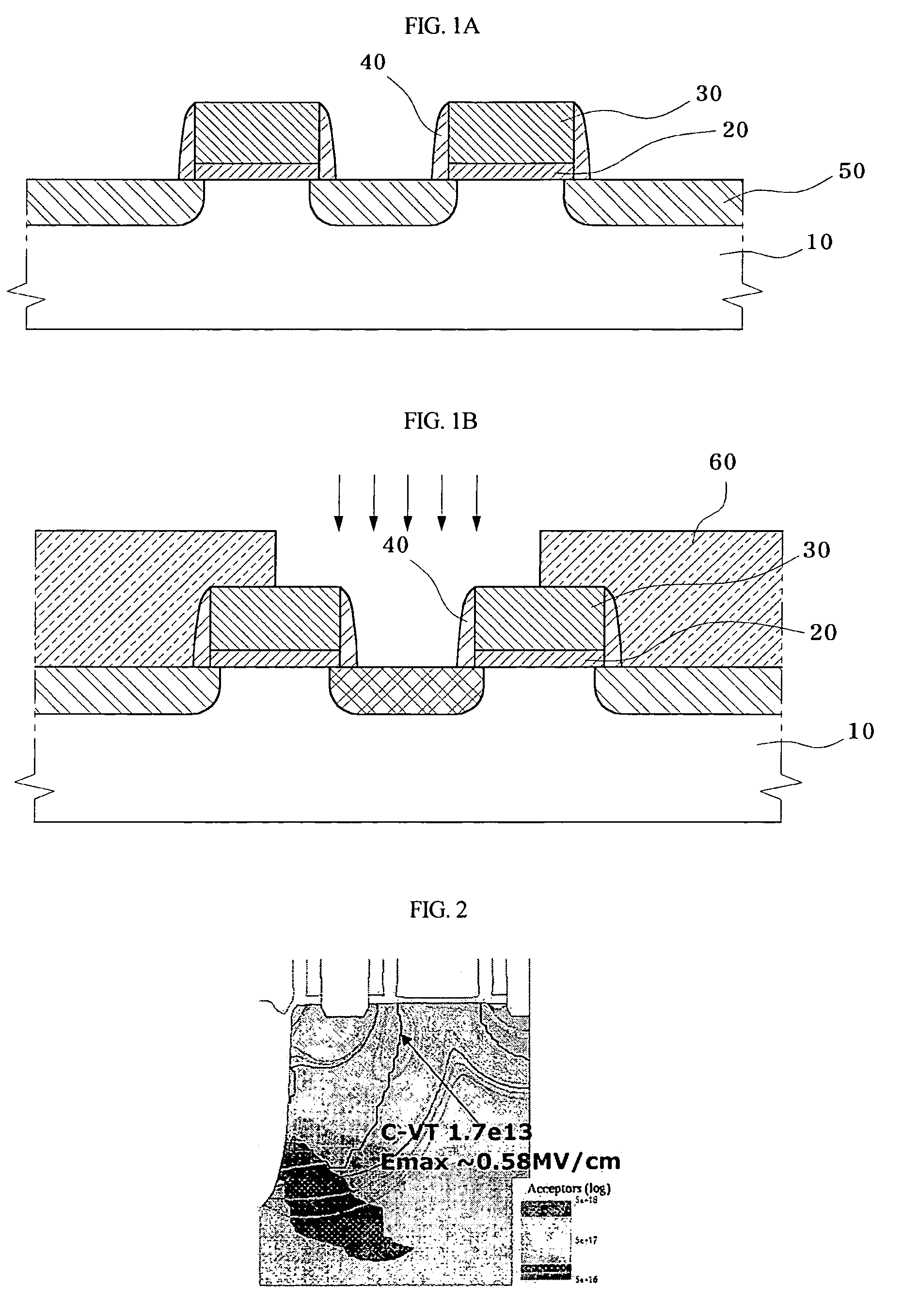

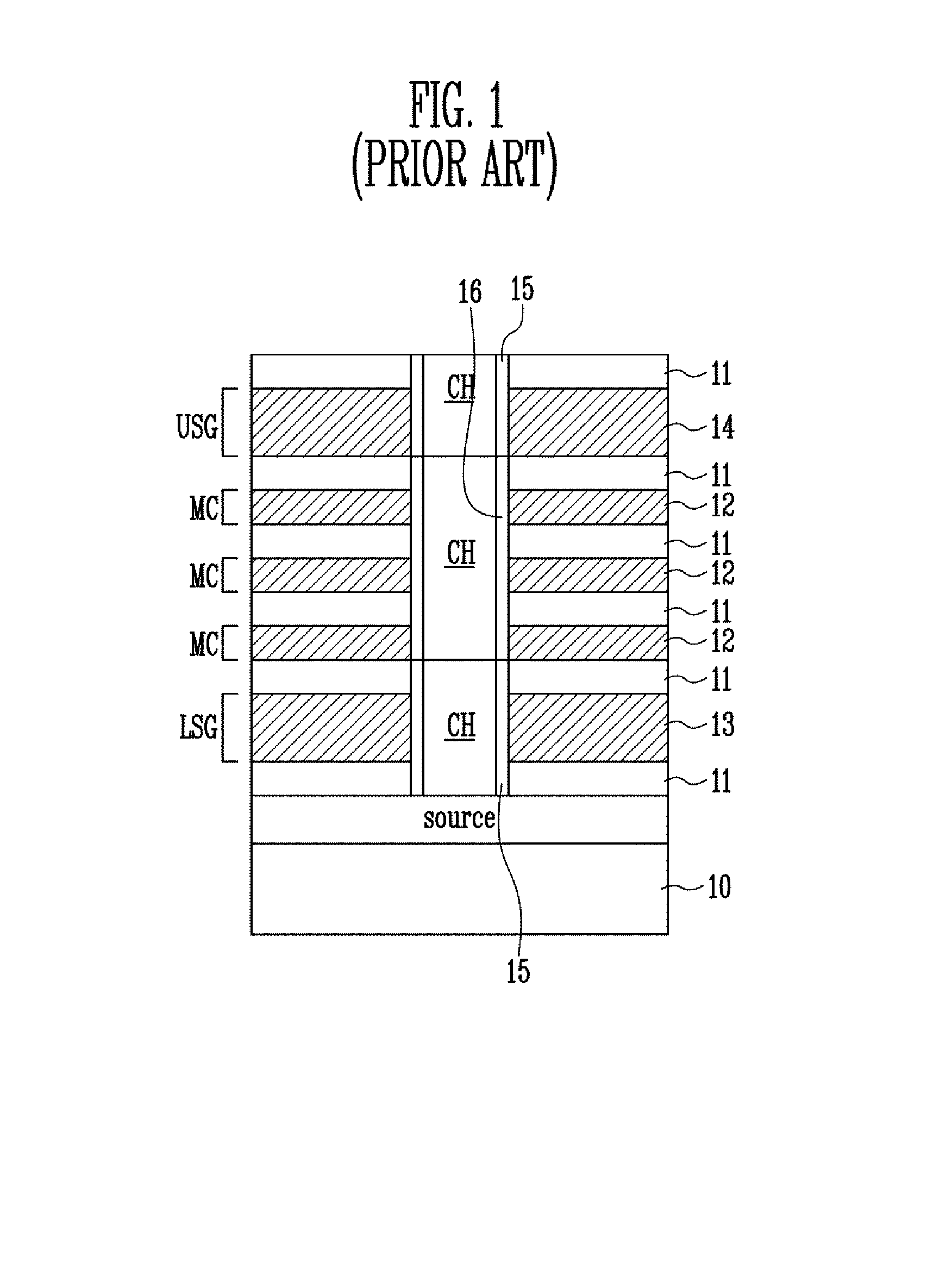

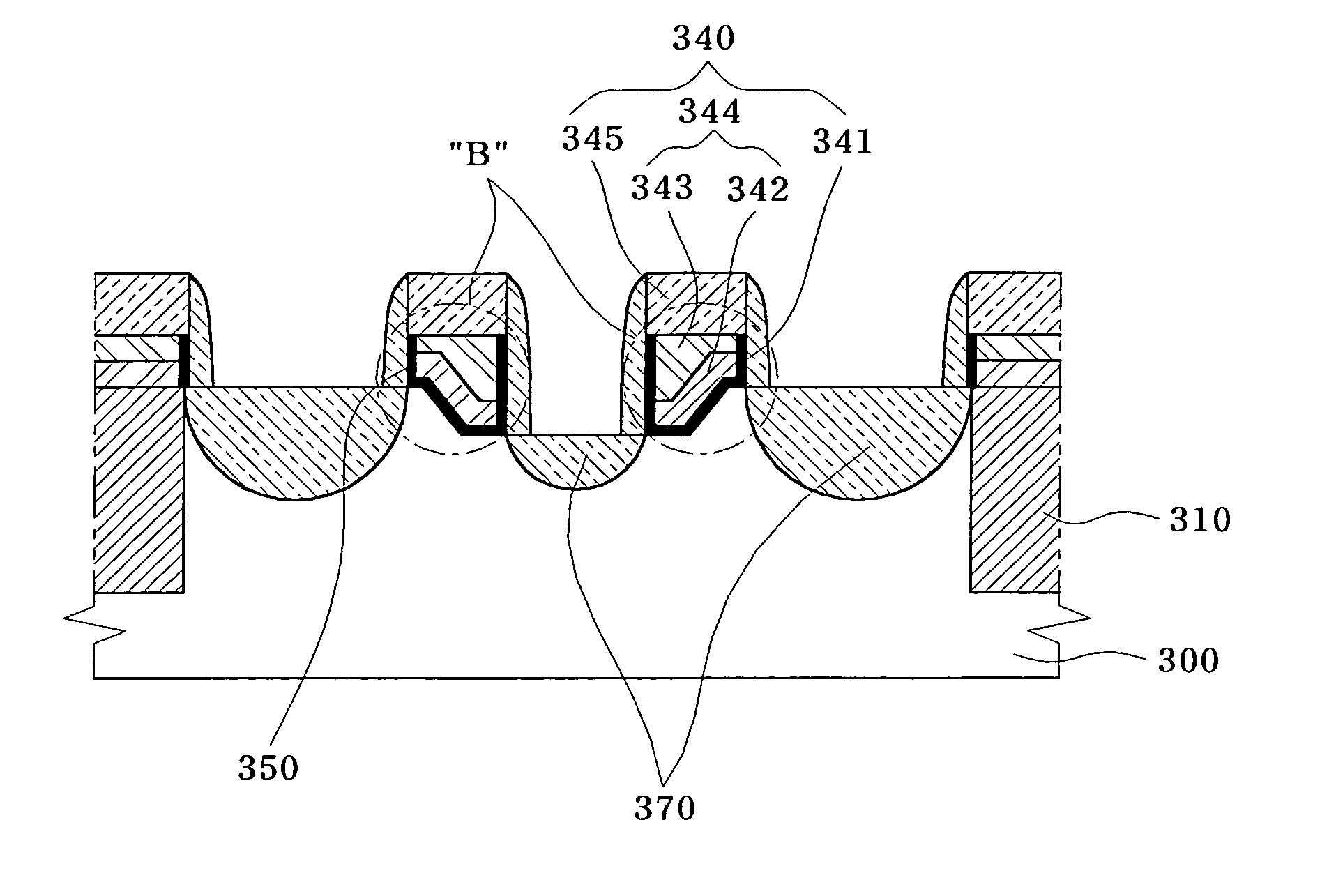

Semiconductor device and method of manufacturing the same

InactiveUS7029989B2Improve level of integrationHighly integratedTransistorSolid-state devicesImpurity diffusionSemiconductor

The present invention relates to a semiconductor device and a method of manufacturing the same. The minimum marginal width of an impurity diffusion layer is defined to reduce by a given width. The reduced width of the impurity diffusion layer is compensated for through a silicon growth layer formed on the top of a device isolation film having a relatively higher degree of freedom than the bottom of the device isolation film. Thus, the degree of integration in the semiconductor device can be improved while keeping intact the minimum marginal width of the impurity diffusion layer.

Owner:MAGNACHIP SEMICONDUCTOR LTD

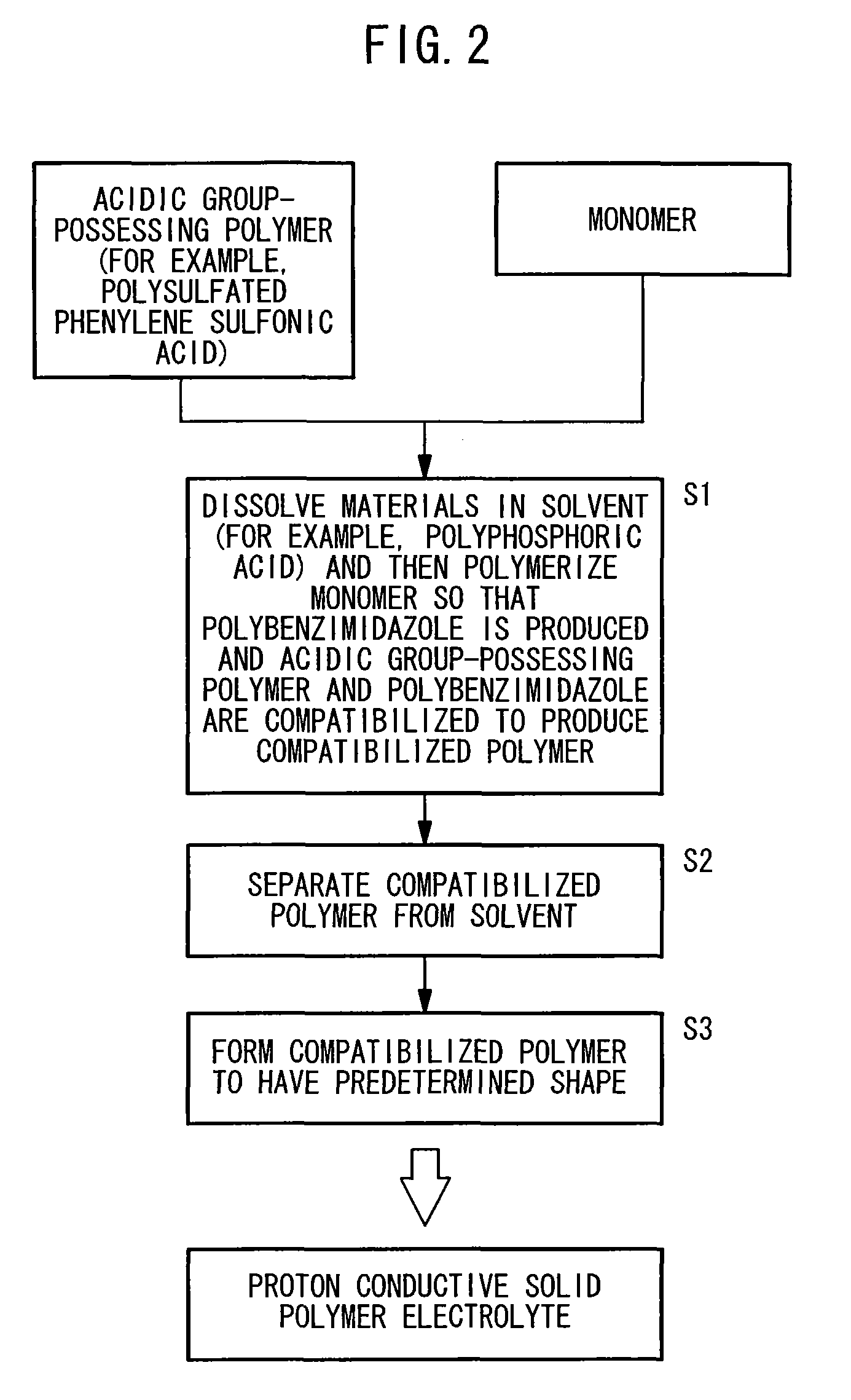

Proton conductive solid polymer electrolyte and method for producing the same

InactiveUS7045241B2Excellent abilitySecure characteristicSolid electrolytesFinal product manufacturePhosphoric acidPoly(benzimidazole)

A monomer to produce polybenzimidazole is dissolved in polyphosphoric acid. For example, polysulfated phenylene sulfonic acid (acidic group-possessing polymer) is further dissolved in this solution. In this procedure, the acidic group-possessing polymer and the monomer are adsorbed to one another in accordance with the acid-base interaction. When the monomer is polymerized, for example, by means of dehydration polymerization in this state, then polybenzimidazole is synthesized, and the polybenzimidazole and the acidic group-possessing polymer are compatibilized with each other to produce a compatibilized polymer. When the compatibilized polymer is deposited as a solid, and the solid is separated from polyphosphoric acid, then the compatibilized polymer is obtained. A proton conductive solid polymer electrolyte as a final product is manufactured by forming the compatibilized polymer to have a predetermined shape.

Owner:HONDA MOTOR CO LTD

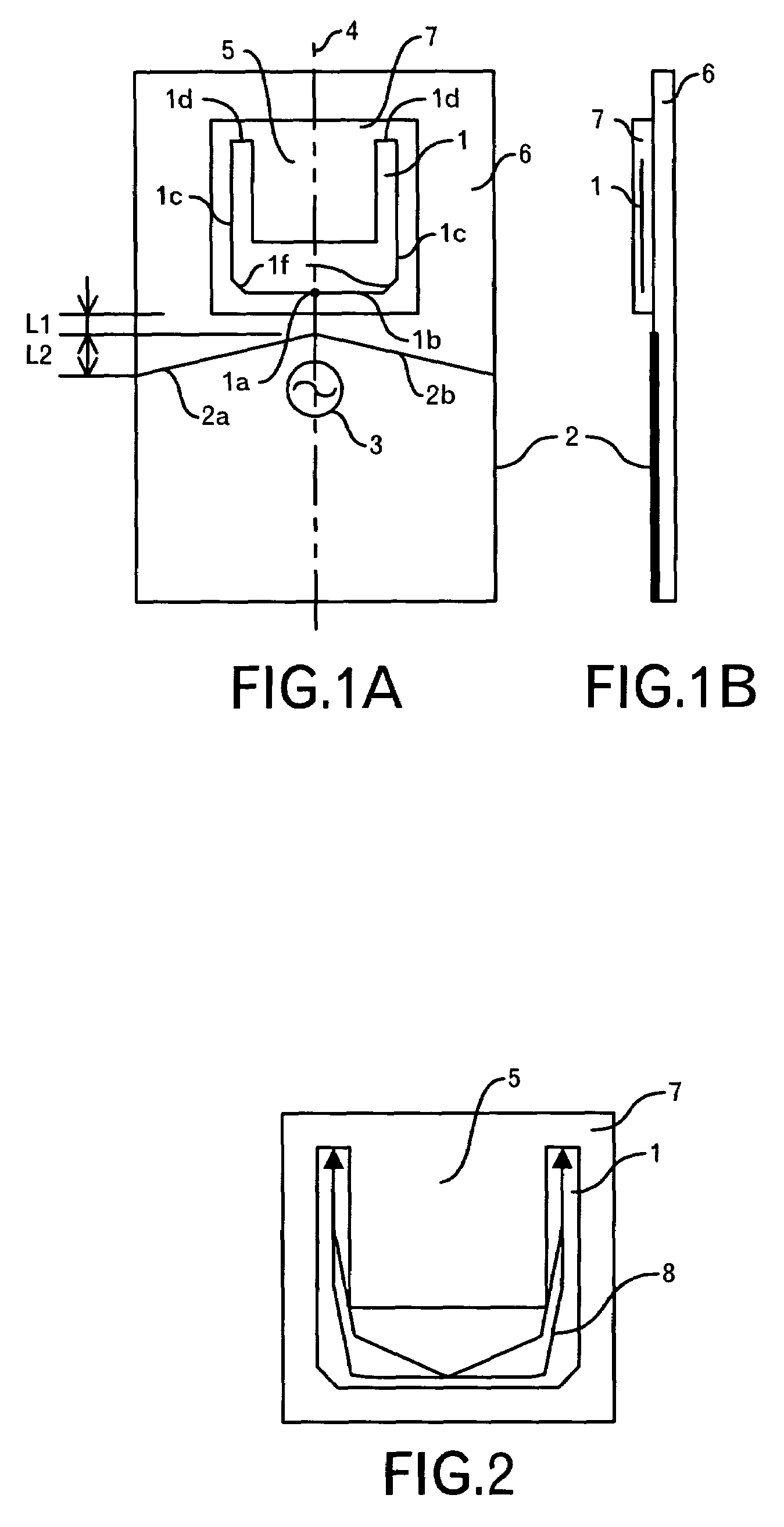

Antenna and wireless communication card

InactiveUS7102572B2Easy to controlHigh bandwidthSimultaneous aerial operationsAntenna supports/mountingsCouplingDielectric substrate

An antenna of this invention comprises an antenna element to which power is fed at a feed point; and a ground pattern that is juxtaposed with the antenna element and in which a tapered shape is formed with respect to the feed point of the antenna element. By providing the tapered shape for the ground pattern, it is possible to appropriately adjust the coupling degree with the antenna element, thereby it is possible to widen the bandwidth. Moreover, since the ground pattern and the antenna element are juxtaposed with each other, miniaturization can be achieved. When the antenna element is integrally formed in a dielectric substrate, further miniaturization can be achieved. Furthermore, when a cut-out portion is formed in the antenna element, the characteristic of the antenna in the low frequency range is improved.

Owner:TAIYO YUDEN KK

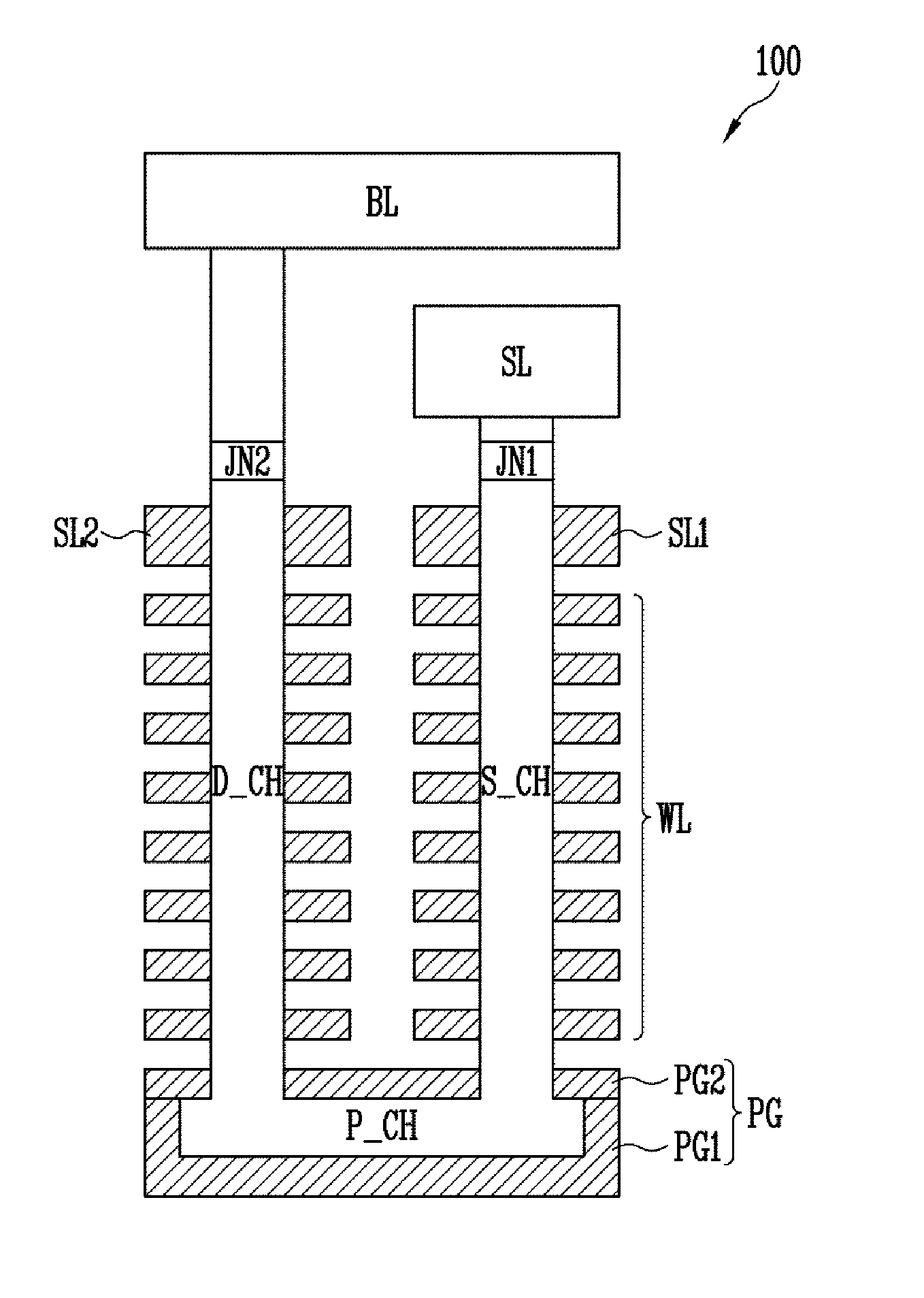

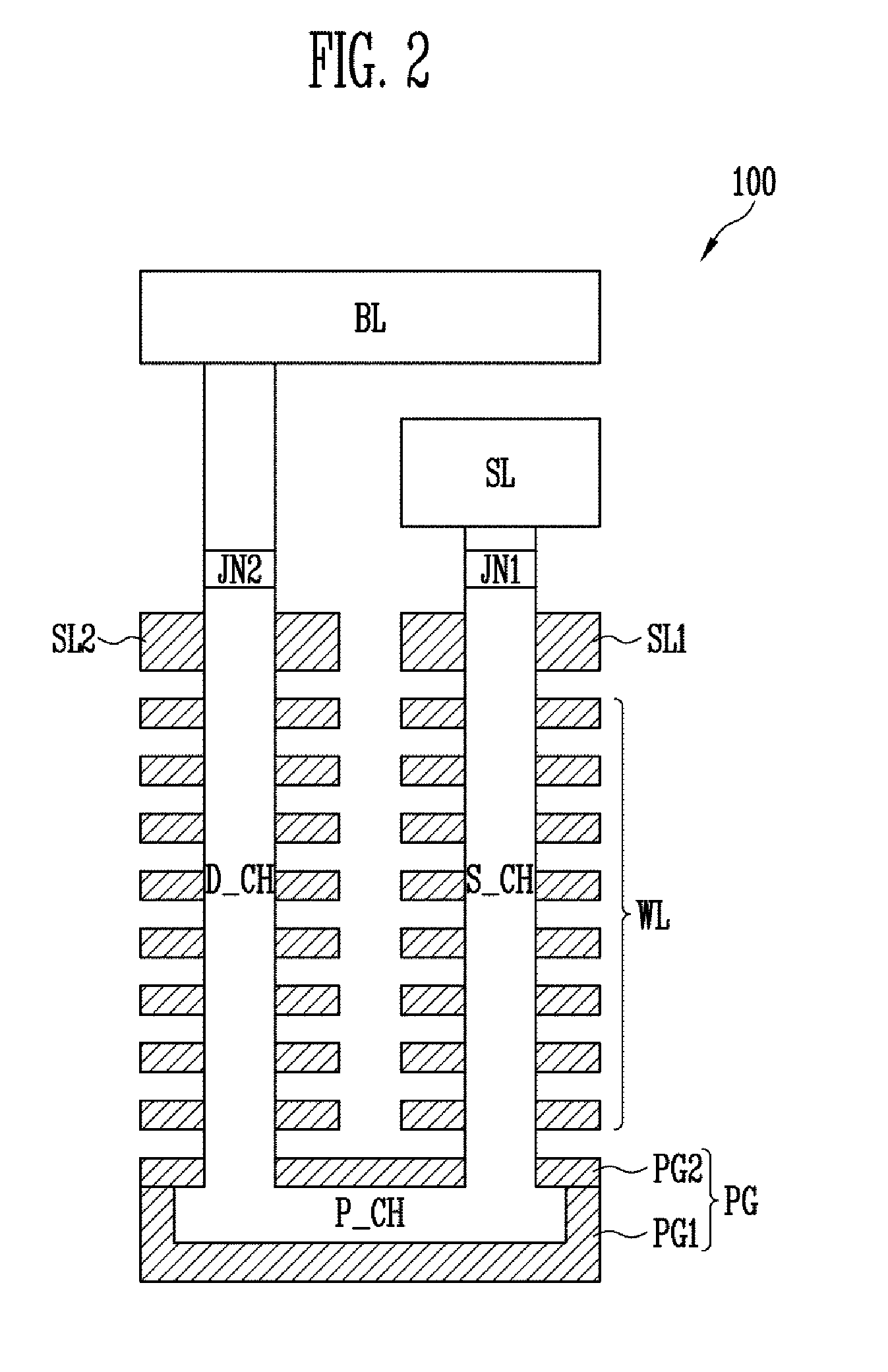

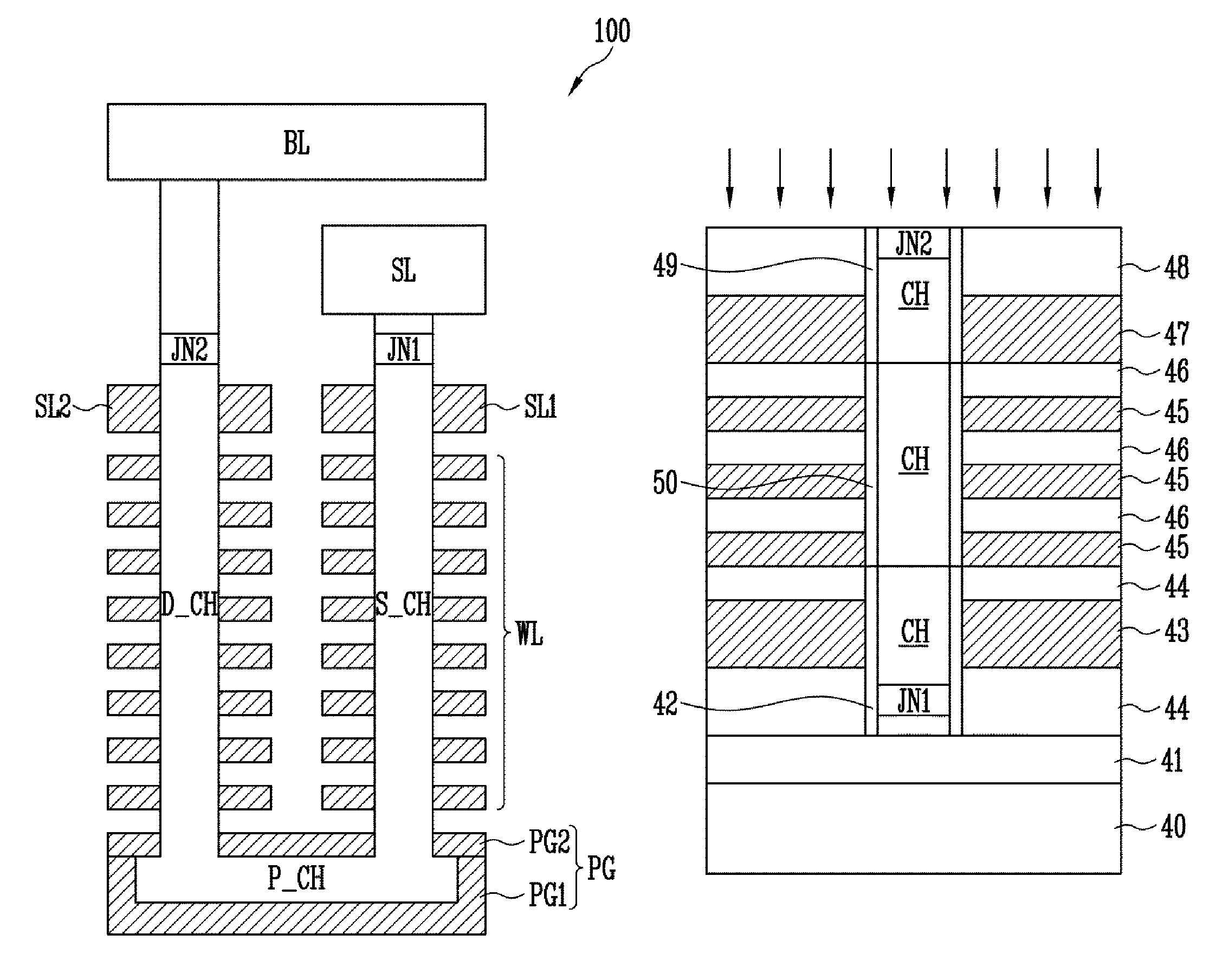

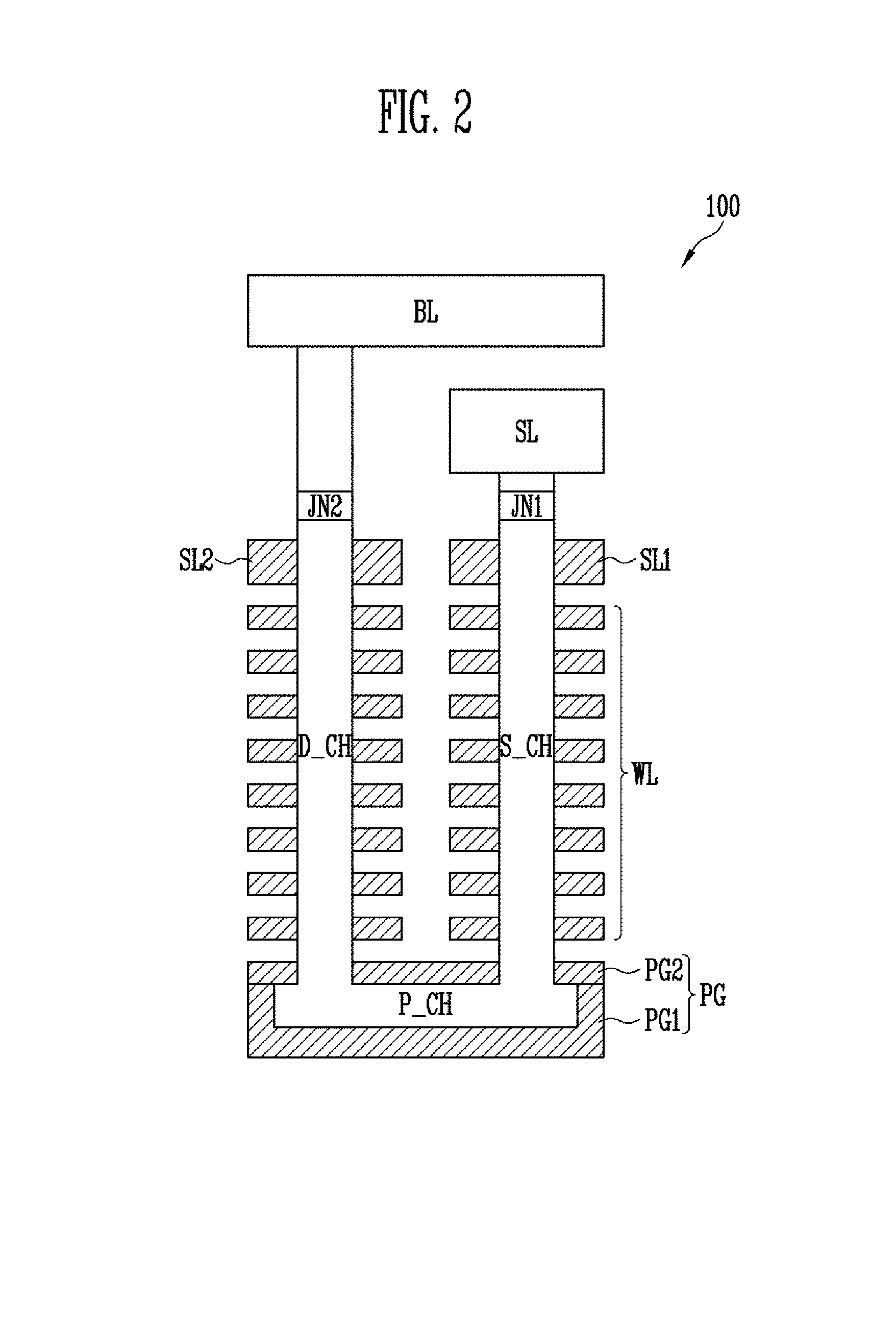

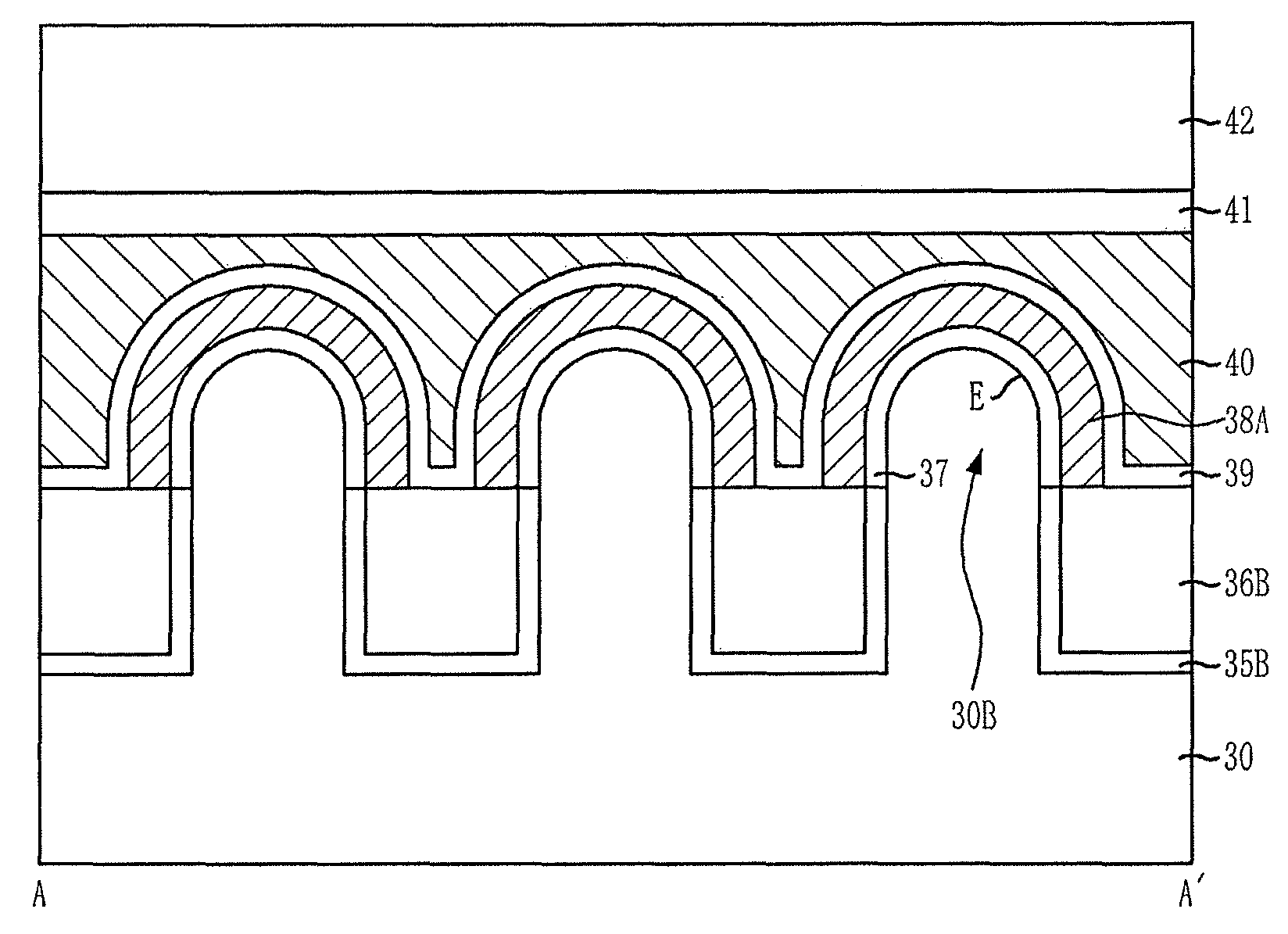

3-d nonvolatile memory devices and methods of manufacturing the same

A three-dimensional (3-D) nonvolatile memory device includes a channel layer protruded from a substrate, a plurality of memory cells stacked along the channel layer, a source line coupled to the end of one side of the channel layer, a bit line coupled to the end of the other side of the channel layer, a first junction interposed between the end of one side of the channel layer and the source line and configured to have a P type impurity doped therein, and a second junction interposed between the end of the other side of the channel layer and the bit line and configured to have an N type impurity doped therein.

Owner:SK HYNIX INC

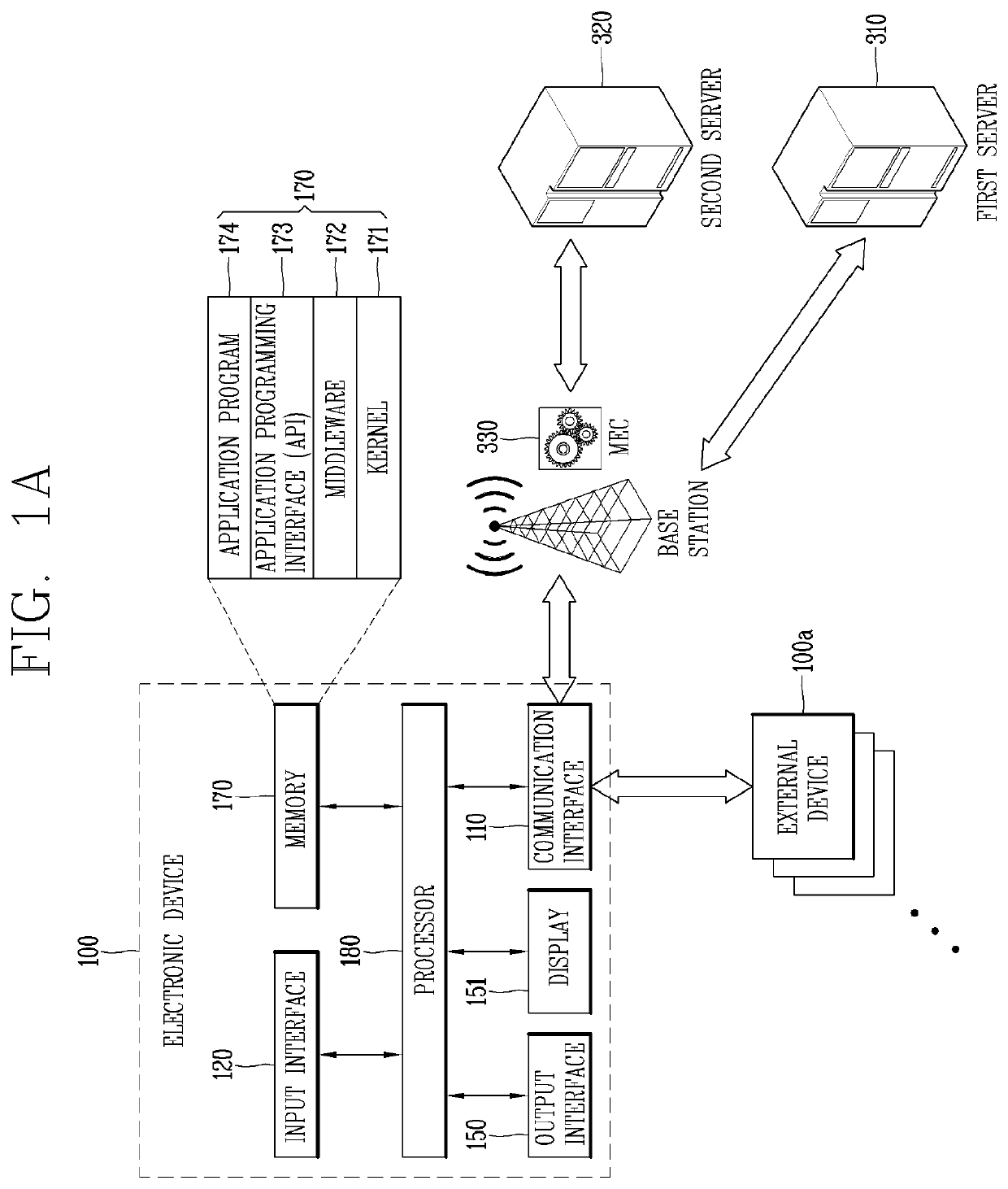

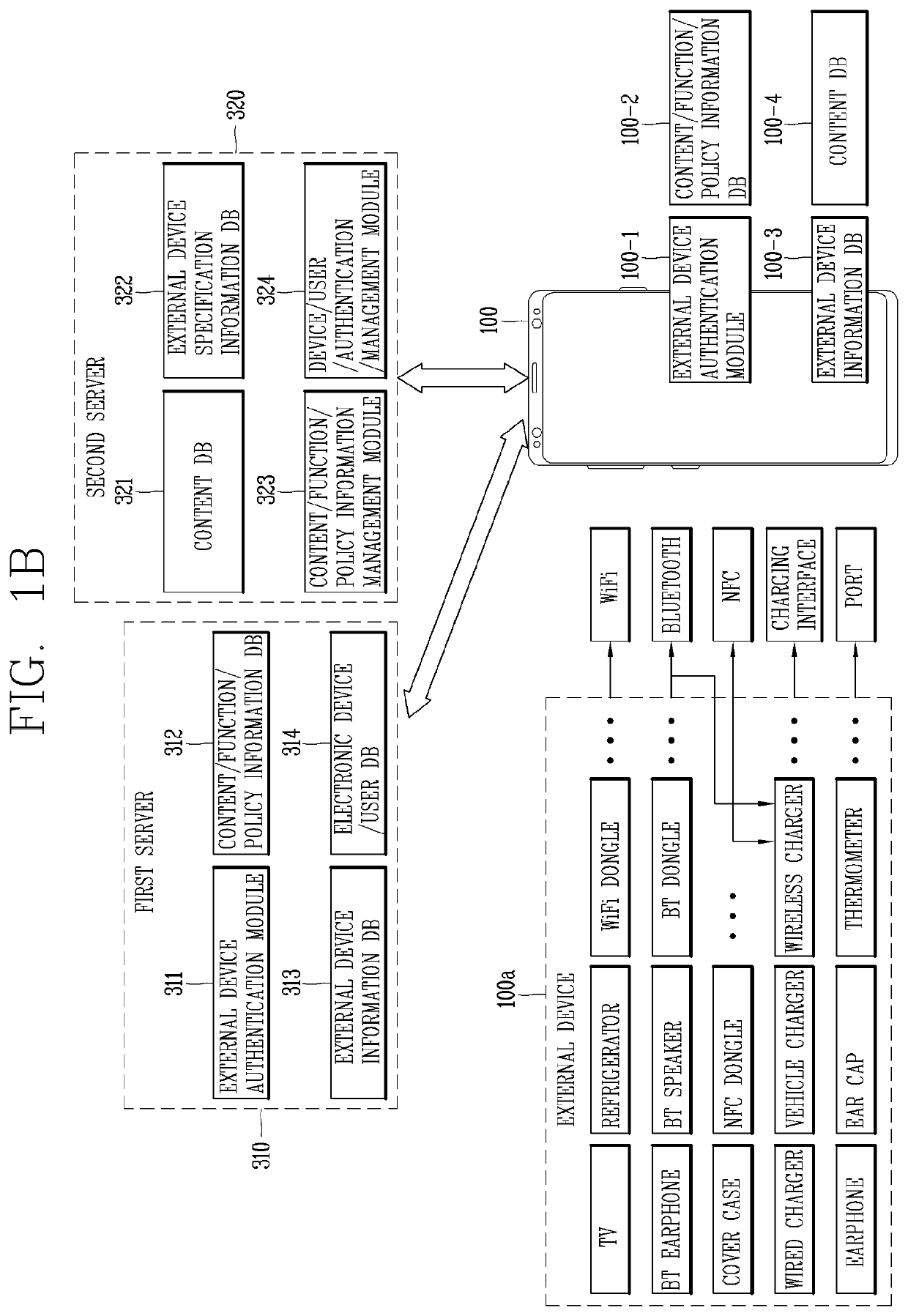

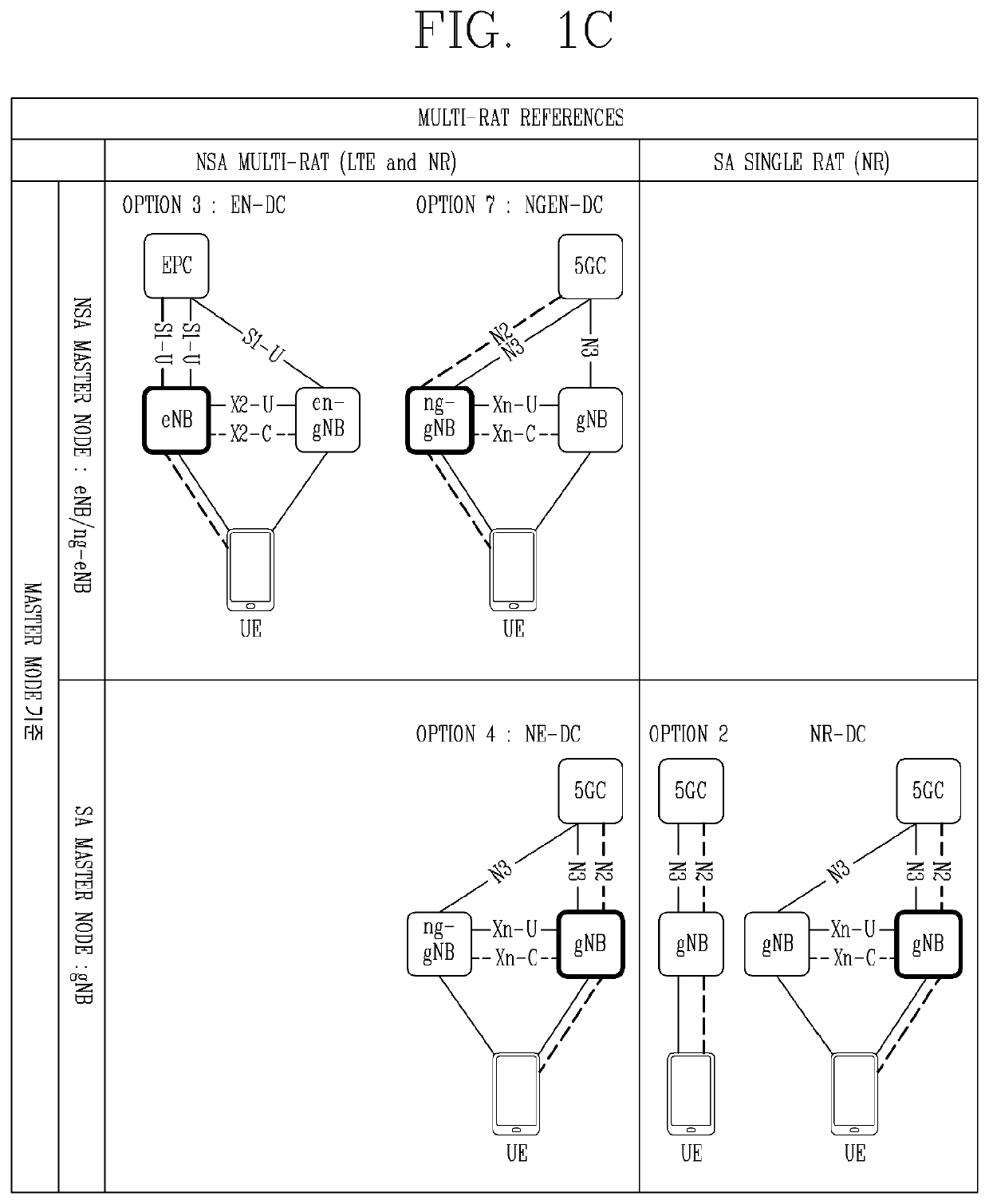

Electronic device having antennas

ActiveUS20210336356A1Interference minimizationImprove performanceSimultaneous aerial operationsDigital data processing detailsDisplay deviceEngineering

An electronic device according to one implementation includes a flexible display having a first region coupled to a front surface of a first frame, a second region coupled to a third frame, and a third region located between the first region and the second region, and an antenna implemented as one of a plurality of metal rims formed on one of the first frame and the third frame, and connected to a feeding unit at one point and a ground at another point through a switching unit to radiate signals through different bands.

Owner:LG ELECTRONICS INC

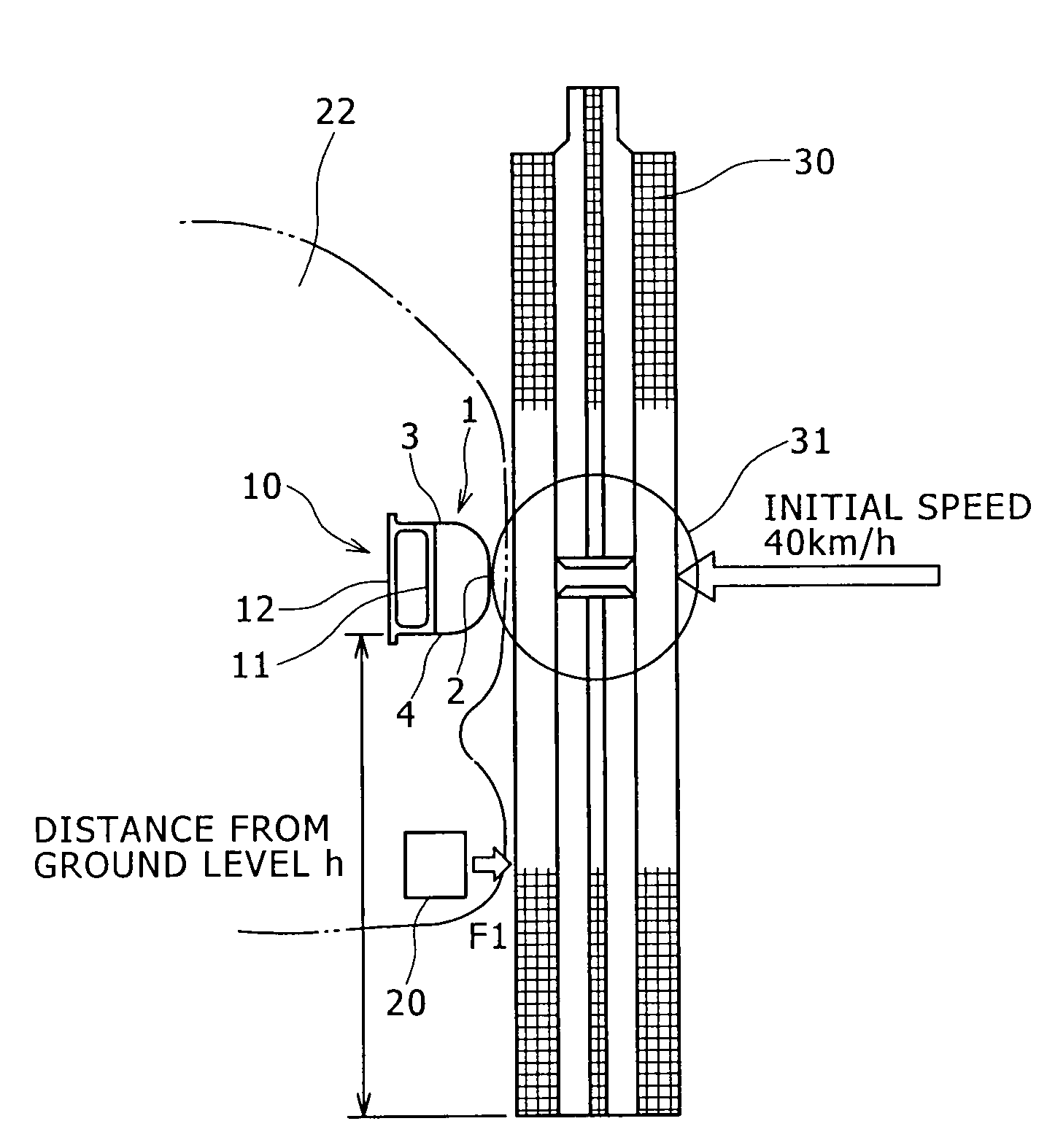

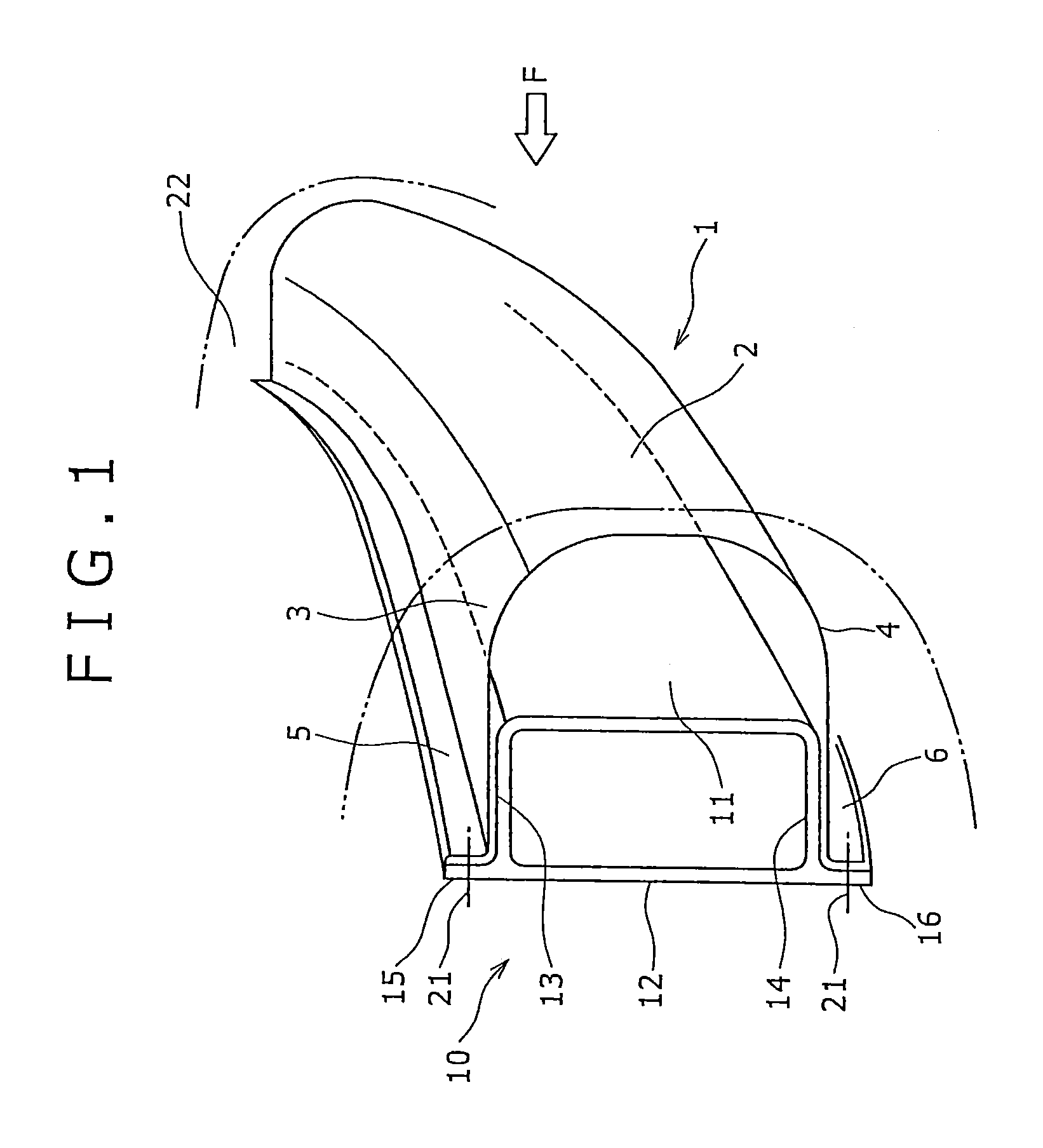

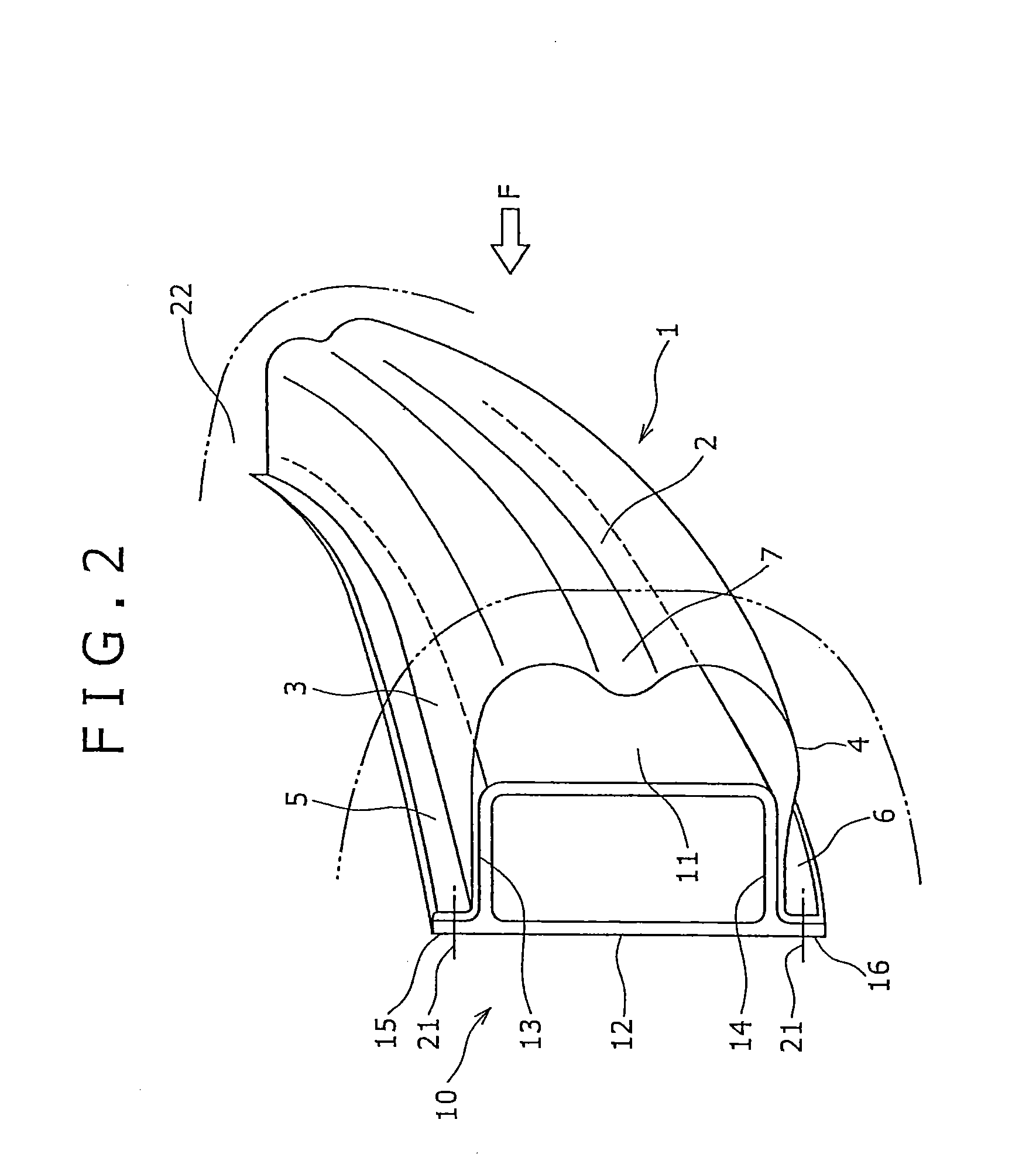

Bumper system for vehicle

InactiveUS20090267368A1Increase the number of choicesFirmly connectedBumpersMetallic materialsEngineering

The bumper system for a vehicle body includes a vehicle body bumper beam of a hollow construction with an impact buffer member arranged in the front side. The impact buffer member is provided with a collision wall part, side wall parts and joint flanges and is integrally formed by a metallic material, the collision wall part and the side wall parts forming a sectional shape of approximately U-shape which embraces the bumper beam. The joint flanges are joined with the flanges protruding from the rear wall of the bumper beam and support the impact buffer member from the rear wall side of the bumper beam.

Owner:KOBE STEEL LTD

Through-silicon via and method for forming the same

InactiveUS7691748B2Low costSecure characteristicSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

Owner:SK HYNIX INC

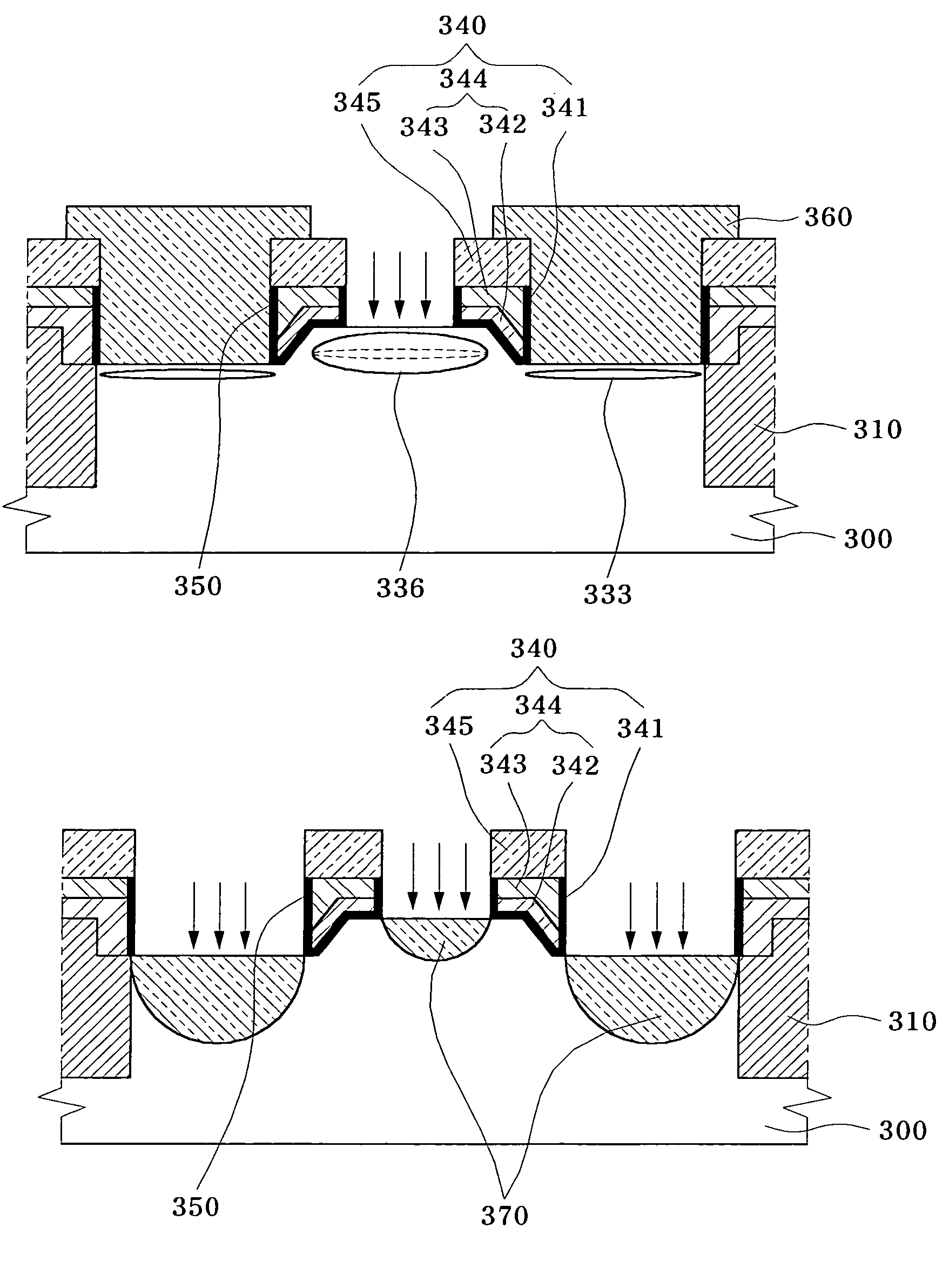

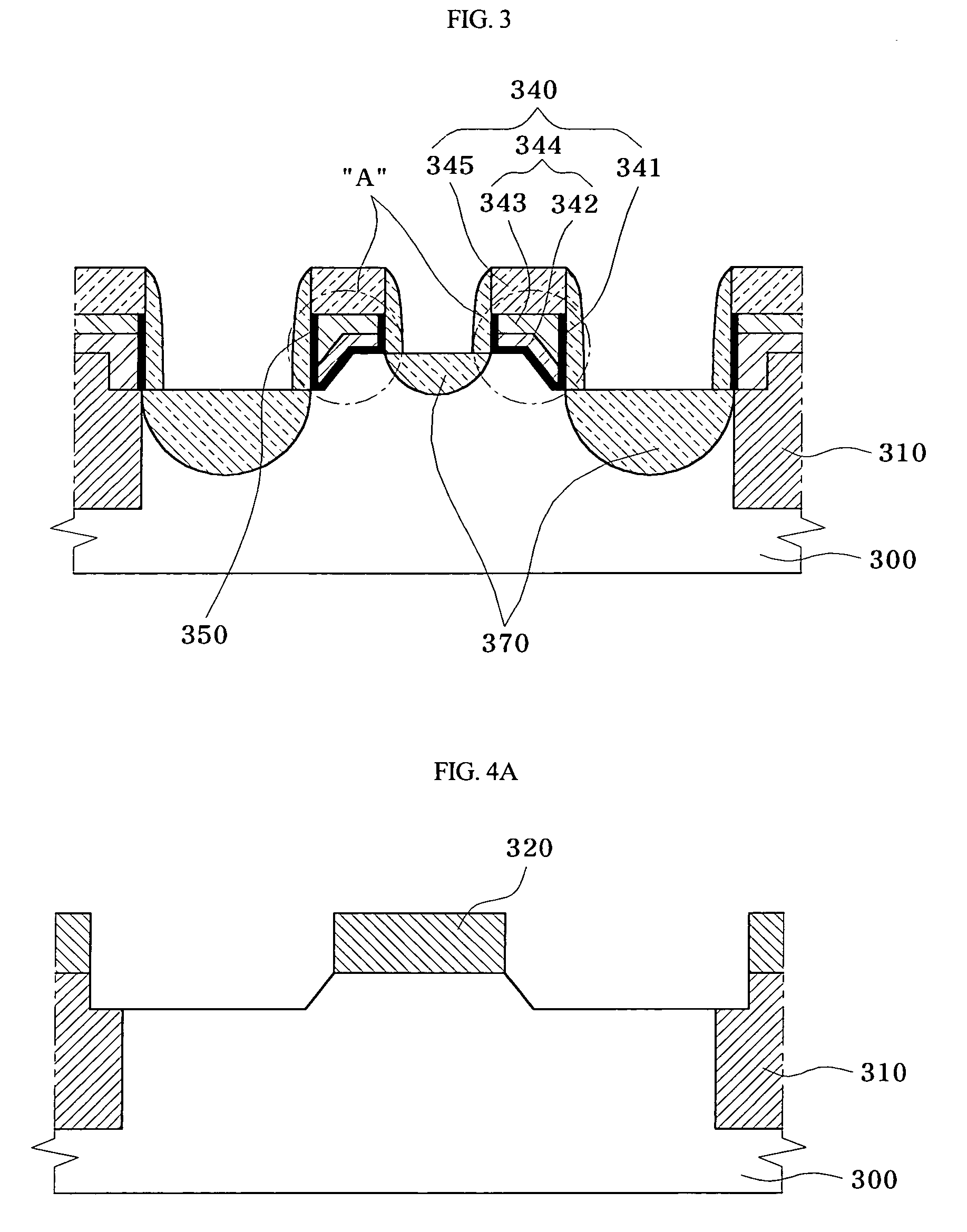

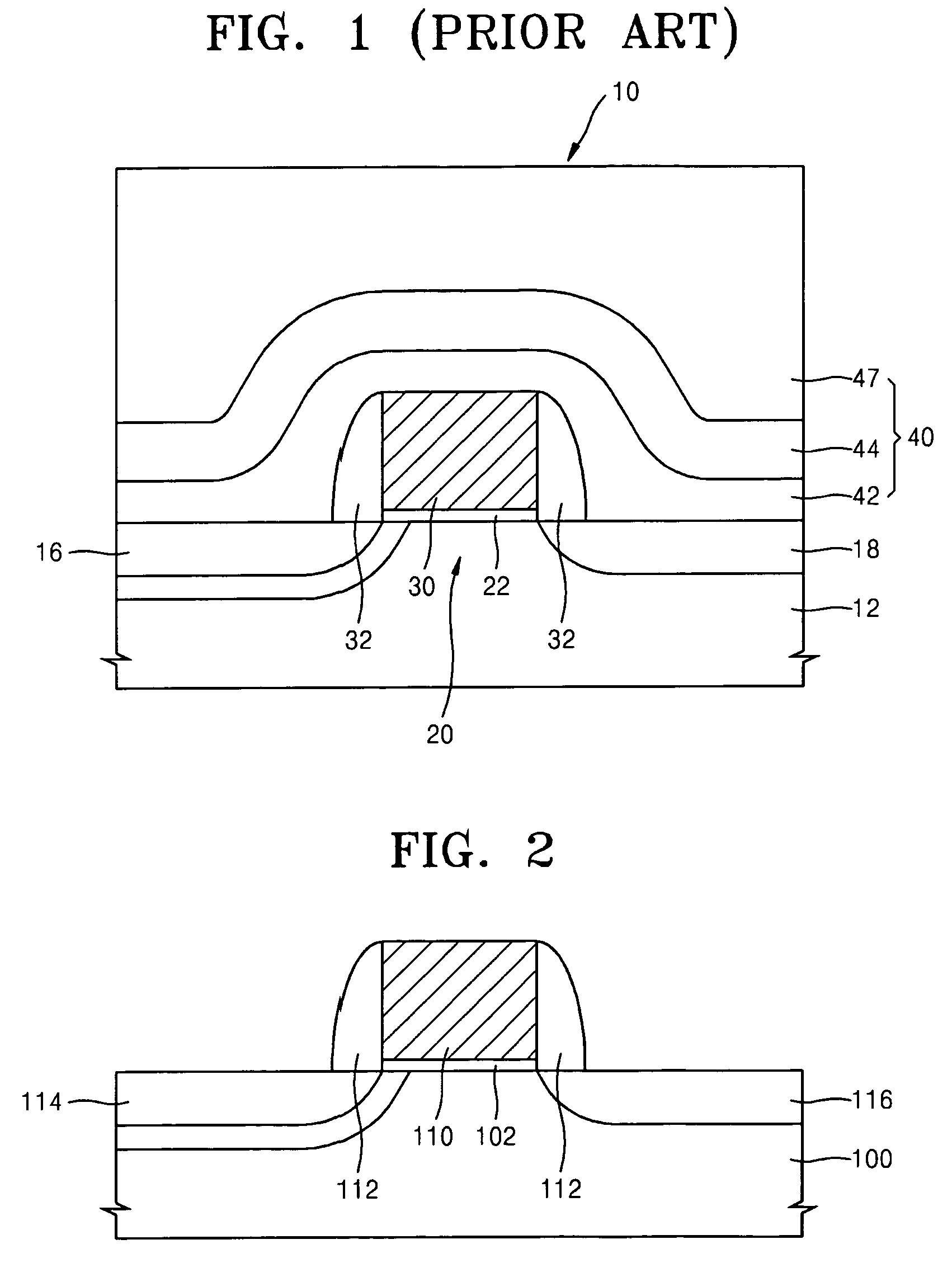

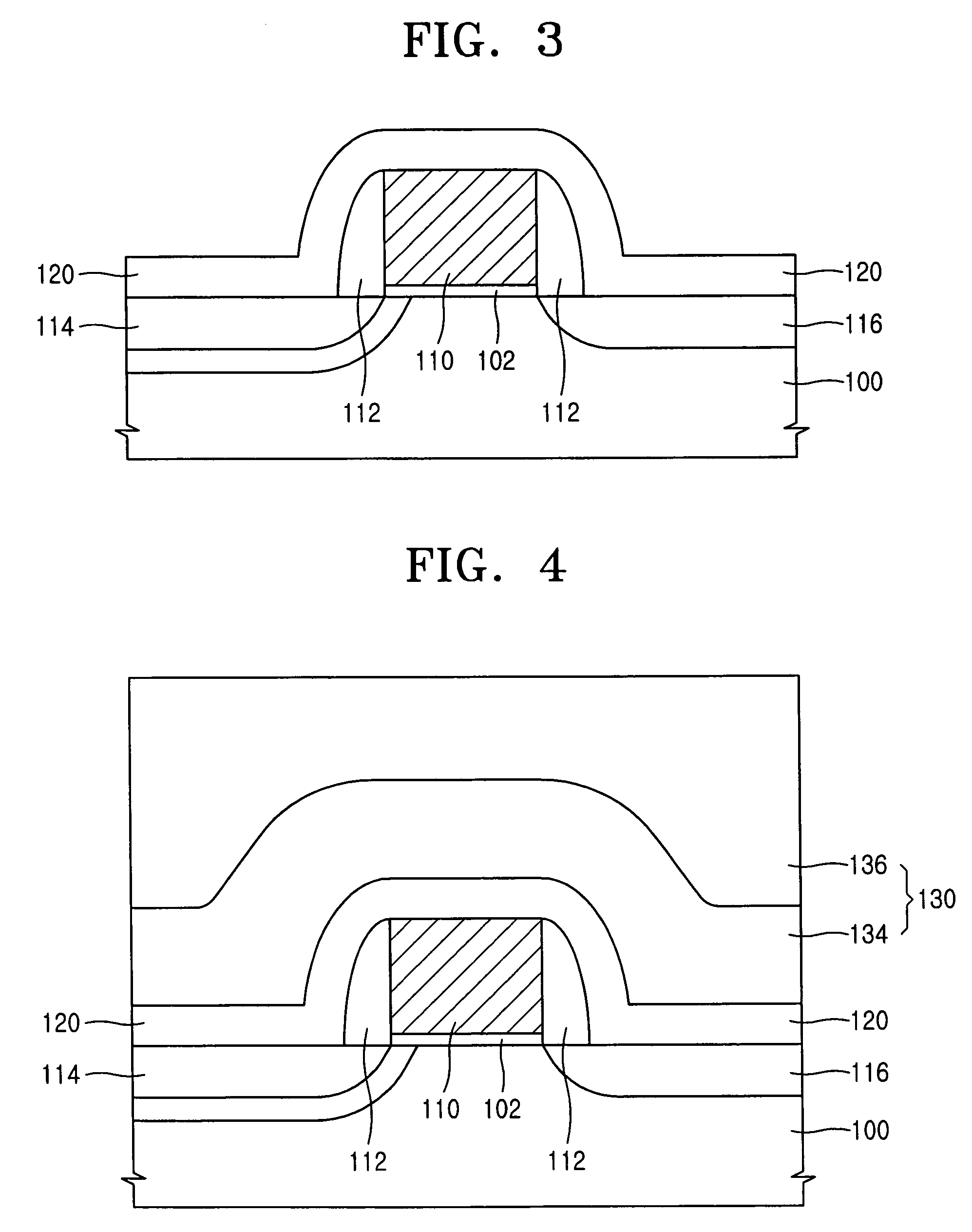

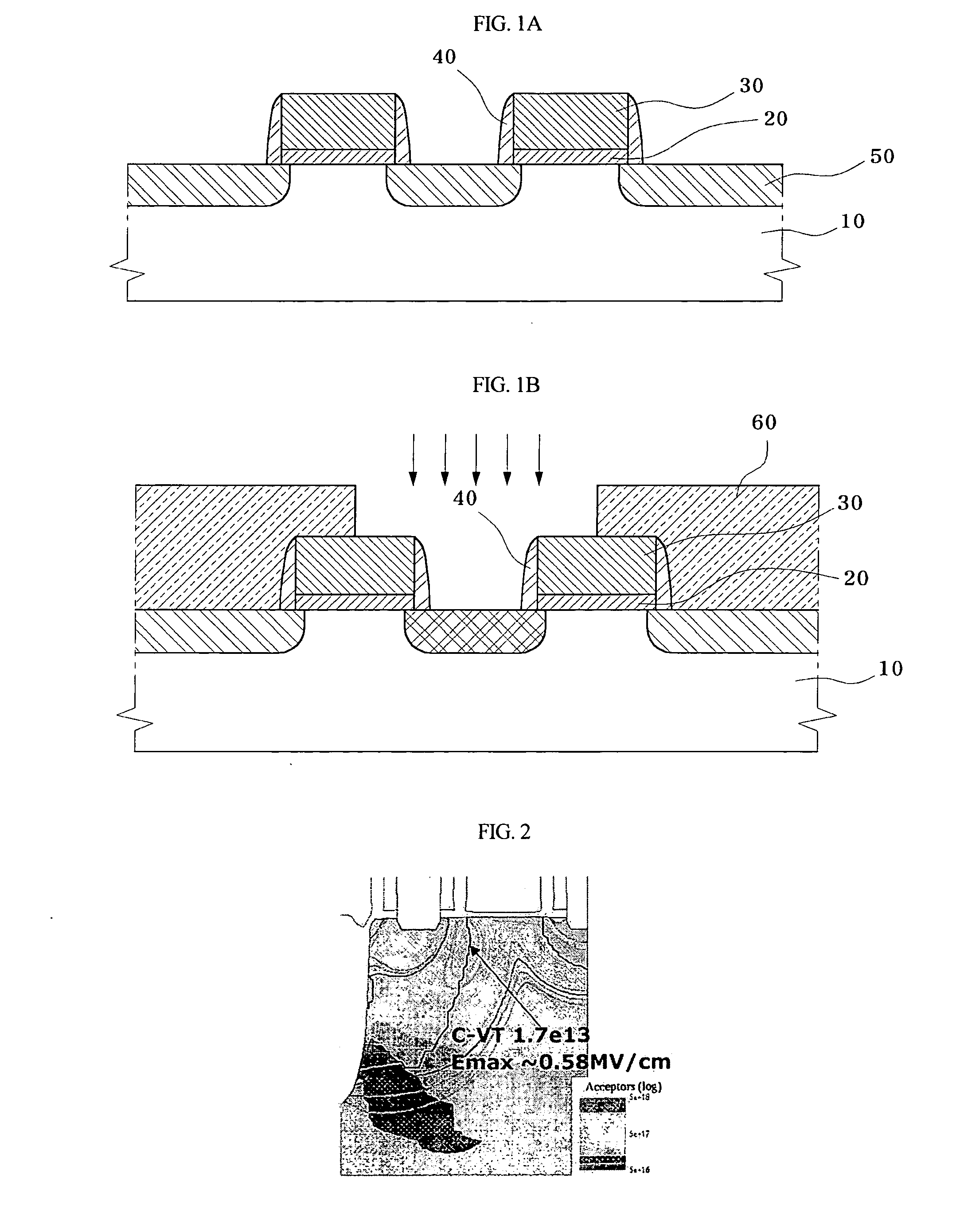

Transistor and method for manufacturing the same

InactiveUS7244650B2Increase concentrationAvoid ion diffusionTransistorSolid-state devicesSemiconductorTransistor

A transistor including a semiconductor substrate defined with an active region and a device isolation region, a gate formed on the semiconductor substrate, an insulating spacers formed on respective side walls of the gate, and source / drain junctions formed in the semiconductor substrate at opposite sides of the gate, the source / drain junctions having asymmetrical junction structures, respectively, wherein the gate has a lower portion arranged on the active region of the substrate, the lower gate portion having a stepped profile having a lower surface, an upper surface and a vertically-extending side surface. The invention also provides a method for manufacturing this transistor. In accordance with this transistor structure, an increase in the dopant concentration of a storage node is prevented. Accordingly, a reduction in the amount of leakage current is achieved, so that an improvement in the refresh characteristics of the transistor is achieved.

Owner:SK HYNIX INC

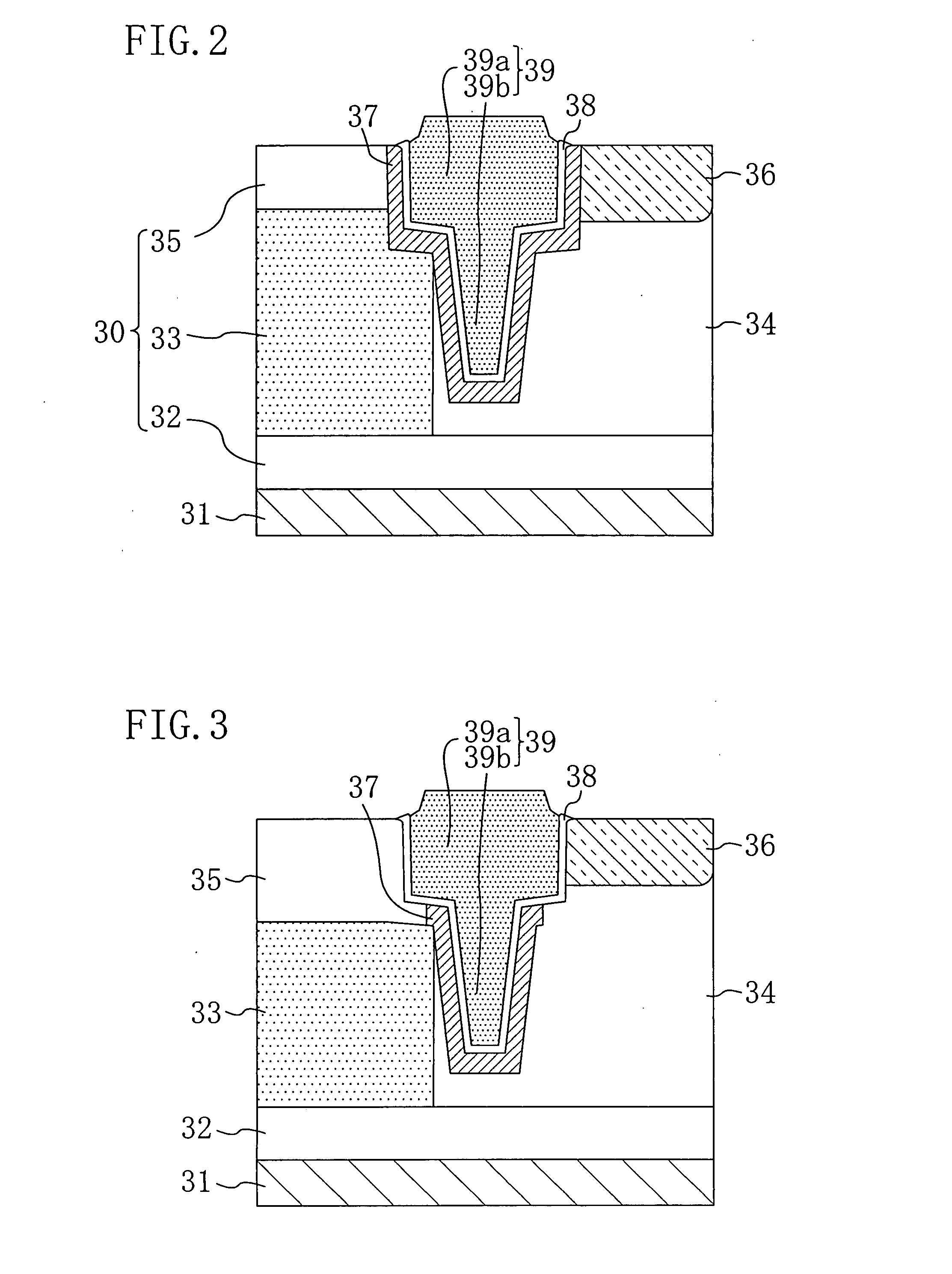

Solid state imaging device, method for fabricating the same, and camera

ActiveUS20080029796A1Secure characteristicIncrease the number ofSolid-state devicesSemiconductor/solid-state device manufacturingPhotoelectric conversionSilicon

A solid state imaging device includes: an imaging region formed in an upper part of a substrate made of silicon to have a photoelectric conversion portion, a charge accumulation region of the photoelectric conversion portion being of a first conductivity type; a device isolation region formed in at least a part of the substrate to surround the photoelectric conversion portion; and a MOS transistor formed on a part of the imaging region electrically isolated from the photoelectric conversion region by the device isolation region. The width of the device isolation region is smaller in its lower part than in its upper part, and the solid state imaging device further includes a dark current suppression region surrounding the device isolation region and being of a second conductivity type opposite to the first conductivity type.

Owner:GK BRIDGE 1

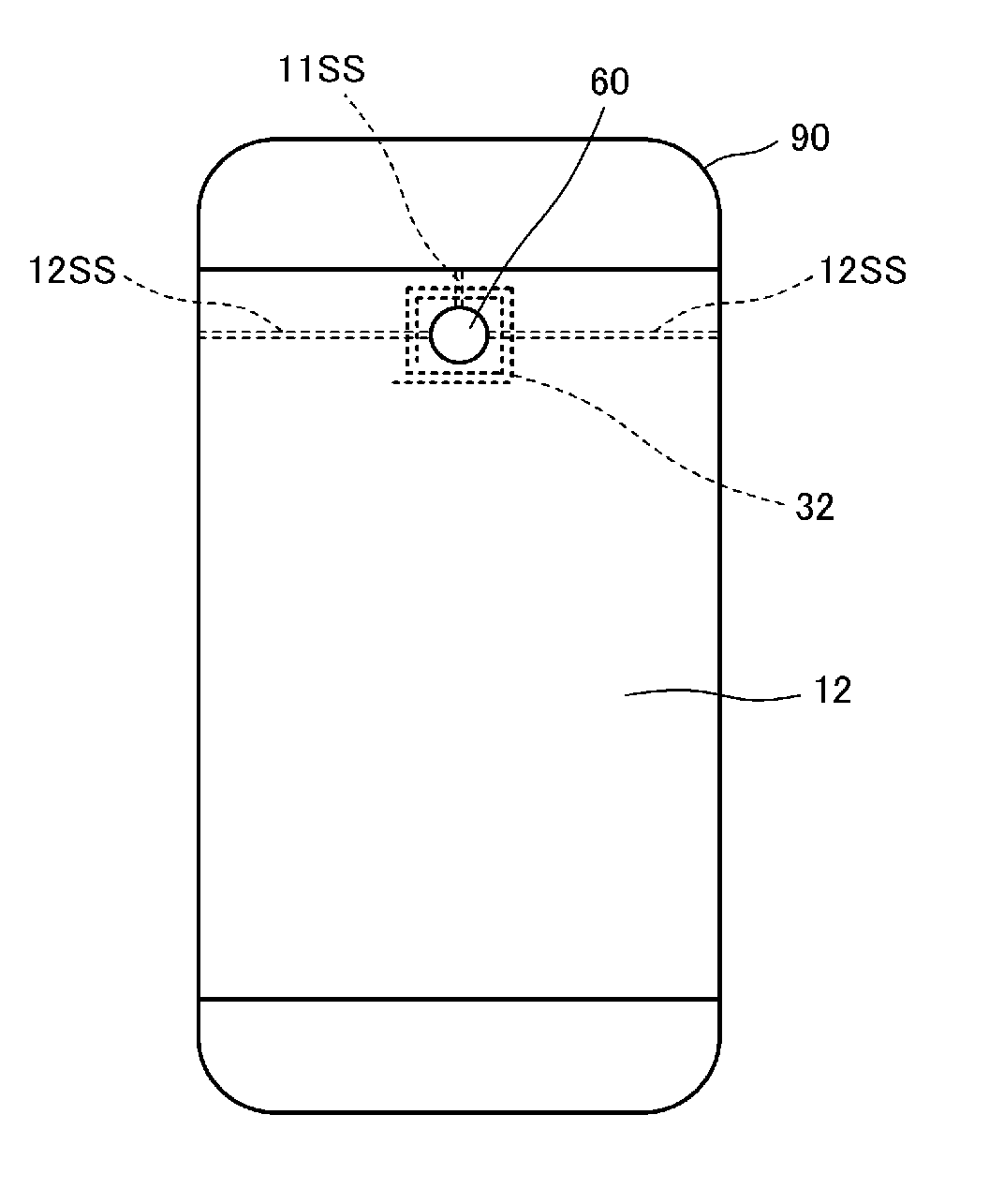

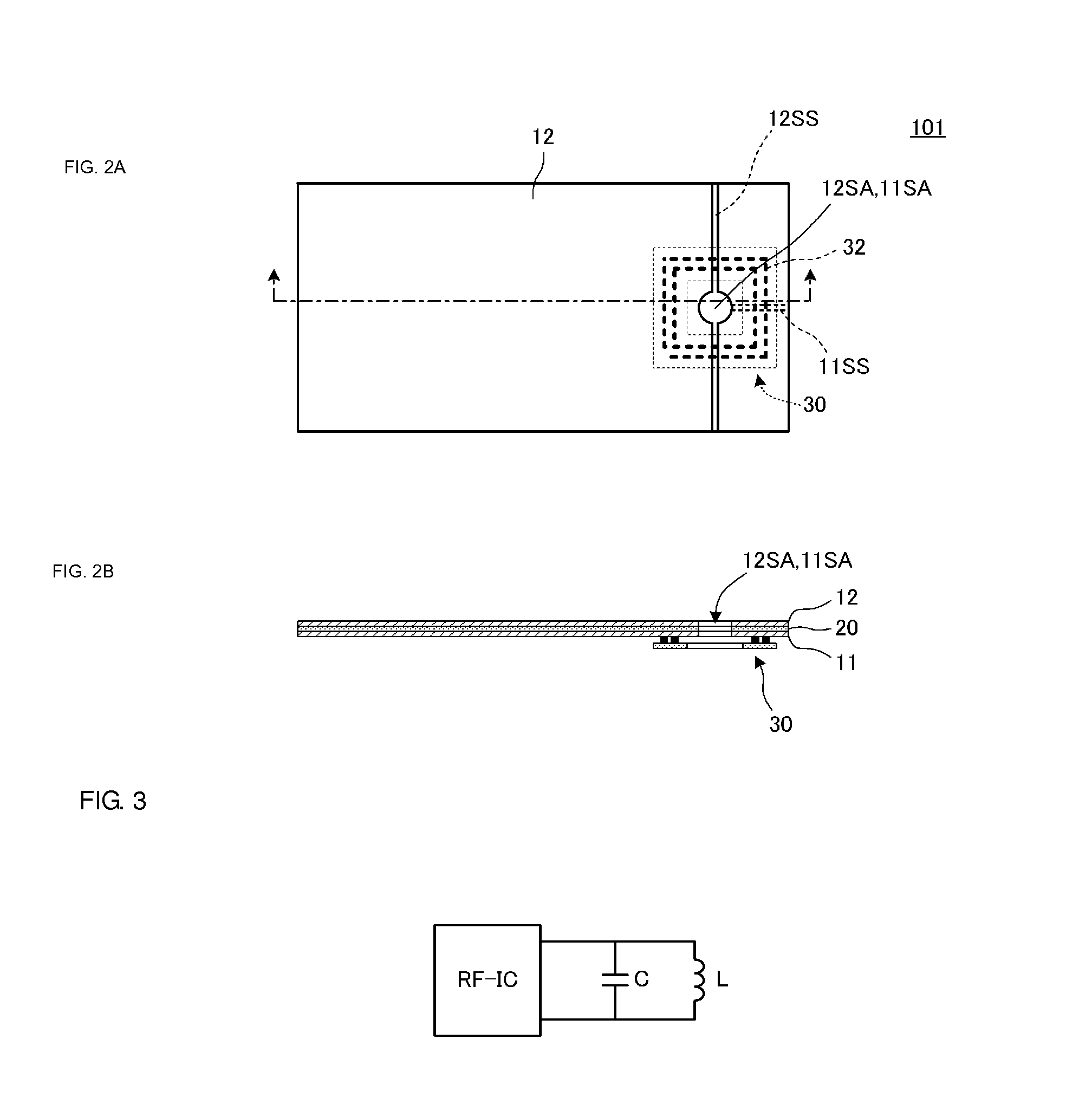

Antenna device and electronic appliance

ActiveUS20150207223A1Ensure normal communicationSecure characteristicLoop antennas with ferromagnetic coreAntenna supports/mountingsElectrical conductorEngineering

Owner:MURATA MFG CO LTD

Electronic device having antennas

ActiveUS20210359392A1Improve communication performanceMaintain performanceSimultaneous aerial operationsAntenna supports/mountingsMetal frameworkMillimetre wave

An electronic device according to one embodiment may include a conductive member antenna implemented as one of a plurality of metal rims and configured to radiate a signal, and an antenna module disposed between a metal frame and a sliding module of the electronic device, and configured to radiate a signal in a millimeter wave (mmWave) band. The sliding module may be coupled to the conductive member antenna and disposed between the conductive member antenna and a moving portion of the electronic device to operate as a slide support portion.

Owner:LG ELECTRONICS INC

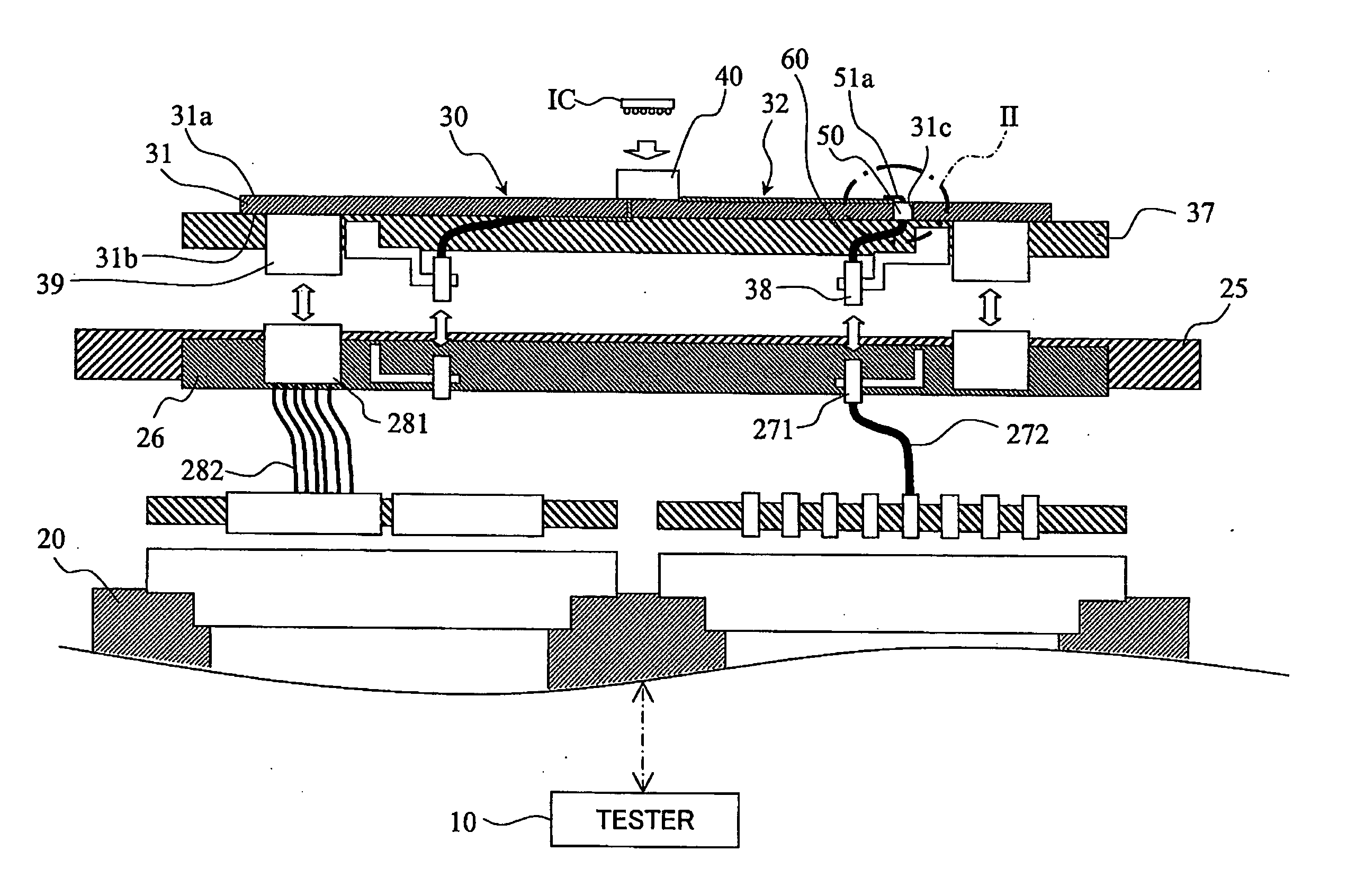

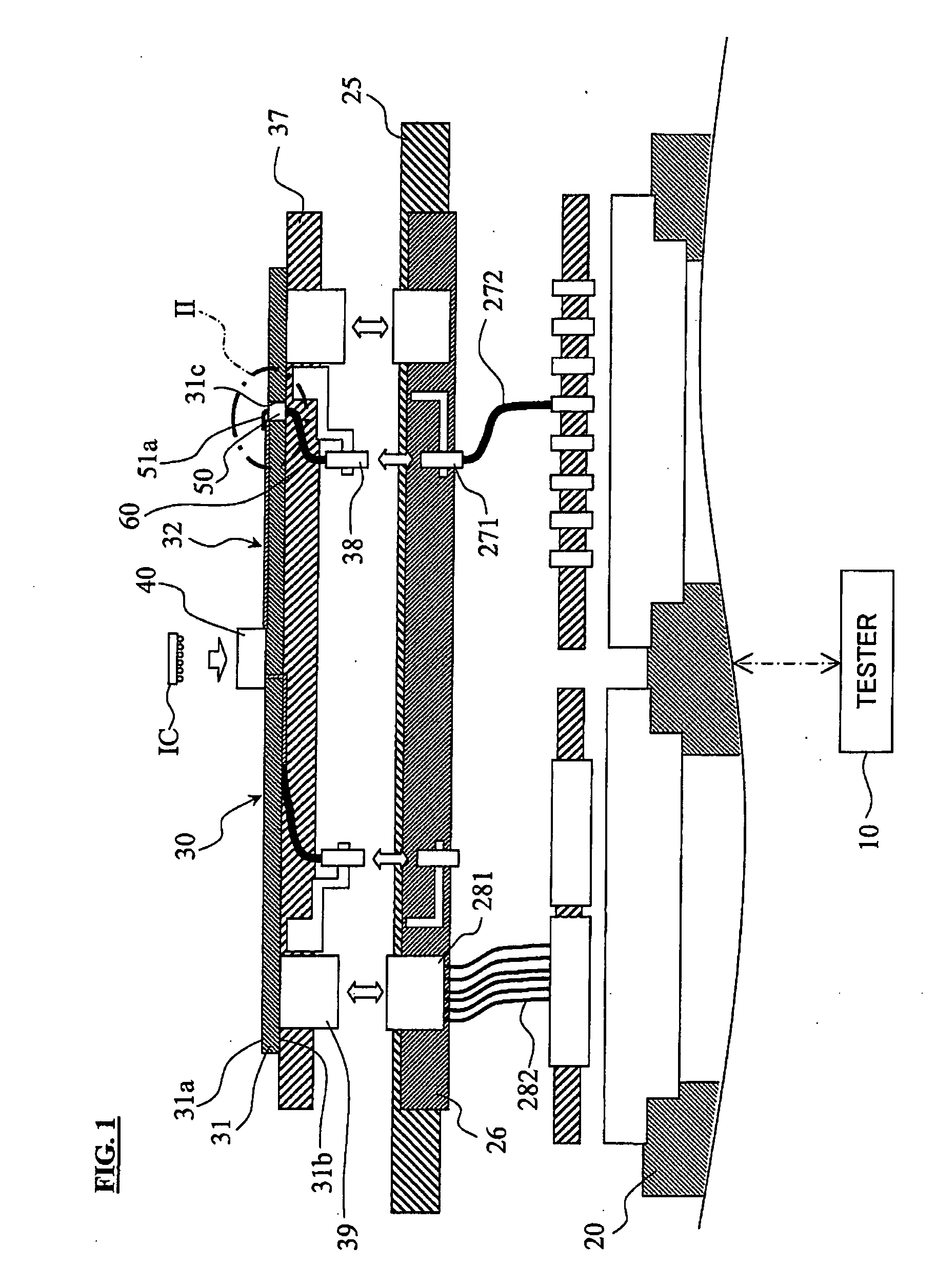

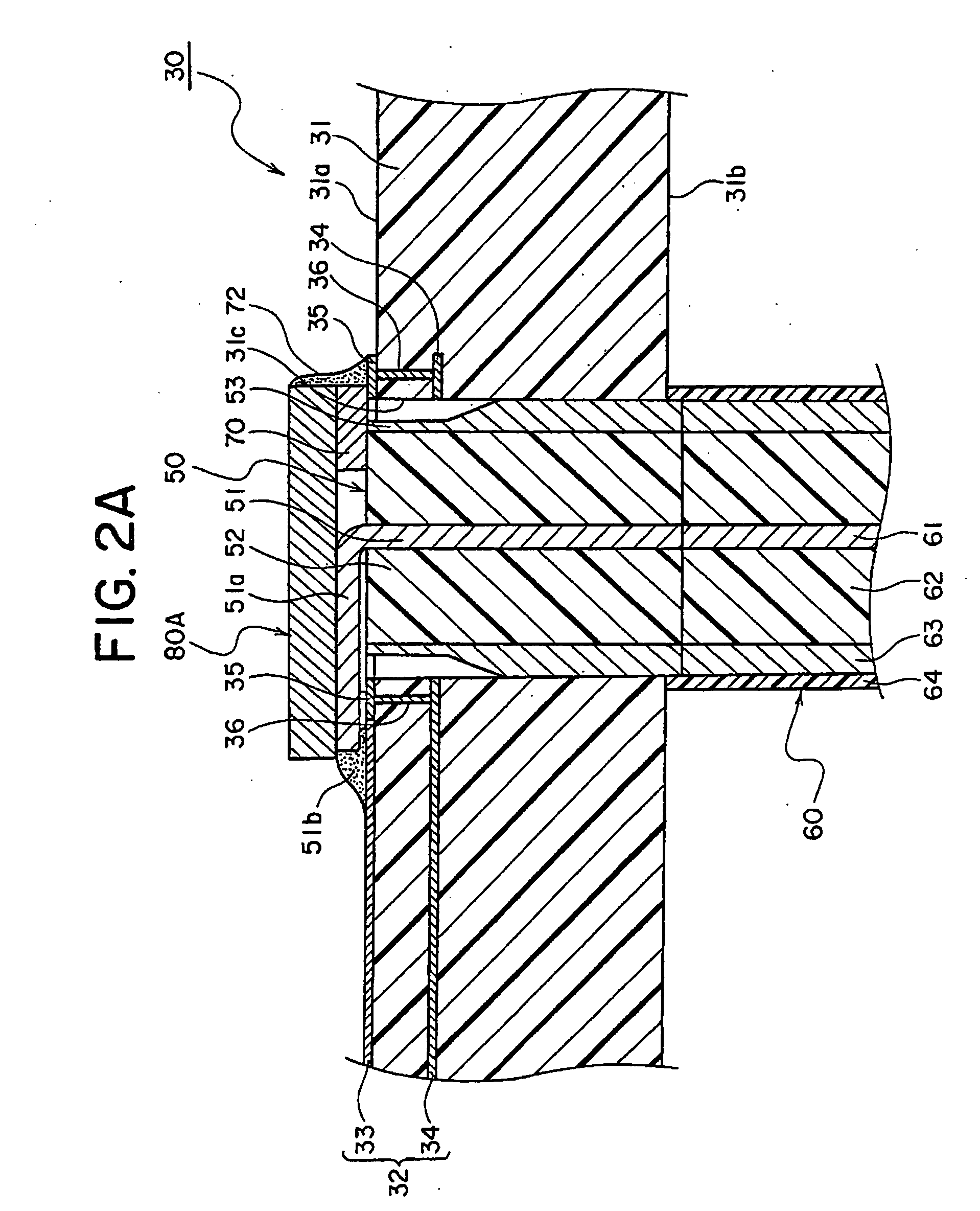

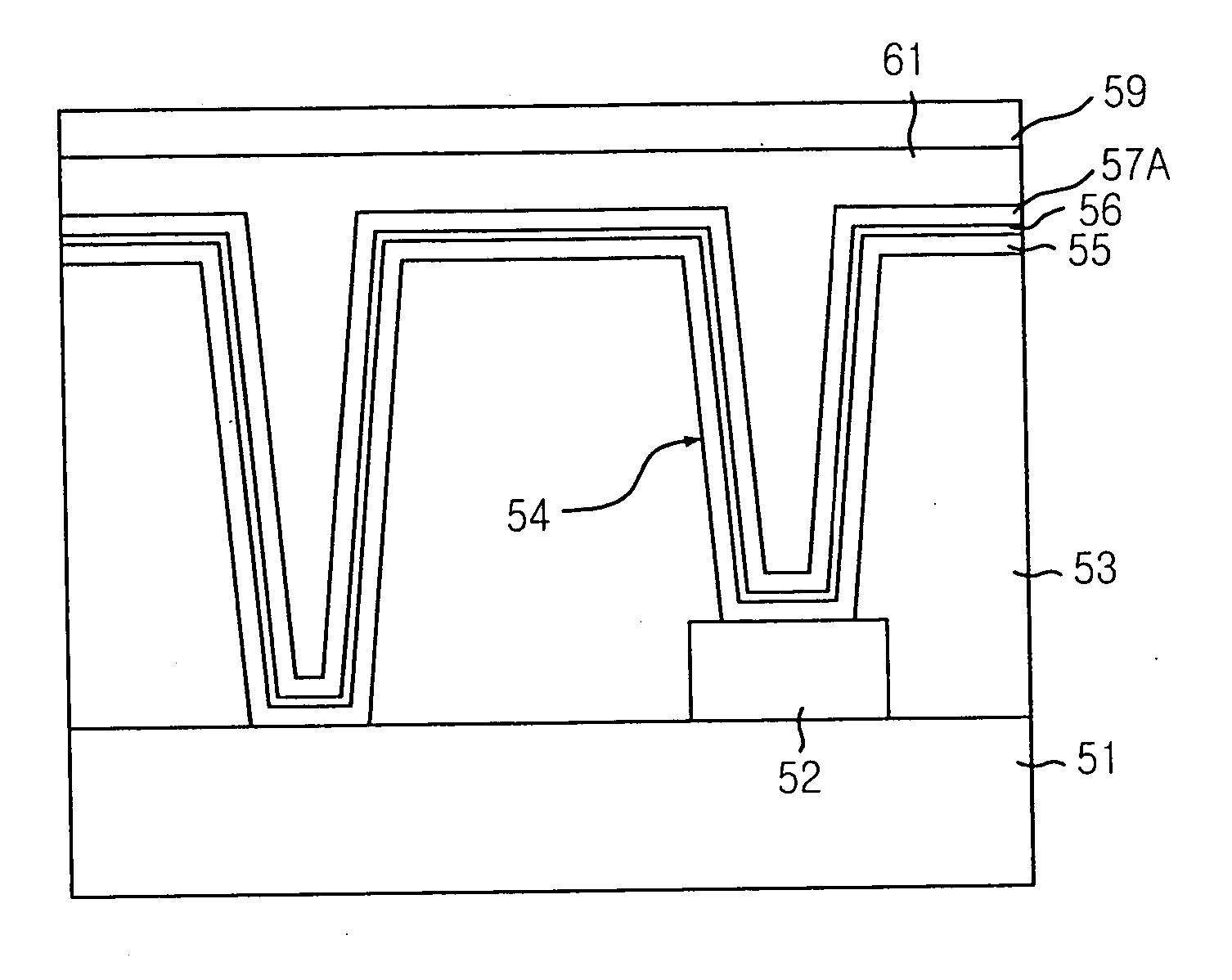

Measurement board for electronic device test apparatus

ActiveUS20070296432A1Reduce lossSuppress signal leakageTwo pole connectionsElectrical measurement instrument detailsElectricityCoaxial cable

A performance board able to secure low loss, low reflection, stable transmission characteristics even when using a high frequency signal to test an electronic device and able to suppress signal leakage to the outside and entry of noise, provided with a base board having a signal pattern electrically connected with a socket formed on its front surface, a coaxial connector to which a coaxial cable electrically connecting the performance board and test apparatus is connected, passing through the base board from the back surface toward the front surface, and having a front exposed part of the center contact bent and electrically connected to the signal pattern, and a cover member covering the front exposed part of the center contact and correcting the impedance of the front exposed part.

Owner:ADVANTEST CORP

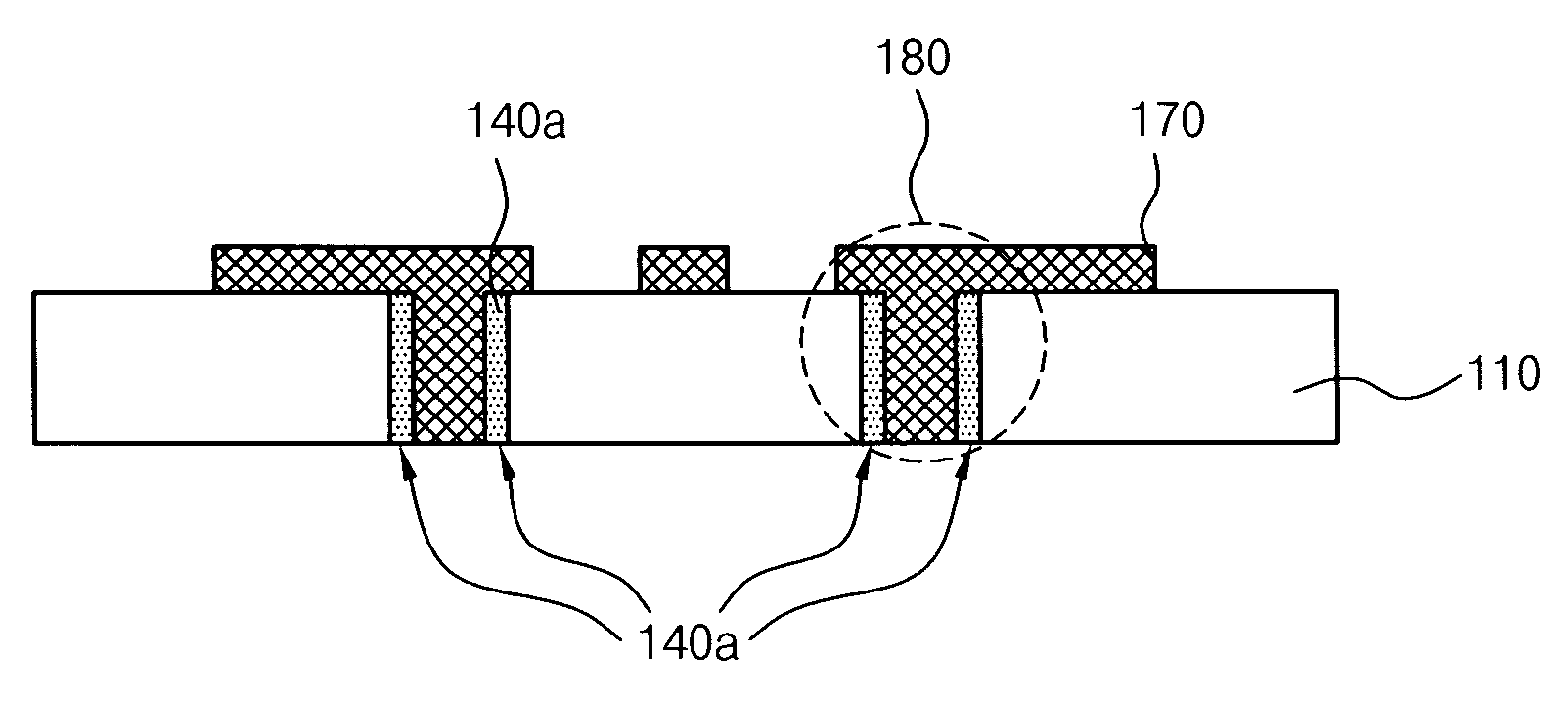

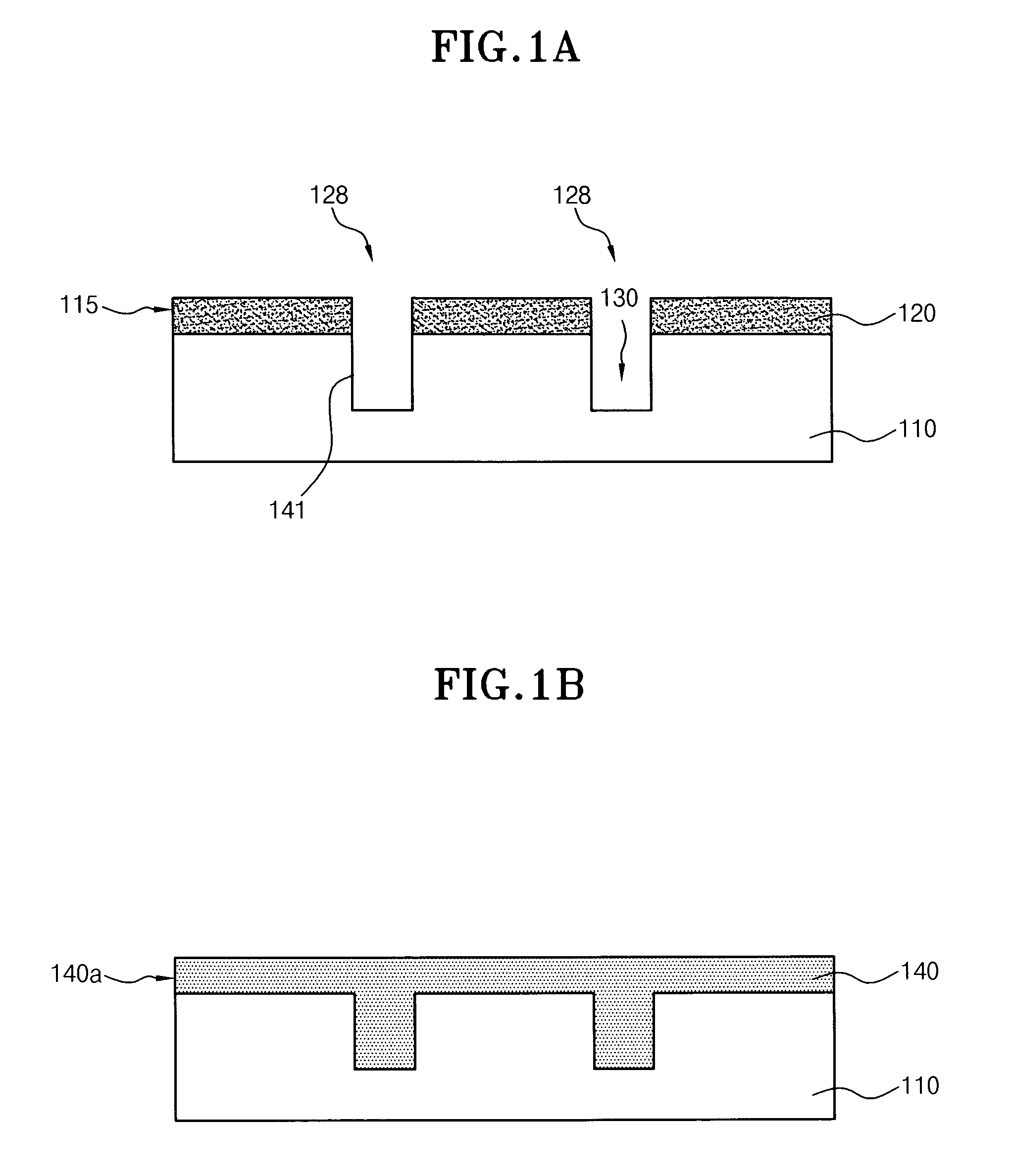

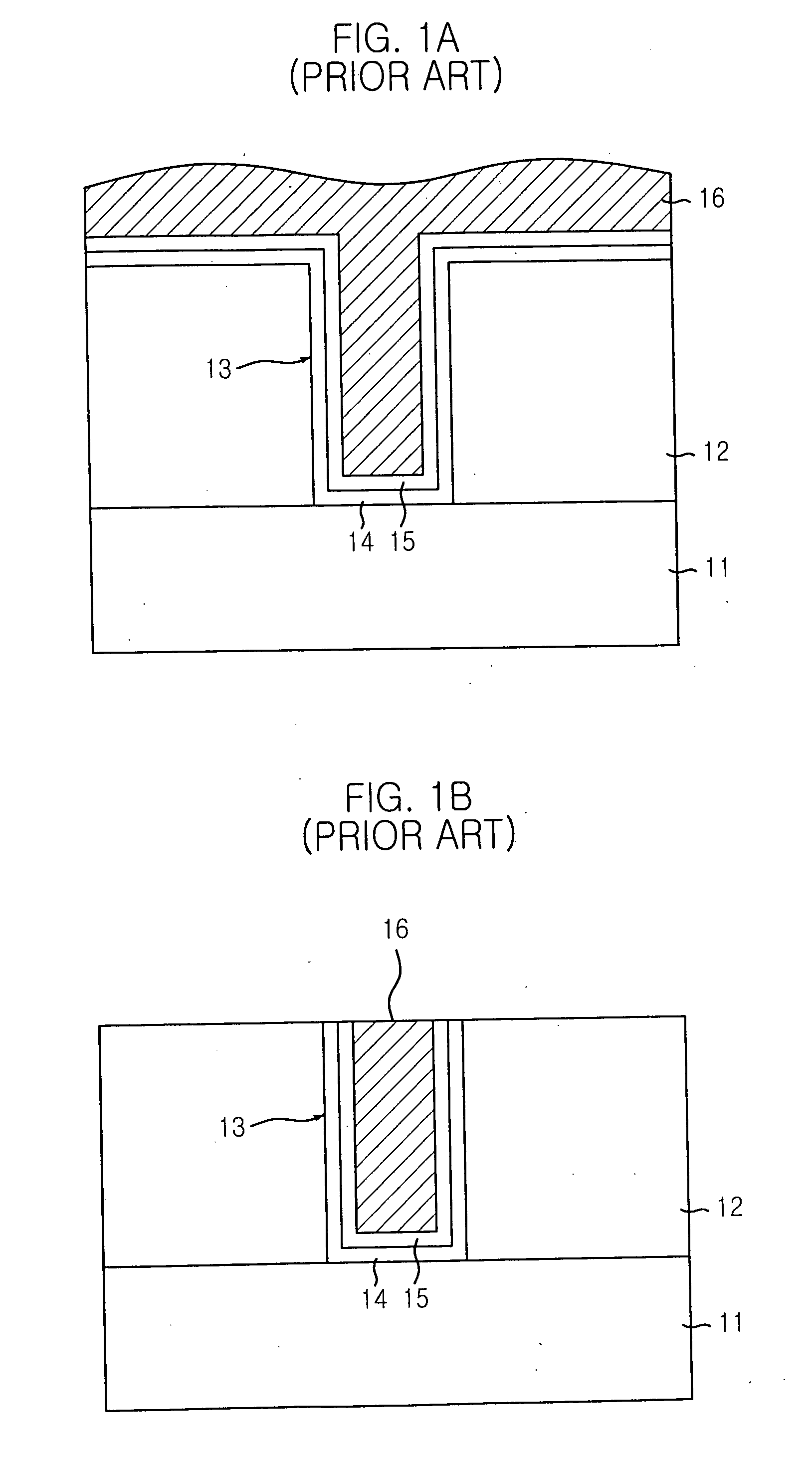

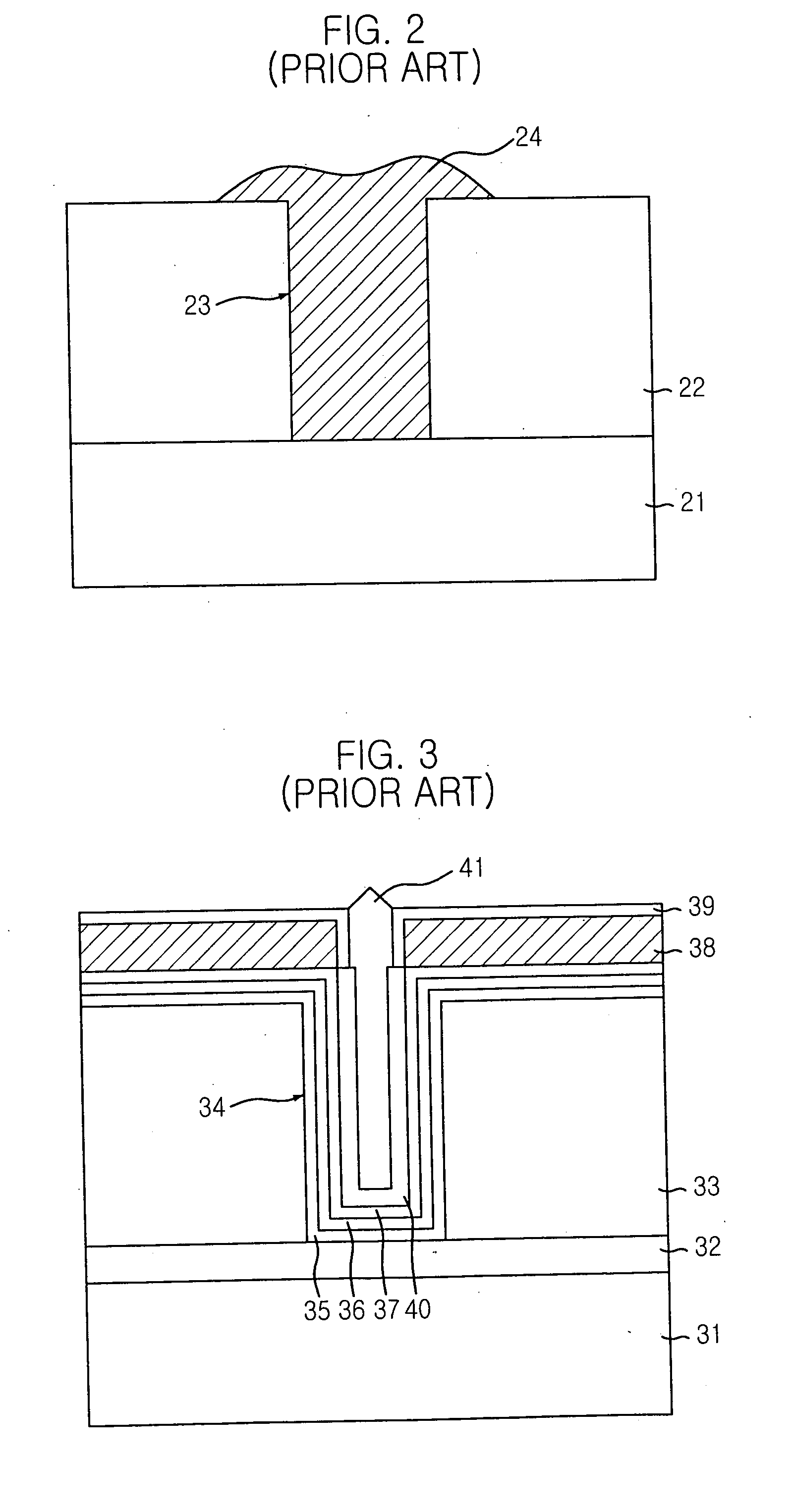

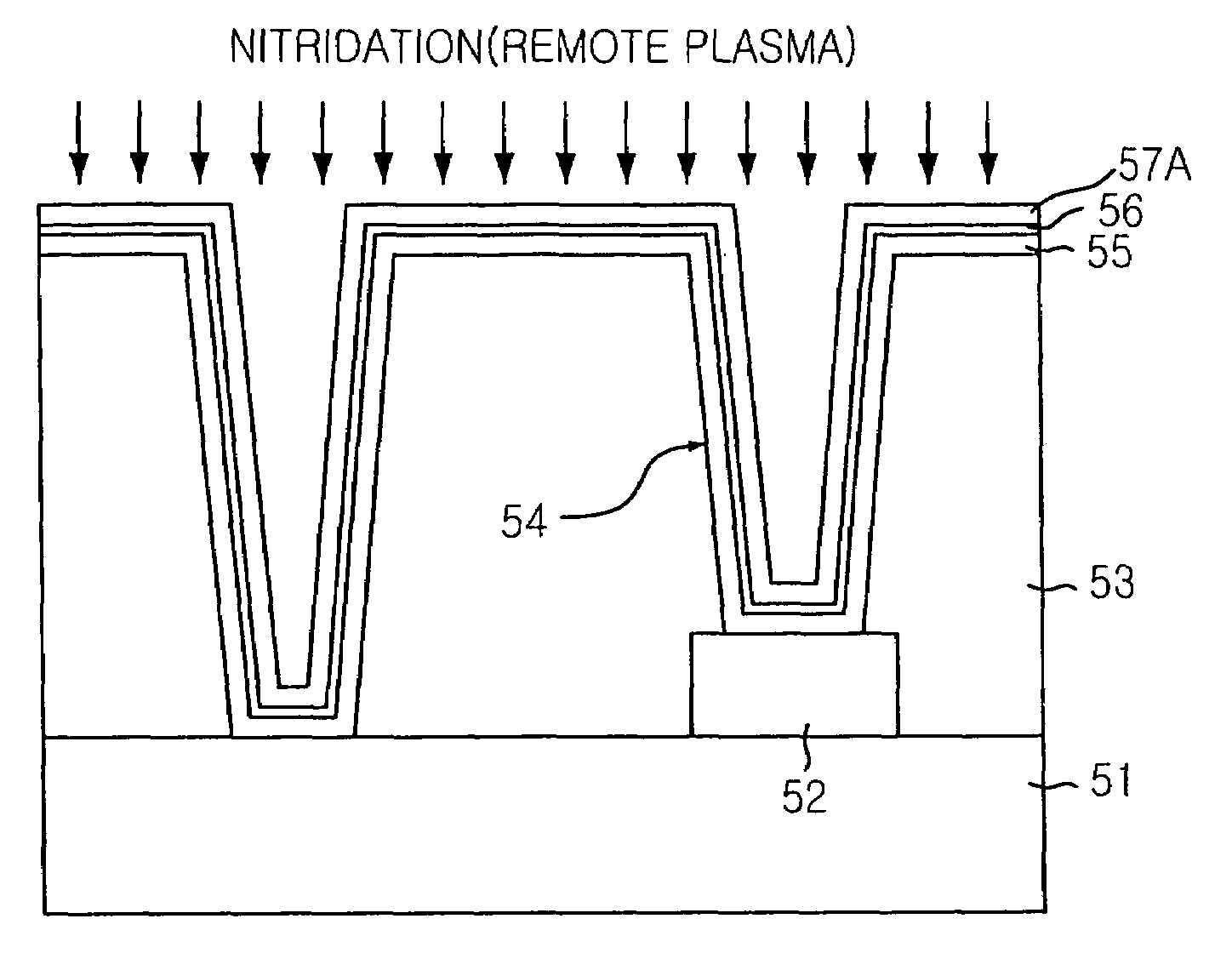

Method for fabricating metal interconnection line with use of barrier metal layer formed in low temperature

InactiveUS20050250314A1Secure characteristicSemiconductor/solid-state device detailsPlastic recyclingMetal interconnectMetallurgy

The present invention relates to a method for fabricating a metal interconnection line with use of a barrier metal layer formed in a low temperature. The method includes the steps of: forming an inter-layer insulation layer on a substrate; etching predetermined regions of the inter-layer insulation layer to form a plurality of contact openings; forming an ohmic metal layer on the contact openings and the etched inter-layer insulation layer; forming a seed layer on the ohmic metal layer; forming a metal layer on the seed layer and nitriding the metal layer in a repeated number of times to form a barrier metal layer; and forming a metal interconnection line on the barrier metal layer by burying the contact openings.

Owner:SK HYNIX INC

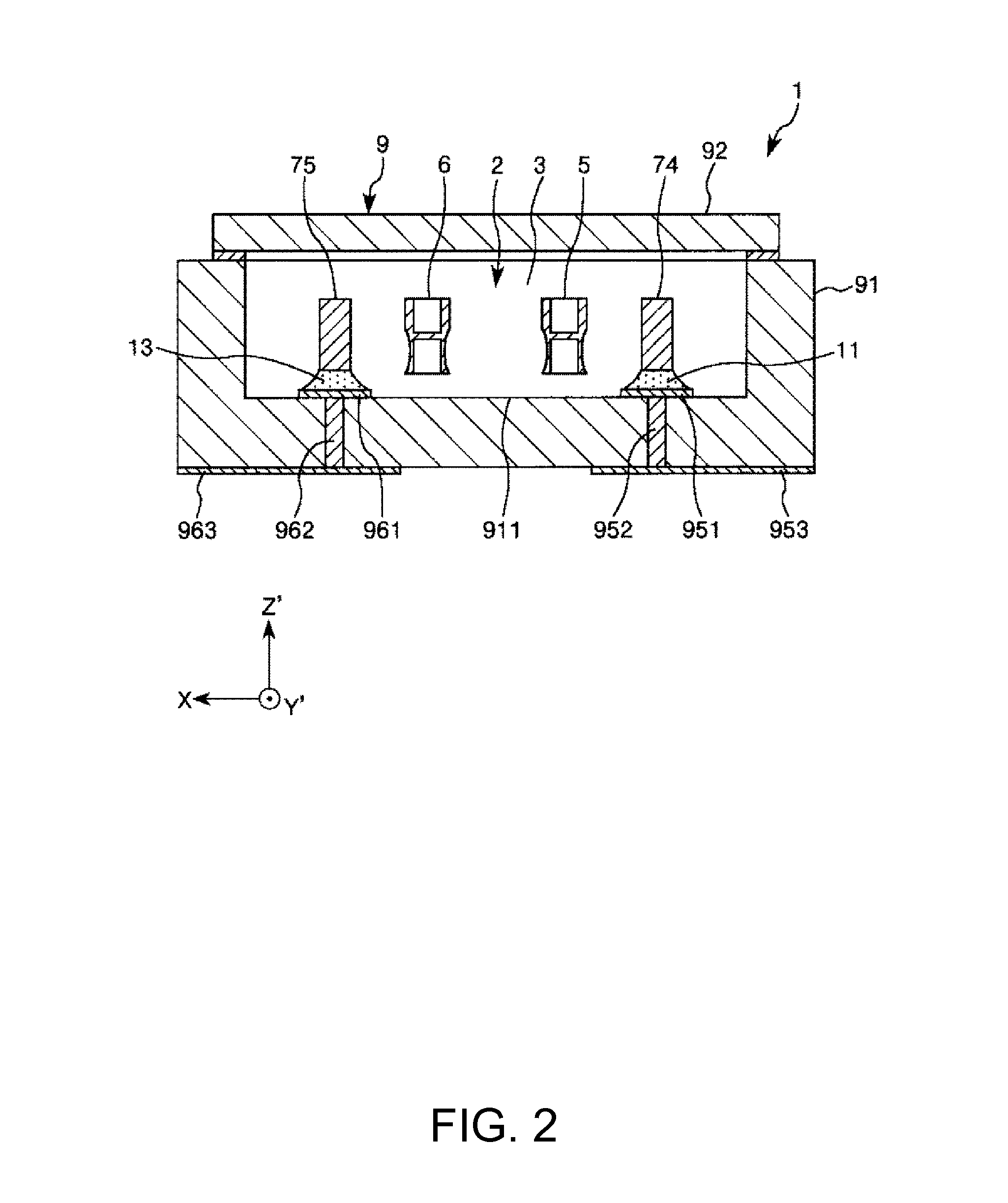

Resonator element, manufacturing method for resonator element, resonator, electronic device, and moving object

ActiveUS20160028370A1Improve reliabilityIncrease surface areaPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksEngineeringElectron

To realize a resonator element capable of obtaining sufficient electric field efficiency and securing a satisfactory element characteristic, a resonator element of the invention includes a base section and a pair of resonating arms extending from the base section. The resonator element includes recesses having a curved surface shape respectively on two side surfaces (surfaces crossing a direction in which the resonating arms resonate) of the resonating arm.

Owner:COLUMBIA PEAK VENTURES LLC

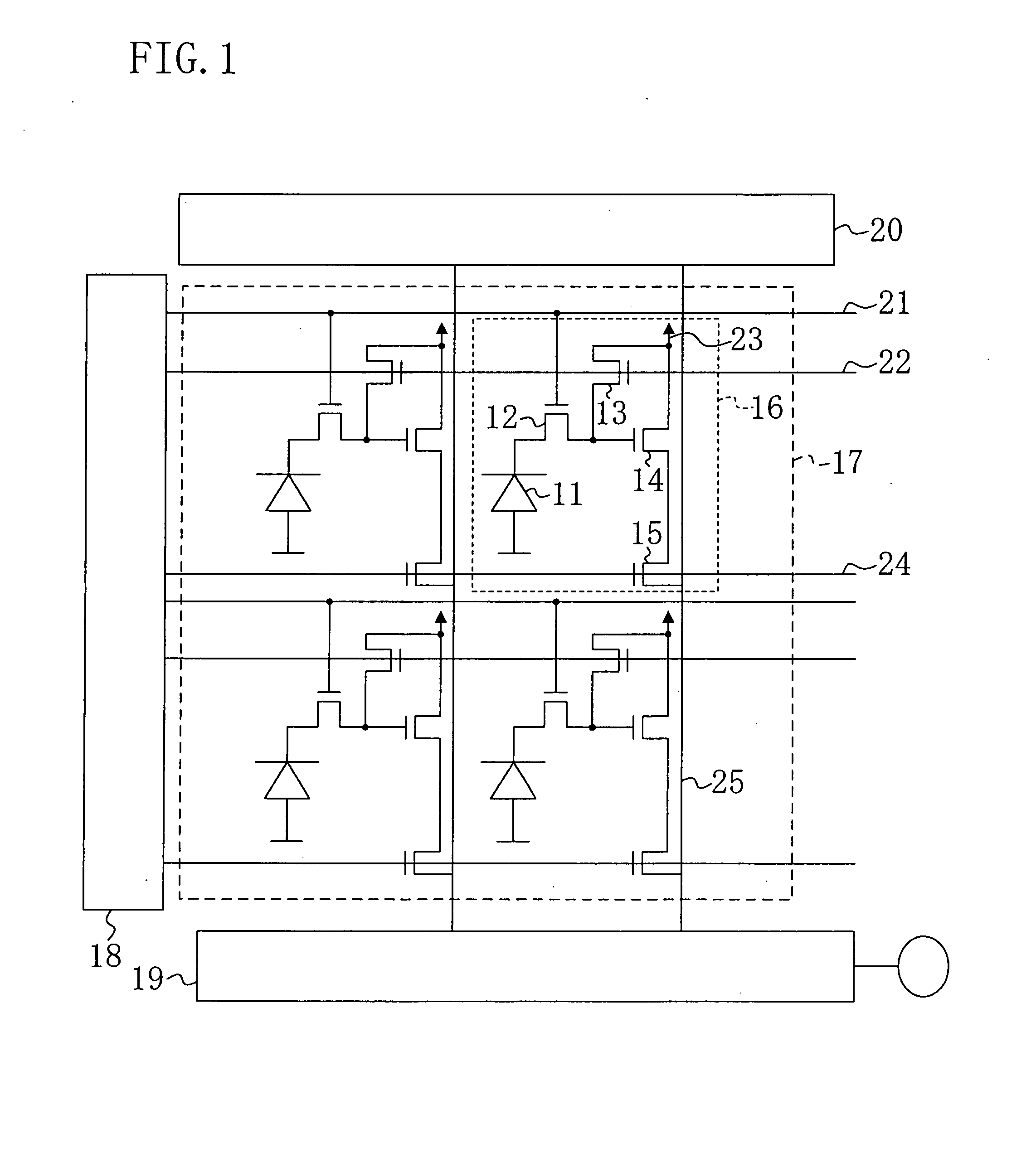

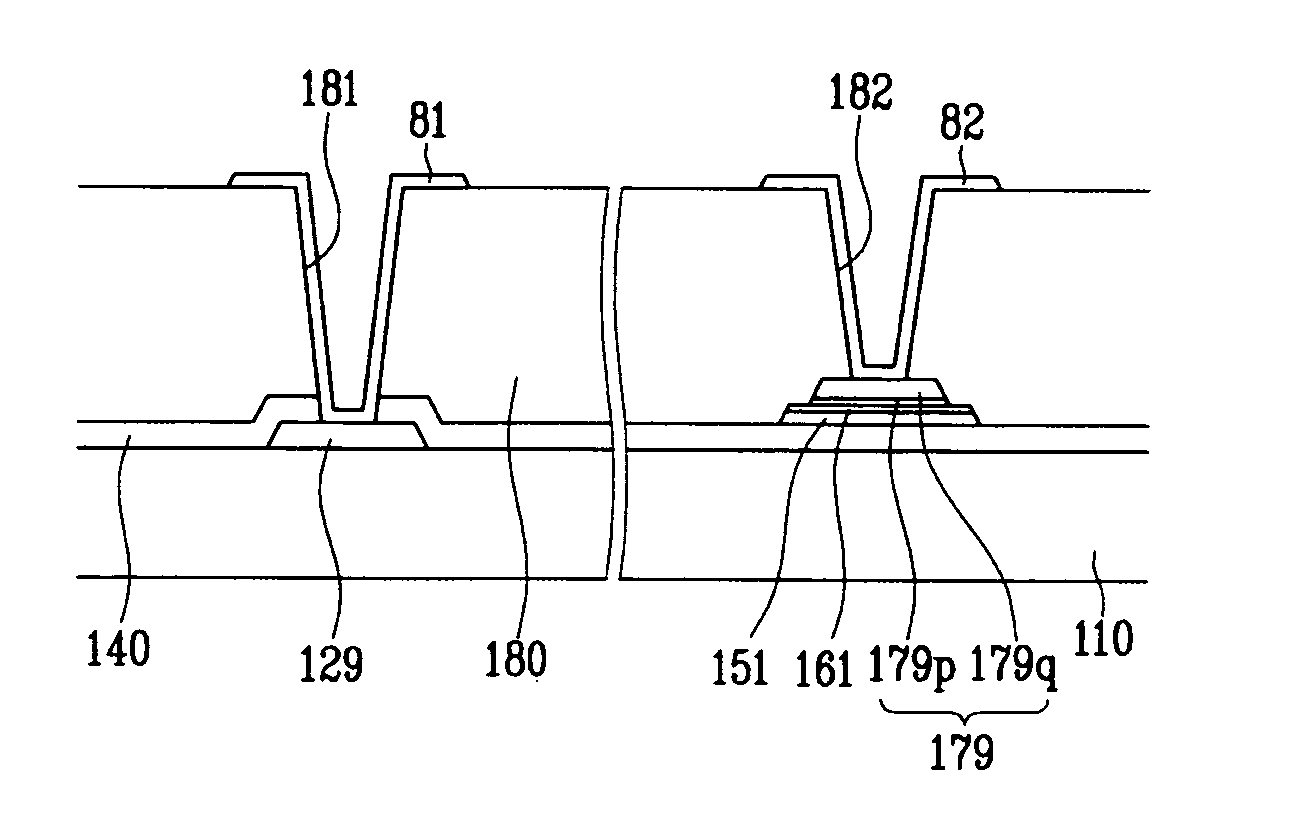

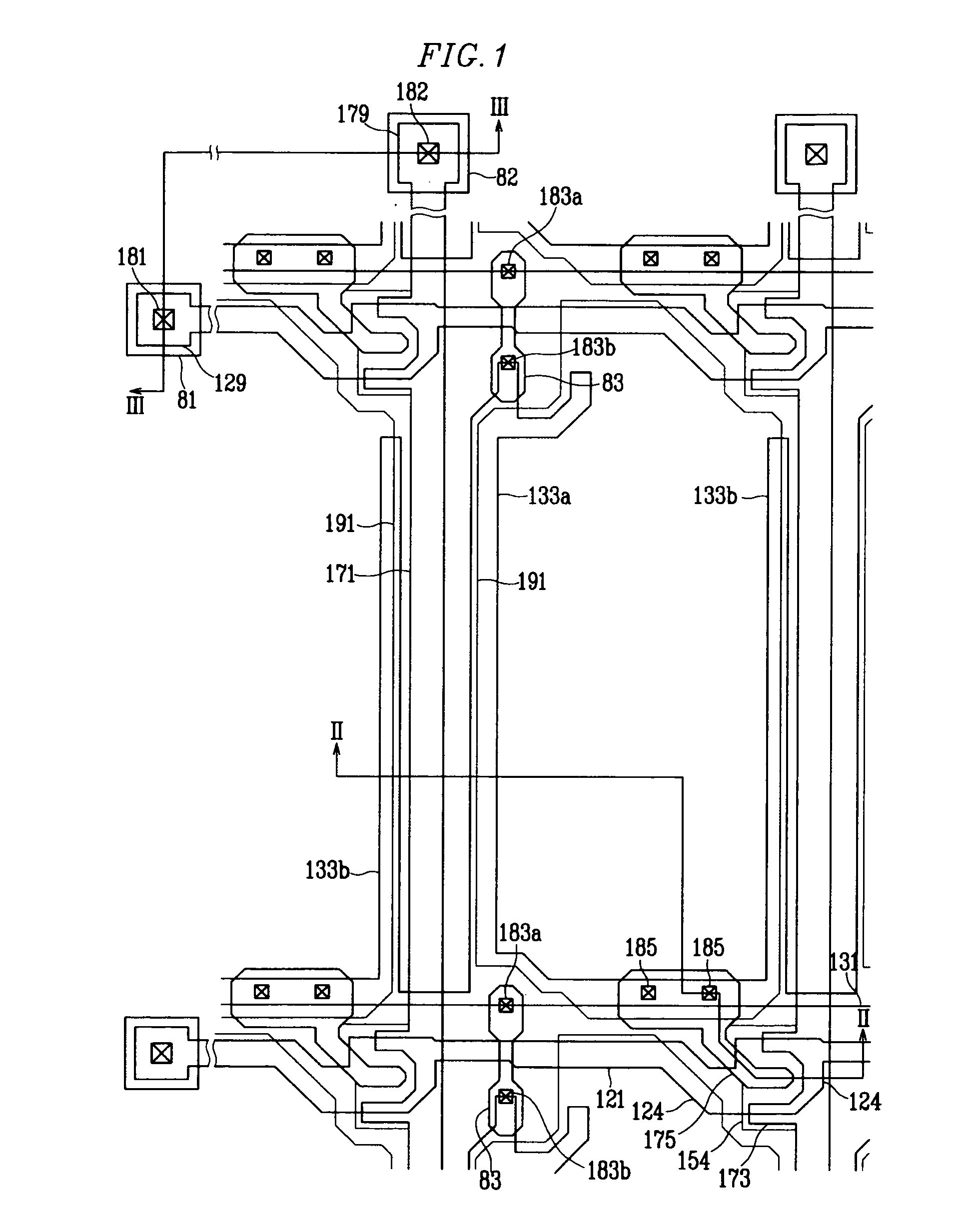

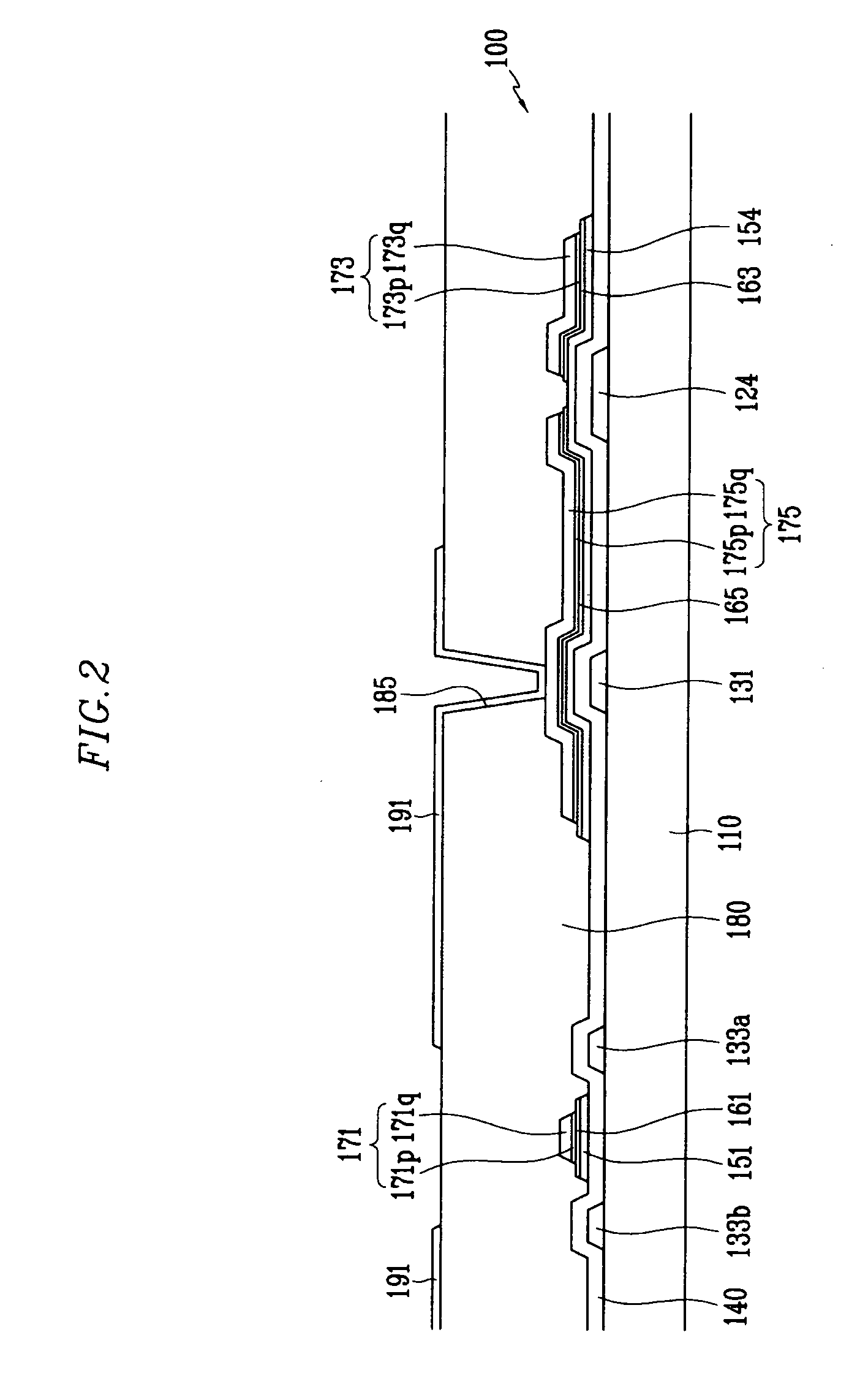

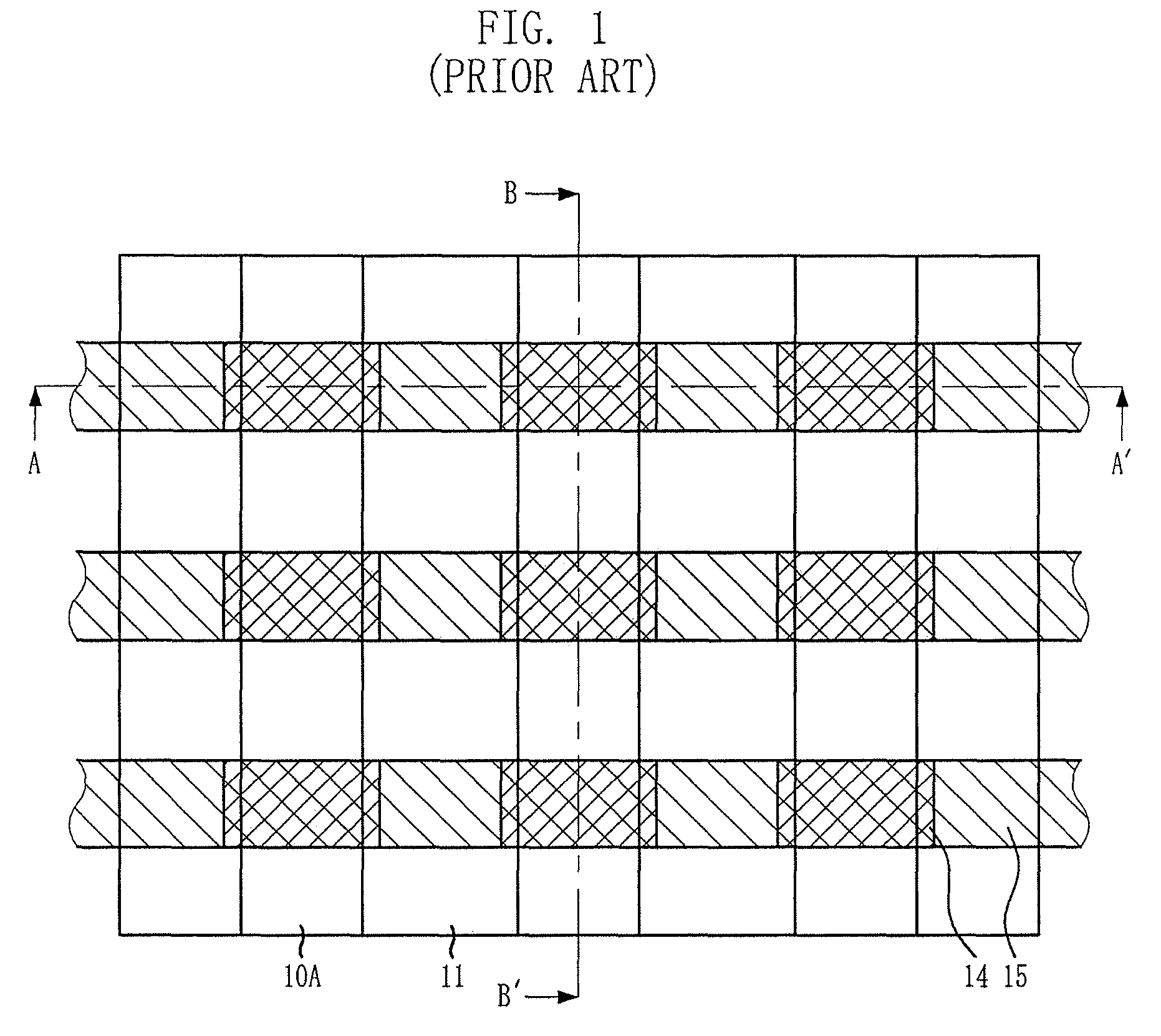

Thin film transistor array panel and method of manufacturing the same

InactiveUS20070111412A1Reduce pollutionSecure characteristicSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayOhmic contact

In one embodiment, a thin film transistor array display panel and method of manufacturing the same are provided. A method includes forming a gate line on a substrate; forming a gate insulating layer, a semiconductor layer, and an ohmic contact layer on the gate line; forming a data layer on the ohmic contact layer; forming a photosensitive pattern on the data layer; etching the data layer to form a data line including a source electrode and a drain electrode that is opposite to the source electrode; reflowing the photosensitive pattern to cover side surfaces of the source electrode and the drain electrode; and etching the ohmic contact layer using the reflowed photosensitive pattern as a mask.

Owner:SAMSUNG ELECTRONICS CO LTD

Out-of band authentication method and system for communication over a data network

A method and system for out-of-band authentication of messages transmitted, e.g. as packets, on a communication network, whereby a first stream of data is received by a sender control module from a sender; the first stream of data is transmitted over a first channel, e.g. a non-secure data channel, toward a receiver control module; the sender control module generates authentication data of the first stream of data; the authentication data are transmitted from the sender control module to the receiver control module on a second channel, e.g. a secure data channel, distinct from the first channel; and a stream of data received by the receiver control module is checked using the authentication data. Before sending the authentication data, the sender control module transmits a control message including synchronization data to the receiver control module over the second channel.

Owner:TELECOM ITALIA SPA

3-D nonvolatile memory devices and methods of manufacturing the same

A three-dimensional (3-D) nonvolatile memory device includes a channel layer protruded from a substrate, a plurality of memory cells stacked along the channel layer, a source line coupled to the end of one side of the channel layer, a bit line coupled to the end of the other side of the channel layer, a first junction interposed between the end of one side of the channel layer and the source line and configured to have a P type impurity doped therein, and a second junction interposed between the end of the other side of the channel layer and the bit line and configured to have an N type impurity doped therein.

Owner:SK HYNIX INC

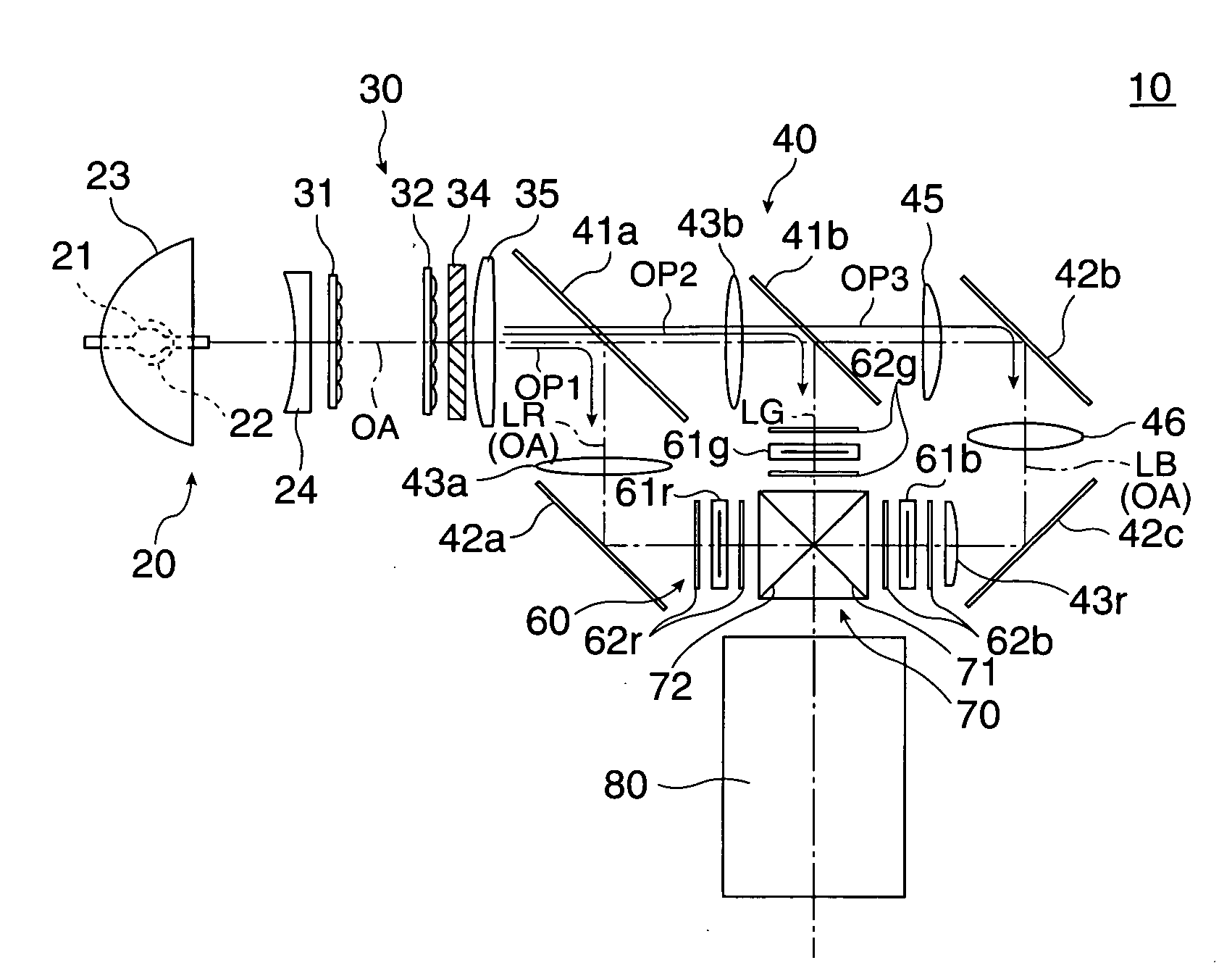

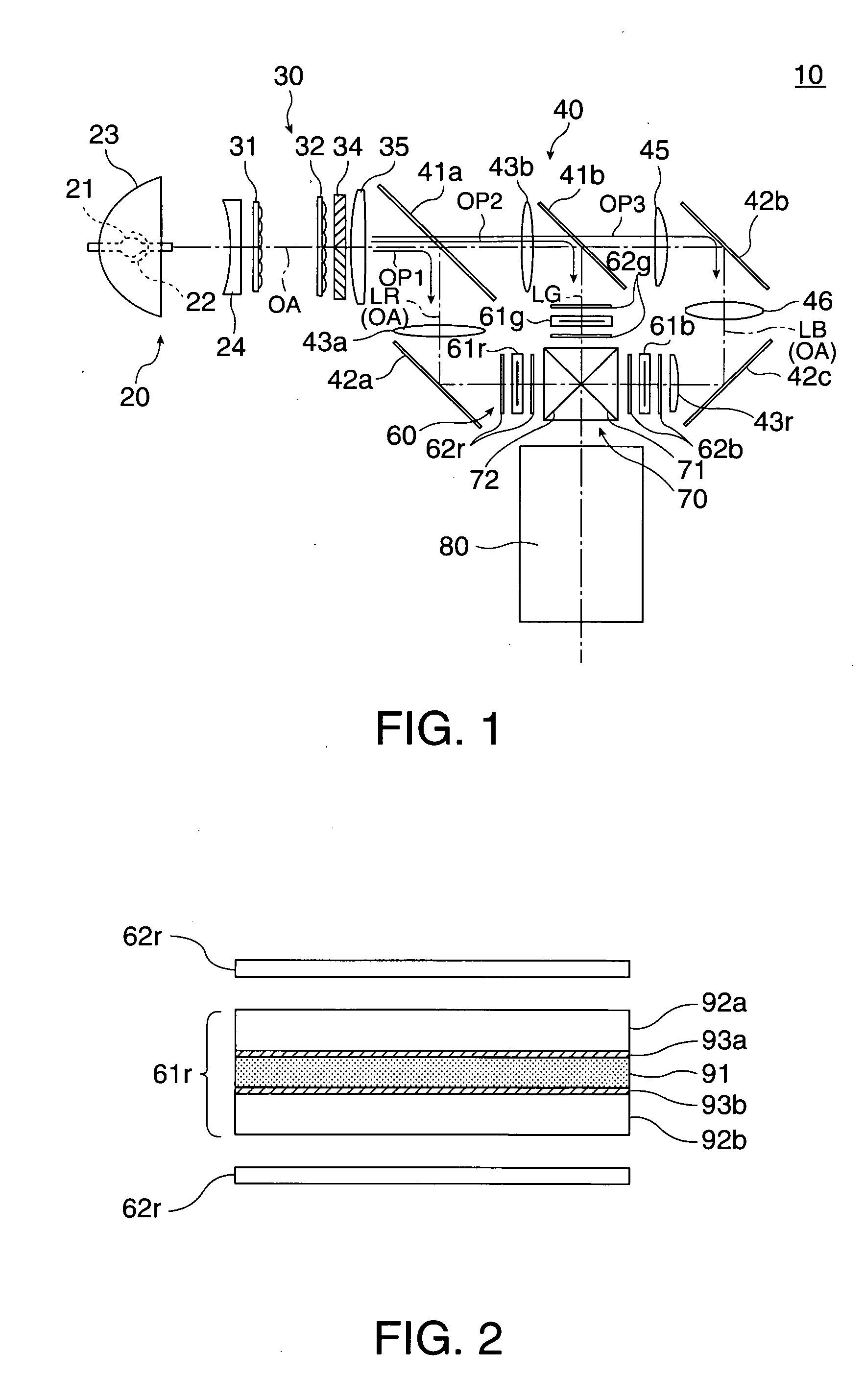

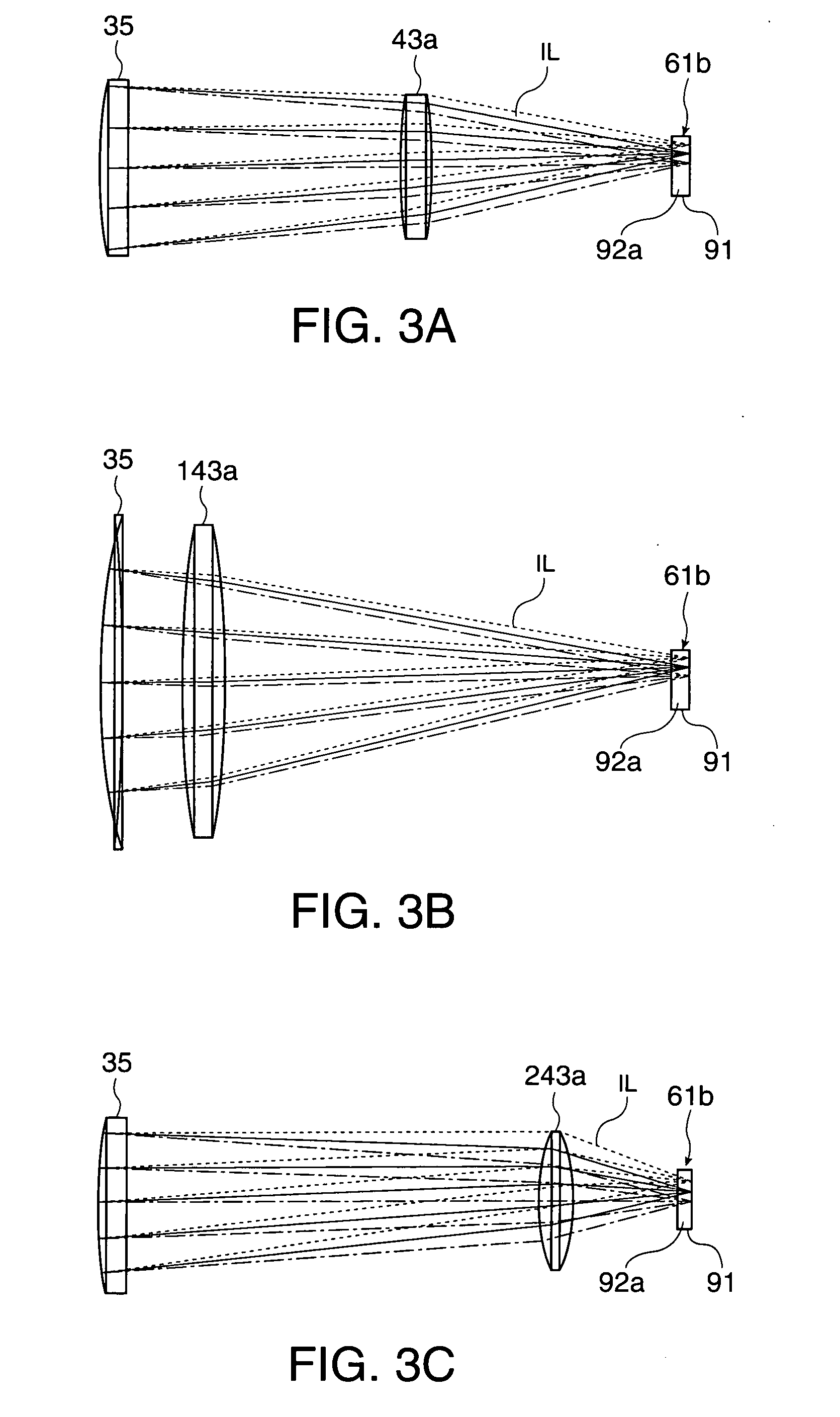

Projector

InactiveUS20080165407A1Small F numberSecure characteristicProjectorsColor television detailsLiquid-crystal displayLight guide

To provide a projector capable of increasing F number of an illumination system without enlarging the size of the illumination system or the like.A combining lens 43a operating in cooperation with a superimposing lens 35 is provided only in a first section between a first dichroic mirror 41a and a red light reflection mirror 42a as a bending mirror on a first optical path OP1 extending from the superimposing lens 35 to a first liquid crystal display panel 61r. Thus, the F number of an illumination system 30 associated with blue light can be controlled with high degree of freedom, and the number of lenses constituting a color separation and light guide system 40 and the illumination system 30 does not increase. Moreover, the incident angle of illumination light does not become large around the first liquid crystal display panel 61r, and thus the telecentric characteristics of the illumination system 30 associated with blue light can be secured.

Owner:COLUMBIA PEAK VENTURES LLC

Method for fabricating metal interconnection line with use of barrier metal layer formed in low temperature

InactiveUS7375024B2Secure characteristicSemiconductor/solid-state device detailsPlastic recyclingInter layerInsulation layer

The present invention relates to a method for fabricating a metal interconnection line with use of a barrier metal layer formed in a low temperature. The method includes the steps of: forming an inter-layer insulation layer on a substrate; etching predetermined regions of the inter-layer insulation layer to form a plurality of contact openings; forming an ohmic metal layer on the contact openings and the etched inter-layer insulation layer; forming a seed layer on the ohmic metal layer; forming a metal layer on the seed layer and nitriding the metal layer in a repeated number of times to form a barrier metal layer; and forming a metal interconnection line on the barrier metal layer by burying the contact openings.

Owner:SK HYNIX INC

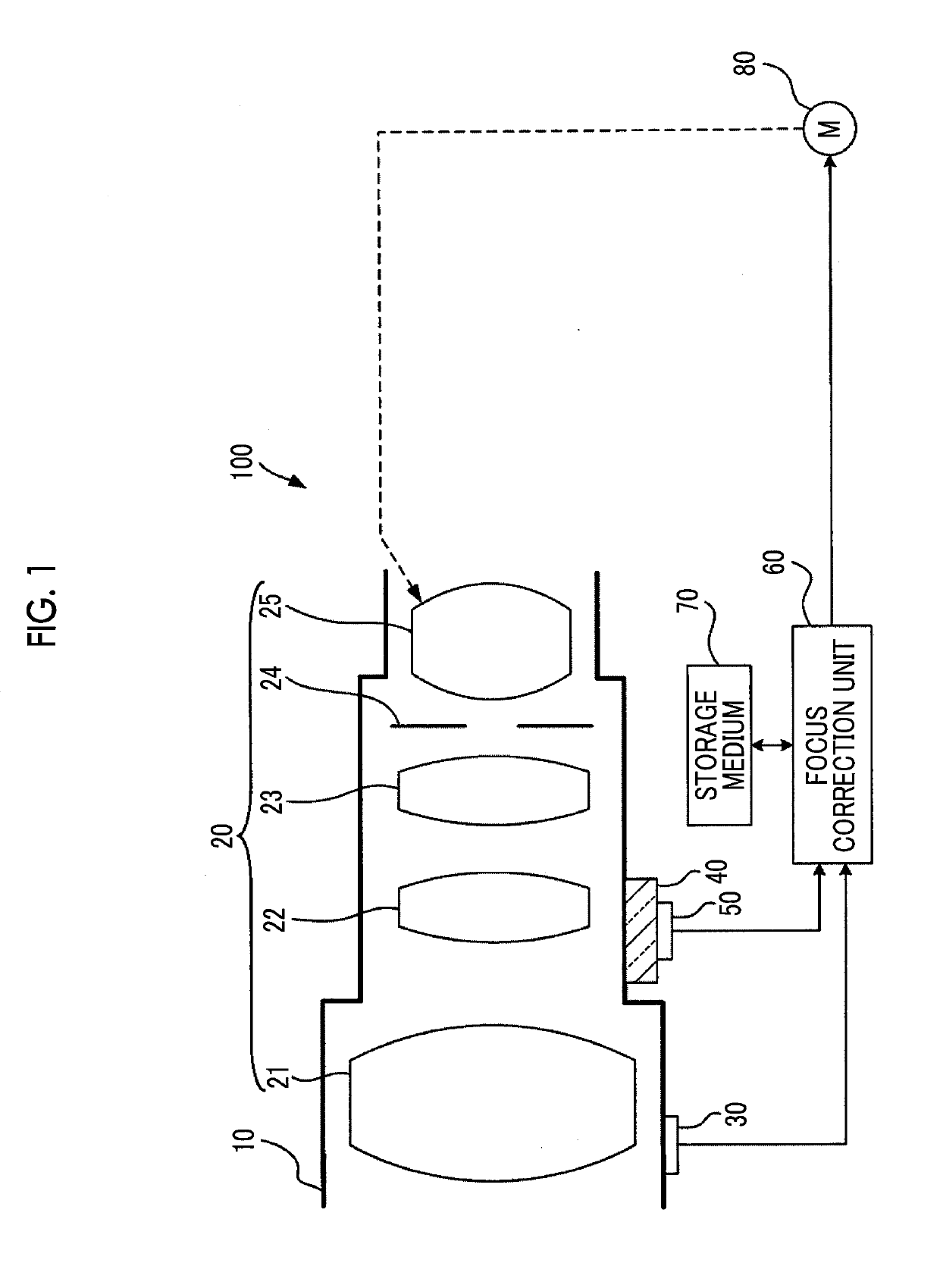

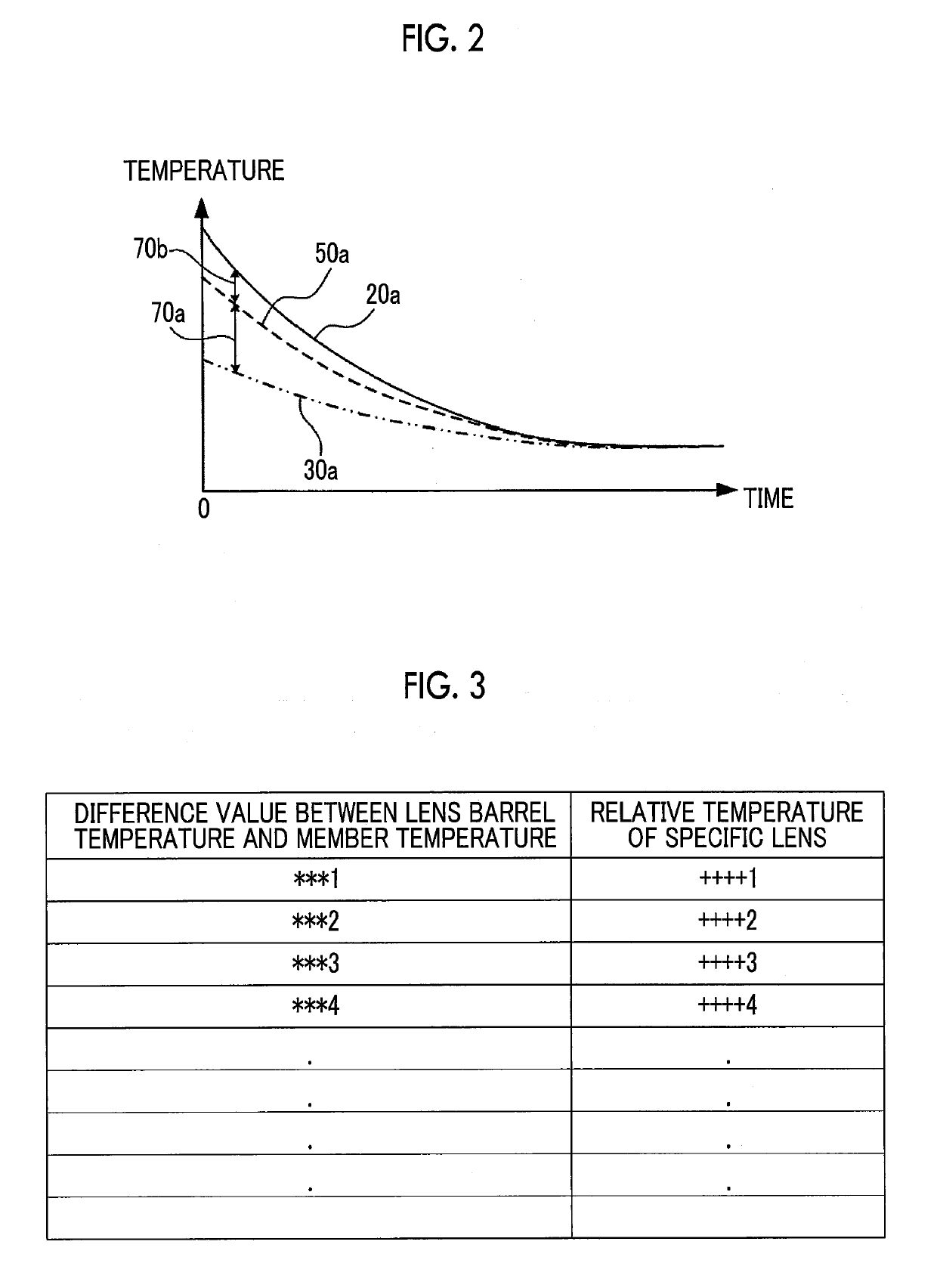

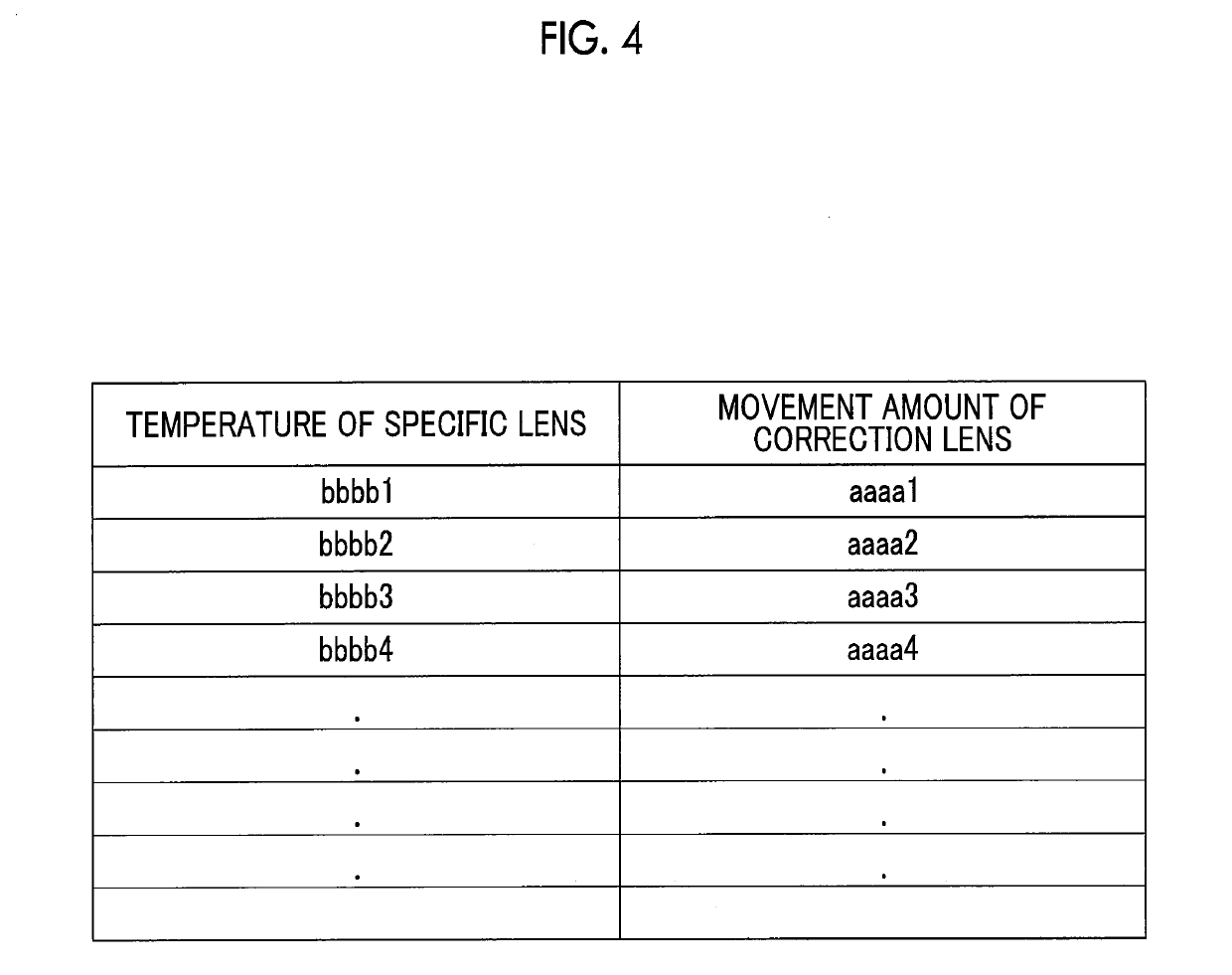

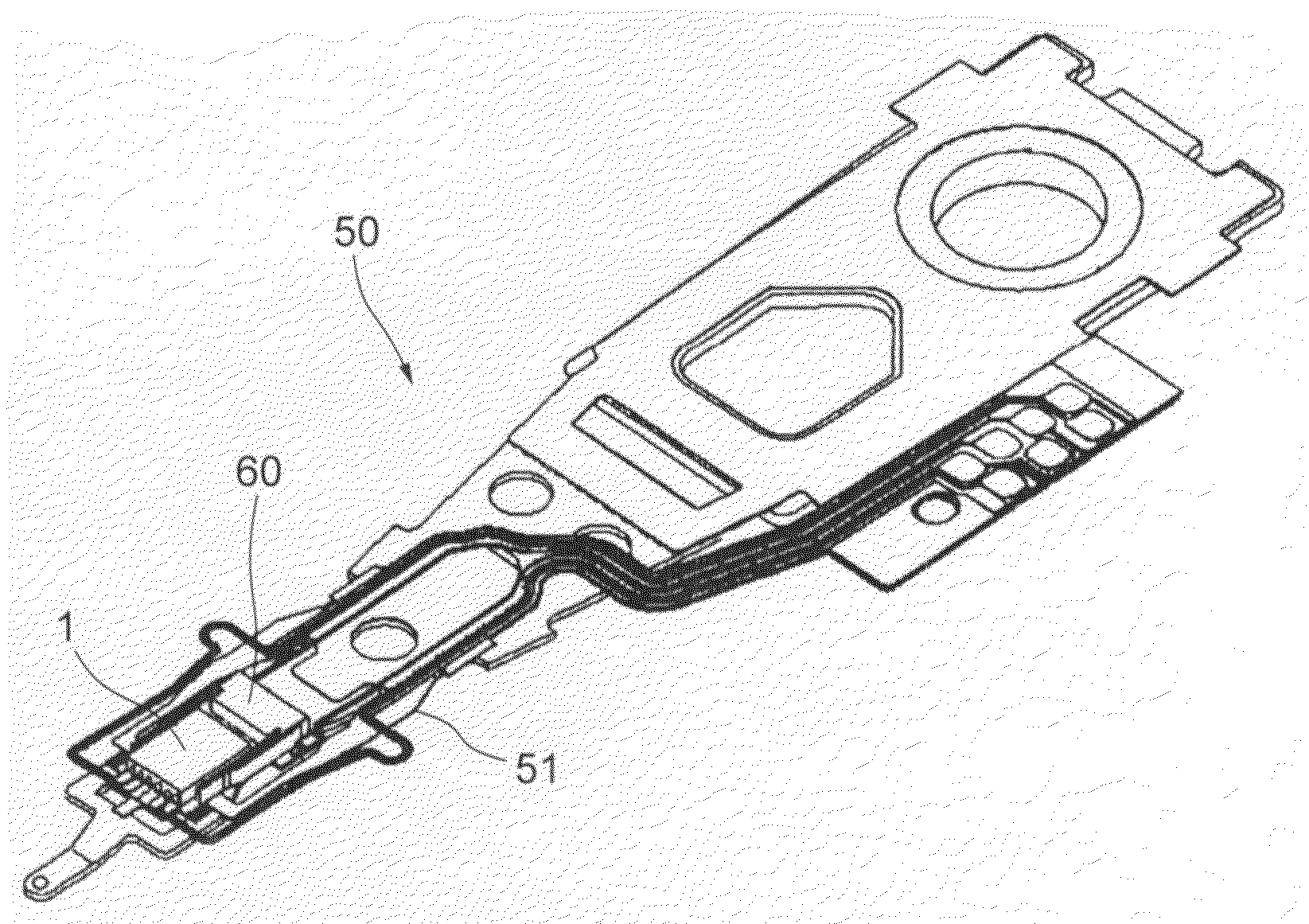

Lens device, imaging device, and focus shift correction method of lens device

ActiveUS20190187403A1Avoid focus shiftIncreased degrees of freedomTelevision system scanning detailsProjector film strip handlingCamera lensTime changes

Provided are a lens device capable of preventing a focus shift of an imaging optical system due to heat without reducing a degree of freedom of design, an imaging device comprising the same, and a focus shift correction method of a lens device. A lens device 100 includes an imaging optical system 20 that includes a plurality of lenses, a lens barrel 10 that accommodates the imaging optical system 20, a temperature sensor 30 that is provided outside the lens barrel 10 to detect a temperature of the lens barrel 10, a temperature sensor 50 that is provided outside the lens barrel 10 to detect a temperature of a member 40 of which a temperature characteristic indicating a temperature change with a time change is different from a temperature characteristic of the lens barrel 10, and a focus correction unit 60 that corrects a focus shift of the imaging optical system 20 by controlling a relay lens 25 as a correction lens included in the imaging optical system 20 based on temperature information items respectively detected by the temperature sensor 30 and the temperature sensor 50.

Owner:FUJIFILM CORP

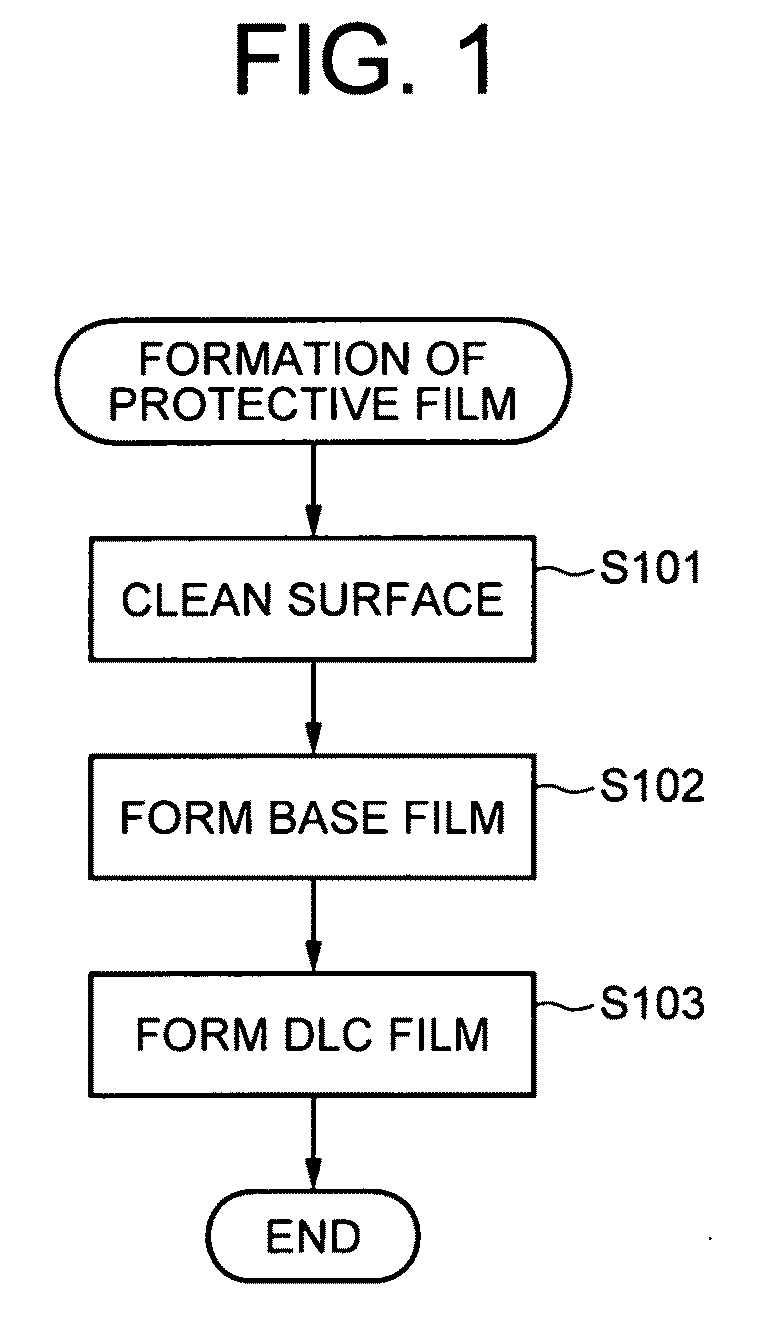

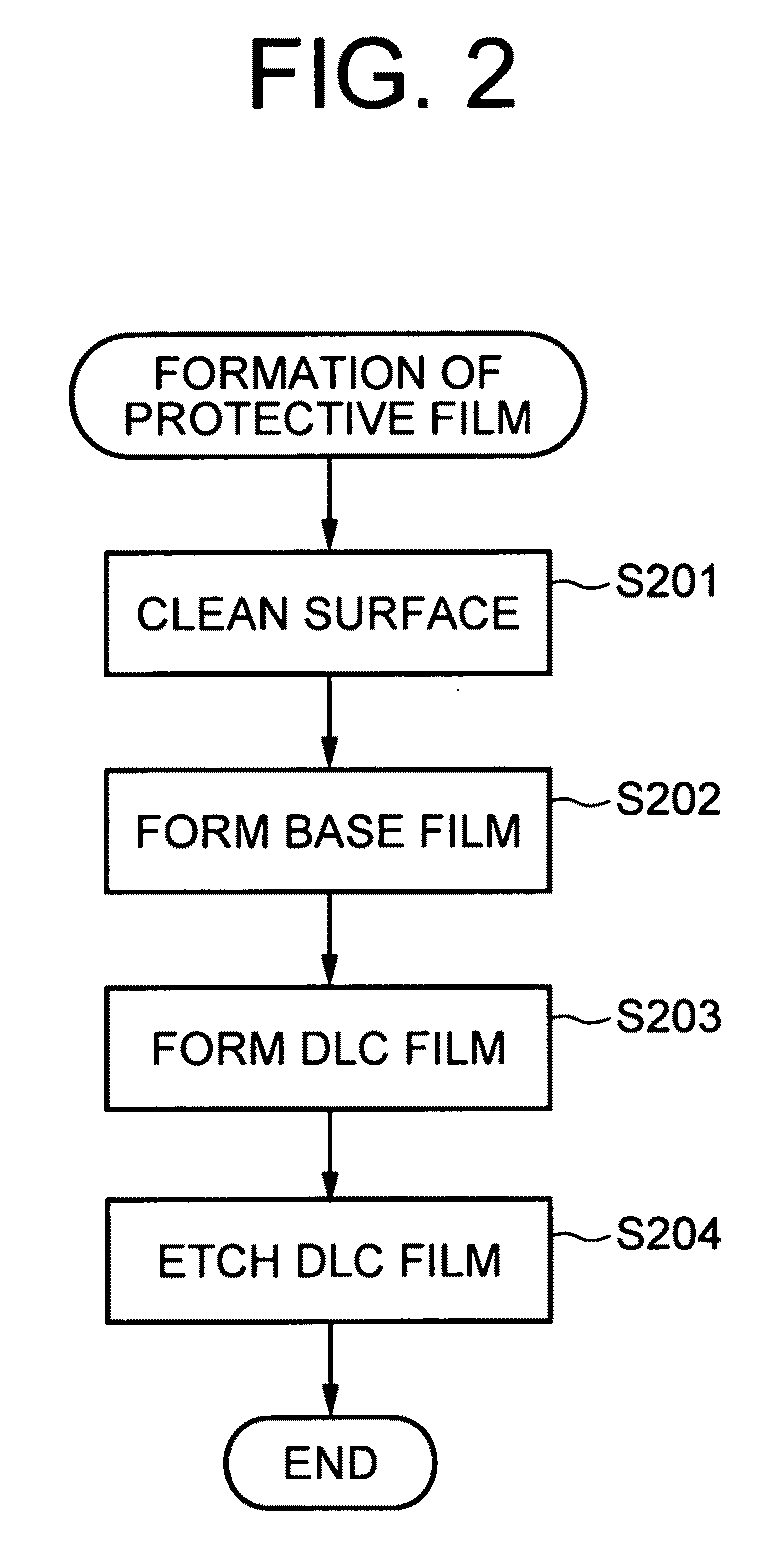

Protective film forming method

ActiveUS20090135521A1Improve corrosion resistanceHigh-quality protectionDecorative surface effectsVacuum evaporation coatingCarbon filmTectorial membrane

To provide a high-quality protection target by forming a protective film that is thin and excellent in corrosion resistance. Provided is a protective film forming method for forming a protective film at least on a surface of a protection target. The method comprises: a base film forming step for forming a base film on the surface of the protection target; and a DLC film forming step for forming a diamond-like carbon film on the base film. The base film forming step forms the base film on the surface of the protection target for a plurality of times by repeating a process of depositing the base film in a prescribed thickness and eliminating a part of or a whole part of the base film. Further, the method comprises, before the DLC film forming step, an insulating layer forming step for forming an insulating layer on the surface of the base film on which the diamond-like carbon film is to be formed.

Owner:SAE MAGNETICS (HK) LTD

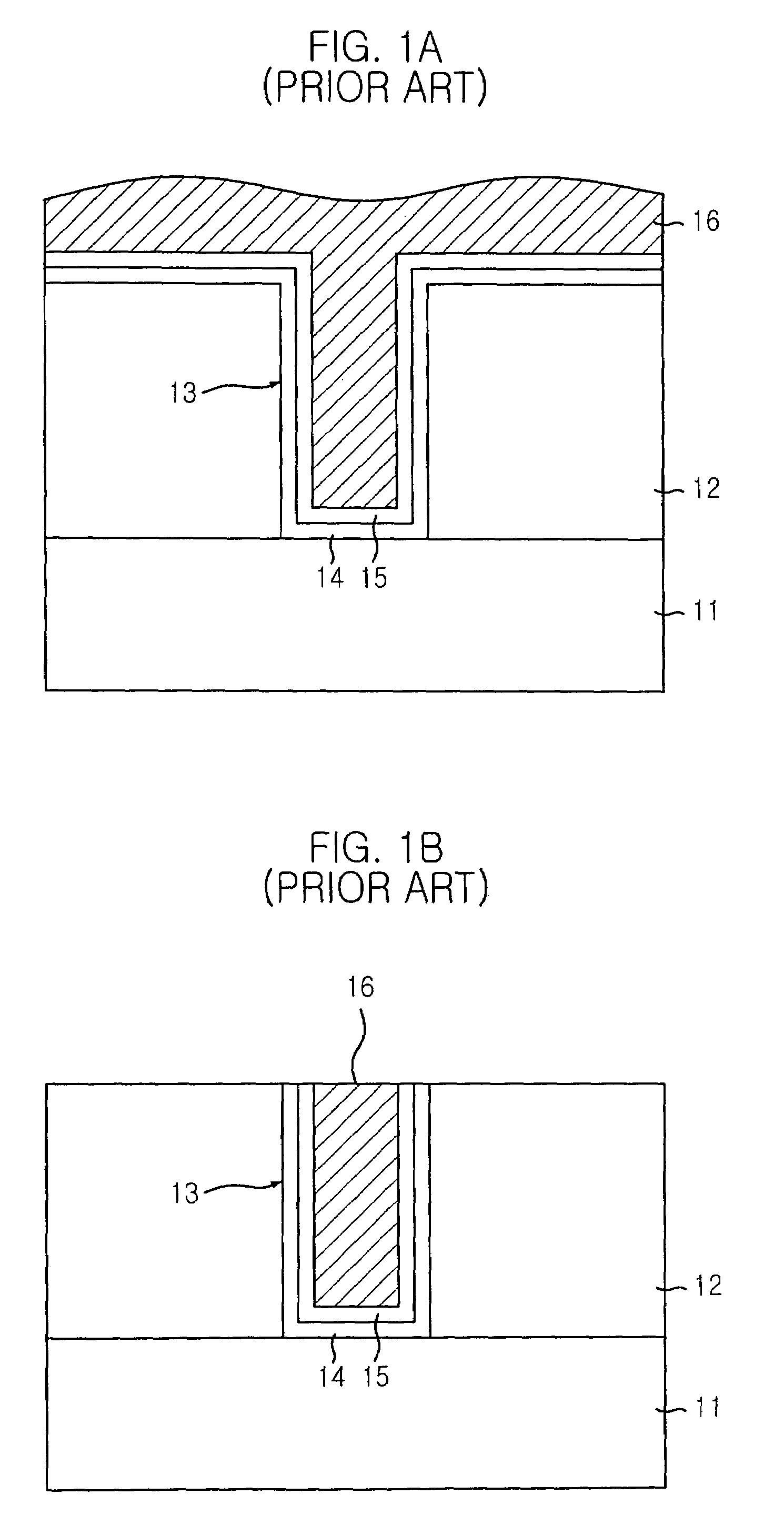

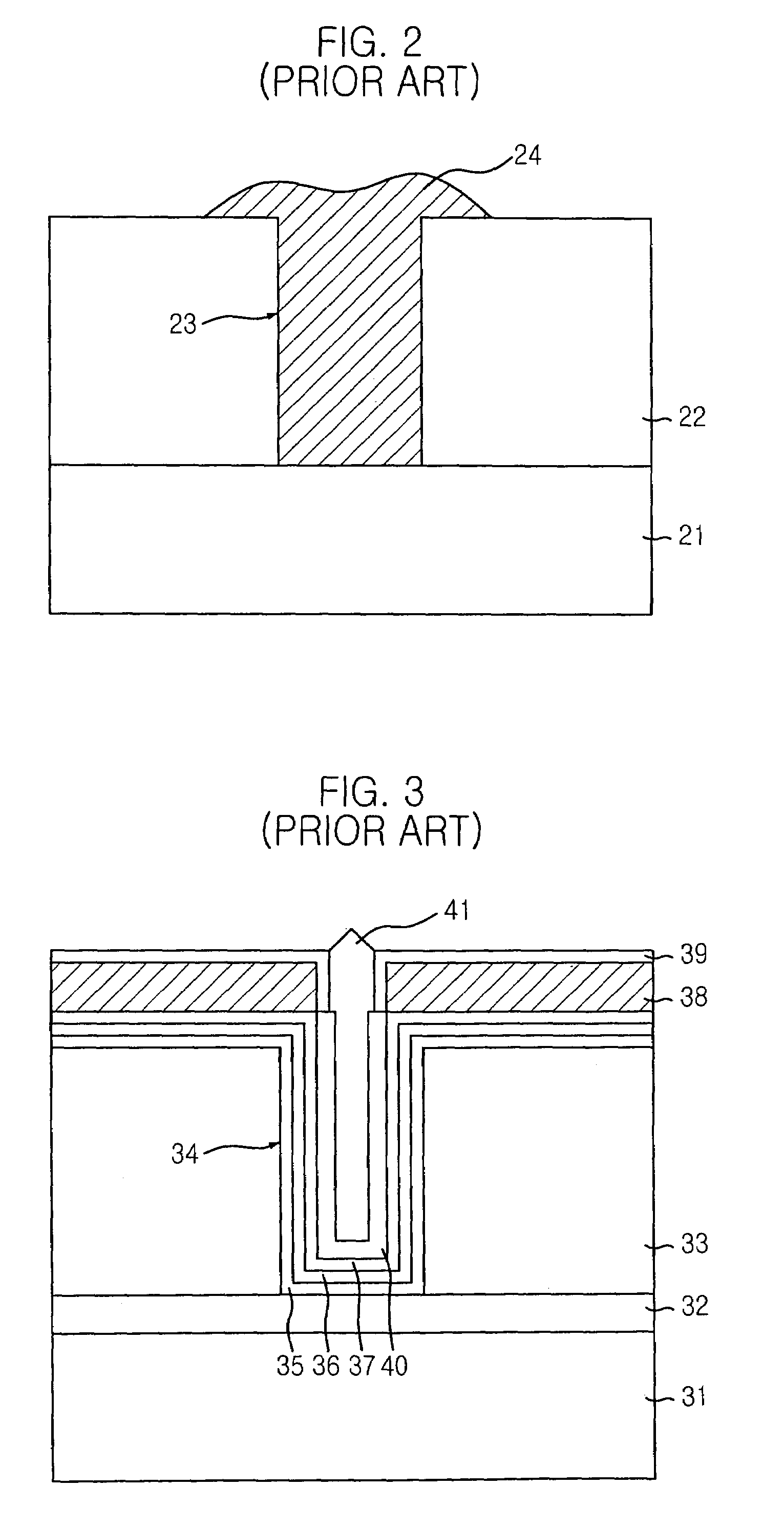

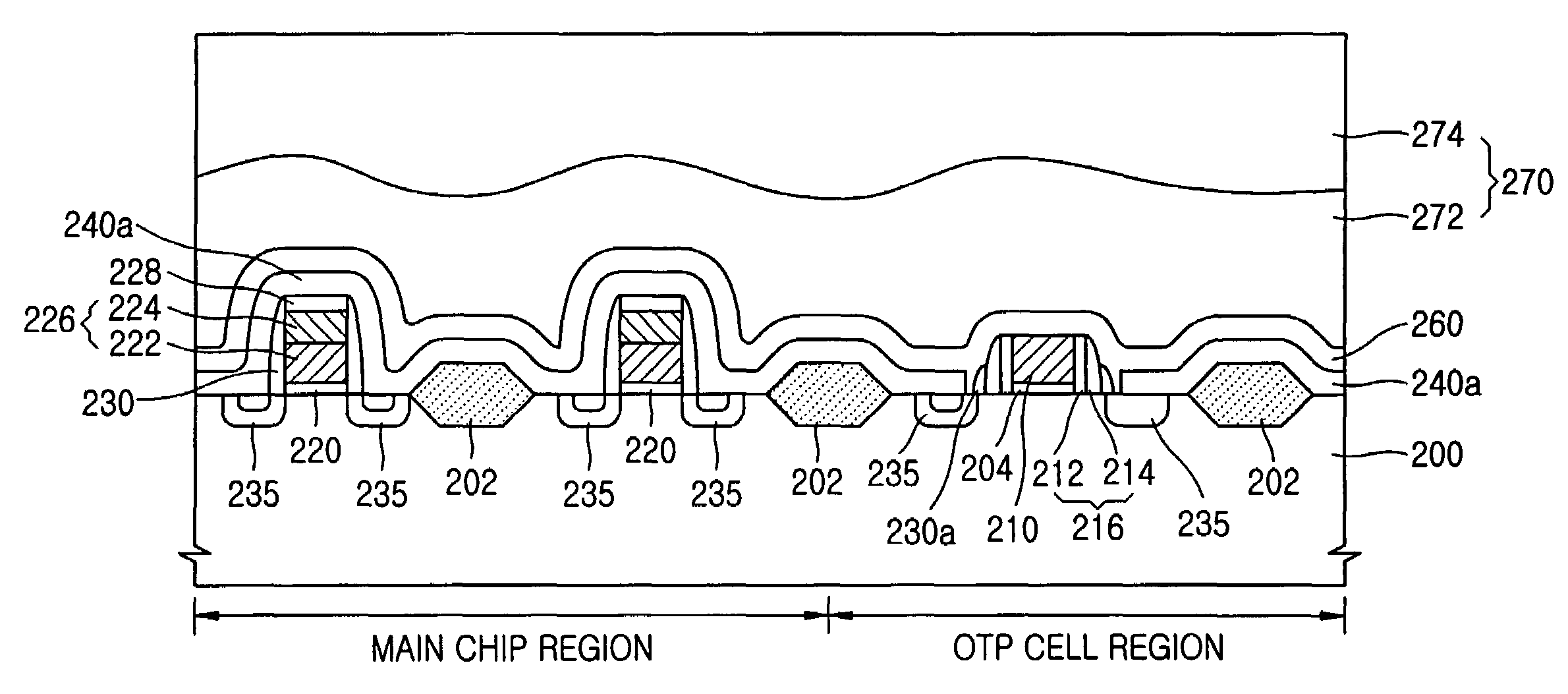

Erasable and programmable read only memory (EPROM) cell of an EPROM device and method of manufacturing a semiconductor device having the EPROM cell

InactiveUS7202522B2Improve data retentionPrevent leakageTransistorSolid-state devicesProgrammable read-only memoryCell region

Provided is an erasable and programmable read only memory (EPROM) device in which a plasma enhanced oxide (PEOX) film covers an upper surface of a floating gate in a single poly one time programmable (OTP) cell and a method of manufacturing a semiconductor device having the same. The semiconductor device comprises a substrate having an OTP cell region, on which a floating gate is formed for making an OTP cell transistor, and a main chip region, on which a gate of a transistor is formed. A PEOX film is formed on the OTP cell region and the main chip region. The PEOX film covers the floating gate in a close state and covers the gate by a predetermined distance. A silicon oxy nitride (SiON) film is interposed between the gate and the PEOX film in the main chip region.

Owner:SAMSUNG ELECTRONICS CO LTD

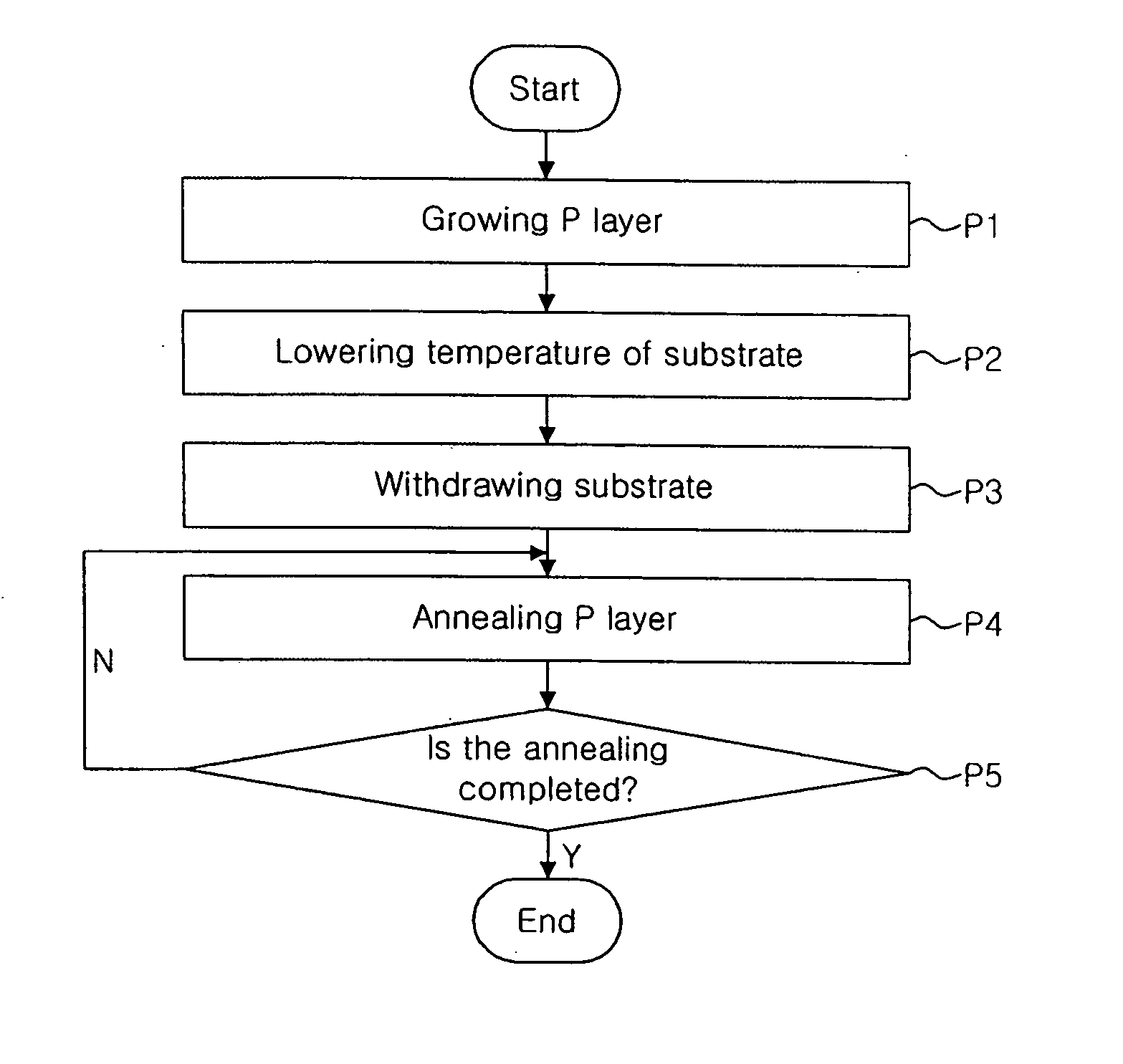

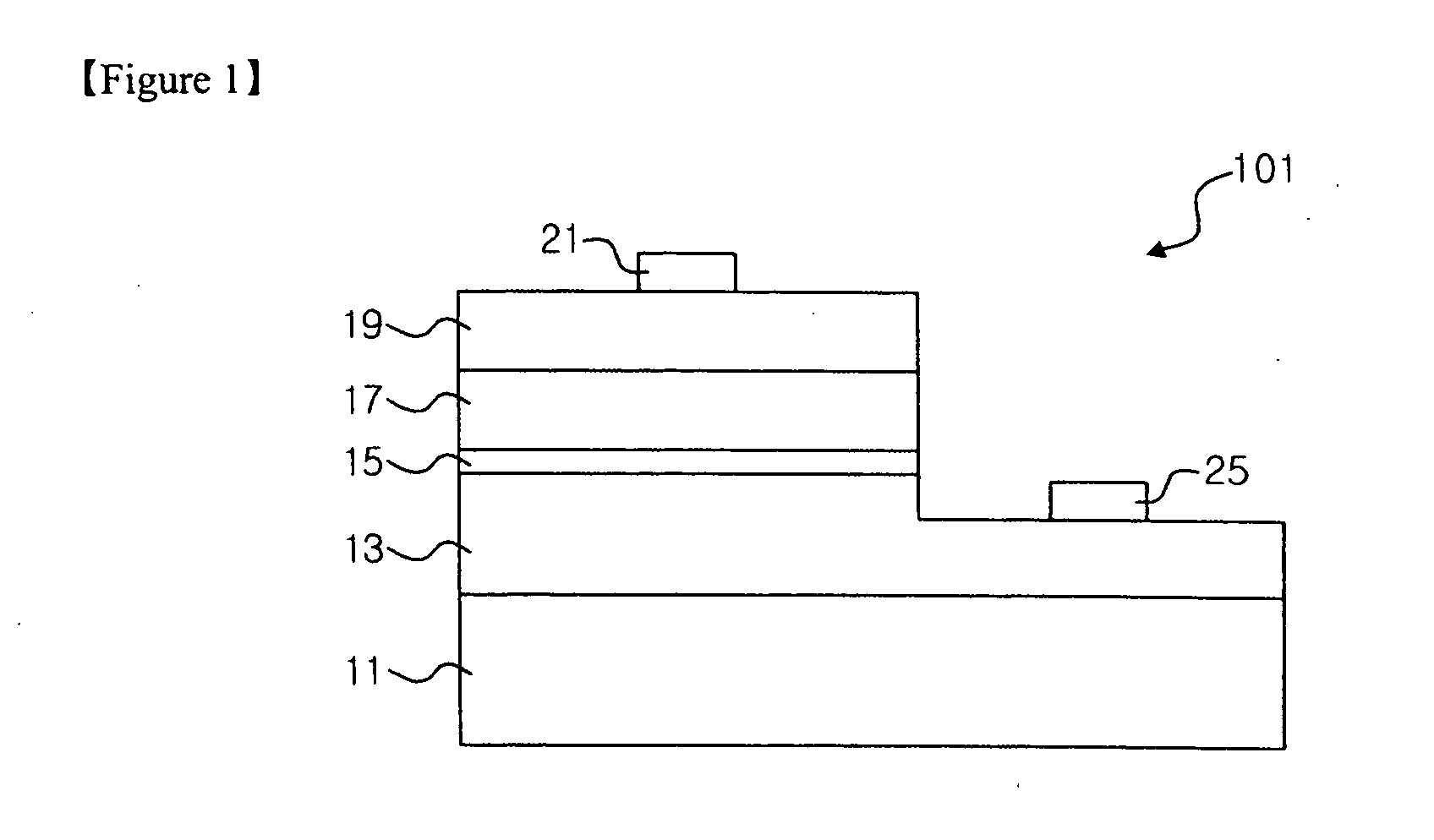

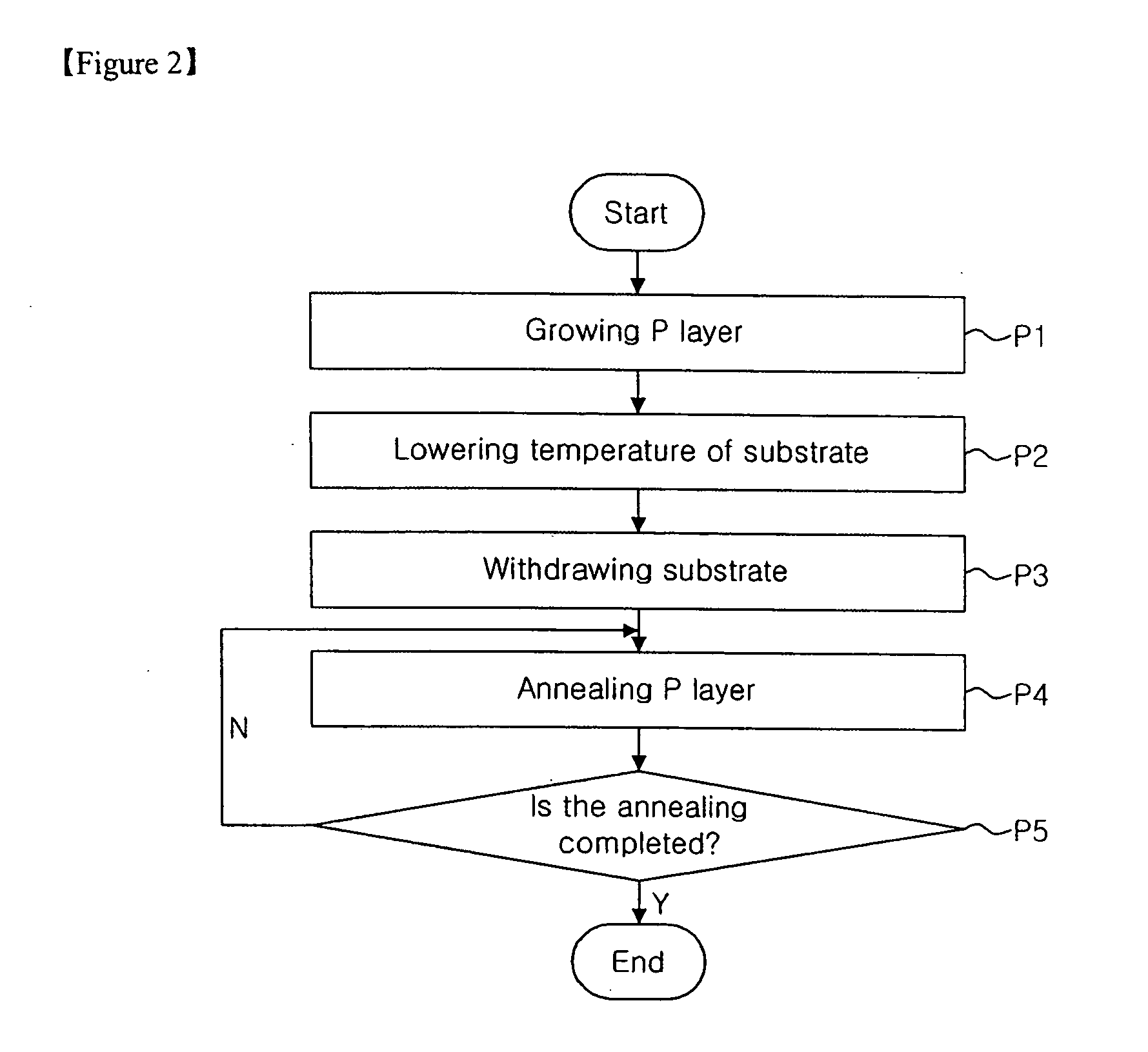

(Al, Ga, In) N-based compound semiconductor and method of fabricating the same

InactiveUS20070074651A1Improved ohmic contact characteristicsSimple and convenient fabricationPolycrystalline material growthFrom chemically reactive gasesHydrogenOhmic contact

Disclosed are a (Al, Ga, In) N-based compound semiconductor device and a method of fabricating the same. The (Al, Ga, In) N-based compound semiconductor device of the present invention comprises a substrate; a (Al, Ga, In) N-based compound semiconductor layer grown on the substrate; and an electrode formed of at least one material or an alloy thereof selected from the group consisting of Pt, Pd and Au on the (Al, Ga, In) N-based compound semiconductor layer. Further, the method of fabricating the (Al, Ga, In) N-based compound semiconductor device comprises the steps of growing a P layer including P type impurities in a growth chamber; discharging hydrogen and a hydrogen source gas in the growth chamber; lowering the temperature of the (Al, Ga, In) N-based compound semiconductor with the P layer formed thereon to such an extent that it can be withdrawn to the outside from the growth chamber; withdrawing the (Al, Ga, In) N-based compound semiconductor from the growth chamber; and forming an electrode of at least one material or an alloy thereof selected from the group consisting of Pt, Pd and Au on the P layer. According to the present invention, it is possible to sufficiently secure P type conductivity and obtain good ohmic contact characteristics without performing an annealing process. And, no ftrther annealing is necessary when Pt, Pd, Au electrode are used.

Owner:SEOUL OPTO DEVICE CO LTD

Electronic device having antennas

ActiveUS20210337054A1Interference minimizationImprove performancePower managementSimultaneous aerial operationsDisplay deviceEngineering physics

An electronic device according to an implementation may include a flexible display having a first region coupled to a front surface of a first frame, a second region coupled to a third frame, and a third region located between the first region and the second region, and an antenna implemented as one of a plurality of metal rims, and connected to a first feeding unit and a second feeding unit to radiate signals through different bands. The first frame may be configured as a metal frame formed on a side surface of the electronic device and having a plurality of metal rims.

Owner:LG ELECTRONICS INC

Transistor and method for manufacturing the same

InactiveUS20050263819A1Increase concentrationAvoid ion diffusionTransistorSolid-state devicesEngineeringSemiconductor

A transistor including a semiconductor substrate defined with an active region and a device isolation region, a gate formed on the semiconductor substrate, an insulating spacers formed on respective side walls of the gate, and source / drain junctions formed in the semiconductor substrate at opposite sides of the gate, the source / drain junctions having asymmetrical junction structures, respectively, wherein the gate has a lower portion arranged on the active region of the substrate, the lower gate portion having a stepped profile having a lower surface, an upper surface and a vertically-extending side surface. The invention also provides a method for manufacturing this transistor. In accordance with this transistor structure, an increase in the dopant concentration of a storage node is prevented. Accordingly, a reduction in the amount of leakage current is achieved, so that an improvement in the refresh characteristics of the transistor is achieved.

Owner:SK HYNIX INC

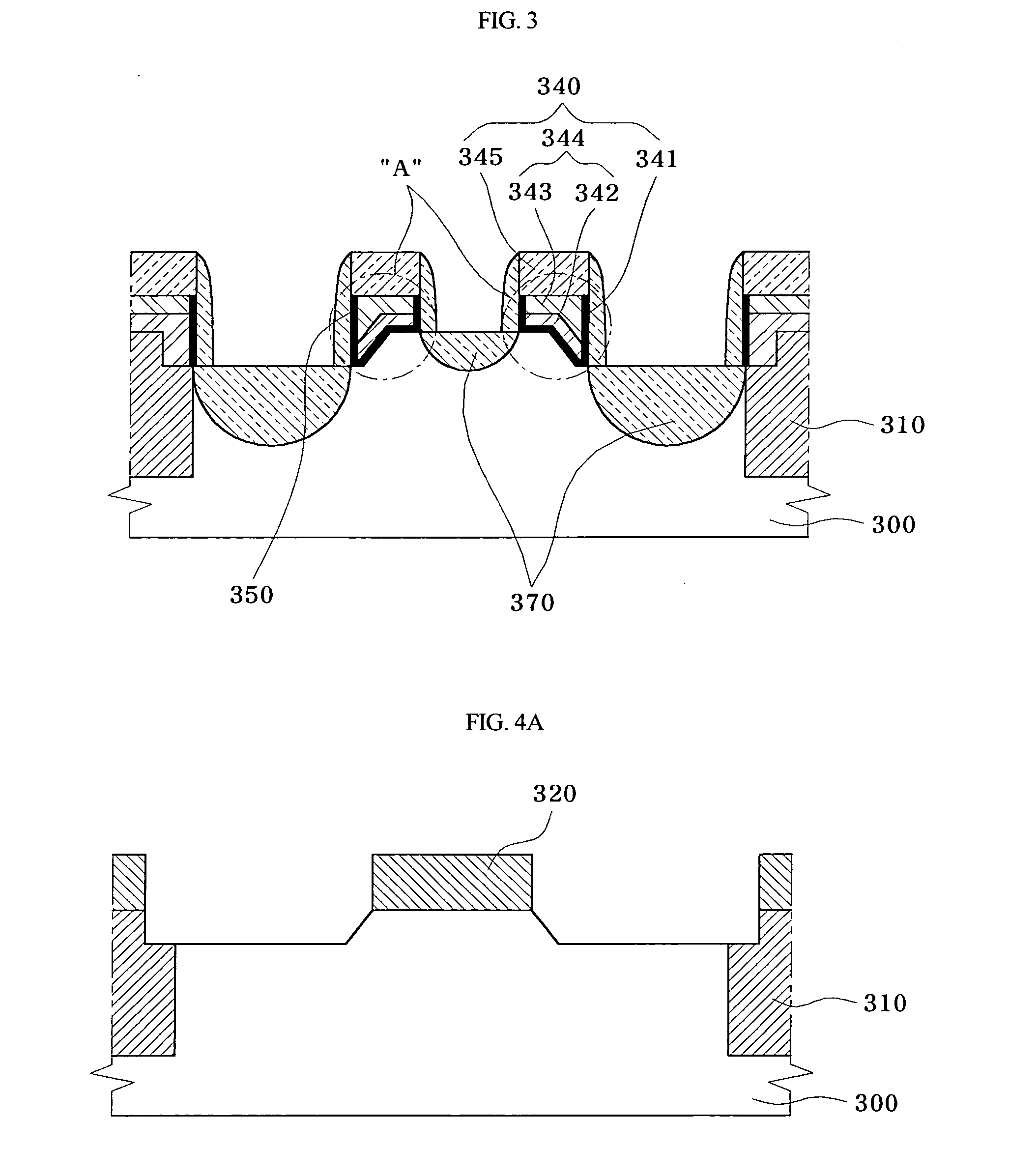

Nonvolatile memory device and method for fabricating the same

InactiveUS7803691B2Increase the effective channel lengthSecure characteristicTransistorSolid-state devicesInsulation layerDielectric layer

A nonvolatile memory device includes a control gate formed along a first direction over a substrate, an active region formed over the substrate, the active region being defined along a second direction crossing the control gate and including a fin type protruding portion having rounded top corners at a region where the control gate and the active region overlap, a floating gate formed over a surface of the protruding portion of the active region below the control gate and formed to a substantially uniform thickness along the surface profile of the protruding portion of the active region, a tunneling insulation layer formed between the floating gate and the active region, and a dielectric layer formed between the floating gate and the control gate.

Owner:SK HYNIX INC