Circuit of gate drive on array, shift register and display screen

A gate integrated drive and circuit technology, used in static memory, digital memory information, instruments, etc., to ensure reliability and stability, and ensure stability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

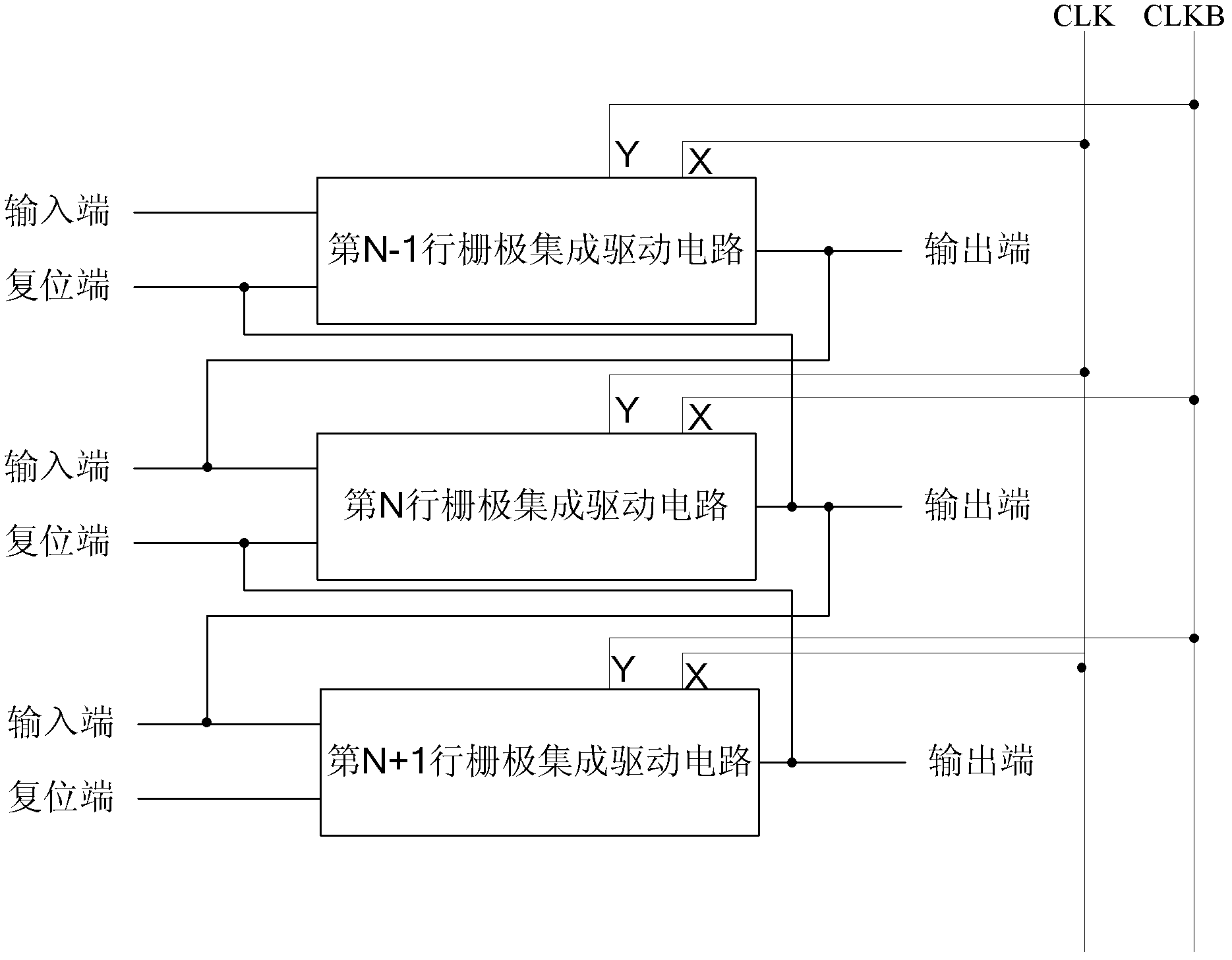

[0026] The embodiments of the present invention will be described in further detail below with reference to the accompanying drawings.

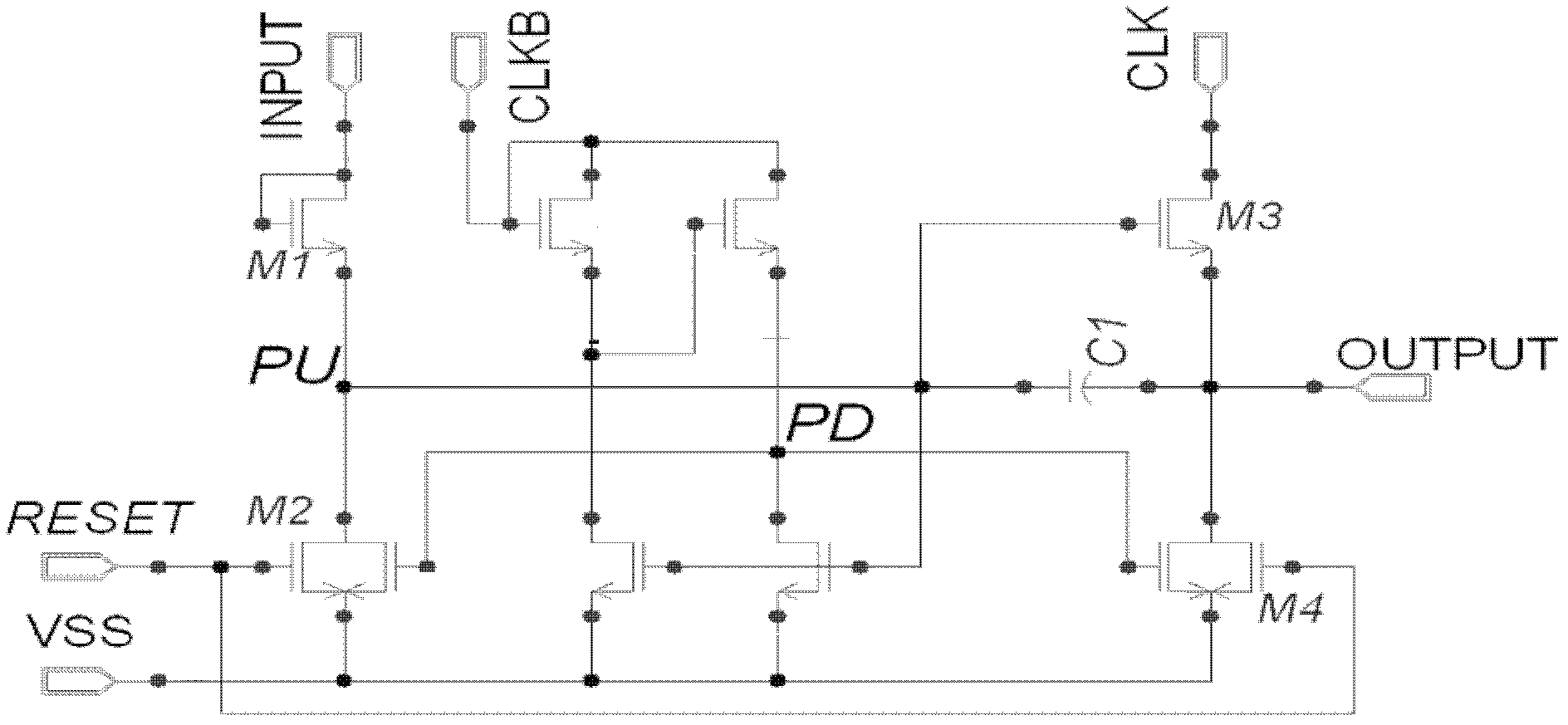

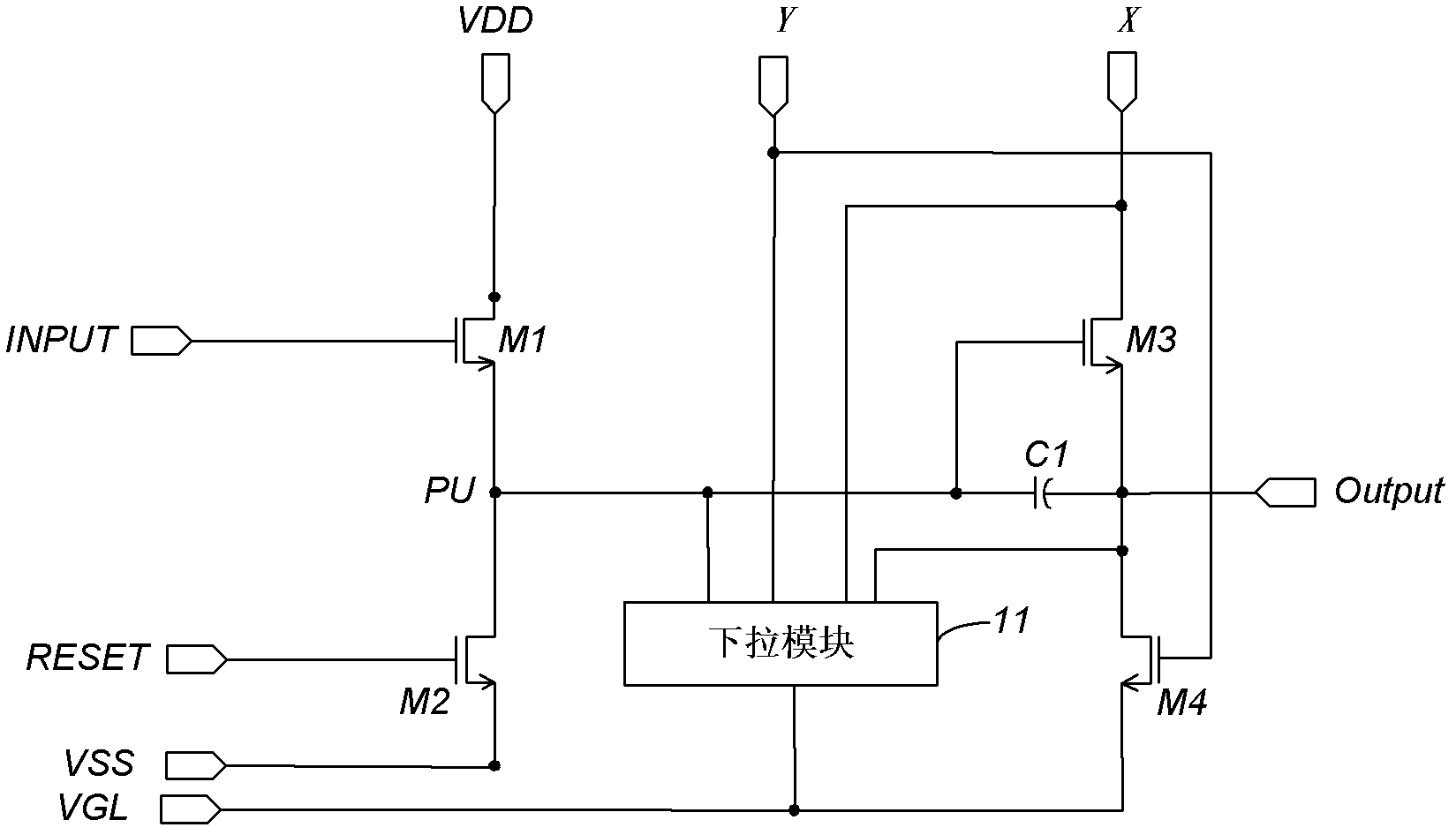

[0027] Embodiments of the present invention provide a multi-row gate integrated driving circuit, such as figure 2 As shown, the gate integrated drive circuit of this row includes:

[0028] the first thin film field effect transistor TFT M1, the gate of which is connected to the input terminal INPUT of the gate integrated driving circuit of the row, the drain is connected to the power supply voltage VDD, and the source is connected to the first node PU serving as a pull-up node;

[0029] The second TFT M2, the gate of which is connected to the reset terminal RESET of the gate integrated driving circuit of the row, the source is connected to the common connection voltage VSS, and the drain is connected to the first node PU;

[0030] The third TFT M3, the gate of which is connected to the first node PU, the drain is connected to the first cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More