Patents

Literature

480results about "Arbitary function generators" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

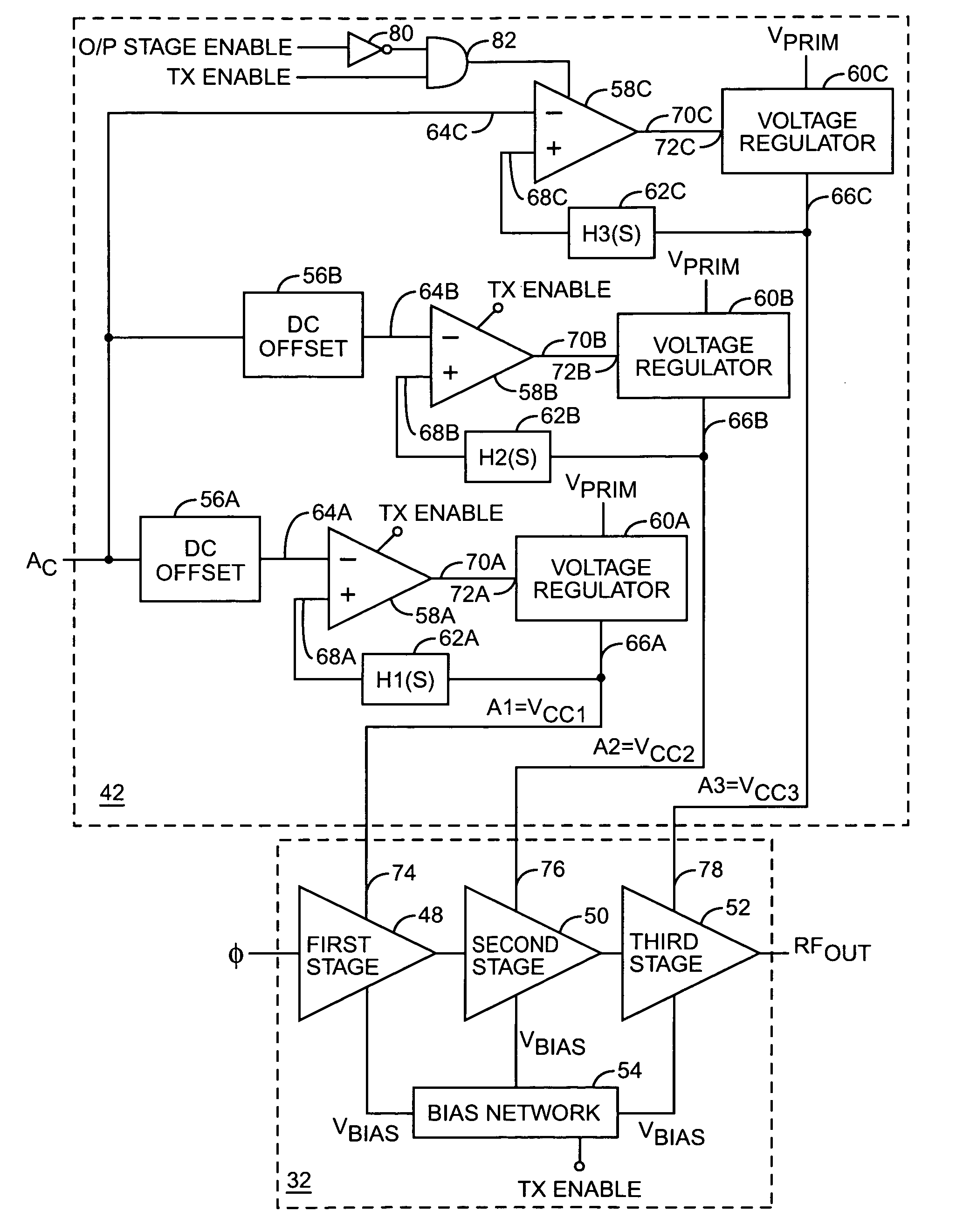

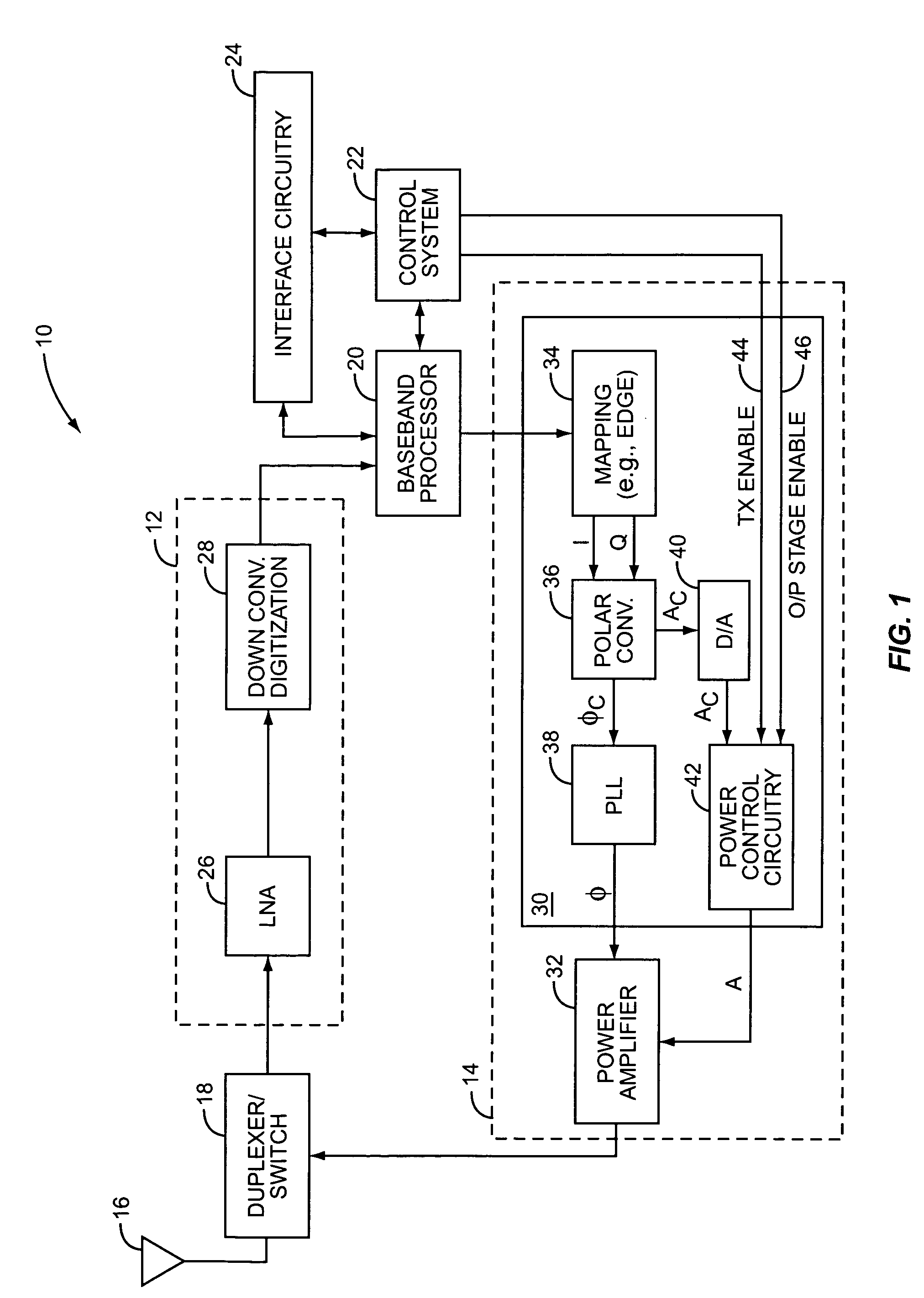

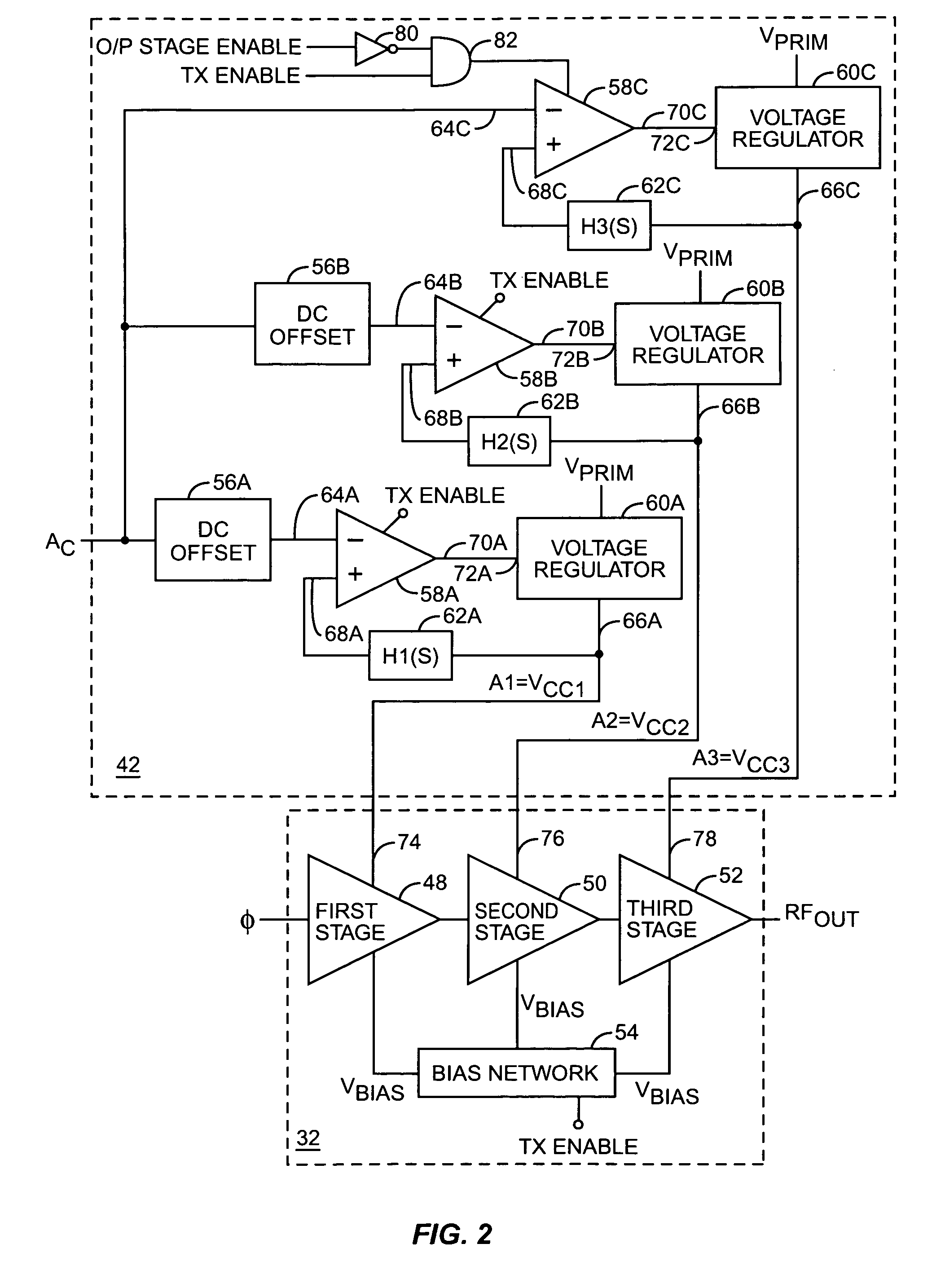

Tailored collector voltage to minimize variation in AM to PM distortion in a power amplifier

ActiveUS7109791B1Reduce variationAmplifier modifications to reduce non-linear distortionPulse automatic controlAudio power amplifierControl signal

A system is provided for substantially reducing variation in AM to PM distortion of a power amplifier caused by variations in RF drive power and temperature. The system includes power control circuitry and power amplifier circuitry. The power amplifier circuitry includes an input amplifier stage and at least one additional amplifier stage coupled in series with the input amplifier stage. The power control circuitry provides a first supply voltage to the input amplifier stage based on a control signal such that the first supply voltage has a predetermined DC offset with respect to the control signal. The first supply voltage is provided such that the predetermined DC offset substantially reduces variations in the AM to PM distortion of the power amplifier due to variations in radio frequency (RF) drive power.

Owner:QORVO US INC

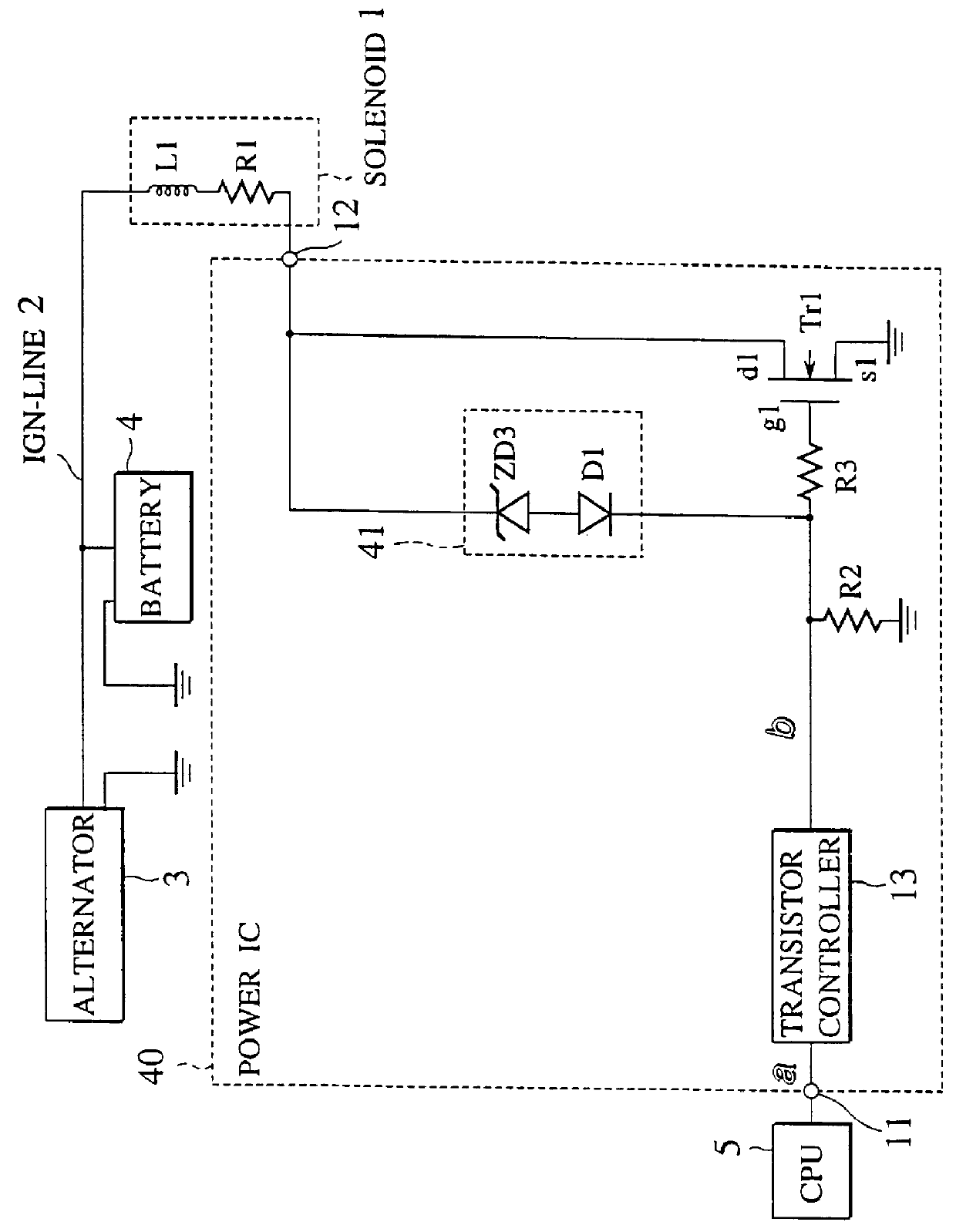

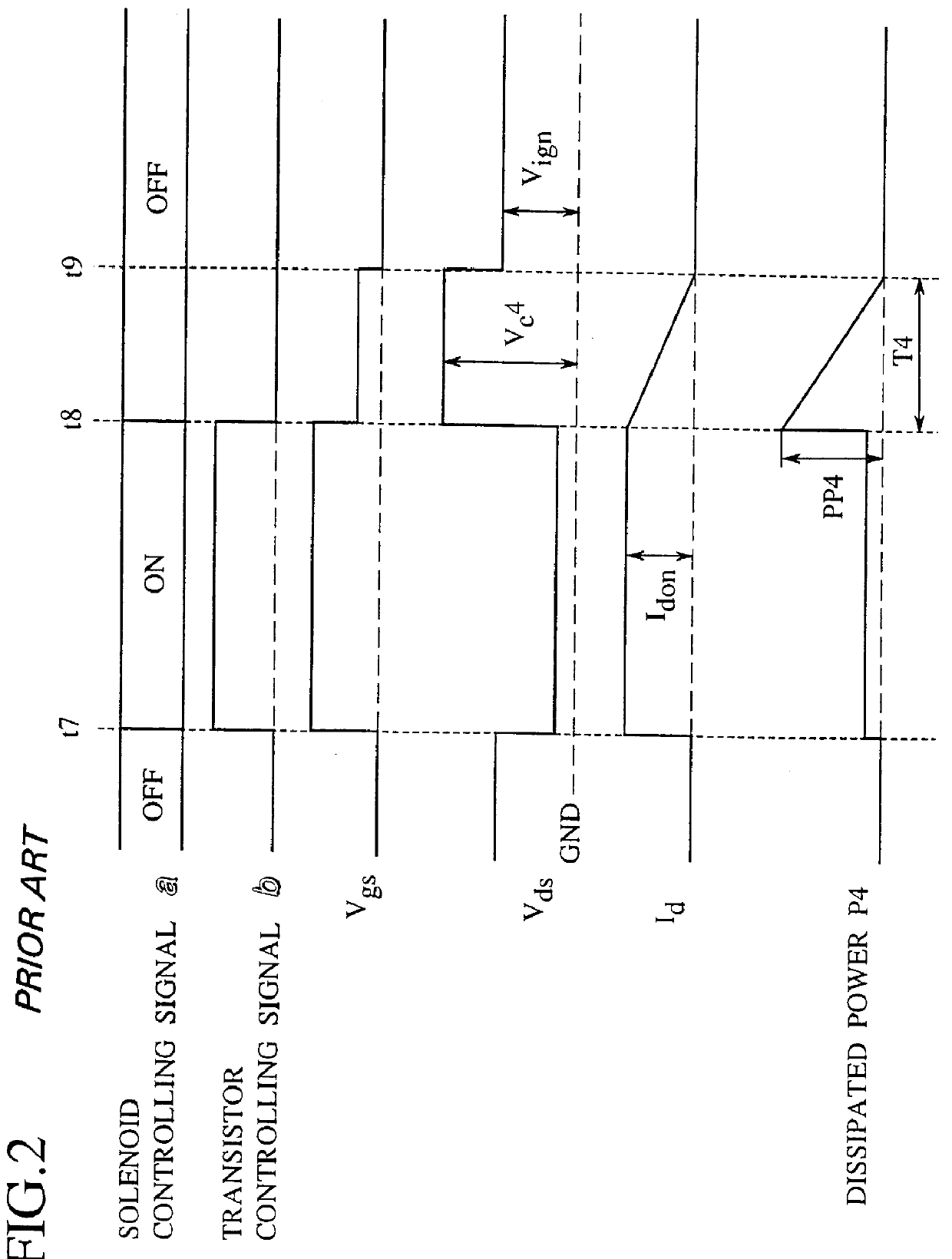

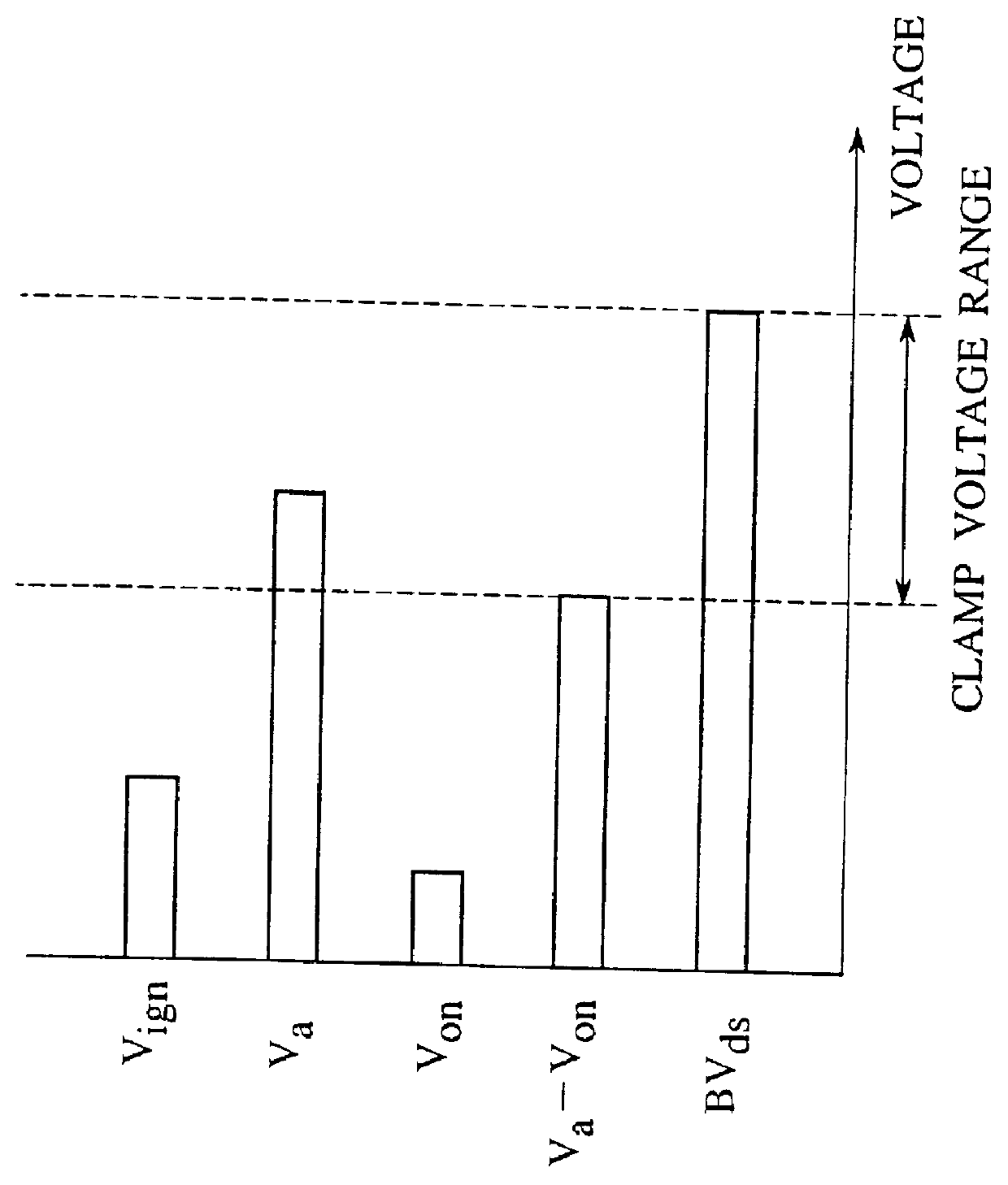

Integrated circuit having surge protection circuit

A trailing edge of a control signal of a transistor controller for controlling an output transistor is detected by an edge detector of a clamp controlling circuit. A surge voltage from a back electromotive voltage induced in an inductance L1 is absorbed from the output transistor, only for a given period immediately after the solenoid is turned off, by turning a switching transistor into an on-state by a timer to force a clamping circuit into conduction. At a normal operation, since the clamping circuit is cut off from an output terminal, the clamping voltage can be set in a manner to reduce to a normal voltage in an IGN-line. Therefore, a peak power value of a power loss caused by the surge voltage at the output transistor can be reduced, whereby generation of heat at the output transistor can be reduced. Therefore, the chip size of the power IC can be reduced.

Owner:NISSAN MOTOR CO LTD

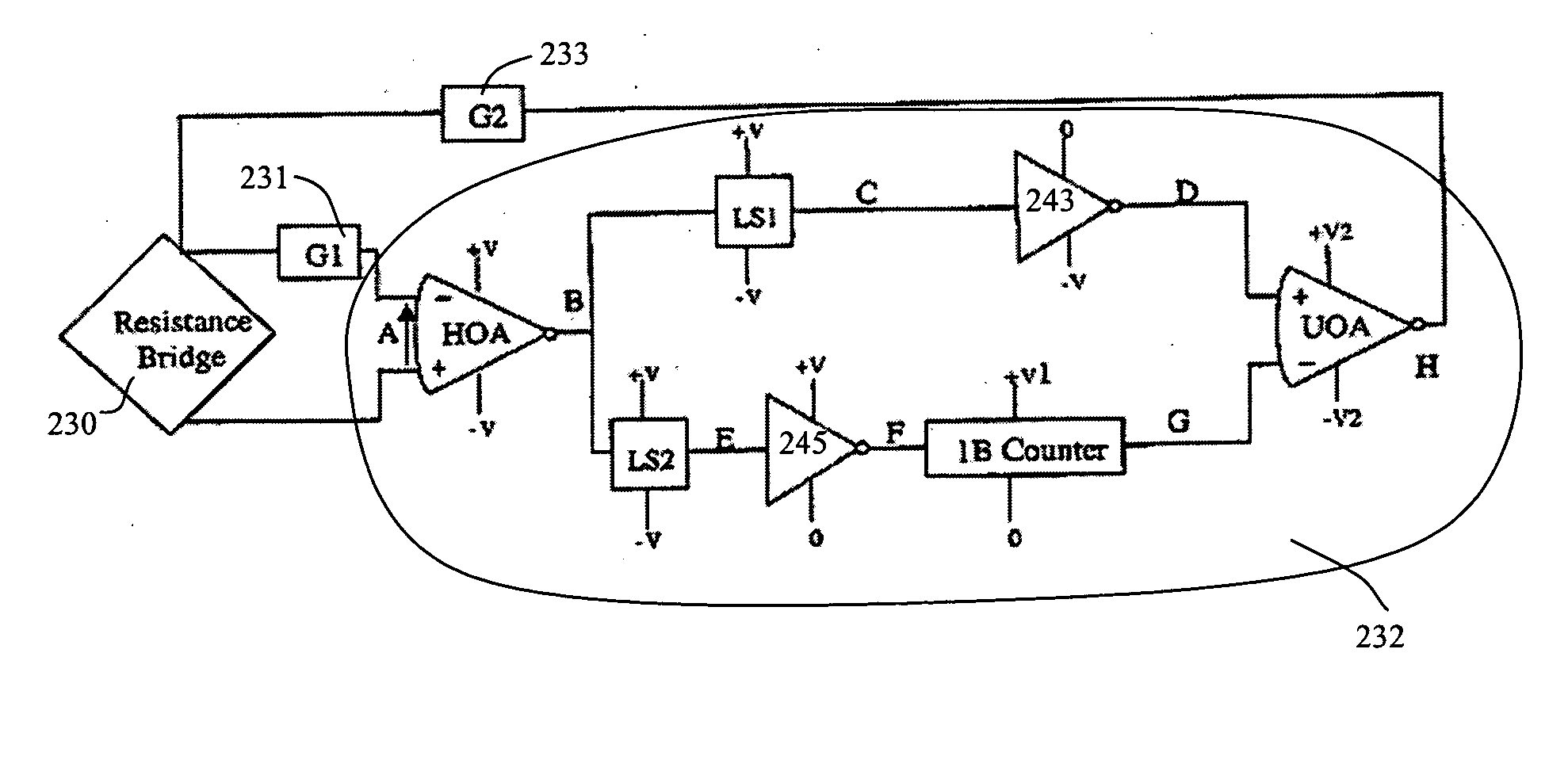

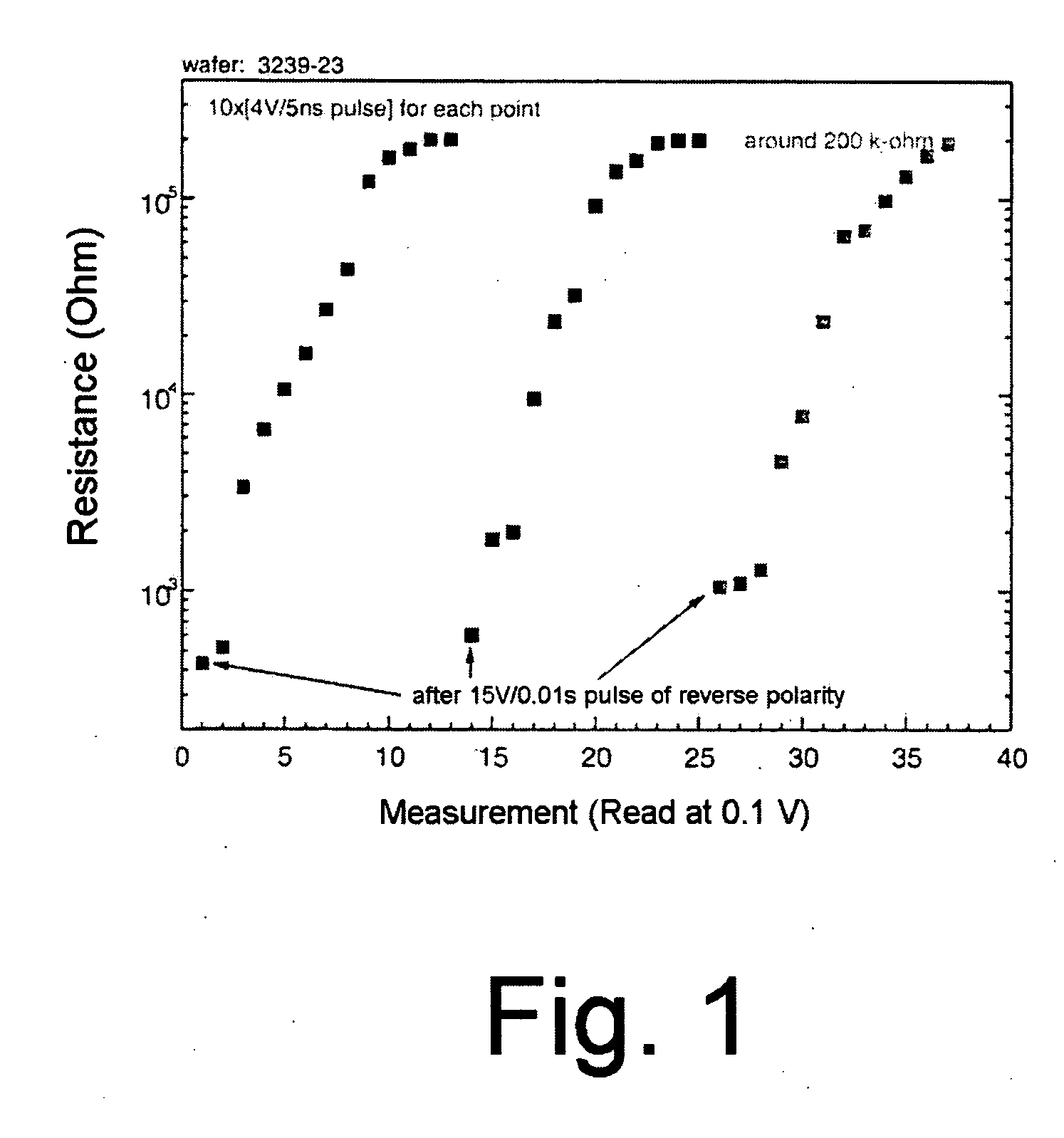

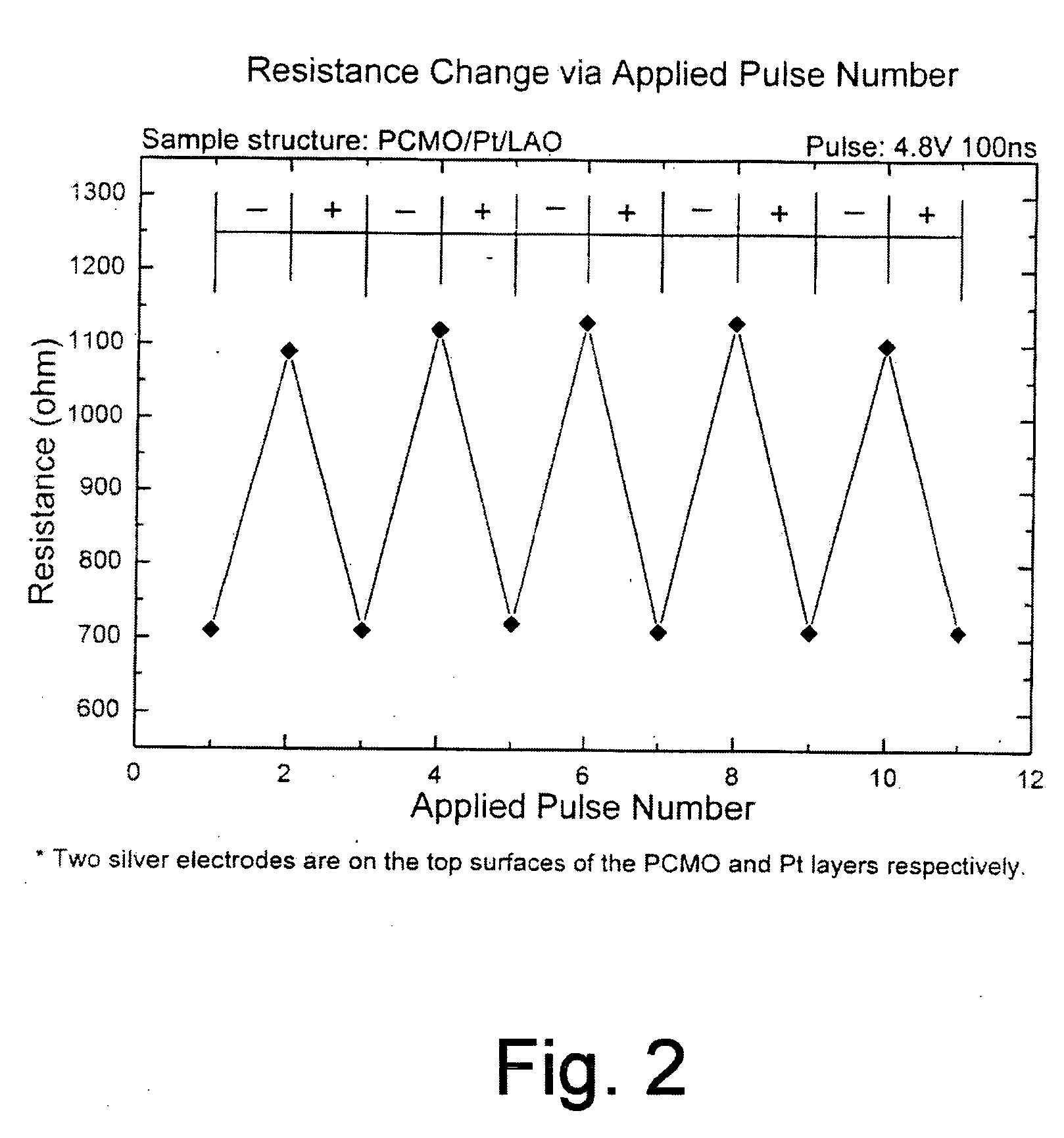

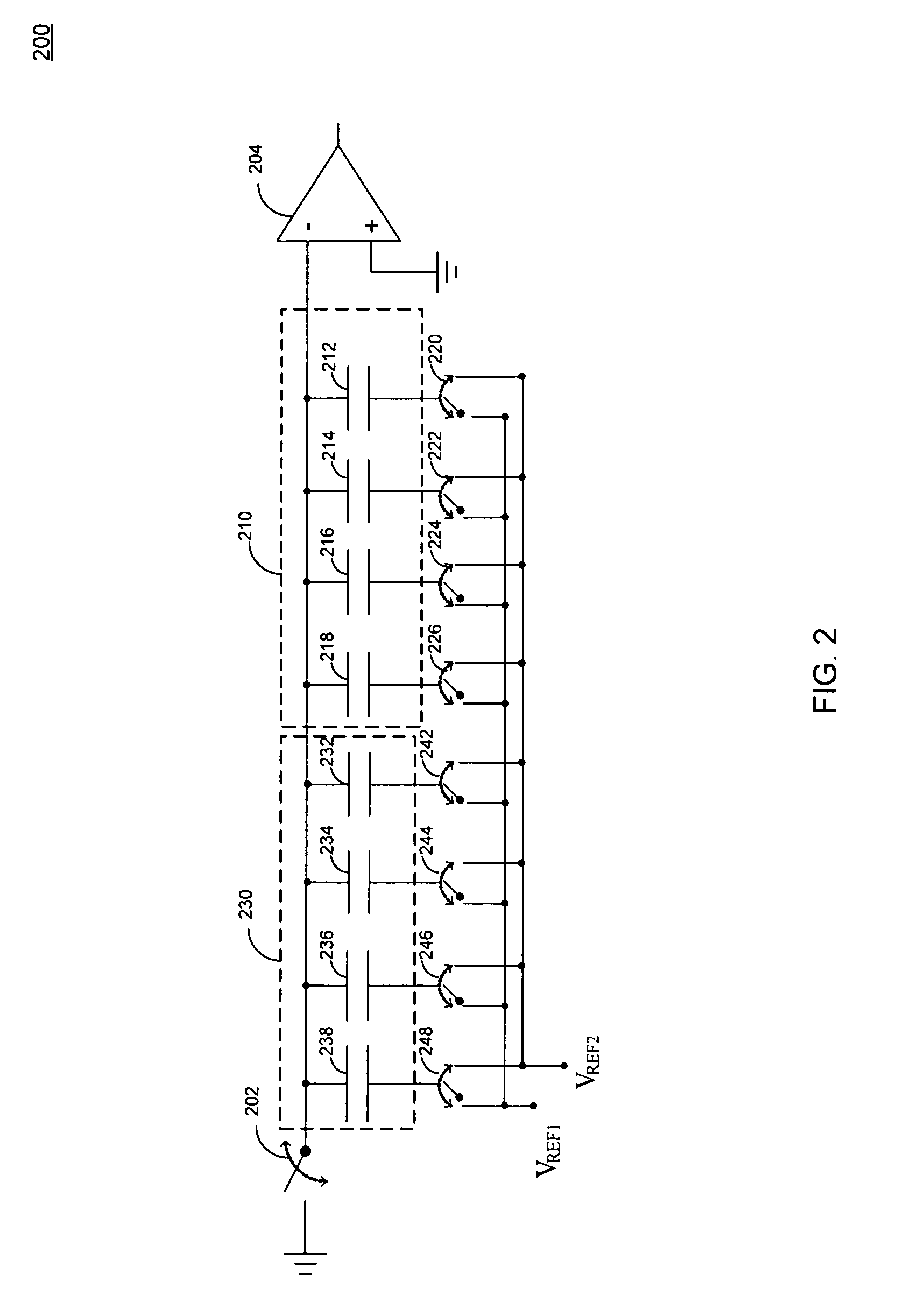

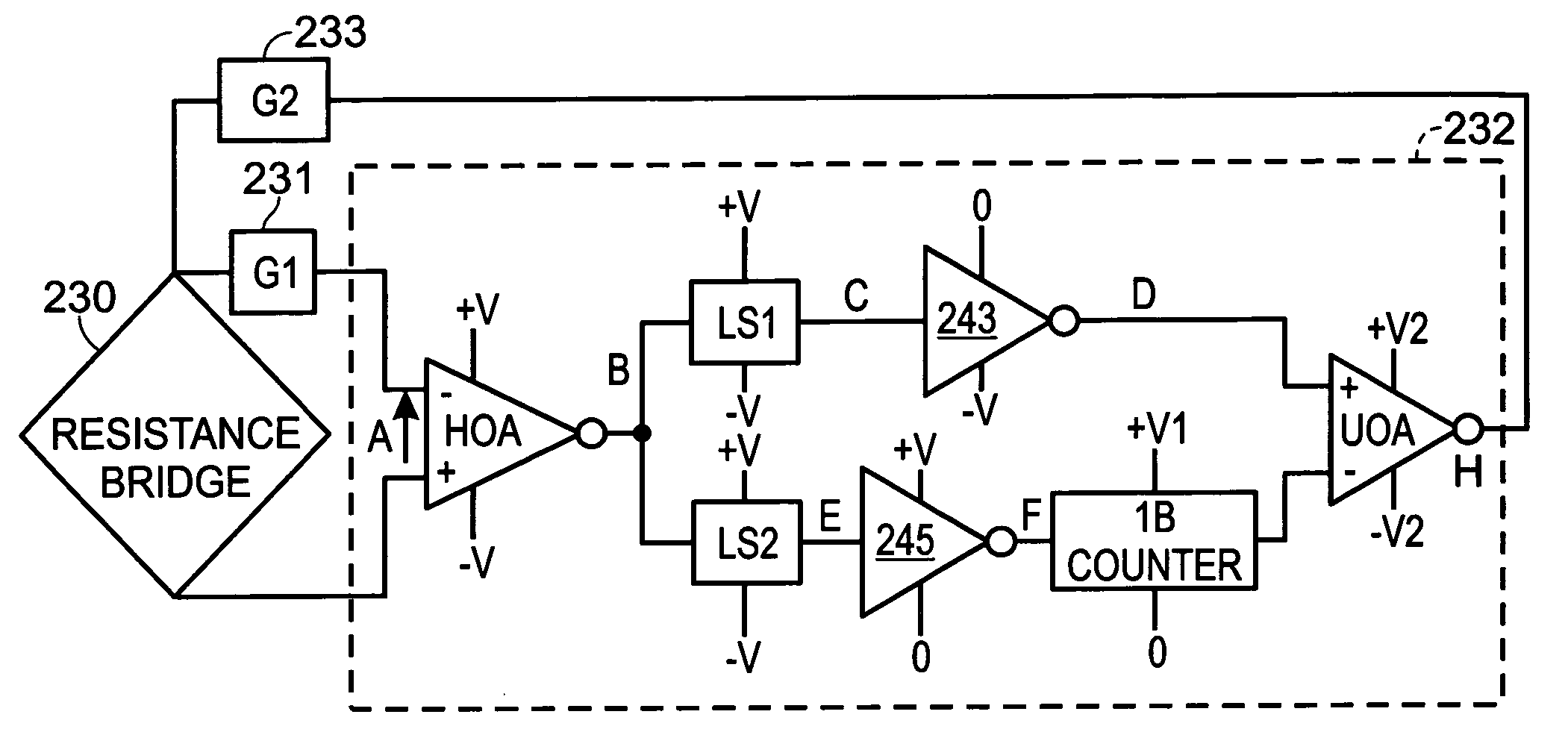

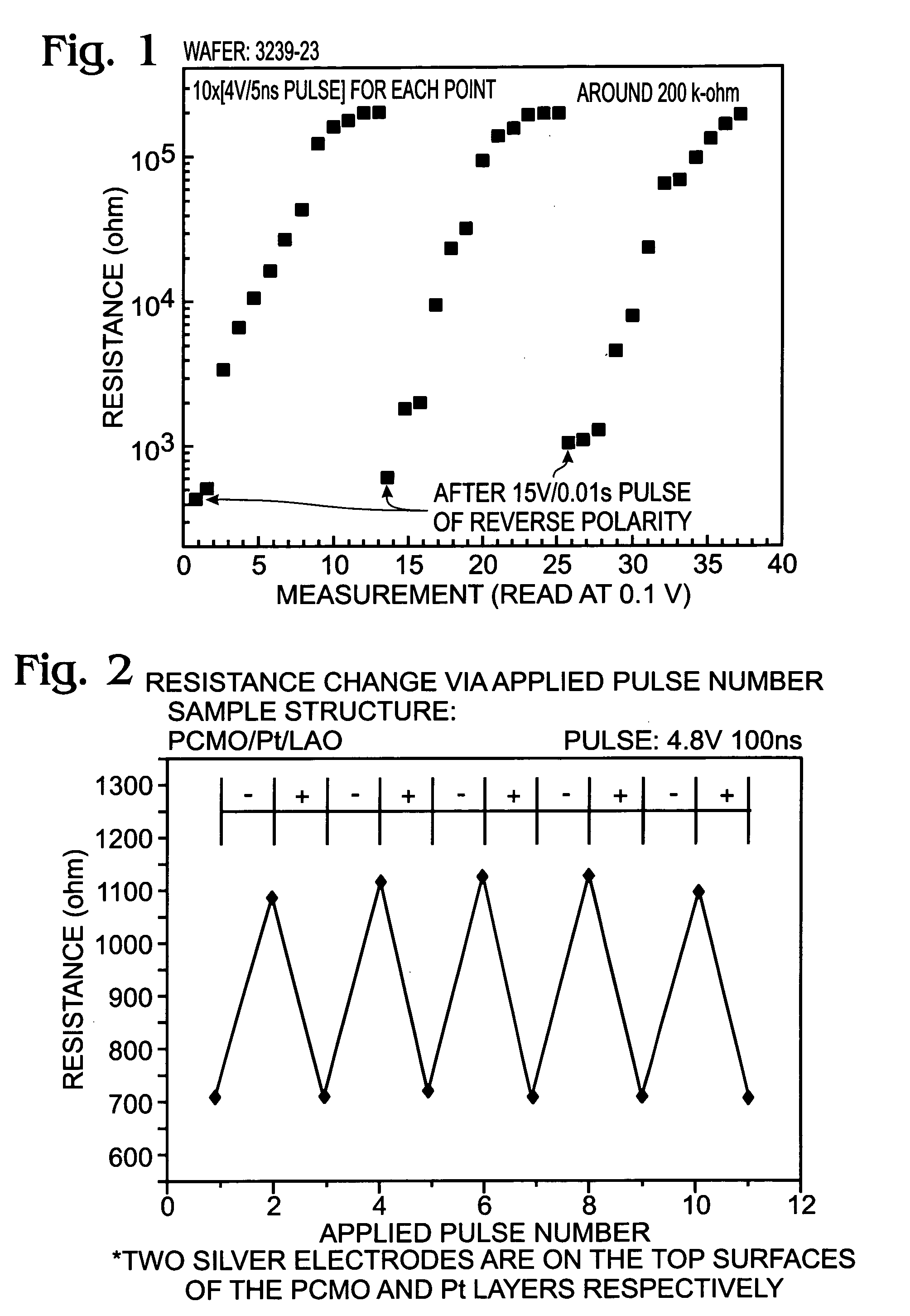

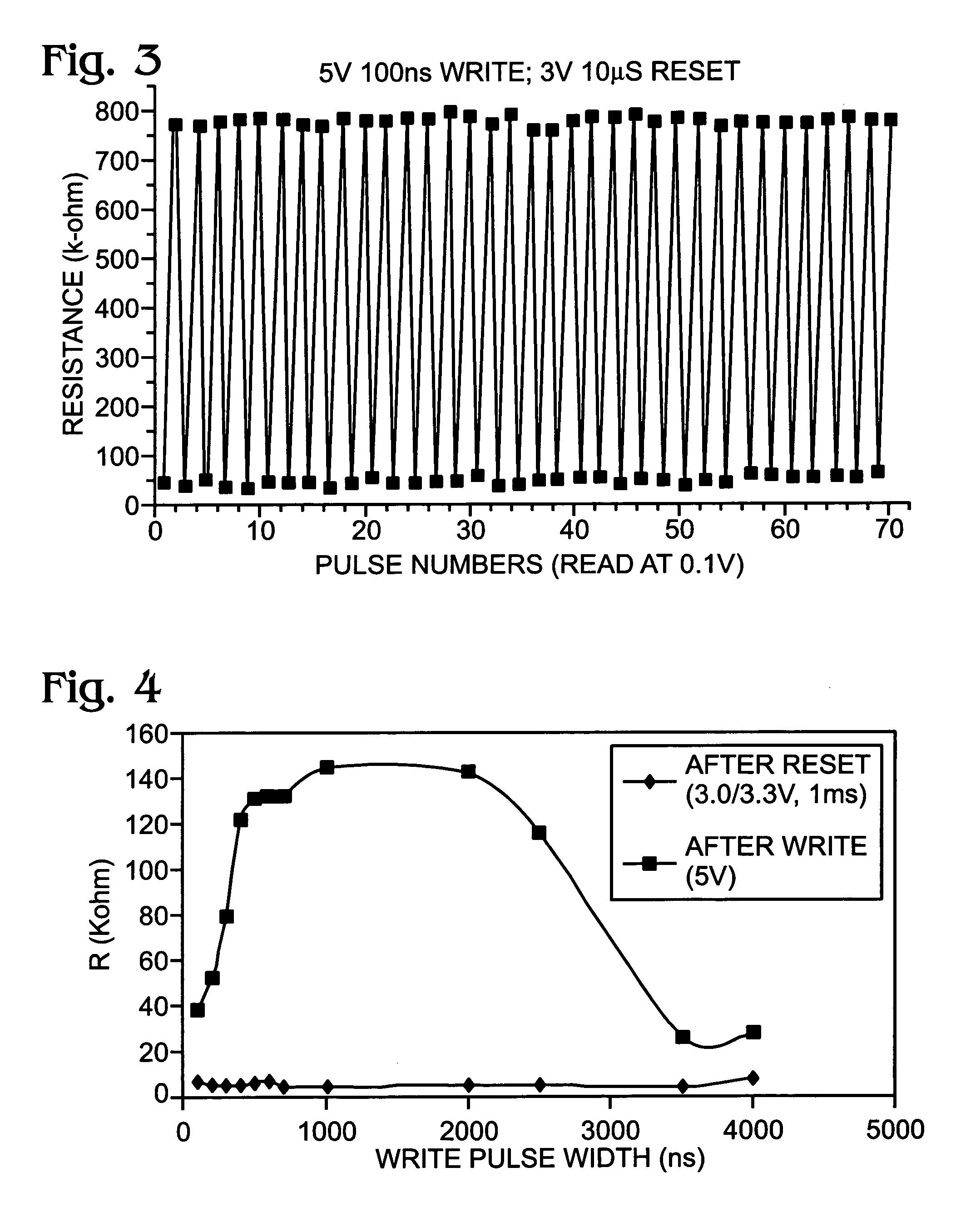

Mono-polarity switchable PCMO resistor trimmer

ActiveUS20060017488A1Improve the immunityPulse automatic controlSolid-state devicesElectrical resistance and conductanceAmorphous silicon

Using programmable resistance material for a matching resistor, a resistor trimming circuit is designed to reversibly trim a matching resistor to match a reference resistor. The programmable resistance materials such as metal-amorphous silicon metal materials, phase change materials or perovskite materials are typically used in resistive memory devices and have the ability to change the resistance reversibly and repeatable with applied electrical pulses. The present invention reversible resistor trimming circuit comprises a resistance bridge network of a matching resistor and a reference resistor to provide inputs to a comparator circuit which generates a comparing signal indicative of the resistance difference. This comparing signal can be used to control a feedback circuit to provide appropriate electrical pulses to the matching resistor to modify the resistance of the matching resistor to match that of the reference resistor.

Owner:XENOGENIC DEV LLC

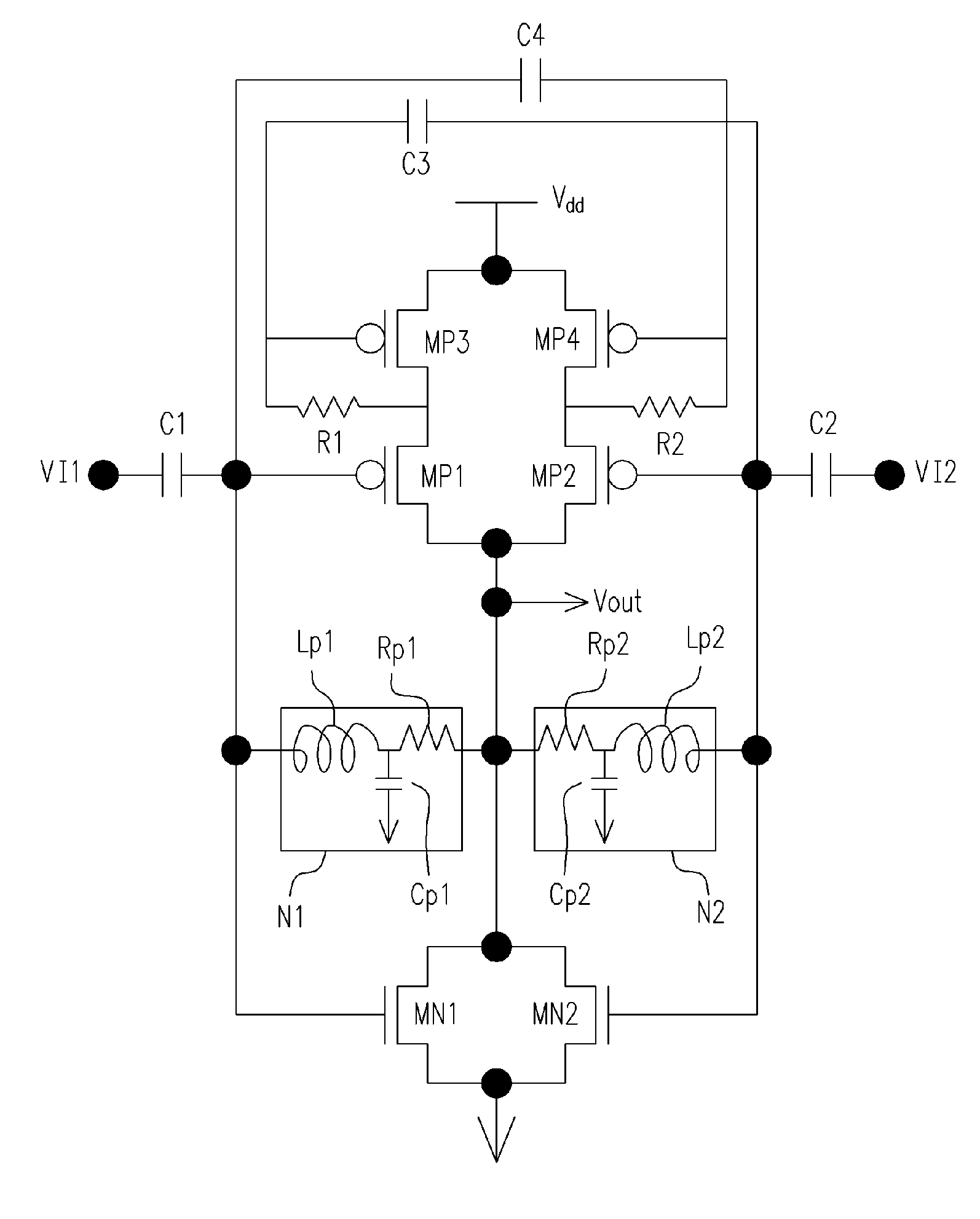

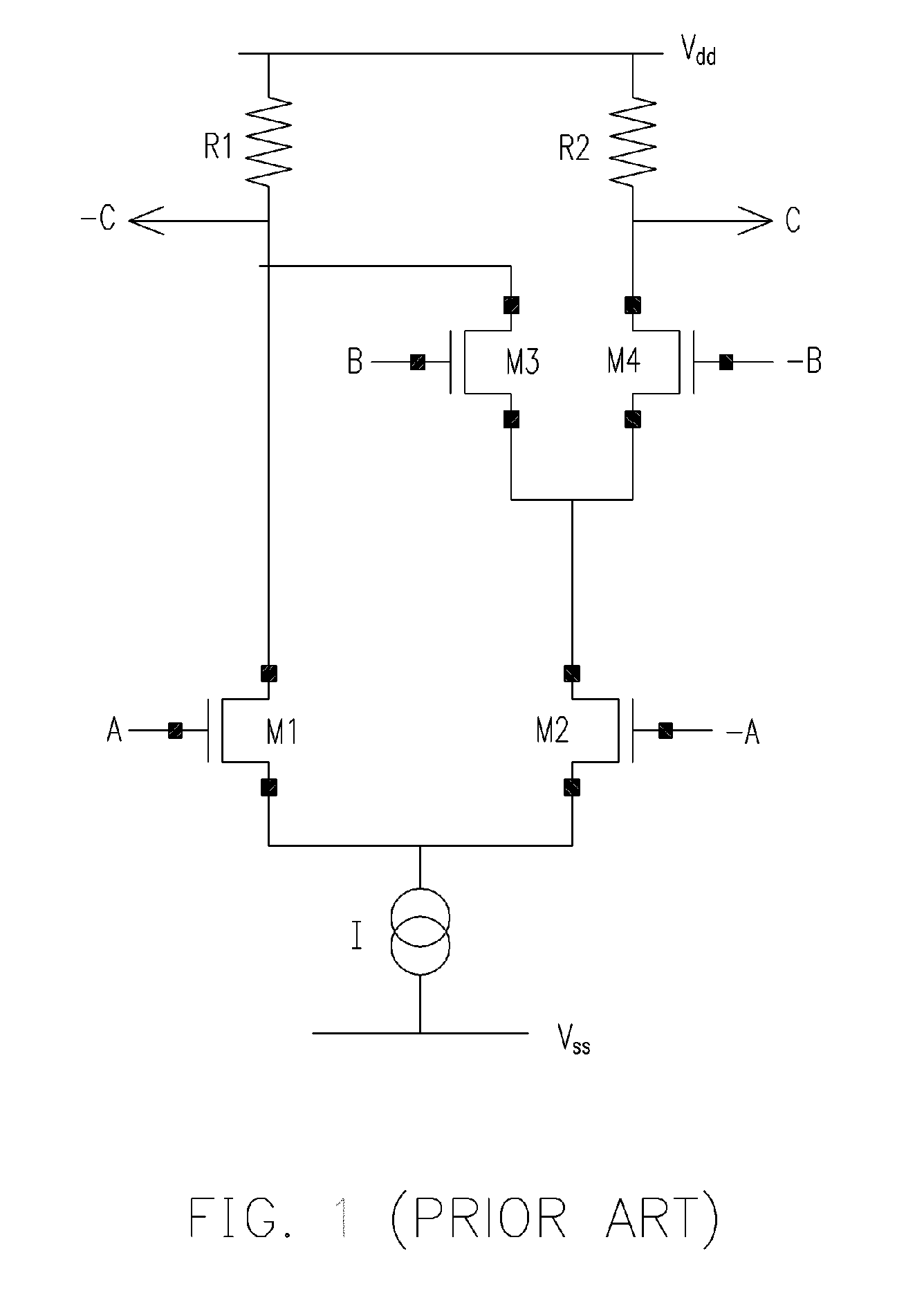

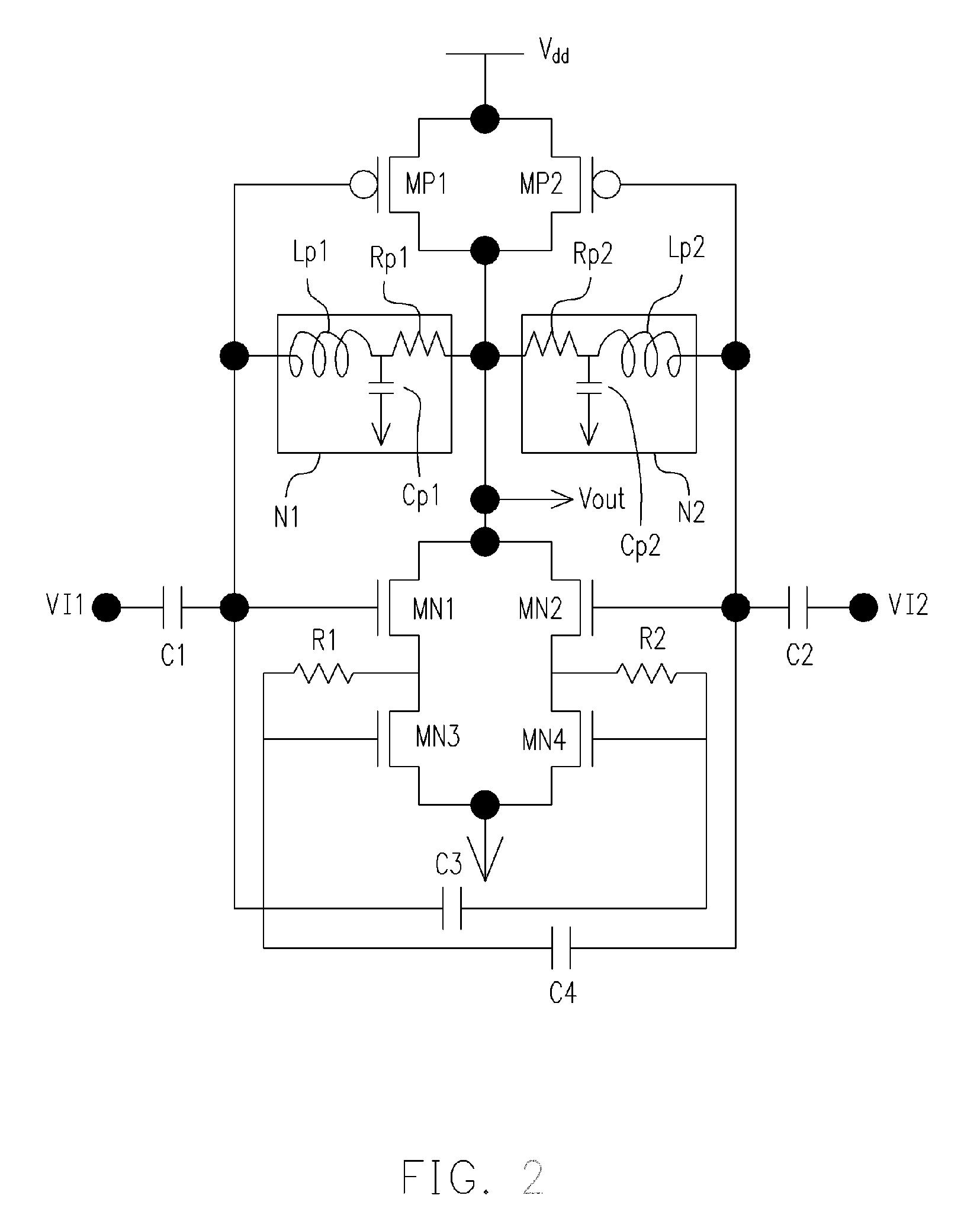

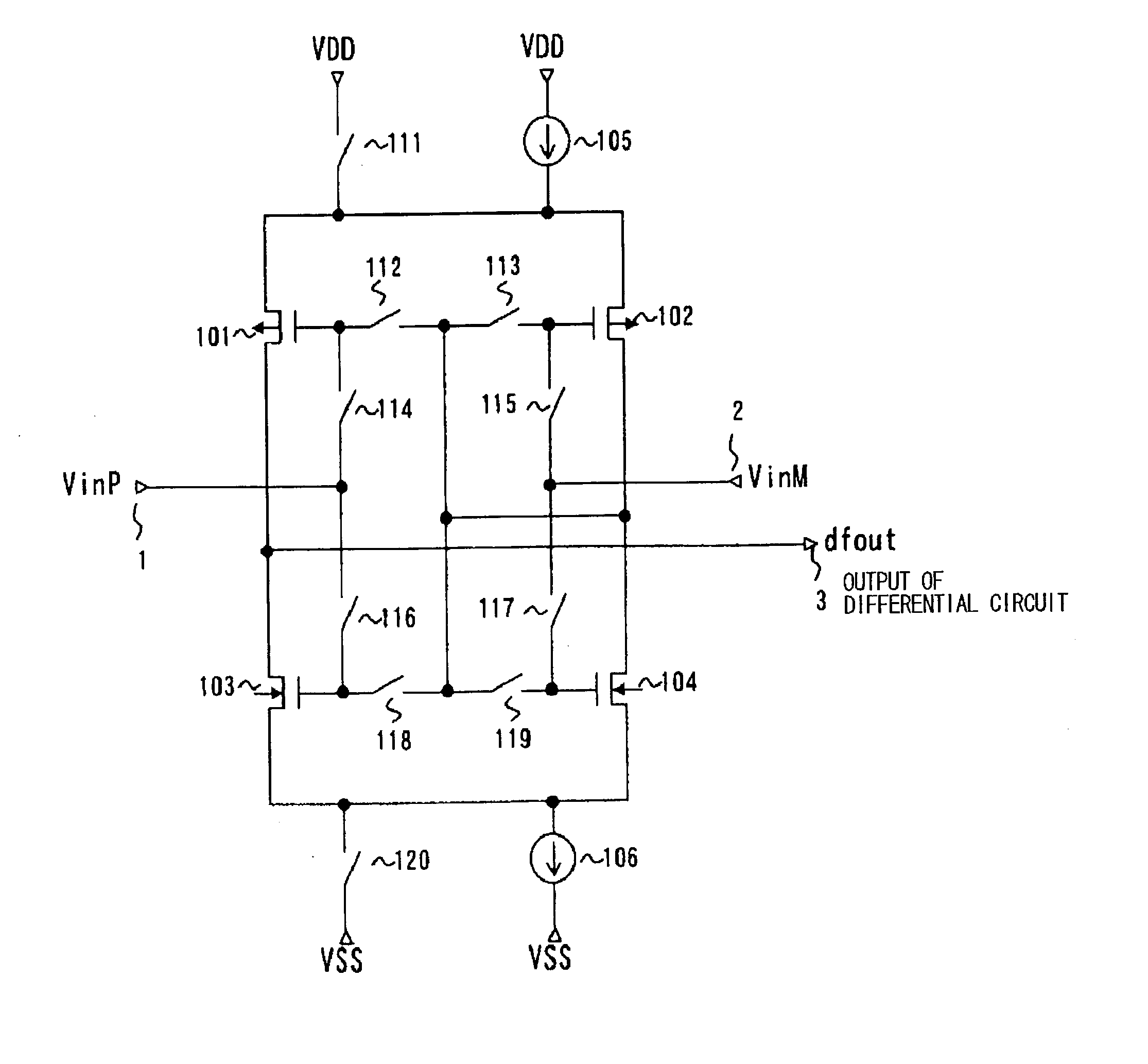

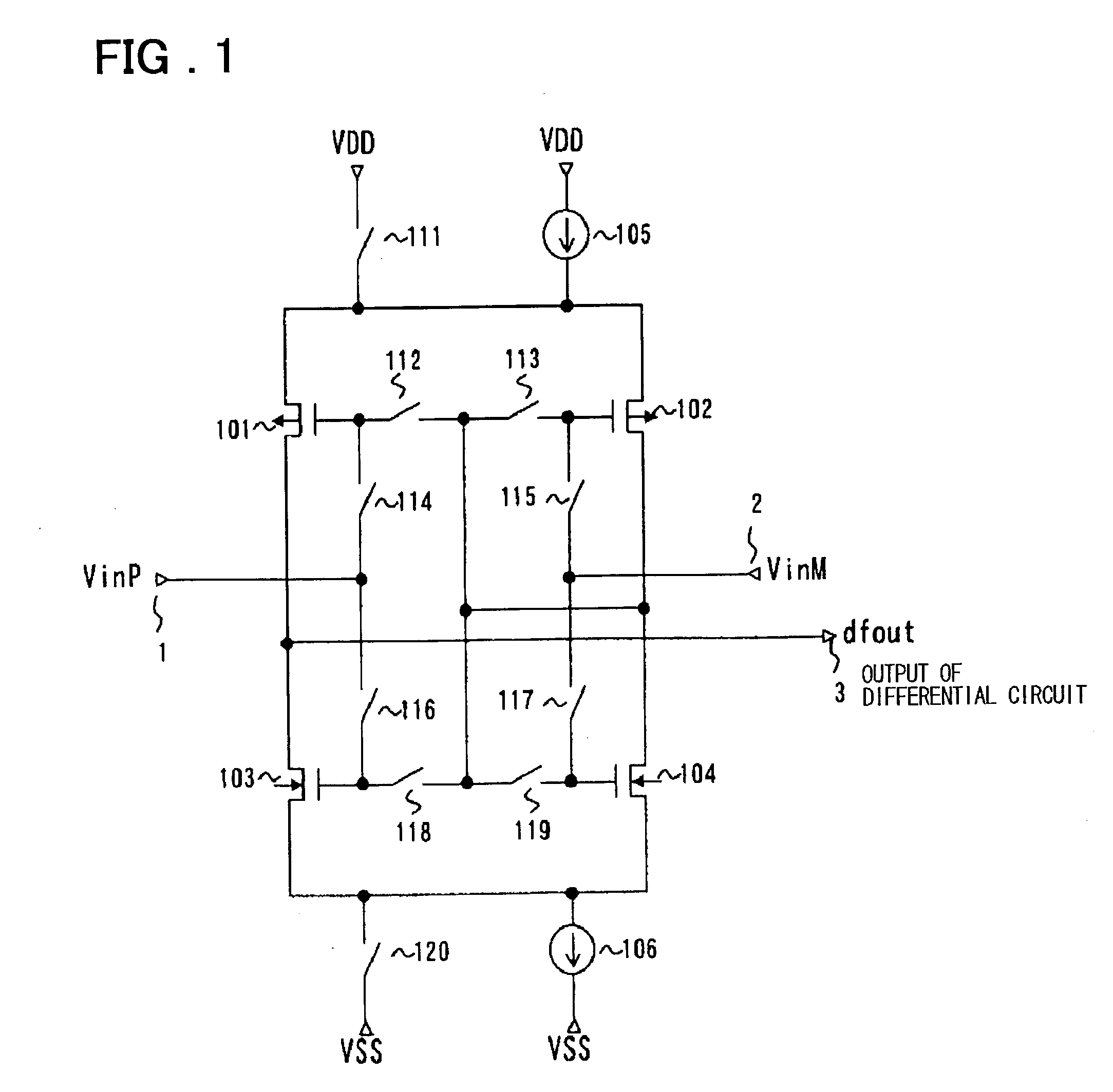

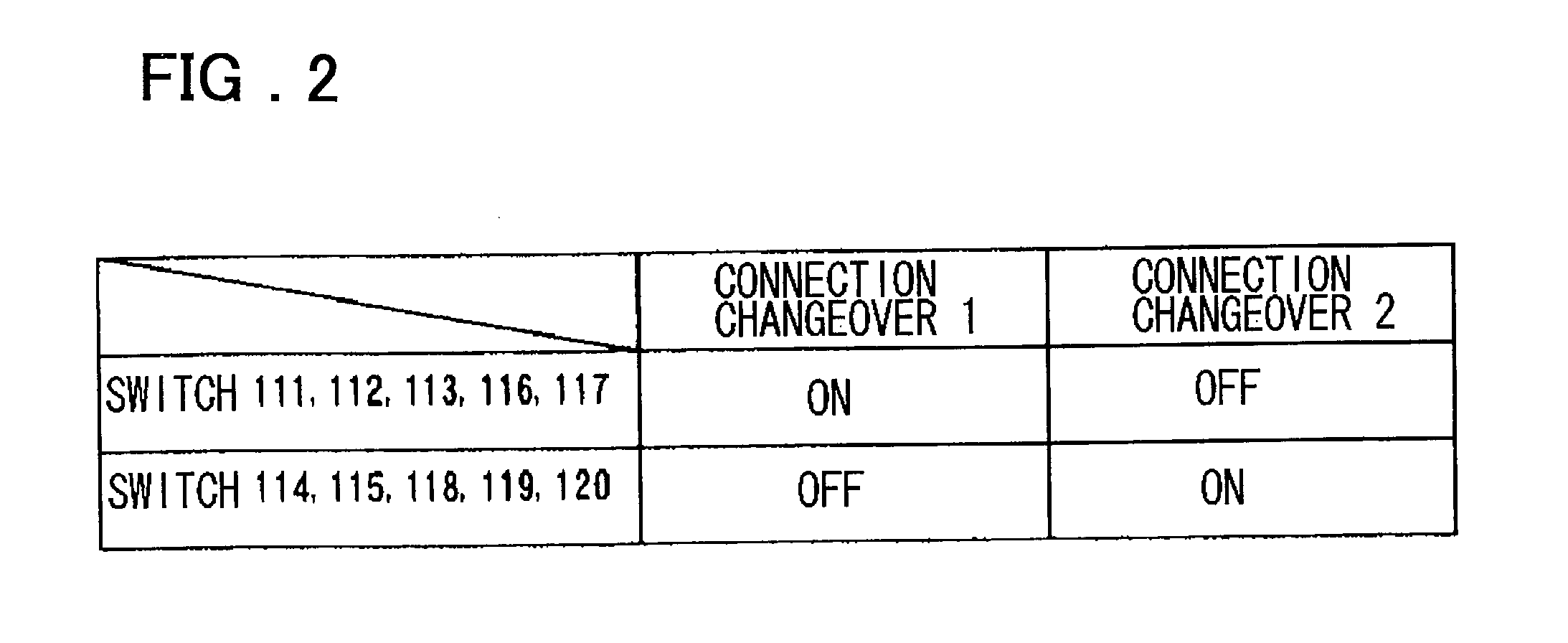

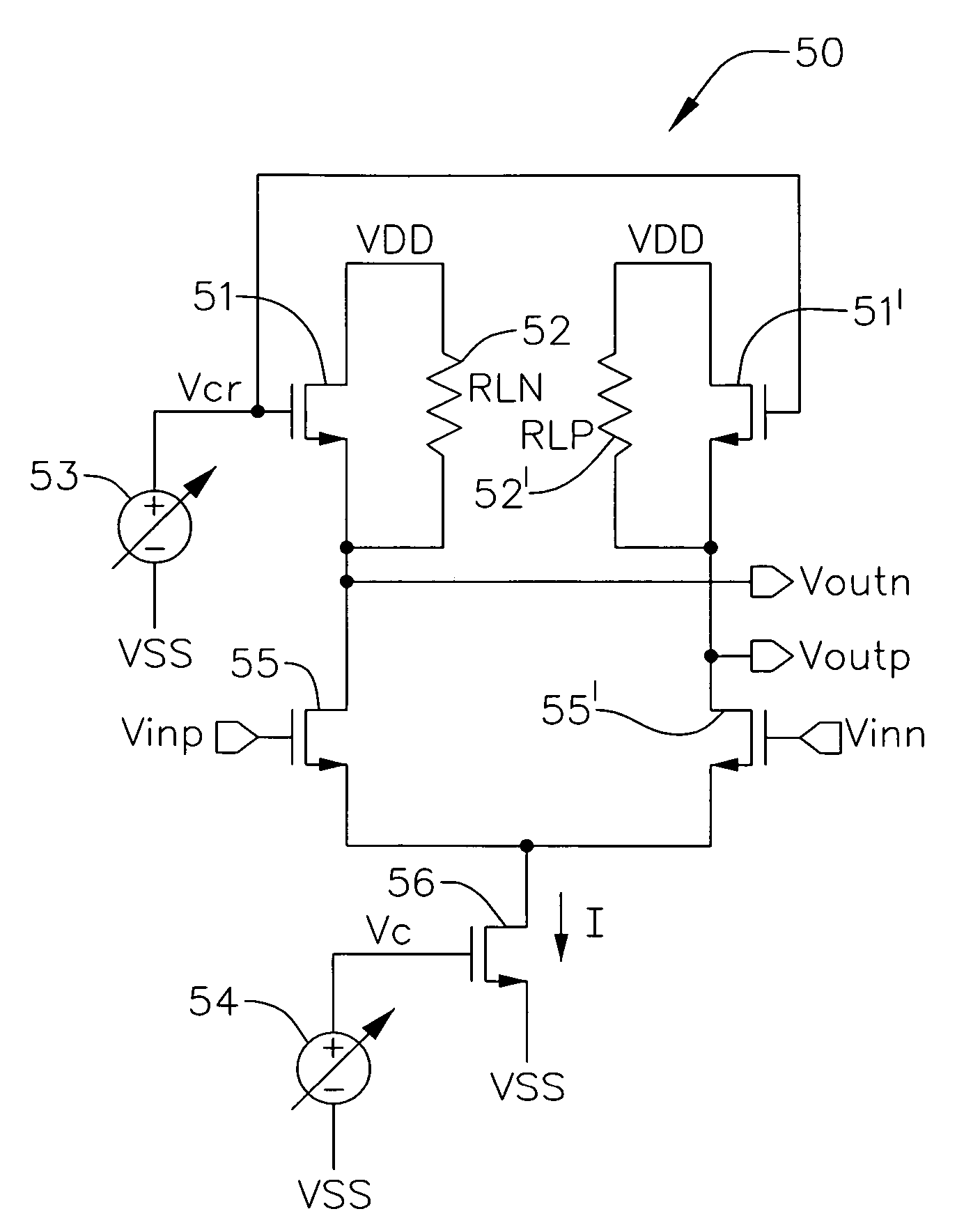

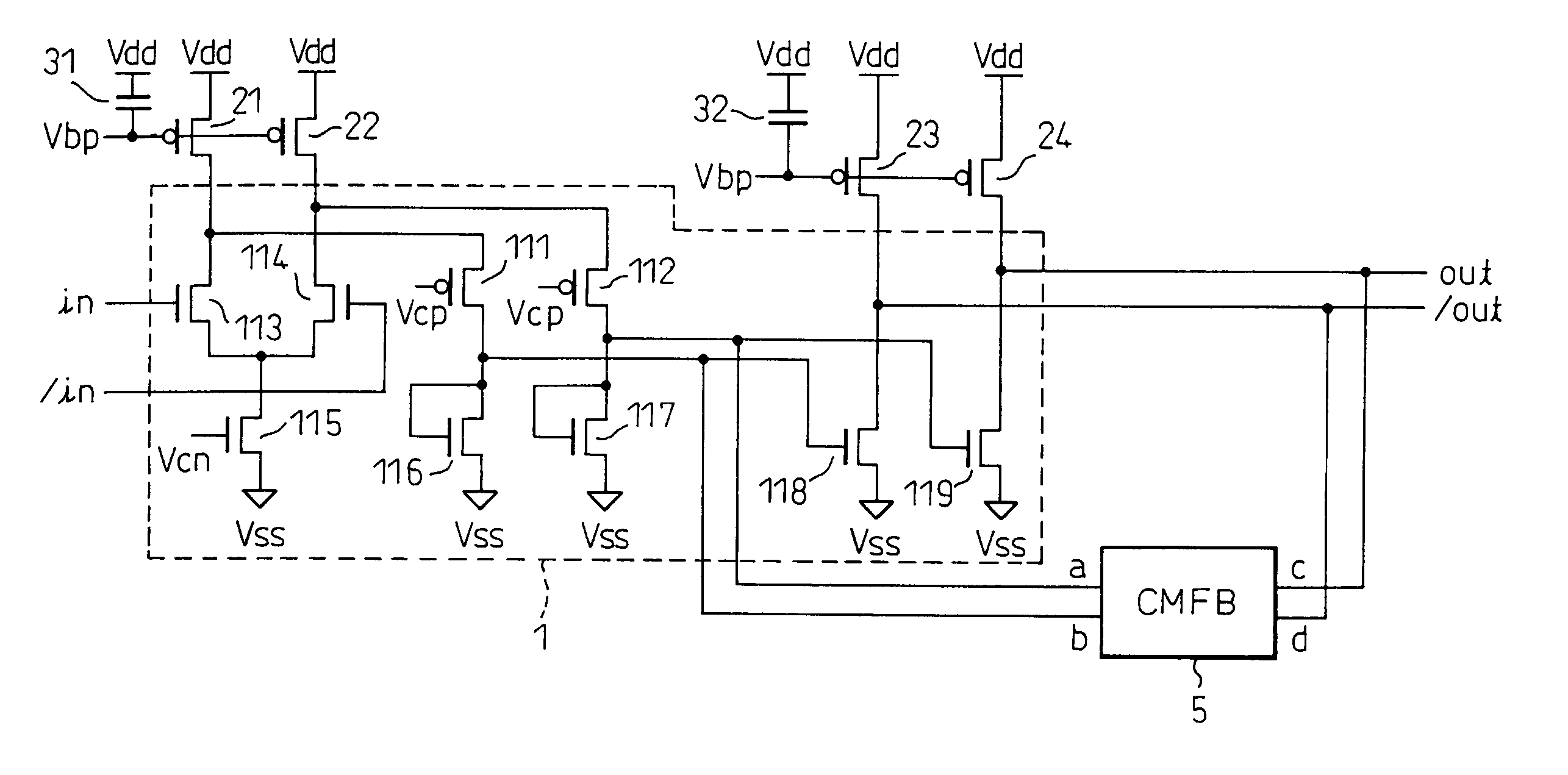

Differential circuit, amplifier circuit, driver circuit and display device using those circuits

ActiveUS20030160749A1Reduce power consumptionReducing amplitude difference deviationStatic indicating devicesGated amplifiersDriver circuitAudio power amplifier

A differential circuit and an amplifier circuit for reducing an amplitude difference deviation, performing a full-range drive, and consuming less power are disclosed. The circuit includes a first pair of p-type transistors and a second pair of n-type transistors. A first current source and a first switch are connected in parallel between the sources of the first pair of transistors, which are tied together, and a power supply VDD. A second current source and a second switch are connected in parallel between the sources of the second pair of transistors, which are tied together, and a power supply VSS. The circuit further includes connection changeover means that performs the changeover of first and second pairs between a differential pair that receives differential input voltages and a current mirror pair that is the load of the differential pair. When one of the two pairs is the differential pair, the other is the current mirror pair. In a differential amplifier circuit, there is provided an added transistor connected in parallel to a transistor, which is one transistor of a differential pair transistors, whose control terminal is a non-inverting input terminal. The added transistor has a control terminal for receiving a control voltage which is set so that, when an input voltage applied to the non-inverting input terminal is in a range in which the transistor whose control terminal is the non-inverting input terminal is turned off, the added transistor is turned on.

Owner:RENESAS ELECTRONICS CORP

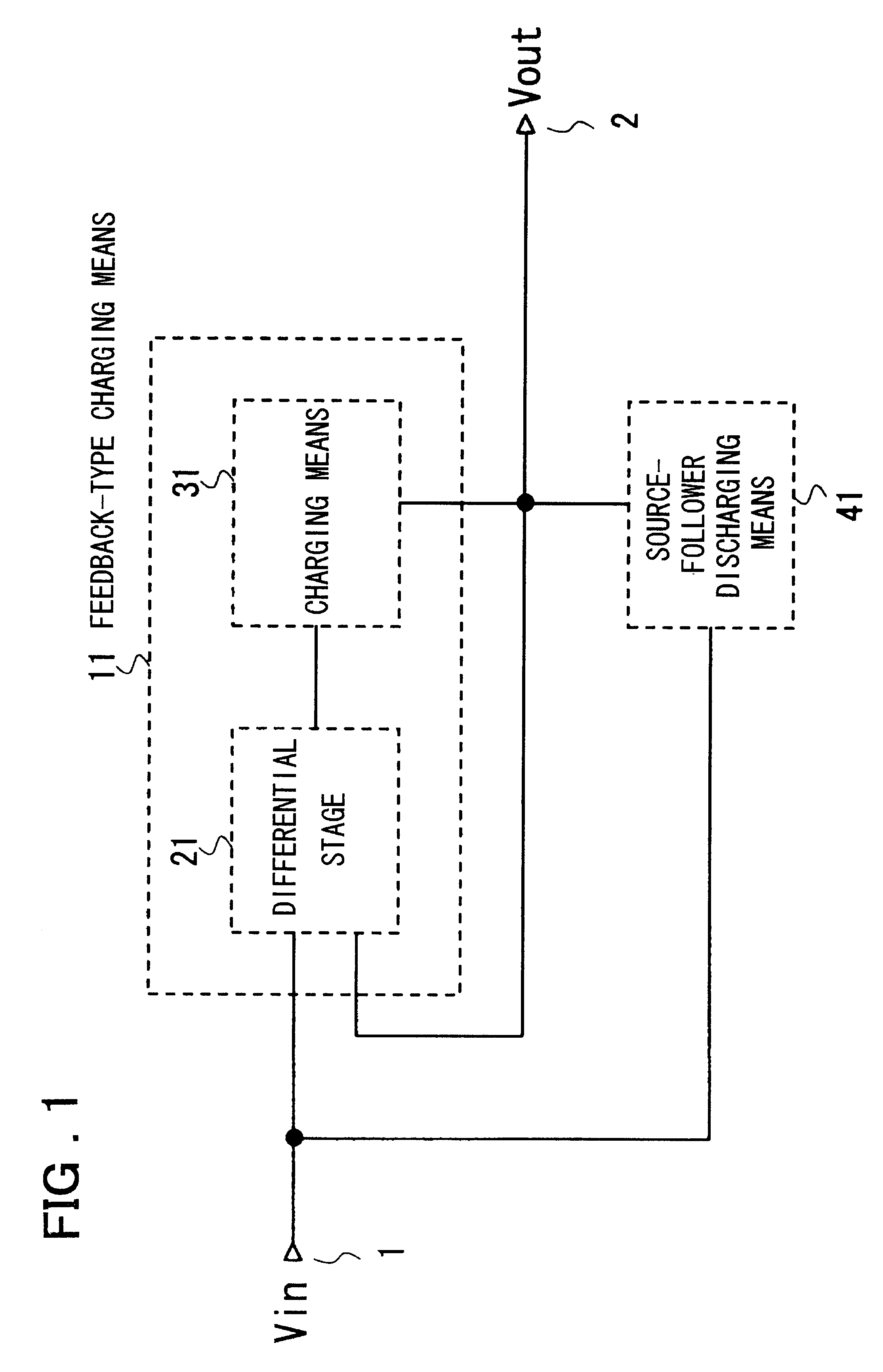

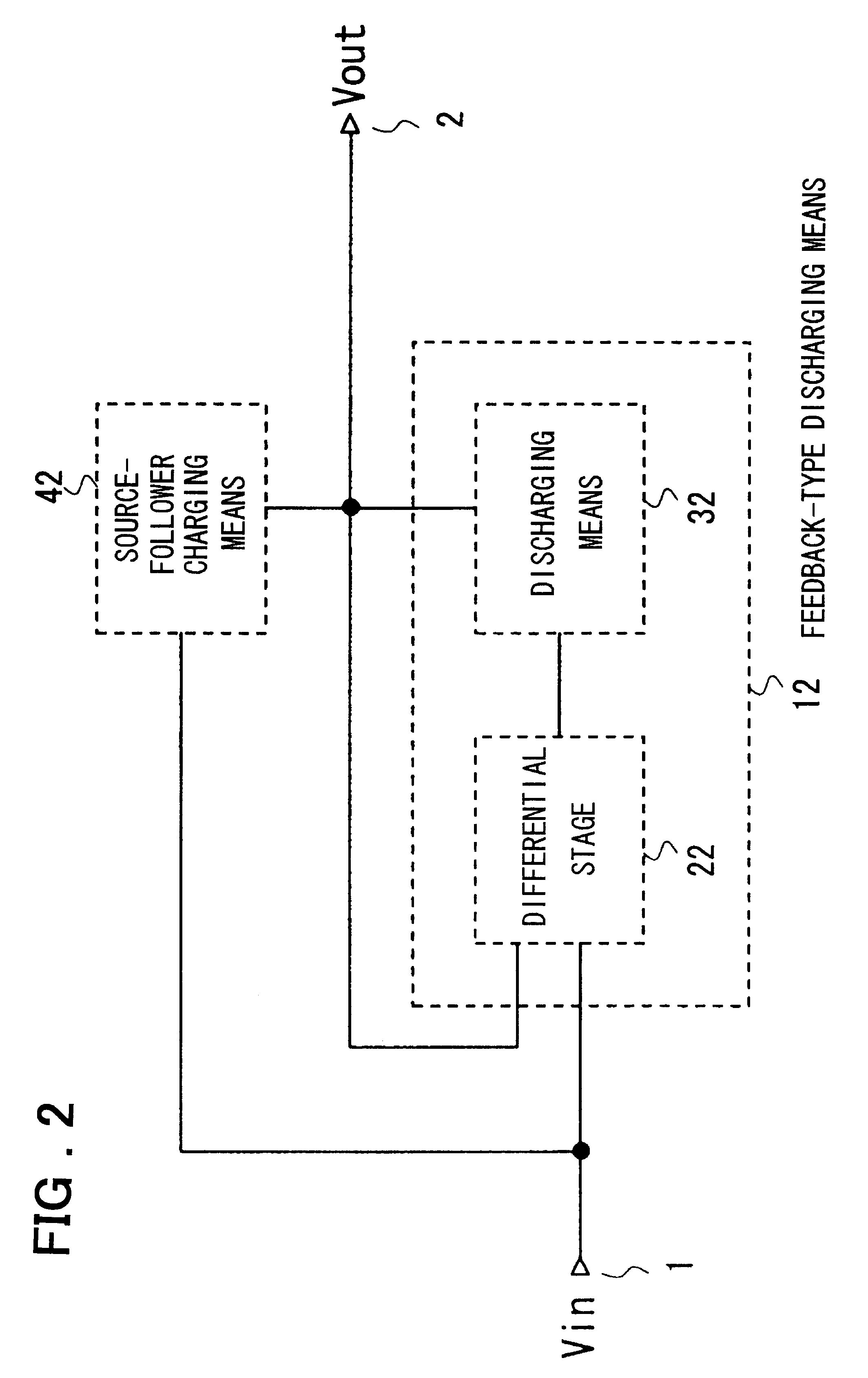

Feedback-type amplifier circuit and driver circuit

InactiveUS6614295B2Guaranteed uptimeIncrease computing speedAmplifier modifications to reduce non-linear distortionStatic indicating devicesDriver circuitAudio power amplifier

Disclosed is a feedback-type amplifier circuit including feedback-type charging means, which operates as a voltage follower, having a differential stage which receives an input-terminal voltage and an output-terminal voltage differentially as inputs and charging means for performing a charging operation at the output terminal based upon an output from the differential stage; and follower-type discharging means for performing a discharging operation at the output terminal by follower operation of an active element in accordance with a voltage difference between the input-terminal voltage and the output-terminal voltage.

Owner:RENESAS ELECTRONICS CORP

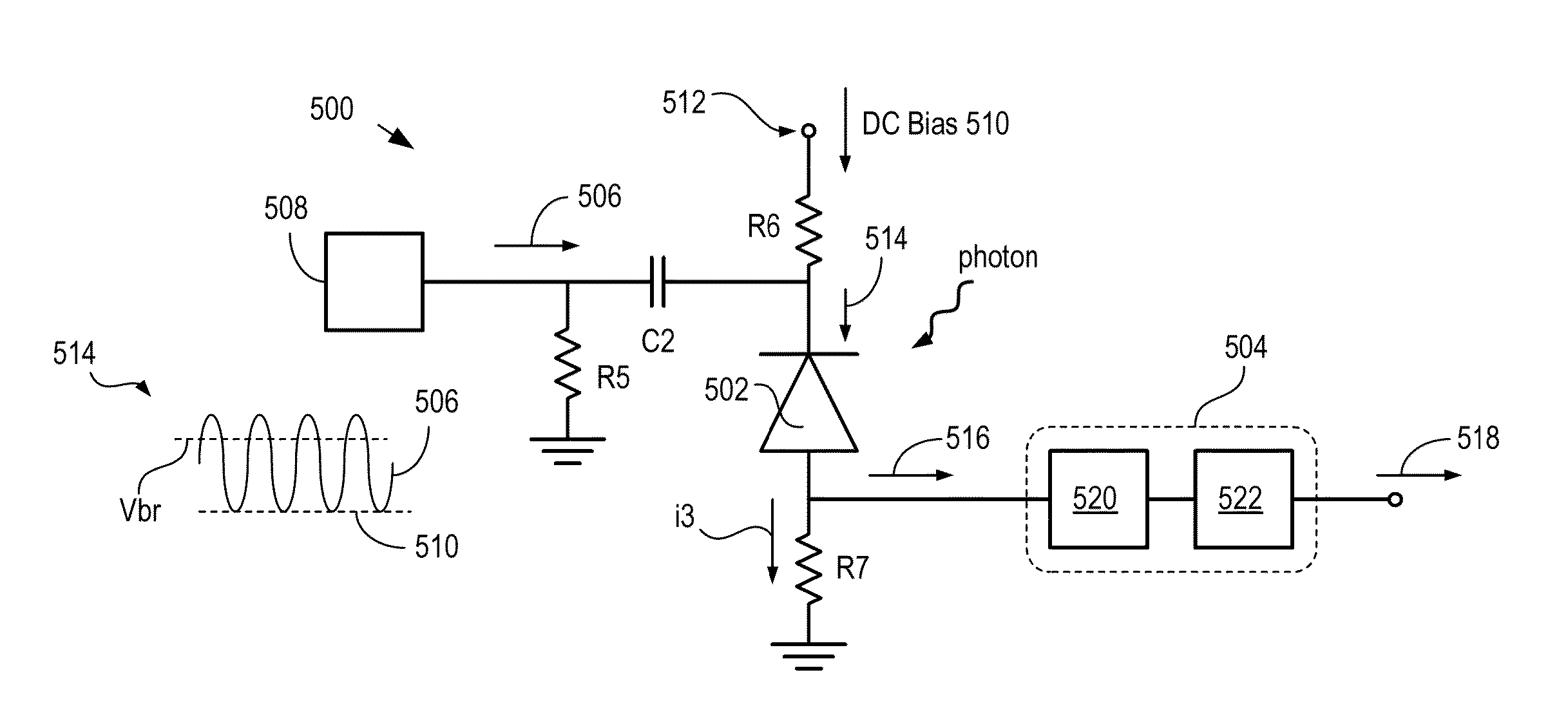

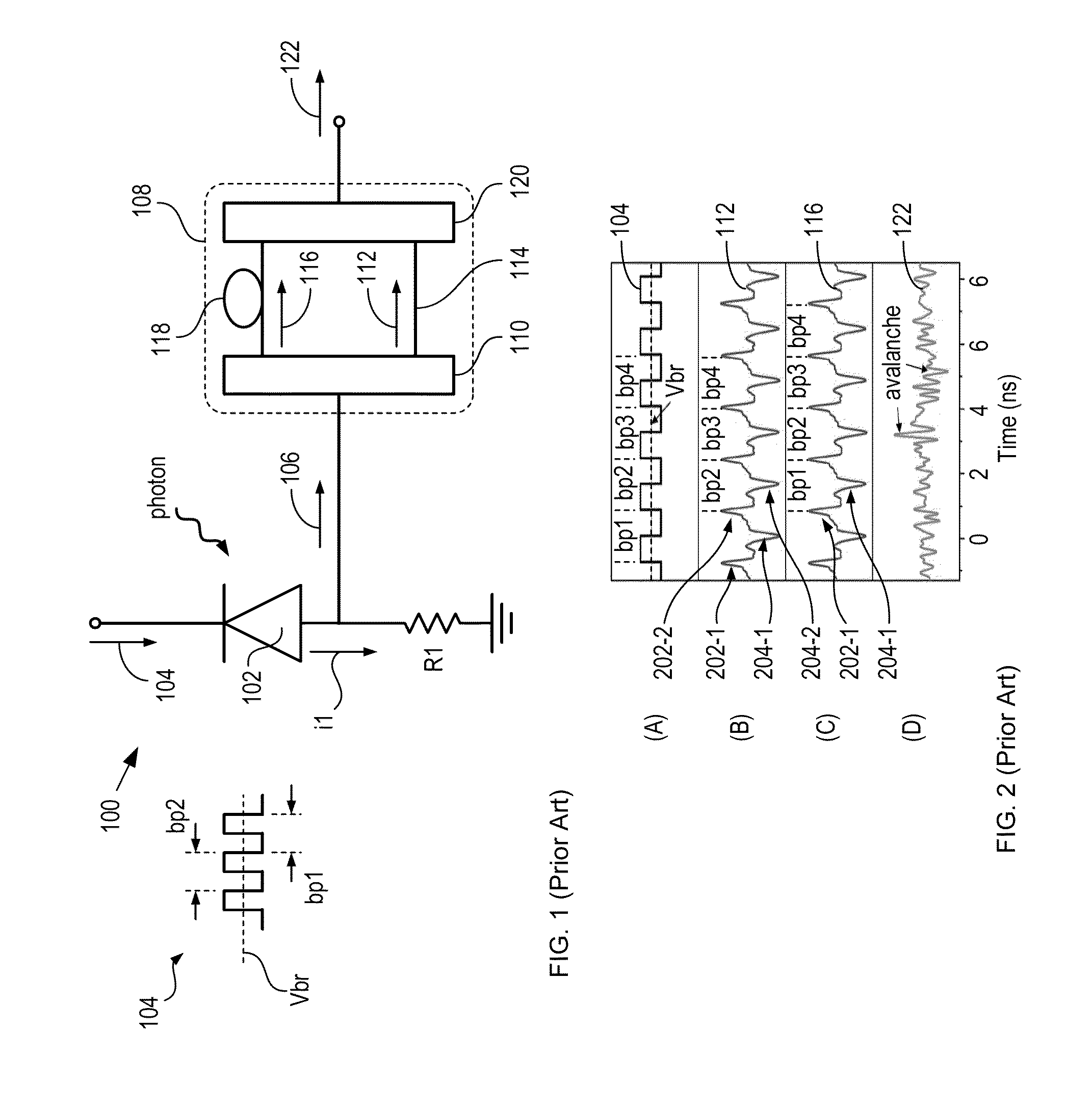

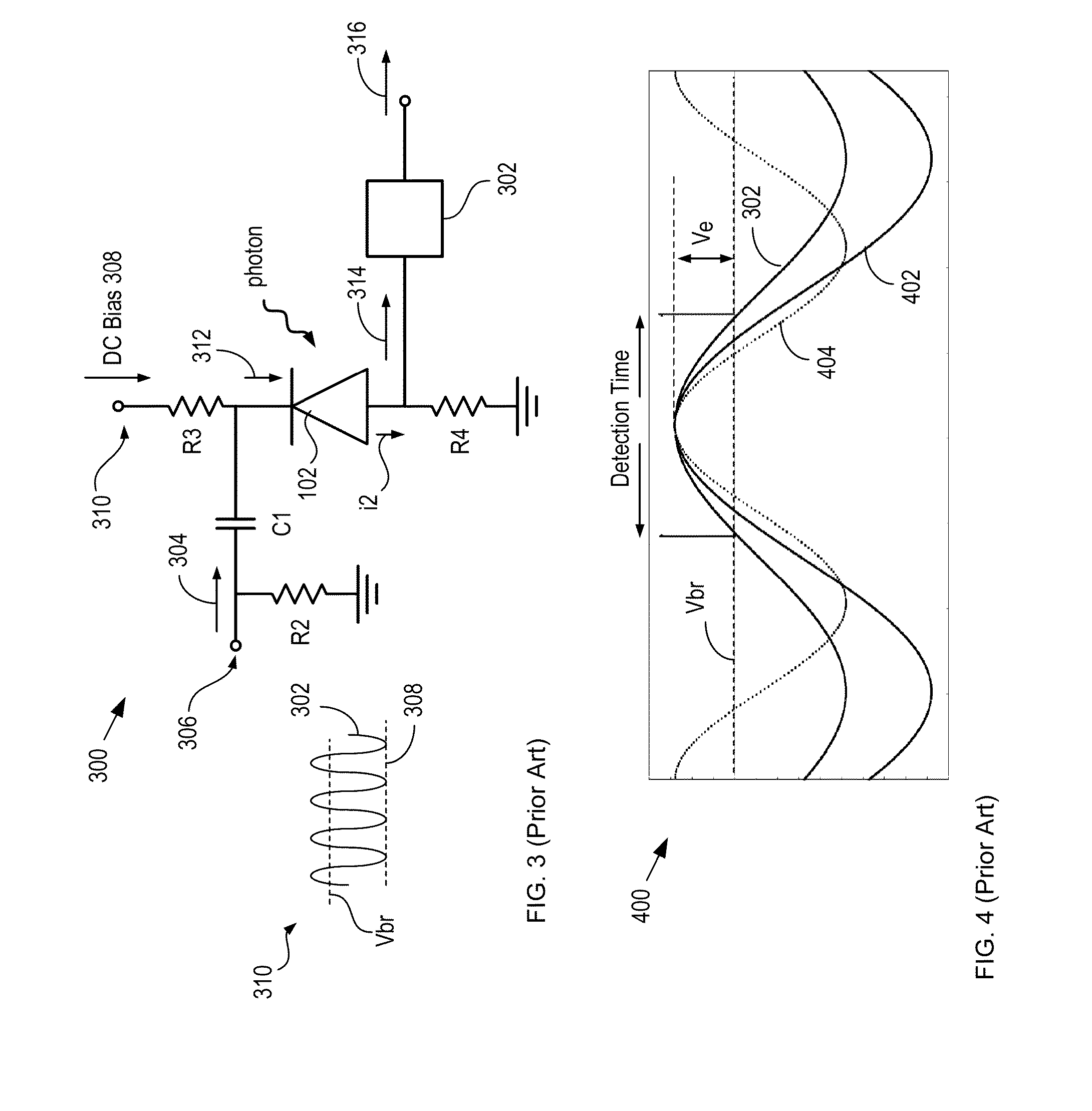

High-repetition-rate single-photon receiver and method therefor

ActiveUS8796605B2Material analysis by optical meansElectronic switchingSignal qualityLow-pass filter

A single-photon receiver and method for detecting a single-photon are presented. The receiver comprises a SPAD that receives a gating signal having a fundamental frequency in the 100 MHz to multiple GHz range. The receiver further comprises a two-stage frequency filter for filtering the output of the SPAD, wherein the filter has: (1) a notch filter response at the fundamental frequency; and (2) a low-pass filter response whose cutoff frequency is less than the first harmonic of the fundamental frequency. As a result, the frequency filter removes substantially all the frequency components in the SPAD output without significant degradation of the signal quality but with reduced complexity, cost, and footprint requirement relative to receivers in the prior art.

Owner:LG INNOTEK CO LTD

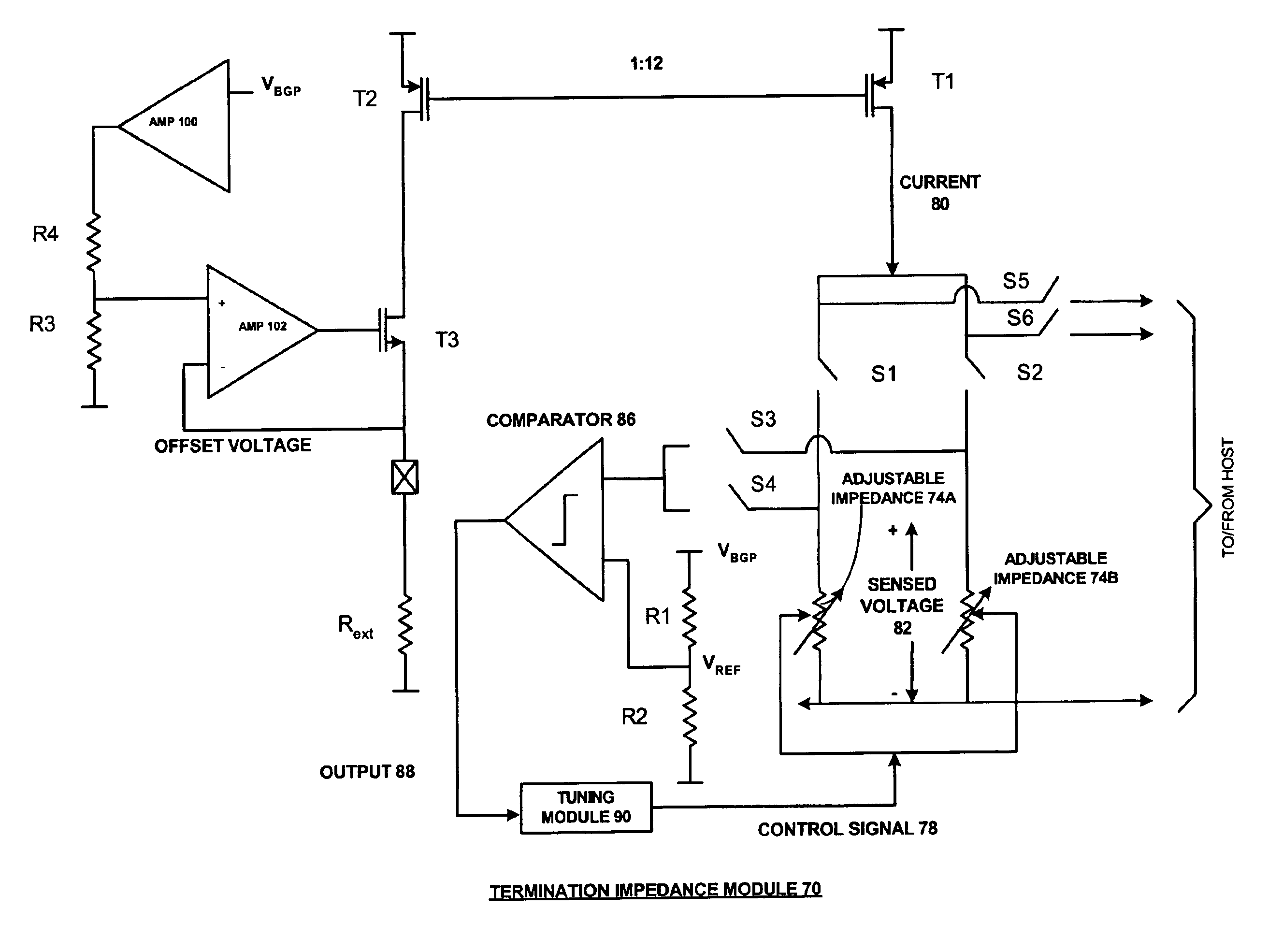

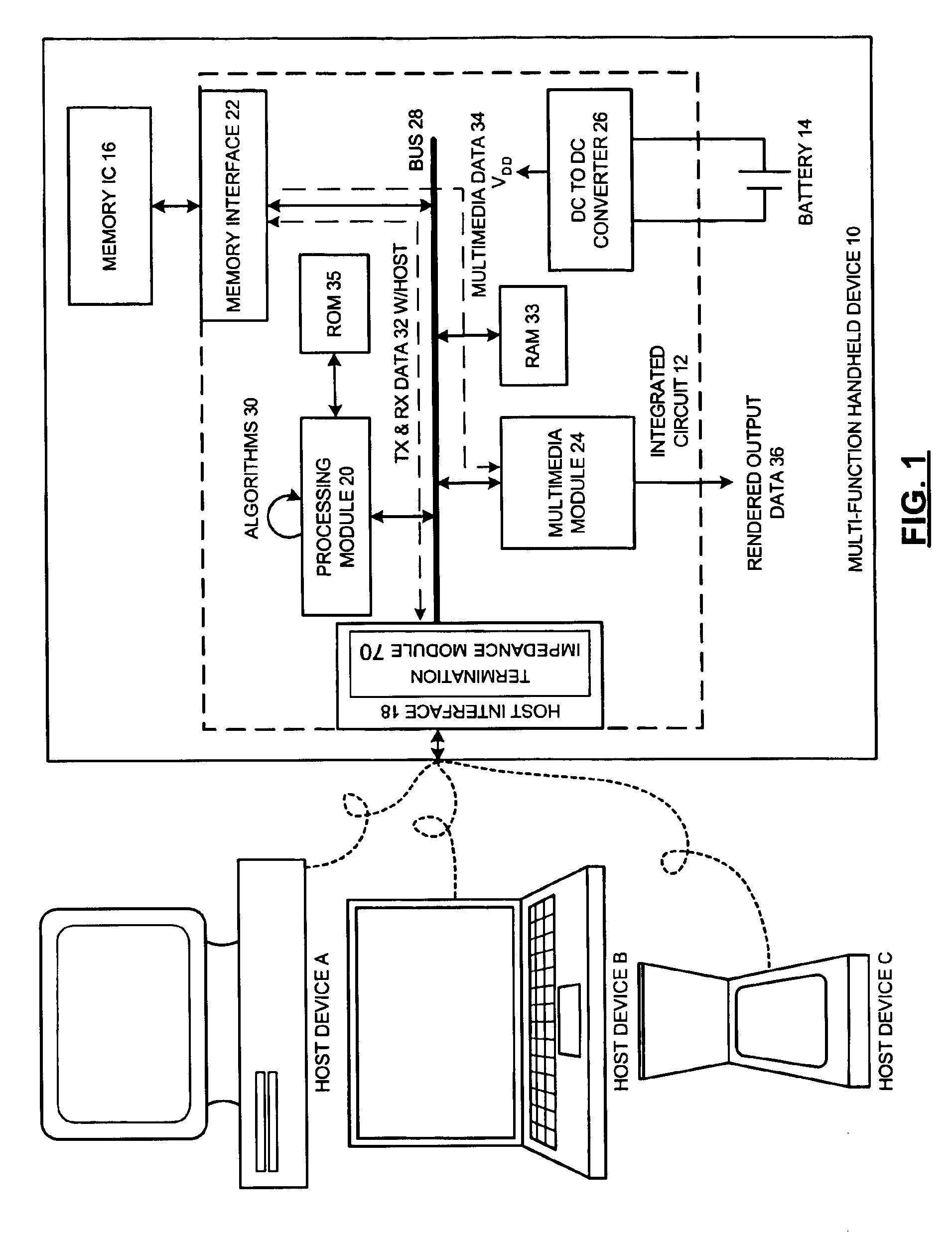

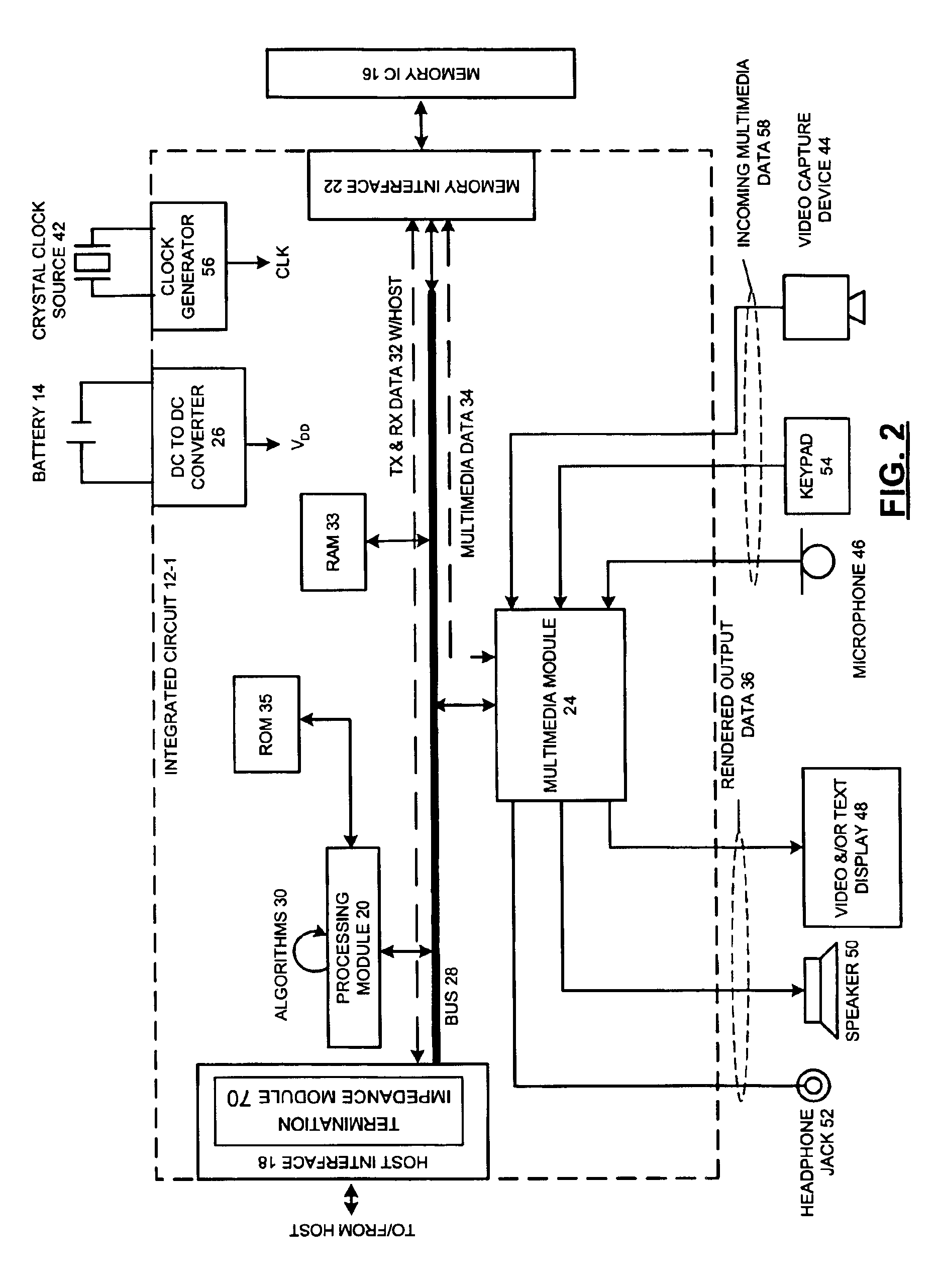

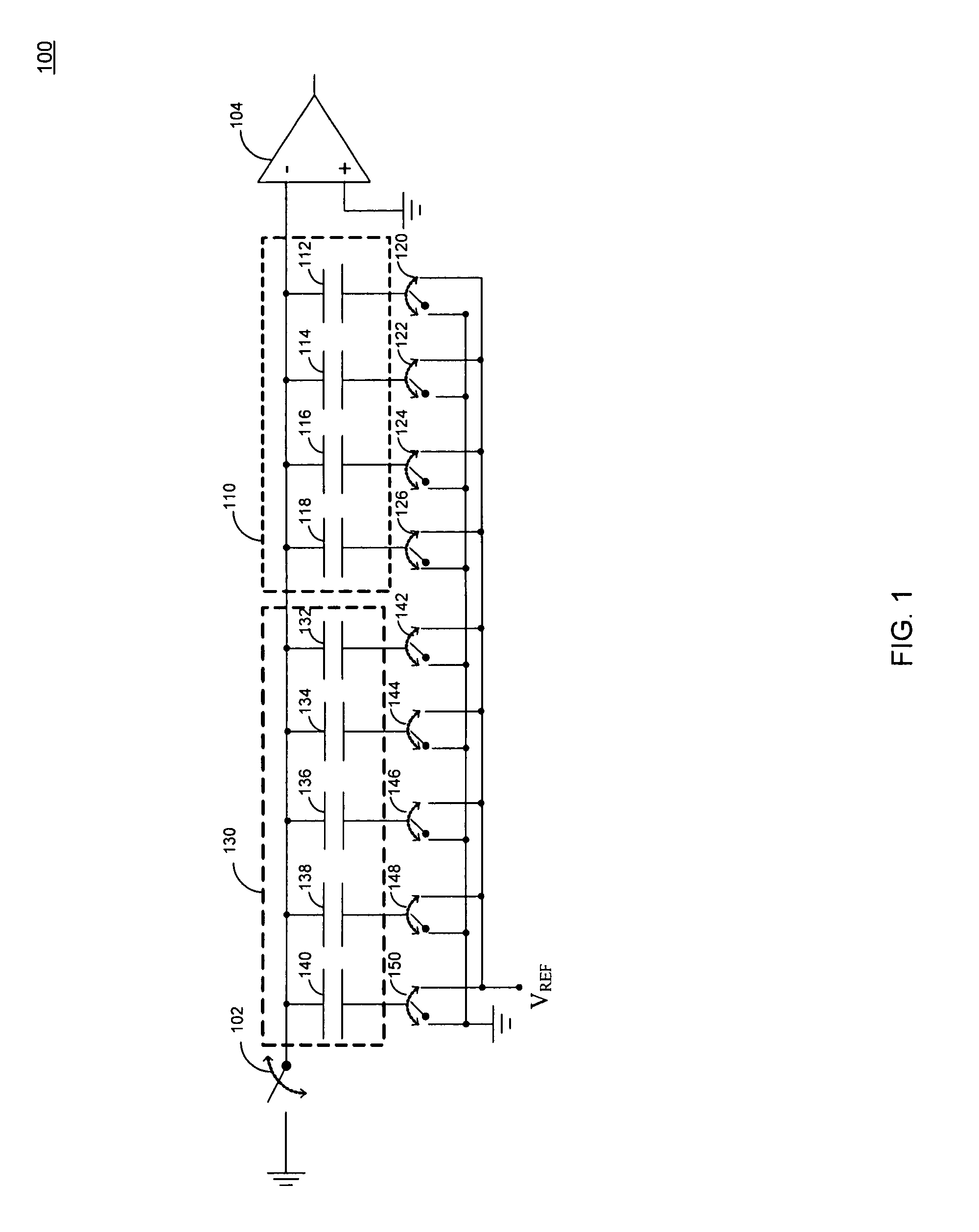

System and method to establish an adjustable on-chip impedance

ActiveUS6940303B2Multiple-port networksReliability increasing modificationsReference currentVoltage reference

A method to establish an adjustable on-chip impedance within a predetermined range that involves establishing a reference current for the adjustable on-chip impedance and applying this reference current to the adjustable on-chip impedance. A voltage produced by applying the reference current to the adjustable on-chip impedance is sensed and compared with the comparator or other similar processor to a reference voltage. This comparison allows the adjustable on-chip impedance to be tuned when the comparison of the sense voltage and the reference voltage is unfavorable. Tuning the impedance results in an impedance value within a predetermined range that accounts for variances of both the reference current and reference voltage.

Owner:APPLE INC

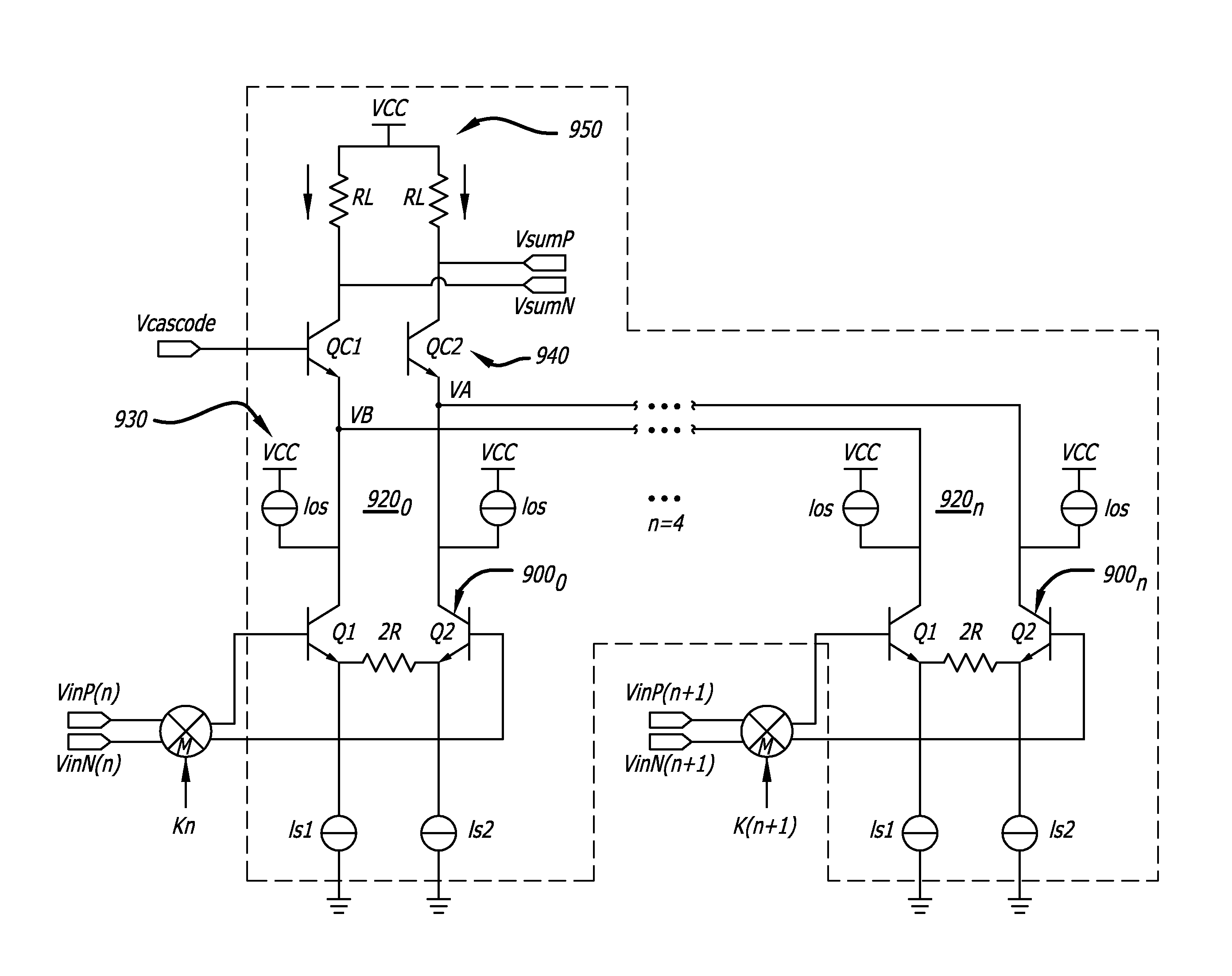

Analog finite impulse response filter

ActiveUS20100271107A1Transversal filtersComputations using contact-making devicesParasitic capacitanceEngineering

According to one embodiment of the invention, a programmable finite impulse response (FIR) filter is implemented with differential isolation circuits to isolate parasitic capacitance from attenuating an output signal at both a first and second differential output terminals of the FIR filter. The FIR includes a summing circuit that provides operational advantages to the FIR filter.

Owner:LUMENTUM OPERATIONS LLC

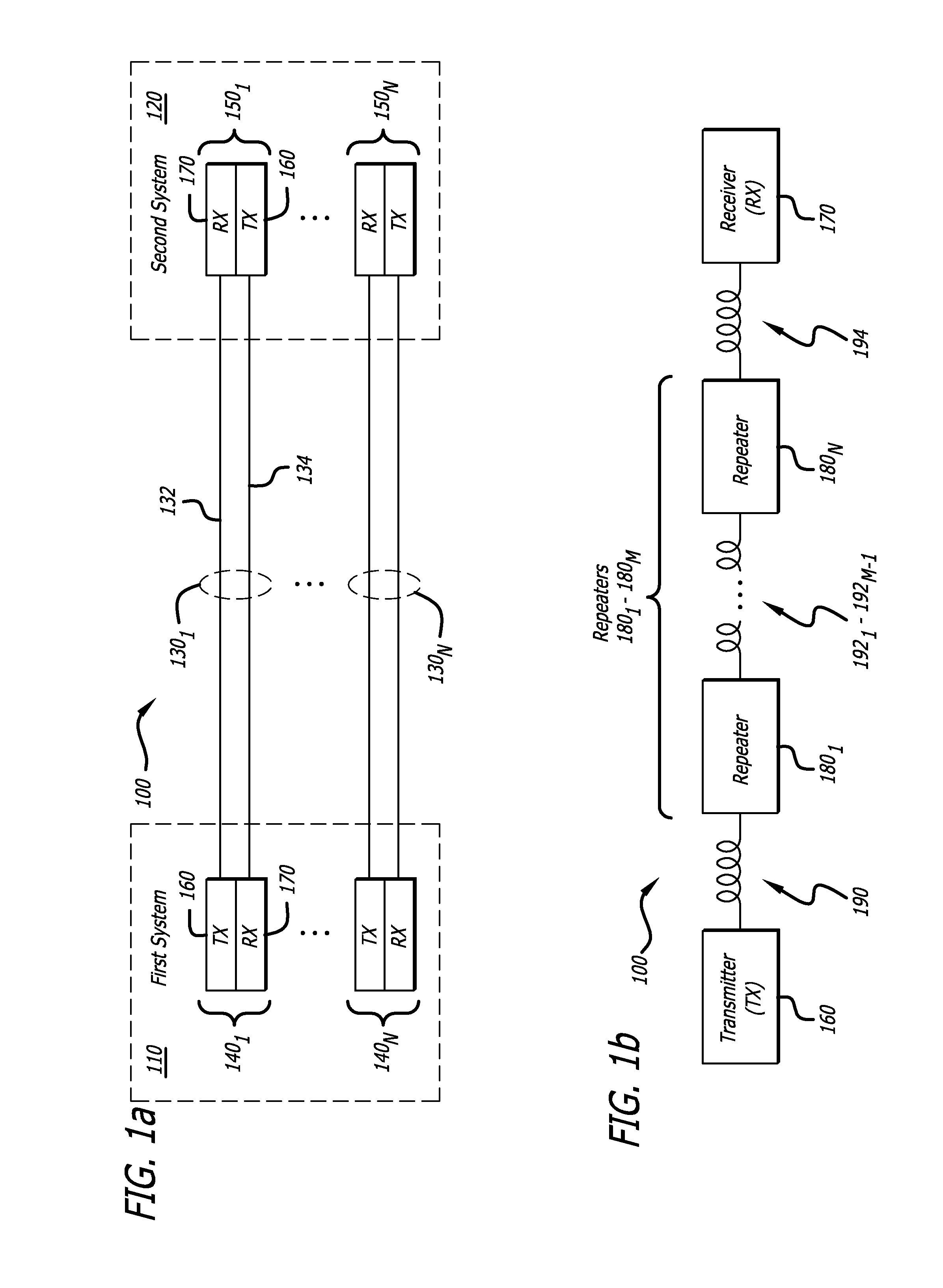

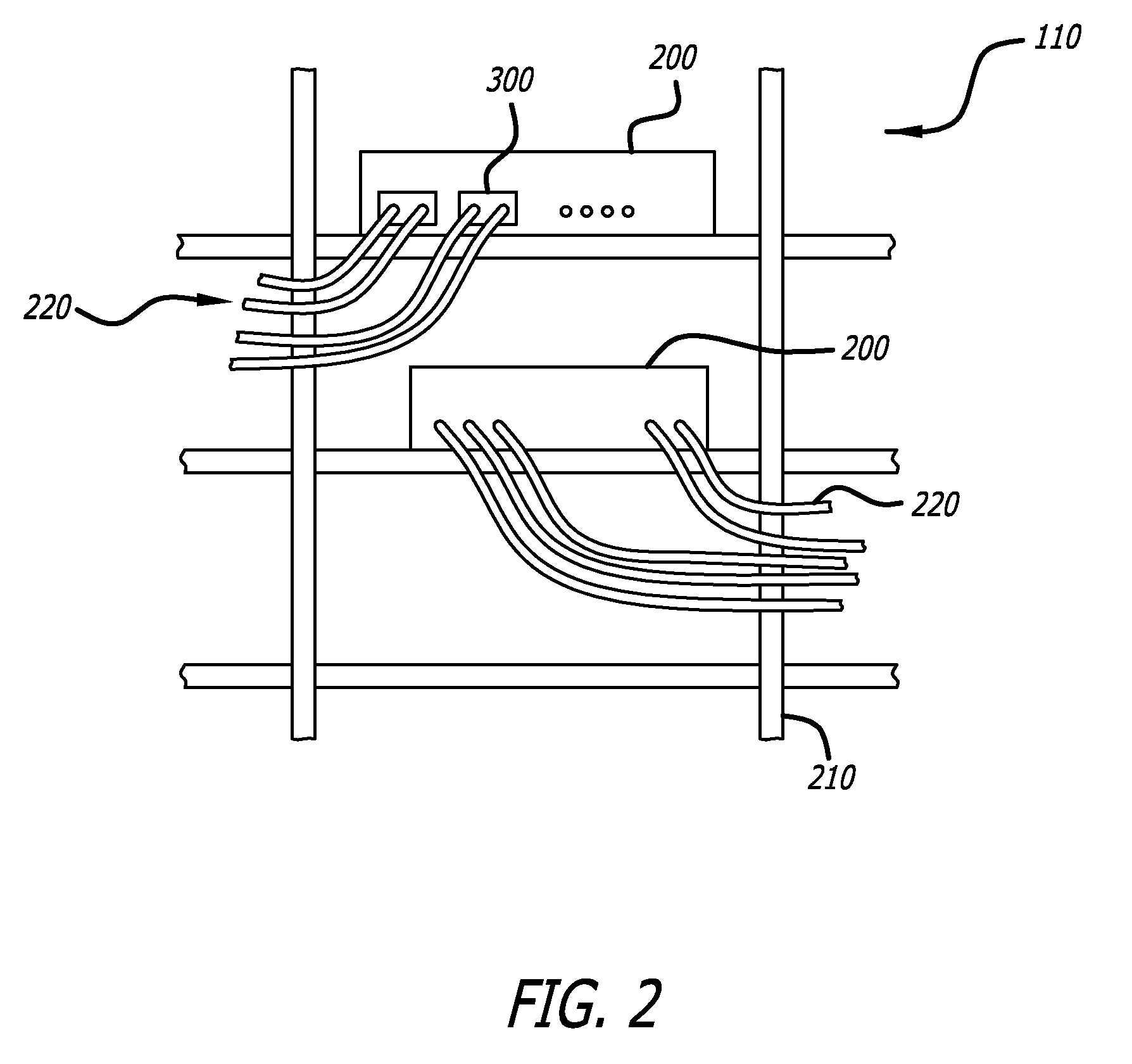

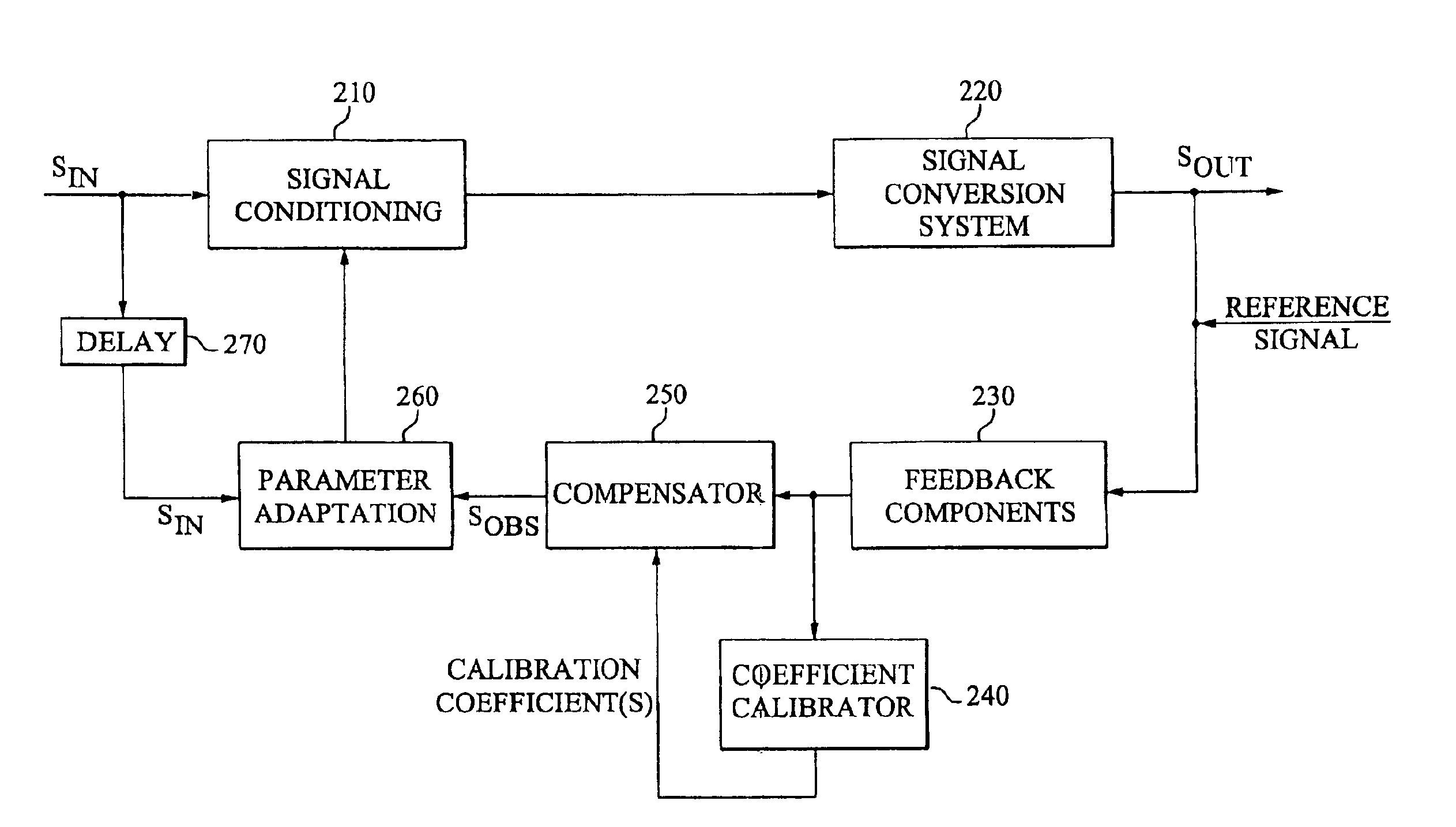

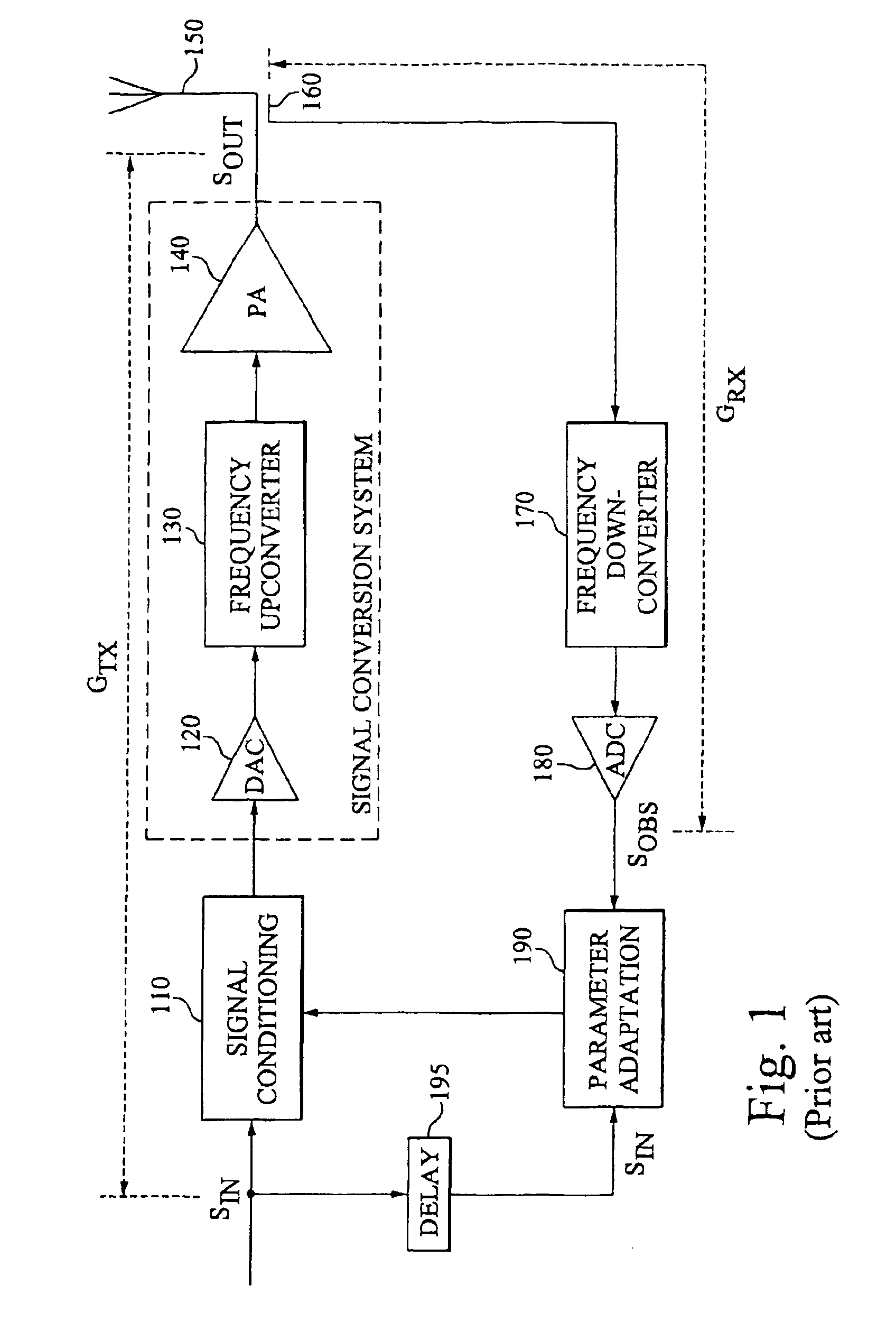

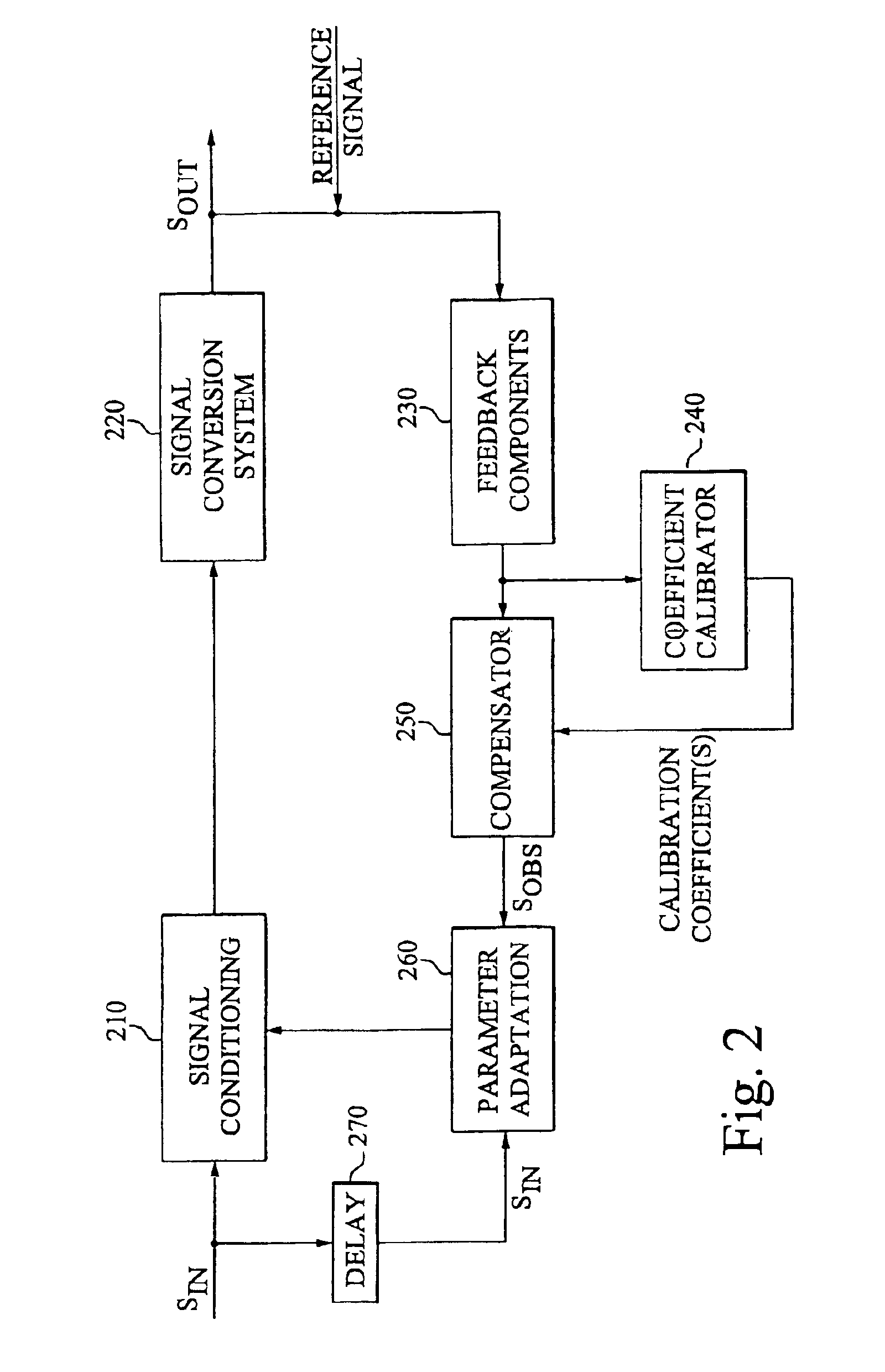

Calibration of an adaptive signal conditioning system

InactiveUS6943627B2Robust and efficient calibrationAccurate conditionAmplifier modifications to reduce non-linear distortionElectric devicesSignal conditioningEngineering

The invention provides robust and non-invasive calibration of an adaptive signal conditioning system having a signal conditioning block in the signal path to a signal conversion system, and a feedback path with a number of feedback components for enabling adaptation, by means of a parameter adaptation block, of the parameters used in the signal conditioning. In order to calibrate the feedback path, a well-defined reference signal is inserted into the feedback path, and an appropriate calibration coefficient is then determined by a coefficient calibrator in response to the received reference signal. The calibration coefficient is provided to a compensator, which effectively compensates for changes in the transfer characteristics of the feedback path due to factors such as variations in ambient temperature and component aging. Accordingly, the feedback signal transferred over the calibrated feedback path will be an accurate representation of the output signal of the signal conversion system, thus allowing accurate adaptive signal conditioning.

Owner:TELEFON AB LM ERICSSON (PUBL)

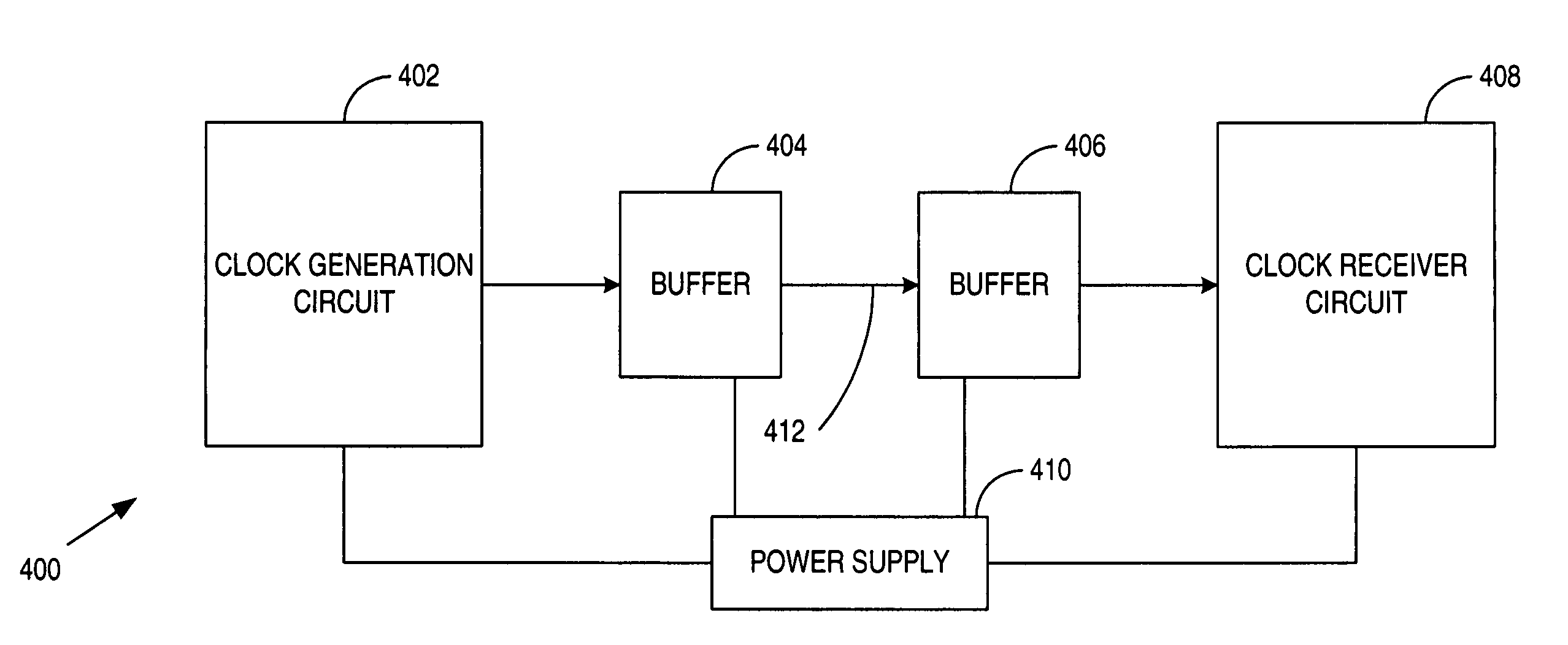

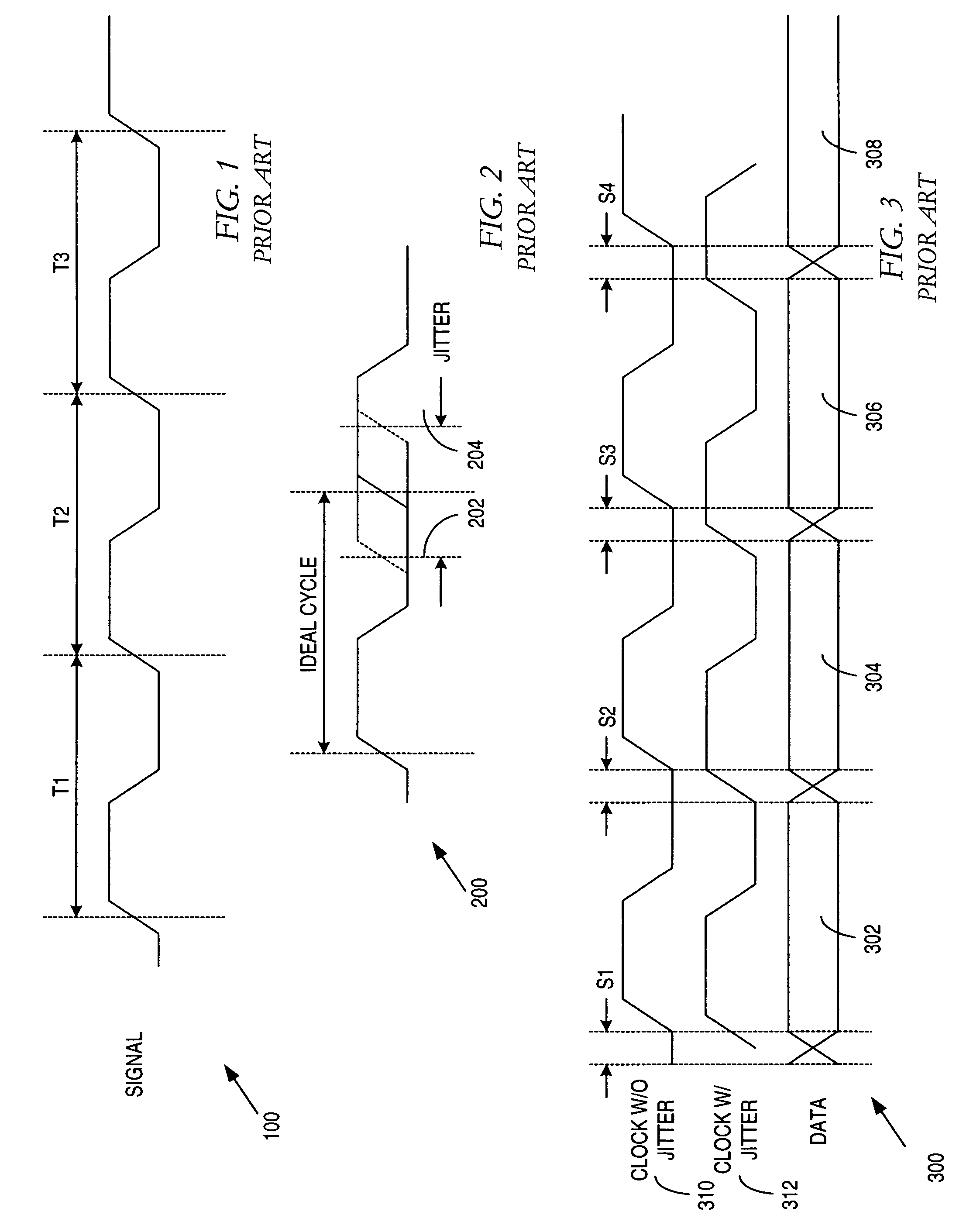

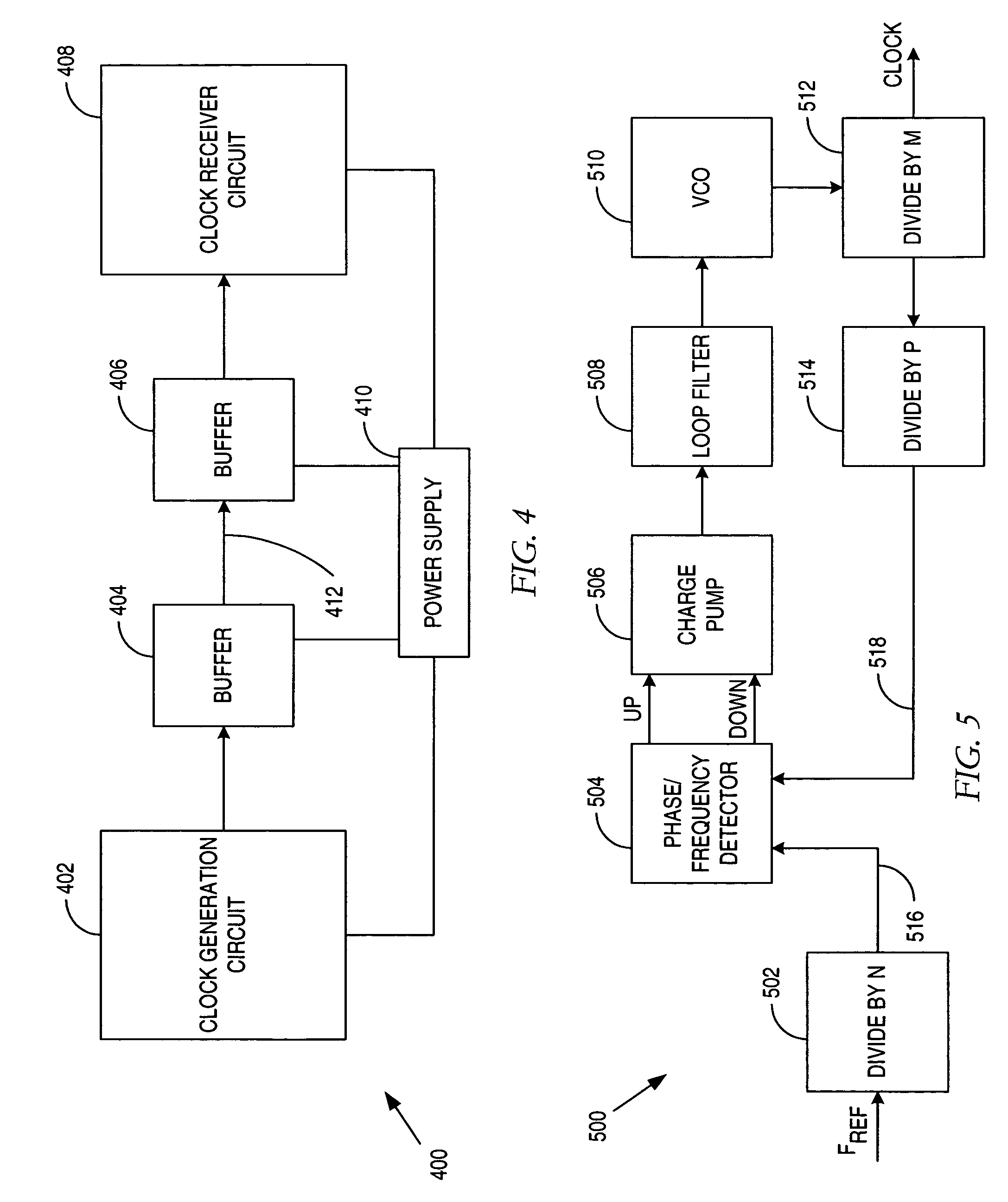

Method and apparatus for a reference clock buffer system

ActiveUS7142005B1Reduces power-supplyReduces noise-induced jitterPulse automatic controlElectronic switchingData bufferCross coupled

Owner:XILINX INC

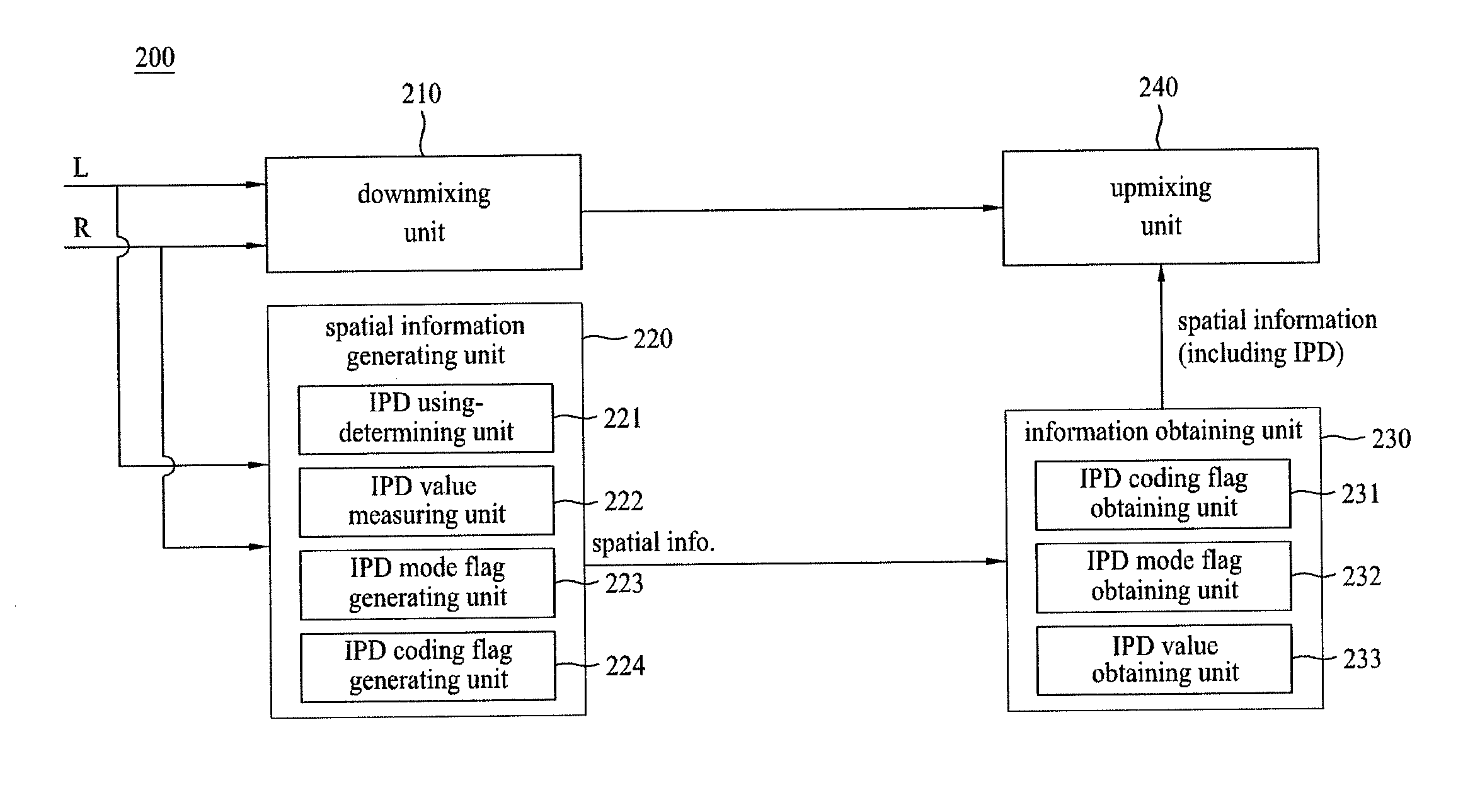

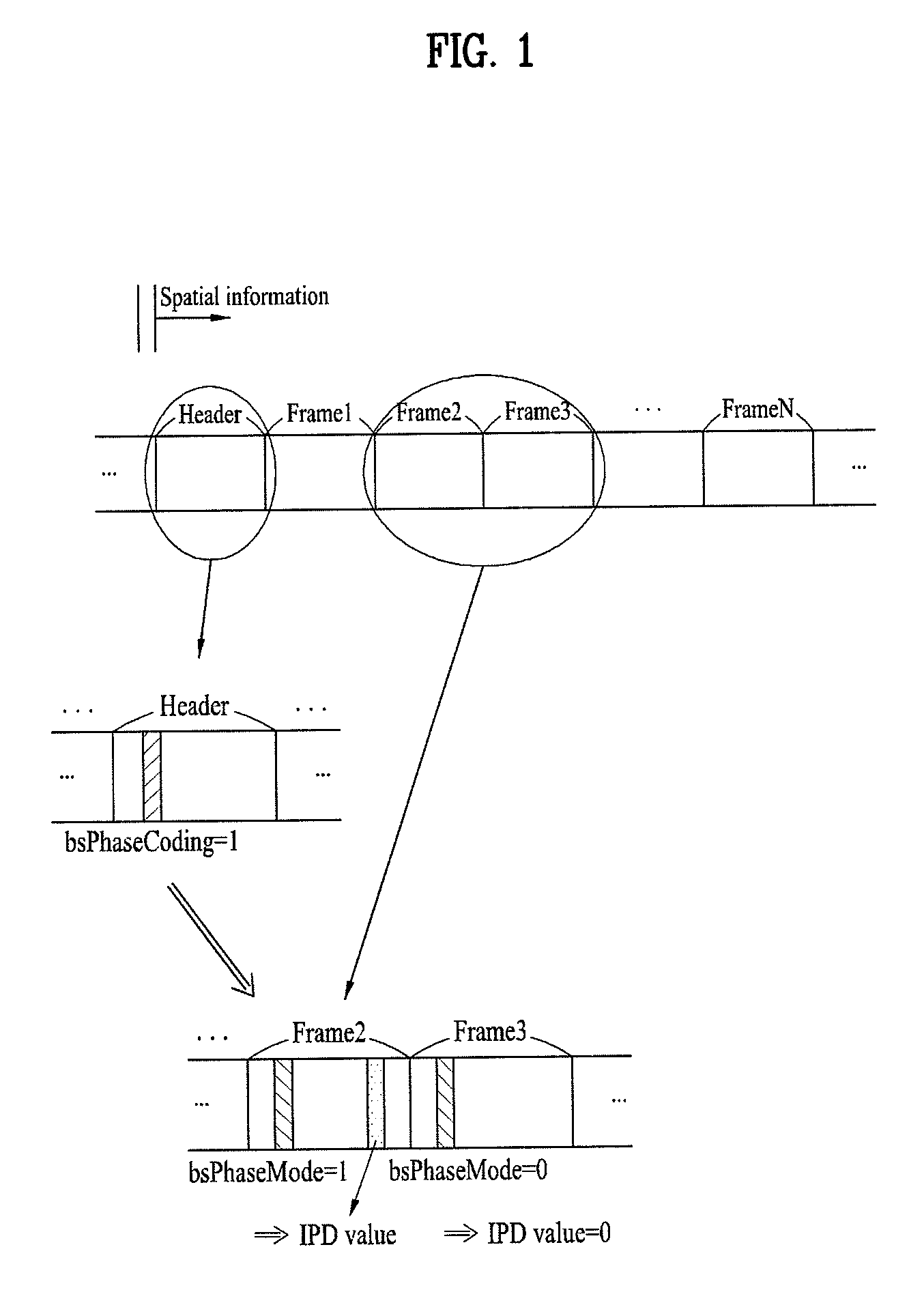

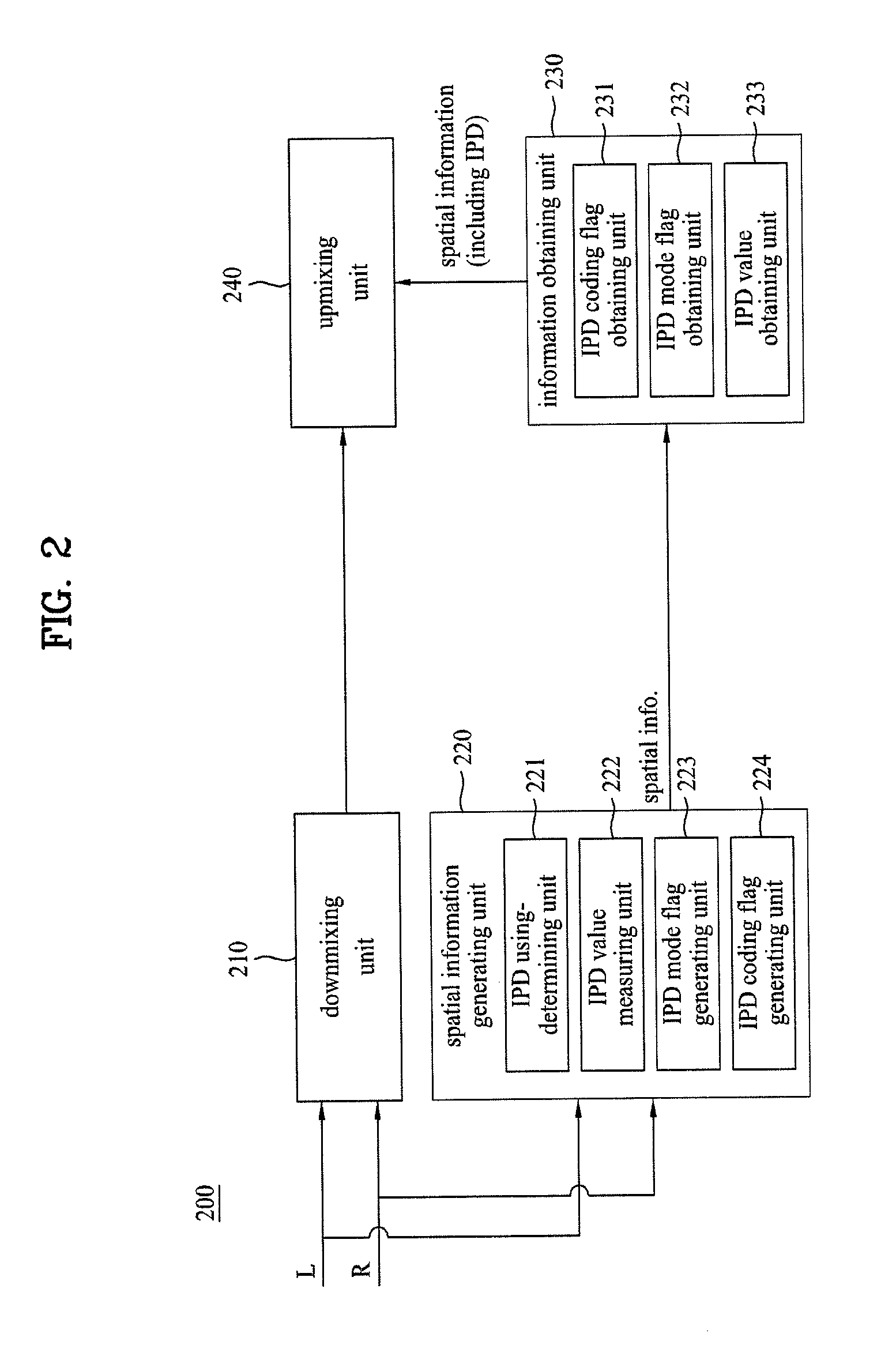

Method and an apparatus for processing a signal

A method of processing a signal is disclosed. The present invention includes receiving (a) a downmix signal being generated from plural-channel signal and (b) spatial information indicating attribute of the plural-channel signal, in order to upmix the downmix signal; obtaining inter-channel phase difference(IPD) coding flag indicating whether IPD value is used to the spatial information from a header of the spatial information; obtaining IPD mode flag indicating whether the IPD is used to frame of the spatial information from the frame based on the IPD coding flag; obtaining the IPD value from a parameter band in the frame based on the IPD mode flag; generating plural-channel signal by applying the IPD value to the downmix signal, wherein the spatial information is divided by header and a plurality of the frame and wherein the IPD value indicates phase difference between two channels of the plural-channel signal and wherein the parameter band is at least one sub-band of frequency domain including the IPD value.

Owner:LG ELECTRONICS INC

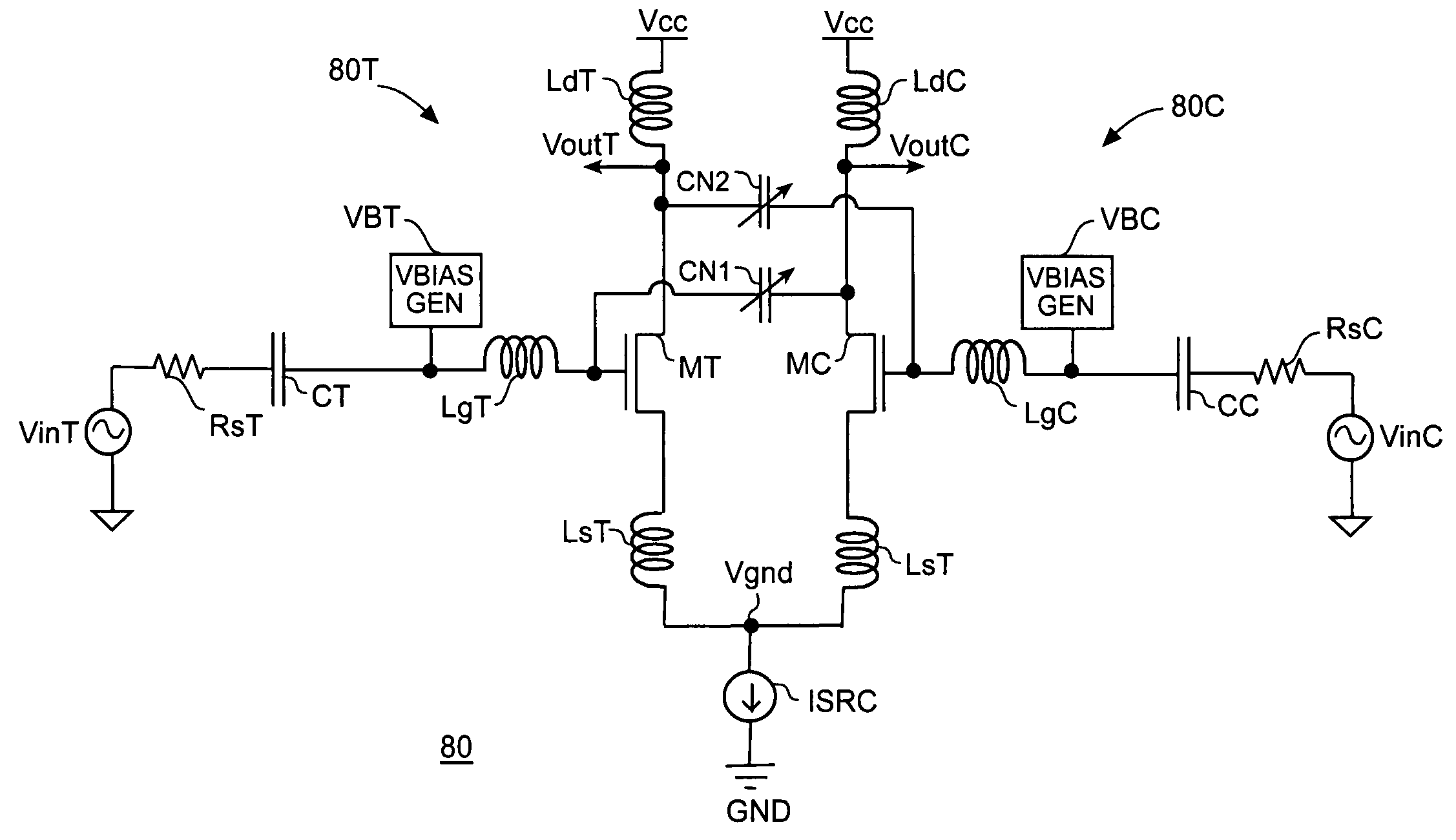

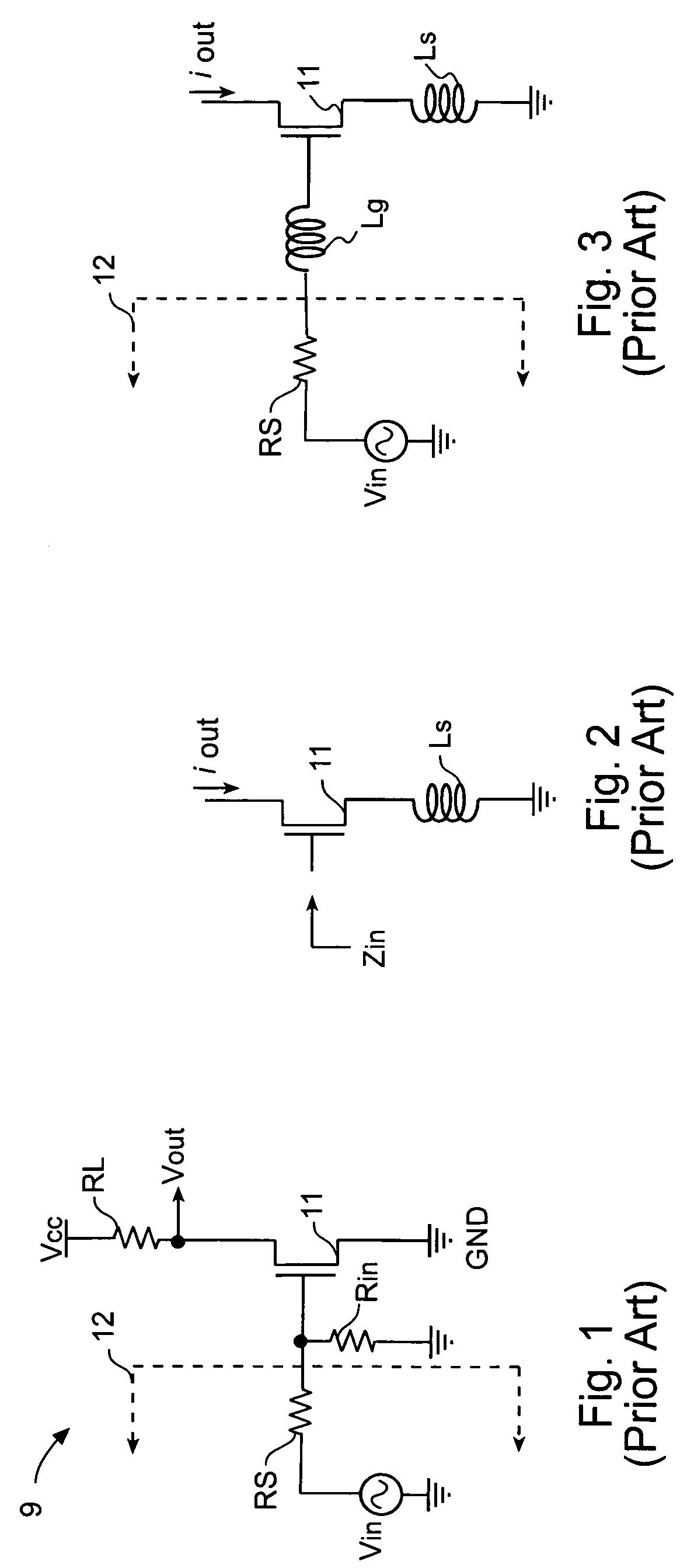

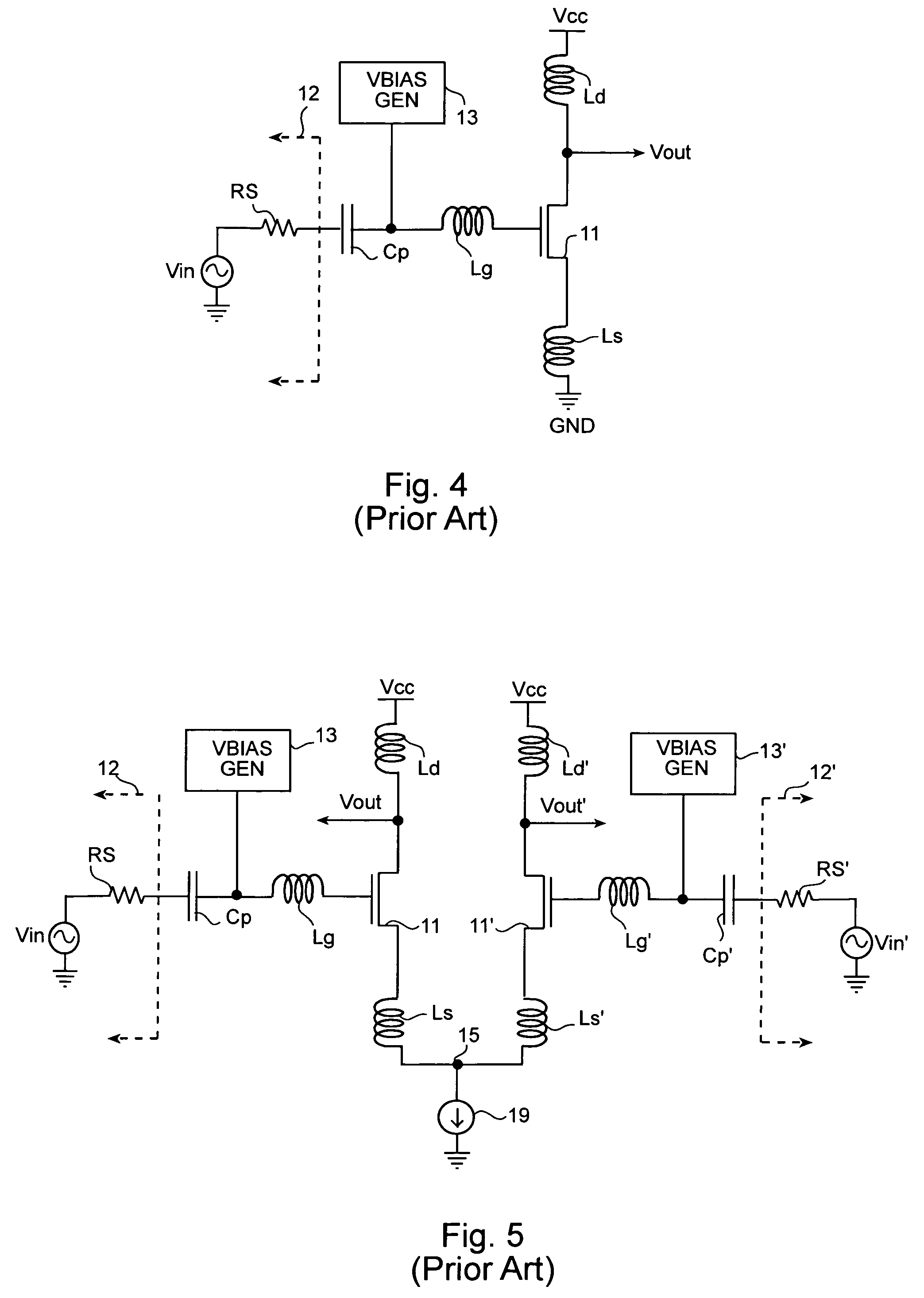

Neutralization techniques for differential low noise amplifiers

InactiveUS7256646B2Reducing available voltage headroomImprove isolationMultiple input and output pulse circuitsAmplifier modifications to reduce noise influenceCapacitanceLow noise

Owner:SEIKO EPSON CORP

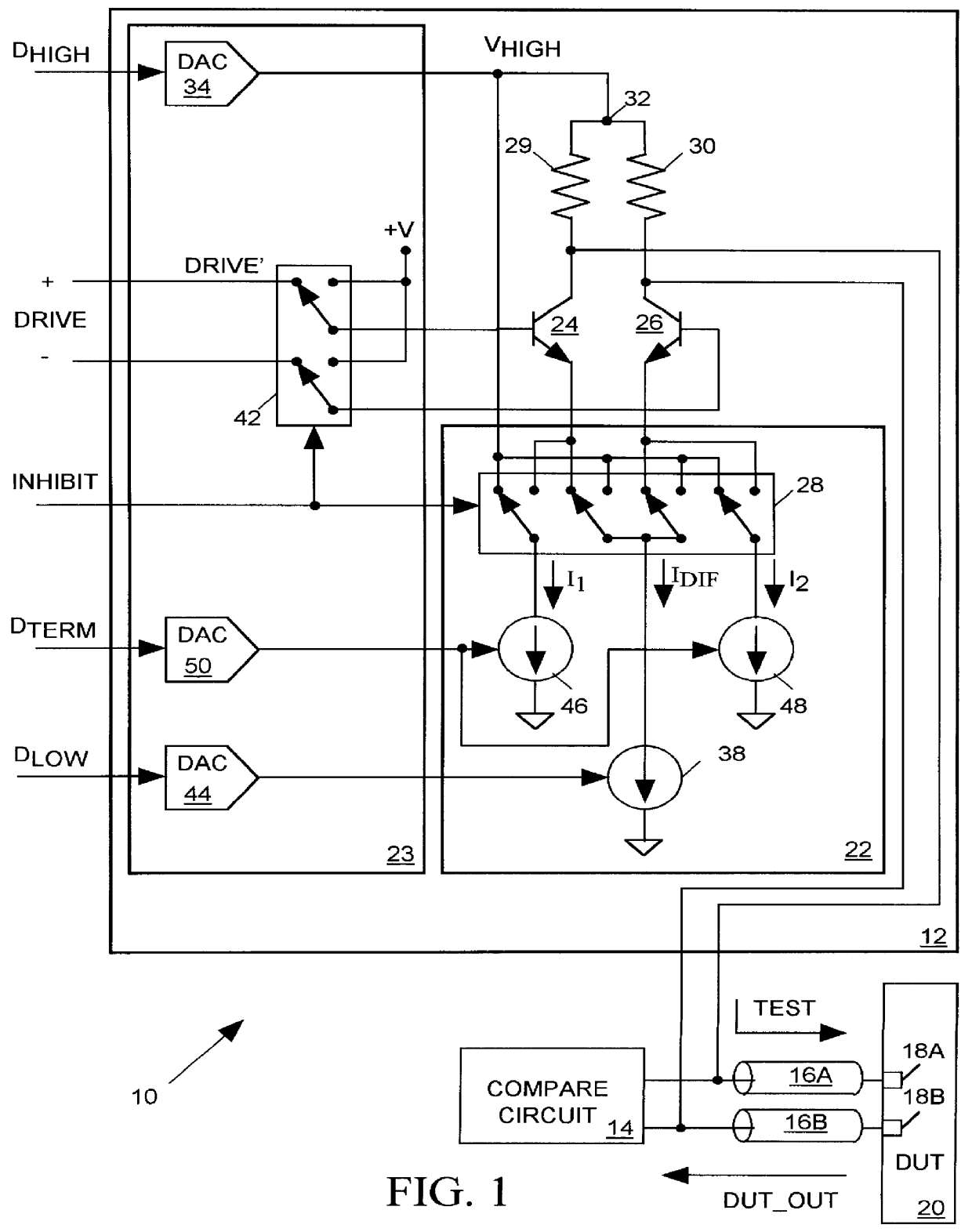

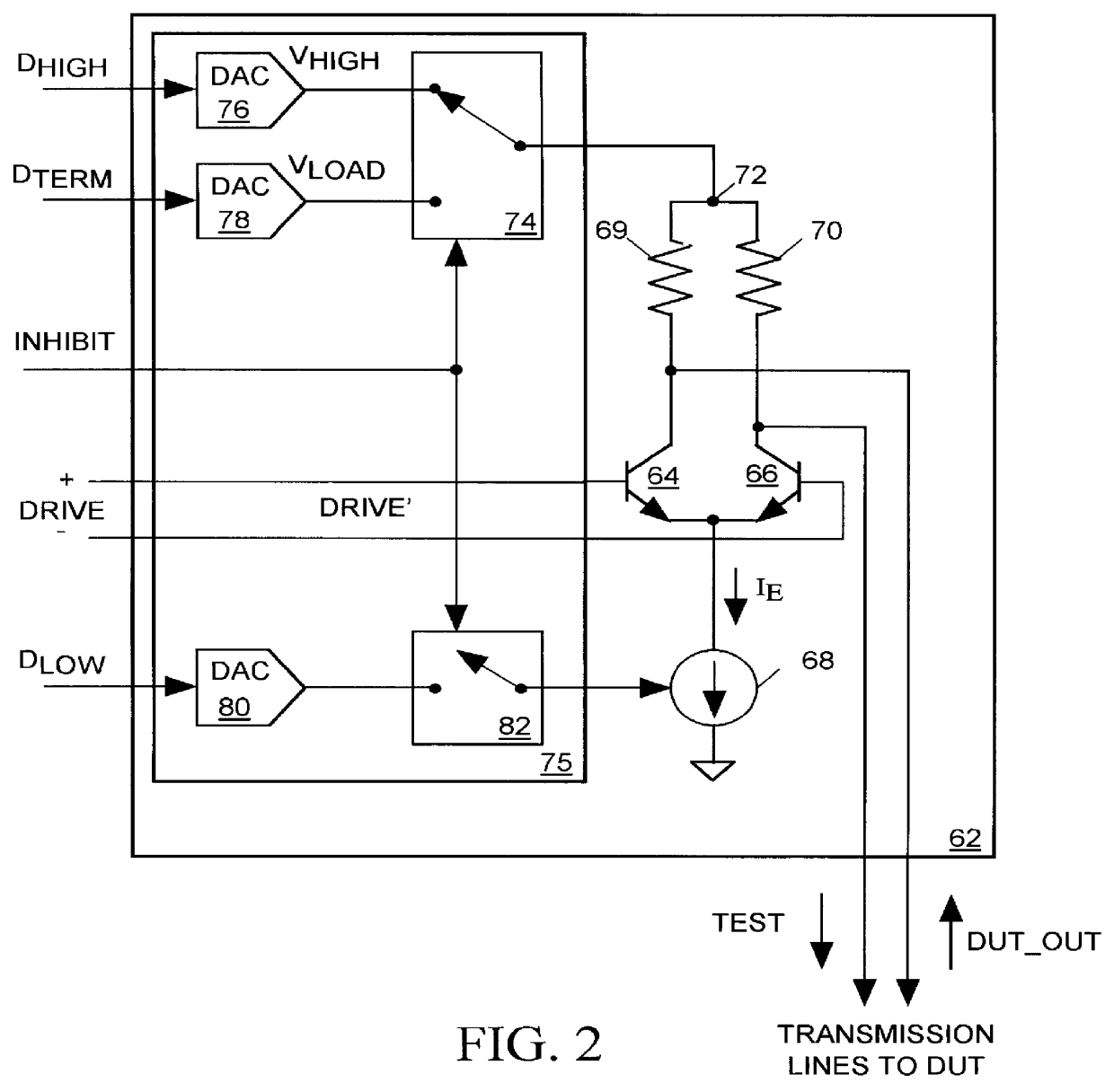

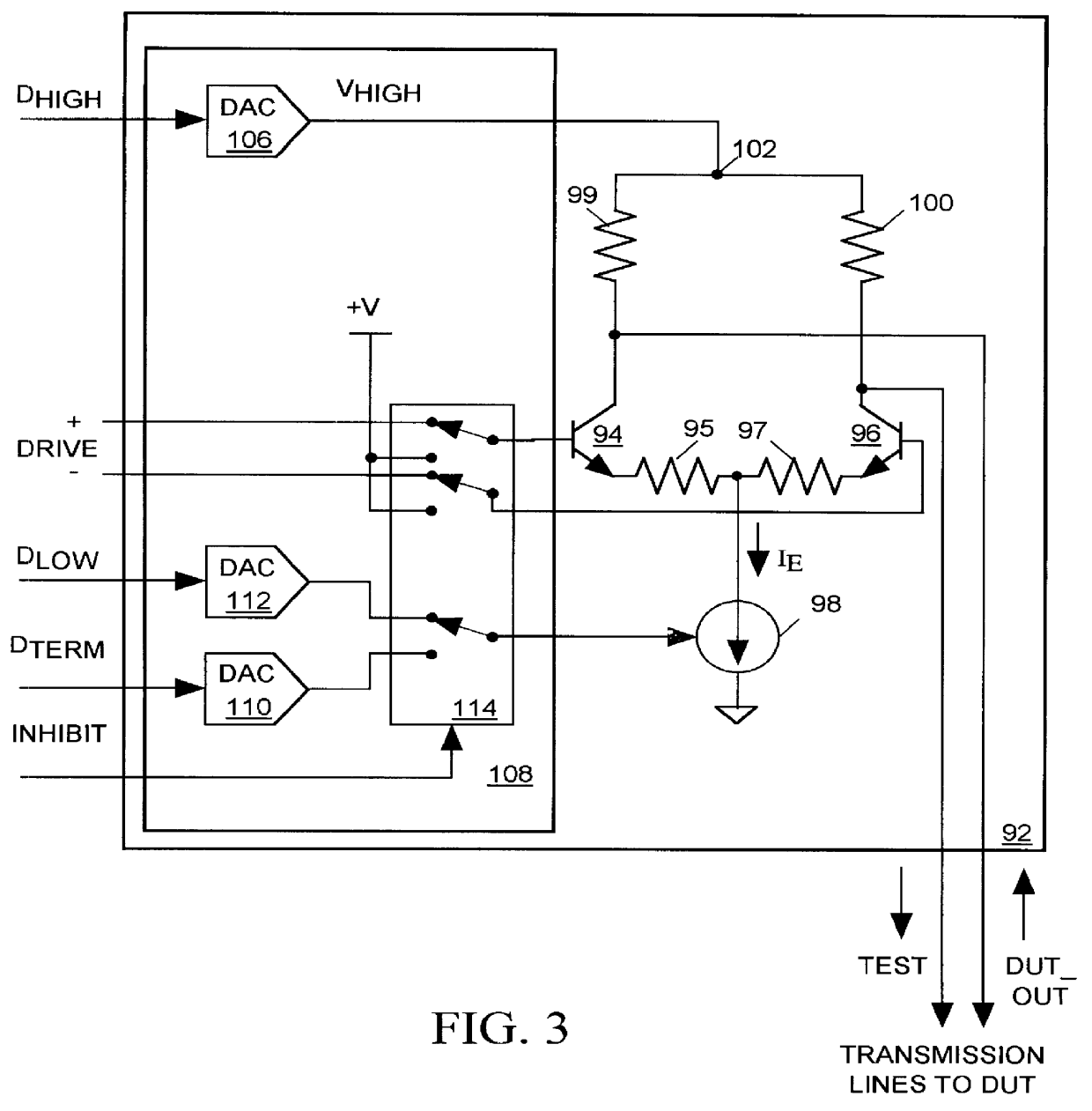

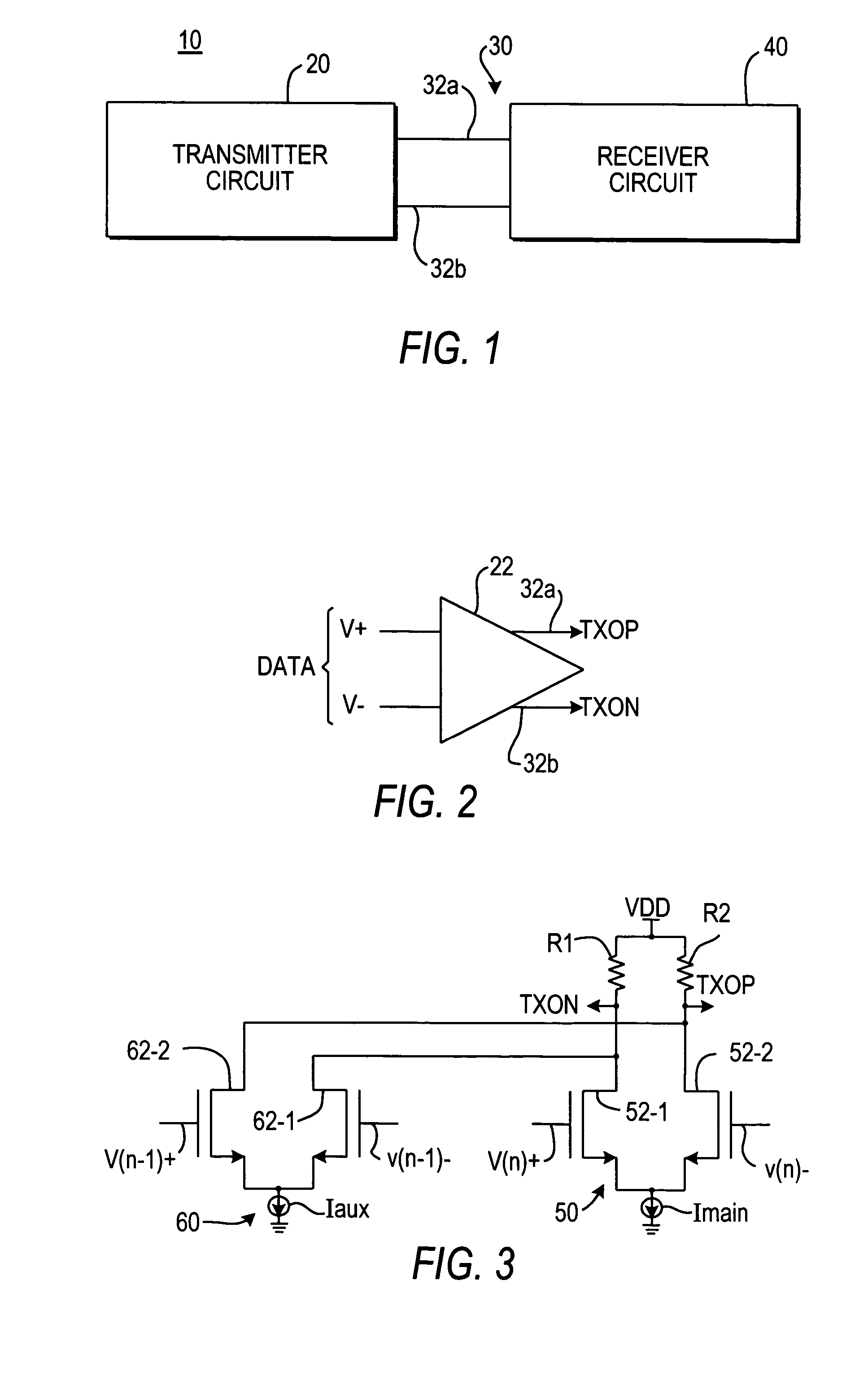

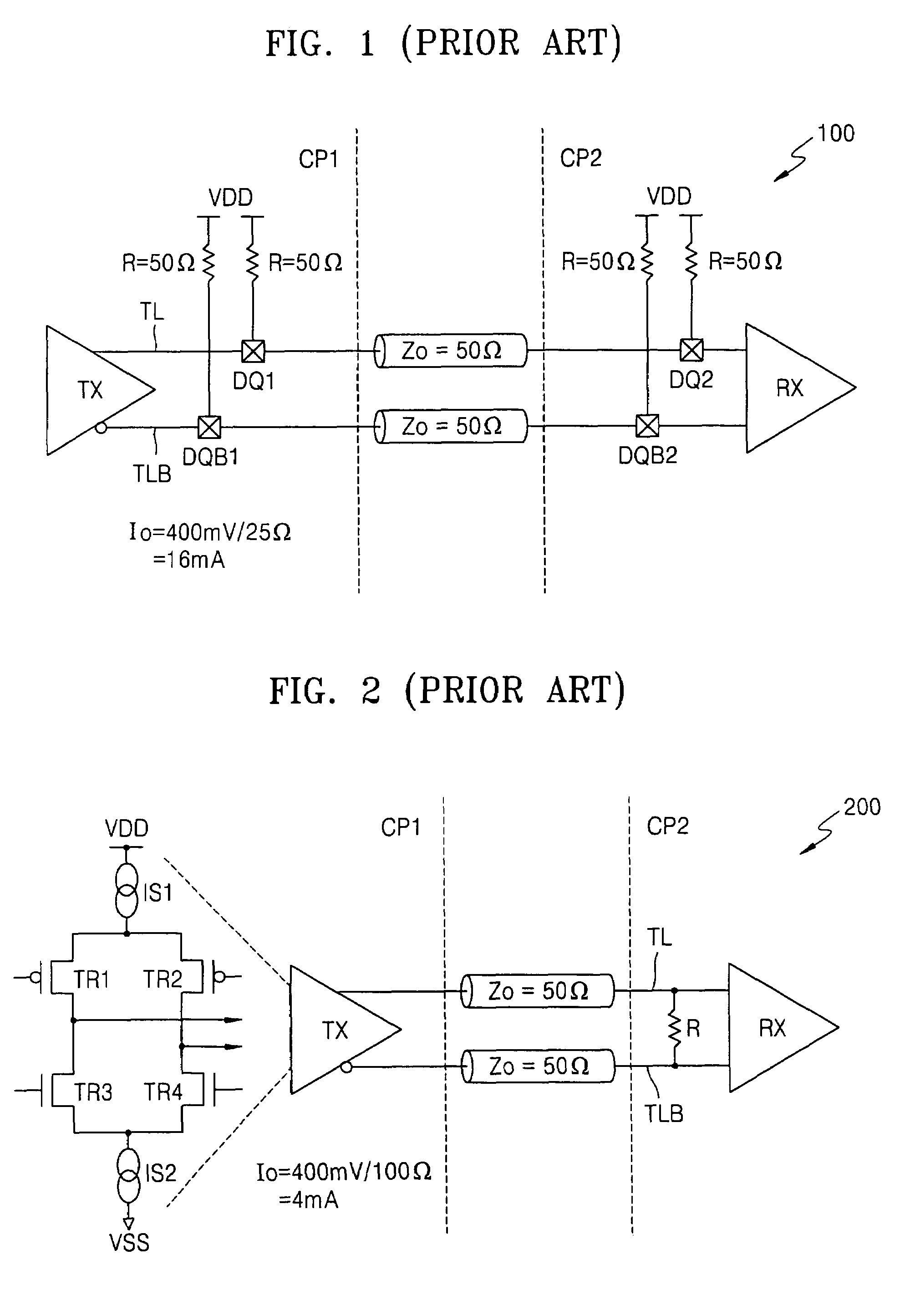

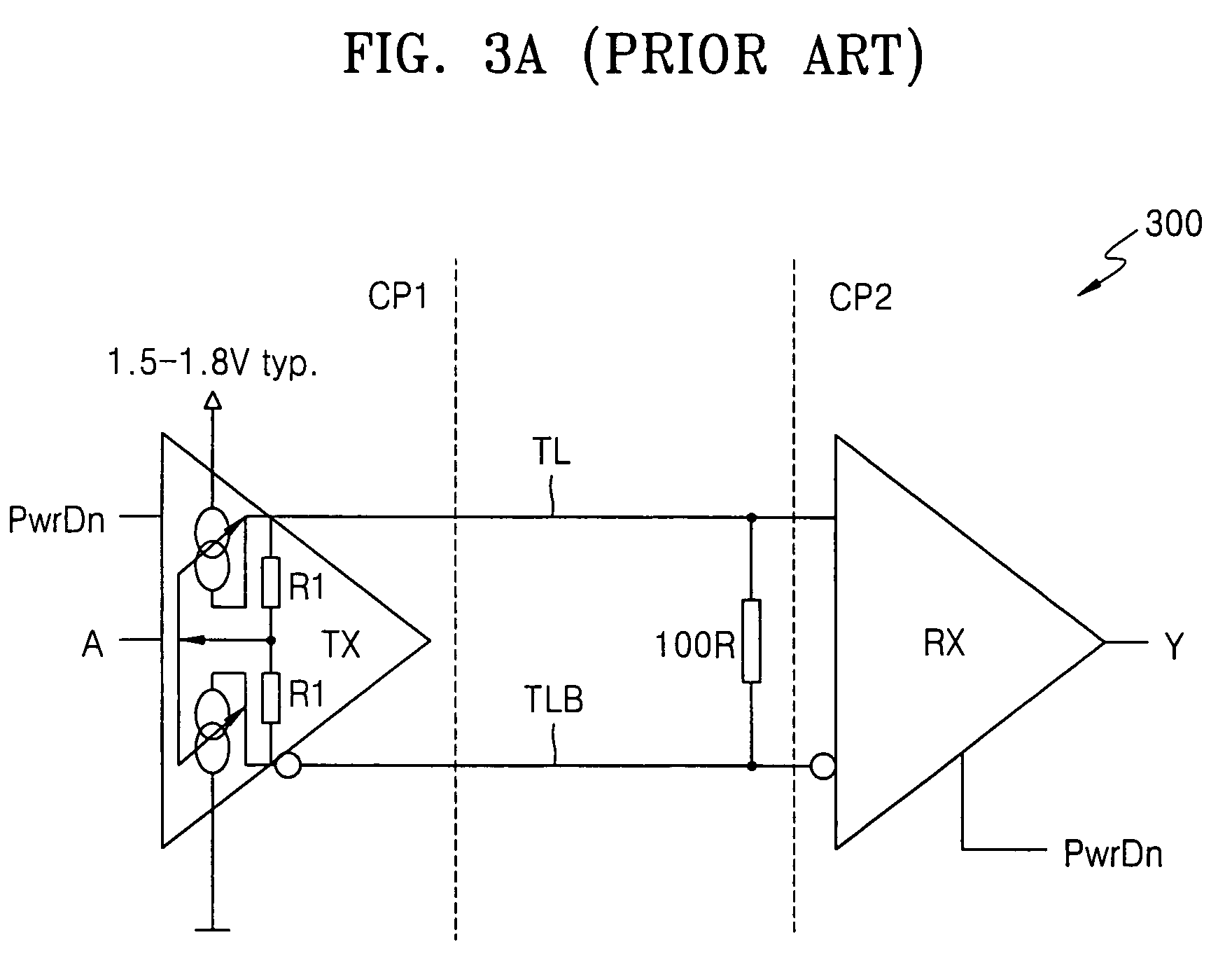

Inhibitable continuously-terminated differential drive circuit for an integrated circuit tester

InactiveUS6057716AMinimal noiseQuick switchReliability increasing modificationsDigital circuit testingDriver circuitCharacteristic impedance

A drive circuit for an integrated circuit tester operates in either a drive mode of a termination mode. In the drive mode, the drive circuit supplies a differential test signal to an integrated circuit device under test (DUT) via a pair of transmission lines. In its termination mode, the drive circuit terminates the transmission lines with their characteristic impedances and provides an adjustable load to a DUT output signal appearing on the transmission lines.

Owner:XCERRA

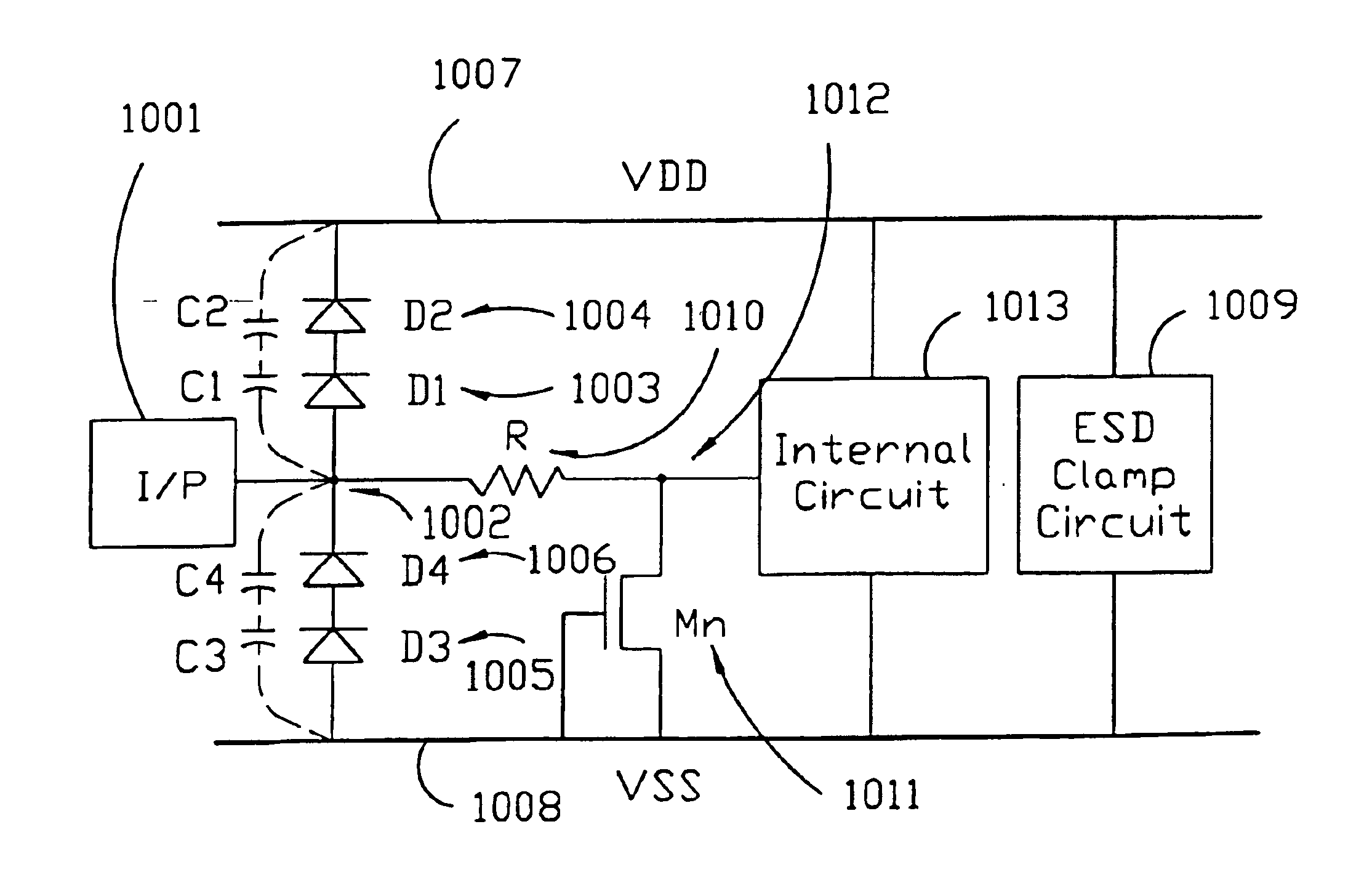

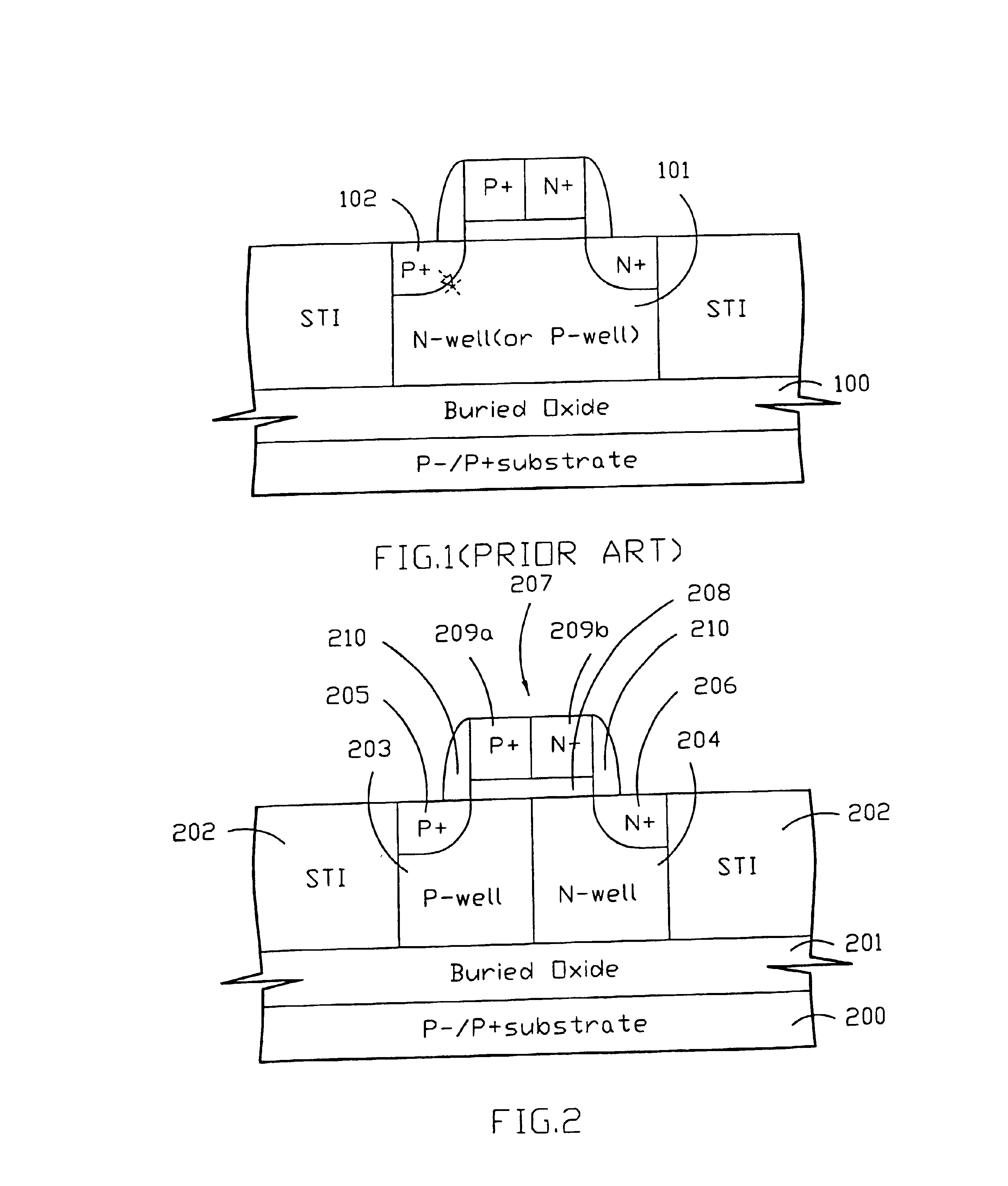

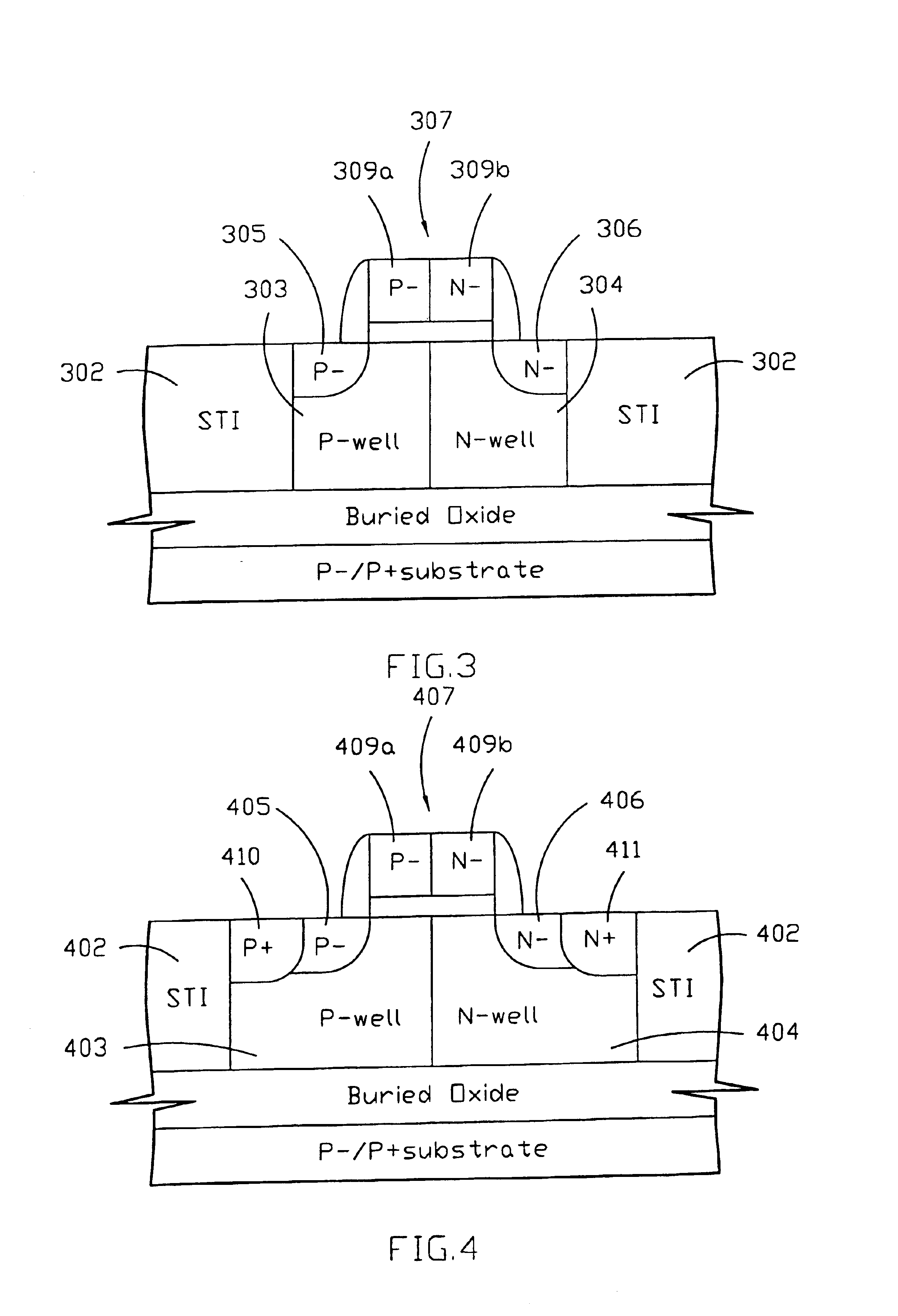

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6861680B2Reduce power densityHigh protection levelTransistorSolid-state devicesCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially-depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

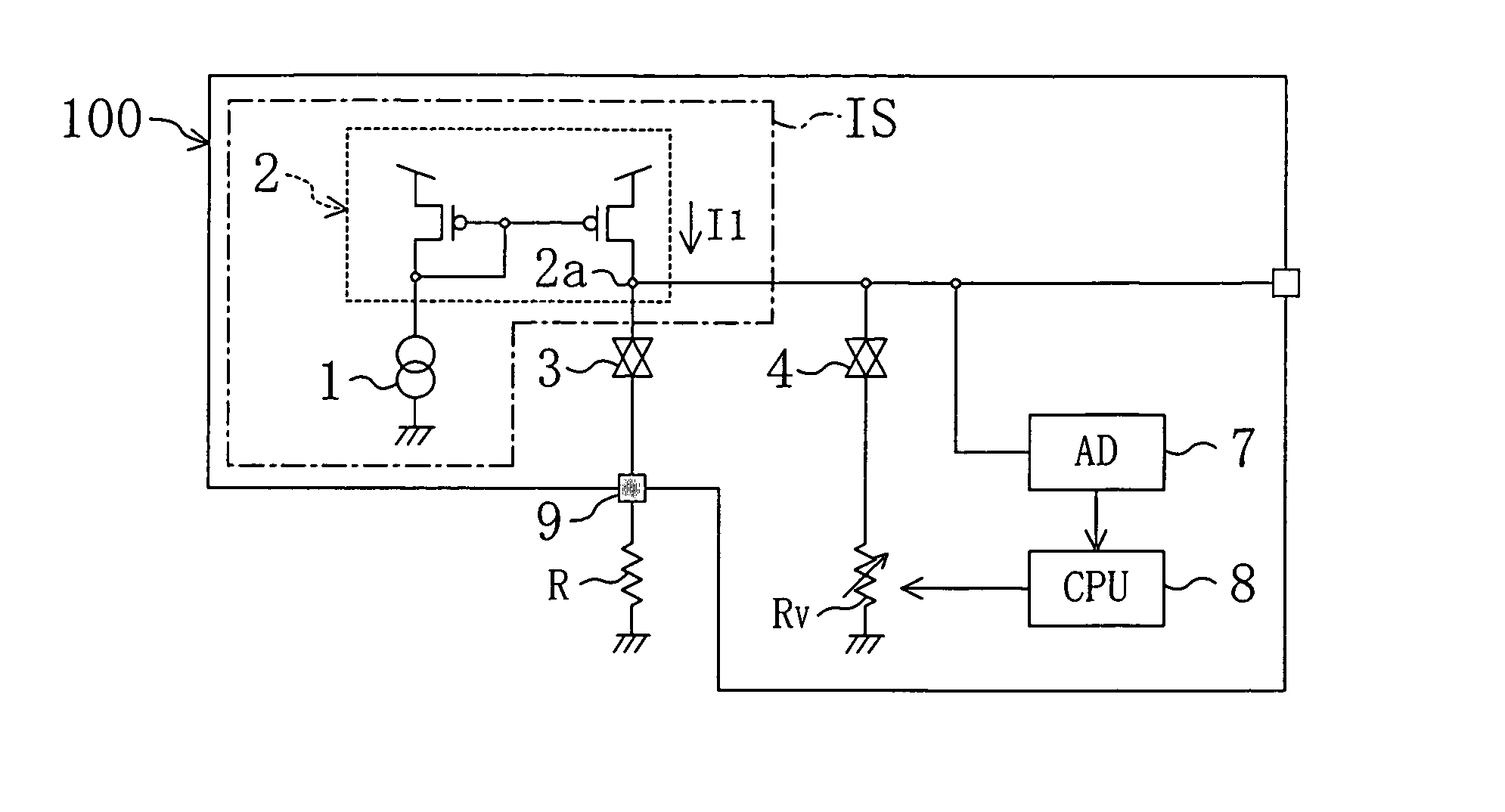

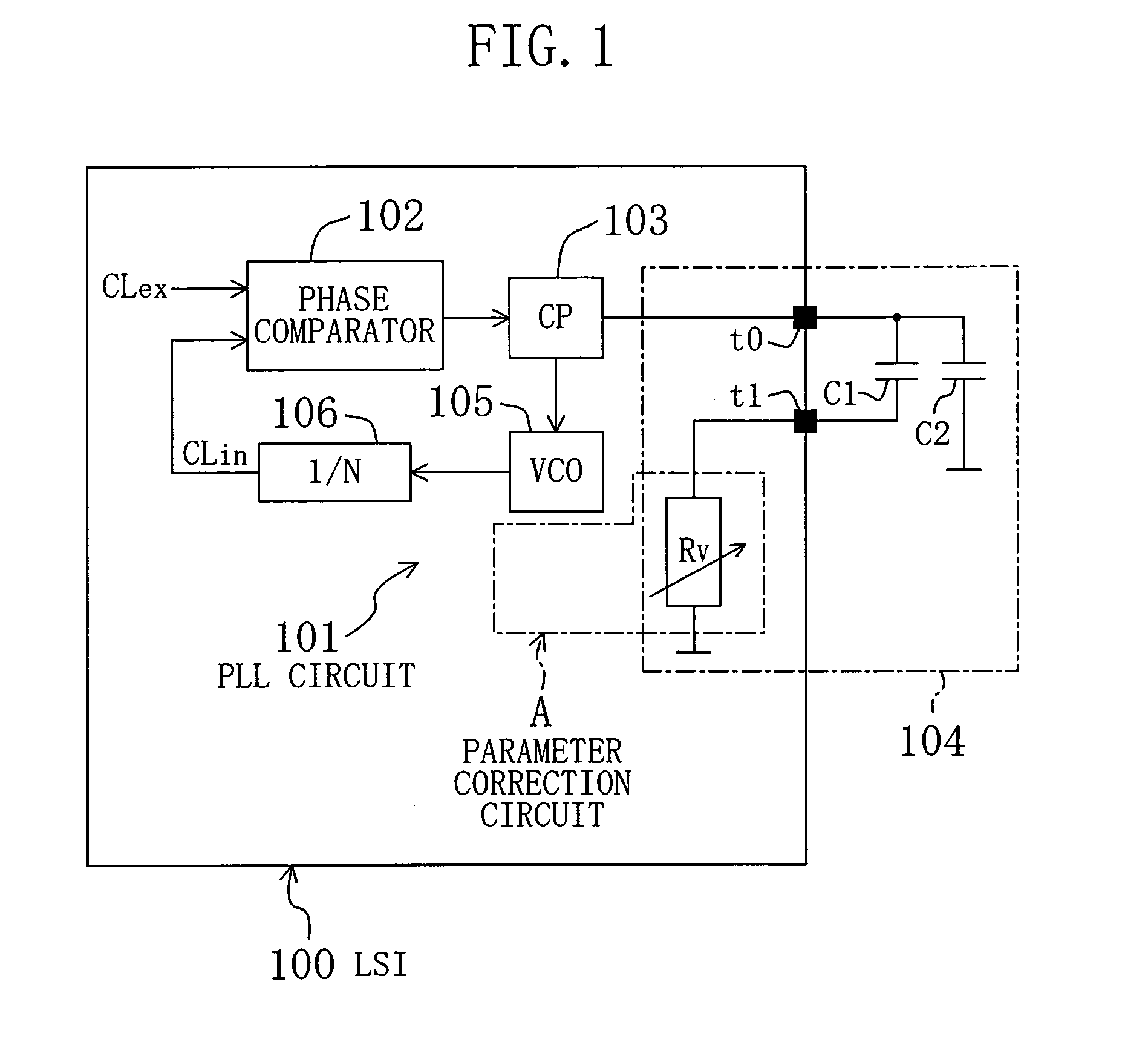

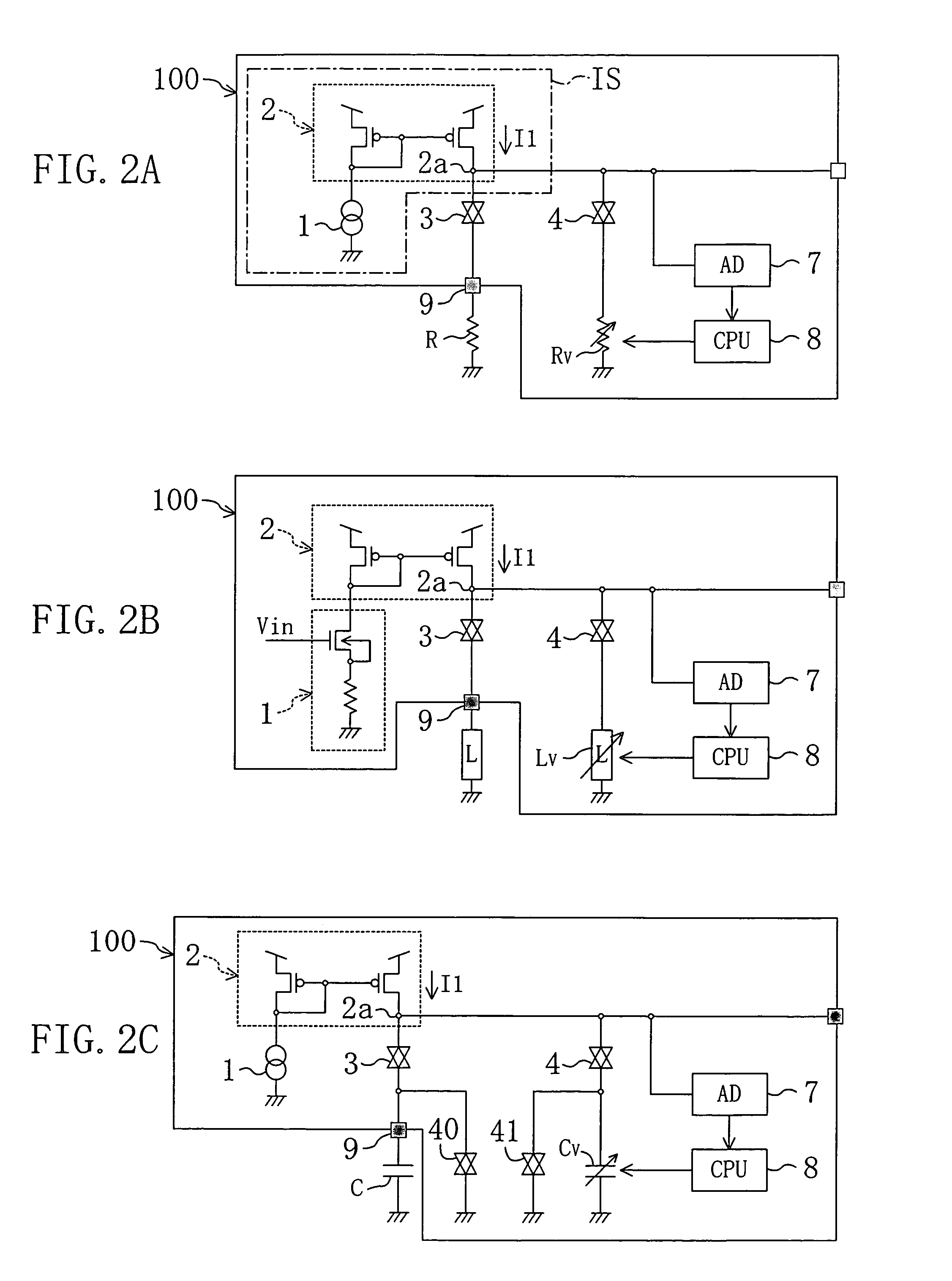

Parameter correction circuit and parameter correction method

InactiveUS7152009B2Improve accuracyAccurately carry-outAmplifier modifications to reduce noise influencePulse automatic controlElectrical resistance and conductanceValue set

In a parameter correction circuit in an LSI, a reference resistor element with high precision having a resistance value set to a target value is connected to an external terminal of the LSI. A constant current from a mirror circuit connected to a current supply flows through the reference resistor element. A voltage value generated in the reference resistor element is measured by a voltage measuring circuit. The constant current also flows through a variable resistor element. The resistance value of the variable resistor element is adjusted so that a voltage generated in the variable resistor element corresponds to the voltage generated by the reference resistor element.

Owner:PANASONIC CORP

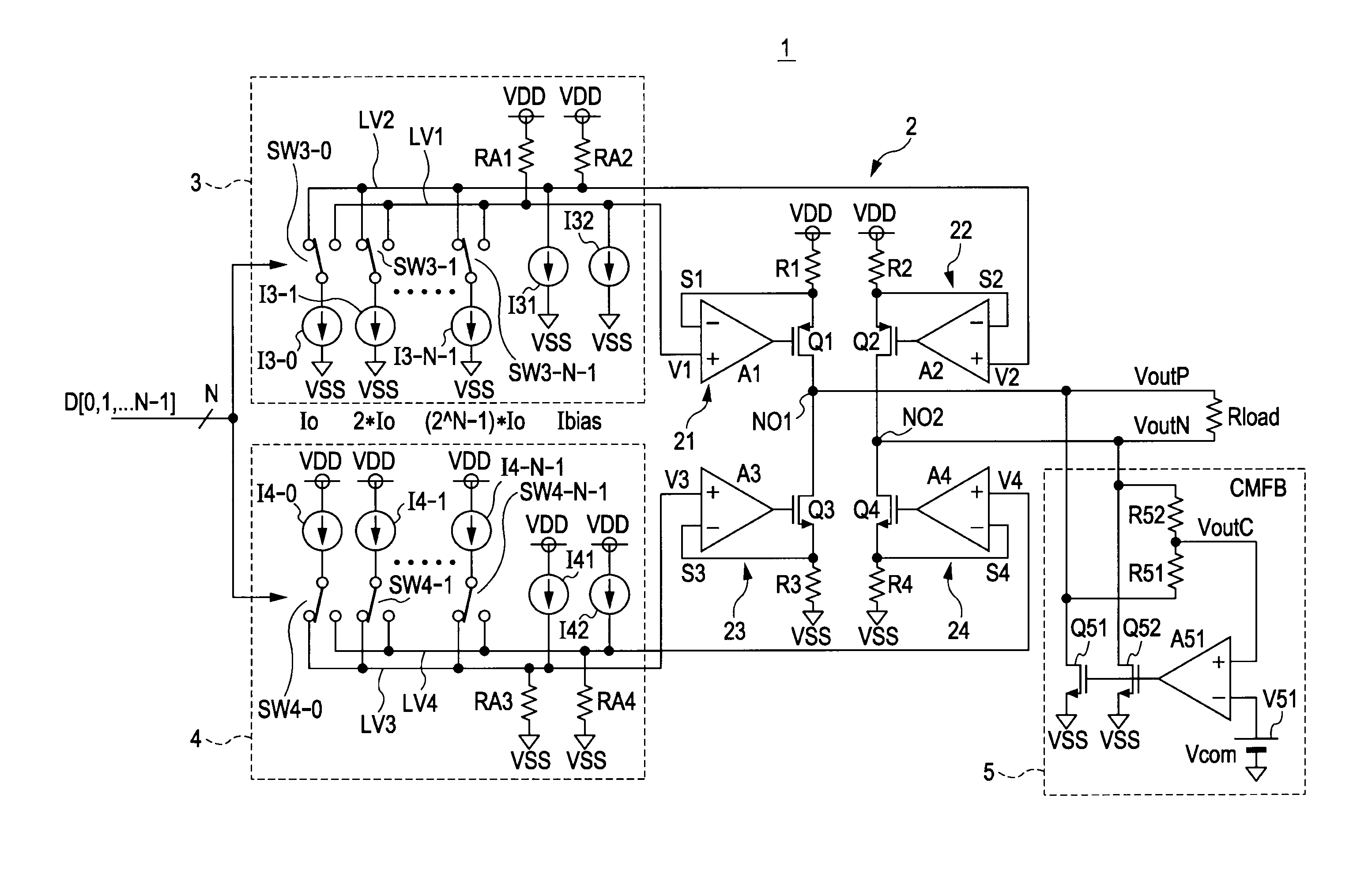

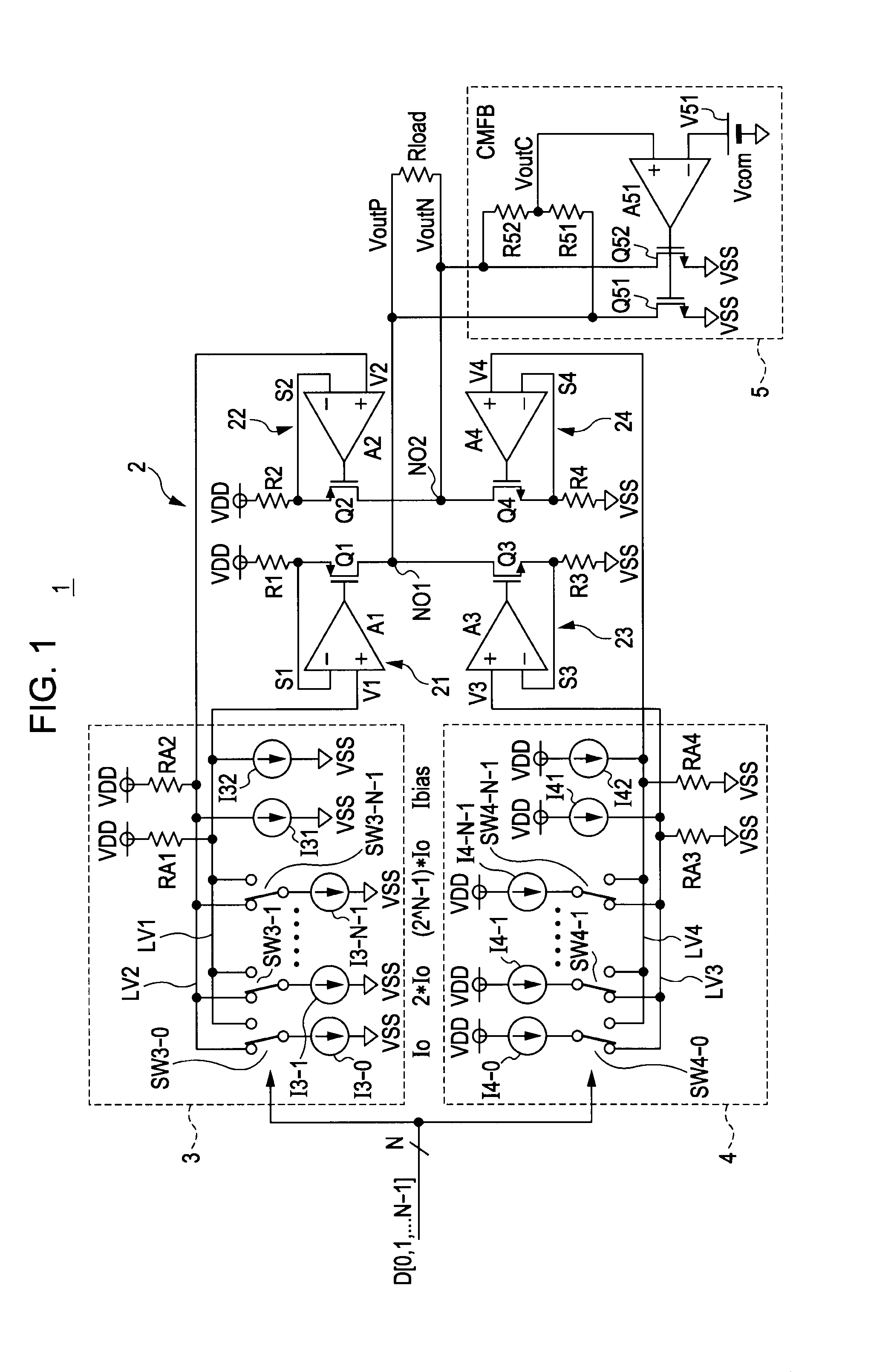

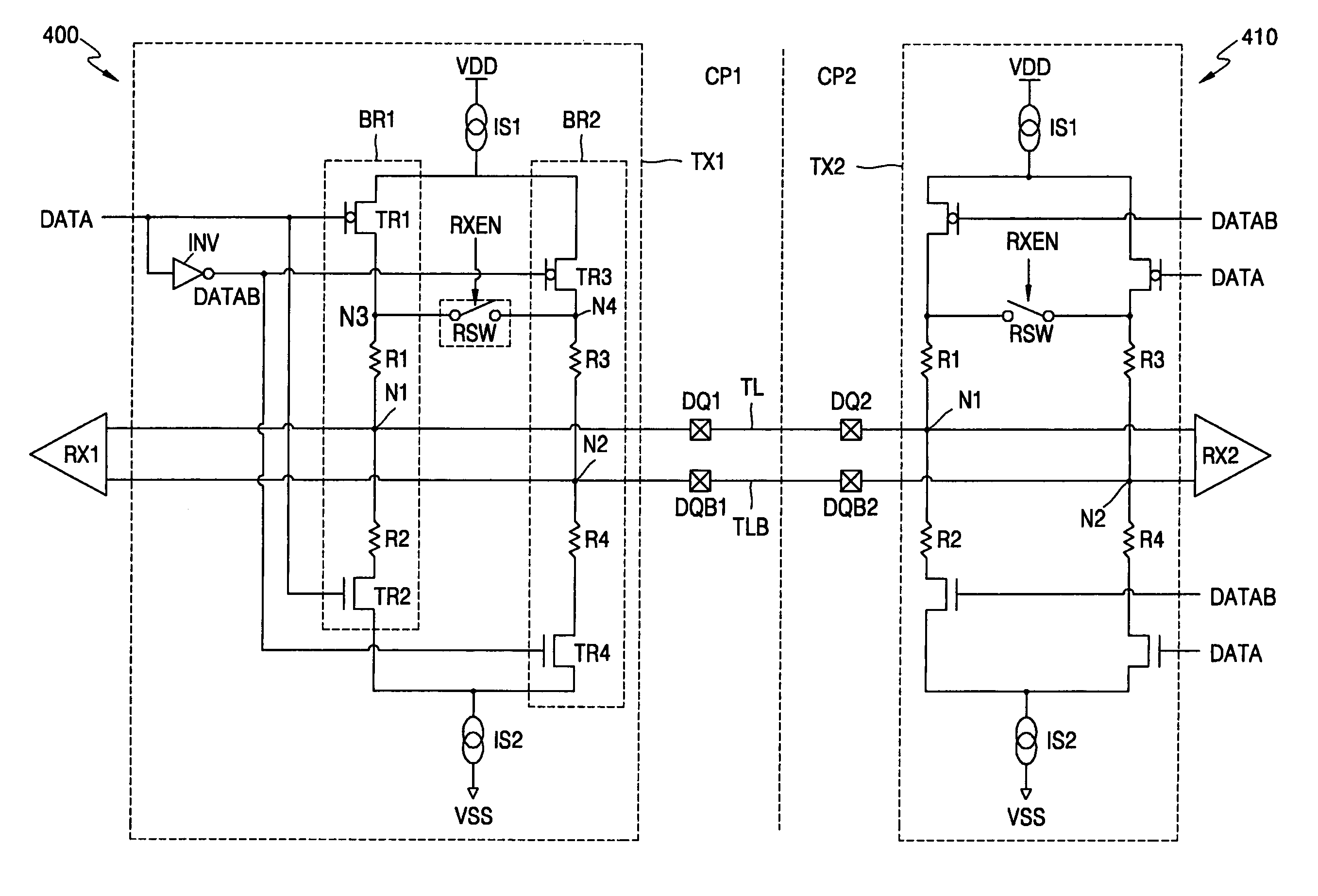

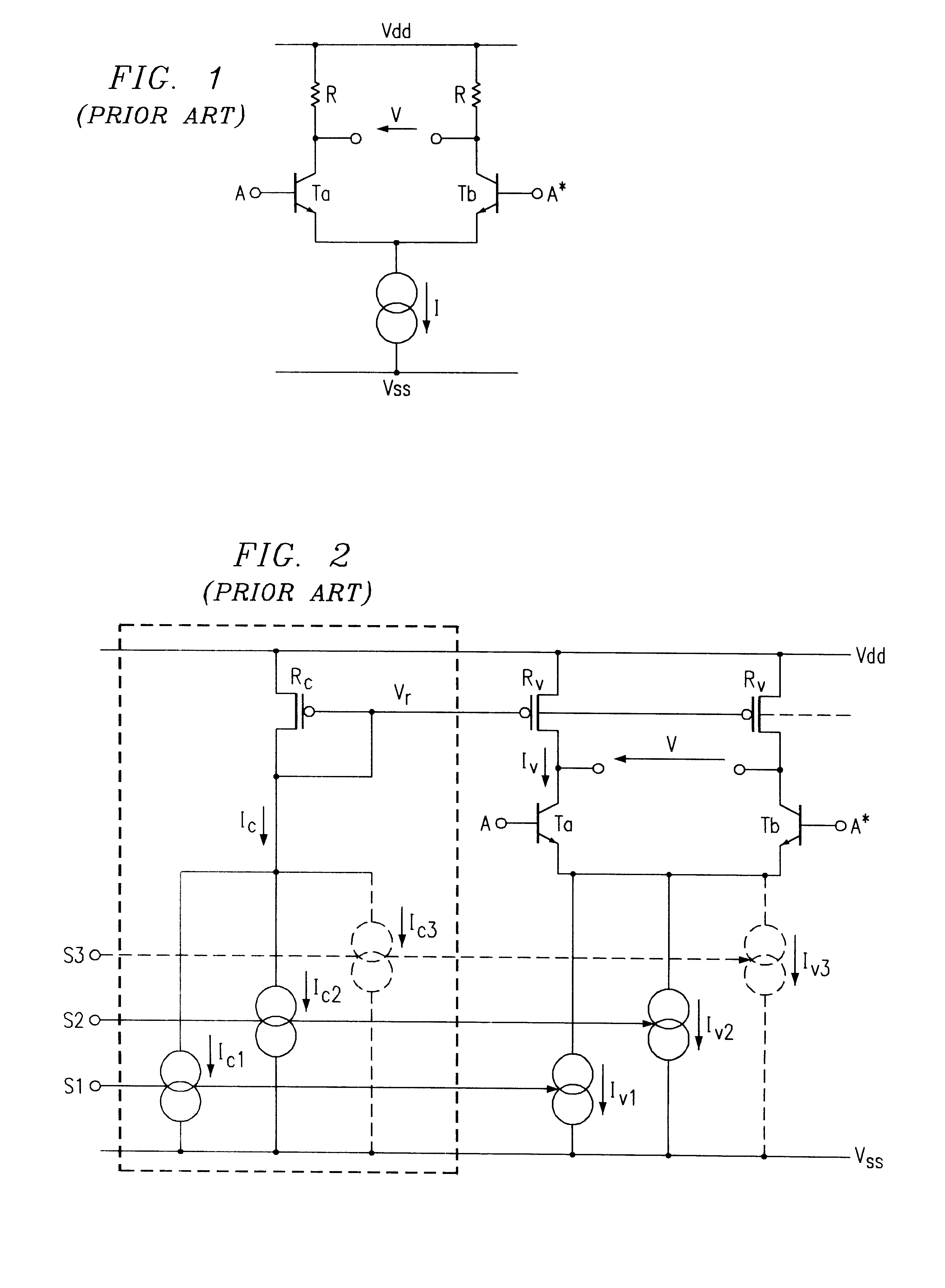

Differential drive circuit and communication device

InactiveUS20090140778A1Increase the number ofSmall sizeAnalogue/digital conversionAmplifier with semiconductor-devices/discharge-tubesLoad resistanceField-effect transistor

A differential drive circuit includes at least a first or second drive system. The first drive system has first and second field effect transistors, first and second resistors, and first and second circuits controlling the source voltages of the first and second field effect transistors to equal first and second drive target voltages, the first and second field effect transistors having sources connected to a power potential via the first and second resistors, respectively. The second drive system has third and fourth field effect transistors, third and fourth resistors, and third and fourth circuits controlling the source voltages of the third and fourth field effect transistors to equal third and fourth drive target voltages, the third and fourth field effect transistors having sources connected to a reference potential via the third and fourth resistors, respectively. A common-mode voltage is driven to form a constant differential signal across a load resistance.

Owner:SONY CORP

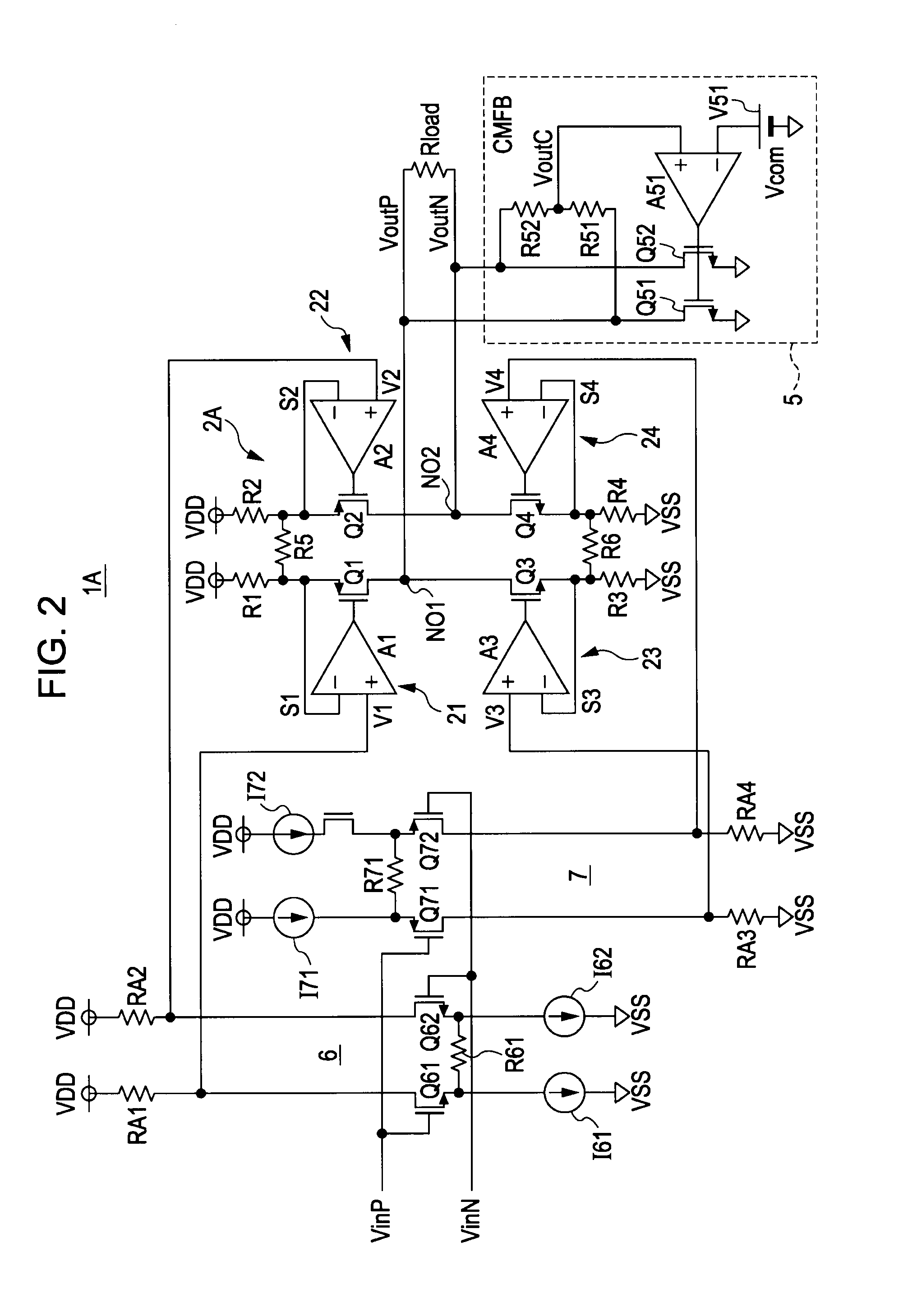

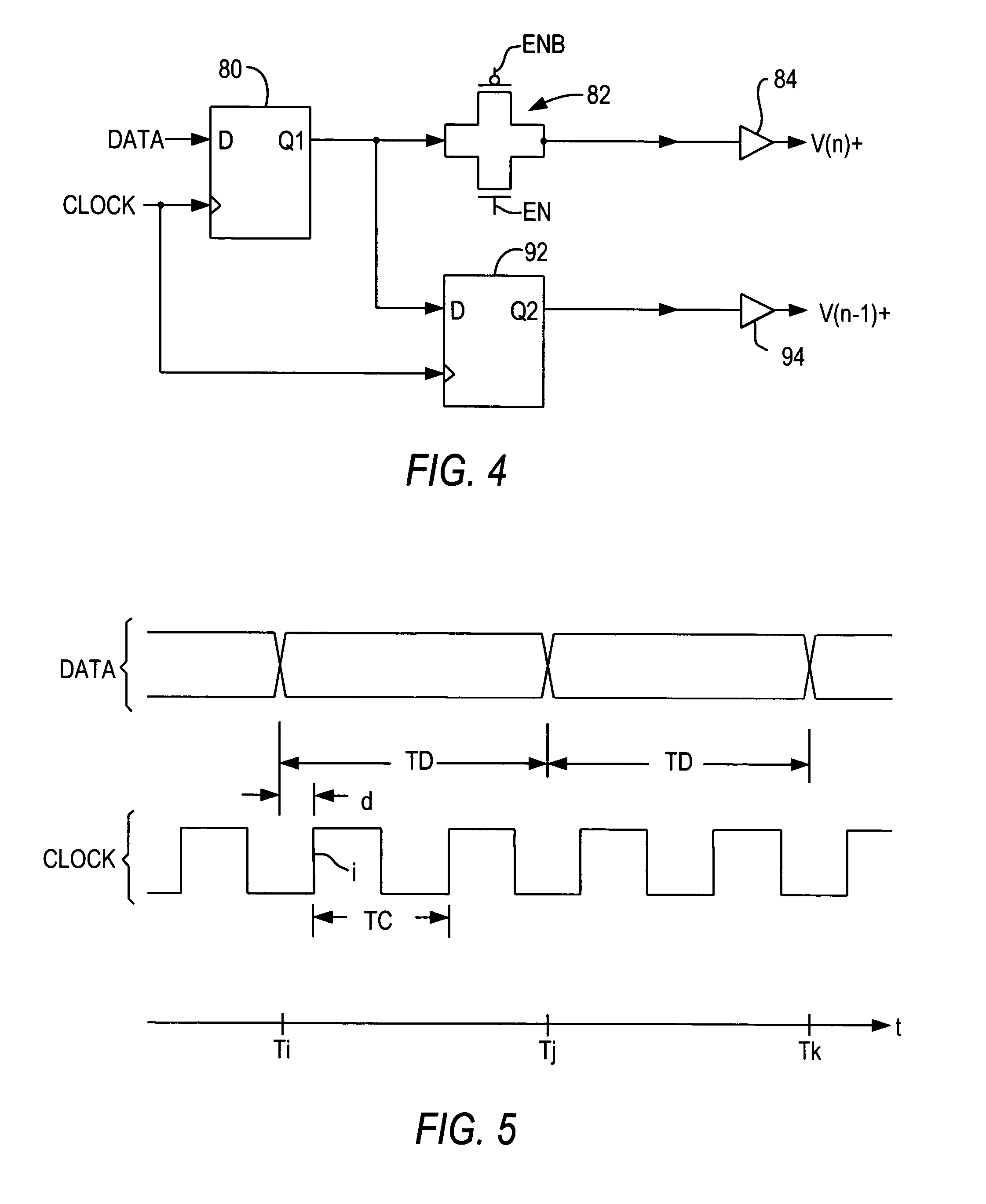

Pre-emphasis circuitry and methods

ActiveUS6956407B2Multiple input and output pulse circuitsPulse automatic controlTime delaysData signal

Pre-emphasis is given to differential output signals emanating from a pair of output nodes by initially (after an input data signal transition) connecting at least two current circuits to only one of the nodes. After a time delay, one of the current circuits is switched to connect only to the node to which the current circuits were not previously connected if there has been no further transition in the input data signal during the time delay. If only single-ended (i.e., non-differential) output is desired, only one of the output nodes is used as an output signal source. More than two current circuits may be used, and their switching from one node to the other may be performed progressively to provide pre-emphasis having any of many different characteristics.

Owner:ALTERA CORP

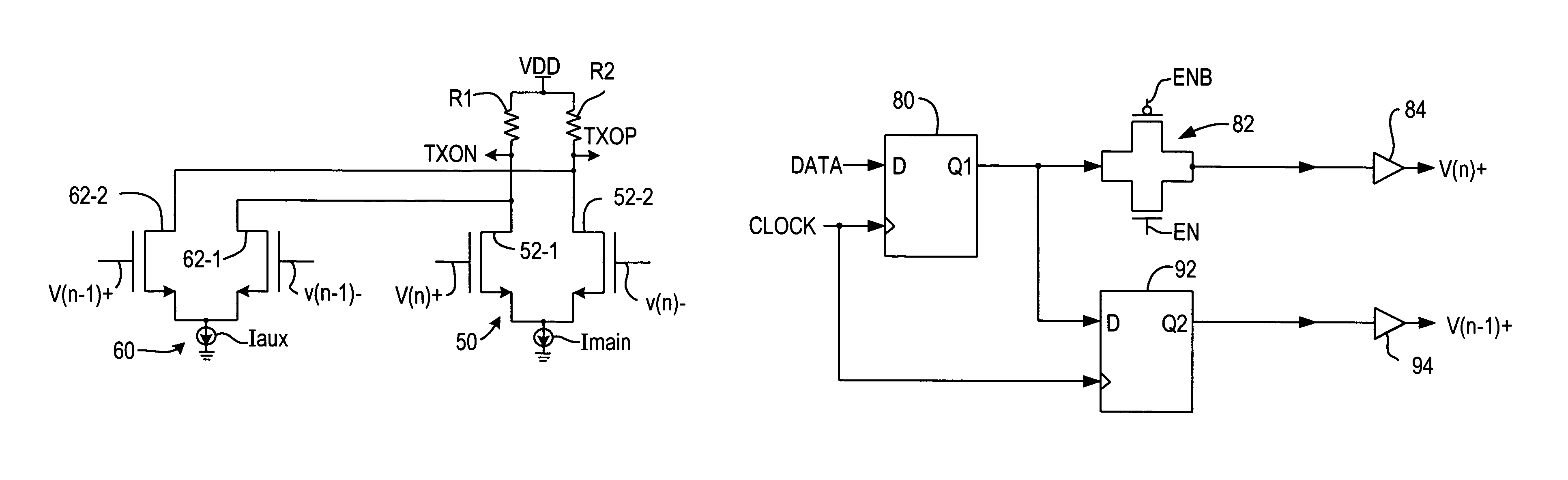

Low voltage differential signaling drivers including branches with series resistors

ActiveUS7595661B2Reduce in quantityMinimizes signal reflectionElectric pulse generatorDifferential amplifiersLow voltageResistor

A low voltage differential signal driver includes first and second current sources, a first branch and a second branch. The first branch includes at least two transistors and at least two resistors between them that are all connected in series between the first and second current sources, to define a first node between adjacent resistors that is configured to transmit and receive differential signals. The second branch also includes at least two transistors and at least two resistors between them that also are all connected in series between the first and second current sources, to define a second node between adjacent resistors that is also configured to transmit and receive differential signals.

Owner:SAMSUNG ELECTRONICS CO LTD

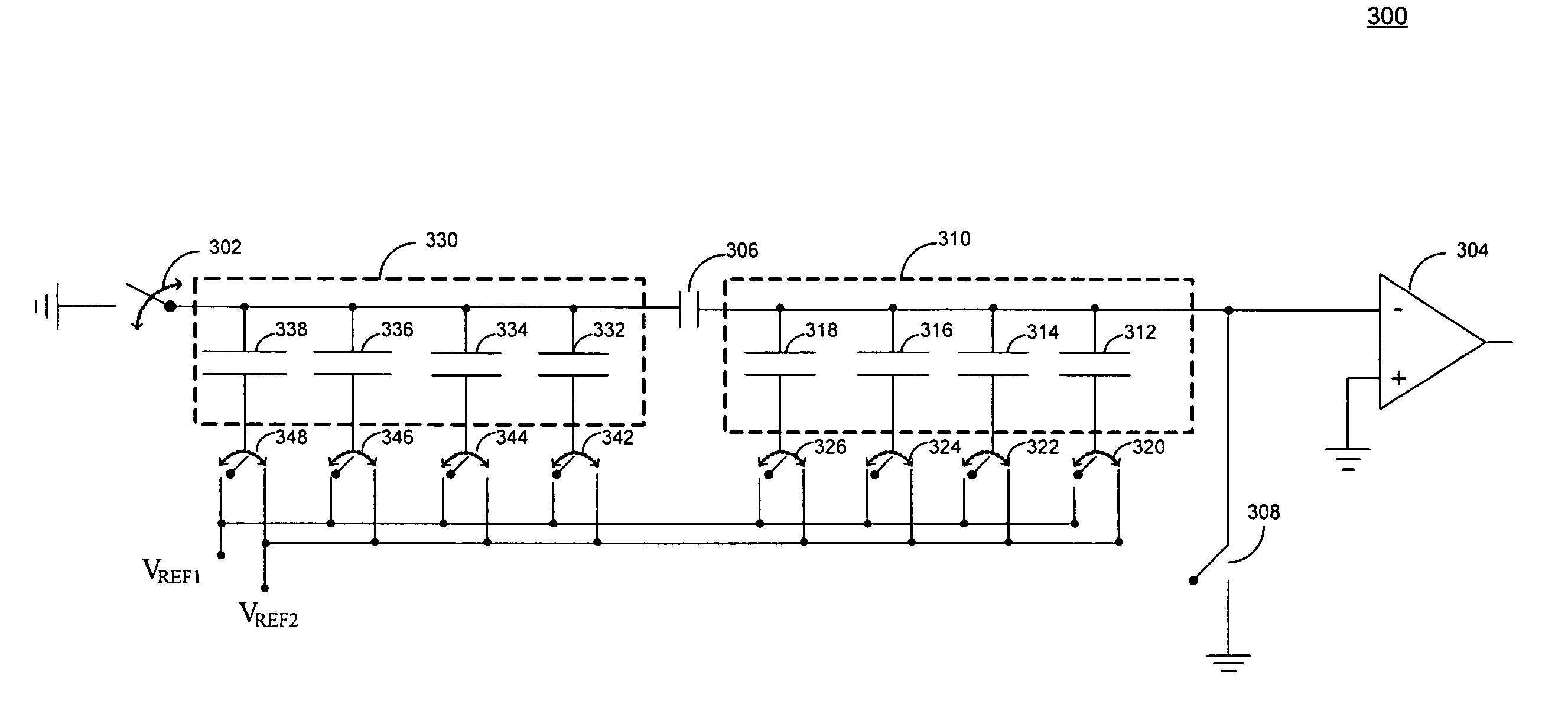

Systems and methods for characterizing component ratios and generating a digital representation of same

ActiveUS7705765B1Electric signal transmission systemsAnalogue-digital convertersAnalog signalAnalog-to-digital converter

Circuits and methods for determining component ratios are provided. An analog to digital converter circuit may include comparison capacitors arranged in an upper group and a lower group for quantizing analog signals into the digital domain. In addition to determining the lower bits during an analog to digital conversion of an input sample, the lower group of comparison capacitors may also be used during calibration mode to quantize a ratio signal that represents the capacitor mismatches of the upper group rather than using a dedicated digital-to-analog converter to perform this function.

Owner:ANALOG DEVICES INT UNLTD

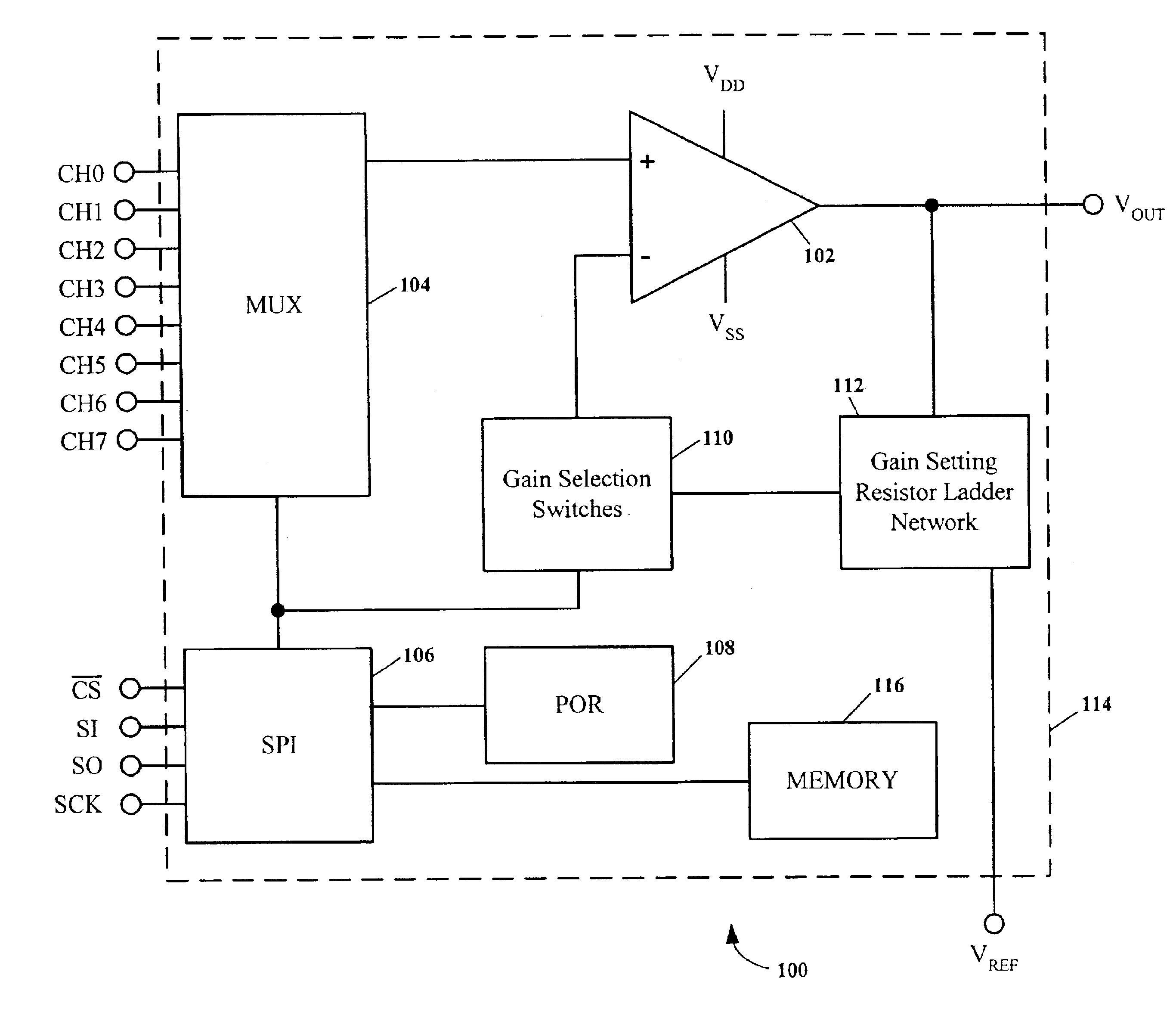

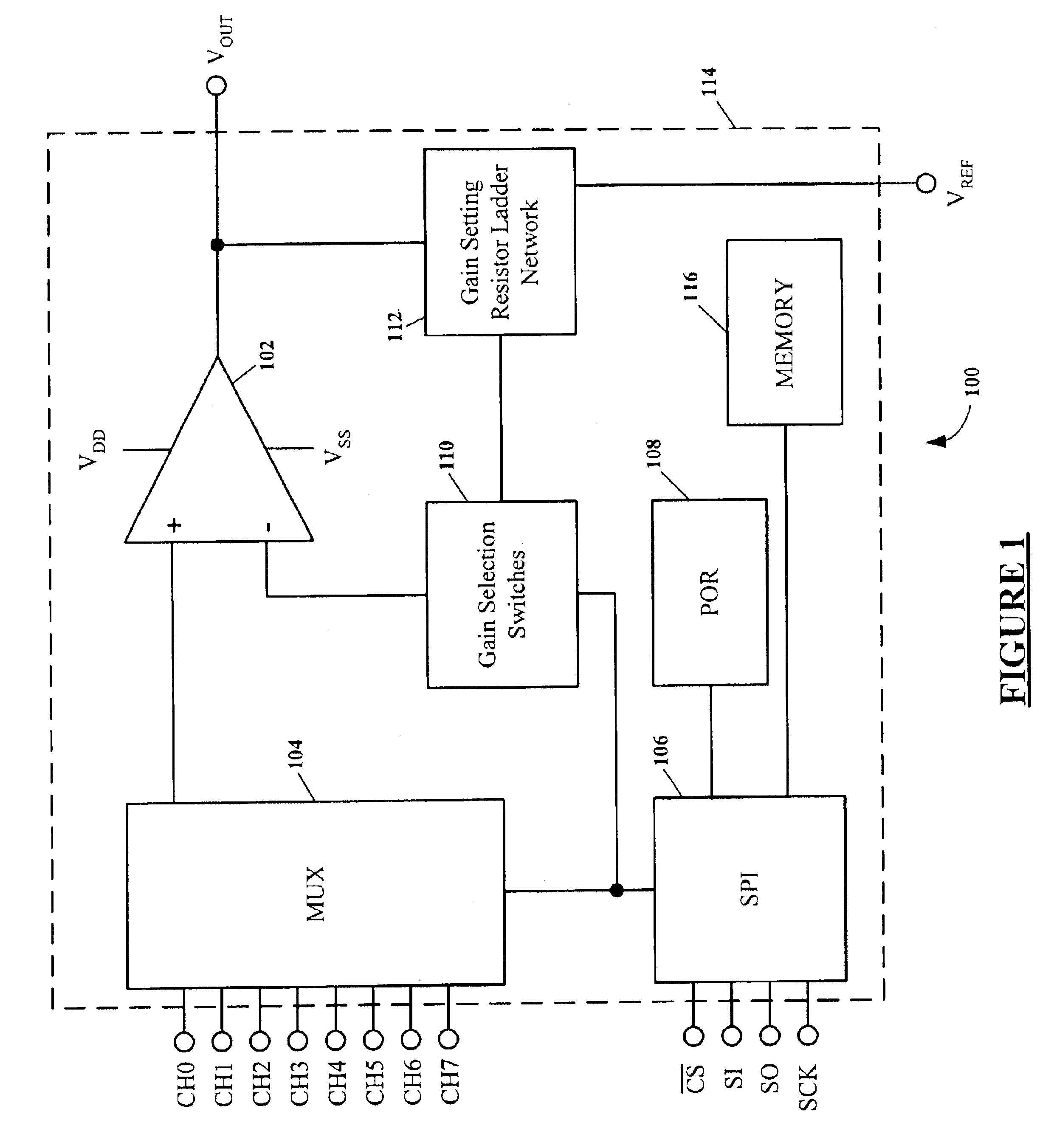

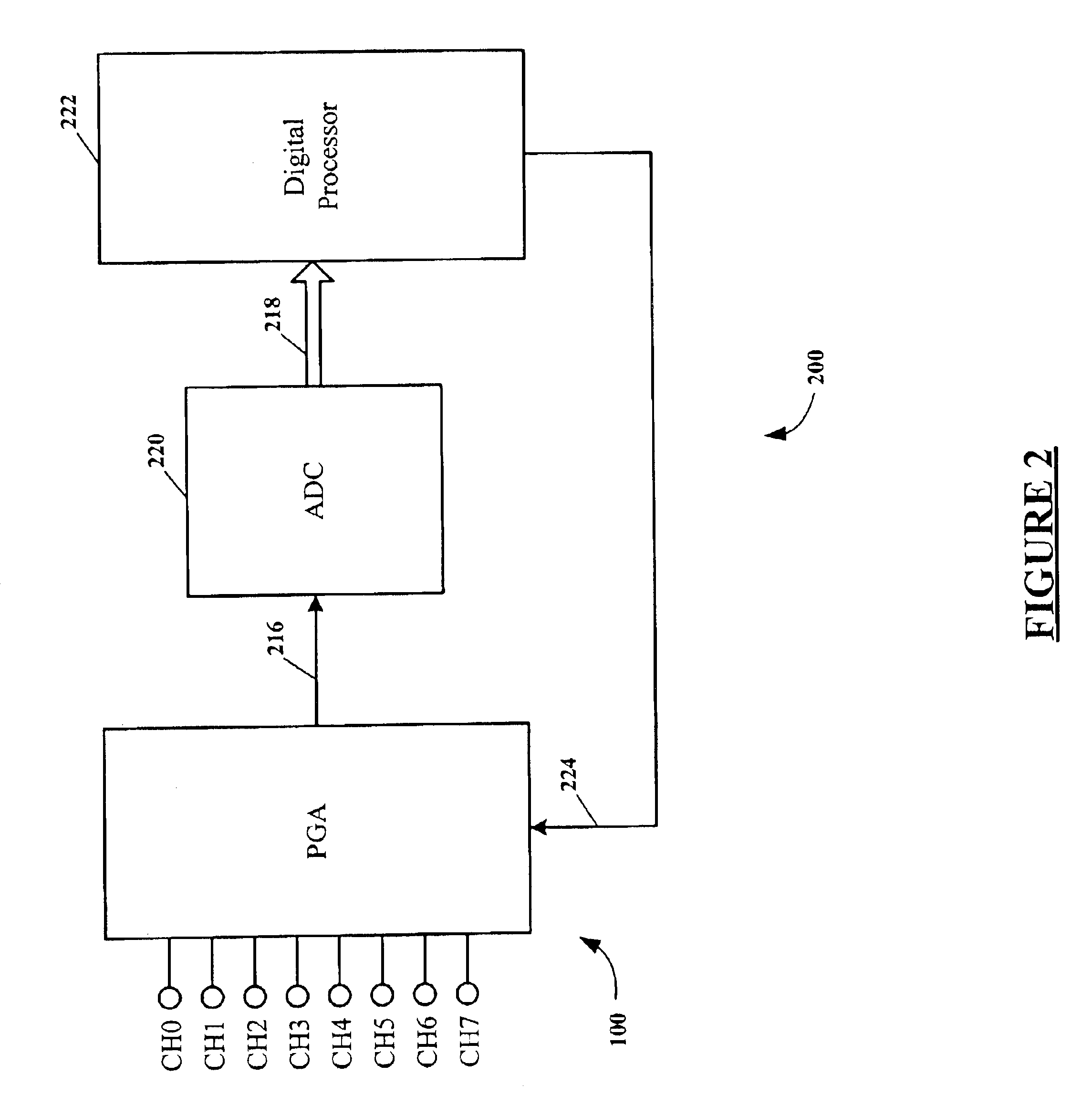

Multi-channel programmable gain amplifier controlled with a serial interface

InactiveUS6847904B2Simple interfaceAmplifier with semiconductor-devices/discharge-tubesAnalog signal digital controlMultiplexerProgrammable-gain amplifier

Owner:MICROCHIP TECH INC

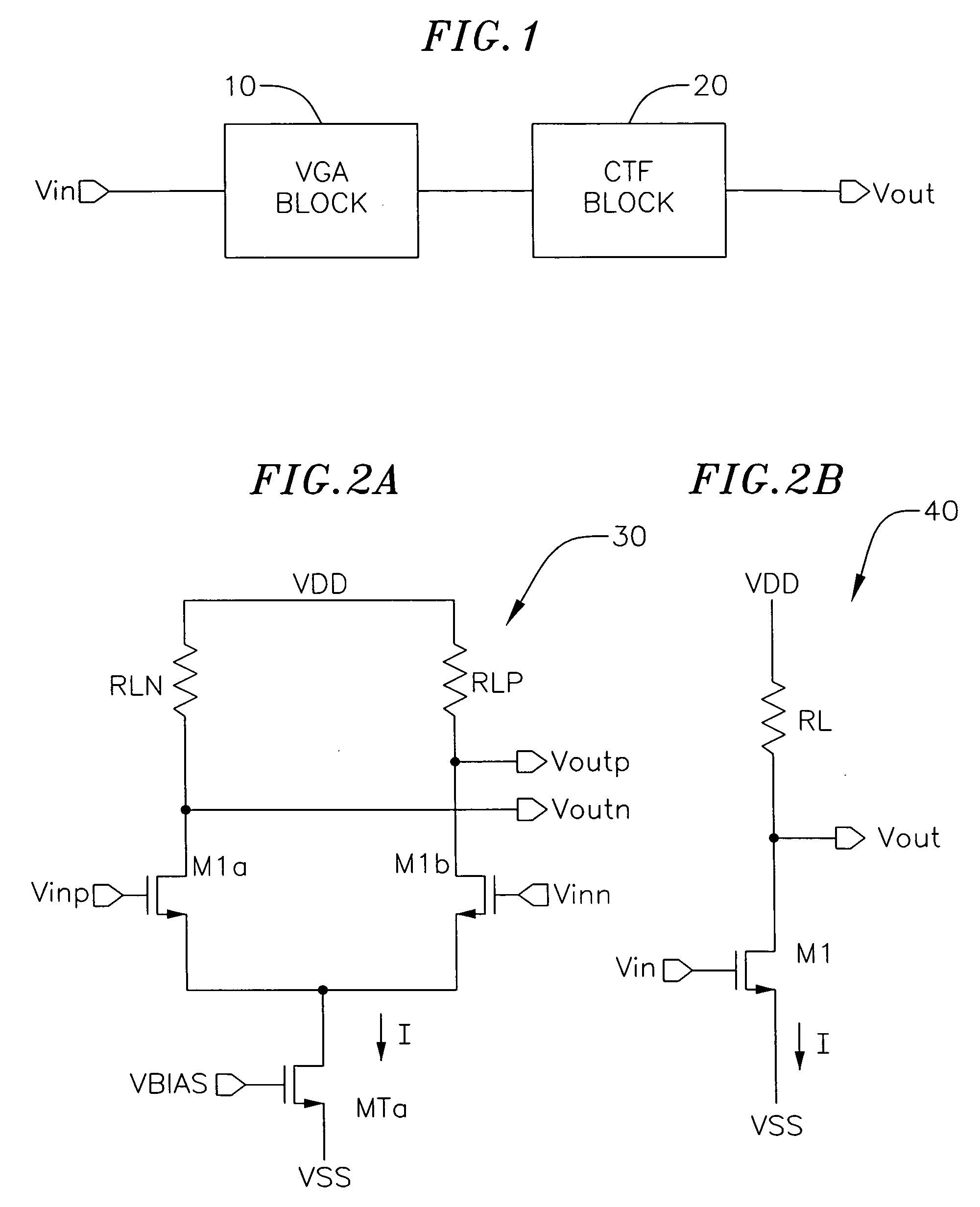

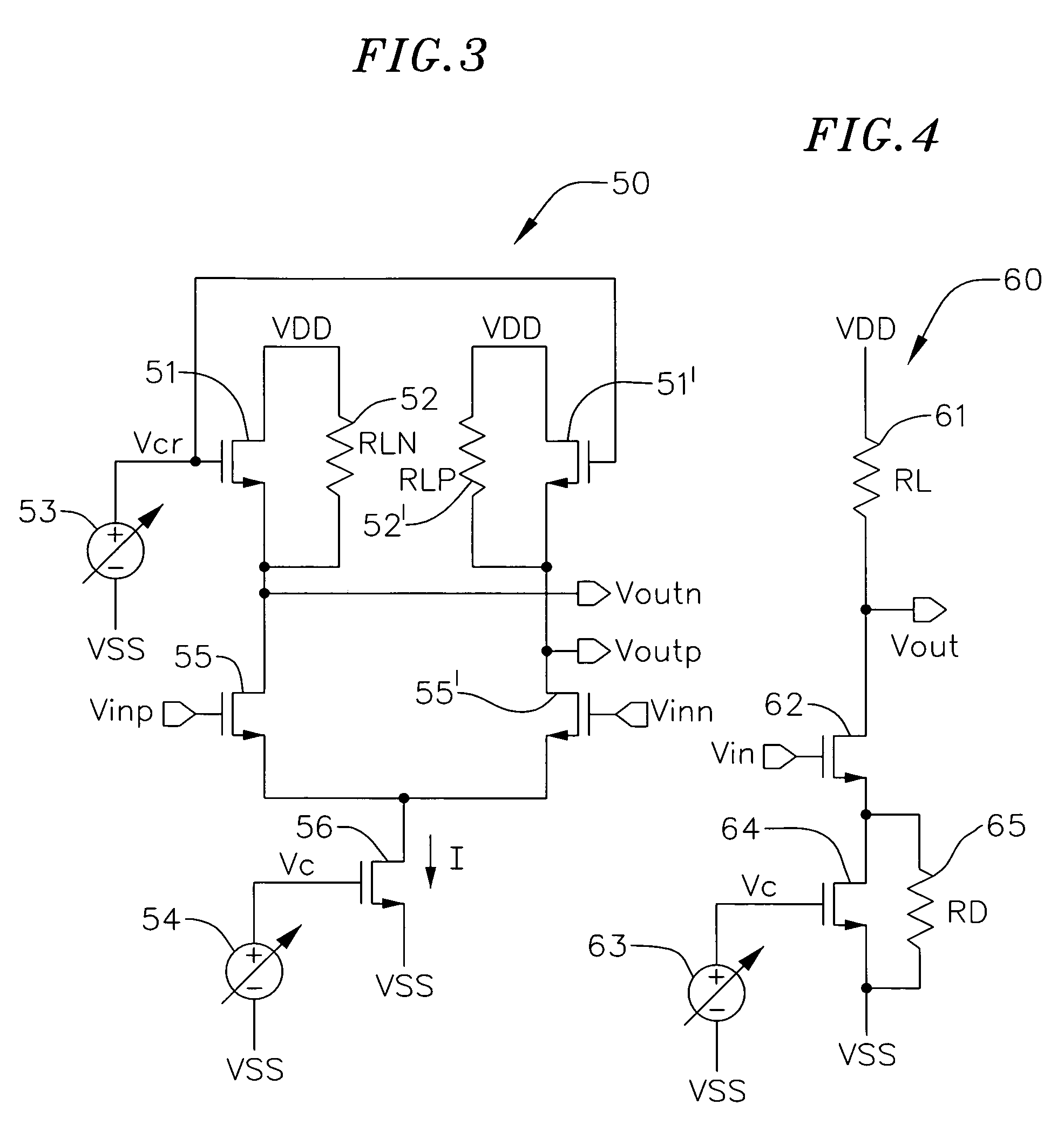

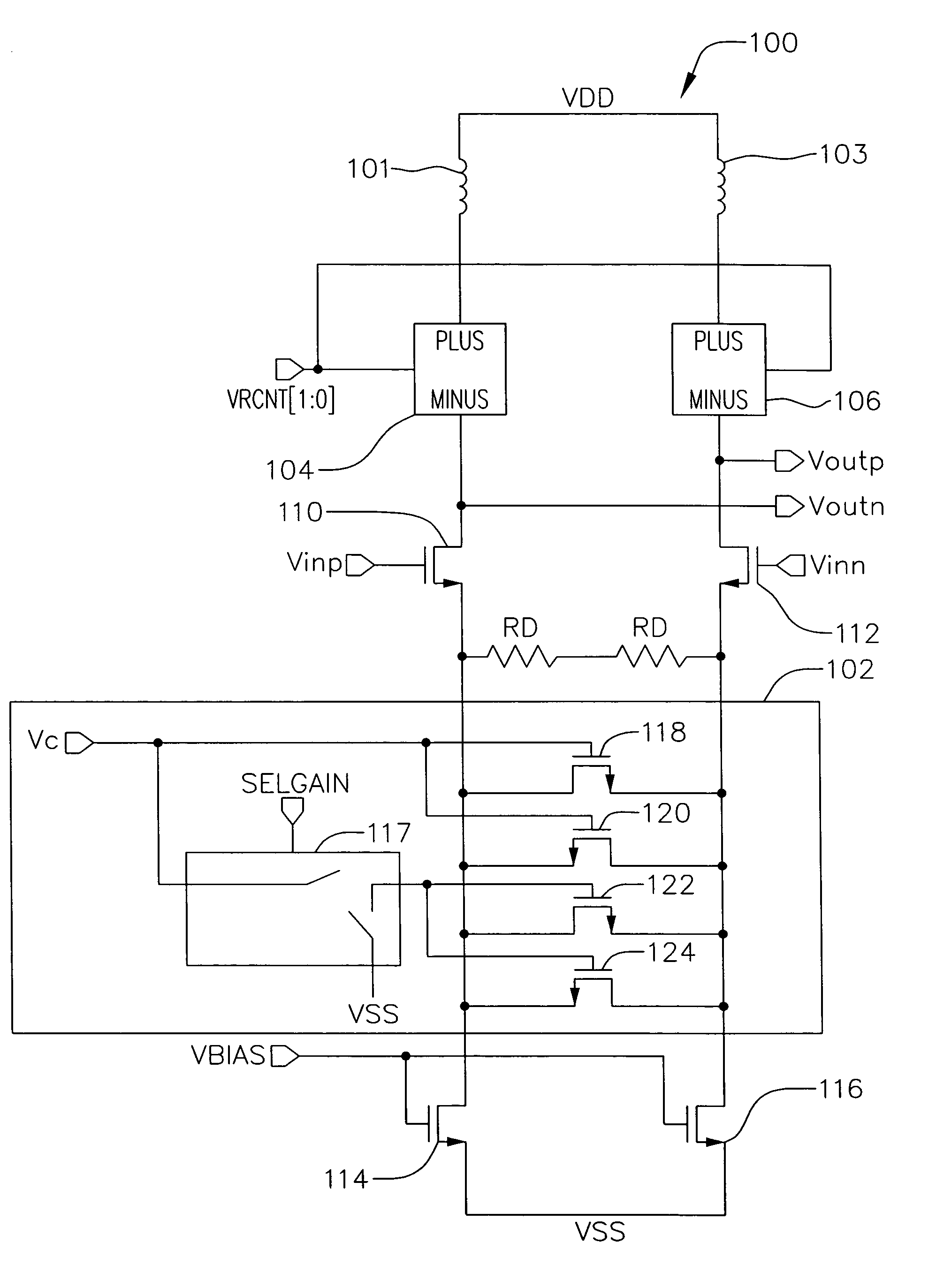

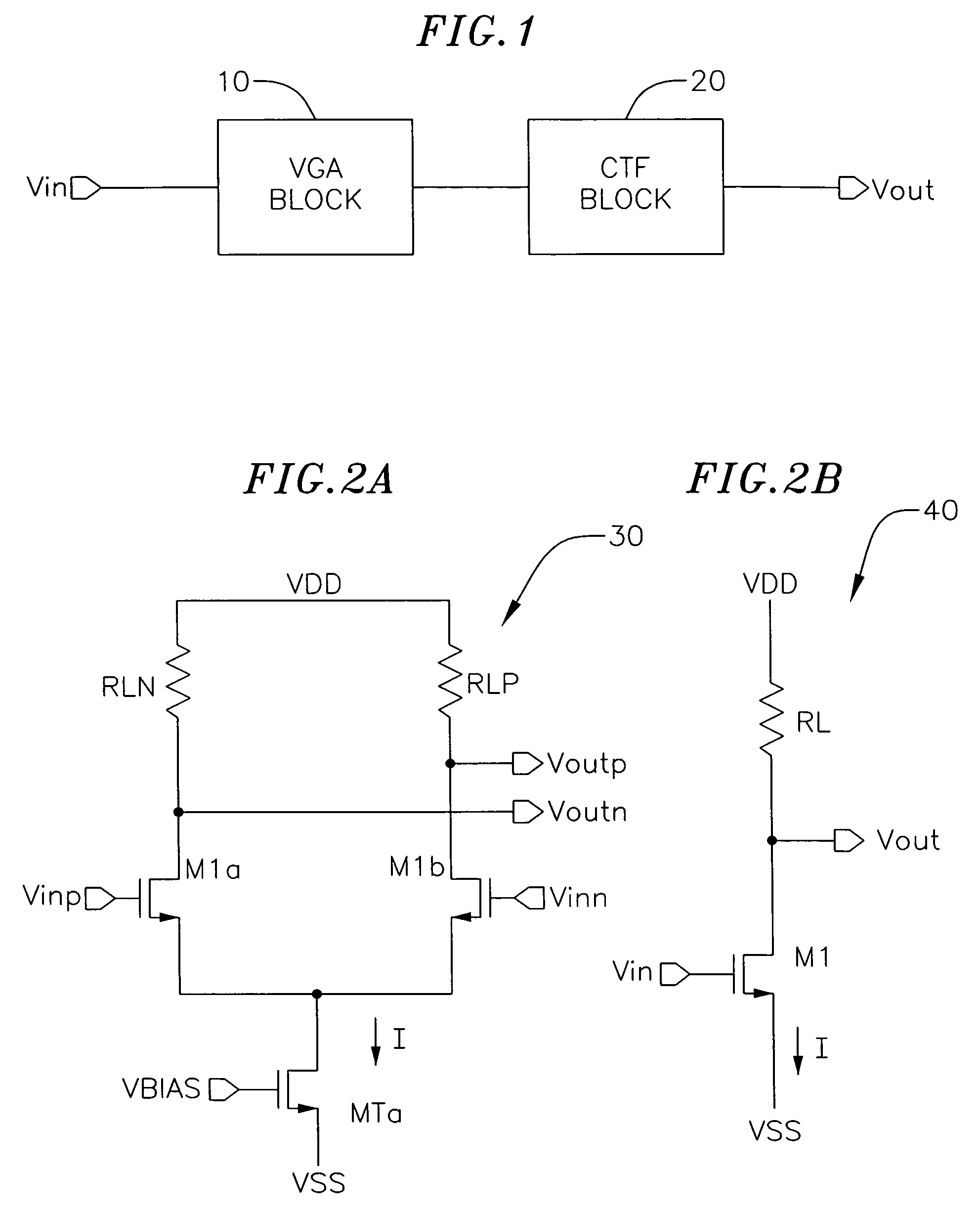

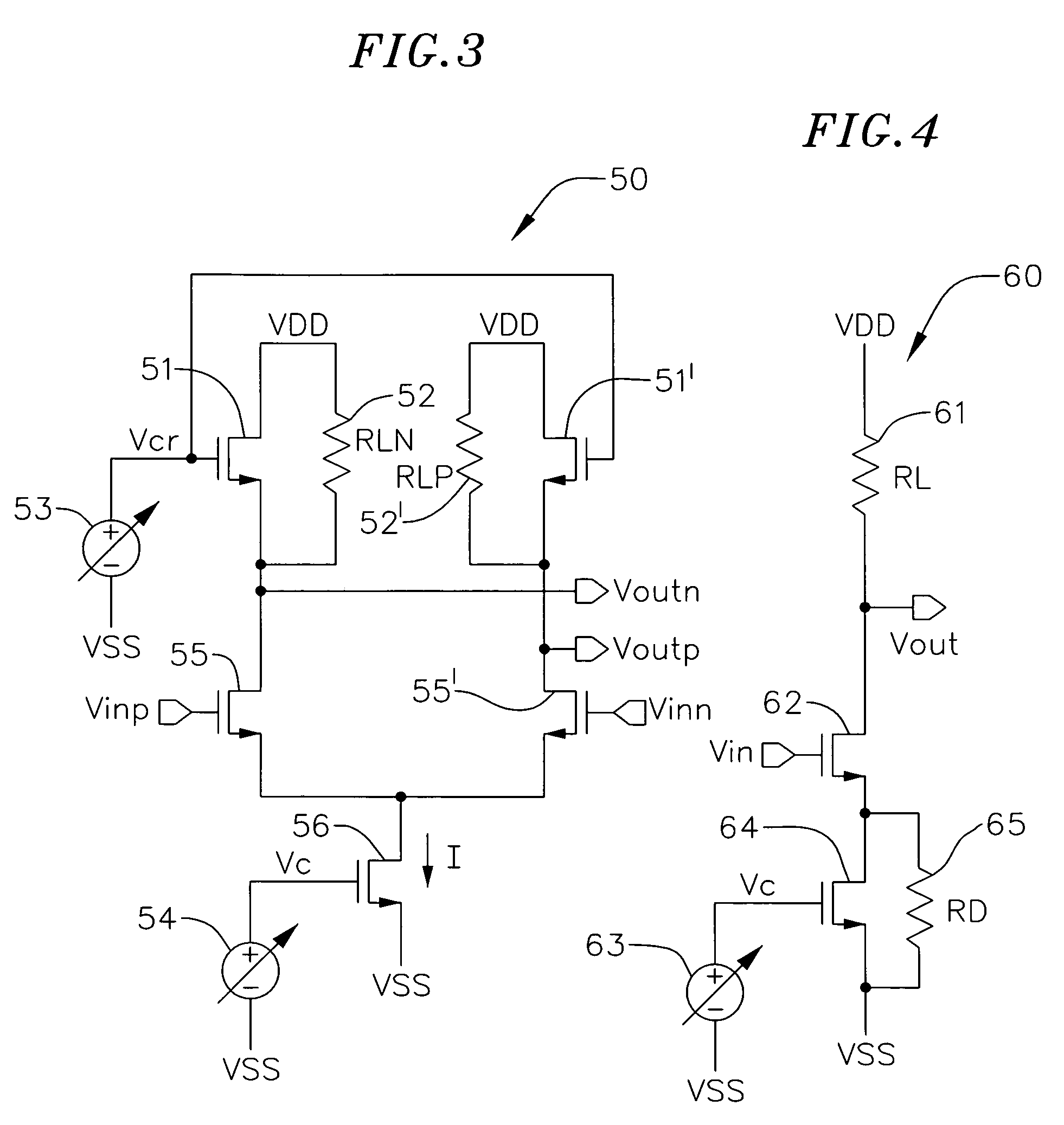

Novel VGA-CTF combination cell for 10 GB/S serial data receivers

InactiveUS20050248396A1Easy to understandGain controlDifferential amplifiersVariable-gain amplifierEngineering

An input processing circuit includes a first and second input transistors for receiving a differential pair of first and second input signals, respectively. At least one resistor is coupled between first terminals of the first and second input transistors. The input processing circuit includes a variable gain amplifier (VGA) circuit. At least one first transistor has a gate terminal, and is coupled between the first terminals of the first and second input transistors. At least one second transistor has a gate terminal, and is coupled between the first terminals of the first and second input transistors. A gate switch is coupled to the gate terminal of the at least one second transistor. The at least one first transistor and the at least one second transistor adjust a gain of the input processing circuit in response to a control voltage. The control voltage is applied to the gate terminal of the at least one first transistor, and the control voltage is applied to the gate terminal of the at least one second transistor through the gate switch.

Owner:AVAGO TECH INT SALES PTE LTD

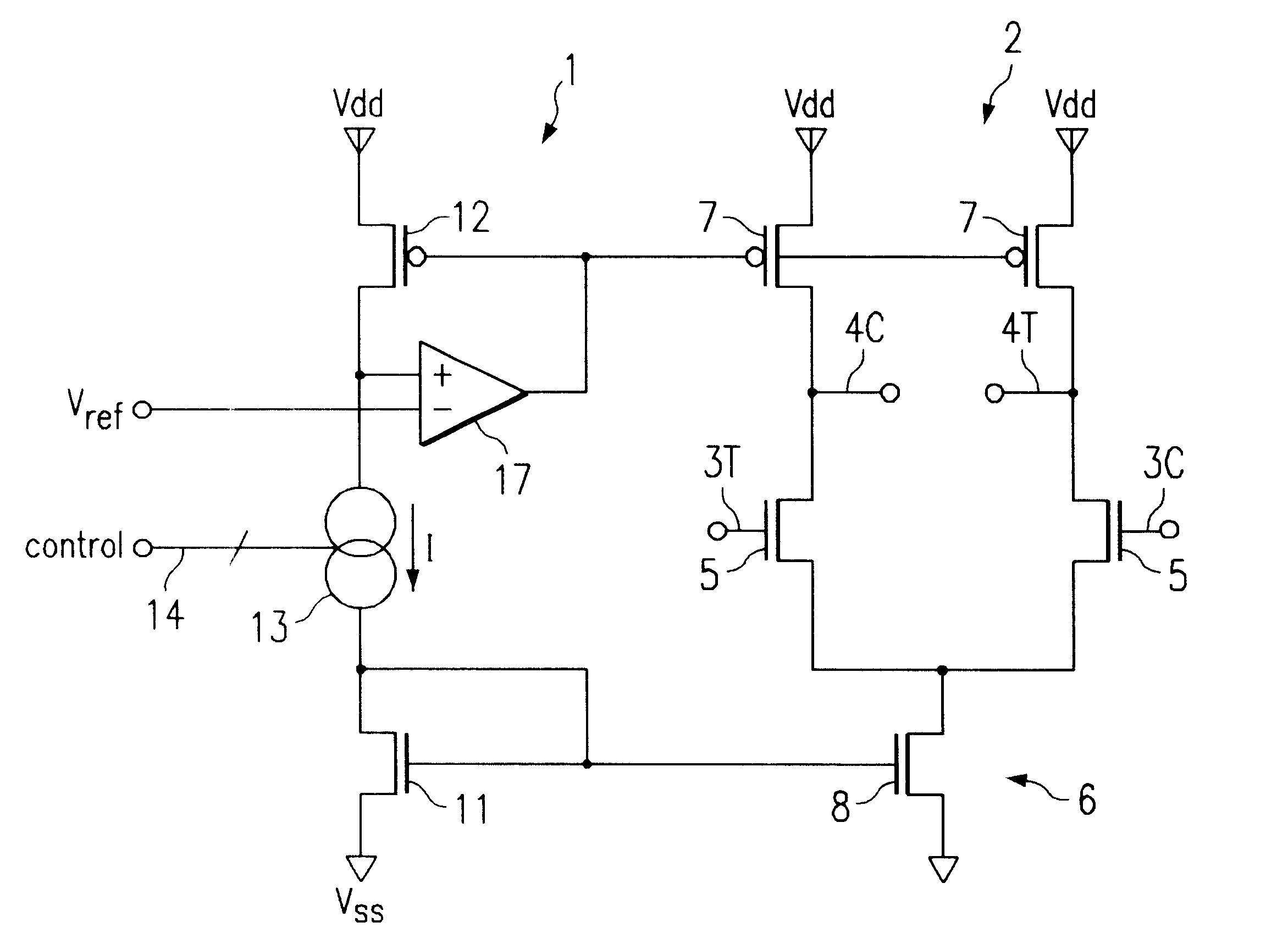

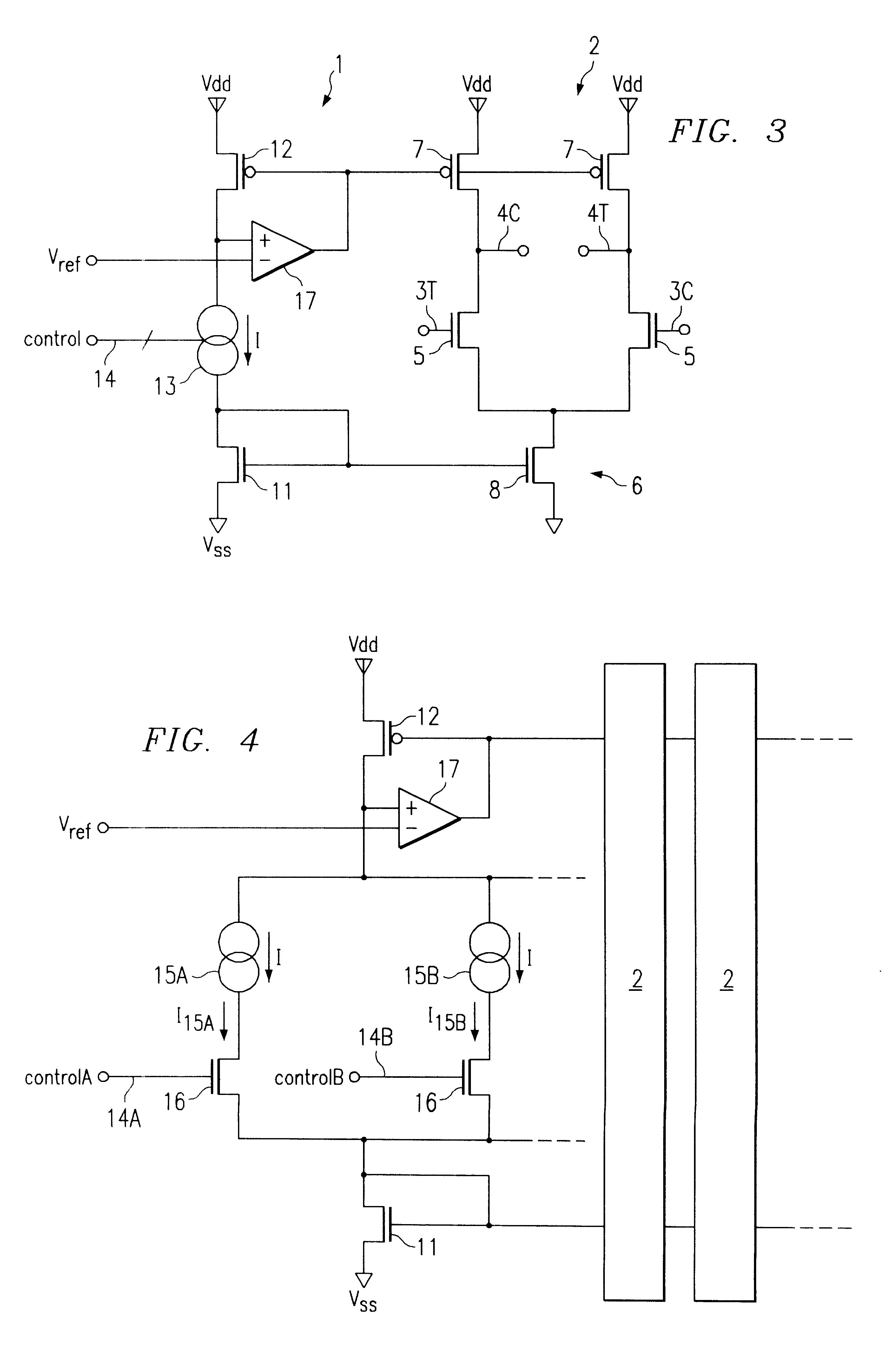

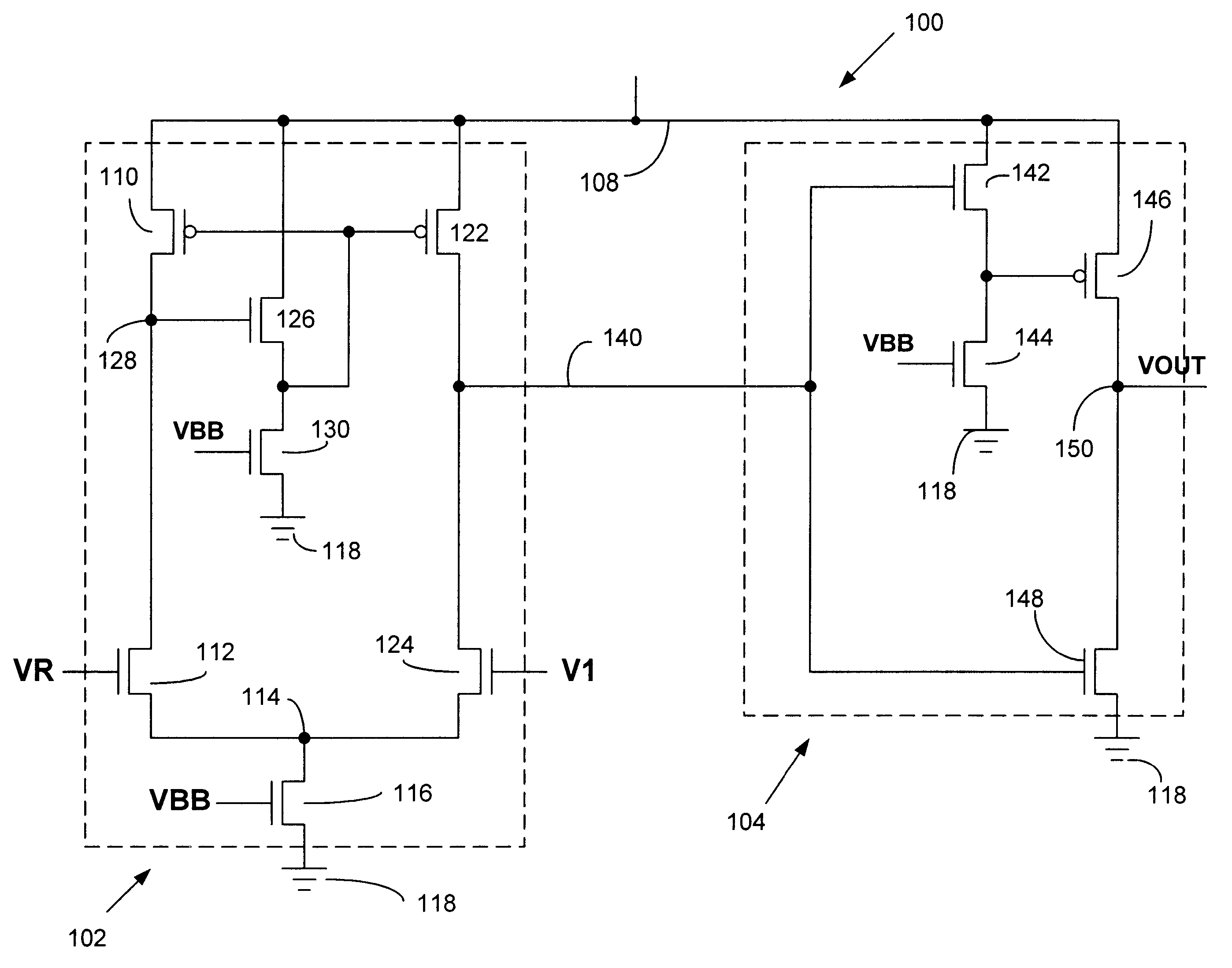

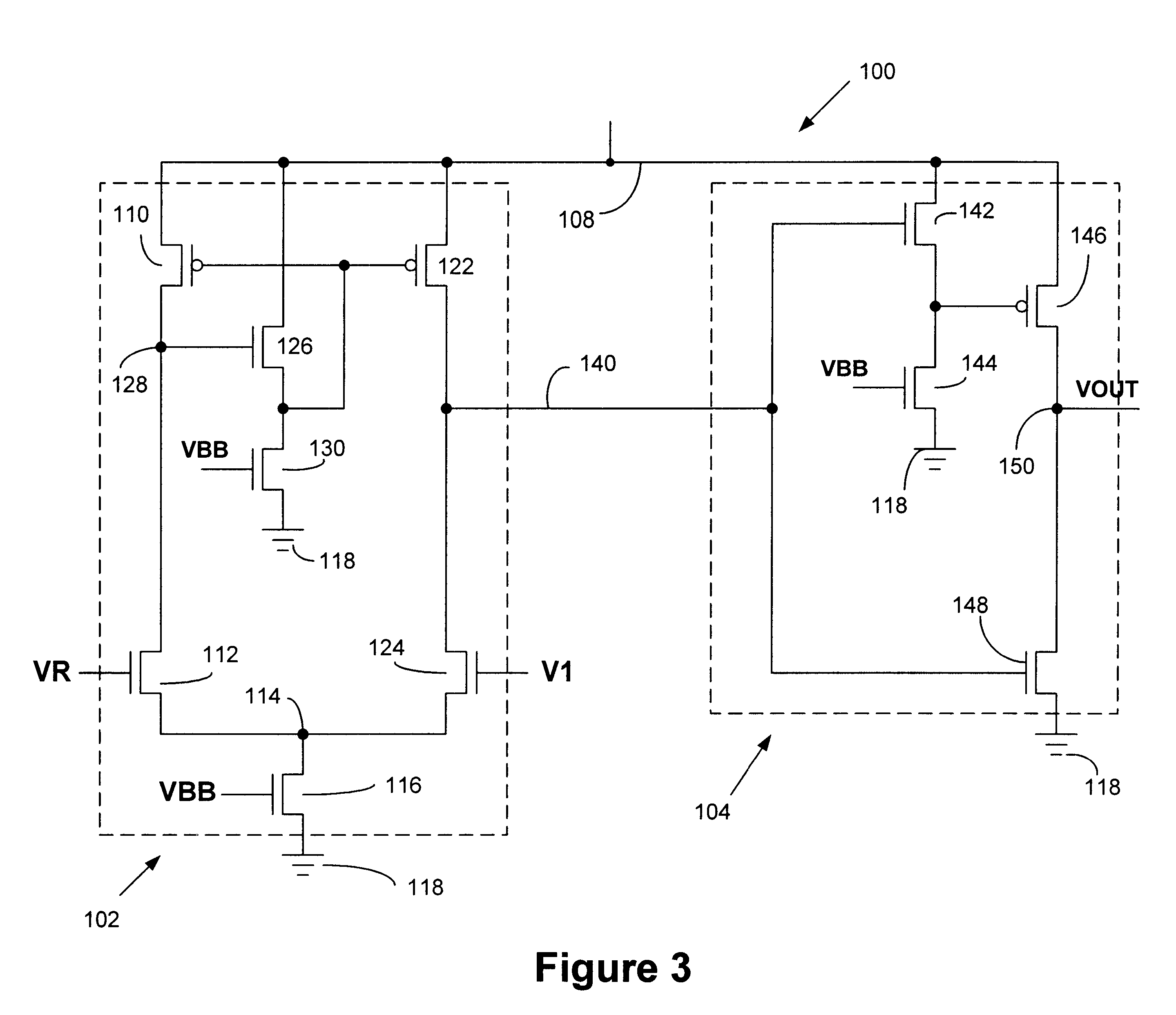

Circuit for controlling current levels in differential logic circuitry

InactiveUS6411159B1Arbitary function generatorsElectric variable regulationElectrical resistance and conductanceVoltage range

A method and circuit are disclosed for controlling the current level of a differential logic circuit having a current source, input transistors which perform current steering based upon the input to the differential logic circuit, and load transistors. The circuit includes a first transistor that forms a current mirror with the current source, a second transistor coupled to the load transistors so that the operating characteristics of the load transistors substantially match the operating characteristics of the second transistor, and current source circuitry coupled between the first and second transistors. The current level selected in the current source circuitry sets the current level in the differential logic circuit and the resistance of the load transistors so that the output voltage swing of the differential logic circuit stays within an acceptable range of voltages, regardless of the selected current level.

Owner:STMICROELECTRONICS SRL

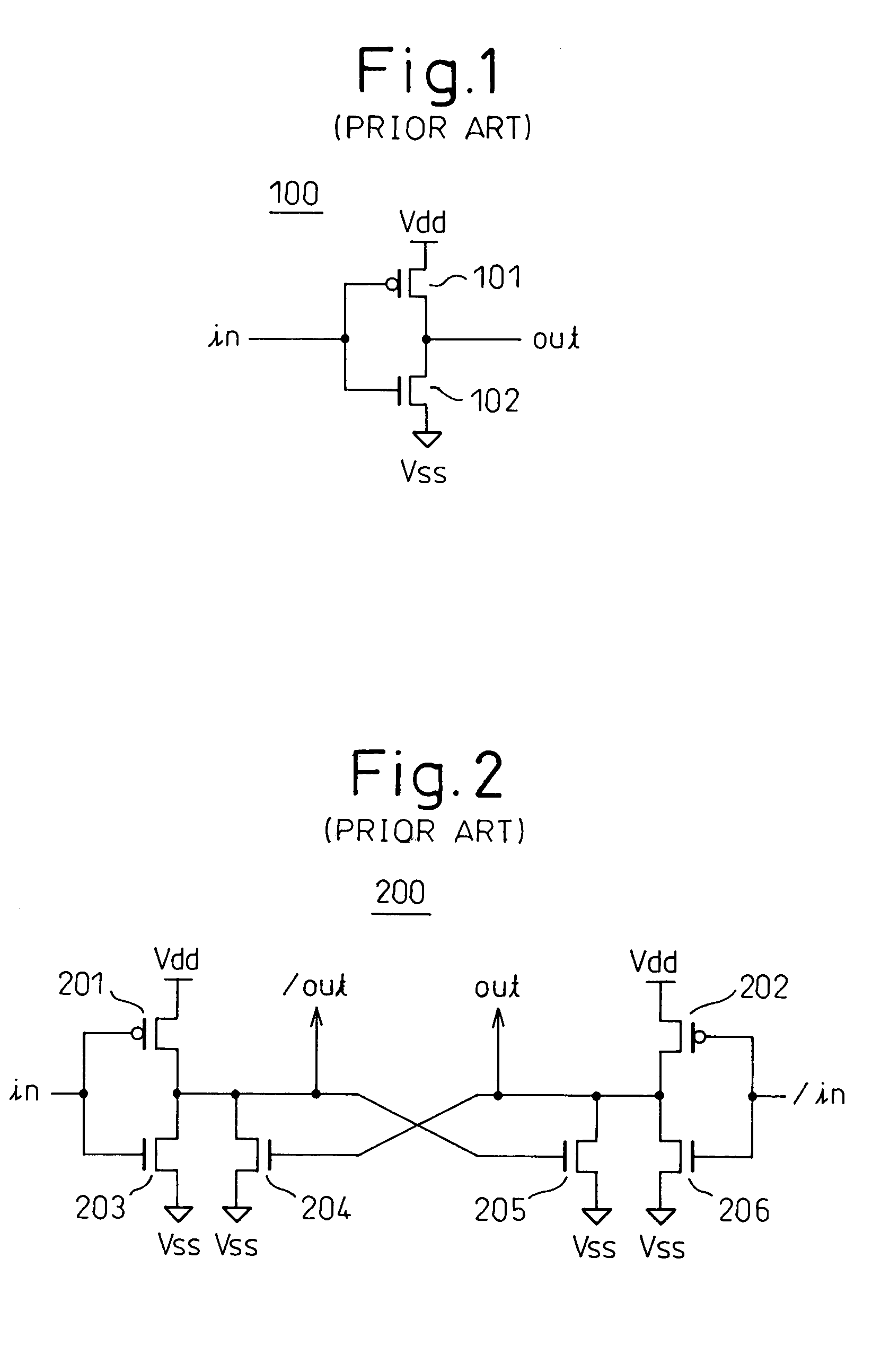

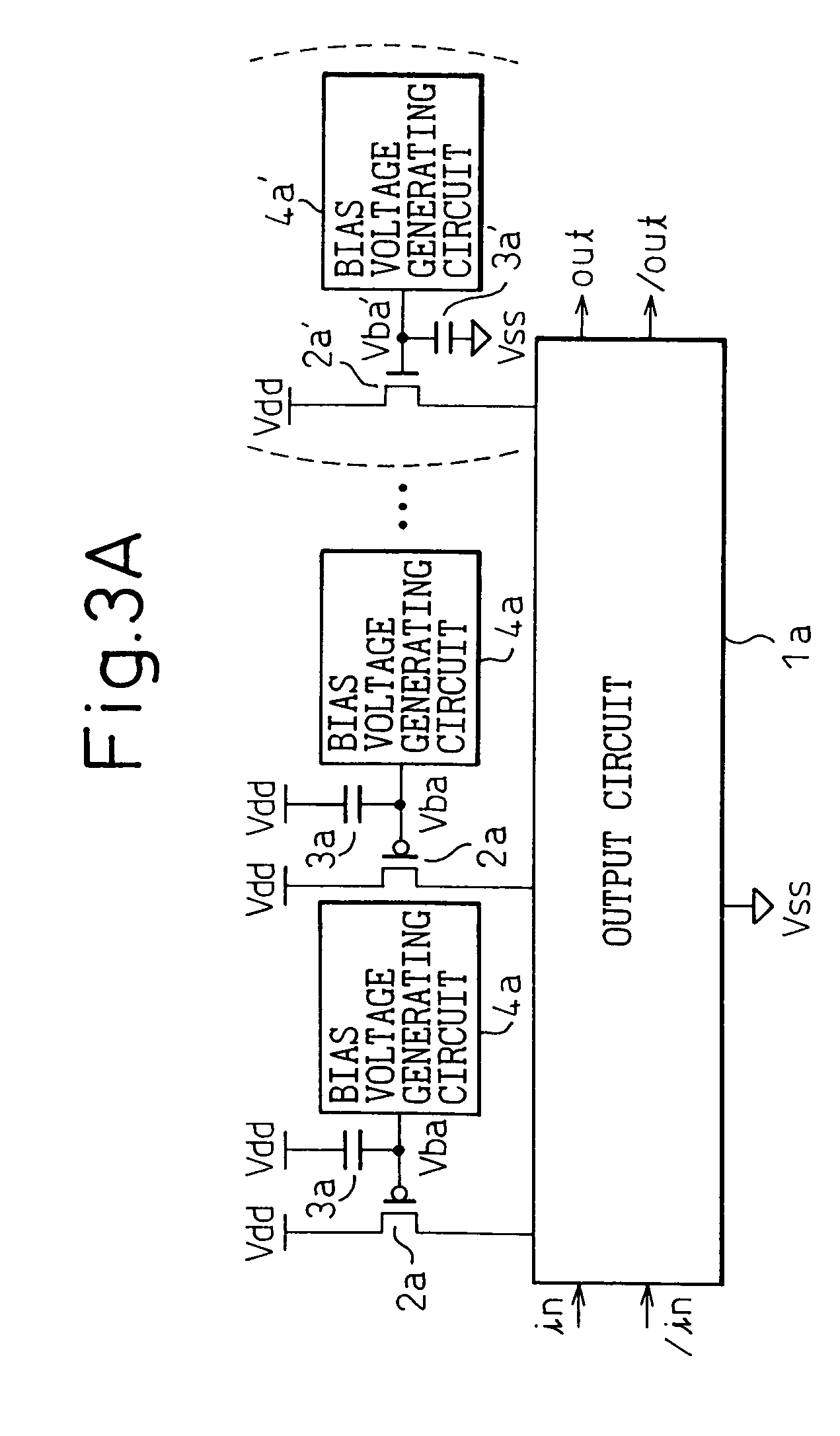

Output circuit device for clock signal distribution in high-speed signal transmission

InactiveUS6963237B2Increase speedAccurate timingMultiple input and output pulse circuitsElectric pulse generatorControl circuitTransistor

An output circuit device has an output circuit connected between a first power supply line and a second power supply line via a control circuit having at least one isolating transistor. A control voltage held at a constant level is applied to a control electrode of the isolating transistor, and the control voltage is a voltage at a level that works to attenuate high-frequency components contained in a voltage supplied from the first or the second power supply line.

Owner:FUJITSU LTD

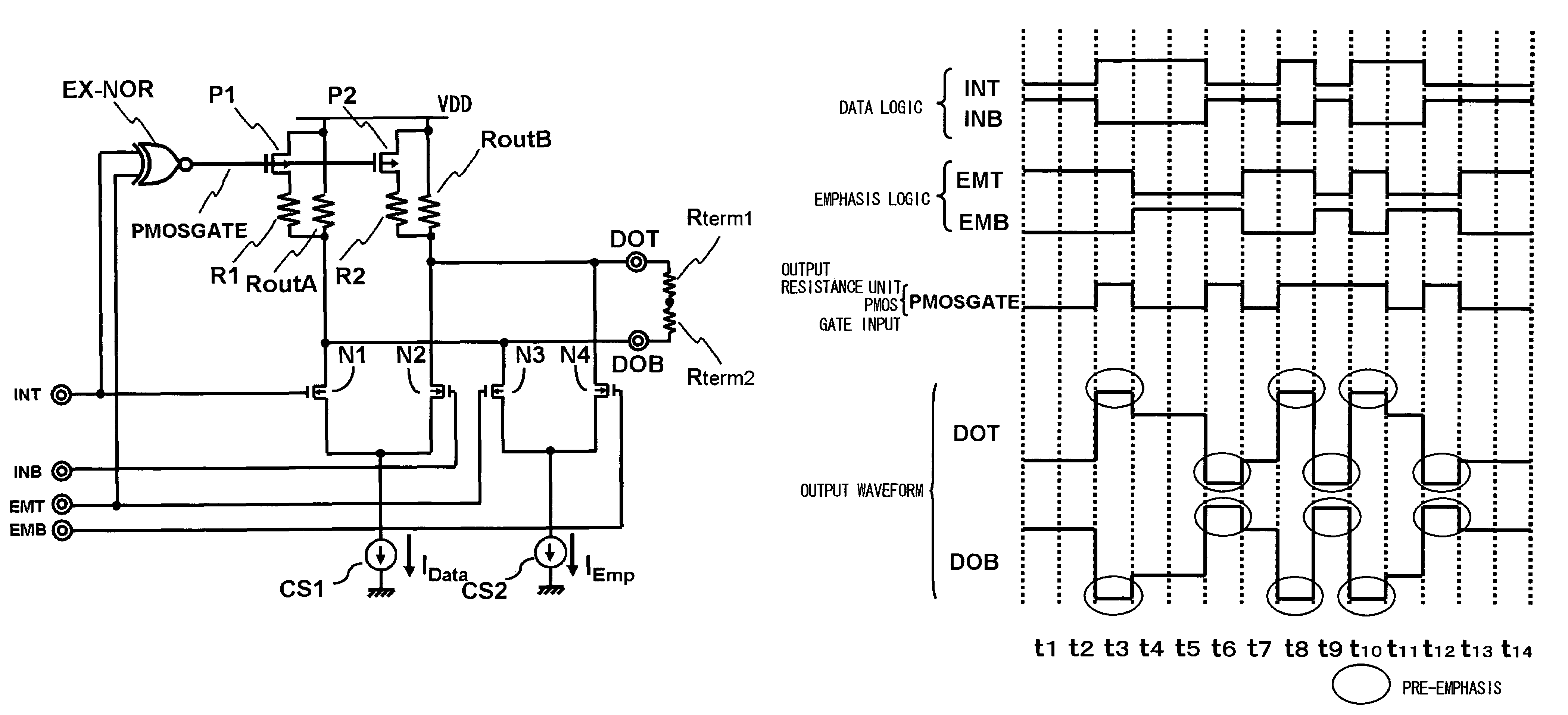

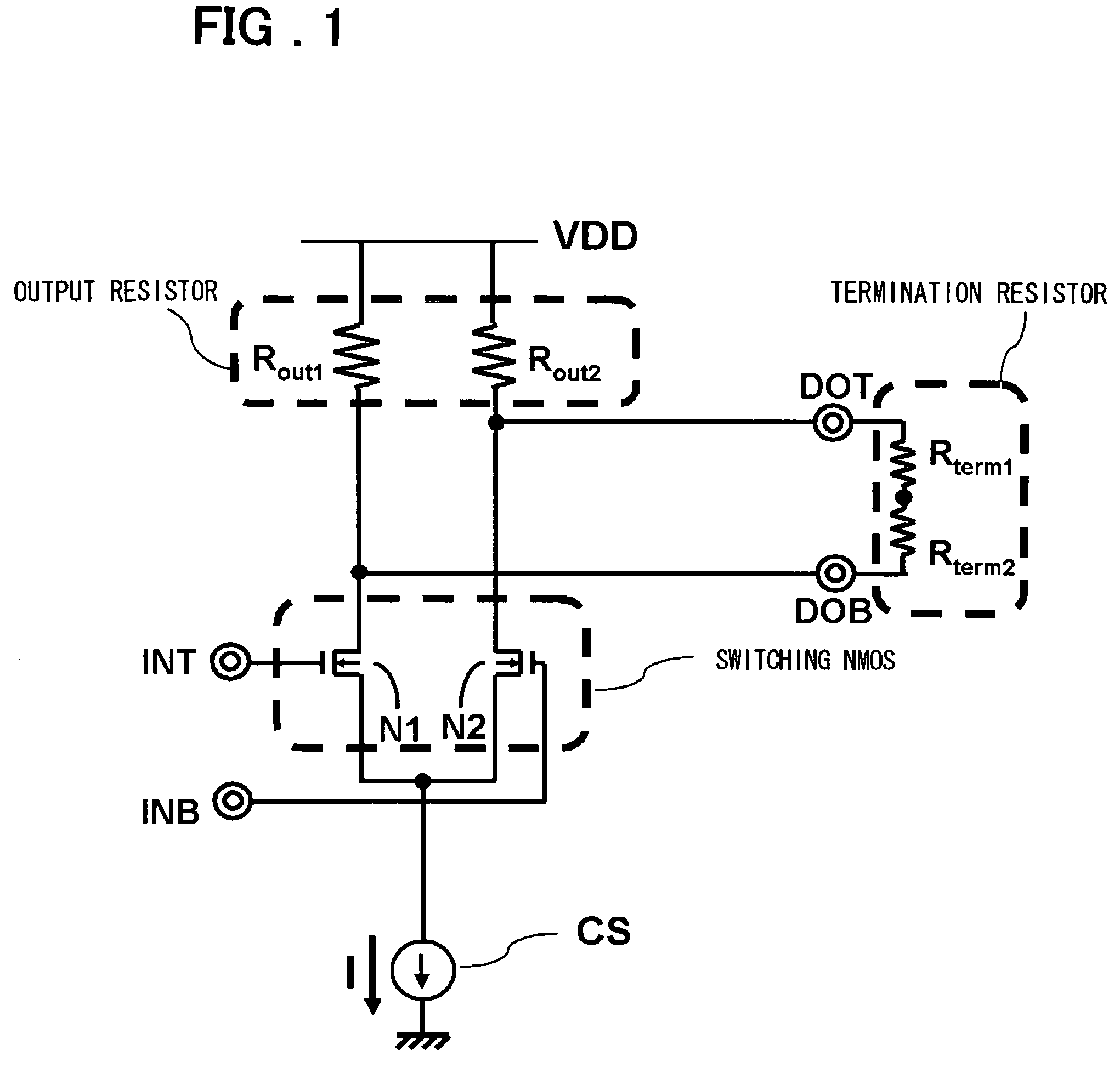

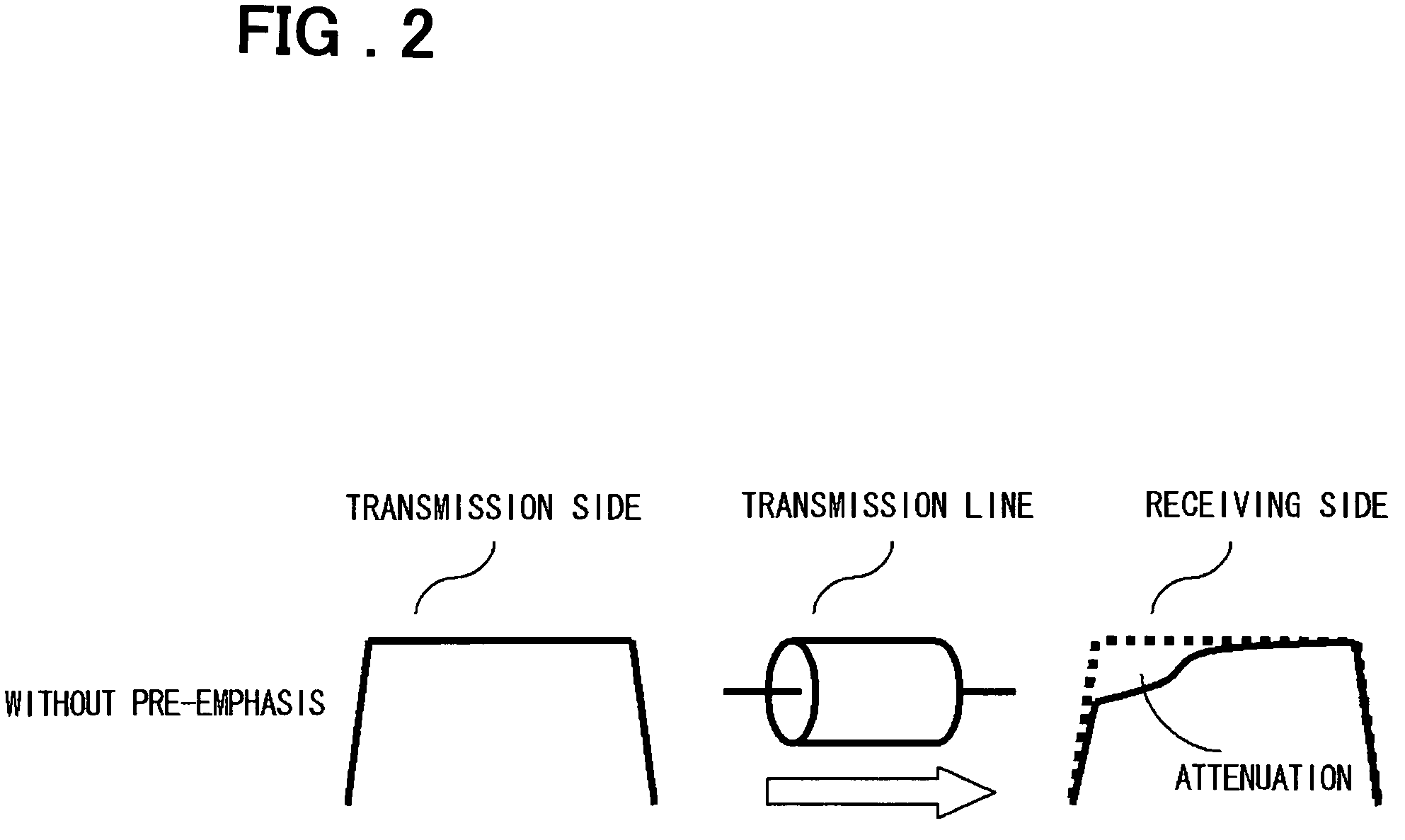

Output buffer circuit with control circuit for changing resistance of output resistor pair

InactiveUS7408387B2Improve rise and fall characteristicIncreased current consumptionElectric pulse generatorOscillations generatorsResistive circuitsControl signal

Disclosed is an output buffer circuit including a first differential transistor pair for differentially receiving a data signal from a differential input pair; and a second differential transistor pair for differentially receiving an emphasis data signal from another differential input pair; a pair of output resistor circuits via which the drains of first and second differential transistor pairs are connected to a power supply, said output resistor circuits each including a transistor; and a logic circuit adapted for receiving the data signal and the emphasis signal and for supplying a control signal which is of first and second values at the time of preemphasis and at other times to the transistors of the output resistor circuit, wherein the output resistance is relatively made larger at the time of emphasis, while being relatively smaller at the time of deemphasis.

Owner:RENESAS ELECTRONICS CORP

VGA-CTF combination cell for 10 Gb/s serial data receivers

An input processing circuit includes a first and second input transistors for receiving a differential pair of first and second input signals, respectively. At least one resistor is coupled between first terminals of the first and second input transistors. The input processing circuit includes a variable gain amplifier (VGA) circuit. At least one first transistor has a gate terminal, and is coupled between the first terminals of the first and second input transistors. At least one second transistor has a gate terminal, and is coupled between the first terminals of the first and second input transistors. A gate switch is coupled to the gate terminal of the at least one second transistor. The at least one first transistor and the at least one second transistor adjust a gain of the input processing circuit in response to a control voltage. The control voltage is applied to the gate terminal of the at least one first transistor, and the control voltage is applied to the gate terminal of the at least one second transistor through the gate switch.

Owner:AVAGO TECH INT SALES PTE LTD

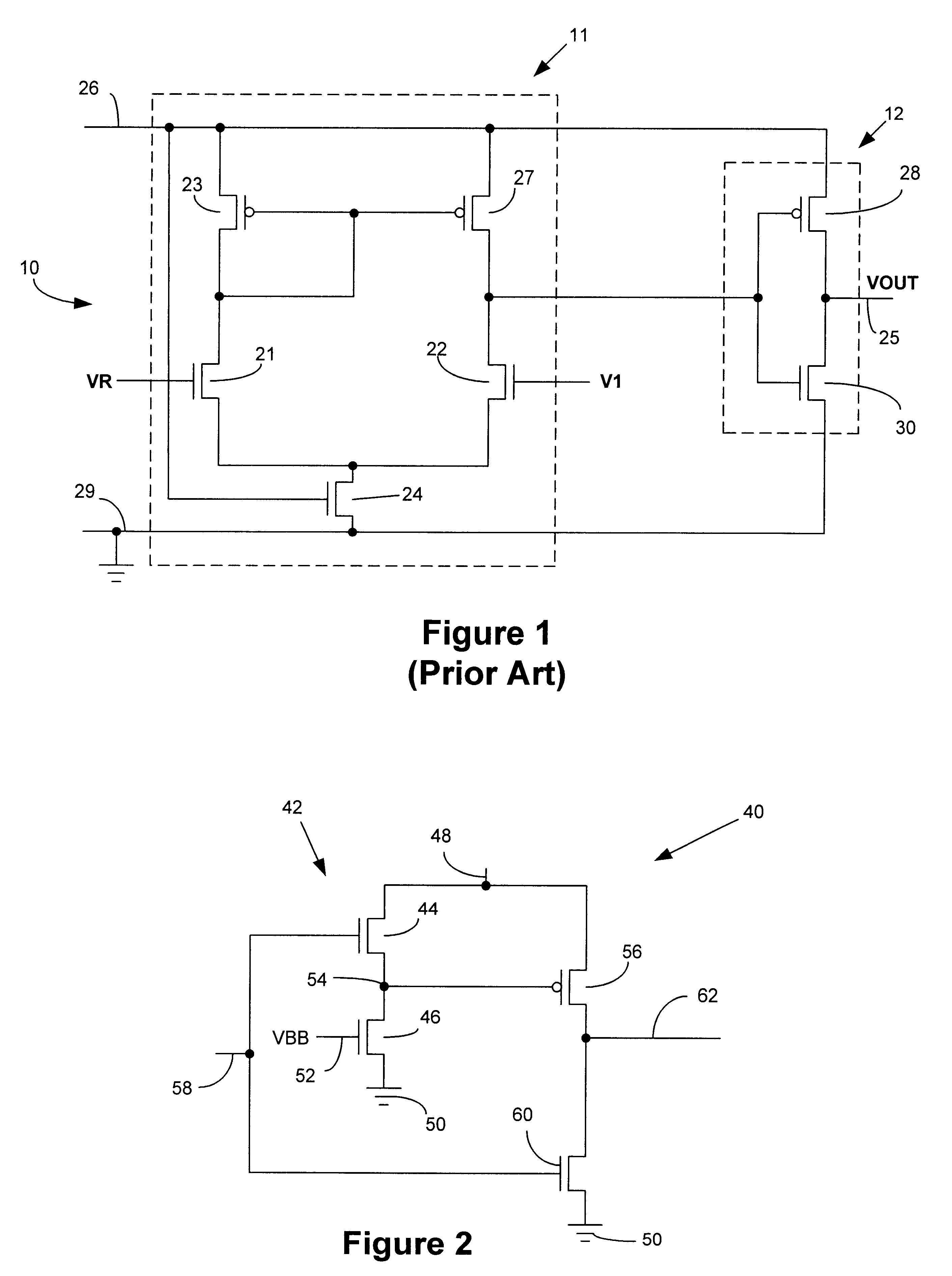

Integrated circuit comparator or amplifier

InactiveUS6512400B1Multiple input and output pulse circuitsDifferential amplifiersAudio power amplifierDifferential amplifier

An integrated circuit comparator includes a differential amplifier, a source follower circuit coupled to a gate terminal of a first transistor in the differential amplifier, and an output circuit. One or more source follower circuits may be utilized in connection with the differential amplifier, and one or more source follower circuits may be utilized in connection with the output circuit.

Owner:MICRON TECH INC

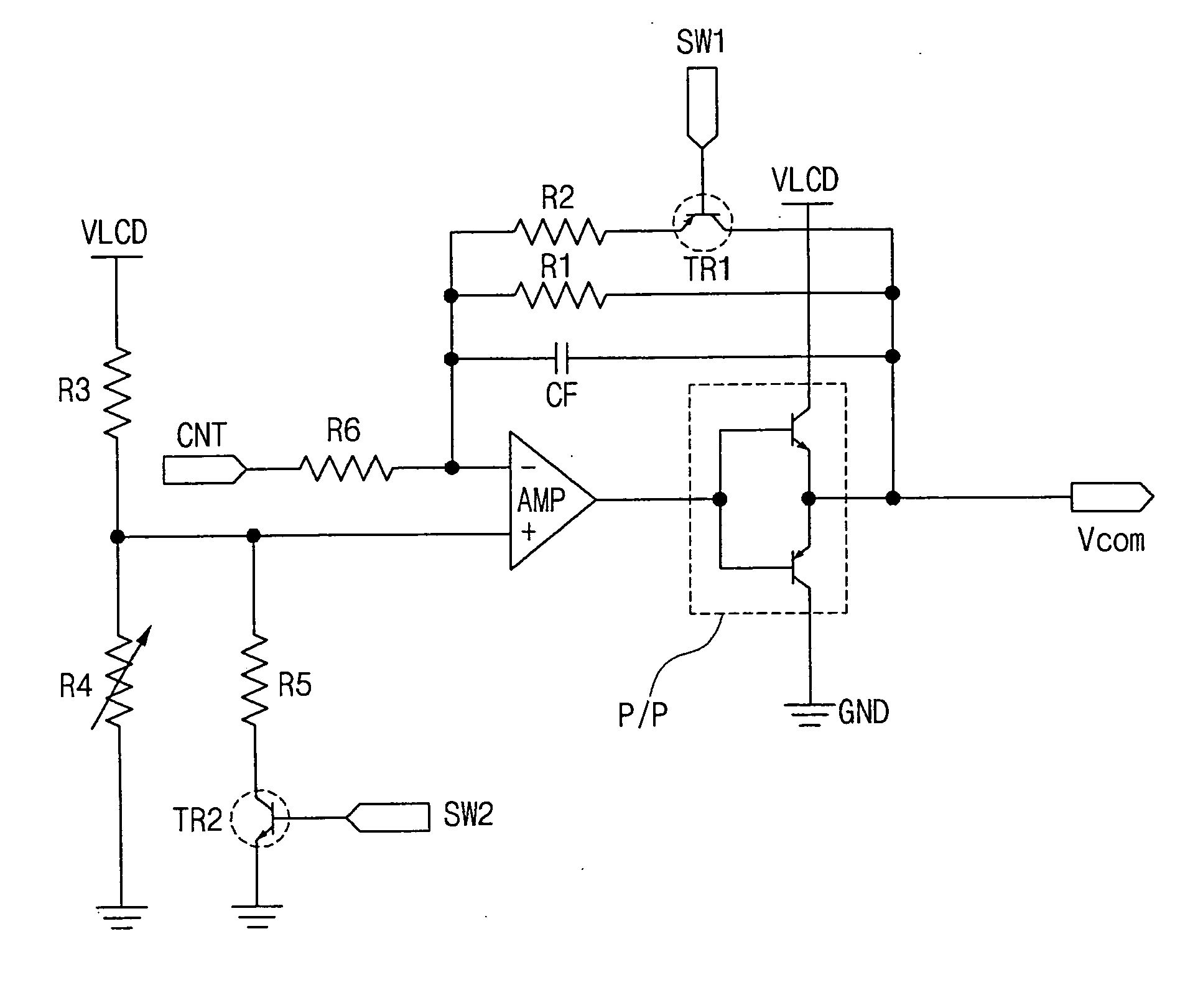

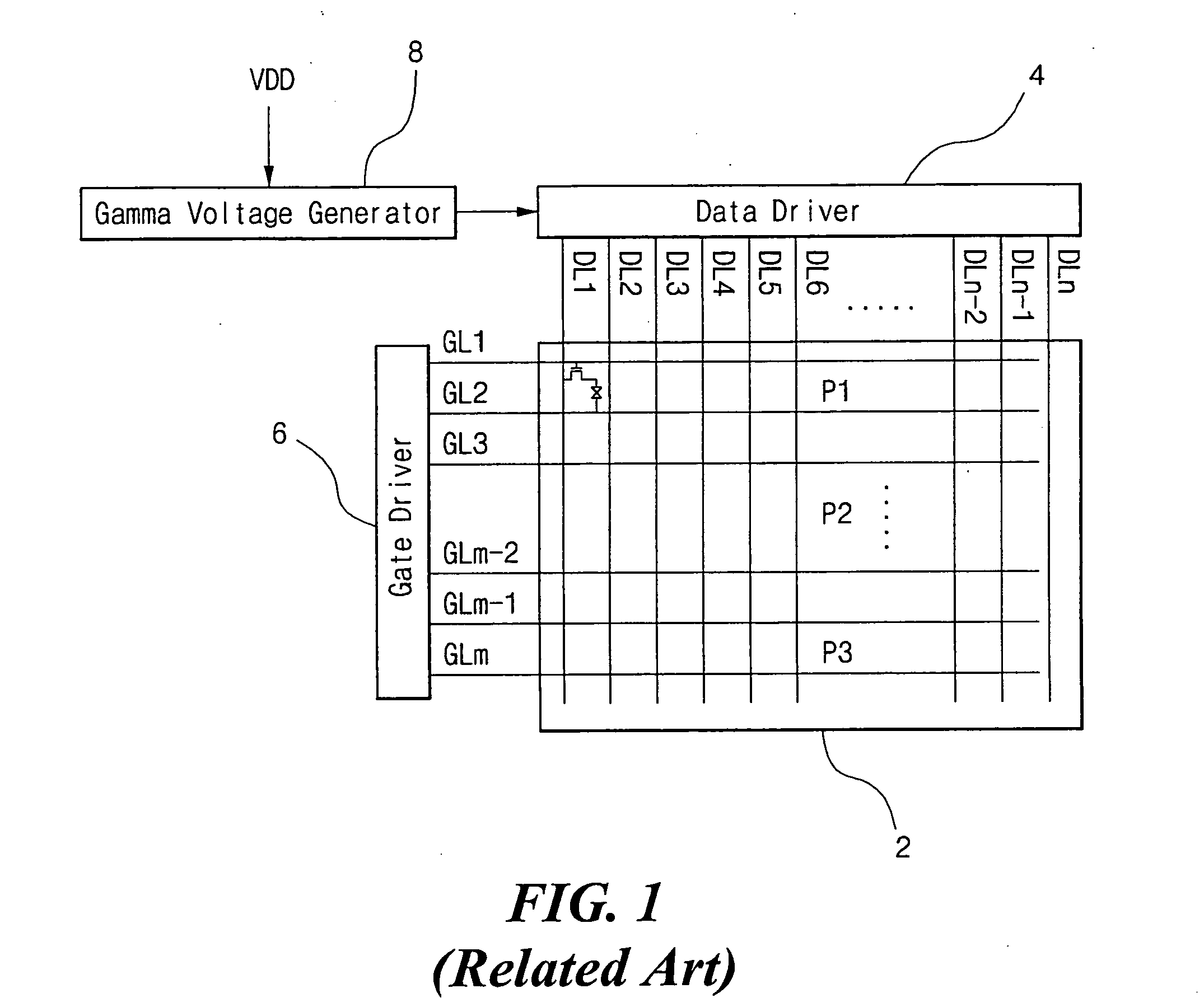

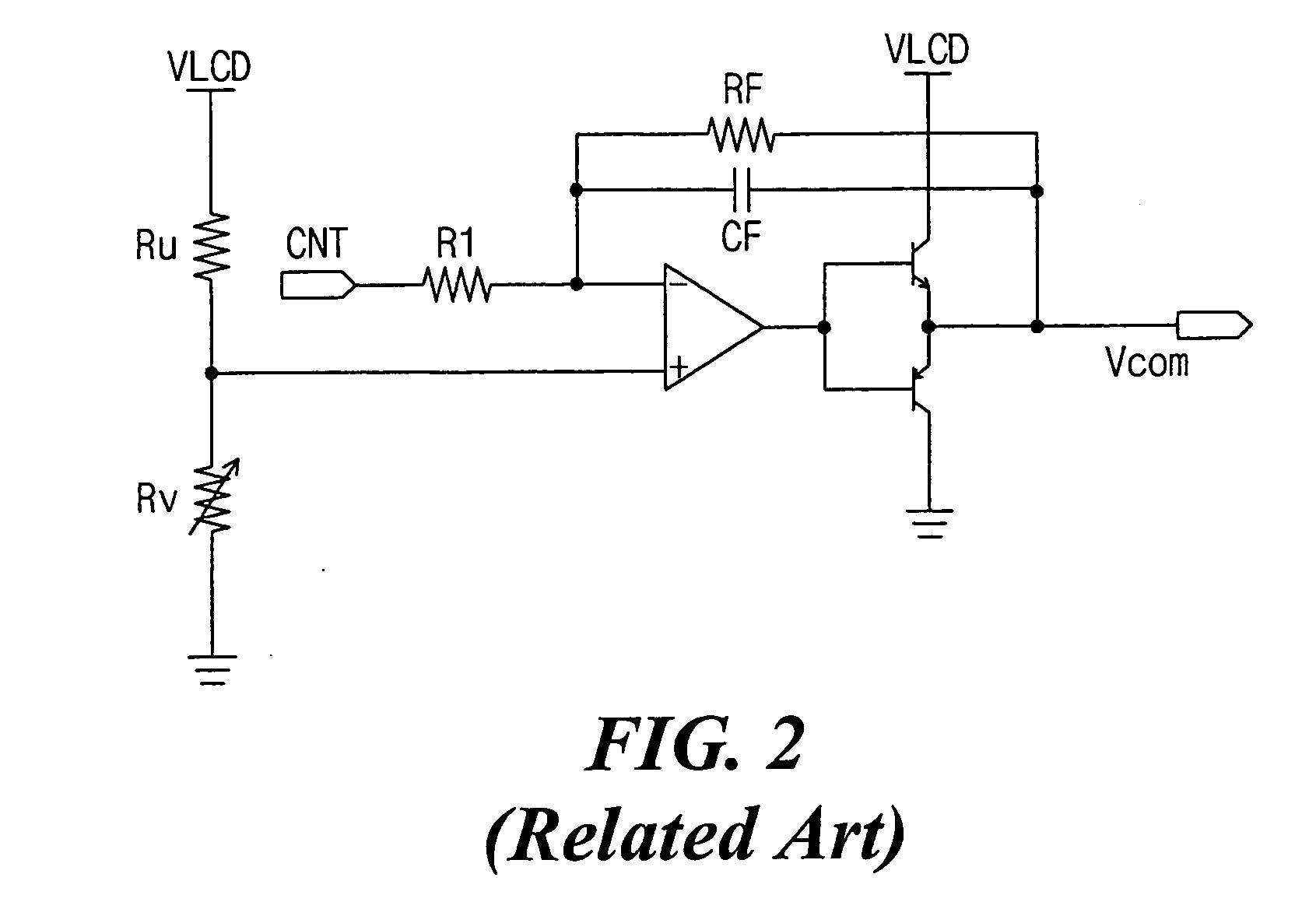

Common voltage source integrated circuit for liquid crystal display device

ActiveUS20050140400A1Avoid signal delayImprove display qualityStatic indicating devicesElectronic switchingCapacitanceAudio power amplifier

A common voltage source IC device includes an operational amplifier, a push-pull circuit receiving an output signal from the operational amplifier and outputting a common voltage to a common voltage terminal; an inverting resistor connected to an inverting input of the operational amplifier; a feedback resistor connected to the common voltage terminal and the inverting input; a capacitor connected to the common voltage terminal and the inverting input; a first switching resistor connected to the inverting input and a first switching transistor, the first switching transistor connected to the common voltage terminal; a driving resistor receiving a drive voltage and connected to a non-inverting input of the operational amplifier; a variable resistor connected to the non-inverting input and a ground source; and a second switching resistor connected to the non-inverting input and a second switching transistor, the second switching transistor connected to the ground source.

Owner:LG DISPLAY CO LTD

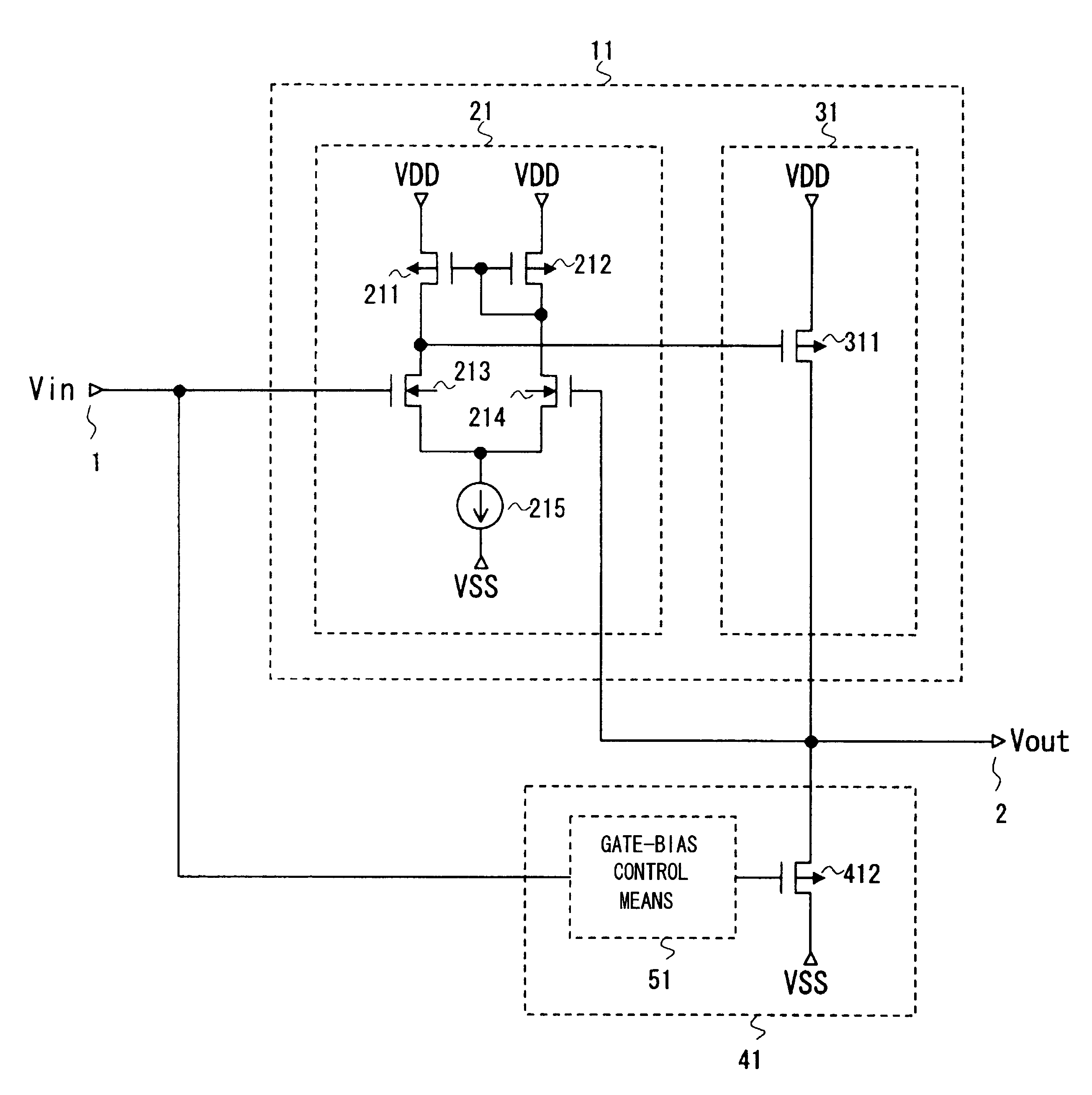

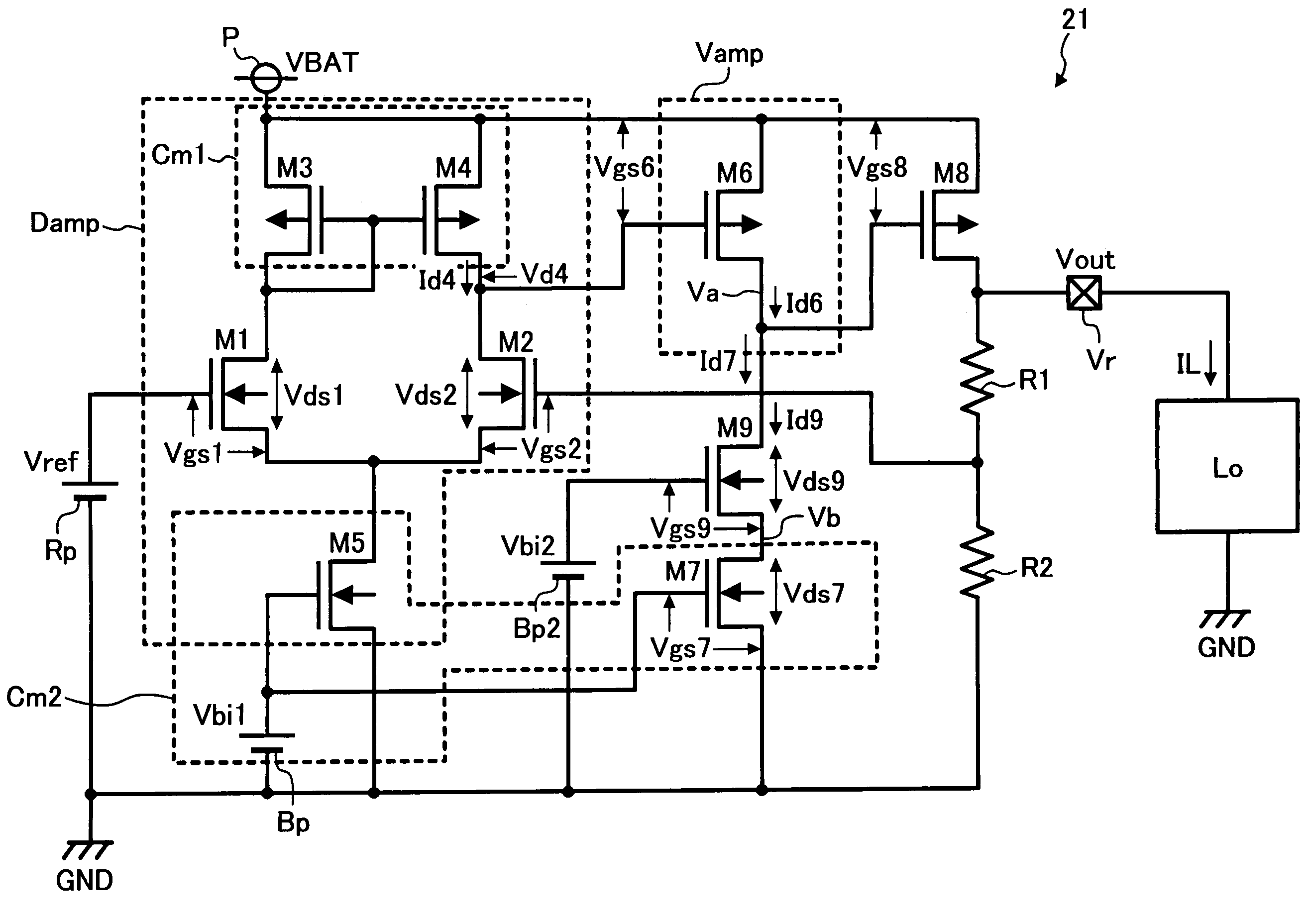

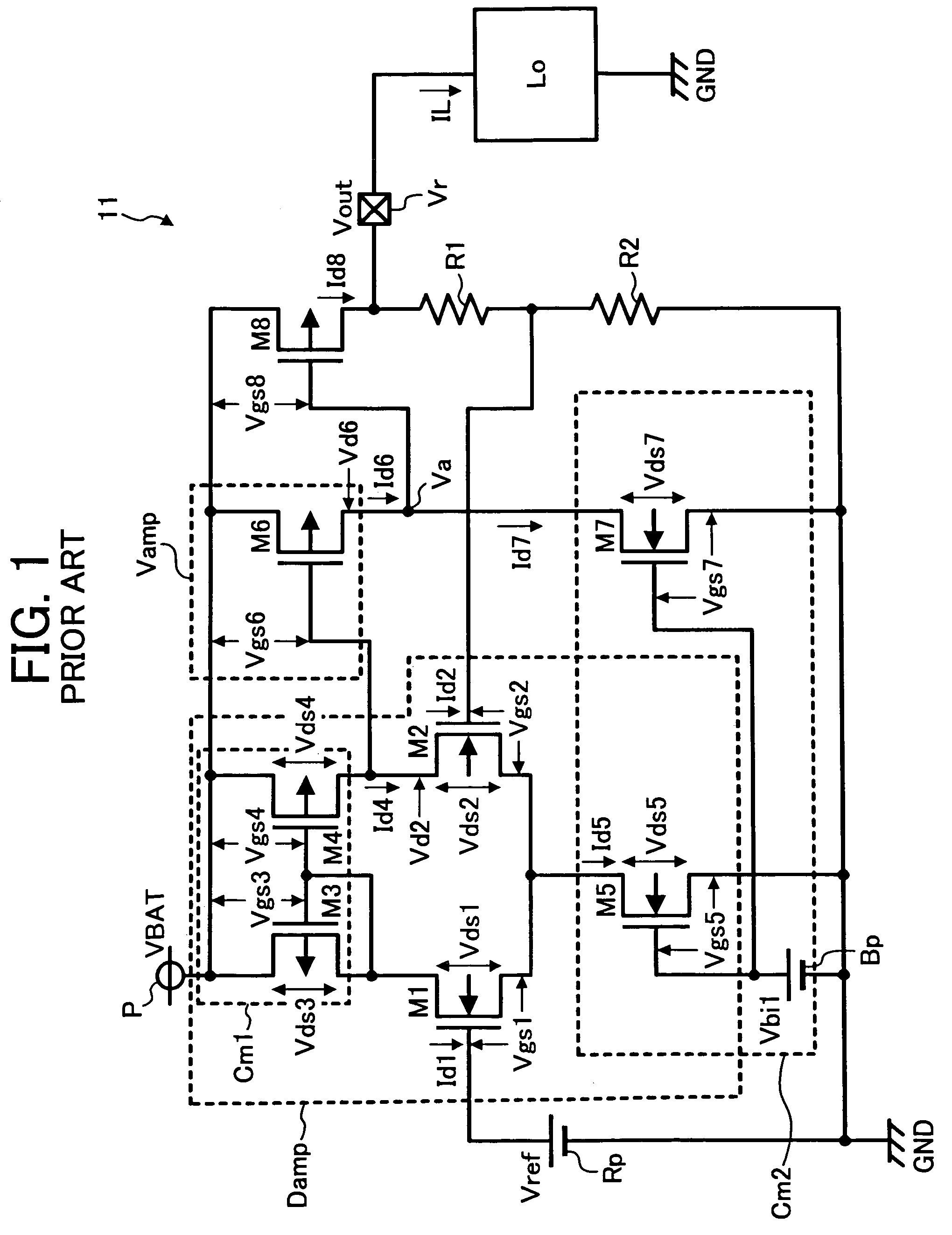

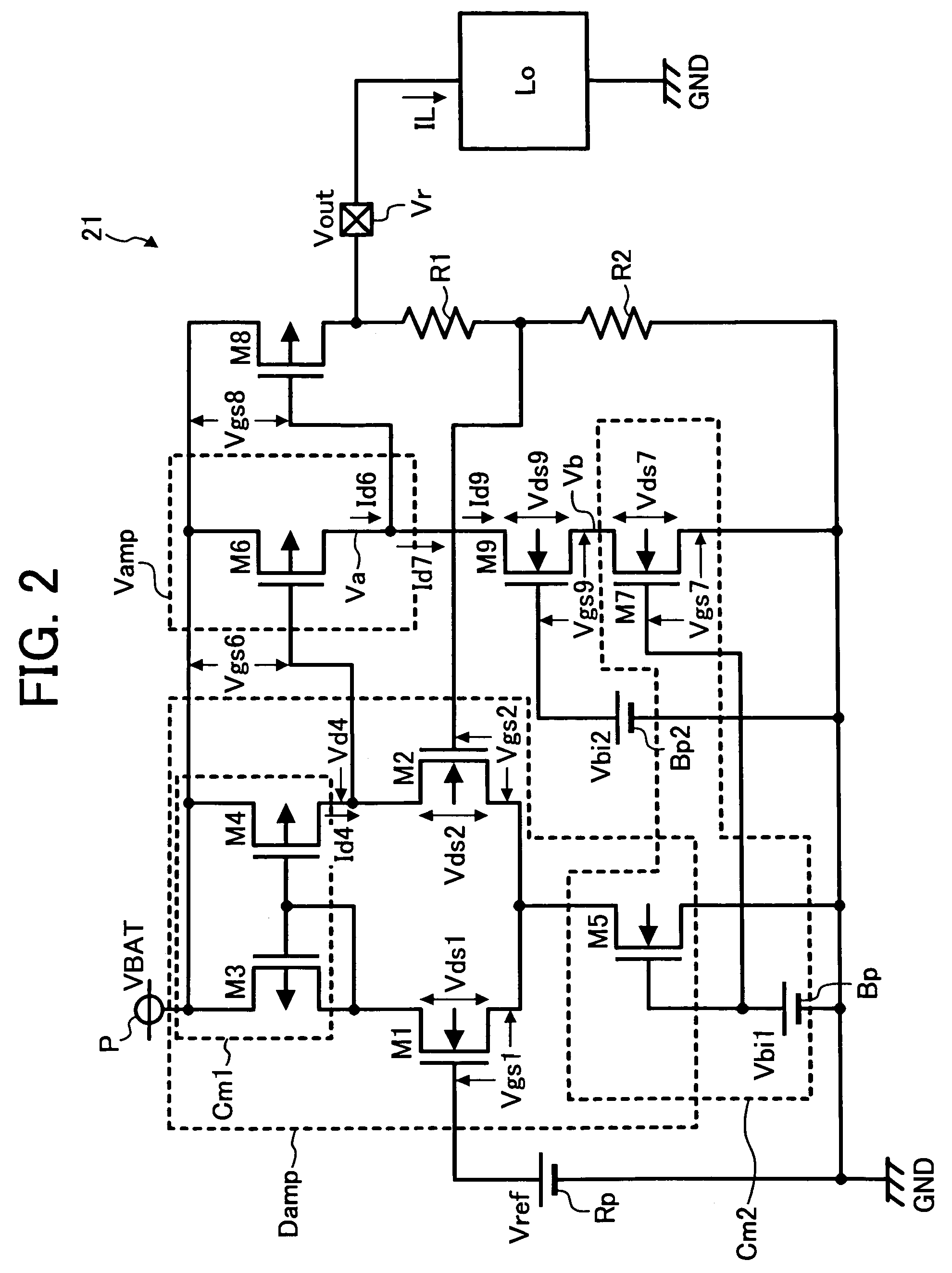

Method and apparatus for outputting constant voltage

ActiveUS7176753B2Instant pulse delivery arrangementsArbitary function generatorsAudio power amplifierEngineering

A constant voltage outputting apparatus includes a differential amplifier circuit, an amplifier circuit, a current adjustment device and a stabilization circuit. The differential amplifier circuit performs a differential amplifying operation and outputs a differential amplified voltage. The amplifier circuit amplifies the differential amplified voltage output from the differential amplifier circuit. The current adjustment device adjusts a current characteristic of the amplifier circuit. The stabilization circuit stabilizes a state of the current adjustment device. A constant voltage outputting method is also described.

Owner:NISSHINBO MICRO DEVICES INC

Mono-polarity switchable PCMO resistor trimmer

ActiveUS7084691B2Improve the immunityPulse automatic controlSolid-state devicesElectrical resistance and conductanceAmorphous silicon

Using programmable resistance material for a matching resistor, a resistor trimming circuit is designed to reversibly trim a matching resistor to match a reference resistor. The programmable resistance materials such as metal-amorphous silicon metal materials, phase change materials or perovskite materials are typically used in resistive memory devices and have the ability to change the resistance reversibly and repeatable with applied electrical pulses. The present invention reversible resistor trimming circuit comprises a resistance bridge network of a matching resistor and a reference resistor to provide inputs to a comparator circuit which generates a comparing signal indicative of the resistance difference. This comparing signal can be used to control a feedback circuit to provide appropriate electrical pulses to the matching resistor to modify the resistance of the matching resistor to match that of the reference resistor.

Owner:XENOGENIC DEV LLC

Popular searches

Logic circuits characterised by logic function Supply voltage varying control Amplifier combinations Automatic tone/bandwidth control Amplifiers with semiconductor devices only Combination controls Dc-amplifiers with dc-coupled stages Semiconductor/solid-state device manufacturing Amplifier protection circuit arrangements Emergency protective arrangements for limiting excess voltage/current