System and method for reducing skew in complementary signals that can be used to synchronously clock a double data rate output

a complementary signal and clocking signal technology, applied in the field of electronic circuitry, can solve the problems of clock skew, delay of one clock relative, and jitter of one complementary pair, so as to minimize clock skew, jitter, and noise placed on complementary signals.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

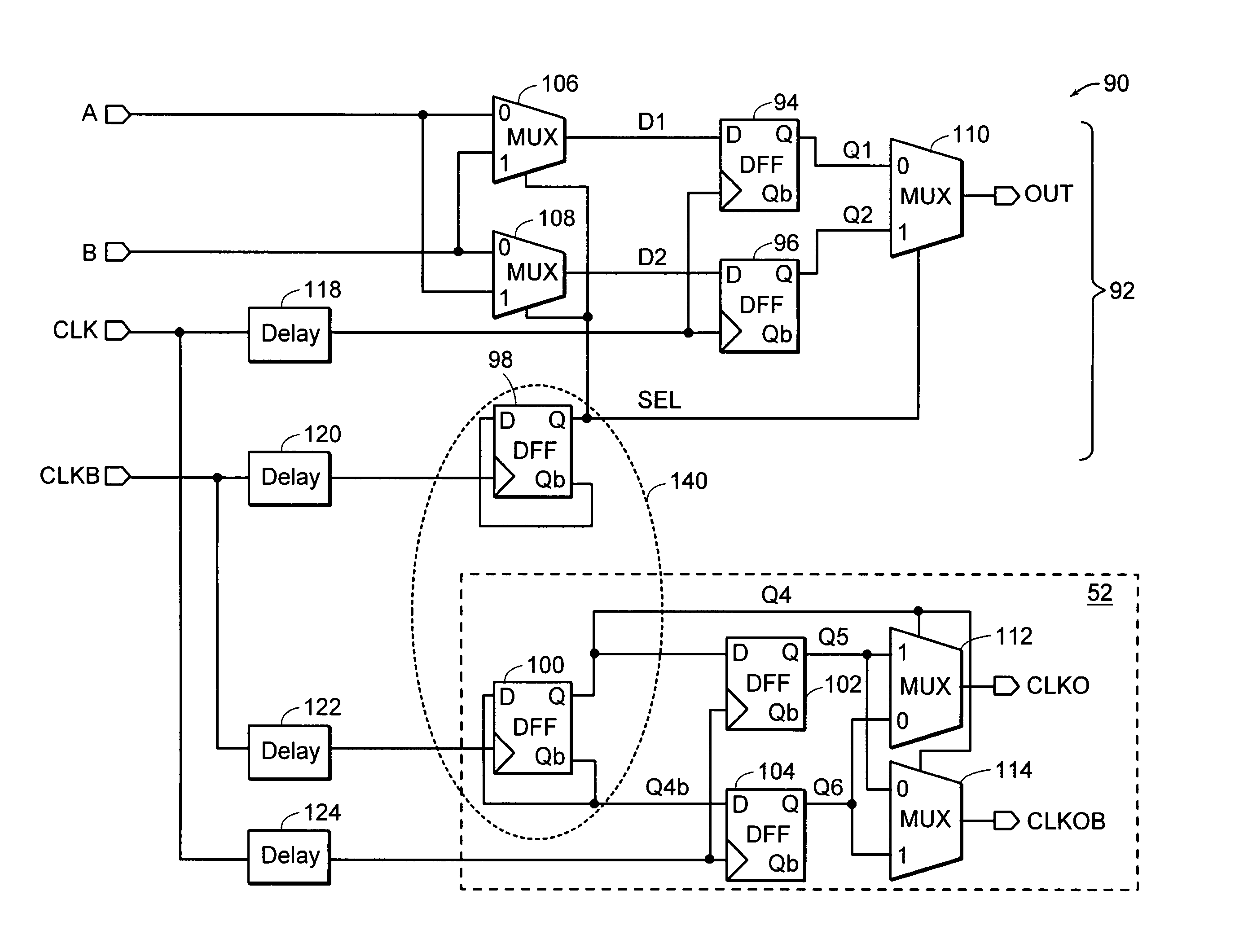

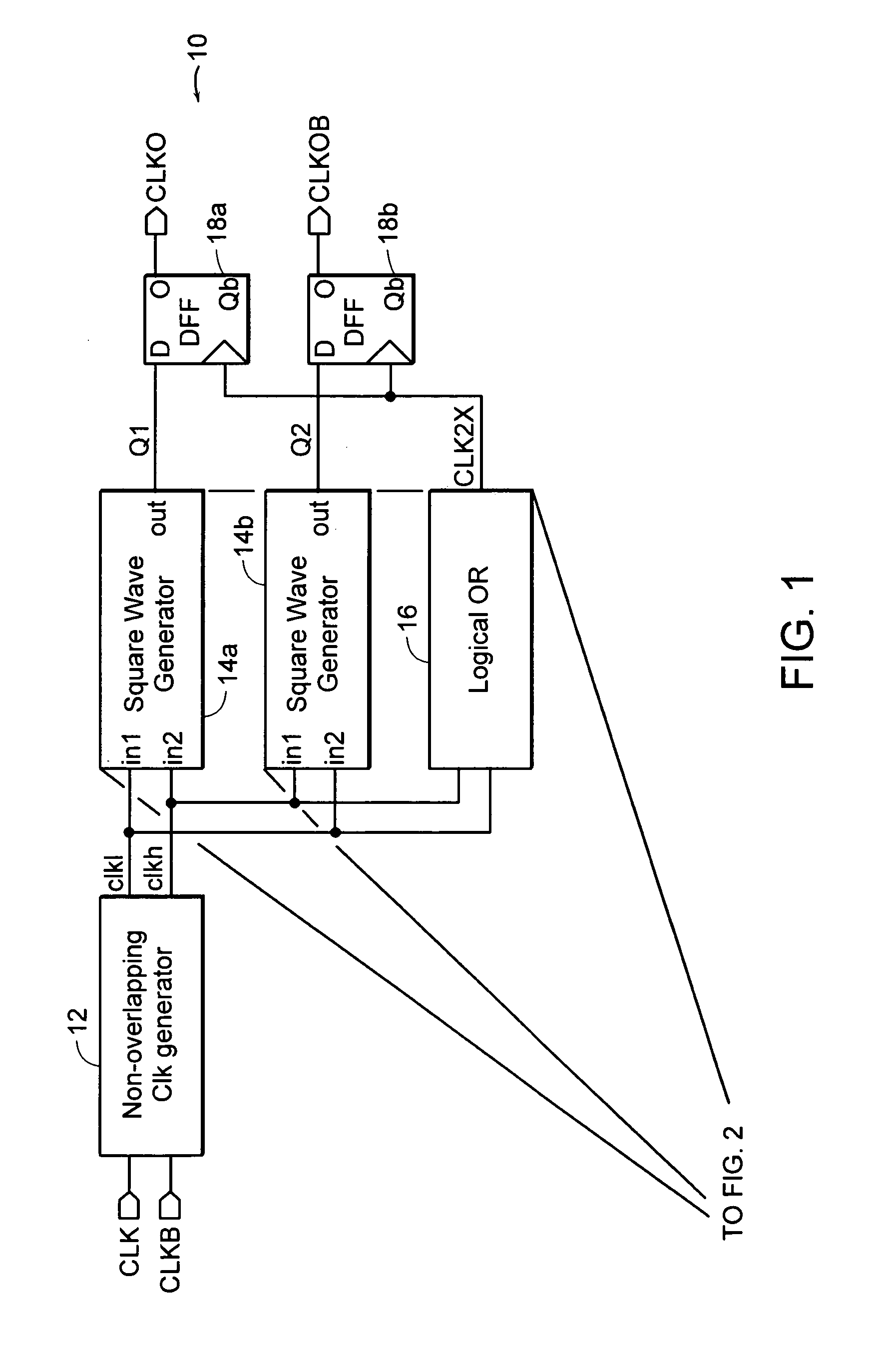

[0027]Turning now to the drawings, FIG. 1 is a block diagram of a circuit 10 used for generating complementary output signals that have little if any skew. Circuit 10 includes a clock generator 12 that generally operates as a mono-stable multi-vibrator, oftentimes referred to as a “one-shot.” One-shot 12 has only one stable state and a quasi-stable state. During operation, the one-shot remains in its stable state until a triggering signal is received, such as a rising edge on the true input clock signal (CLK) or the rising edge of the inverted input clock signal (CLKB). Upon receipt of the rising edges, the one-shot changes to the quasi-stable state for a fixed period of time. That time value is predetermined based on the cycle length of the true and inverted complementary pair of input signals. It is generally desired that the fixed period of time be somewhere less than ¼ cycle of the complementary pair of input signals, both of which transition at the same rate.

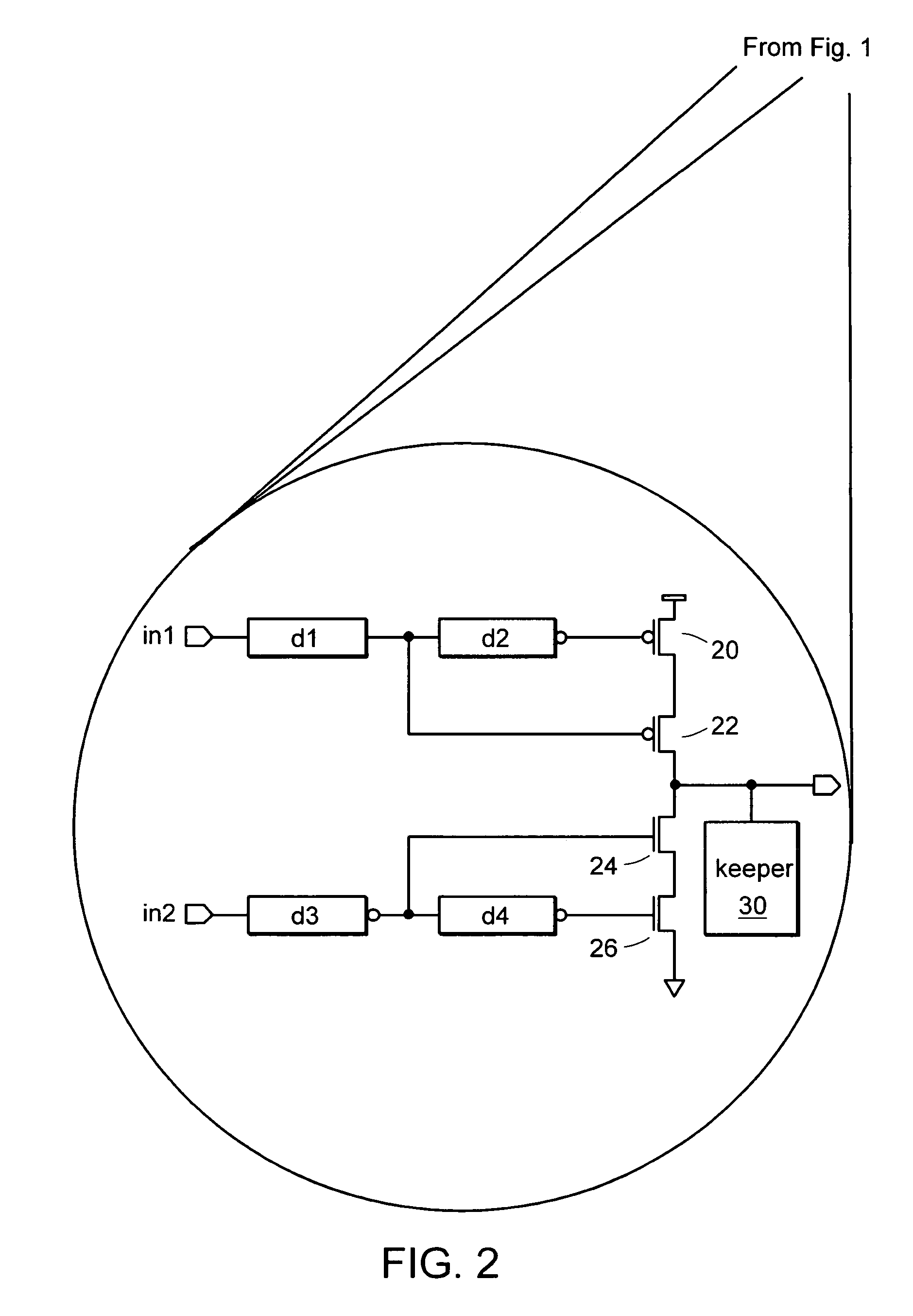

[0028]Circuit 10 al...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More