Patents

Literature

141 results about "Resistor ladder" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

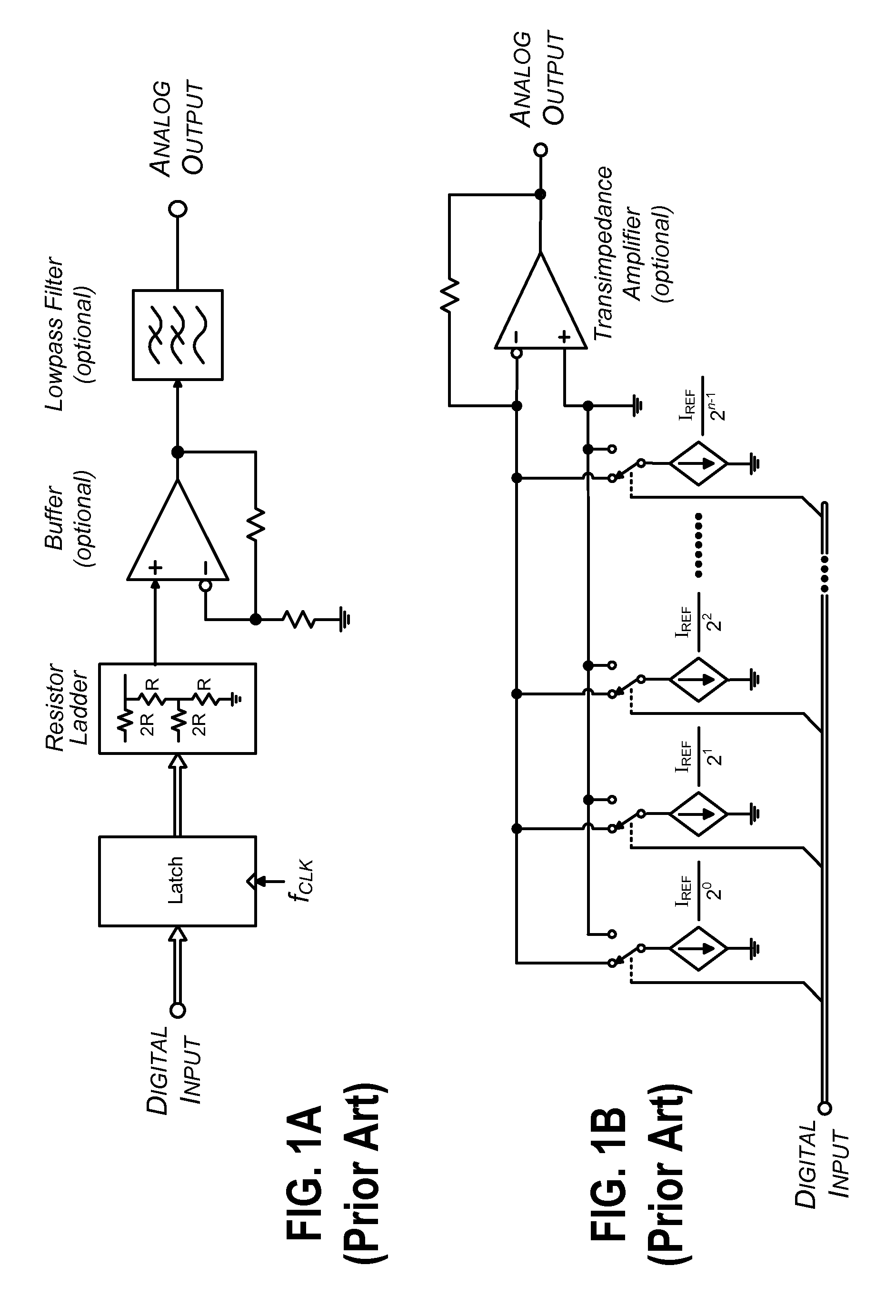

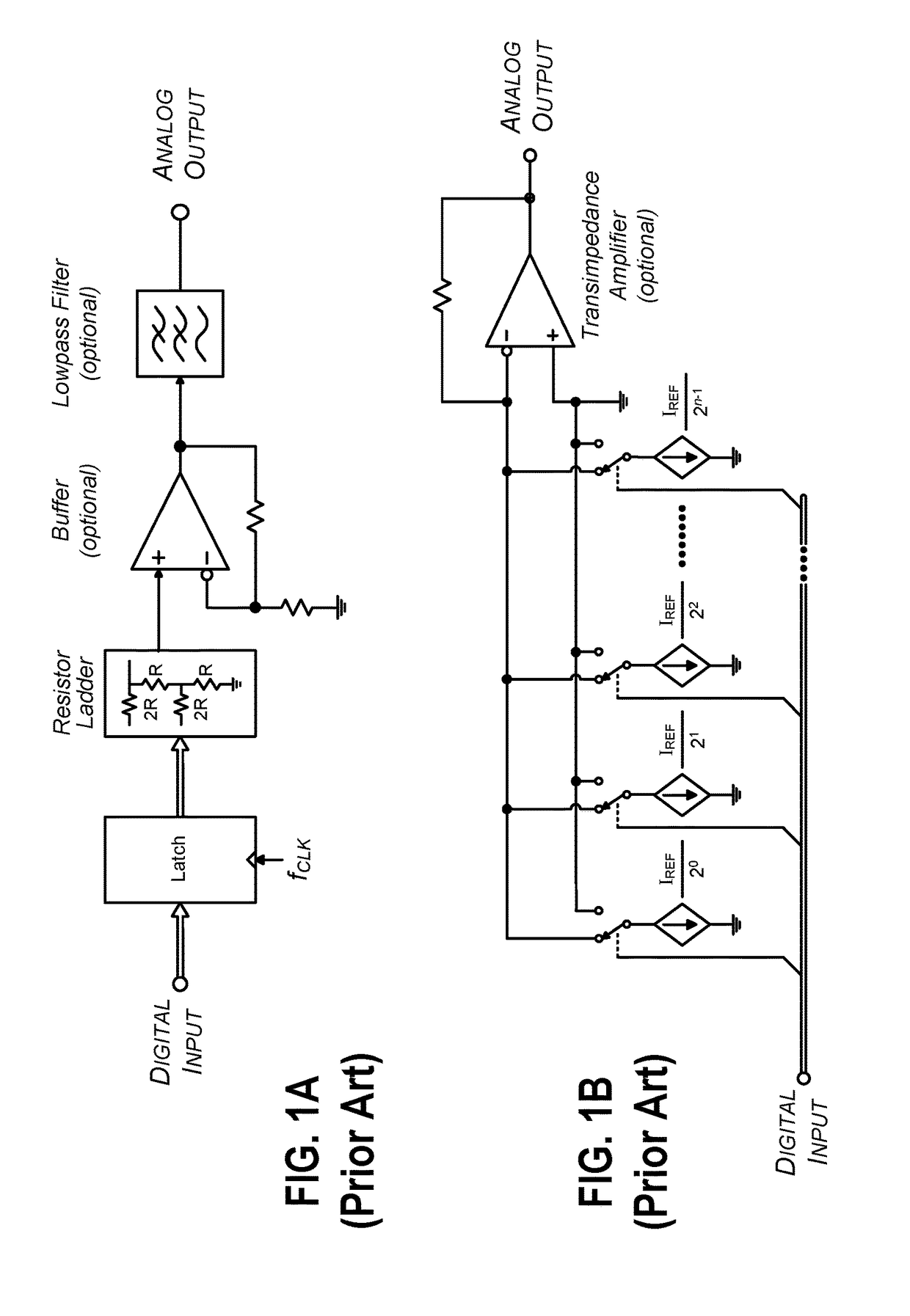

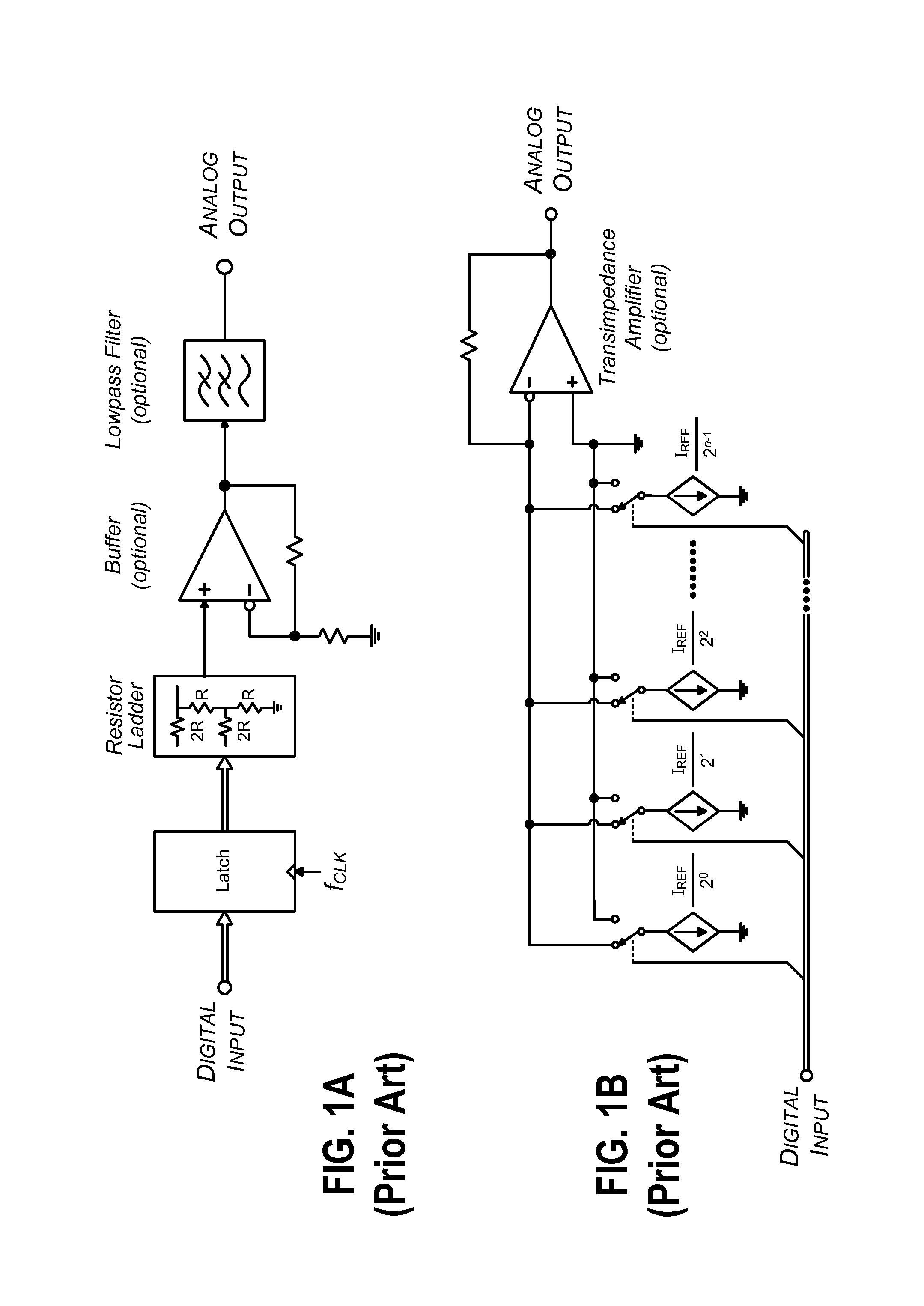

A resistor ladder is an electrical circuit made from repeating units of resistors. Two configurations are discussed below, a string resistor ladder and an R–2R ladder. An R–2R ladder is a simple and inexpensive way to perform digital-to-analog conversion, using repetitive arrangements of precise resistor networks in a ladder-like configuration. A string resistor ladder implements the non-repetitive reference network.

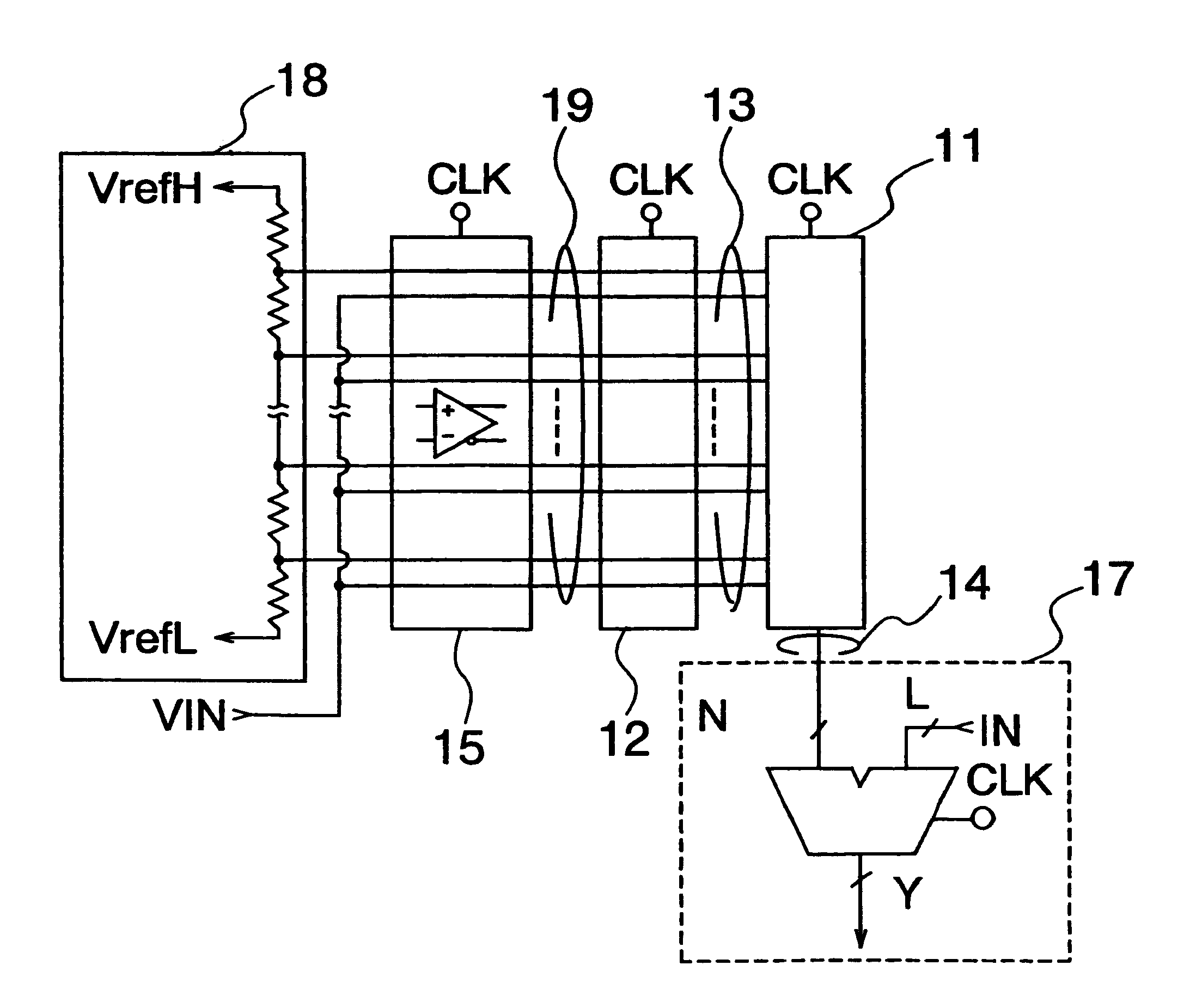

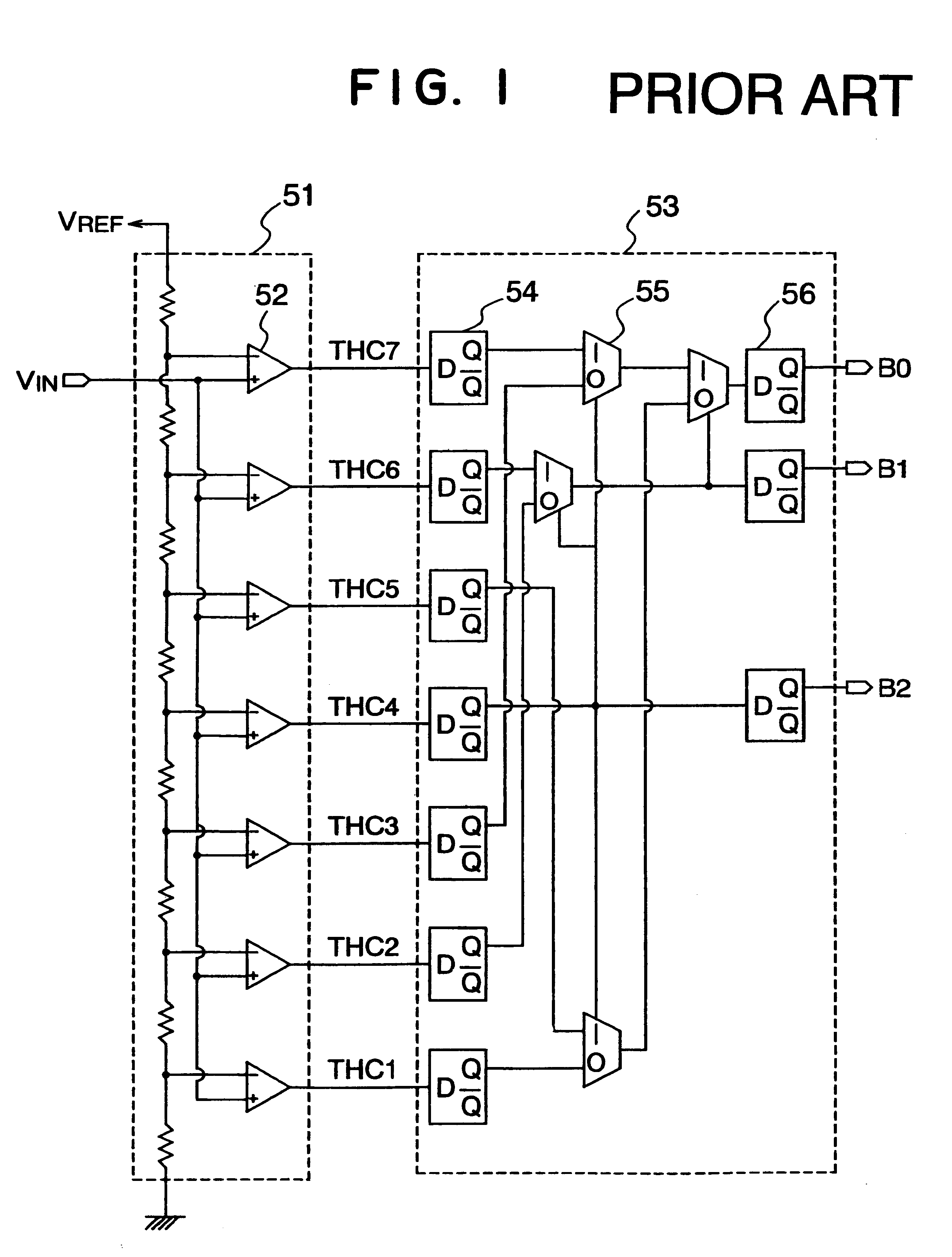

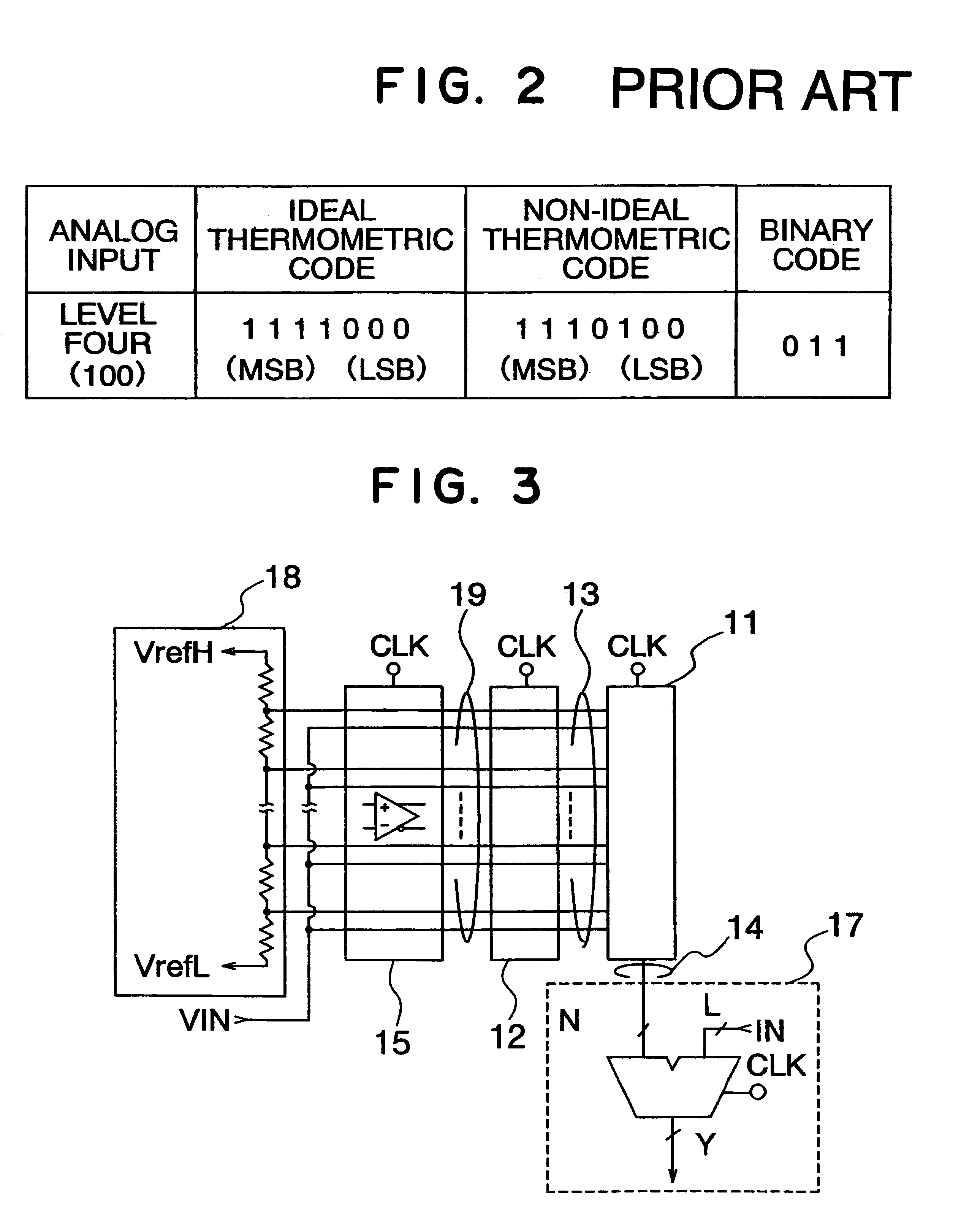

A/D converter having a dynamic encoder

InactiveUS6232908B1Increase speedReduce circuit sizeElectric signal transmission systemsAnalogue-digital convertersBuck converterA d converter

An A / D converter includes a resistor ladder for generating a plurality of reference potentials, a comparing section for comparing each of the reference potentials against an input analog signal to output a thermometric code, and a dynamic encoder composed of a combinational circuit to encode the thermometric code to a binary code by responding a clock signal. The A / D conversion is finished in a single clock cycle at a high speed, with a reduced number of elements and reduced power dissipation.

Owner:NEC ELECTRONICS CORP

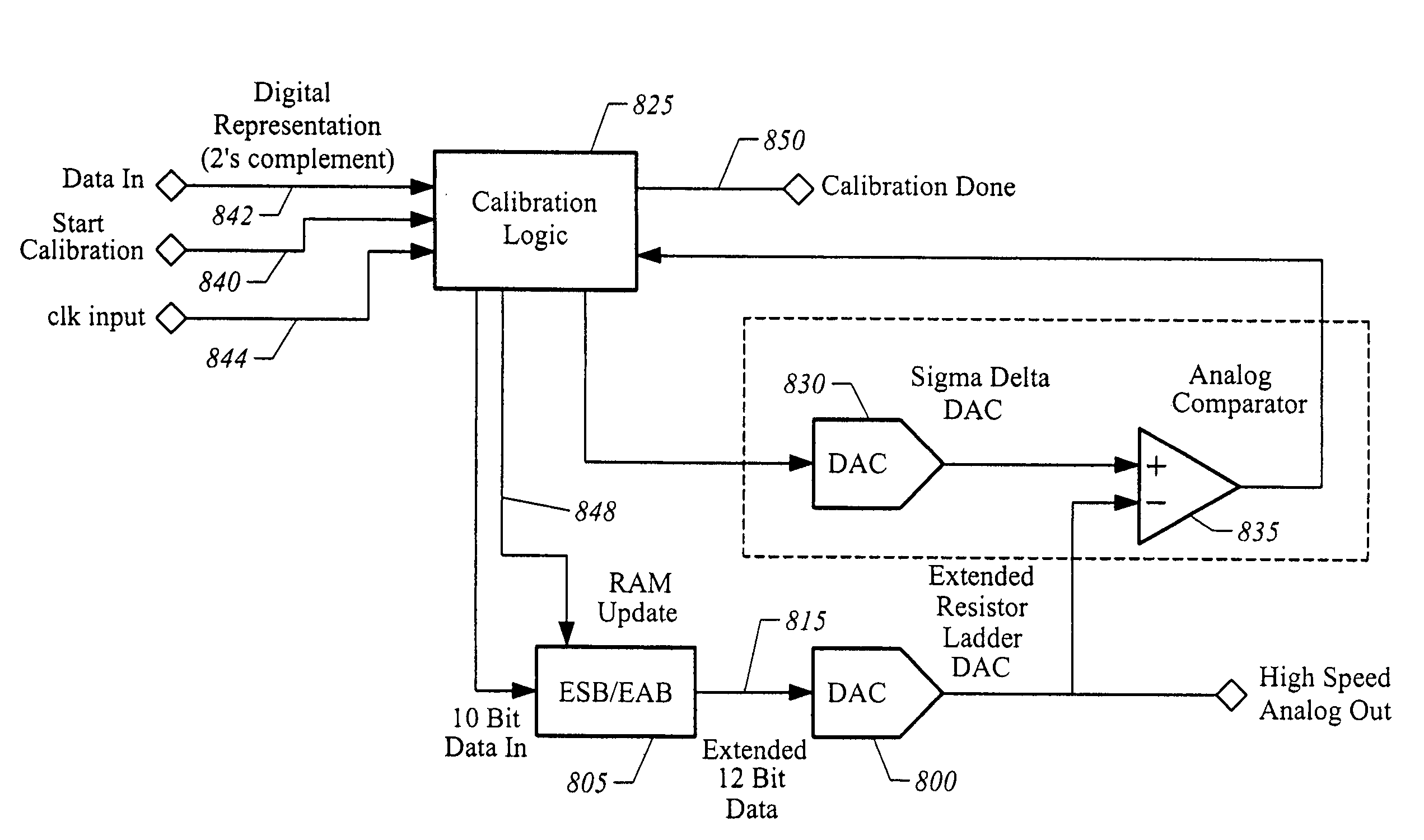

Calibration of resistor ladder using difference measurement and parallel resistive correction

InactiveUS20030151532A1Electric signal transmission systemsAnalogue-digital convertersDifferential measurementComplementary pair

A calibration system and method for a resistor ladder that employs relative measurement and adjustment between pairs of resistors. The system includes a resistor tree of complementary pairs of programmable resistors coupled to the resistor ladder, a measurement circuit that measures voltage differences between complementary pairs of programmable resistors, and control logic. The control logic controls the measurement circuit to measure a voltage difference between each complementary pair of programmable resistors and adjusts the relative resistance of each complementary pair of programmable resistors to equalize voltage. The measurement is facilitated by a sigma-delta ADC that converts a measured voltage difference into a bit stream. The programmable resistors are implemented with binary weighted resistors that are digitally adjusted one LSB at a time. Lower and upper adjustment thresholds may be employed to avoid unnecessary over-adjustments while maintaining a requisite level of accuracy.

Owner:INTERSIL INC

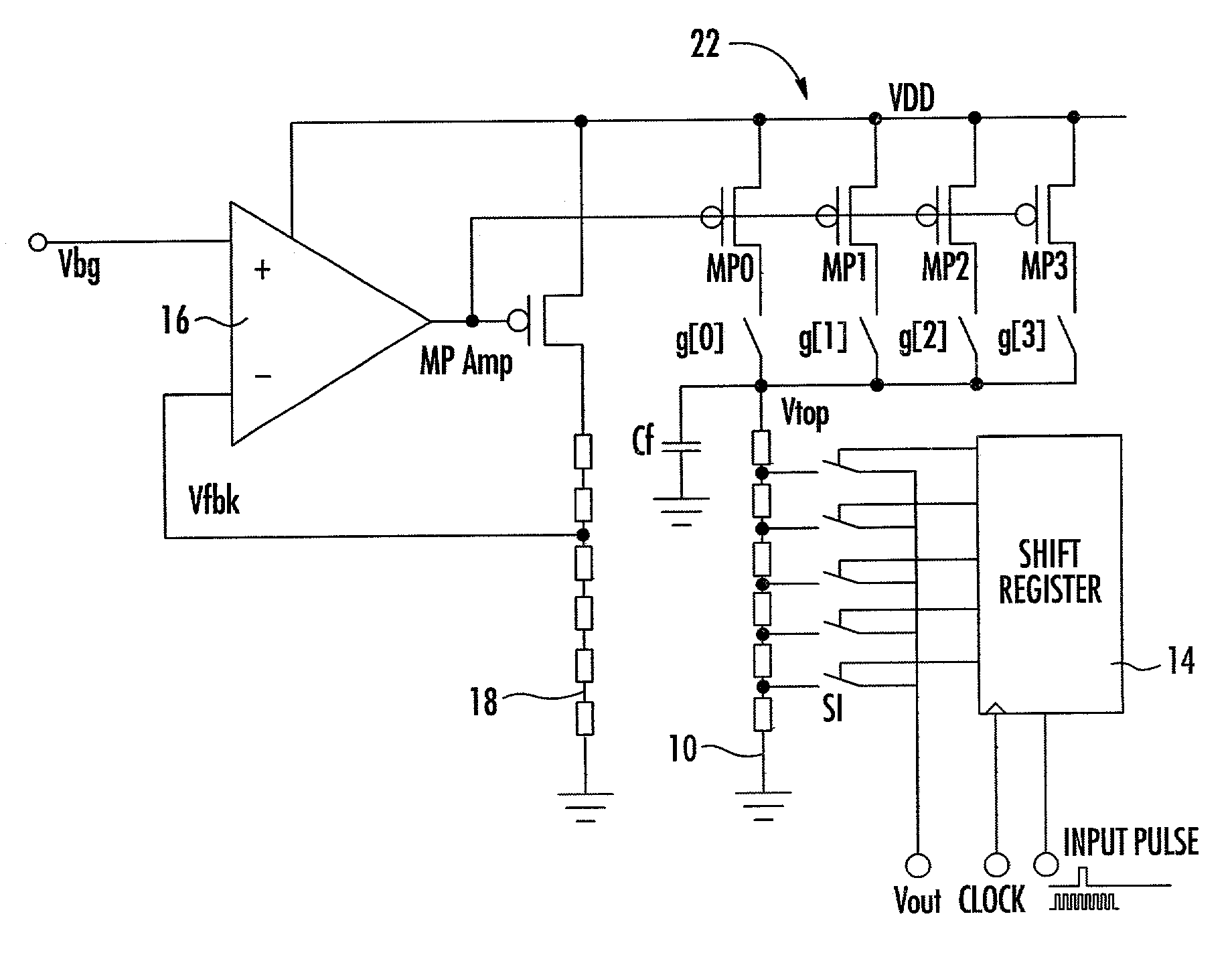

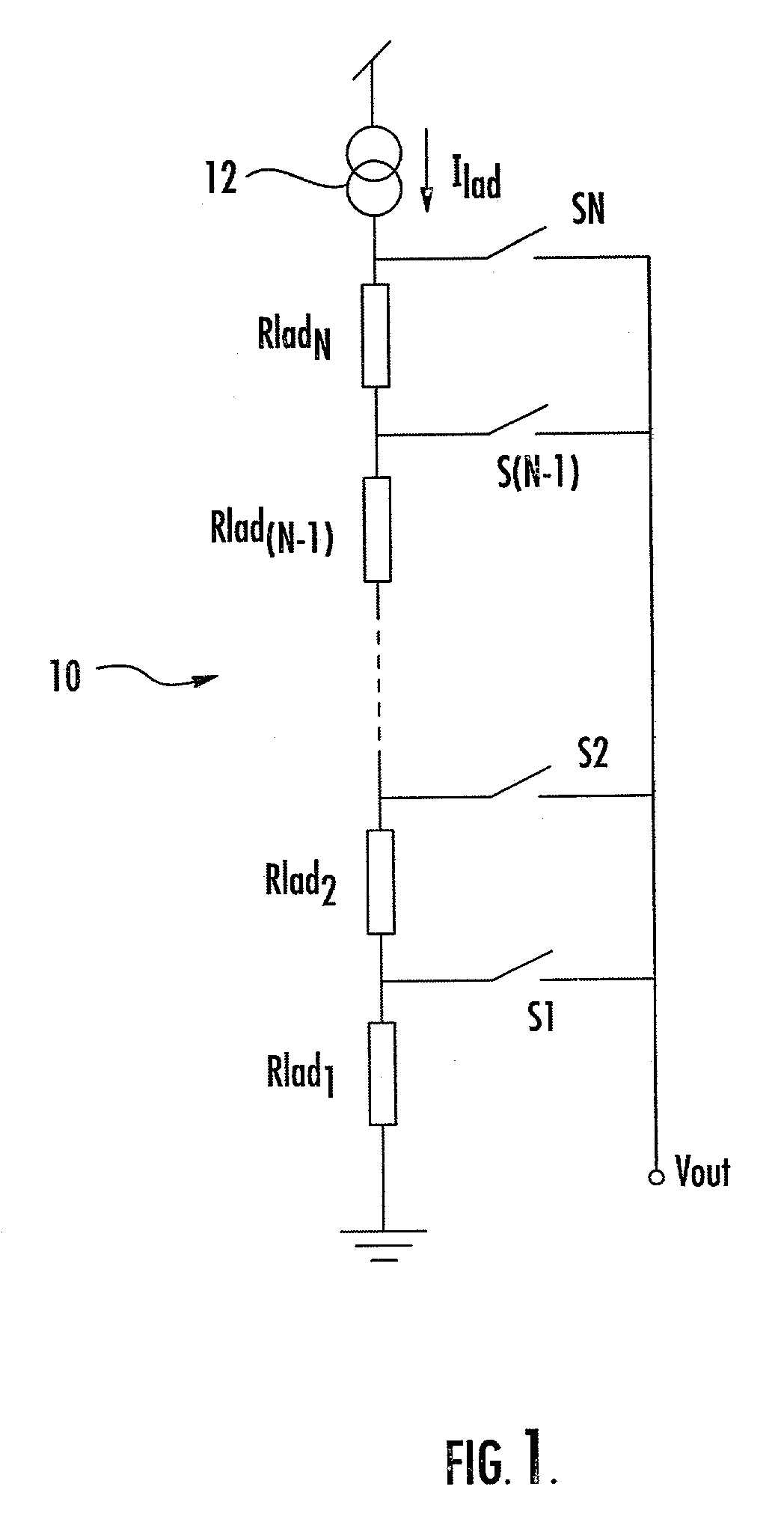

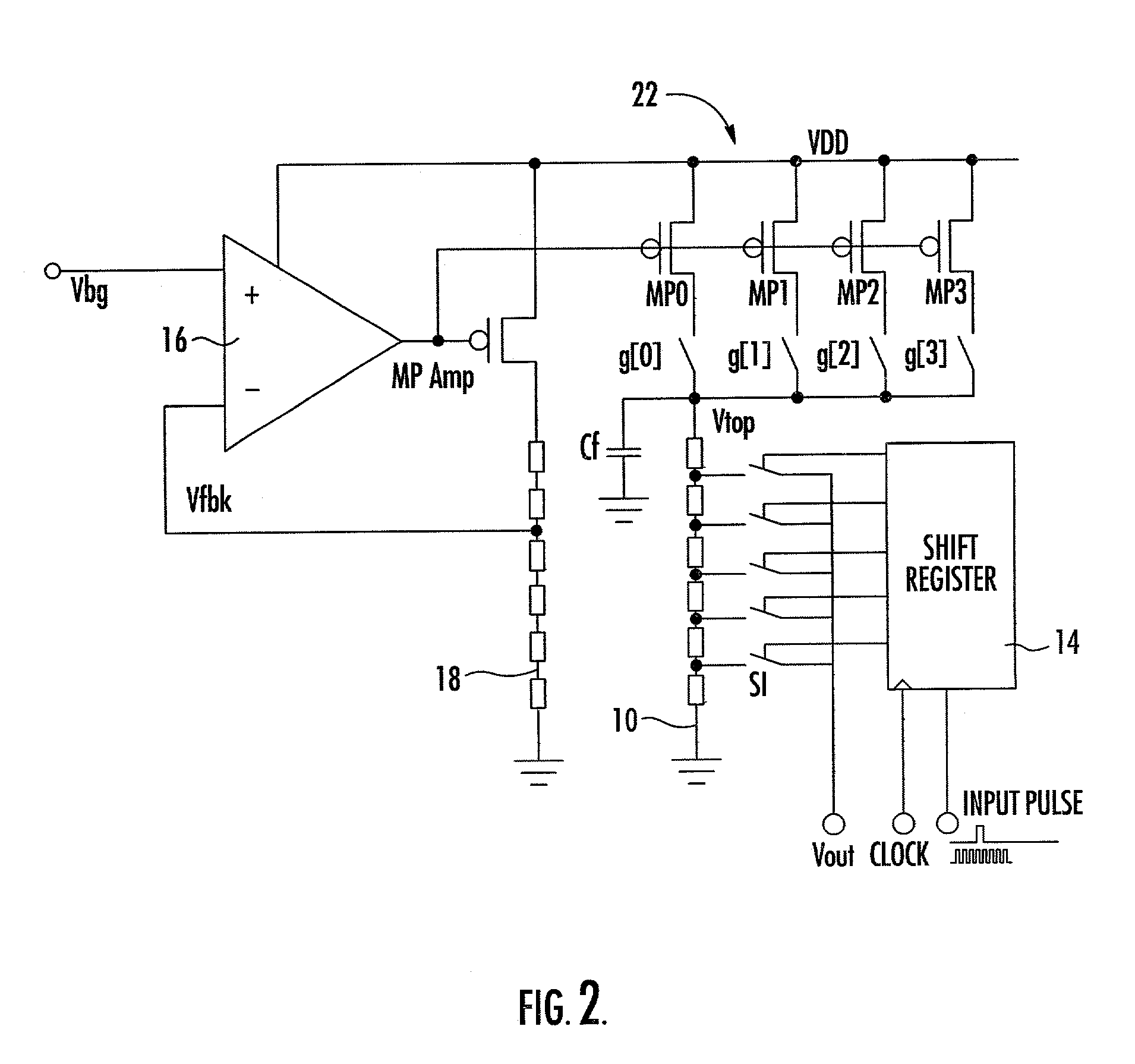

Ramp generator for image sensor ADC

A ramp generator includes a resistance ladder supplied with a constant current. Switches are closed in sequence by a shift register to provide a stepped ramp output. The constant current is controlled by referencing an on-chip bandgap voltage that is used as an input to a feedback circuit controlling current through a reference resistor ladder.

Owner:STMICROELECTRONICS LTD

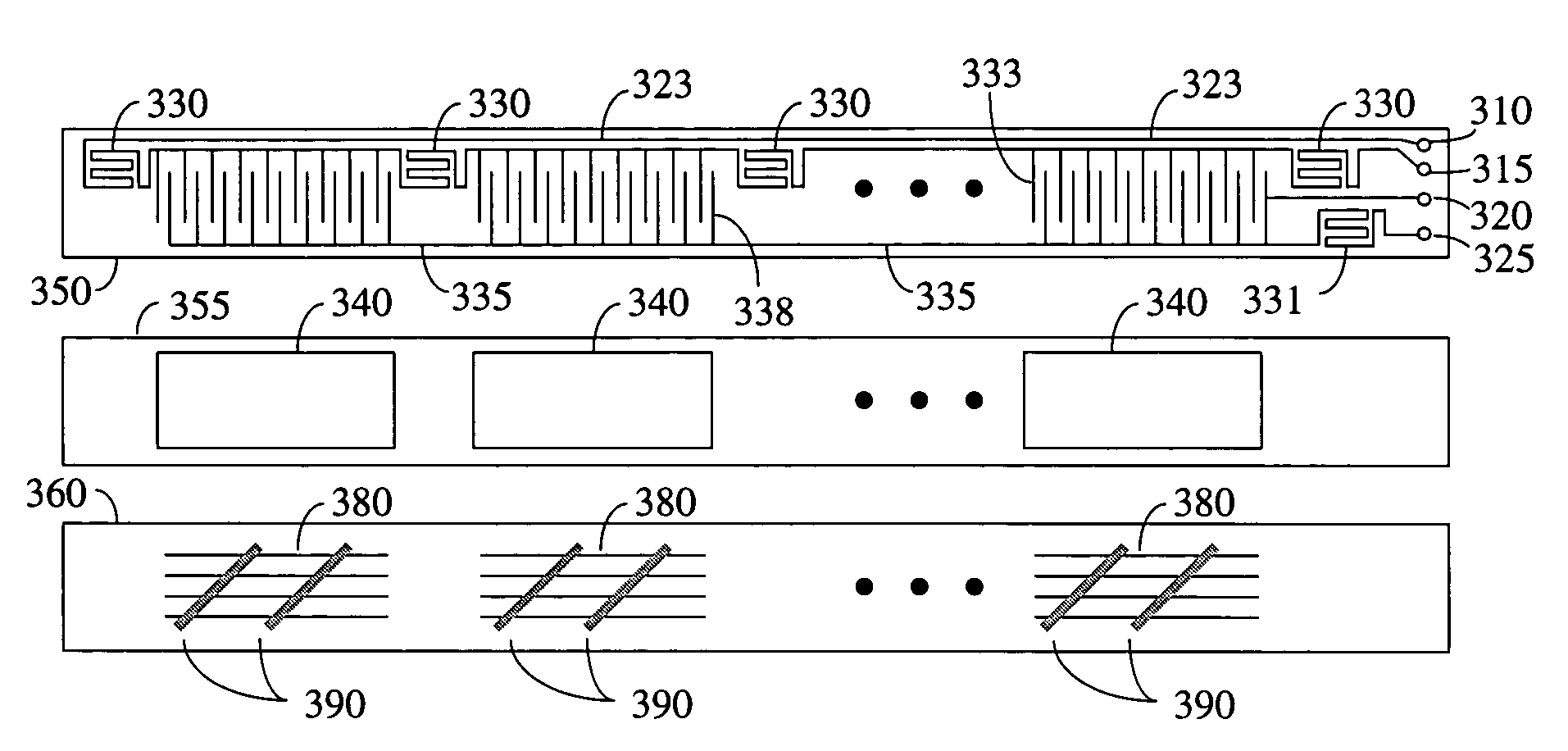

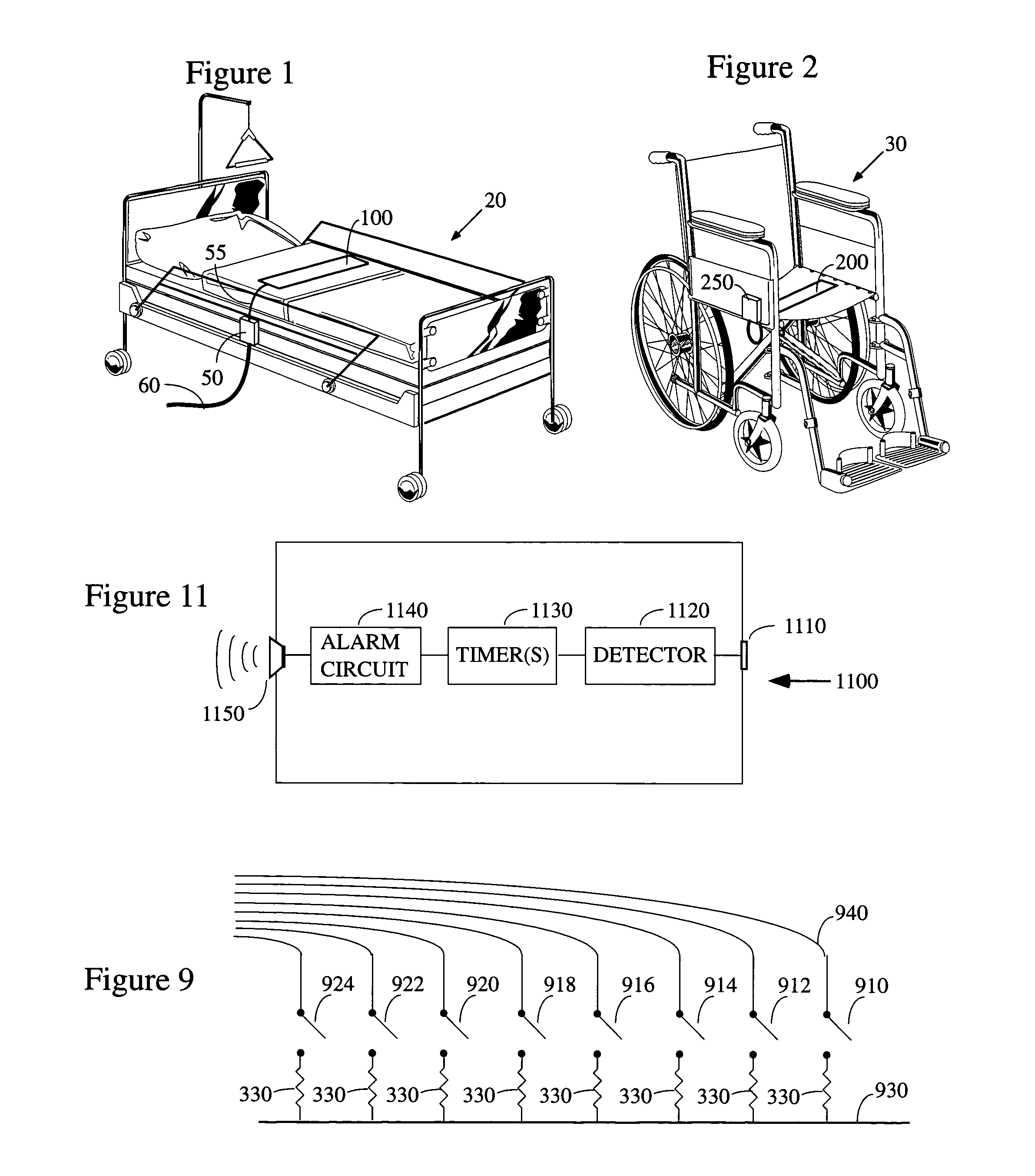

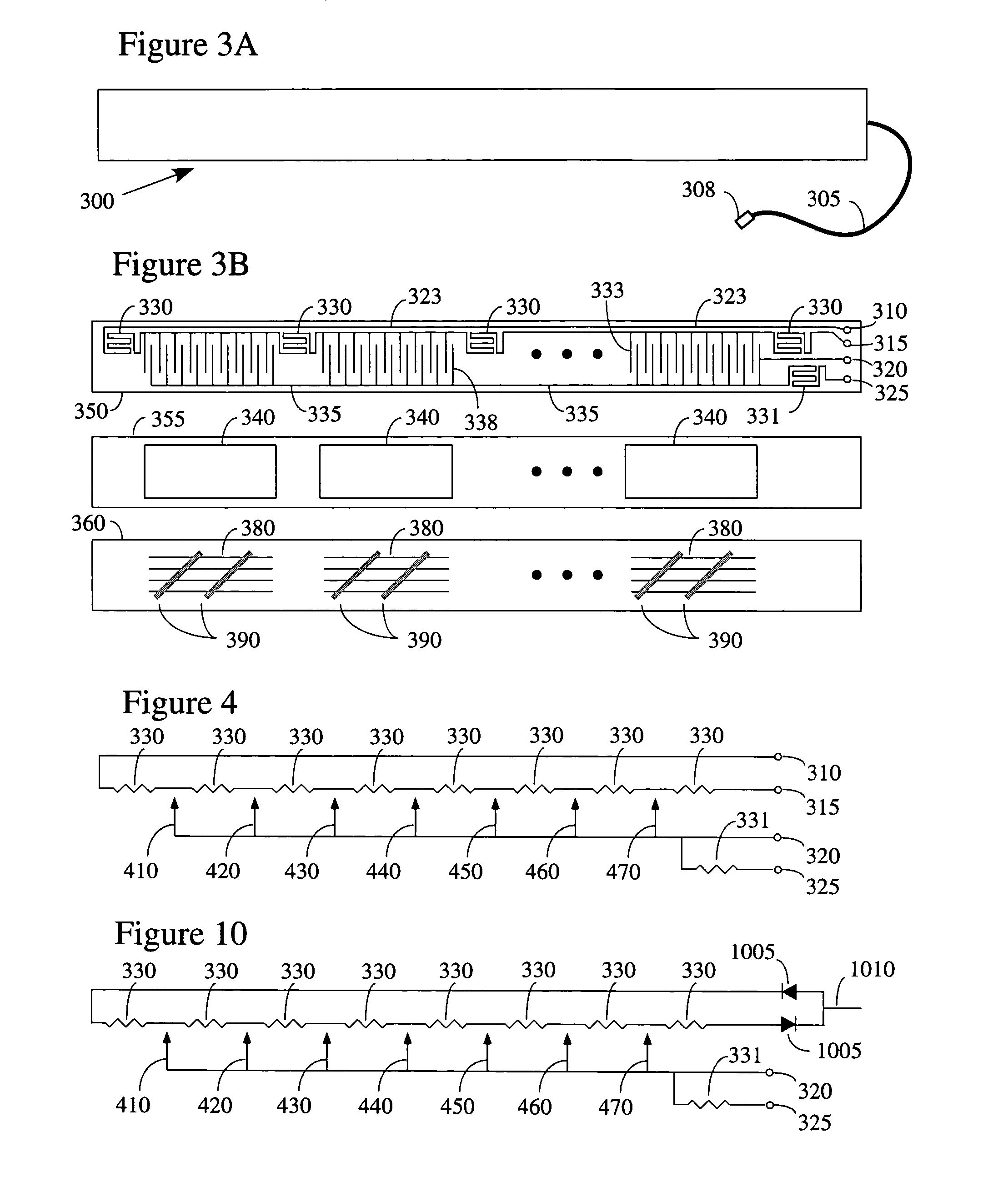

Sensor and method for detecting a patient's movement via position and occlusion

Owner:BED CHECK CORP

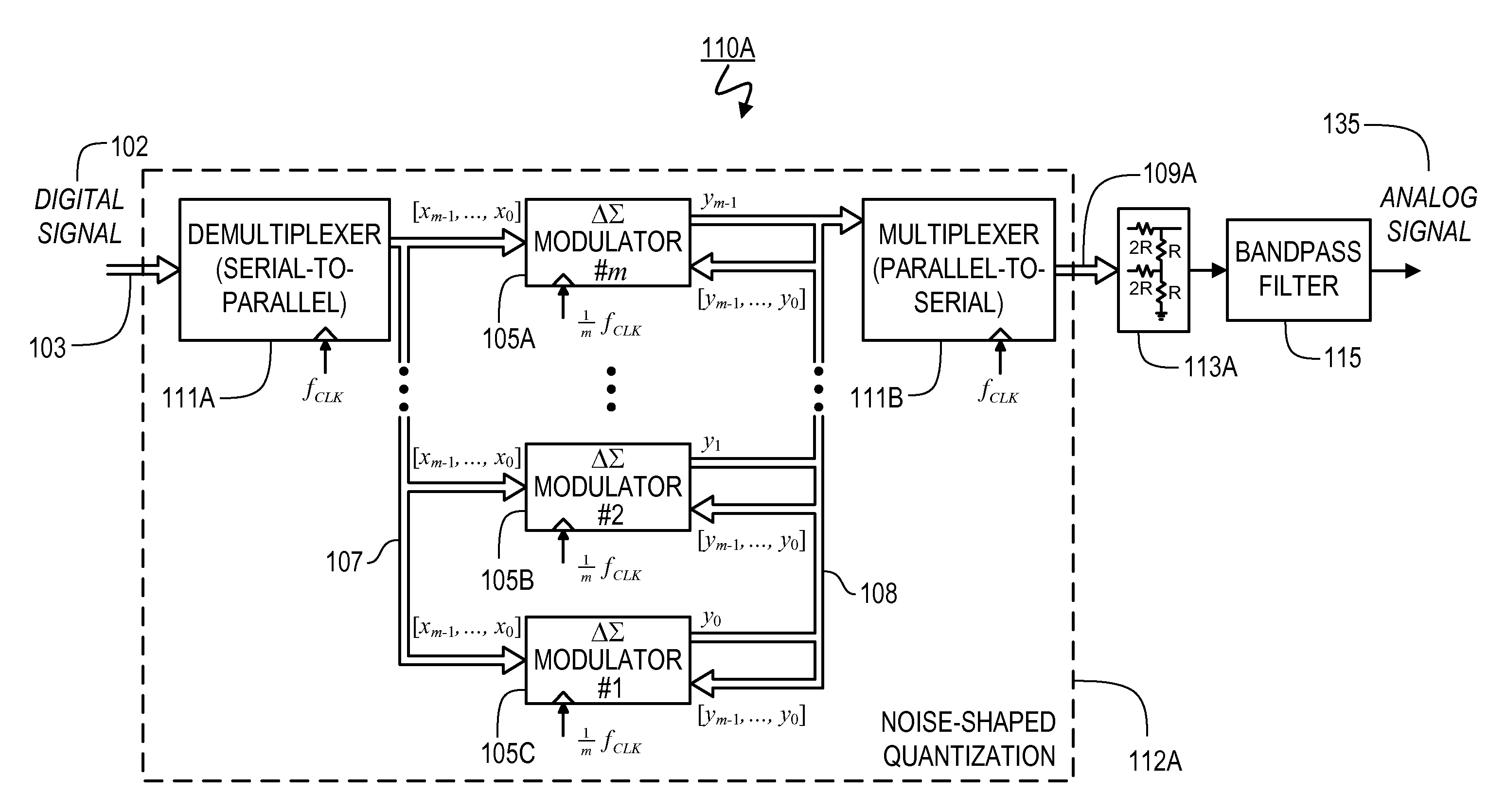

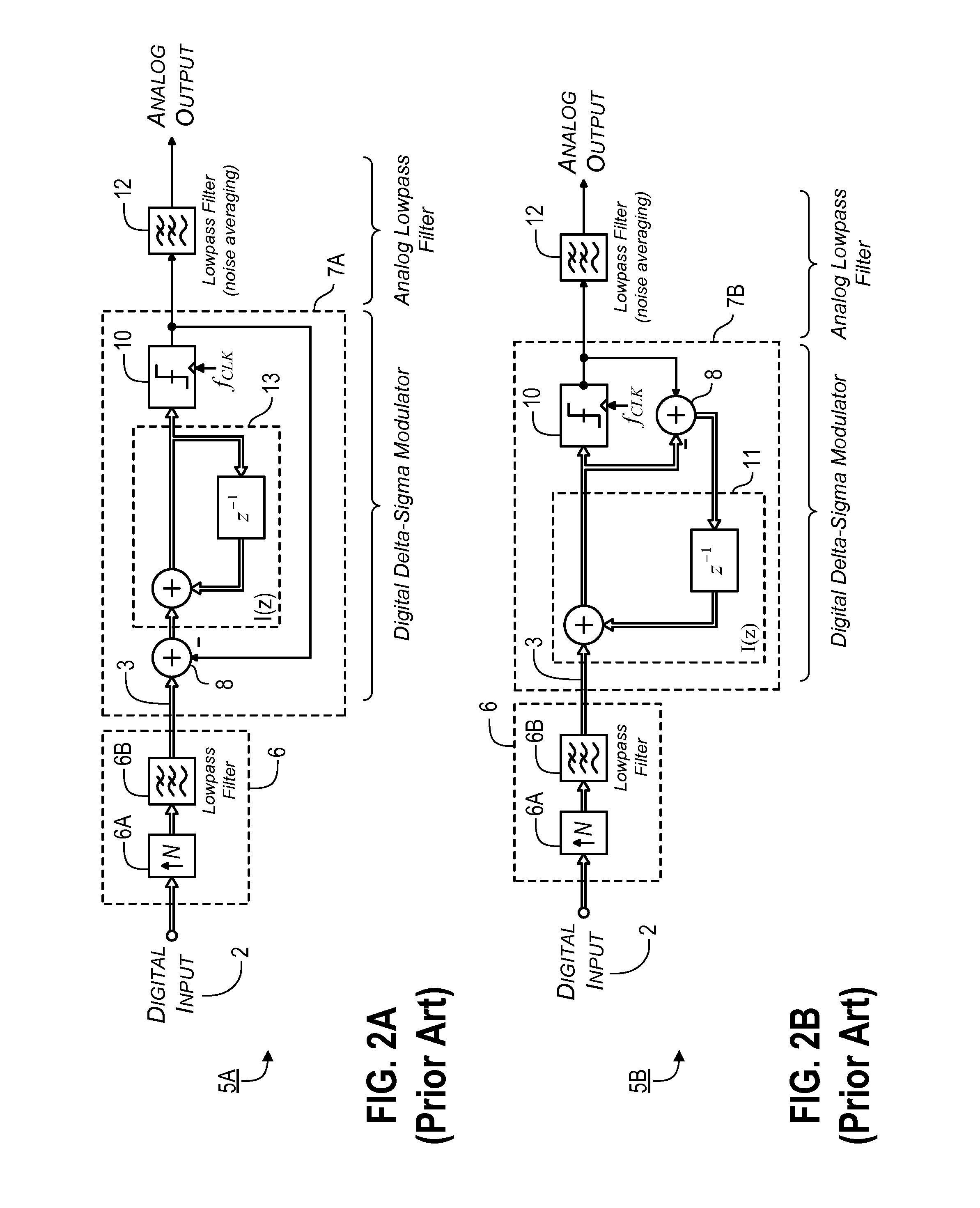

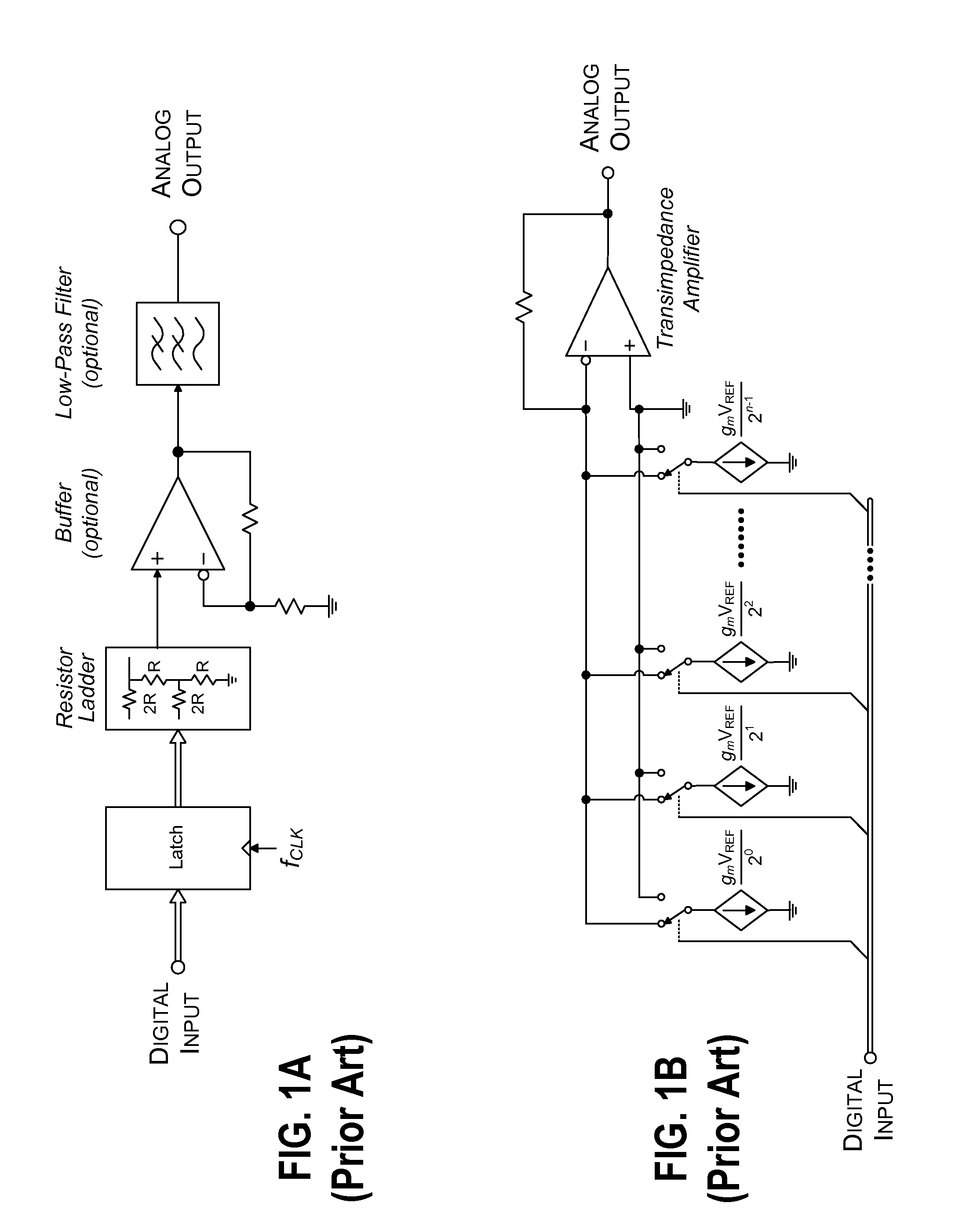

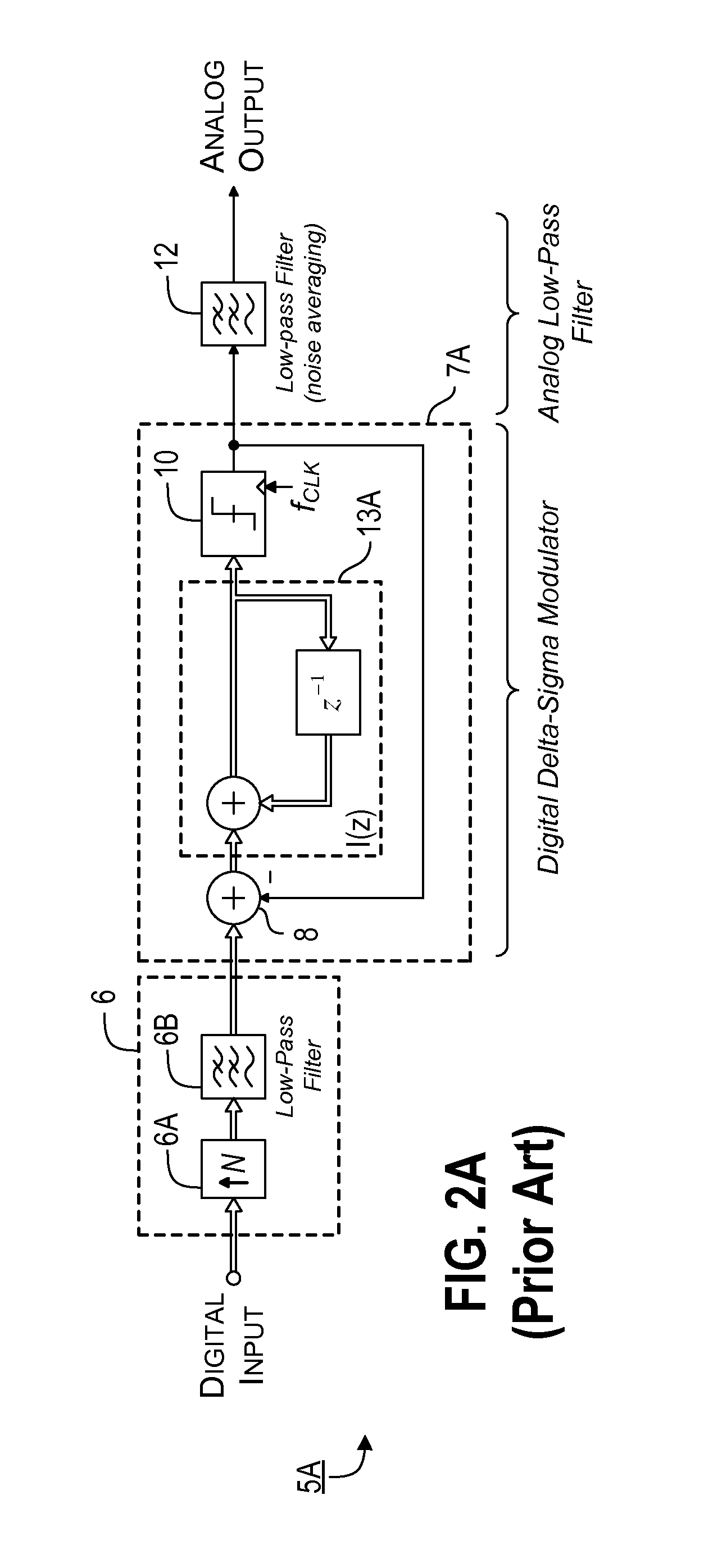

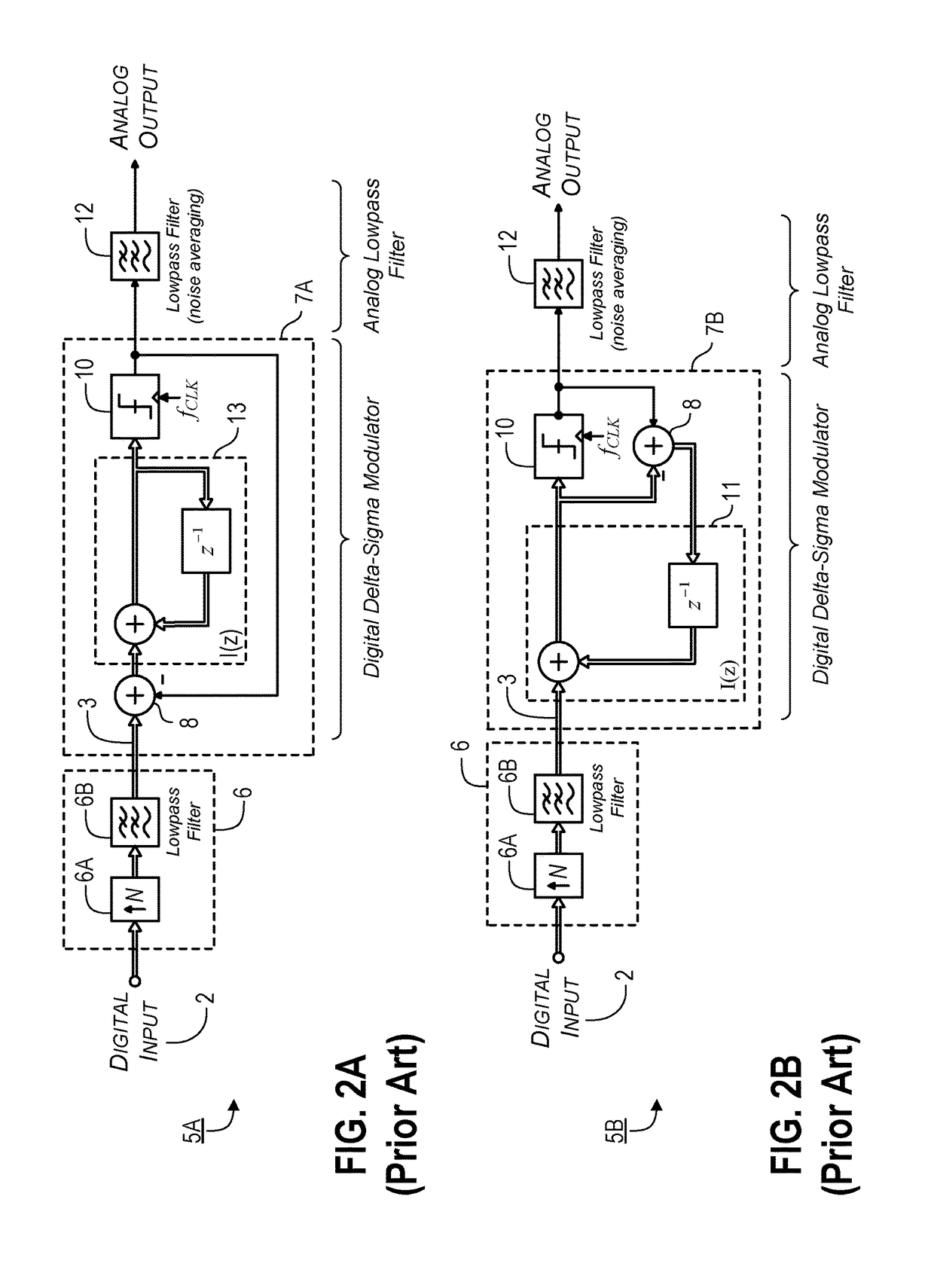

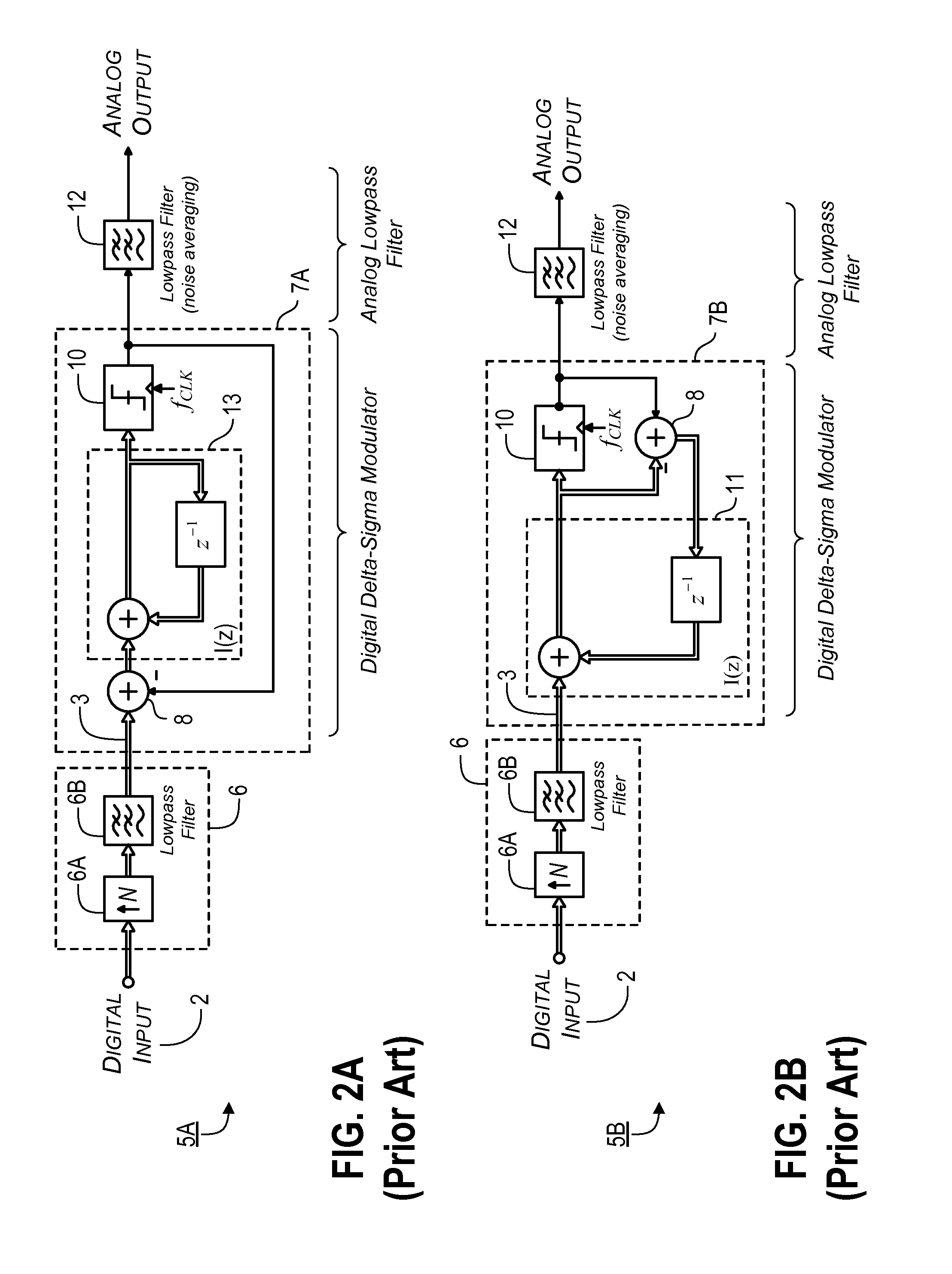

Conversion of a discrete time quantized signal into a continuous time, continuously variable signal

ActiveUS8294605B1Limit can be overcomeMinimize amplitudeElectric signal transmission systemsAnalogue conversionMulti bandAnalog signal

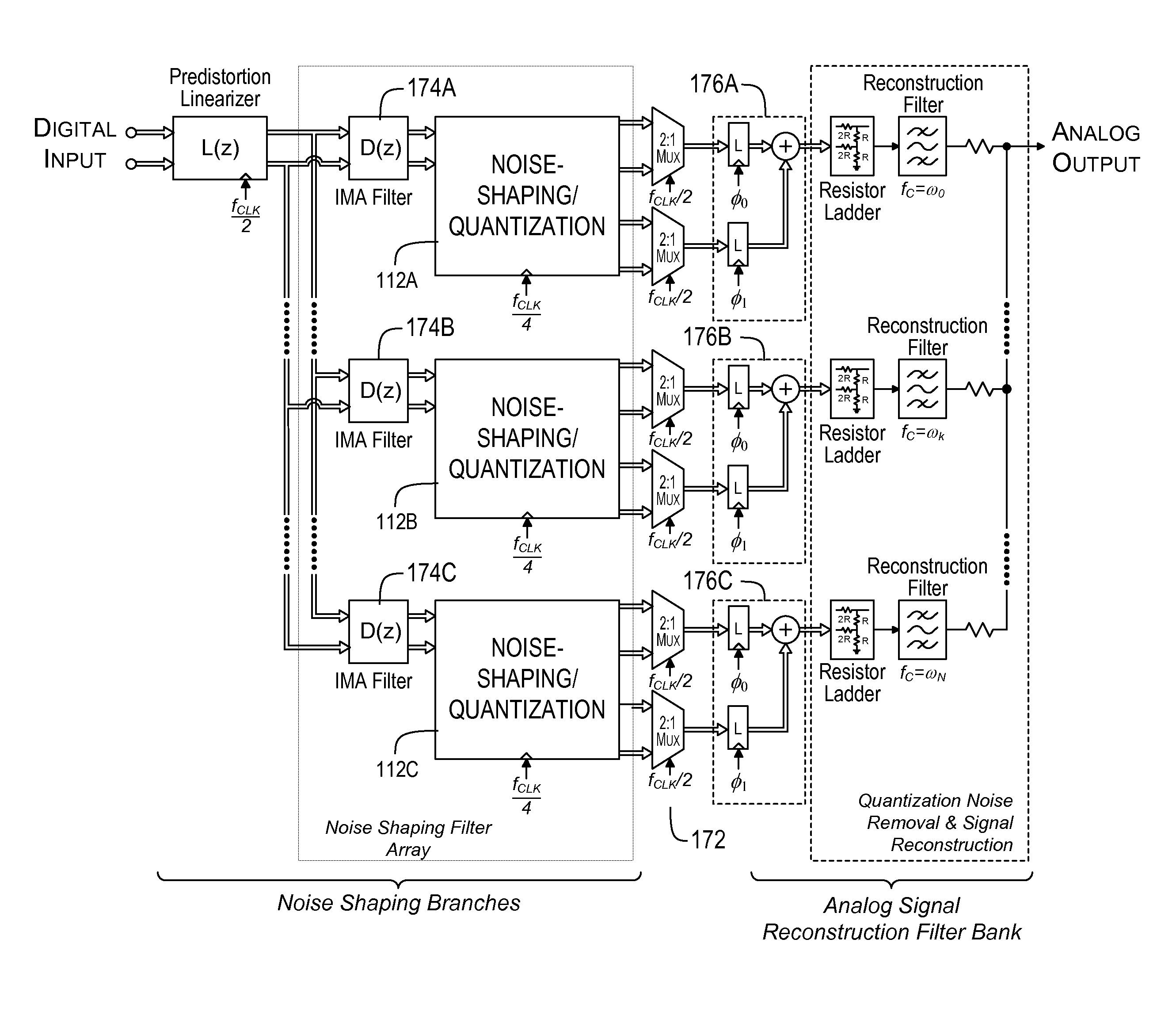

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive nonlinear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

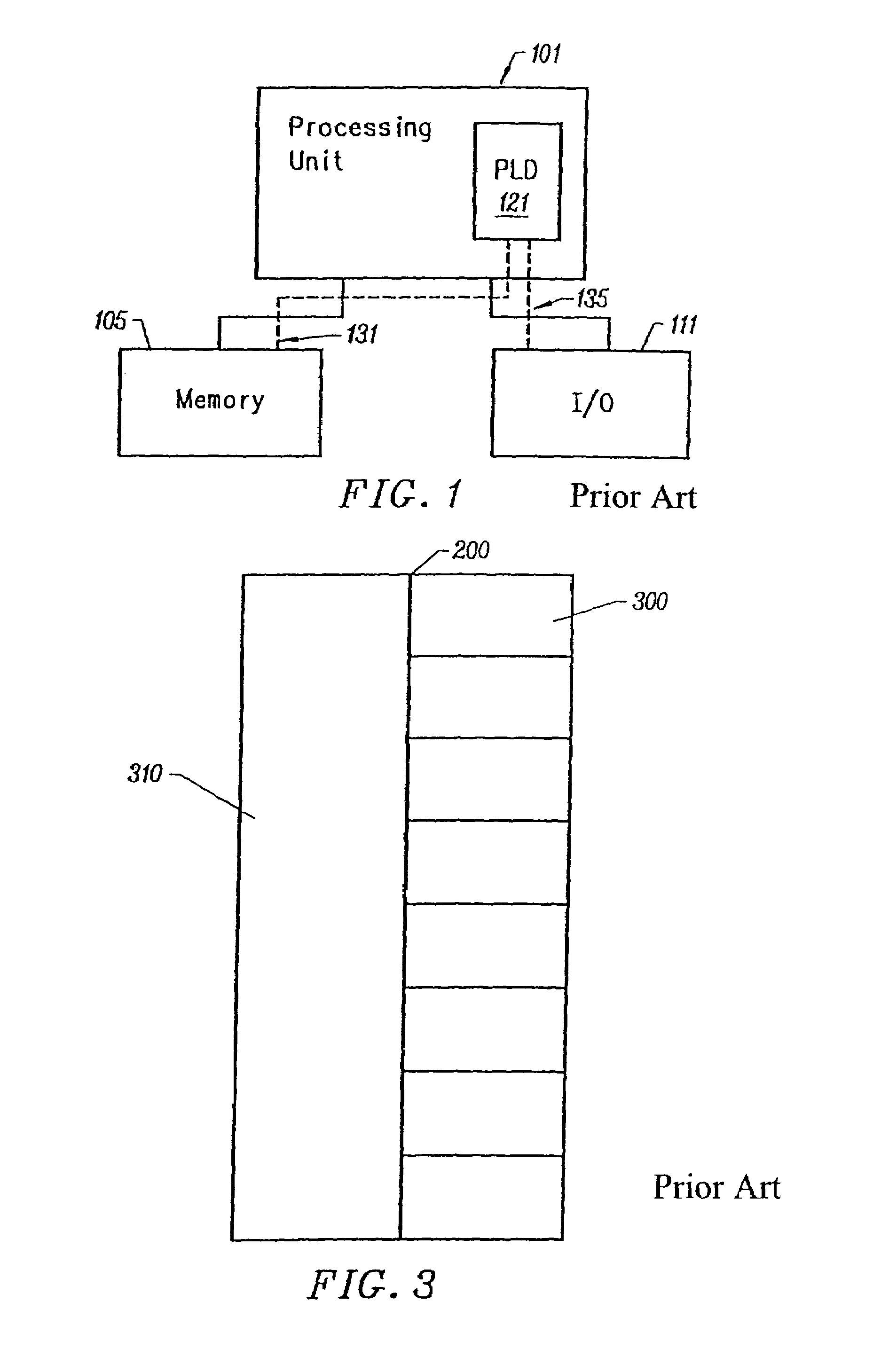

Analog-to-digital converter for programmable logic

InactiveUS6956512B1Electric signal transmission systemsResistance/reactance/impedenceProgrammable logic deviceLogic cell

Digital-to-analog and analog-to-digital conversion are implemented in or using programmable logic. The DAC and ADC circuits may be hardwired in a programmable logic integrated circuit or may be implemented using an intellectual property (IP) core. The IP core would be a series of bits to configure the logic cells and other programmable logic of an integrated circuit to include one or more DACs or ADC, or both on the same integrated circuit. The DAC may be a sigma-delta-modulator-based implementation or a resistor-ladder-based implementation.

Owner:ALTERA CORP

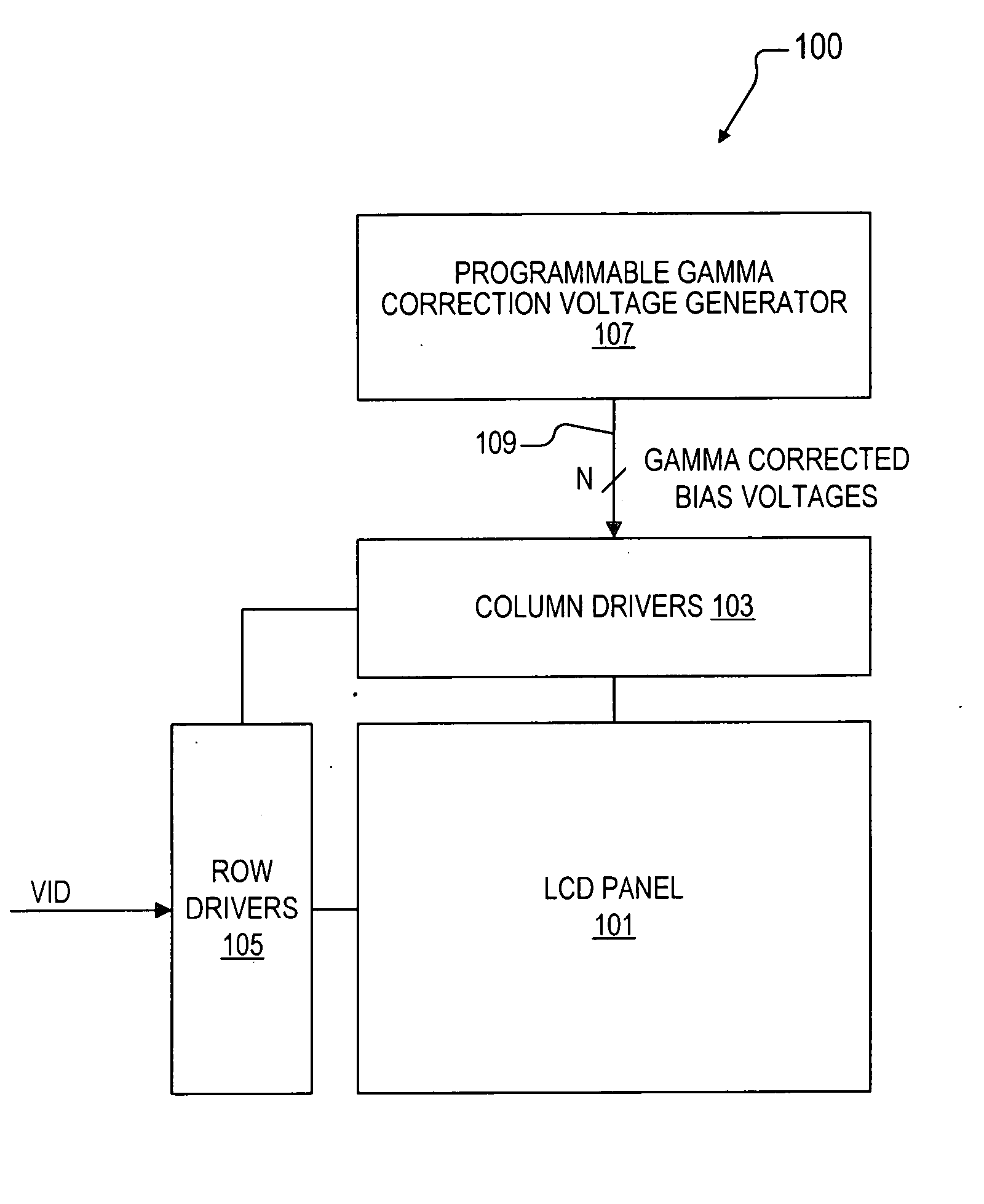

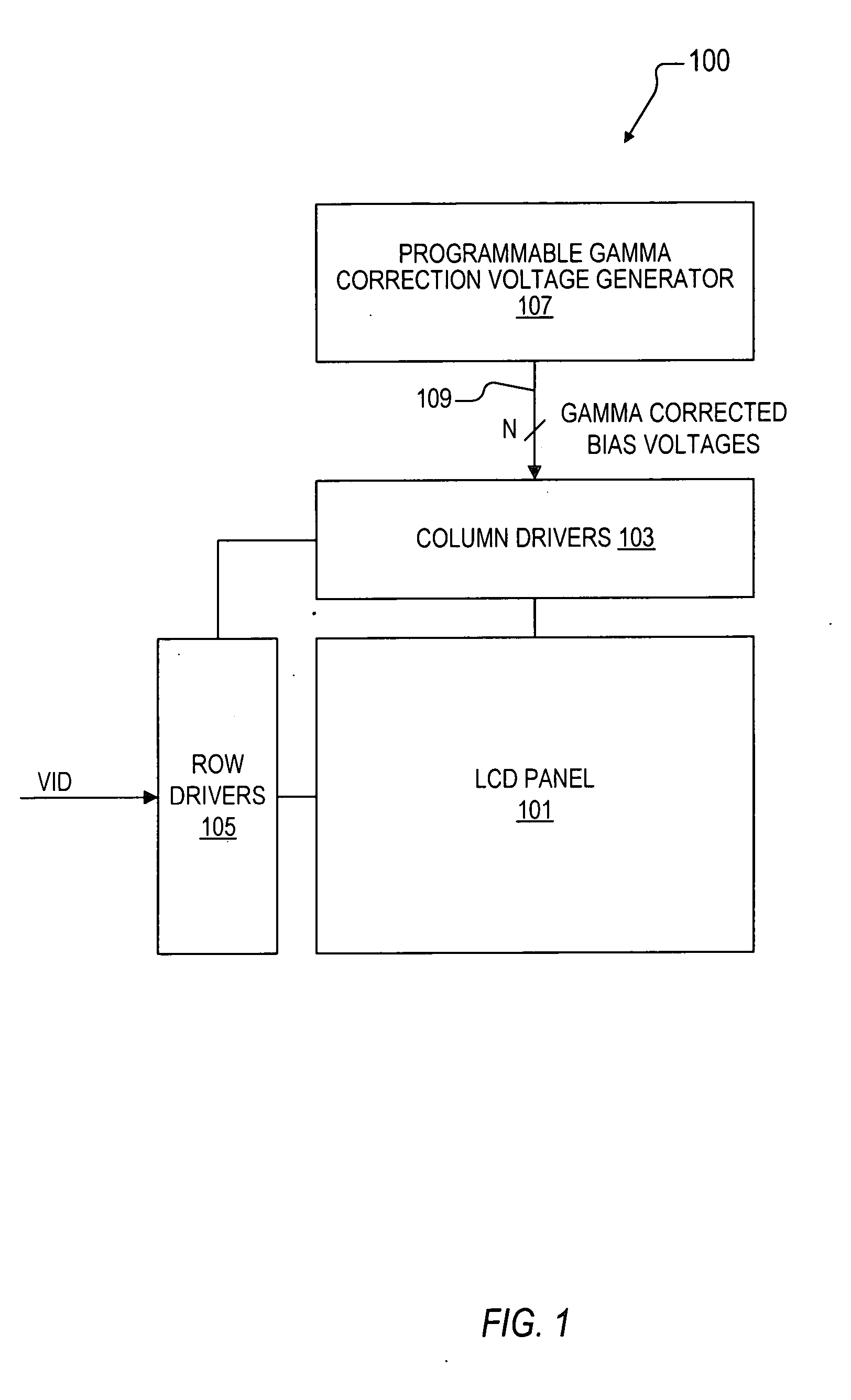

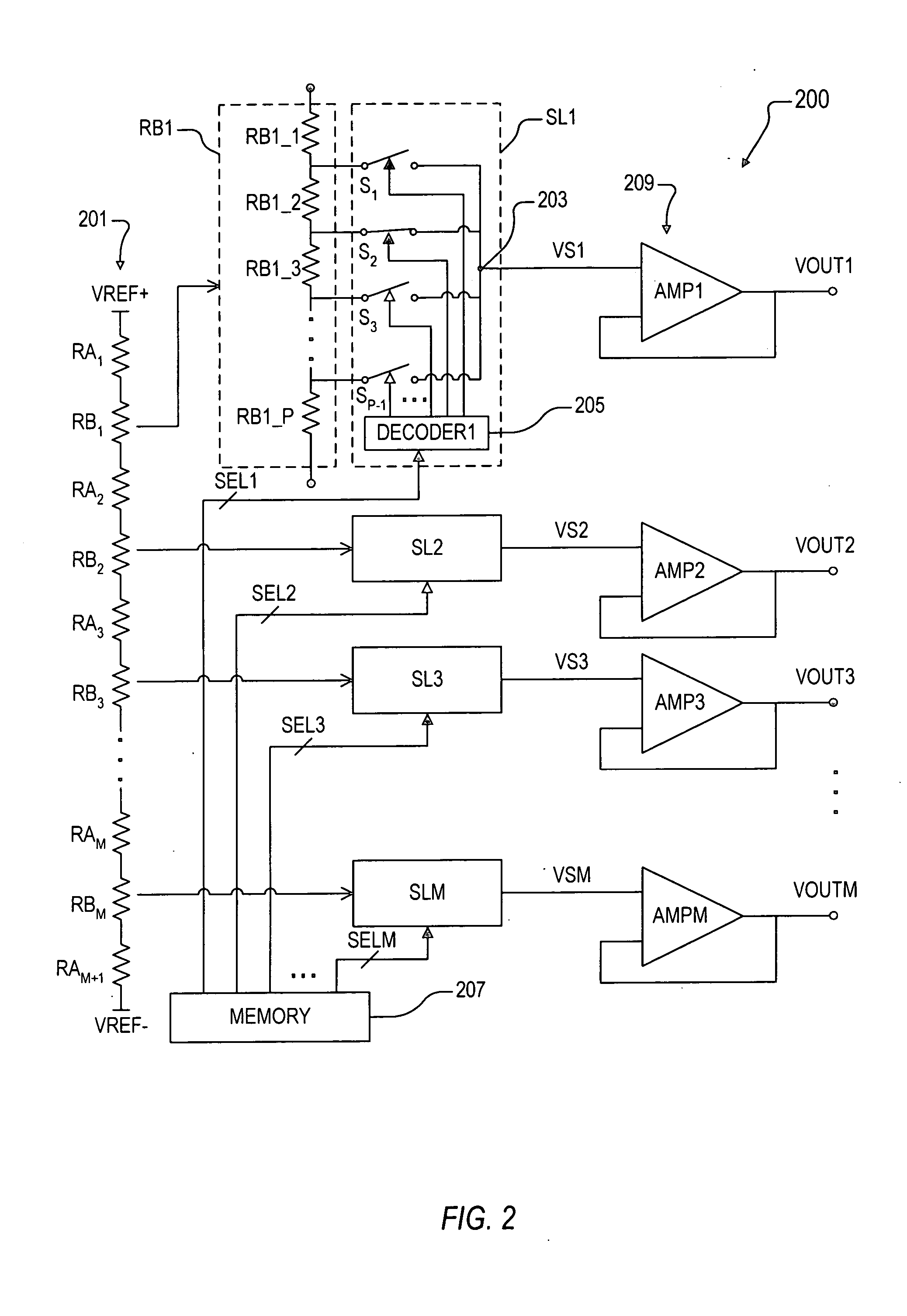

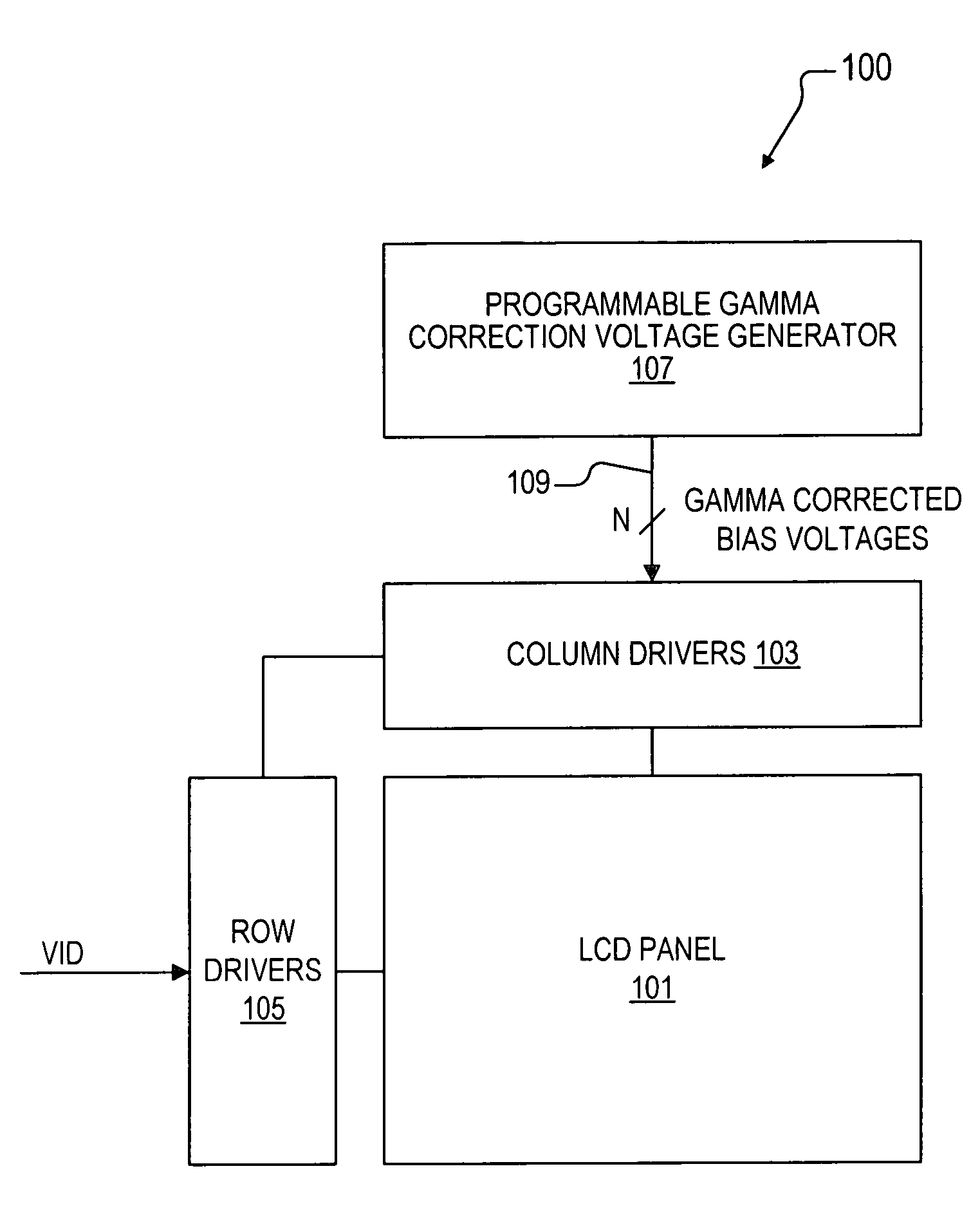

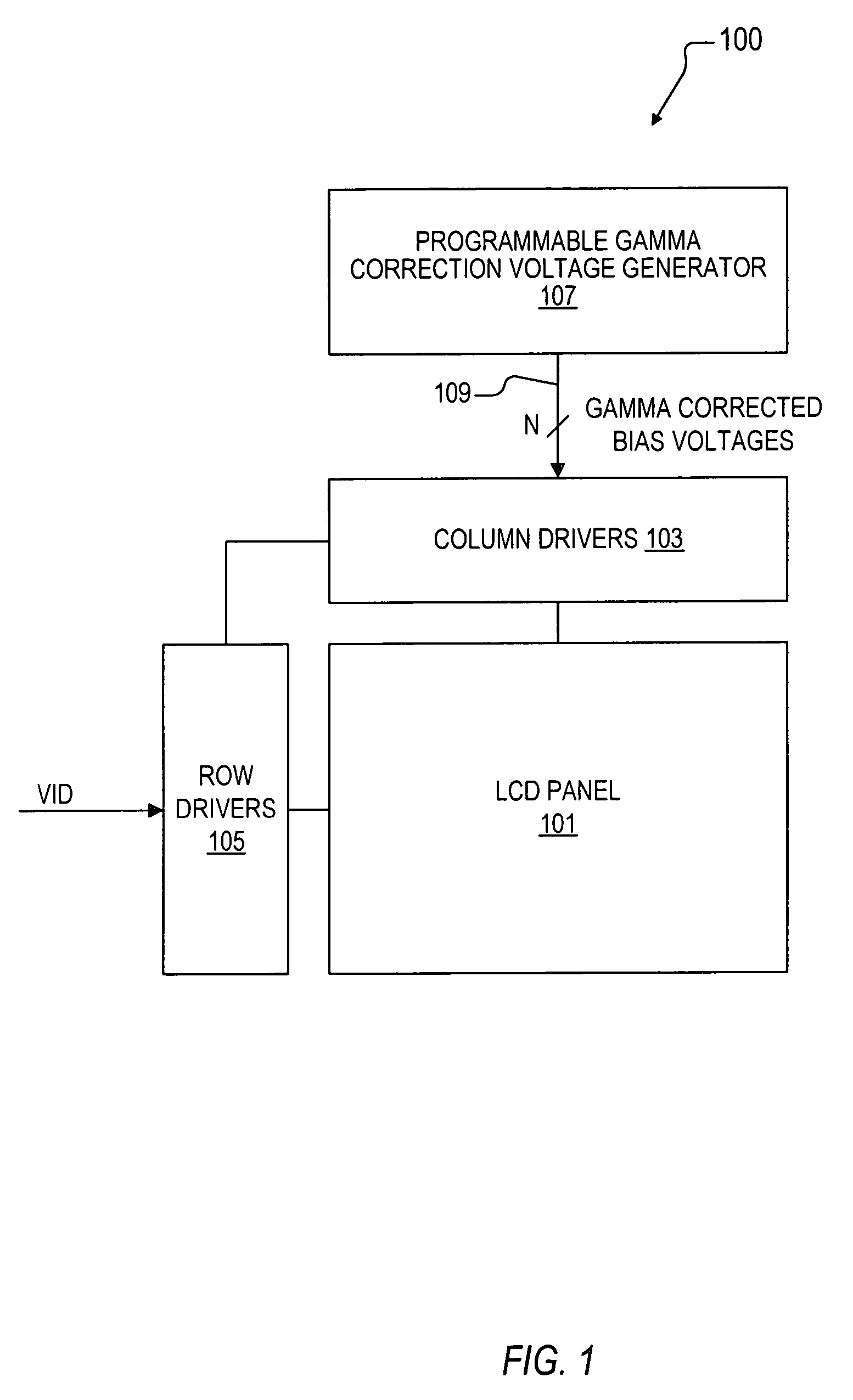

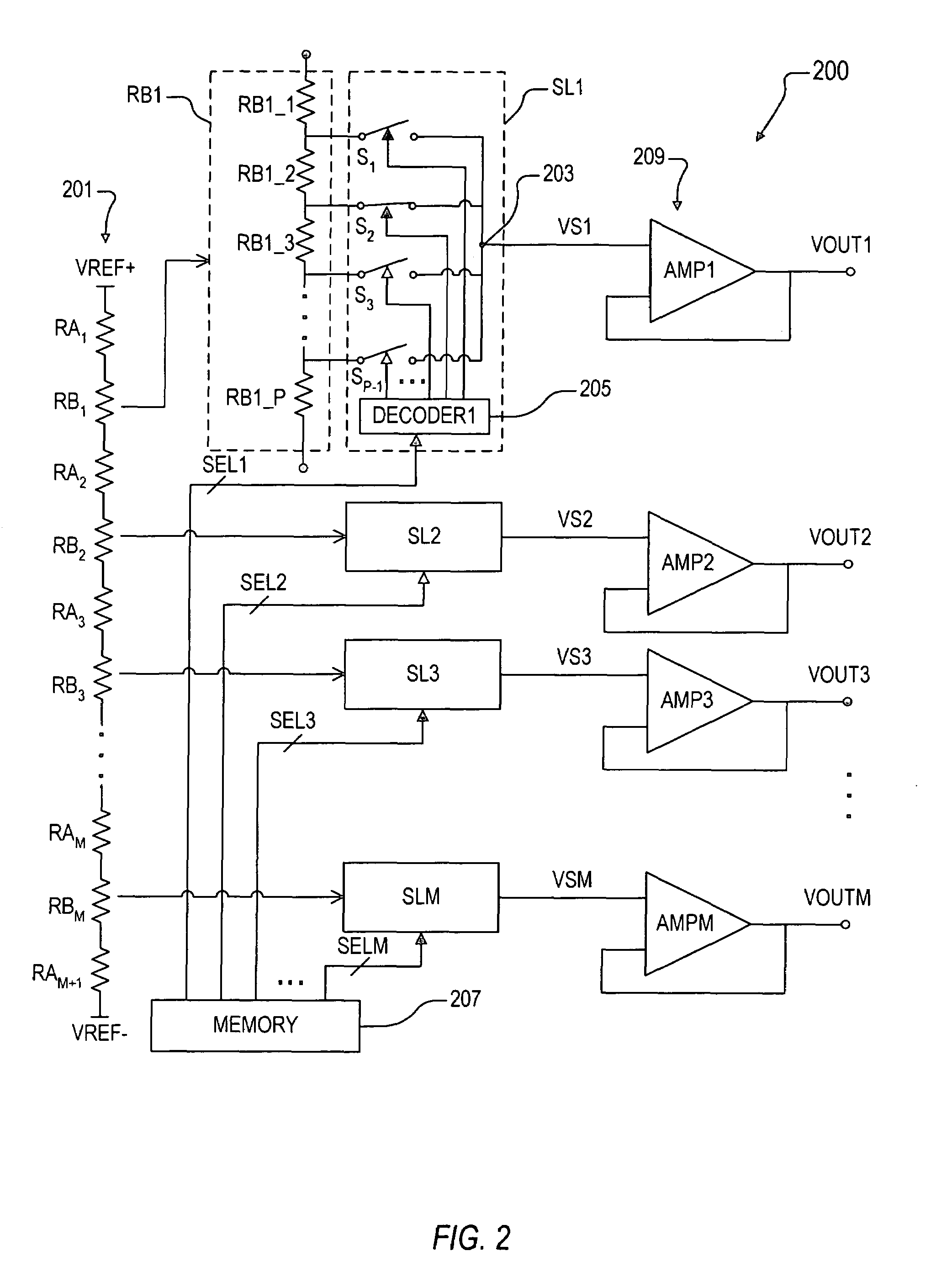

Multiple channel programmable gamma correction voltage generator

InactiveUS20050057482A1Improve driftReduce component countTelevision system detailsStatic indicating devicesResistor ladderEngineering

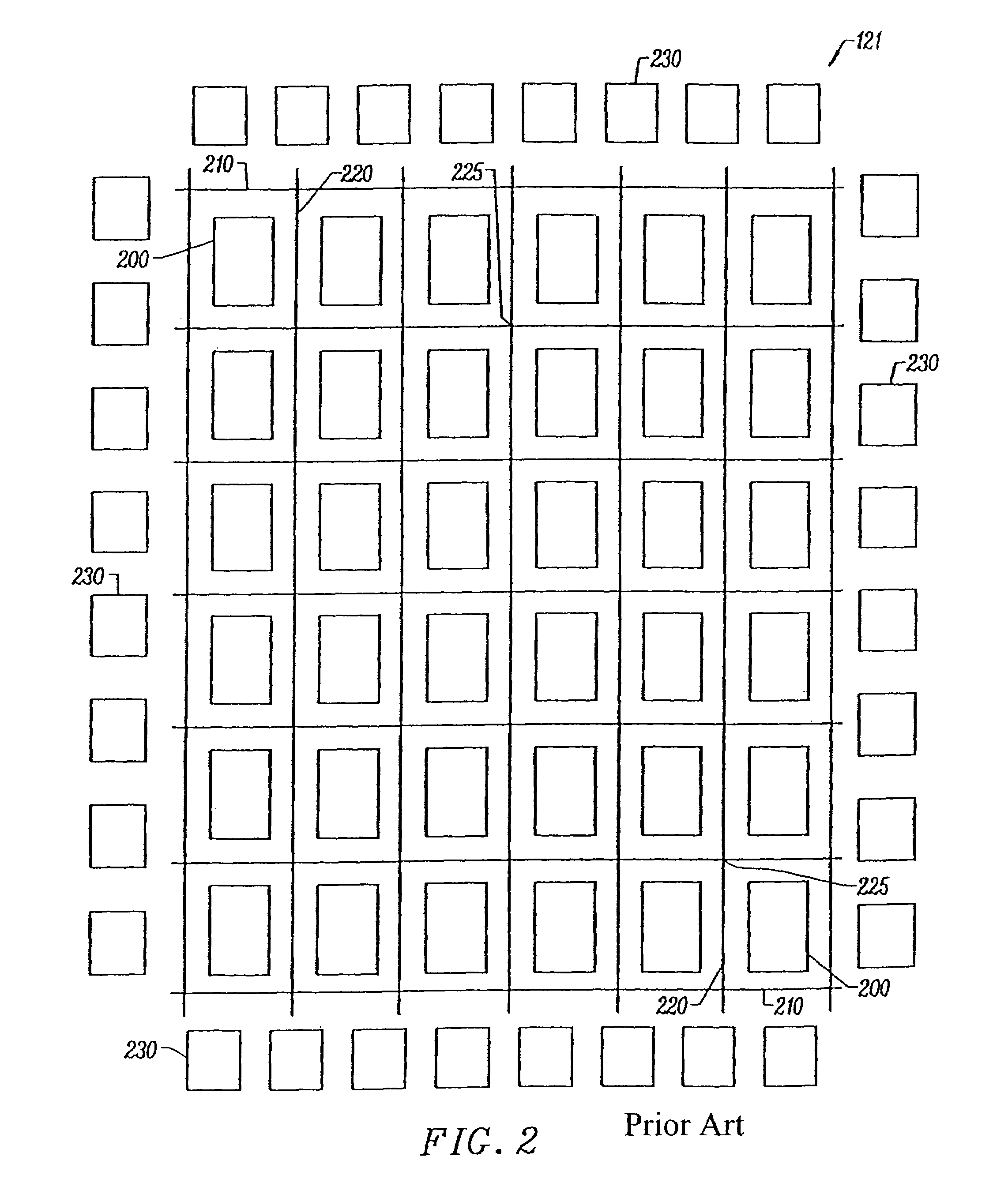

A multiple channel programmable gamma correction voltage generator including a resistor ladder, buffers, select logic, and a programmable non-volatile memory device. The memory provides select values indicative of one or more stored gamma correction values. The resistor ladder includes adjustable tap resistors distributed along the resistor ladder. The adjustable tap resistors provide multiple tap voltages distributed according to the gamma correction value. The buffers receive the tap voltages and provide gamma correction voltages. The select logic selects tap points of the adjustable tap resistors to select the tap voltages based on the select values stored in the memory. Additional resistors and switch logic may be included to enable re-positioning of the adjustable tap resistor within the resistor ladder. Latches and address control may be provided on the memory to enable programming and selection of multiple gamma correction values.

Owner:INTERSIL INC

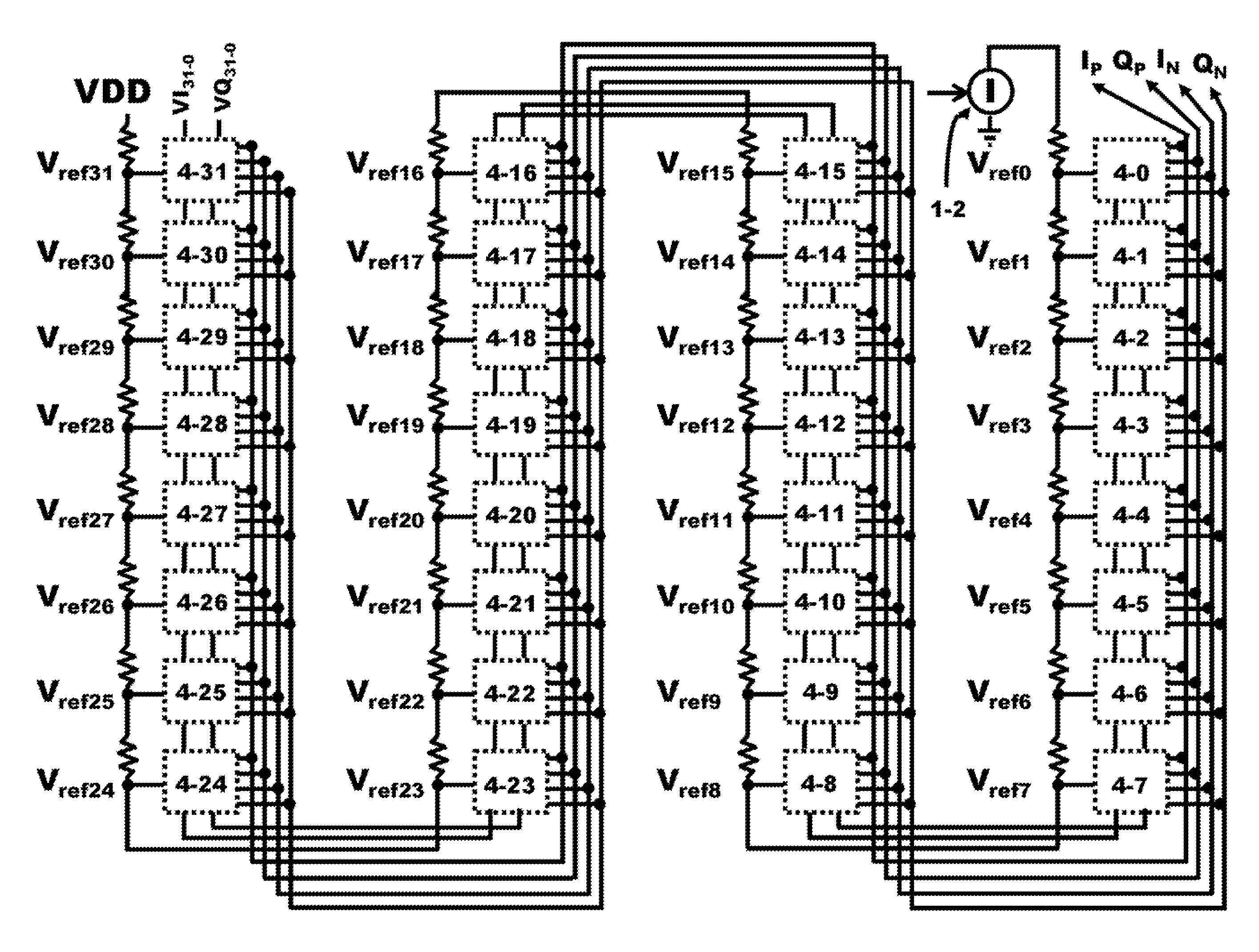

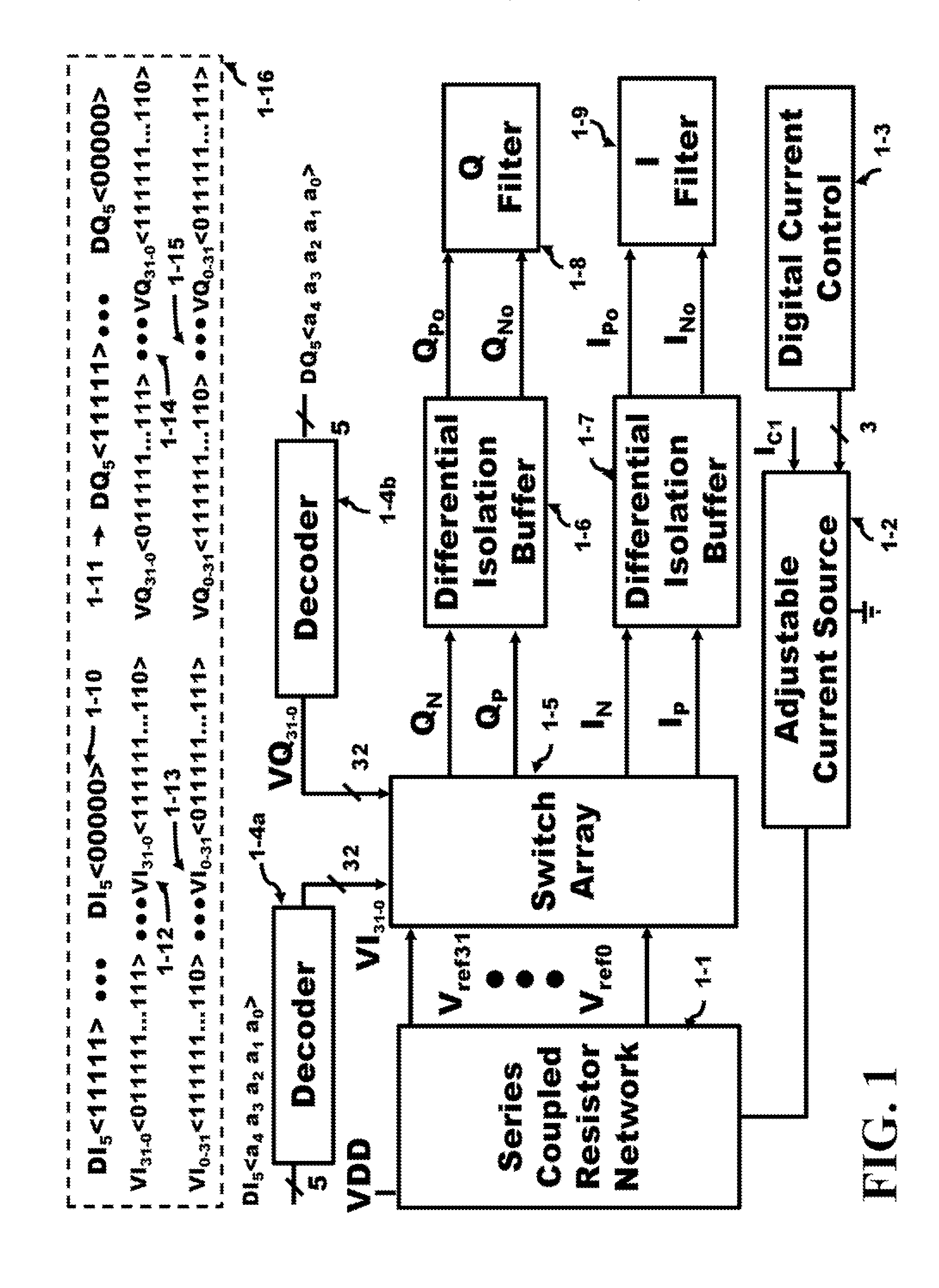

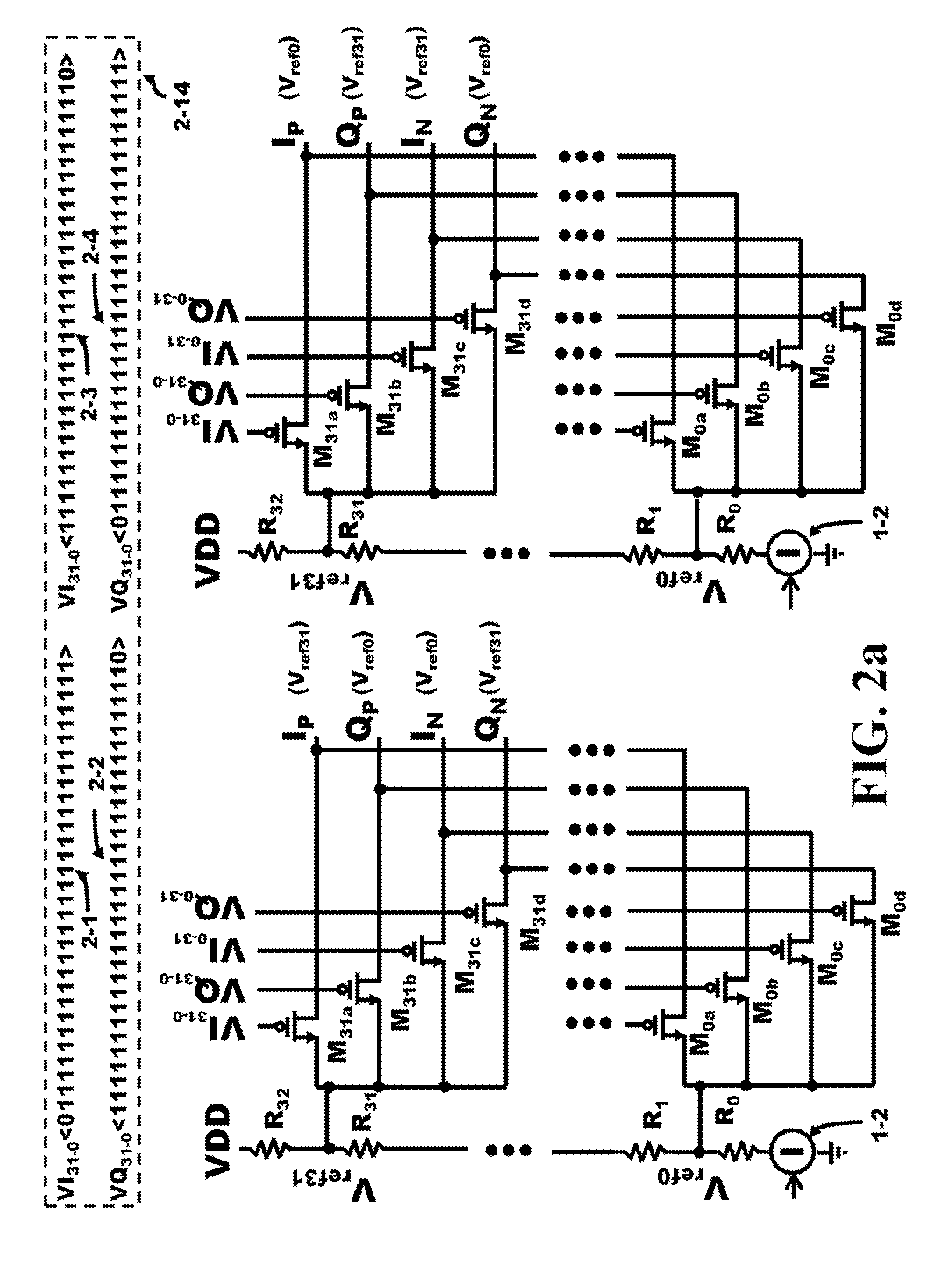

Method and Apparatus for Improving the Performance of a DAC Switch Array

ActiveUS20130307614A1Reduced voltage headroomReduce power supply voltageSolid-state devicesOscillations generatorsLow voltageVoltage drop

One of the critical design parameters occurs when a digital signal is converted into an analog signal. As the supply voltage drops to less than 2 times of threshold voltage to reduce leakage and save power, generating a relative large swing with a resistor-ladder DAC becomes more difficult. For a 5 bit DAC, 32 sub-arrays are used to select the appropriate voltage from the series coupled resistor network. Each sub-array uses p-channel transistors where the sub-array extracting the lowest voltage 700 mV only has a 100 mV of gate to source voltage. To compensate for the reduced gate to source voltage, the sub-arrays are partitioned into four groups. In each group, the p-channel width is increased from 2 um to 5 um, as the tap voltage drops from 1.2 V to 0.7 V. This allows the p-channel transistor with a small gate to source voltage to have a larger width thereby improving performance.

Owner:TENSORCOM

Multiple channel programmable gamma correction voltage generator

InactiveUS7446747B2Increase temperatureExtension of timeTelevision system detailsStatic indicating devicesElectrical resistance and conductanceVoltage generator

A multiple channel programmable gamma correction voltage generator including a resistor ladder, buffers, select logic, and a programmable non-volatile memory device. The memory provides select values indicative of one or more stored gamma correction values. The resistor ladder includes adjustable tap resistors distributed along the resistor ladder. The adjustable tap resistors provide multiple tap voltages distributed according to the gamma correction value. The buffers receive the tap voltages and provide gamma correction voltages. The select logic selects tap points of the adjustable tap resistors to select the tap voltages based on the select values stored in the memory. Additional resistors and switch logic may be included to enable re-positioning of the adjustable tap resistor within the resistor ladder. Latches and address control may be provided on the memory to enable programming and selection of multiple gamma correction values.

Owner:INTERSIL INC

Programmable attenuator using digitally controlled CMOS switches

A programmable attenuator includes a resistor ladder having a plurality of taps to provide a coarse gain control. Coupled to each tap is a plurality of switches. Control logic activates or deactivates individual switches in the plurality of switches to provide a fine gain control. More specifically, a set of activated switches provides fine gain control by determining an overall attenuation level interpolated between an adjacent pair of taps.

Owner:AVAGO TECH INT SALES PTE LTD

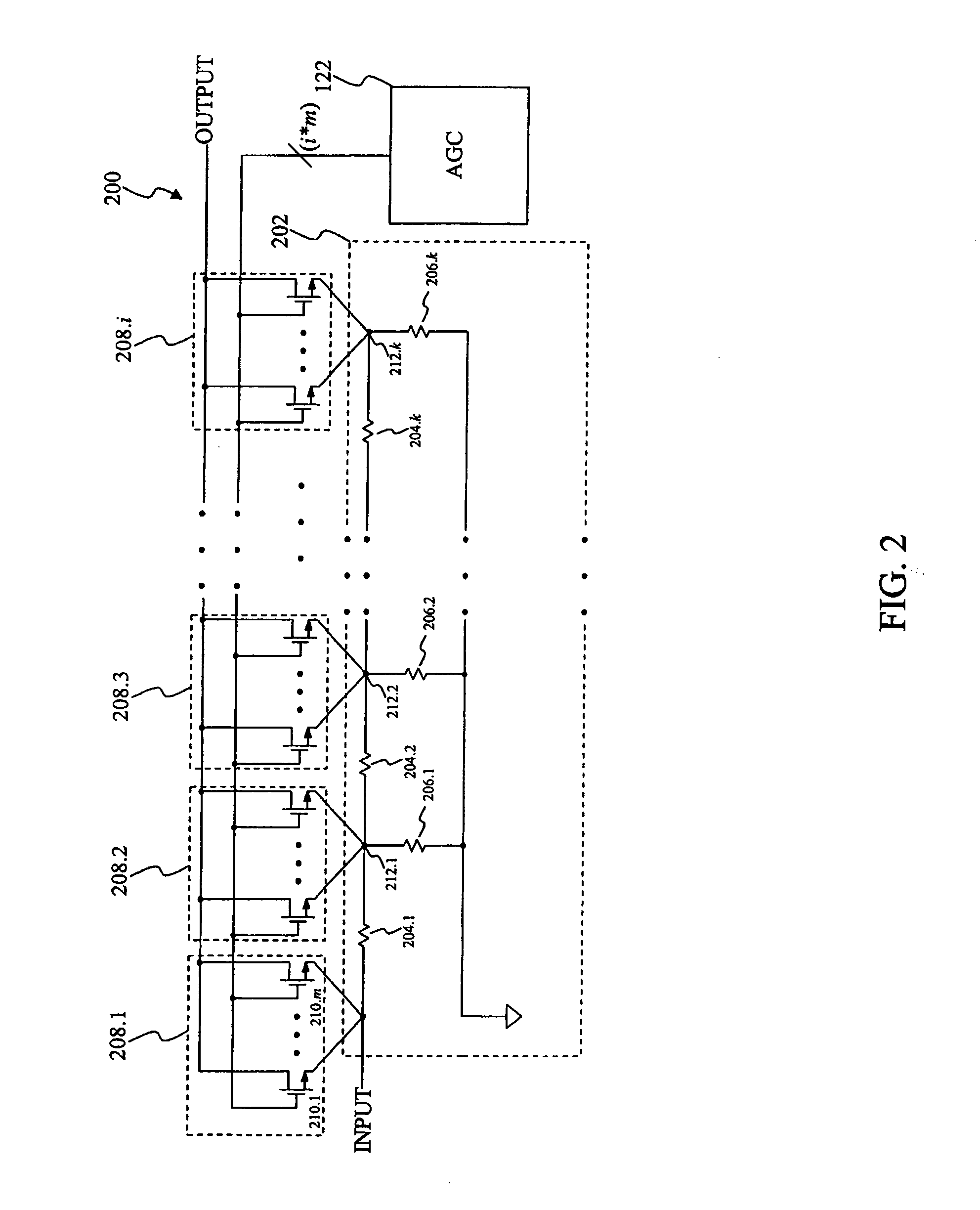

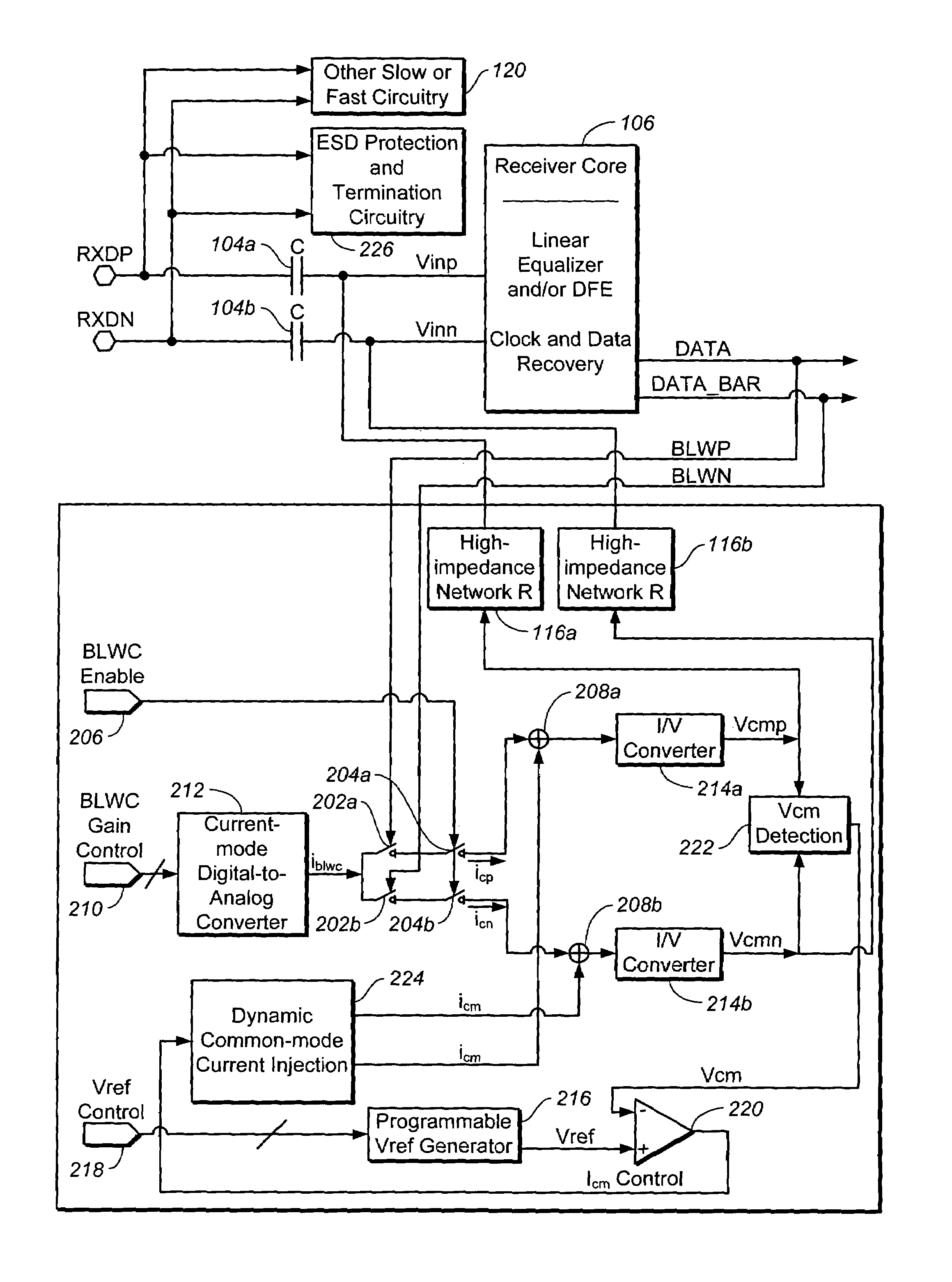

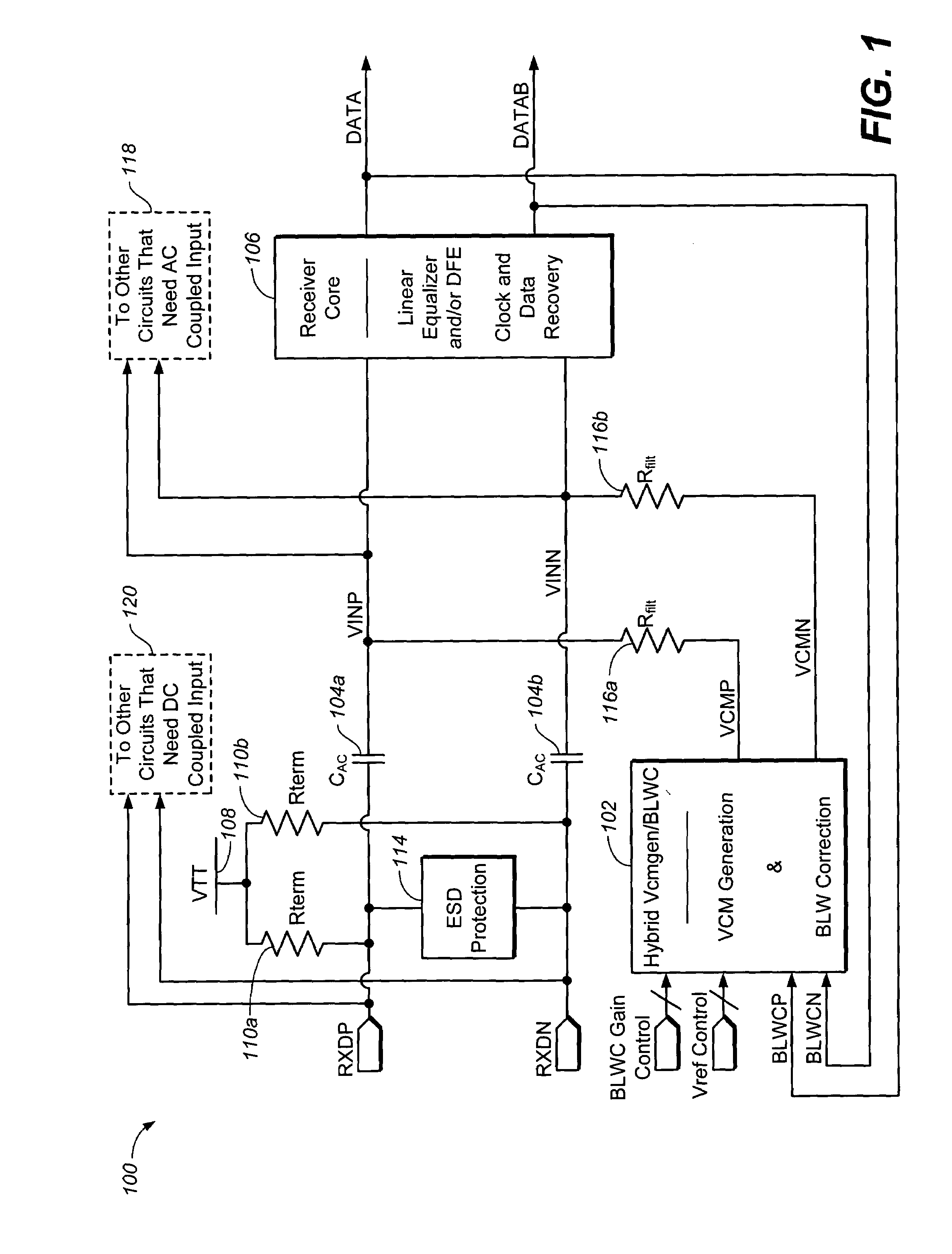

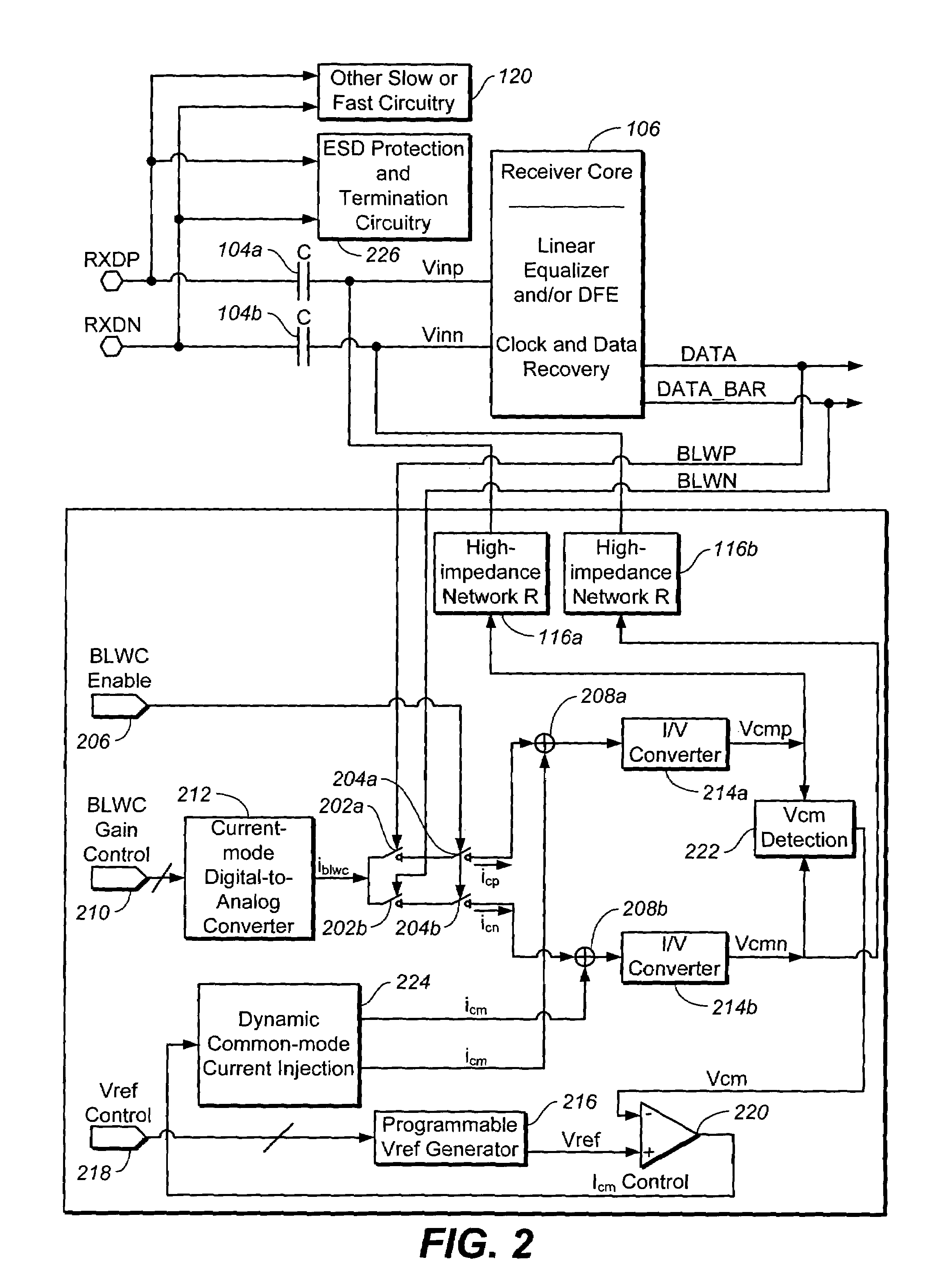

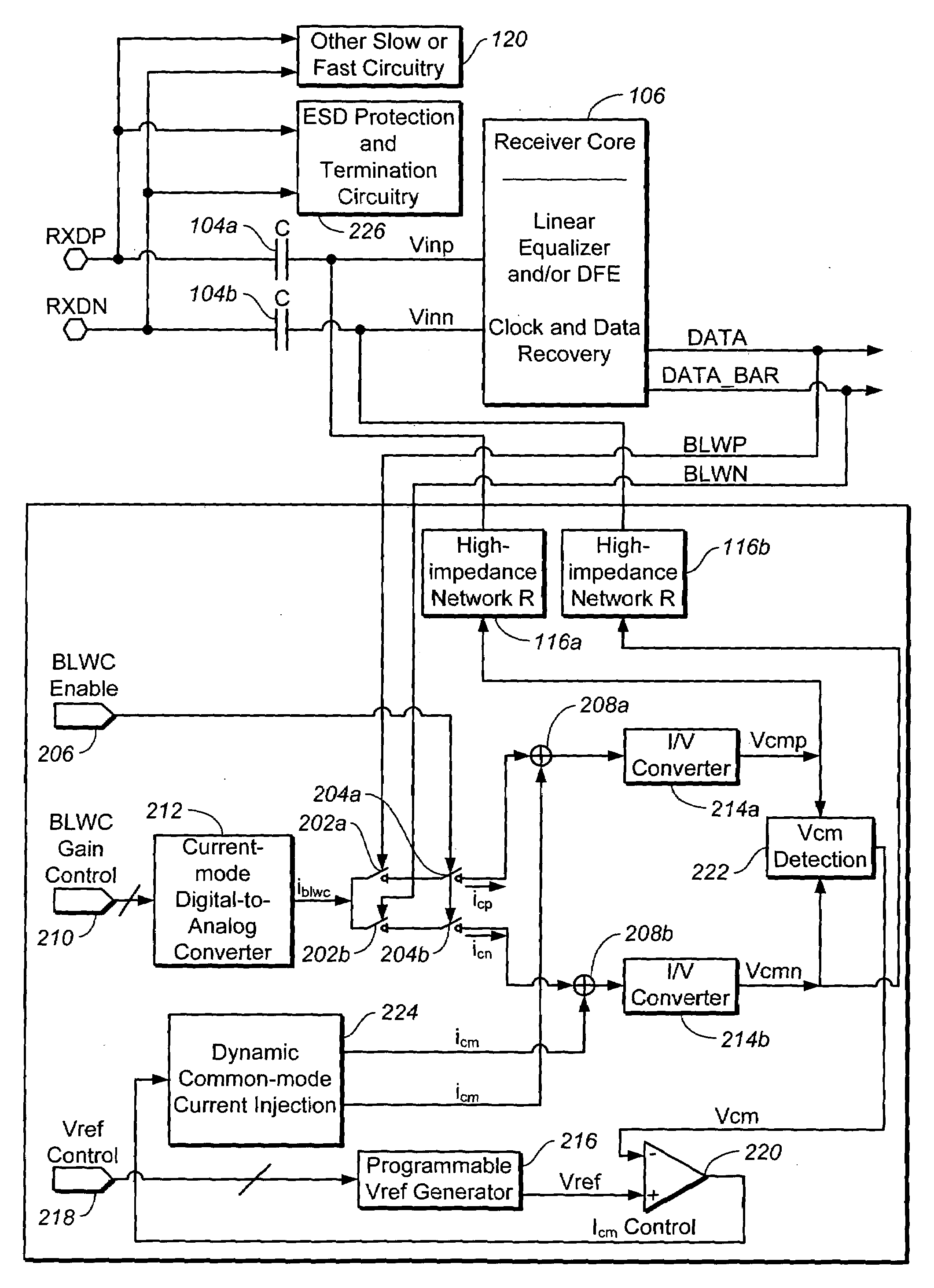

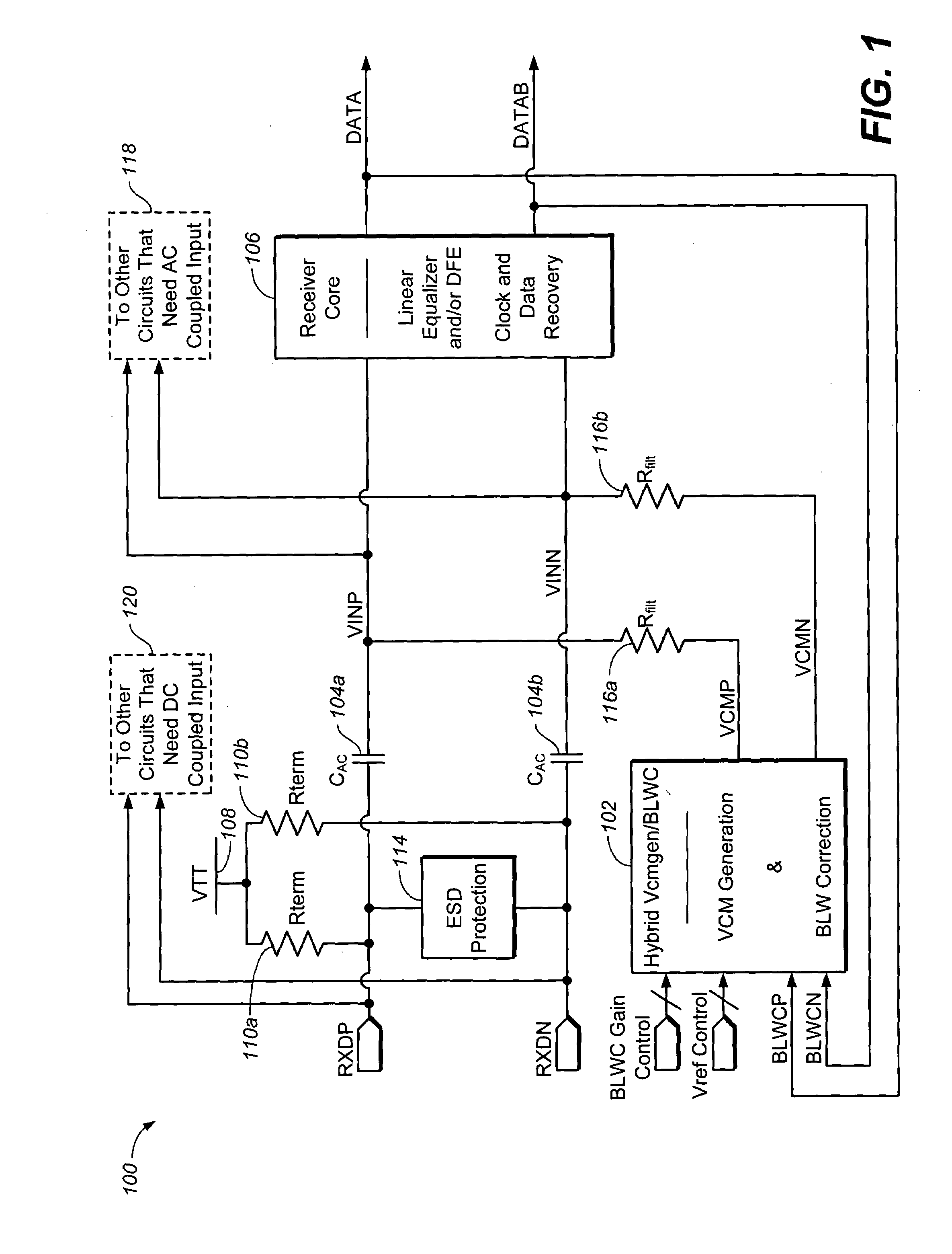

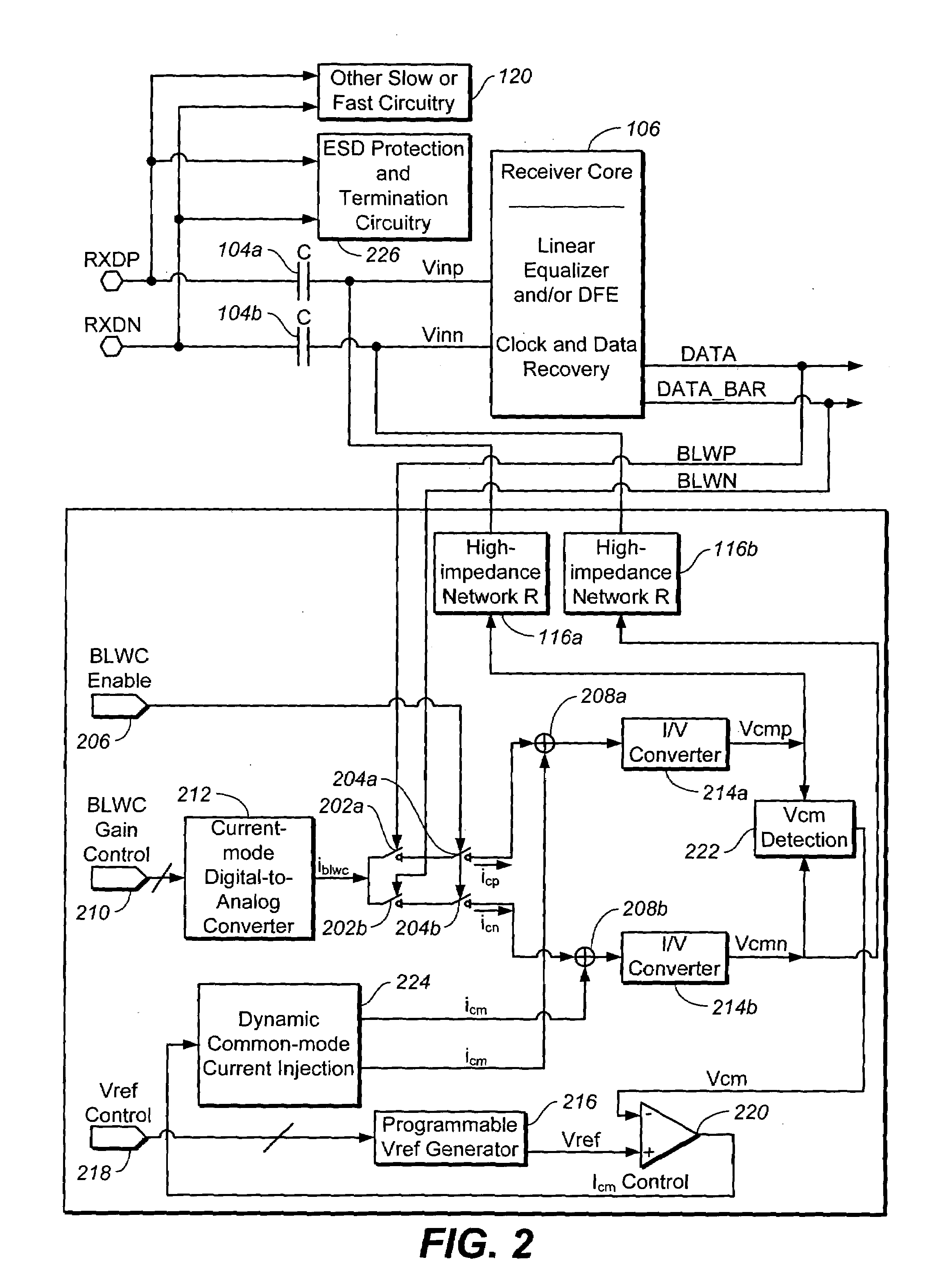

AC coupling circuit integrated with receiver with hybrid stable common-mode voltage generation and baseline wander compensation

InactiveUS7961817B2Reduce pollutionMaximum freedom for optimizationMultiple-port networksTransmission control/equlisationVoltage generatorVoltage reference

In a receiver, an AC-coupling solution uses a fully integrated circuit for simultaneously providing both baseline wander compensation and common-mode voltage generation. Usefully, an integrated capacitor is placed between the receiver input pin and the input buffer, and a high resistive impedance element is connected to the internal high-speed data node after the capacitor. An on-chip voltage generation and correction circuit is connected to the other side of the impedance element to generate a common-mode voltage, and to provide dynamic, fine adjustment for the received data voltage level. The voltage correction circuit is controlled by the feedback of data detected by the clock and data recovery unit (CDRU) of the receiver. The feedback data passes through a weighting element, wherein the amount of feedback gain is adjustable to provide a summing weight and thereby achieve a desired BLW compensation. Register bits are used to control an on-chip reference voltage generator that consists of a resistor ladder to generate the reference voltage.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

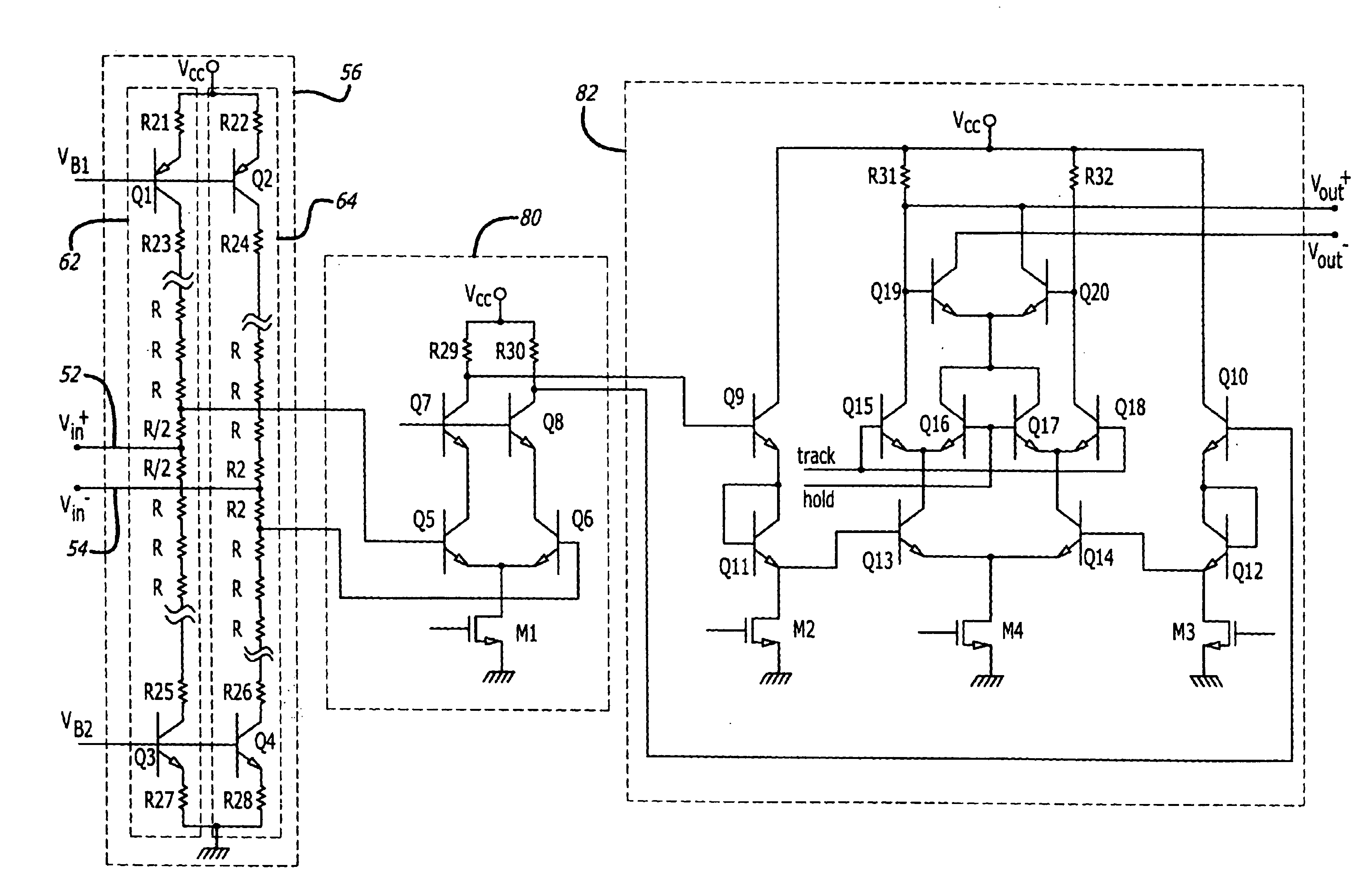

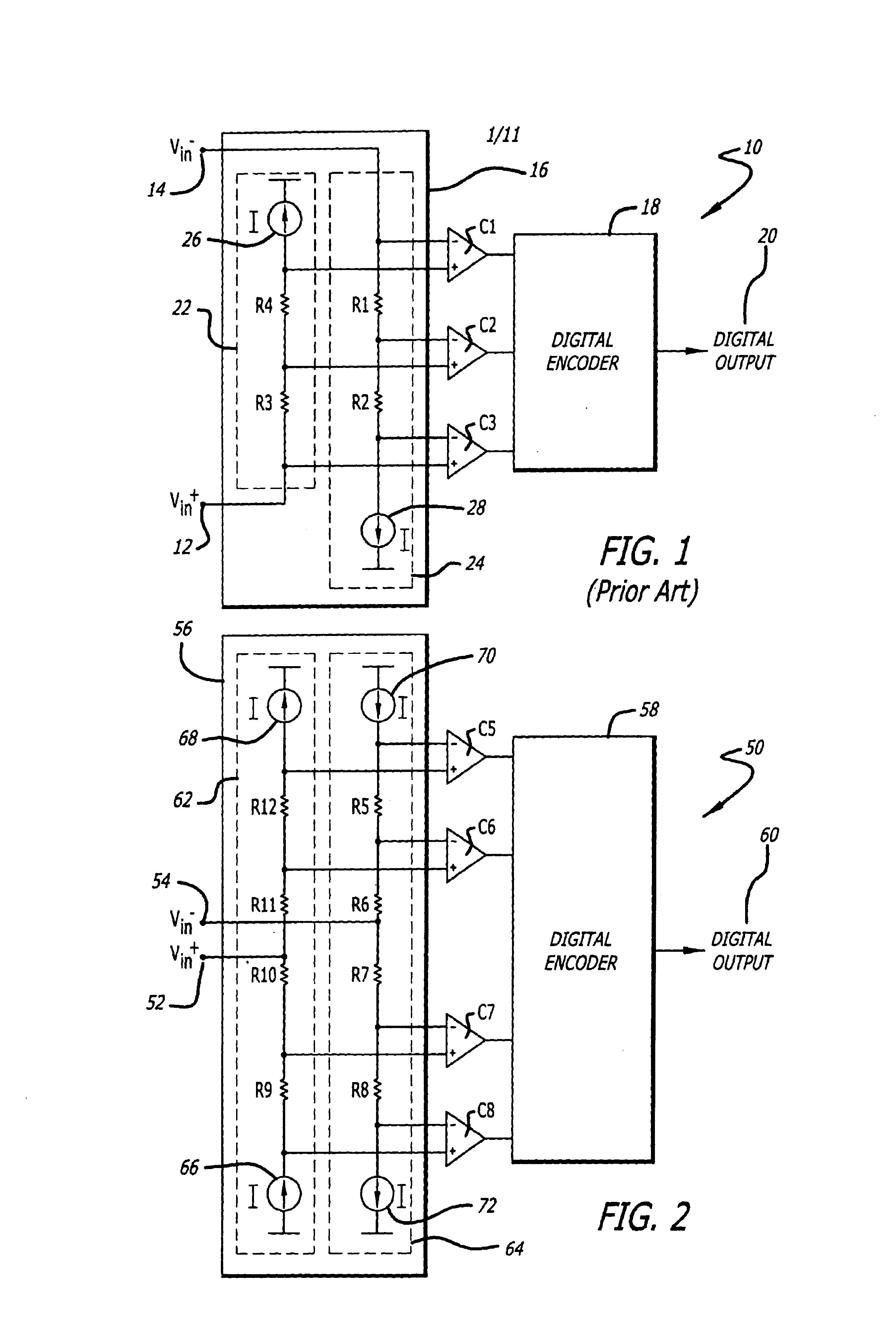

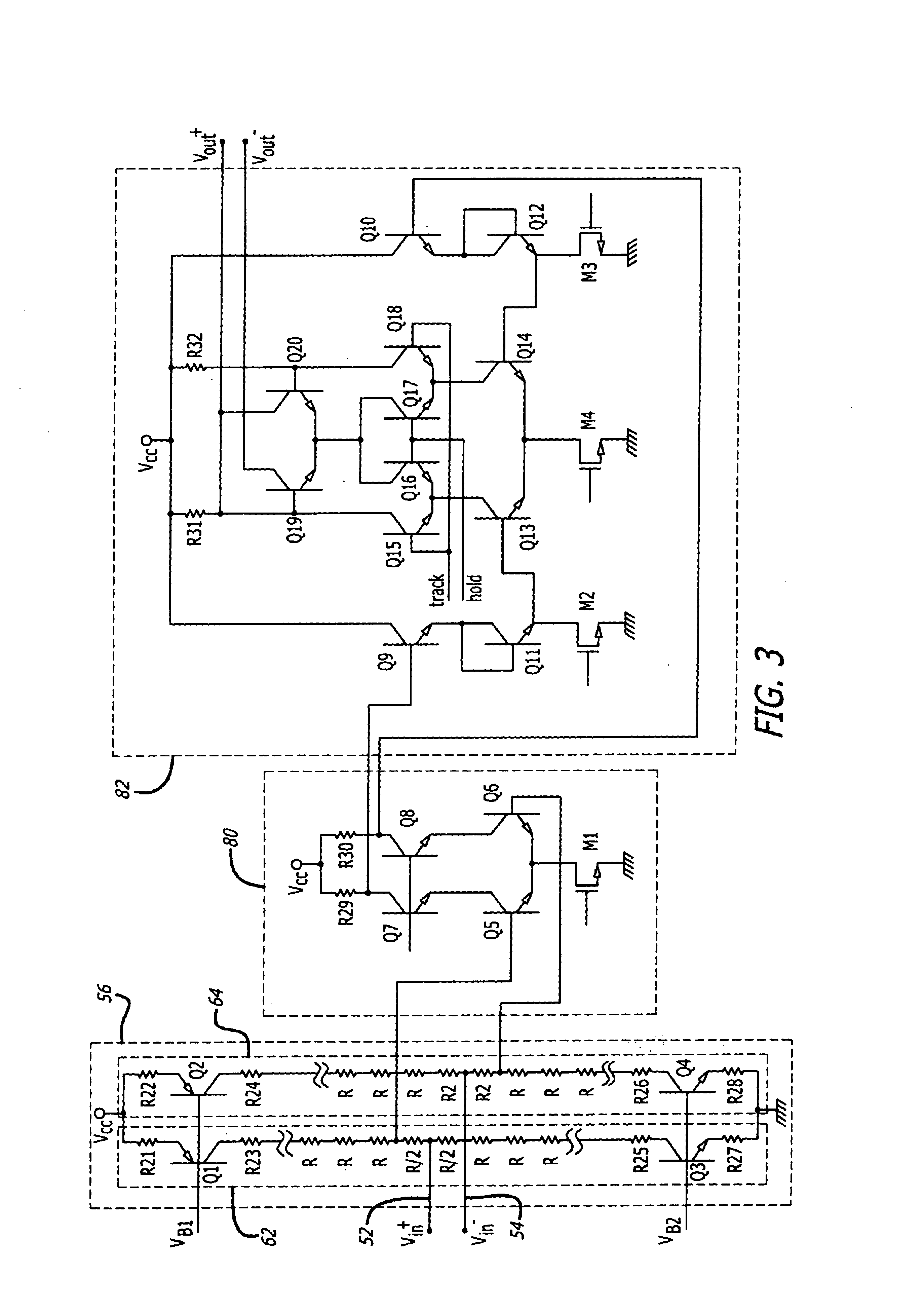

Resistive ladder, summing node circuit, and trimming method for a subranging analog to digital converter

InactiveUS6882294B2Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierAnalog-to-digital converter

A subranging analog to digital converter (ADC). The ADC (200) includes a novel resistive ladder (56) for a differential quantizer (50) and a novel summing node circuit (150). The novel resistive ladder (56) includes an input terminal (52), a plurality of serially connected resistors R coupled to the input terminal (52), and a pair of complementary current sources (66 and 68) for maintaining a constant current flow through the ladder (56). The novel summing node circuit (150) includes an input terminal (152) for receiving an input signal, a pair of complementary DACs (156 and 158) for generating a reconstruction signal, and a summing amplifier (164) for subtracting the reconstruction signal from the input signal to produce a residue signal.The invention also includes a method for trimming the subranging ADC. The novel method (250) includes the steps of trimming the complementary current sources of the coarse quantizer to match each other (252), trimming each of the DAC cells on one of the complementary DACs (254), trimming the overall DAC gain to match the gain of the coarse quantizer (256); and trimming the gain of the fine quantizer to match one coarse quantization Q level (260).

Owner:MICROELECTRONICS TECH INC

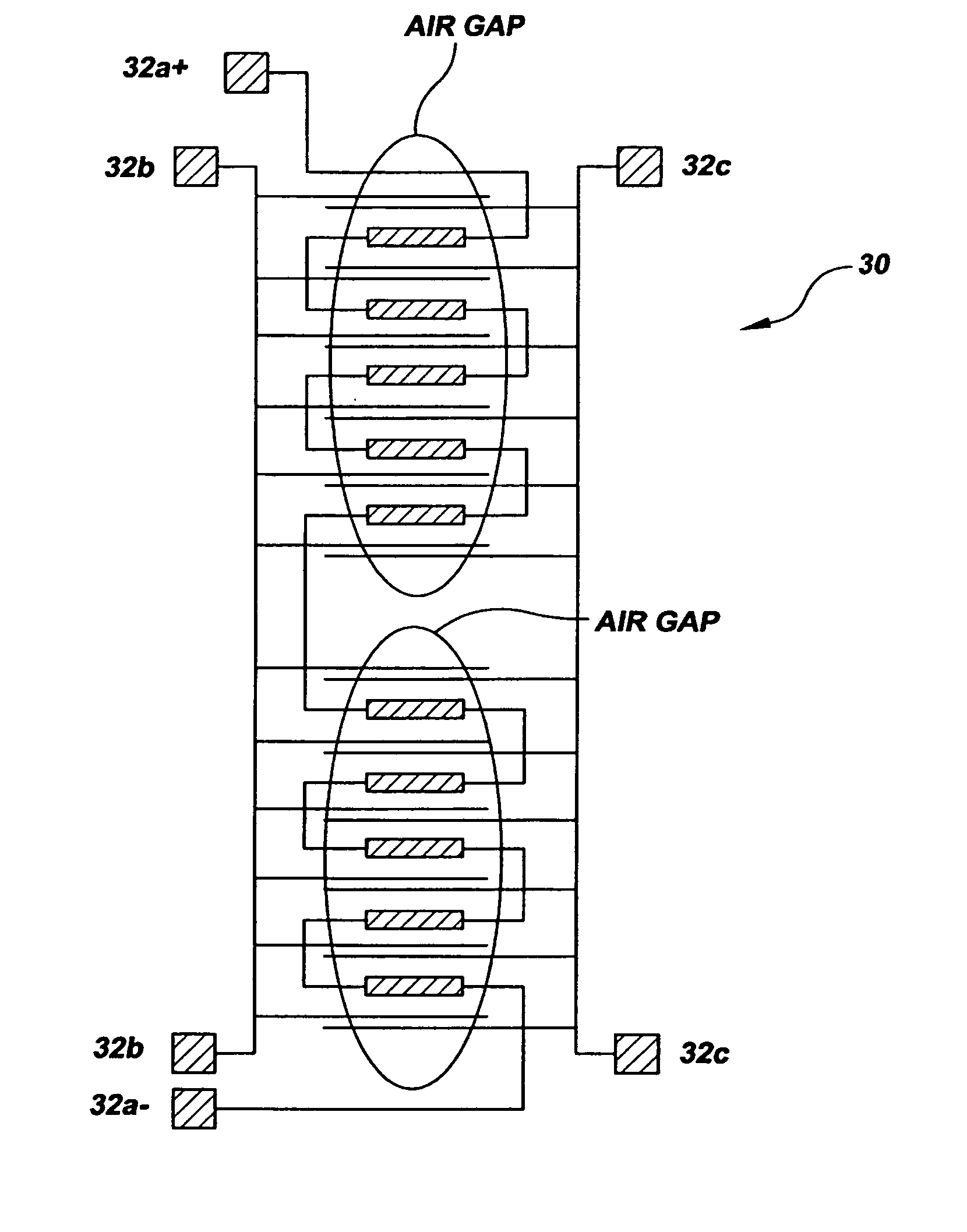

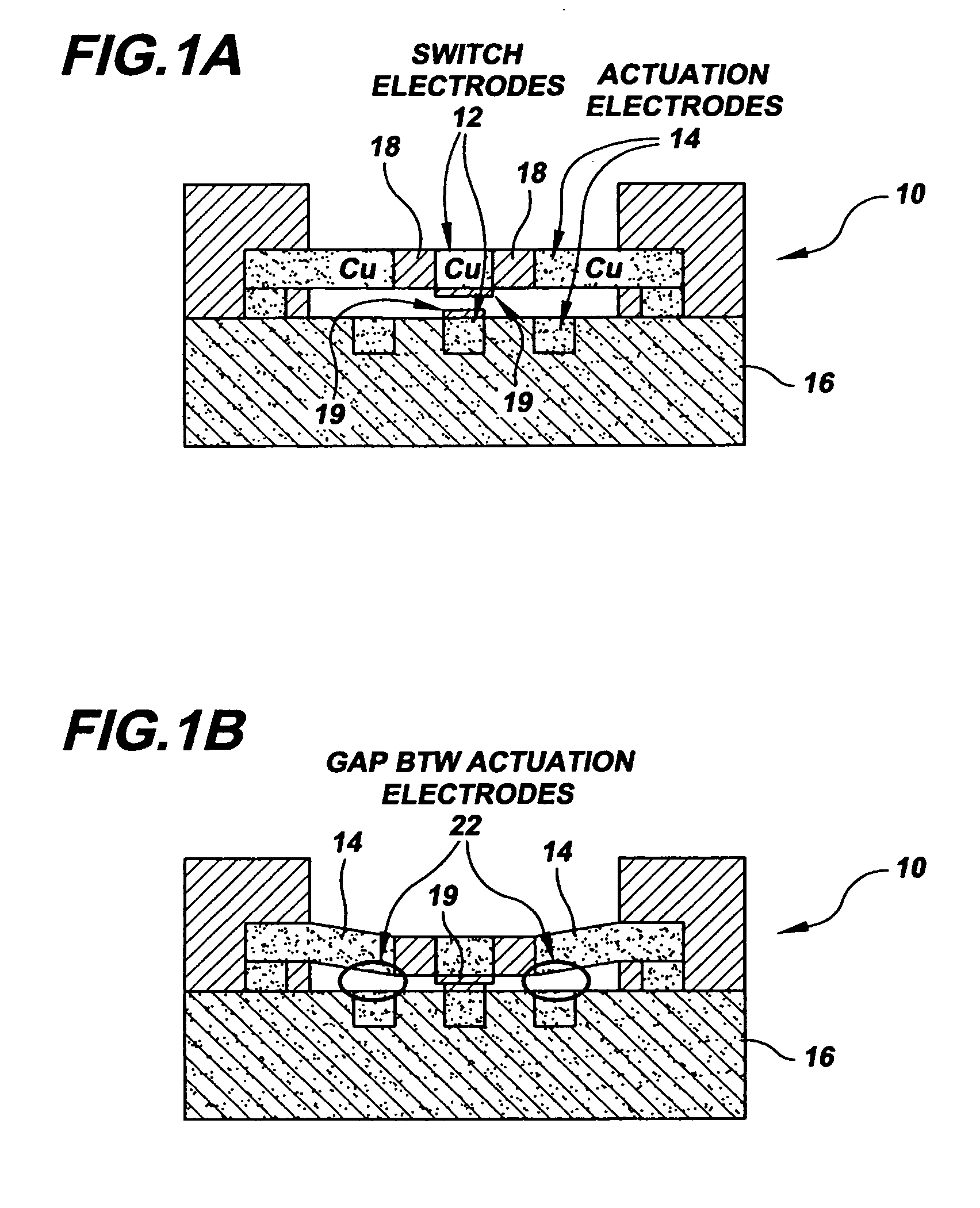

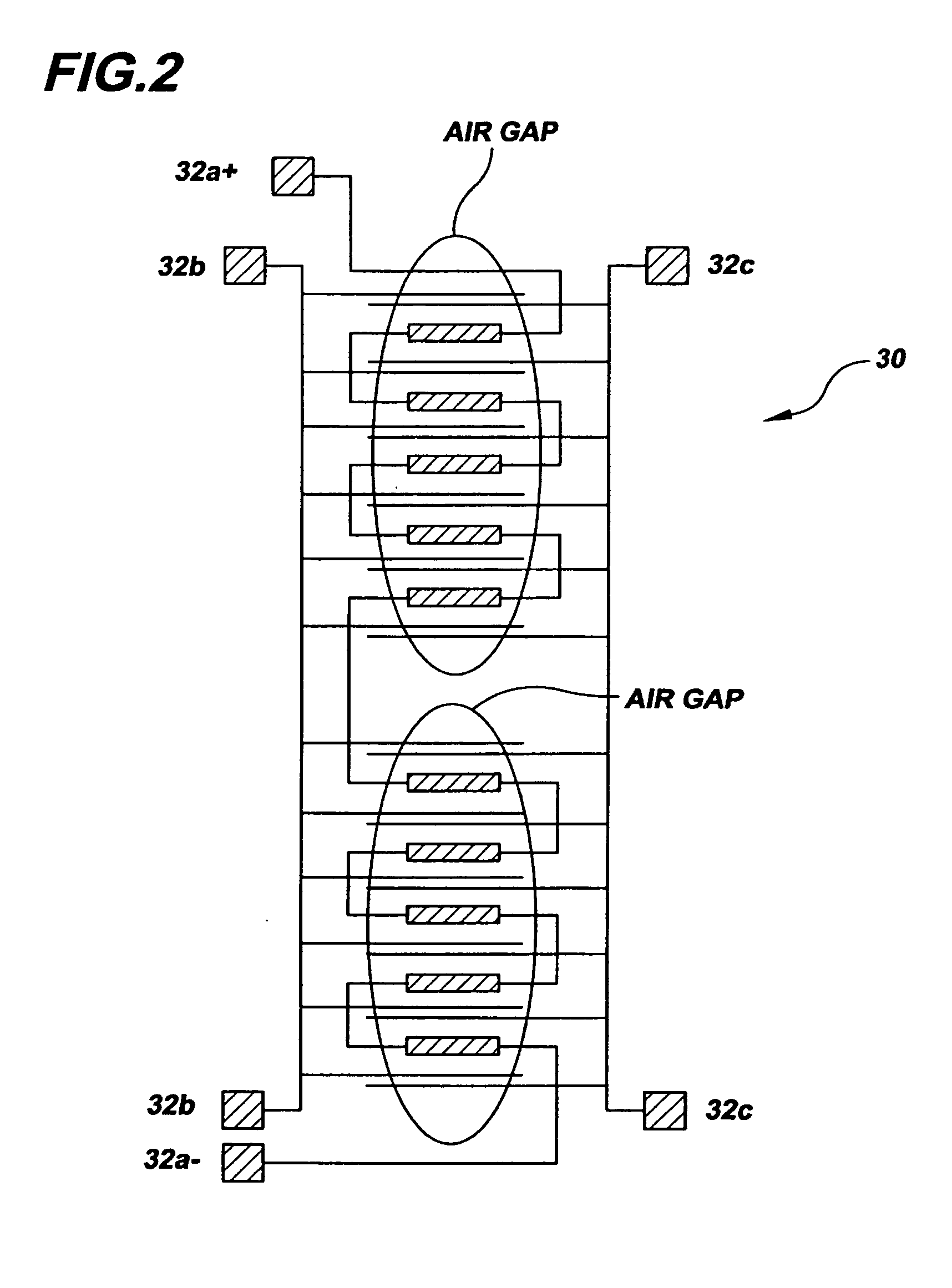

Apparatus for accurate and efficient quality and reliability evaluation of micro electromechanical systems

InactiveUS20070090902A1Accurate measurementElectrostatic/electro-adhesion relaysElectrostrictive/piezoelectric relaysShift registerElectricity

The present invention provides multiple test structures for performing reliability and qualification tests on MEMS switch devices. A Test structure for contact and gap characteristic measurements is employed having a serpentine layout simulates rows of upper and lower actuation electrodes. A cascaded switch chain test is used to monitor process defects with large sample sizes. A ring oscillator is used to measure switch speed and switch lifetime. A resistor ladder test structure is configured having each resistor in series with a switch to be tested, and having each switch-resistor pair electrically connected in parallel. Serial / parallel test structures are proposed with MEMS switches working in tandem with switches of established technology. A shift register is used to monitor the open and close state of the MEMS switches. Pull-in voltage, drop-out voltage, activation leakage current, and switch lifetime measurements are performed using the shift register.

Owner:GLOBALFOUNDRIES INC

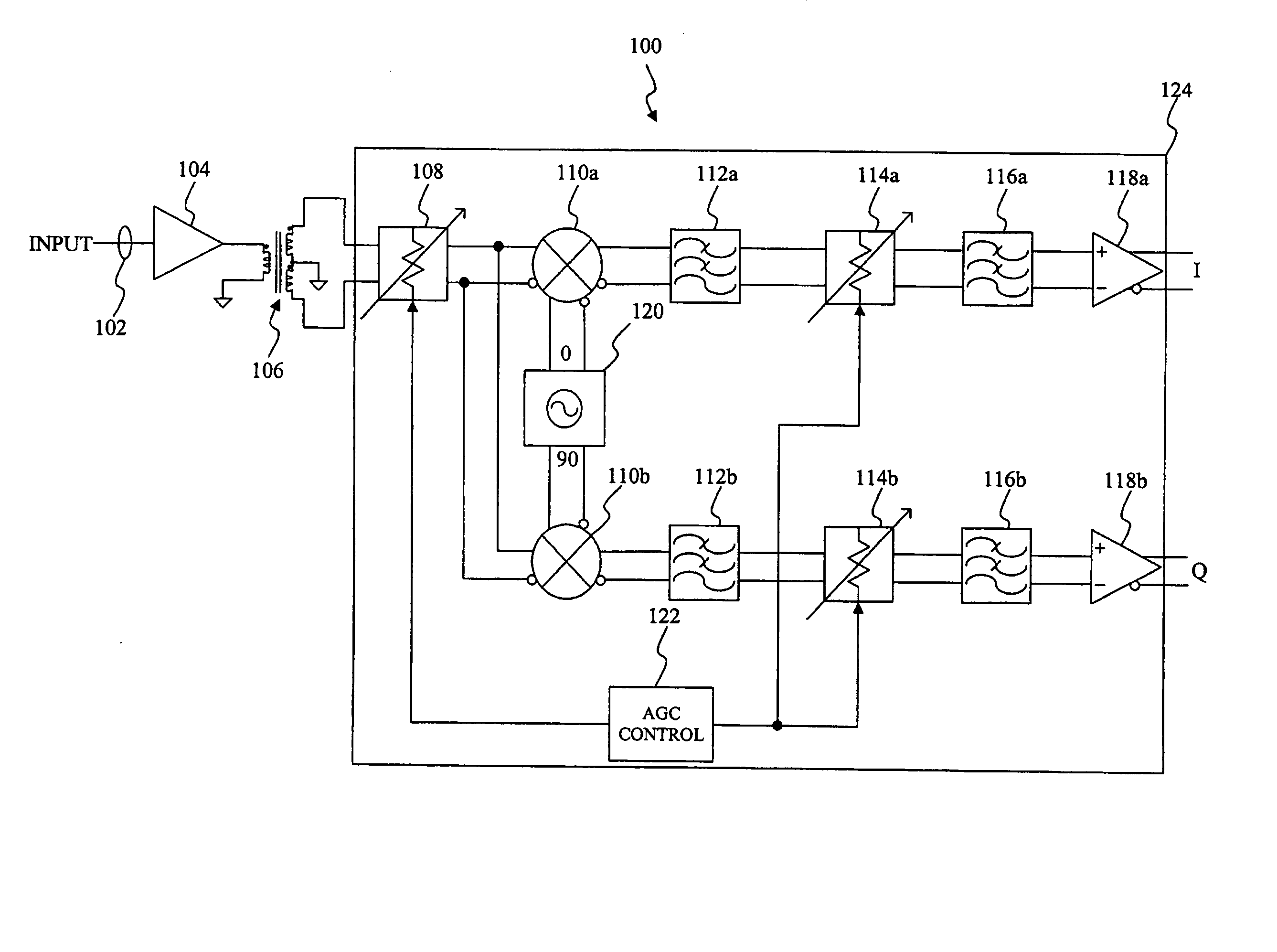

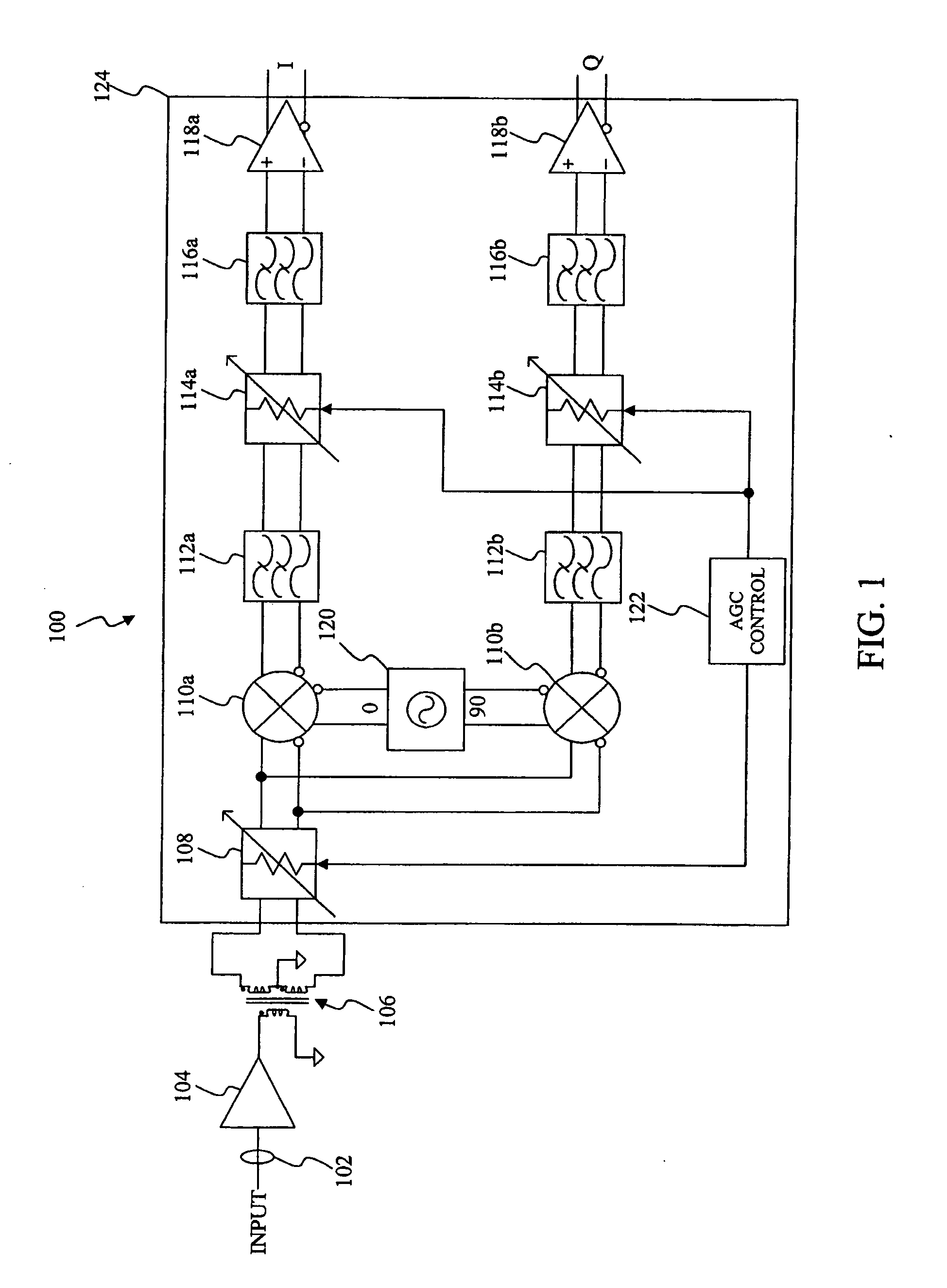

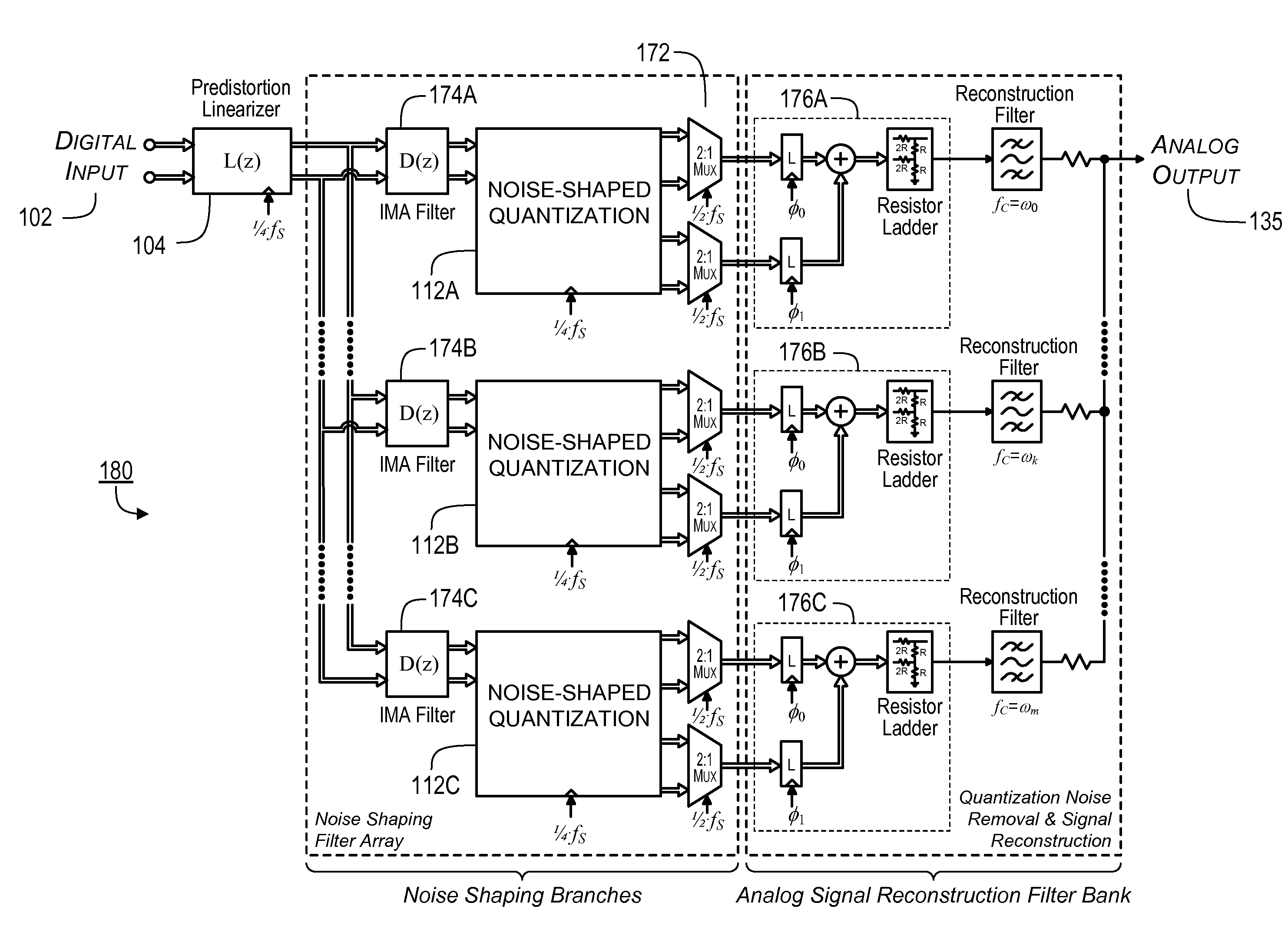

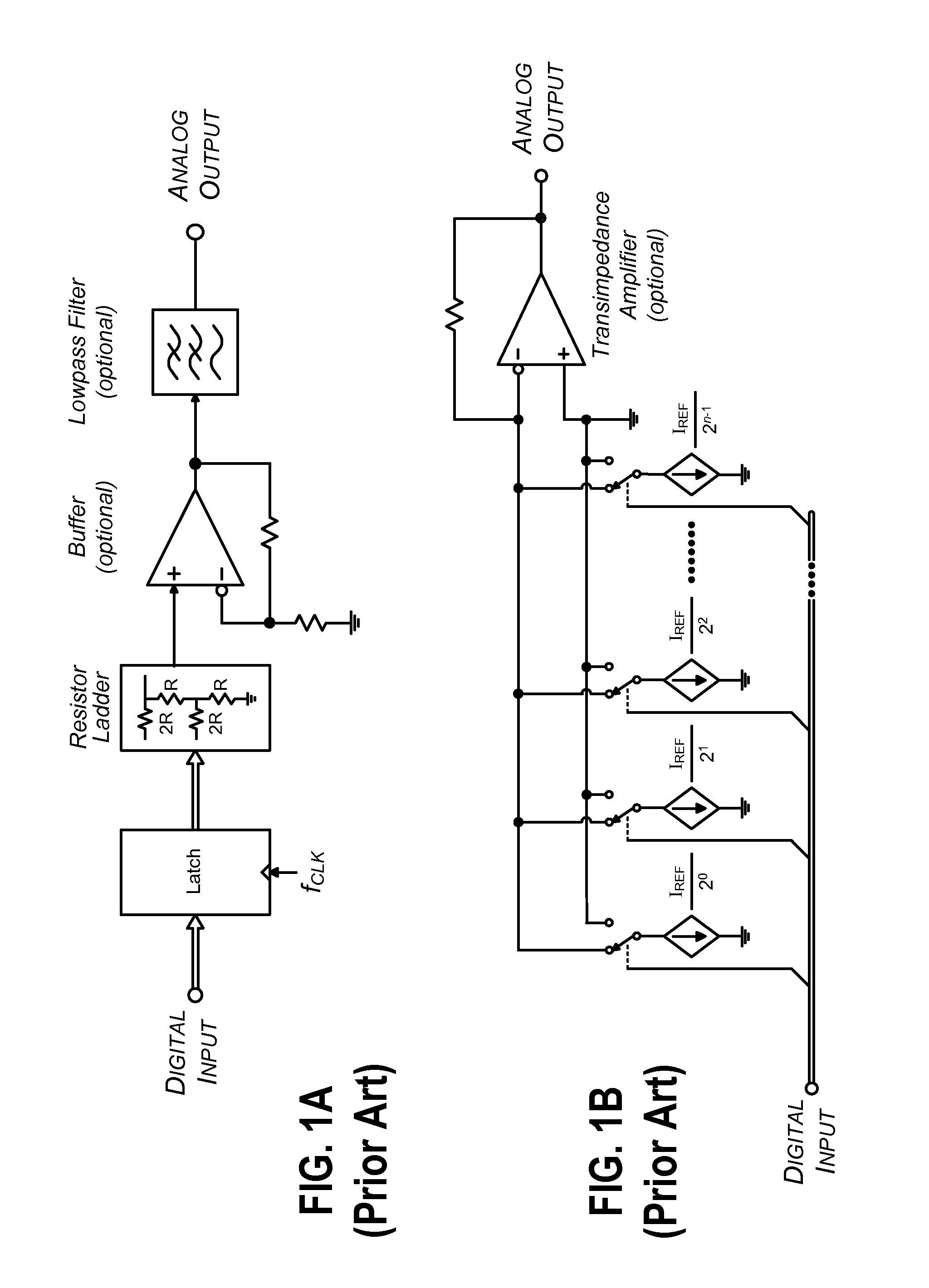

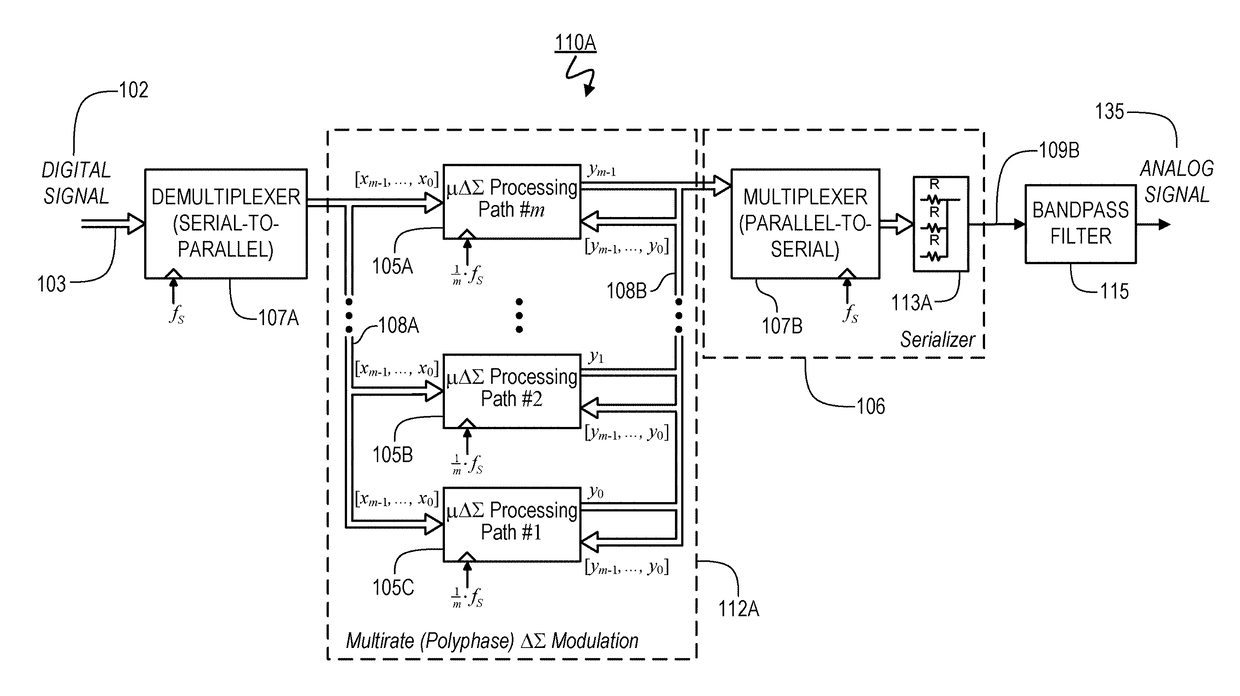

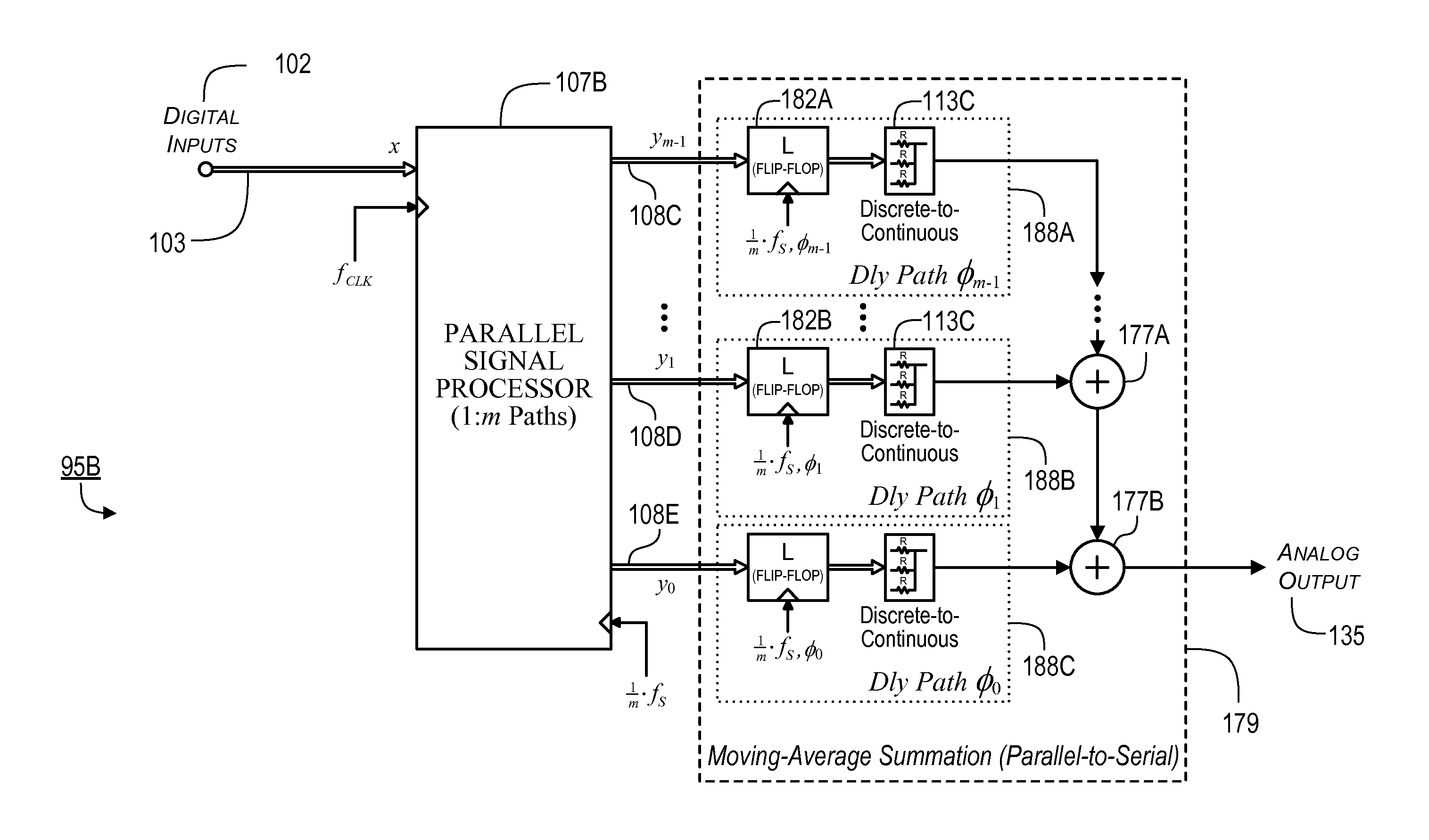

Conversion of a Discrete Time Quantized Signal into a Continuous Time, Continuously Variable Signal

ActiveUS20150061911A1Overcome limitationsLimit can be overcomeElectric signal transmission systemsAnalogue conversionMulti bandEngineering

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive nonlinear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

Conversion of a Discrete Time Quantized Signal into a Continuous Time, Continuously Variable Signal

ActiveUS20110140942A1Overcome limitationsLimit can be overcomeElectric signal transmission systemsAnalogue conversionOversamplingAnalog signal

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive non-linear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

Calibration of resistor ladder using difference measurement and parallel resistive correction

InactiveUS6628216B2Electric signal transmission systemsAnalogue-digital convertersDifferential measurementComplementary pair

Owner:INTERSIL INC

Conversion of a Discrete-Time Quantized Signal into a Continuous-Time, Continuously Variable Signal

ActiveUS20170077945A1Overcome limitationsLimit can be overcomeAnalogue/digital conversionModulated-carrier systemsMulti bandAnalog signal

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive nonlinear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

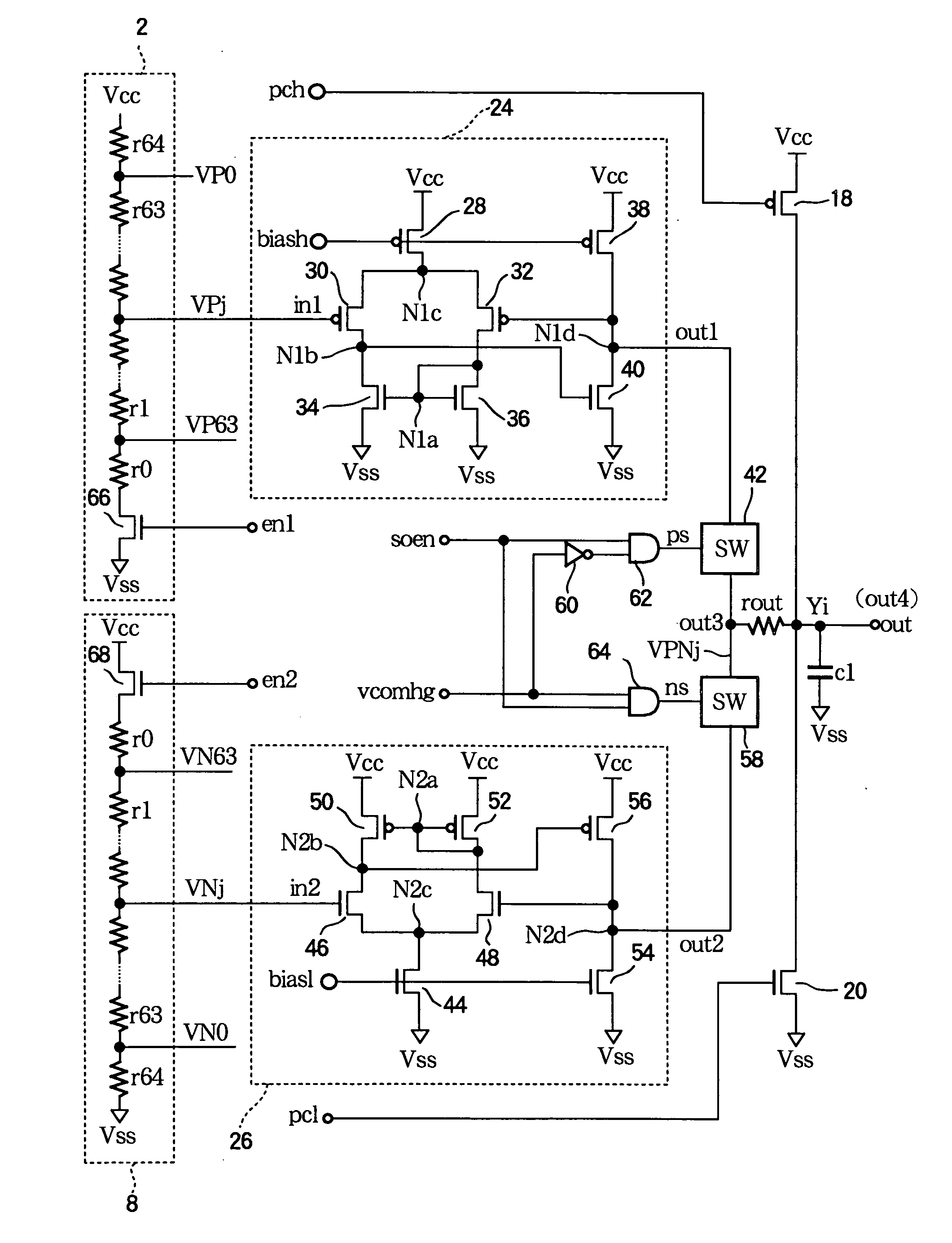

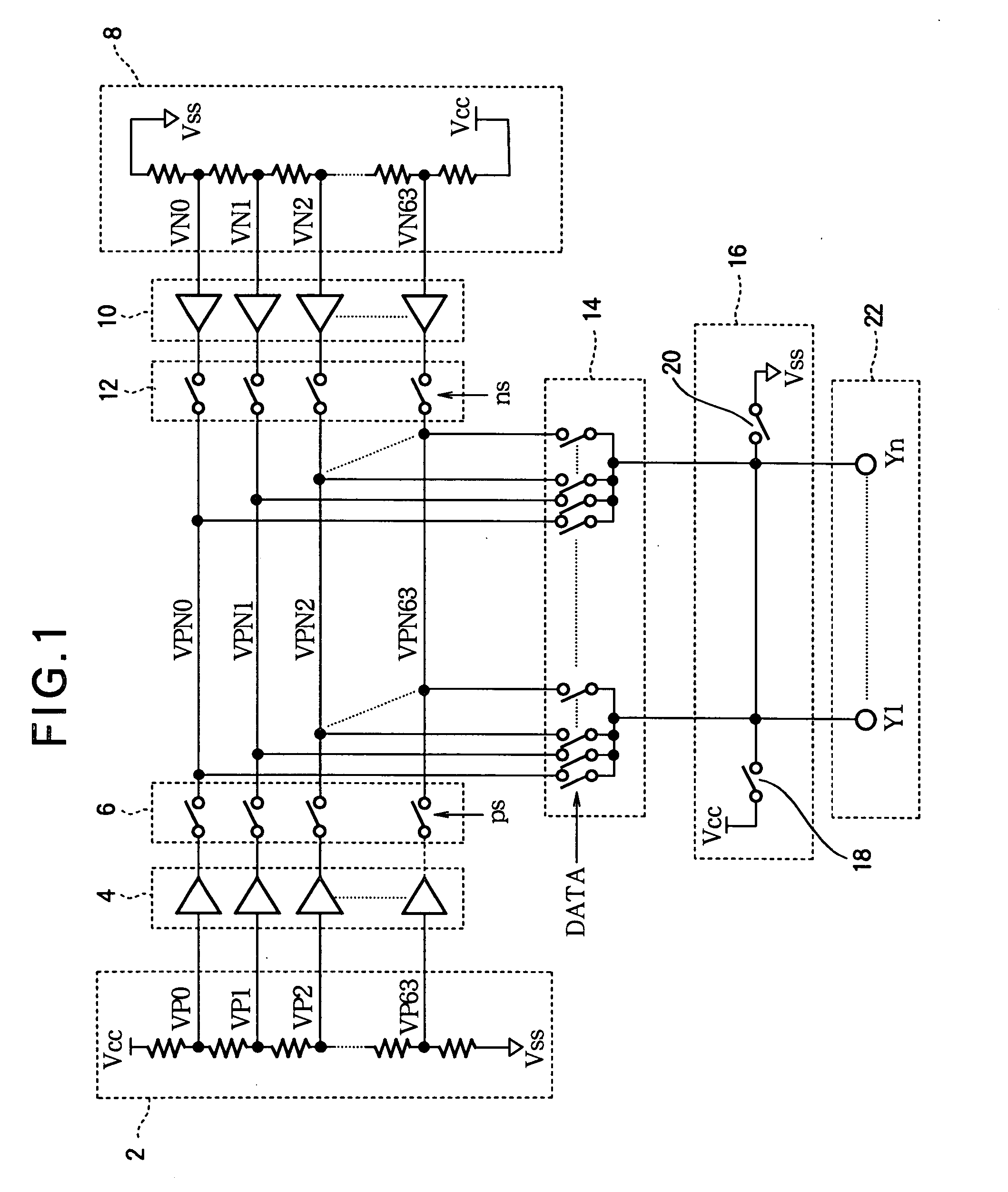

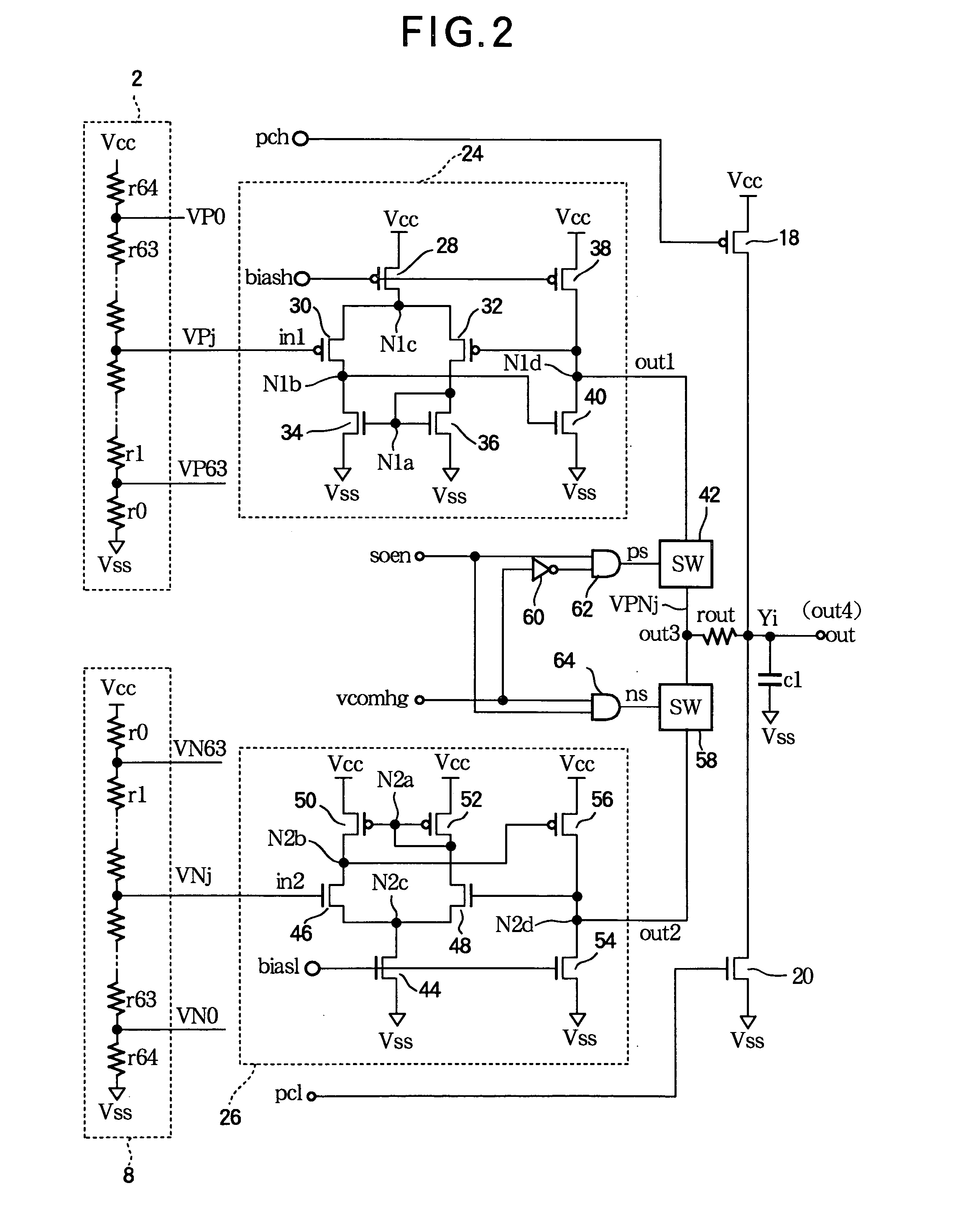

Voltage generating circuit with two resistor ladders

InactiveUS20060006928A1Reduce overshoot and undershootAccurate output levelStatic indicating devicesElectronic switchingElectrical resistance and conductanceAudio power amplifier

A voltage generating circuit that drives multiple output terminals in alternating positive and negative cycles has two resistor ladders, one resistor ladder generating voltages for the positive cycles, the other resistor ladder generating voltages for the negative cycles. Single-ended amplifiers are connected directly to the resistor ladders, and a switching circuit connects each output terminal to a selectable one of the amplifiers. The output terminals may be precharged to opposite potentials at the beginning of positive and negative cycles, and the resistor ladders may include switching elements that initially set all generated voltages to these potentials so that the amplifiers start each cycle with equal input and output levels, reducing overshoot and undershoot. This voltage generating circuit saves space and power in driving, for example, a display panel in a mobile telephone.

Owner:LAPIS SEMICON CO LTD

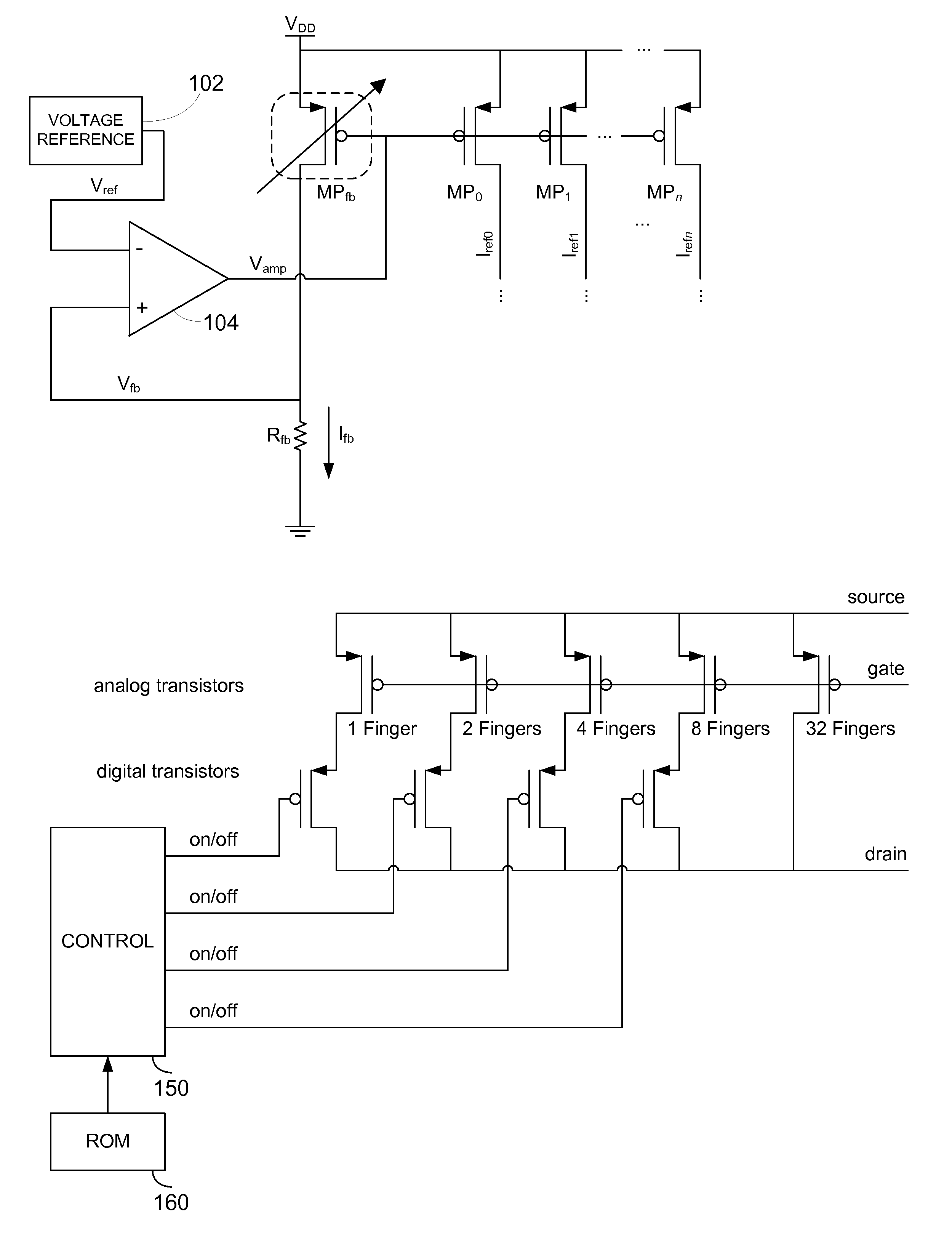

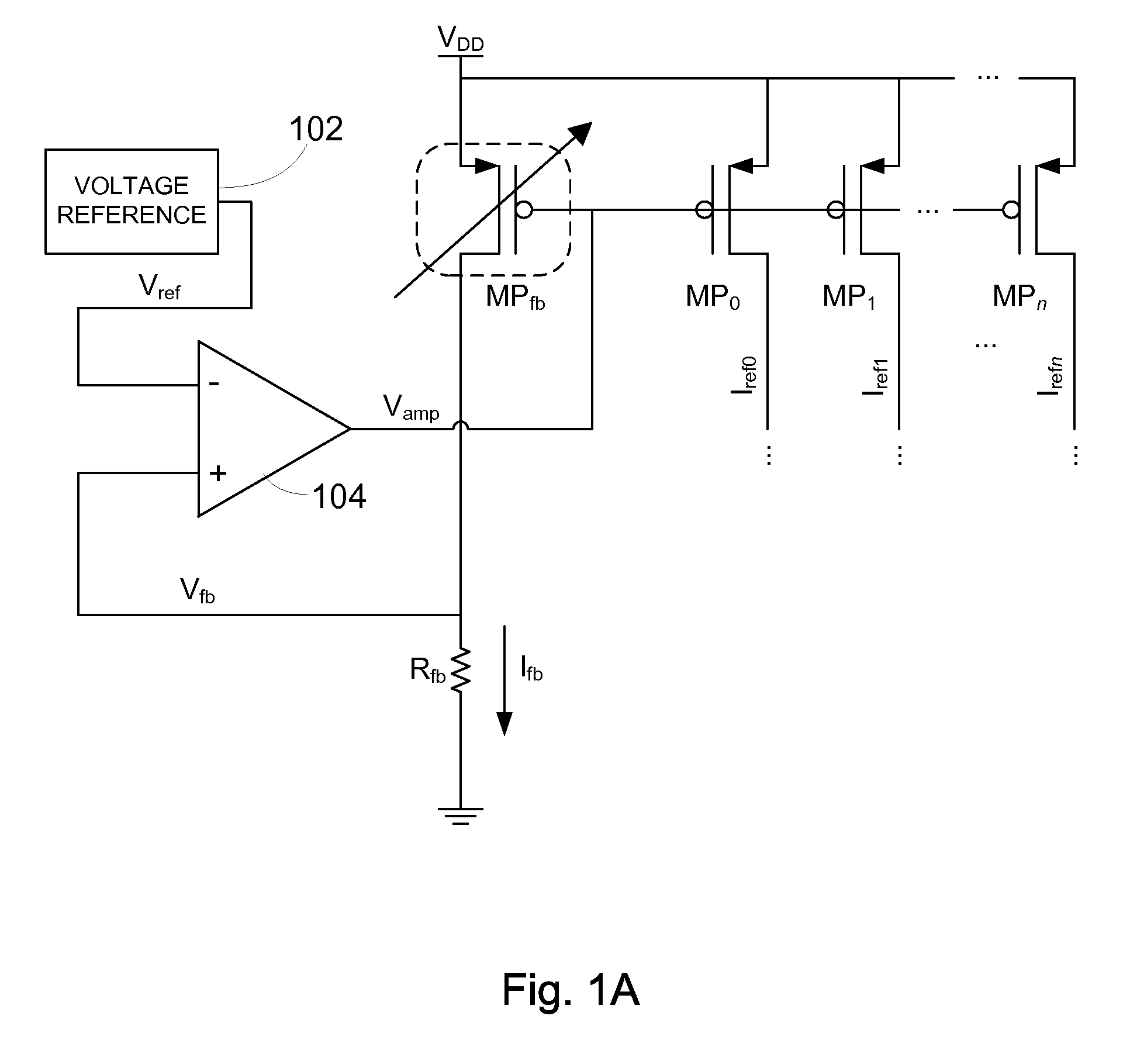

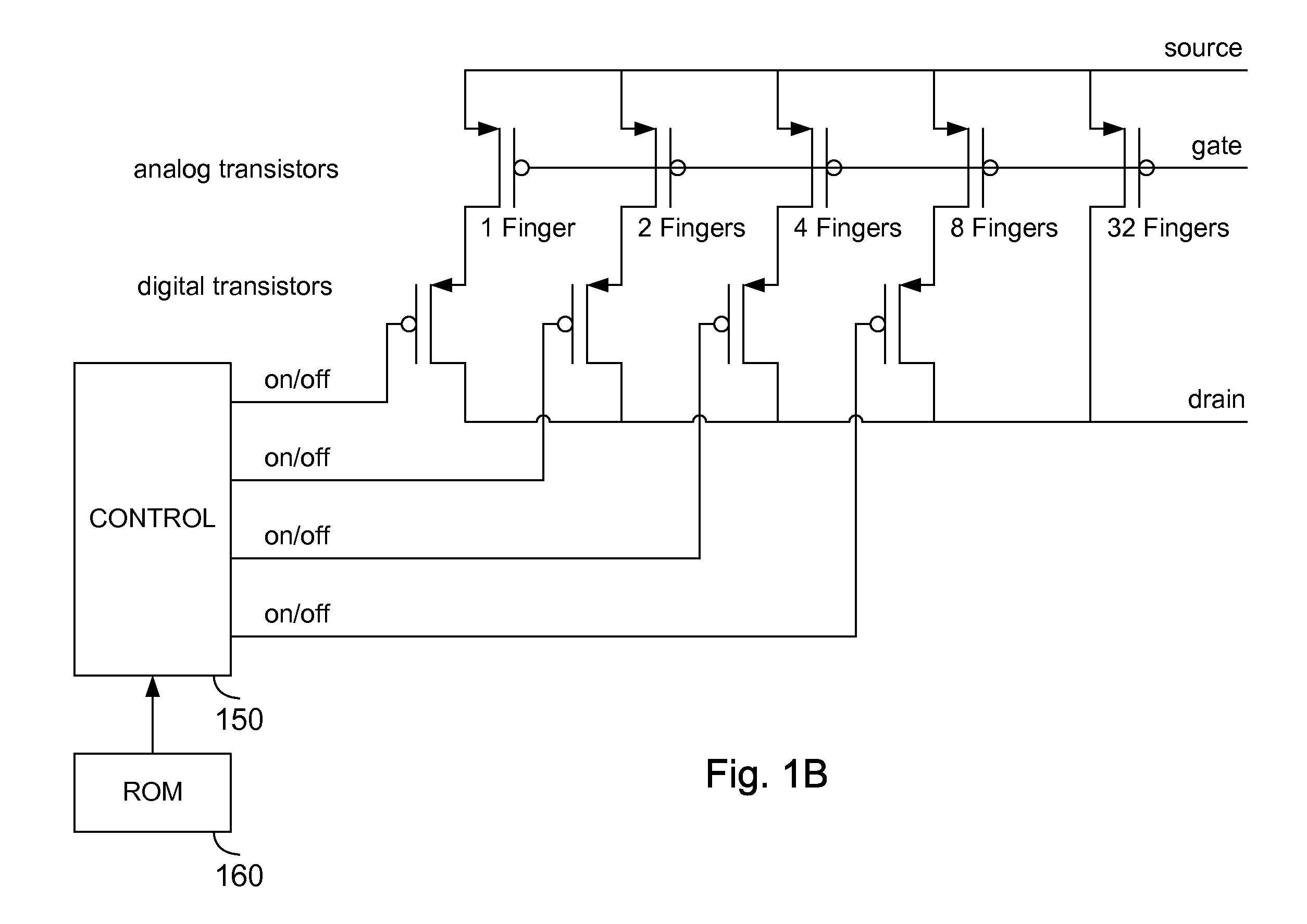

Current mirror bias trimming technique

A reference current is generated by a current mirror circuit. An operational amplifier of a feedback circuit generates a control voltage for control of the feedback circuit transistor. The size of the feedback circuit transistor is trimmed, and the current through the feedback circuit transistor remains relatively constant via operation of the feedback circuit. The feedback circuit transistor is scaled in size relative to the size of current reference transistor(s) (e.g., current sources or sinks), which are tied to the same control voltage. The reference current of the current reference transistors thus varies with the size of the feedback circuit transistor. Further advantageously, transistors providing reference currents for resistor ladders can also be tied to the same control voltage, but scaled proportionally with changes in size to the feedback circuit transistor, thereby maintaining relatively constant voltage from taps of the resistor ladder, even when the feedback circuit transistor is trimmed.

Owner:SEMICON COMPONENTS IND LLC

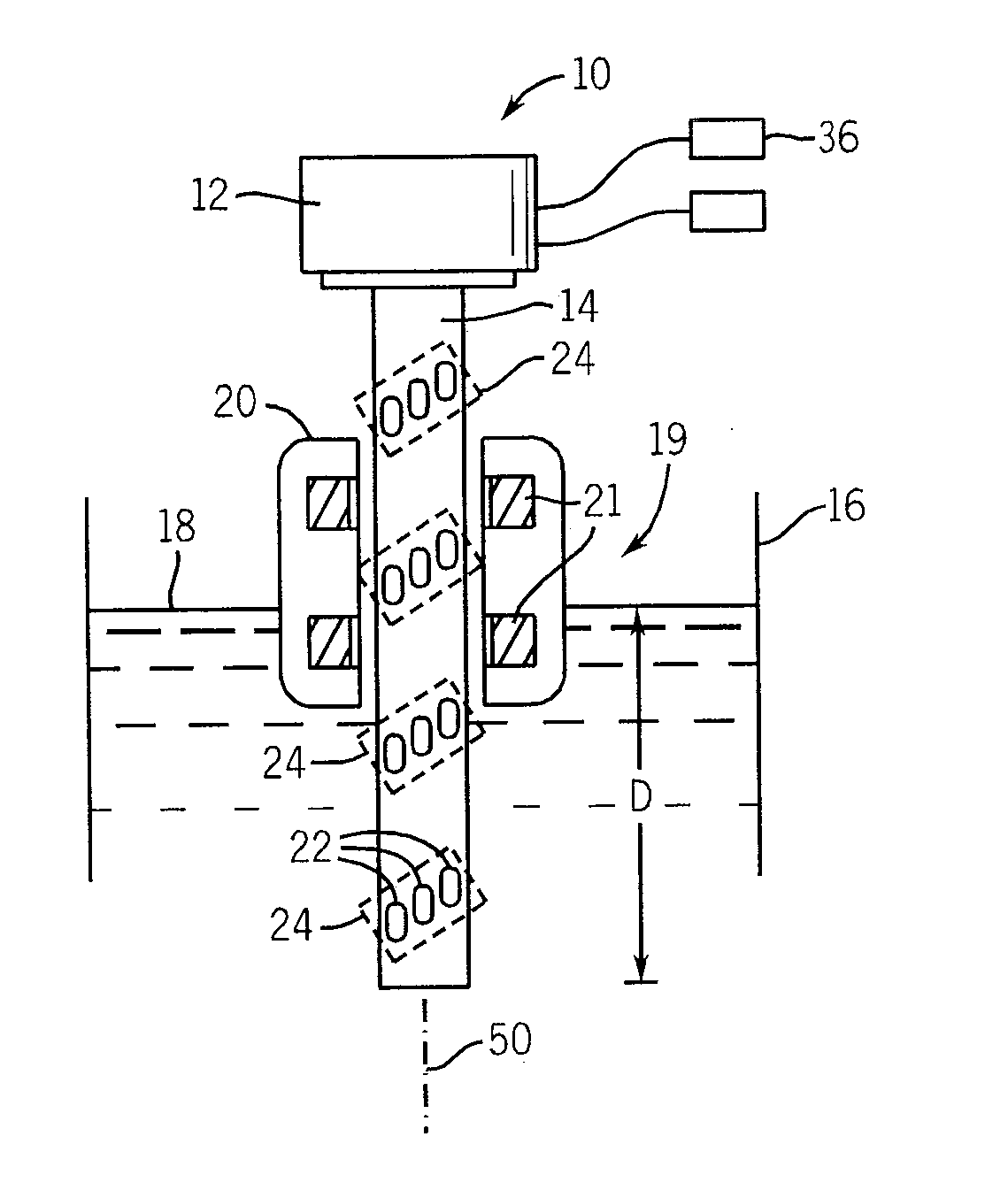

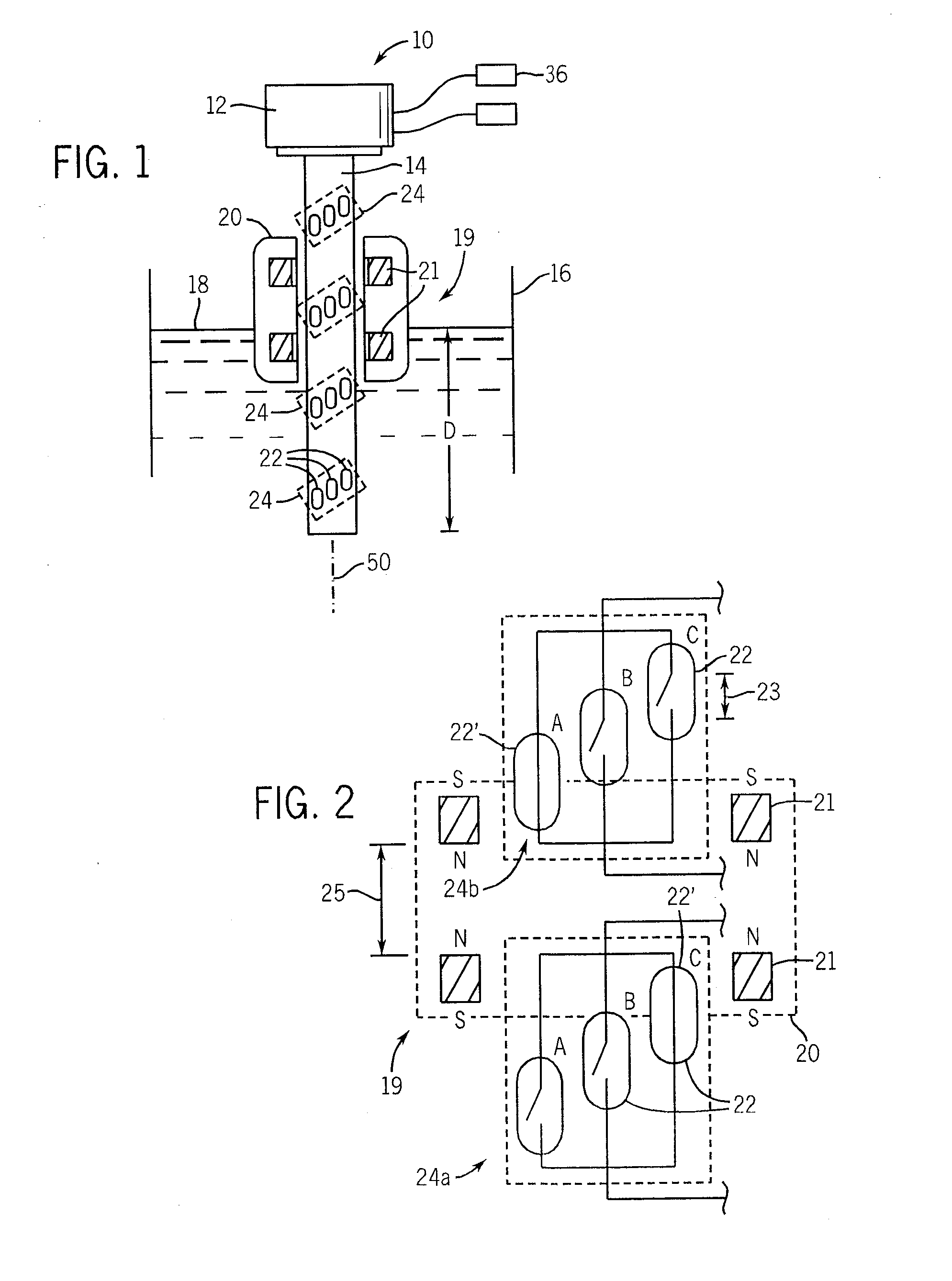

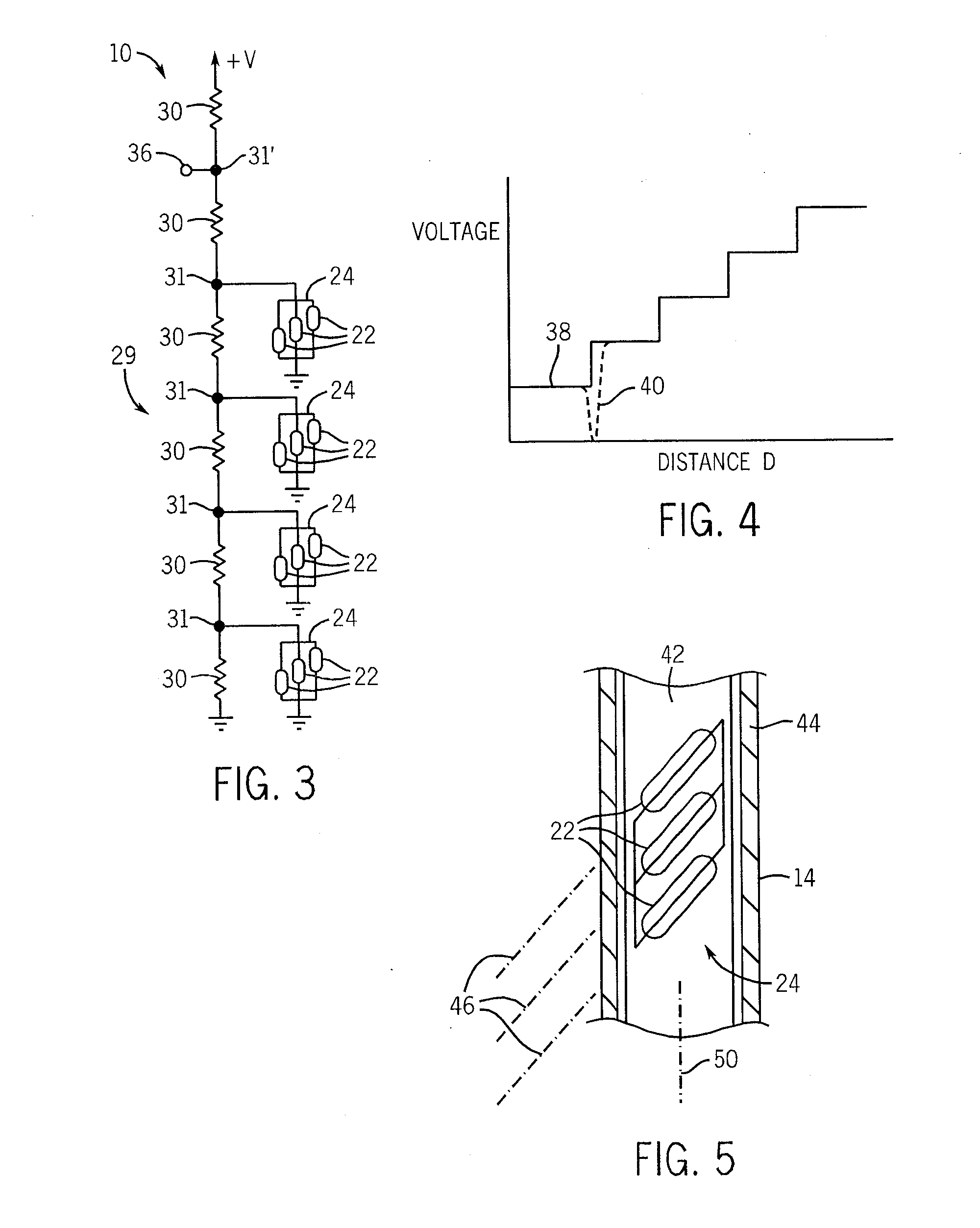

Multi-level liquid level magnetic sensor

InactiveUS20110138907A1Expand the scope of operationLow costMachines/enginesLubrication indication devicesElectrical resistance and conductanceEngineering

A liquid level sensor employs a set of axially displaced magnetic sensing switches and a magnet on a float that may rise and fall on liquid level to activate and deactivate the switches. The switches and magnet are configured so that movement of the magnetic float activates a new switch before deactivation of an adjacent previously activated switch. An electronic circuit provides a signal based on the uppermost activated switch to provide a signal that is monotonic with liquid level. The design may be readily implemented using reed switches and a resistive ladder.

Owner:ILLINOIS TOOL WORKS INC

AC coupling circuit integrated with receiver with hybrid stable common-mode voltage generation and baseline-wander compensation

InactiveUS20080063091A1Maximum freedom for circuit optimizationReduce pollutionMultiple-port networksPulse automatic controlVoltage generatorEngineering

In a receiver, an AC-coupling solution uses a fully integrated circuit for simultaneously providing both baseline wander compensation and common-mode voltage generation. Usefully, an integrated capacitor is placed between the receiver input pin and the input buffer, and a high resistive impedance element is connected to the internal high-speed data node after the capacitor. An on-chip voltage generation and correction circuit is connected to the other side of the impedance element to generate a common-mode voltage, and to provide dynamic, fine adjustment for the received data voltage level. The voltage correction circuit is controlled by the feedback of data detected by the clock and data recovery unit (CDRU) of the receiver. The feedback data passes through a weighting element, wherein the amount of feedback gain is adjustable to provide a summing weight and thereby achieve a desired BLW compensation. Register bits are used to control an on-chip reference voltage generator that consists of a resistor ladder to generate the reference voltage.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

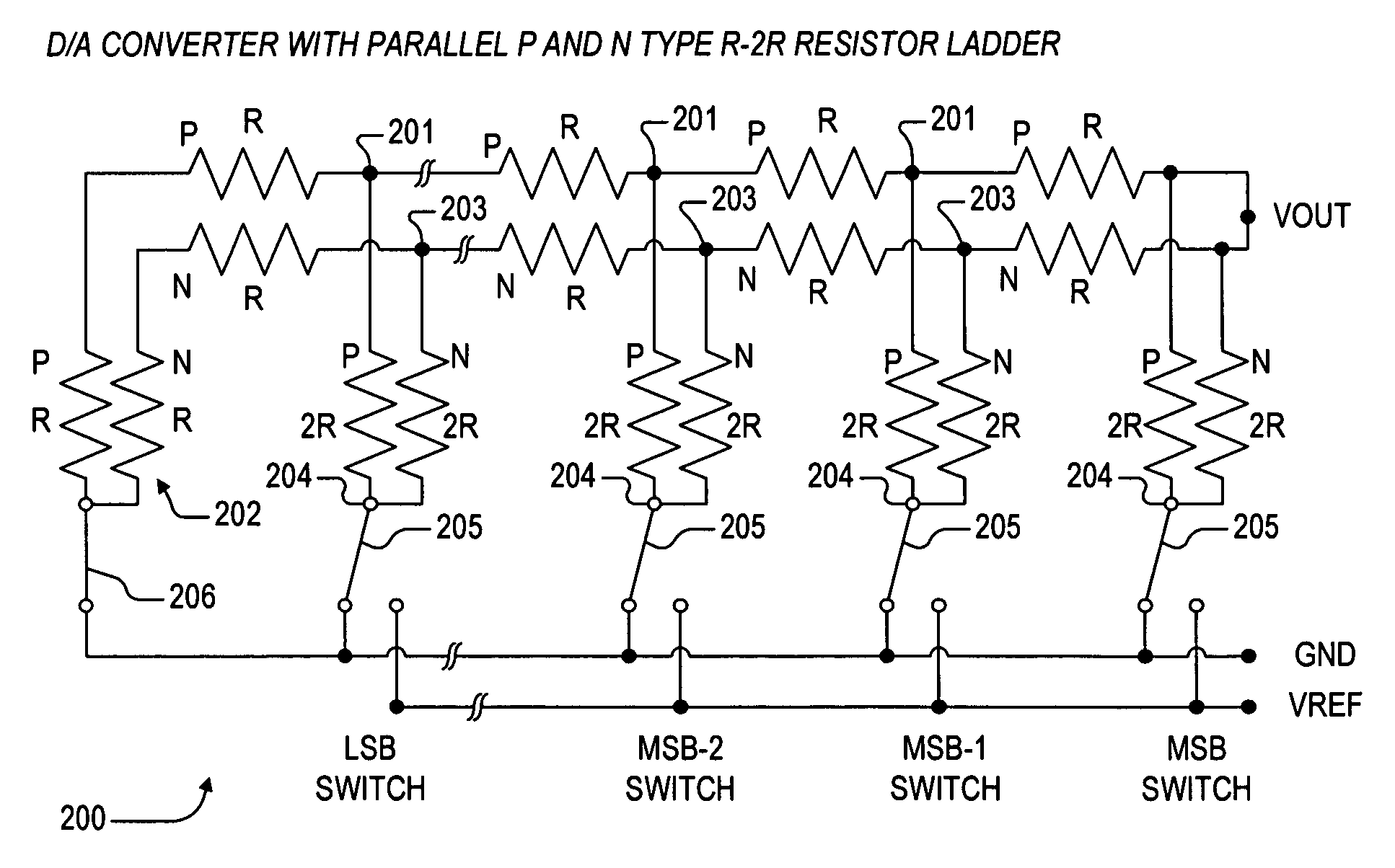

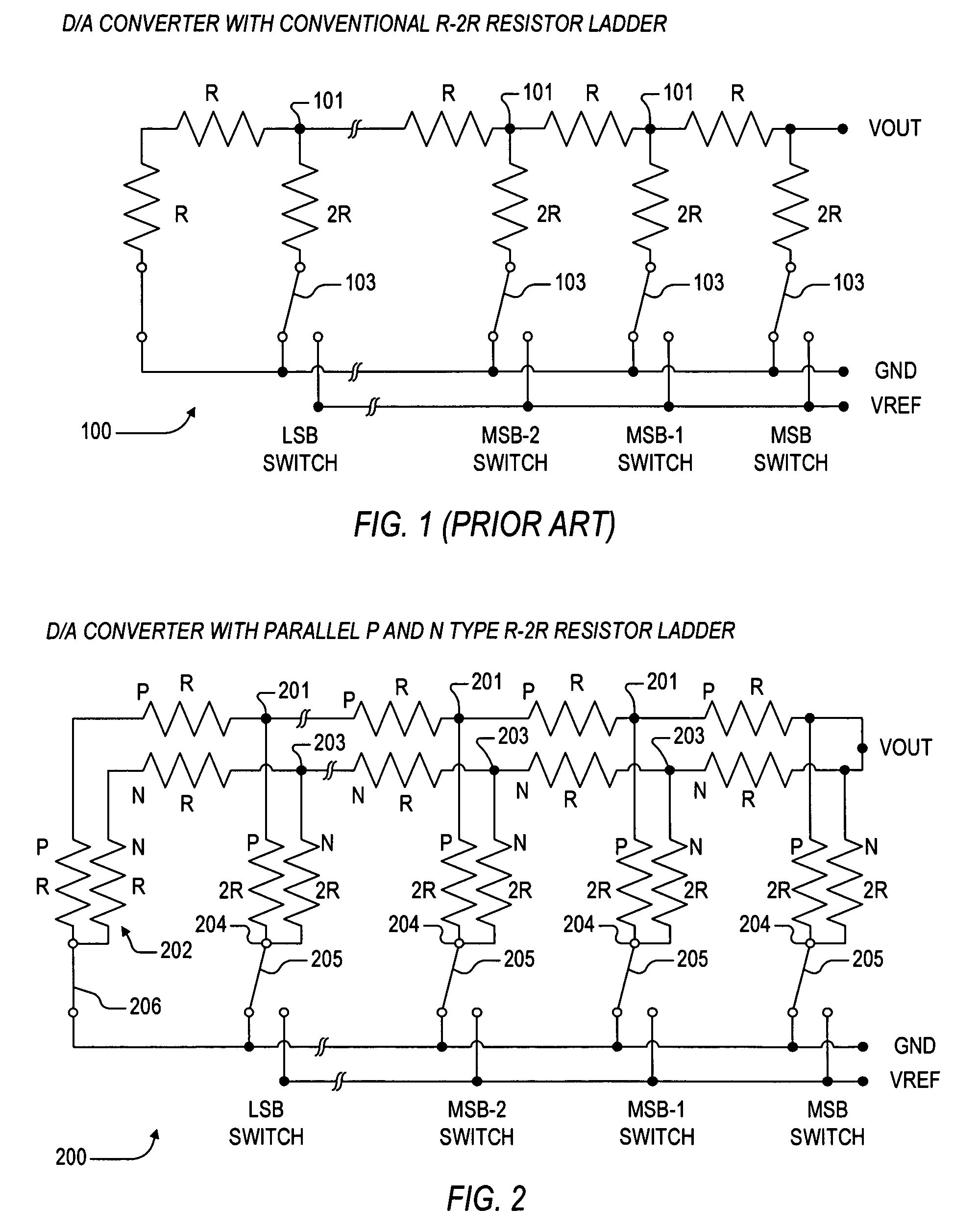

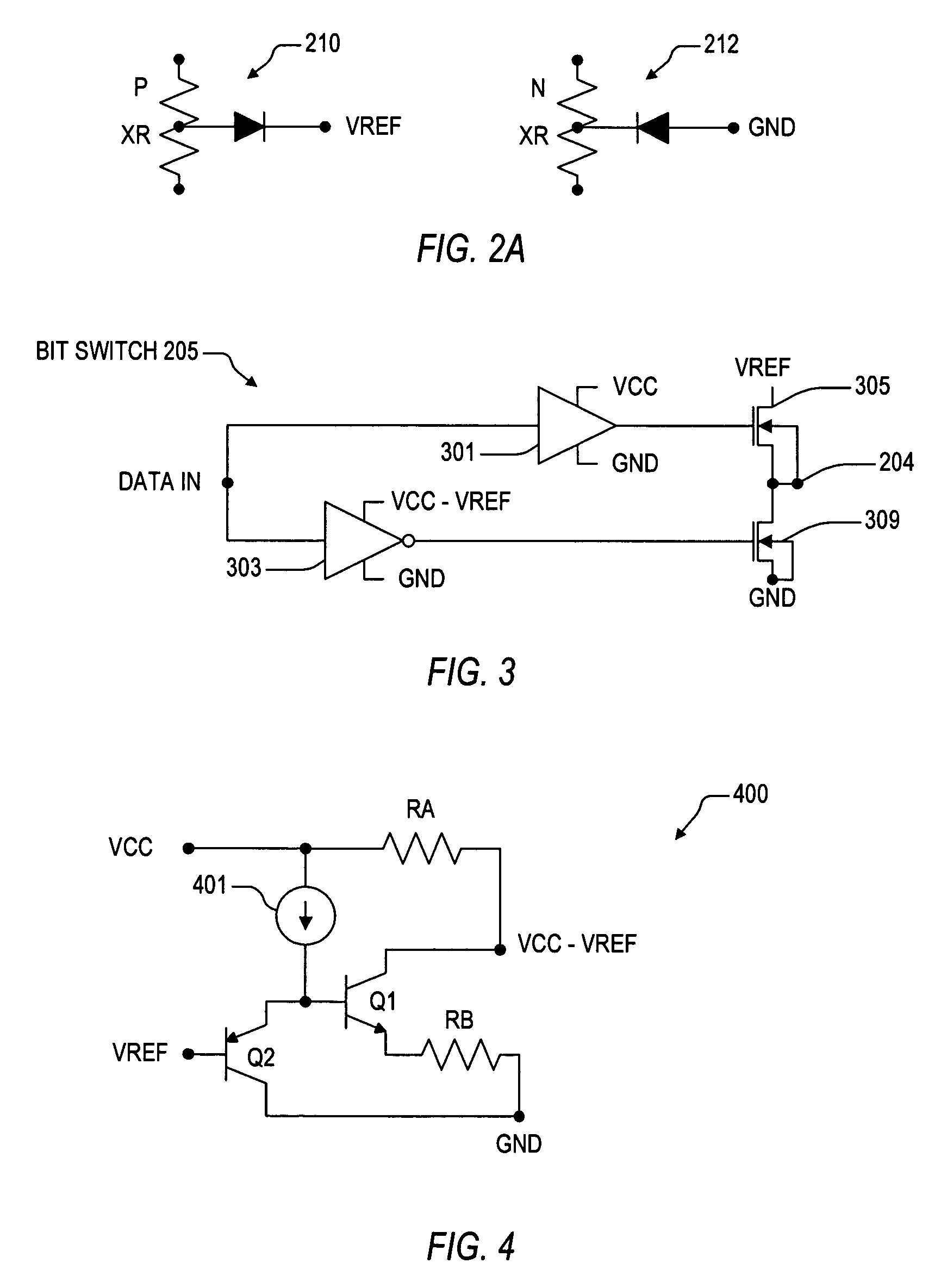

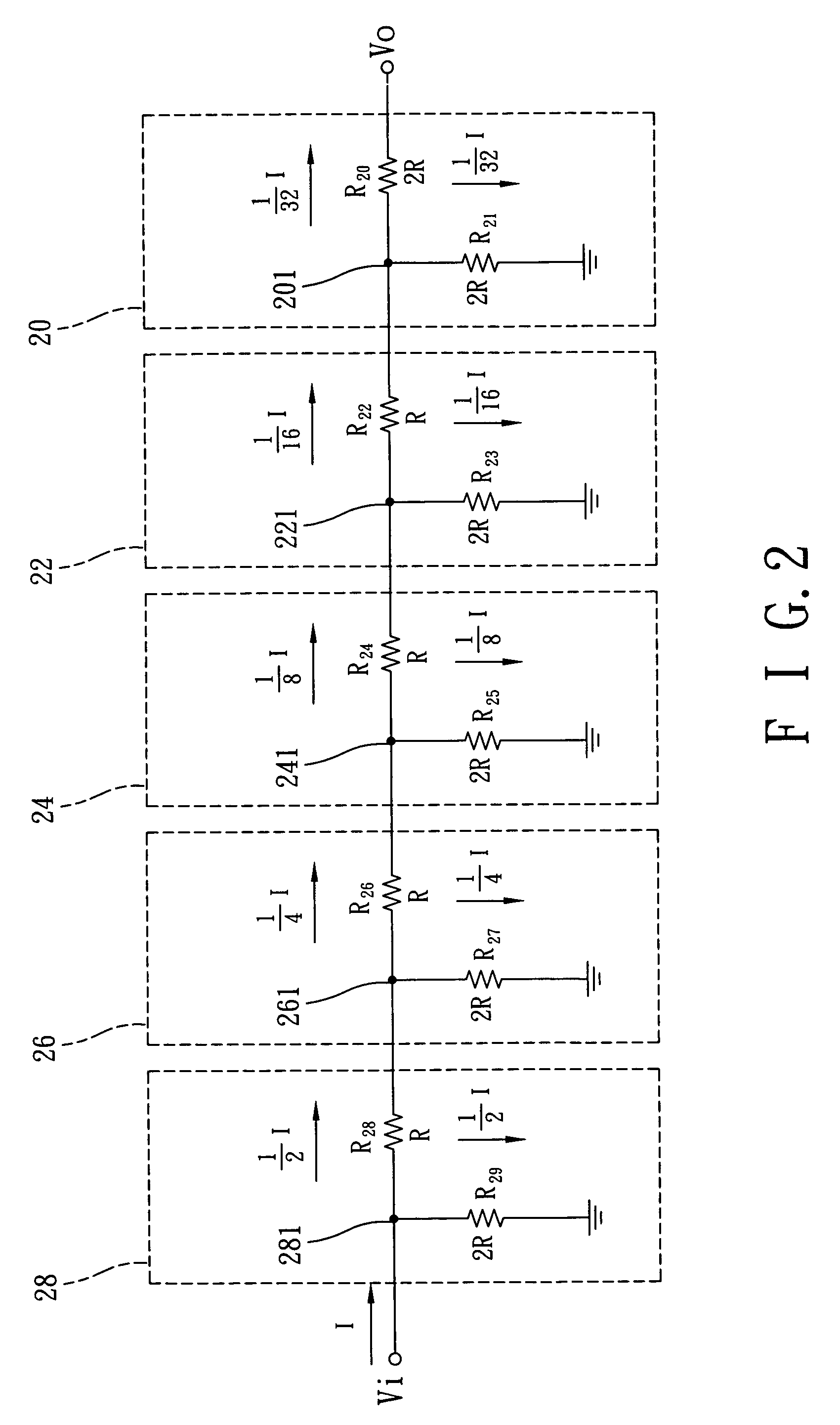

High accuracy digital to analog converter using parallel P and N type resistor ladders

ActiveUS6975261B1Electric signal transmission systemsDigital-analogue convertorsVoltage referenceResistor ladder

A D / A converter including first and second R-R2 resistor ladders and a set of SPDT switches. The first R-2R resistor ladder includes N type resistors coupled between a common voltage node and an output voltage node and the second R-2R resistor ladder includes P type resistors coupled between the common and output voltage nodes. The R-2R resistor ladders have multiple common switch terminals, each coupling an N type 2R resistor to a corresponding P type 2R resistor. Each SPDT switch is responsive to a data bit for switching a common switch terminal between the common voltage and a reference voltage. Each N type resistor may be formed in a PWell coupled to the common (or more negative) voltage and each P type resistor may be formed in an NWell coupled to the reference (or more positive) voltage. The SPDT switches may be configured with equivalent switch path impedances.

Owner:INTERSIL INC

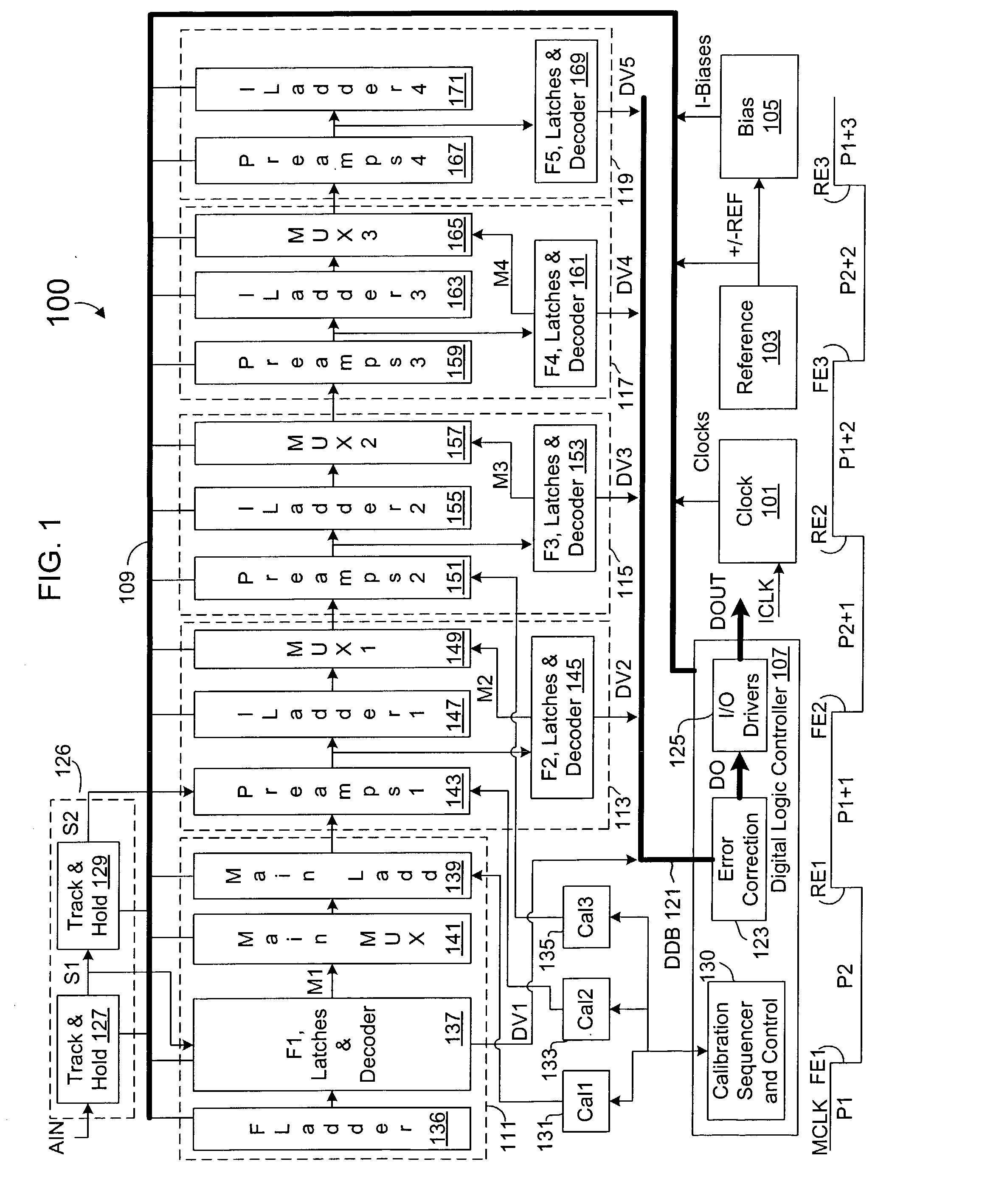

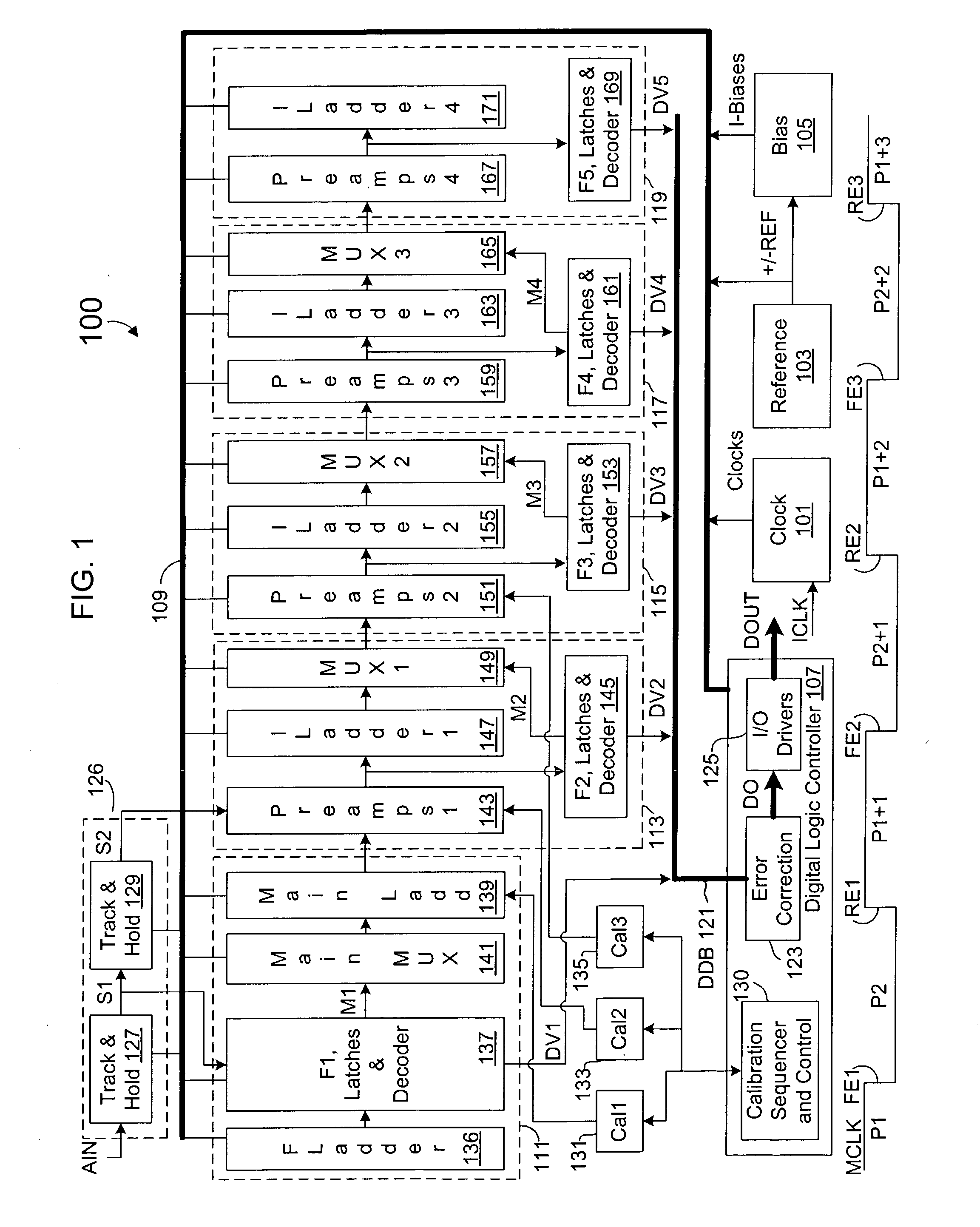

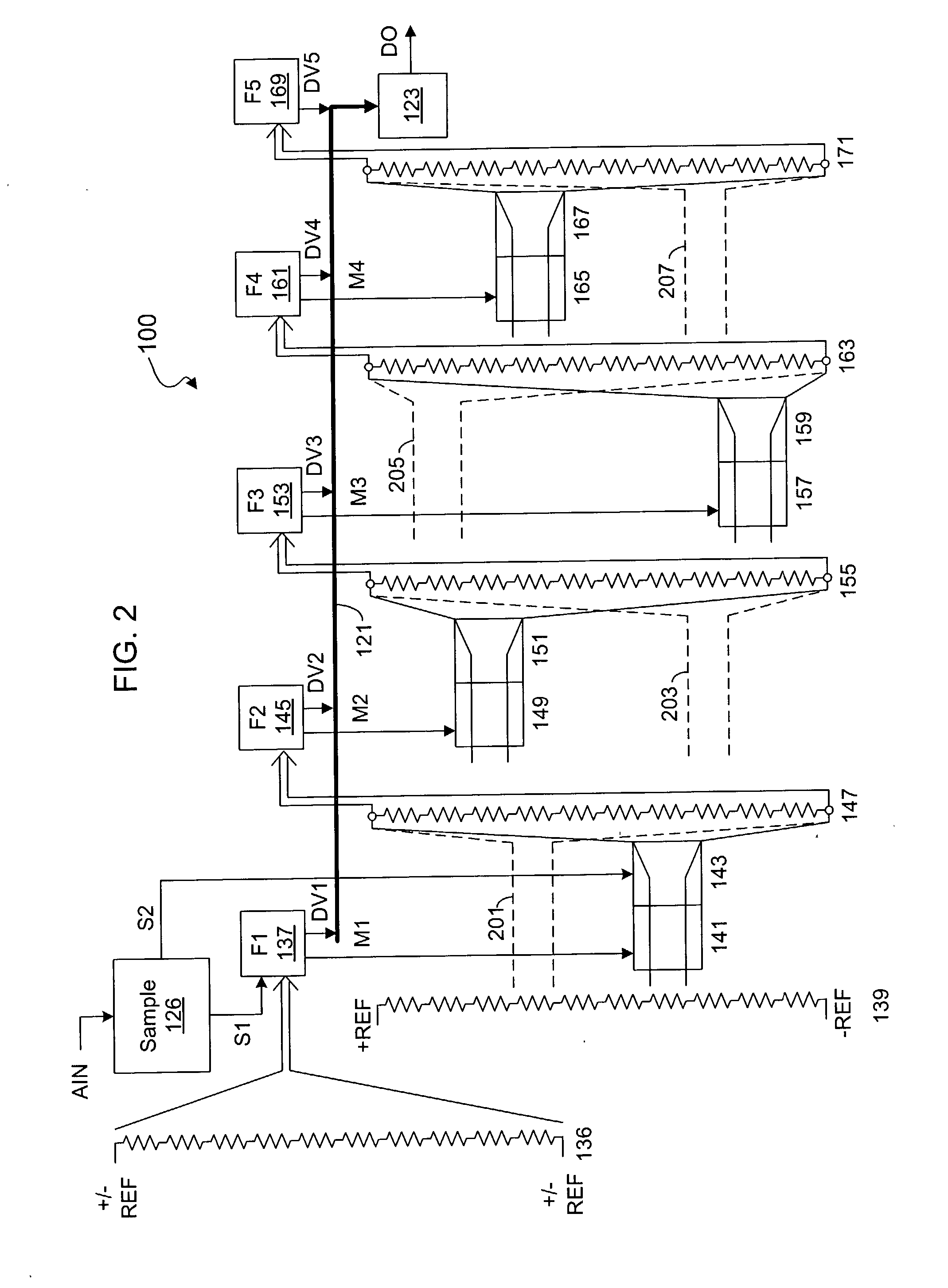

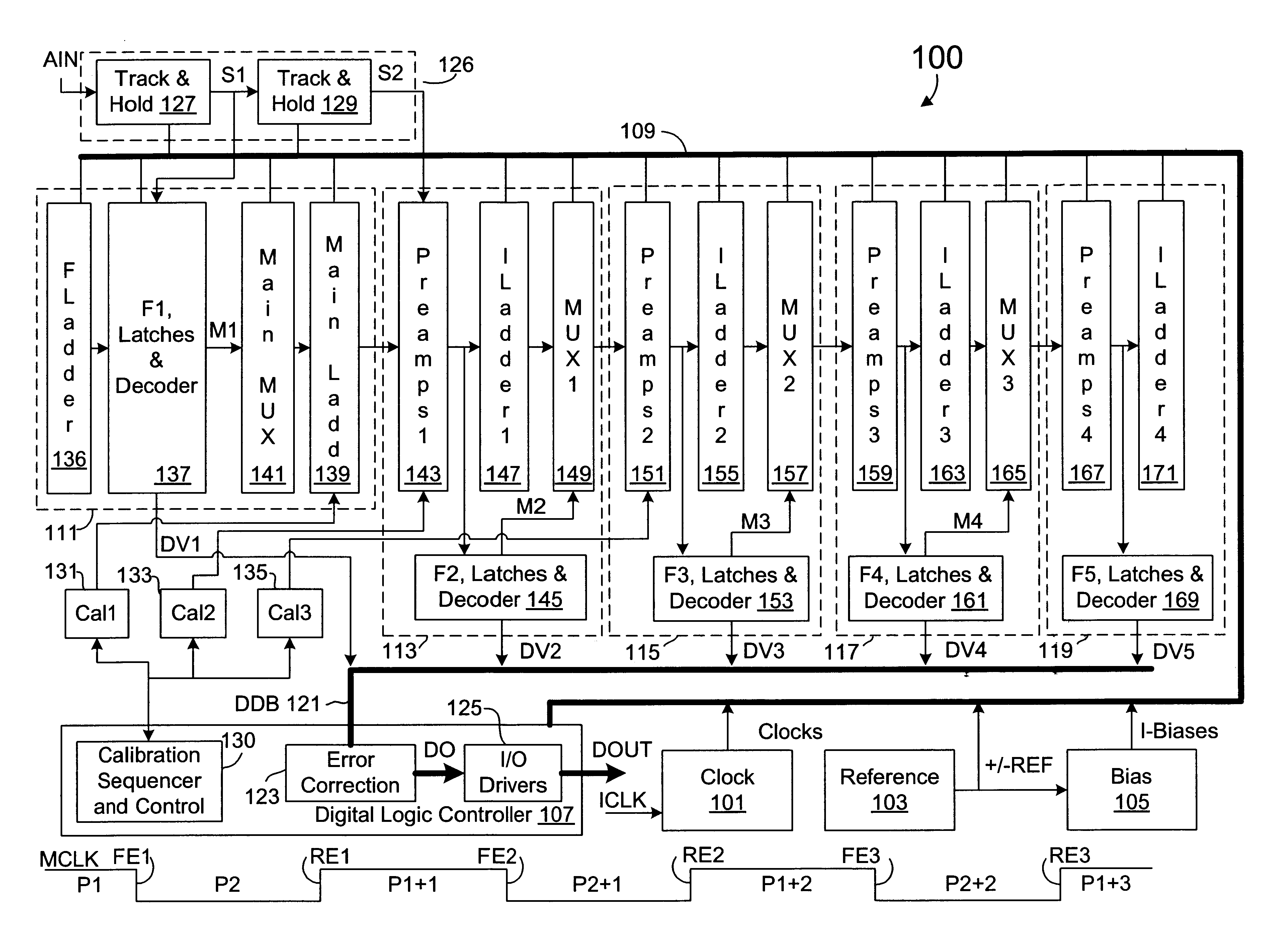

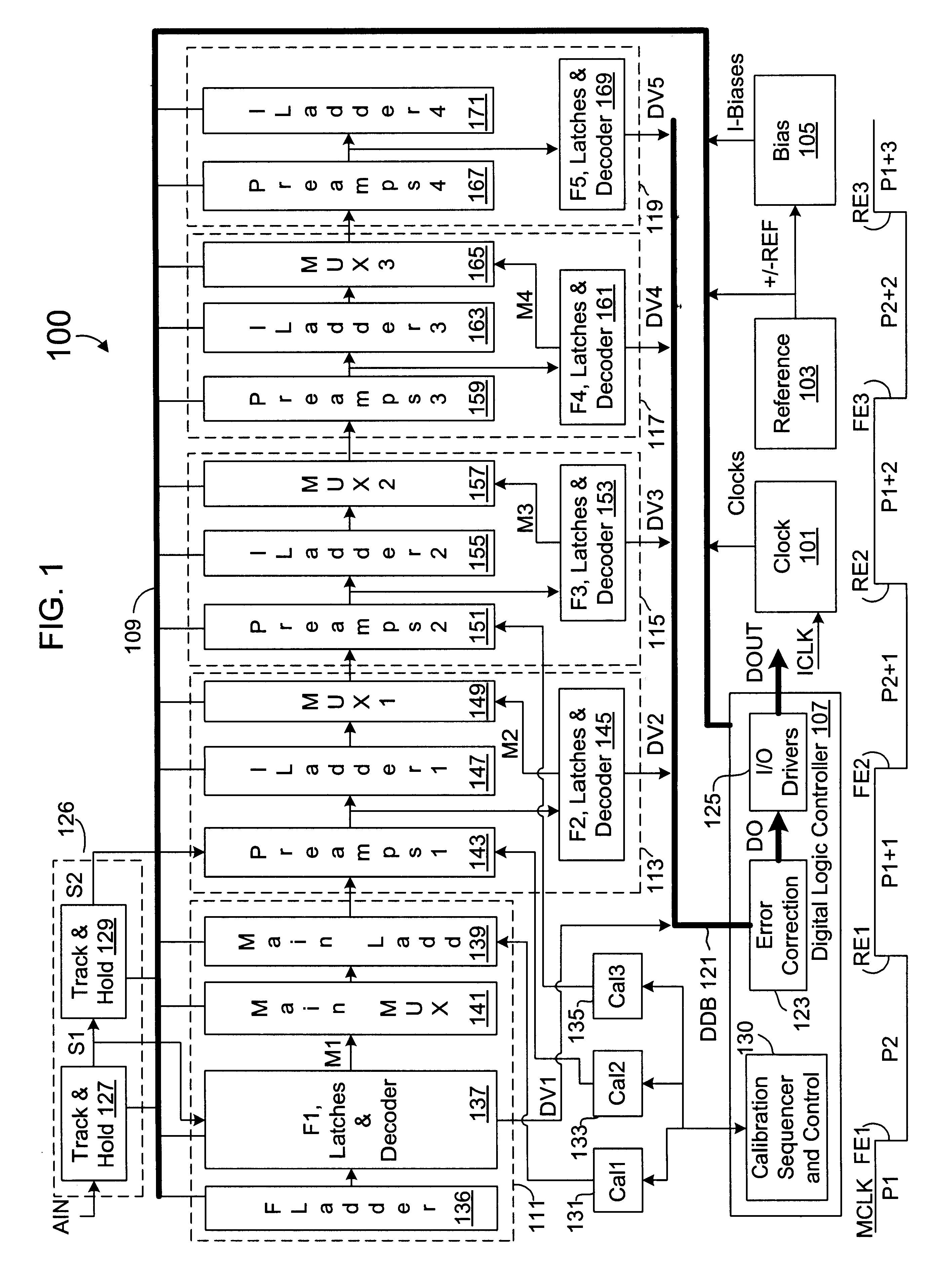

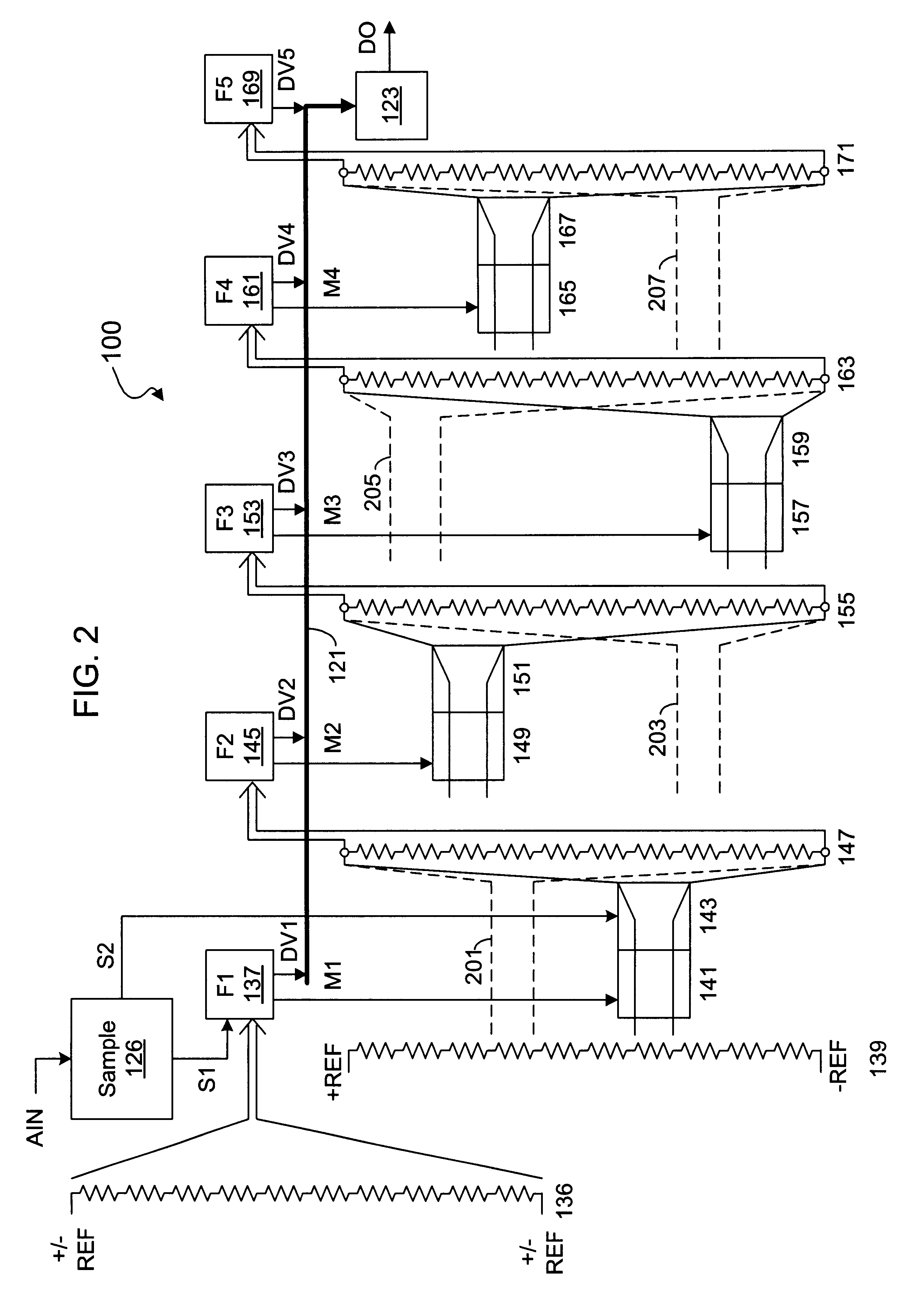

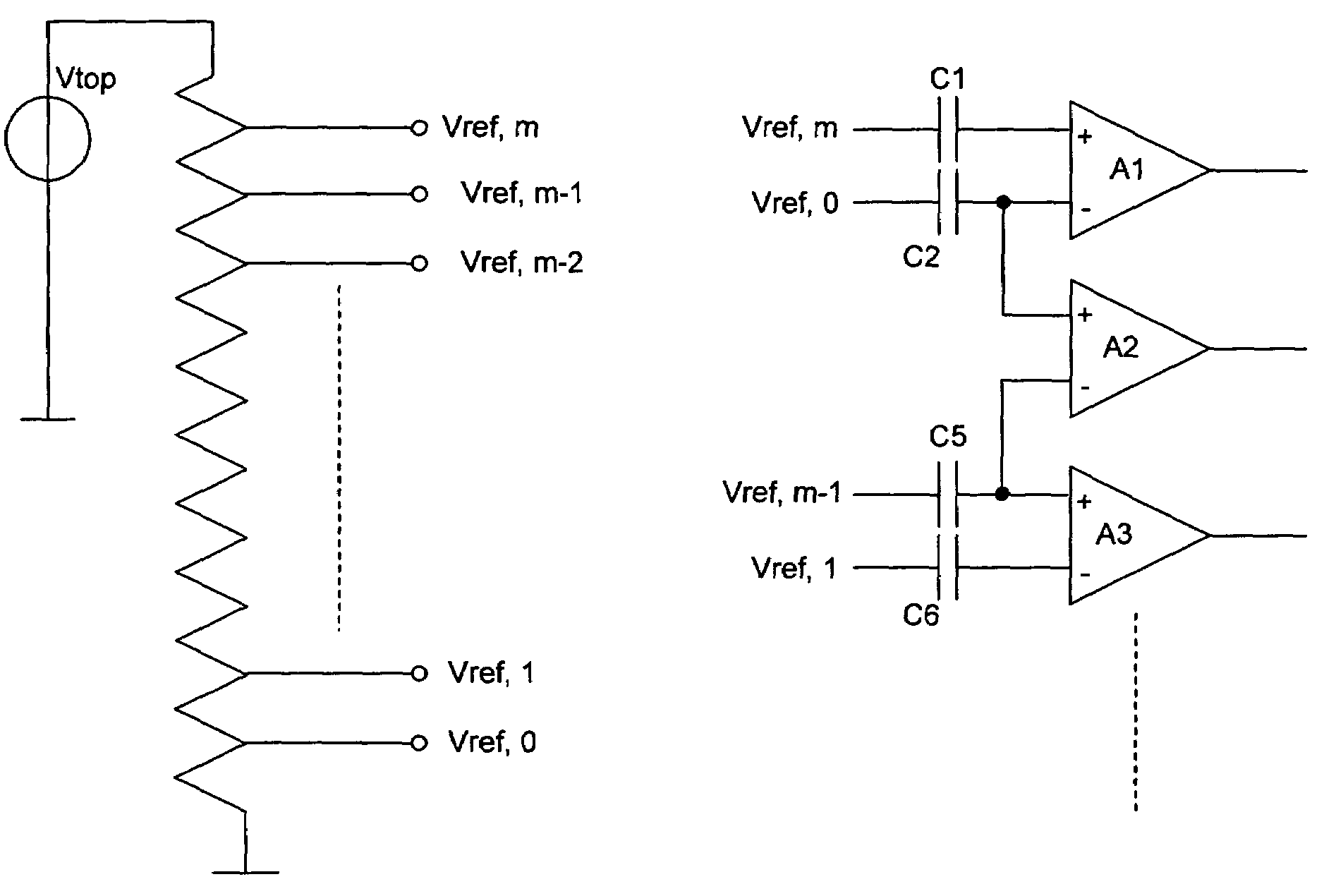

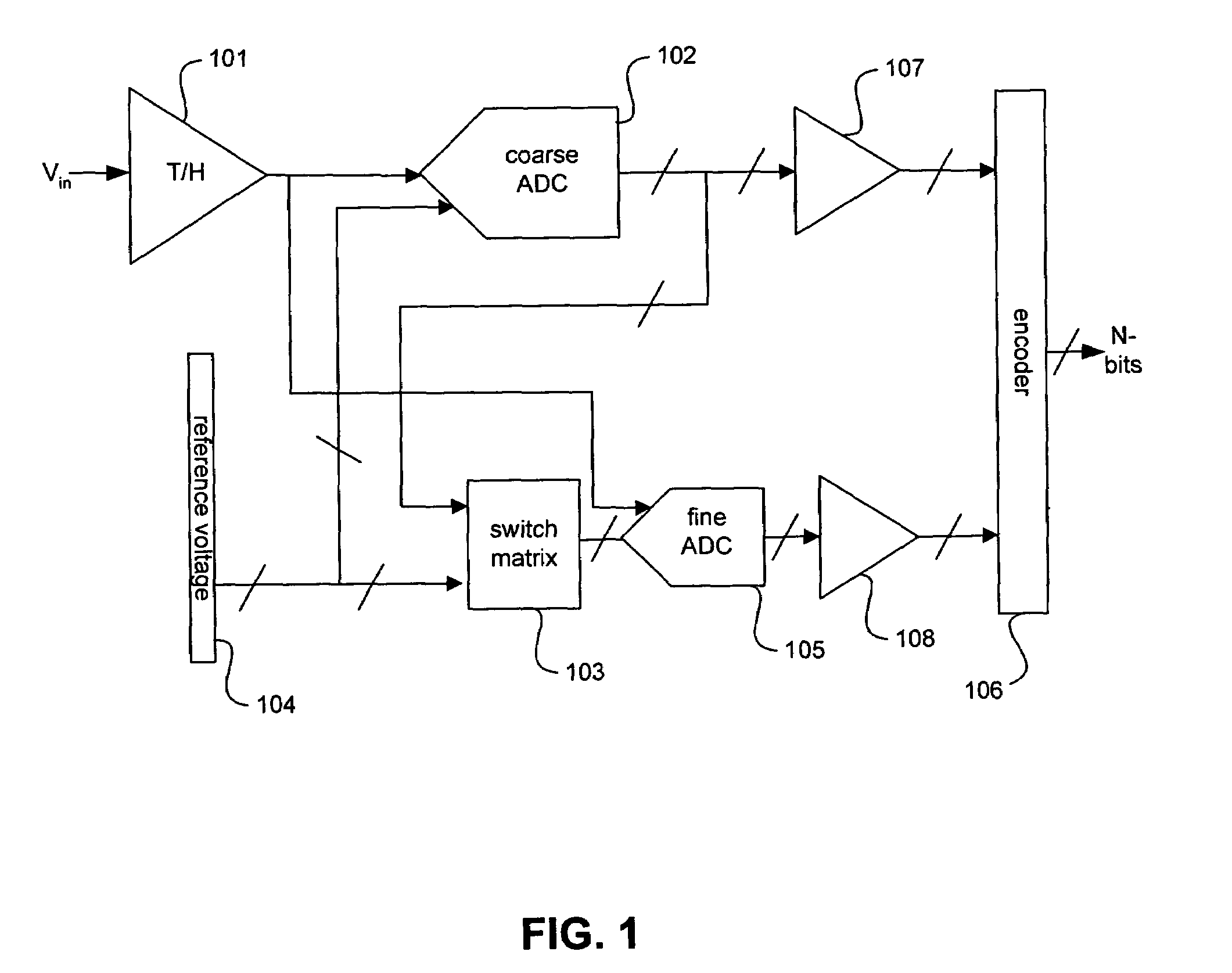

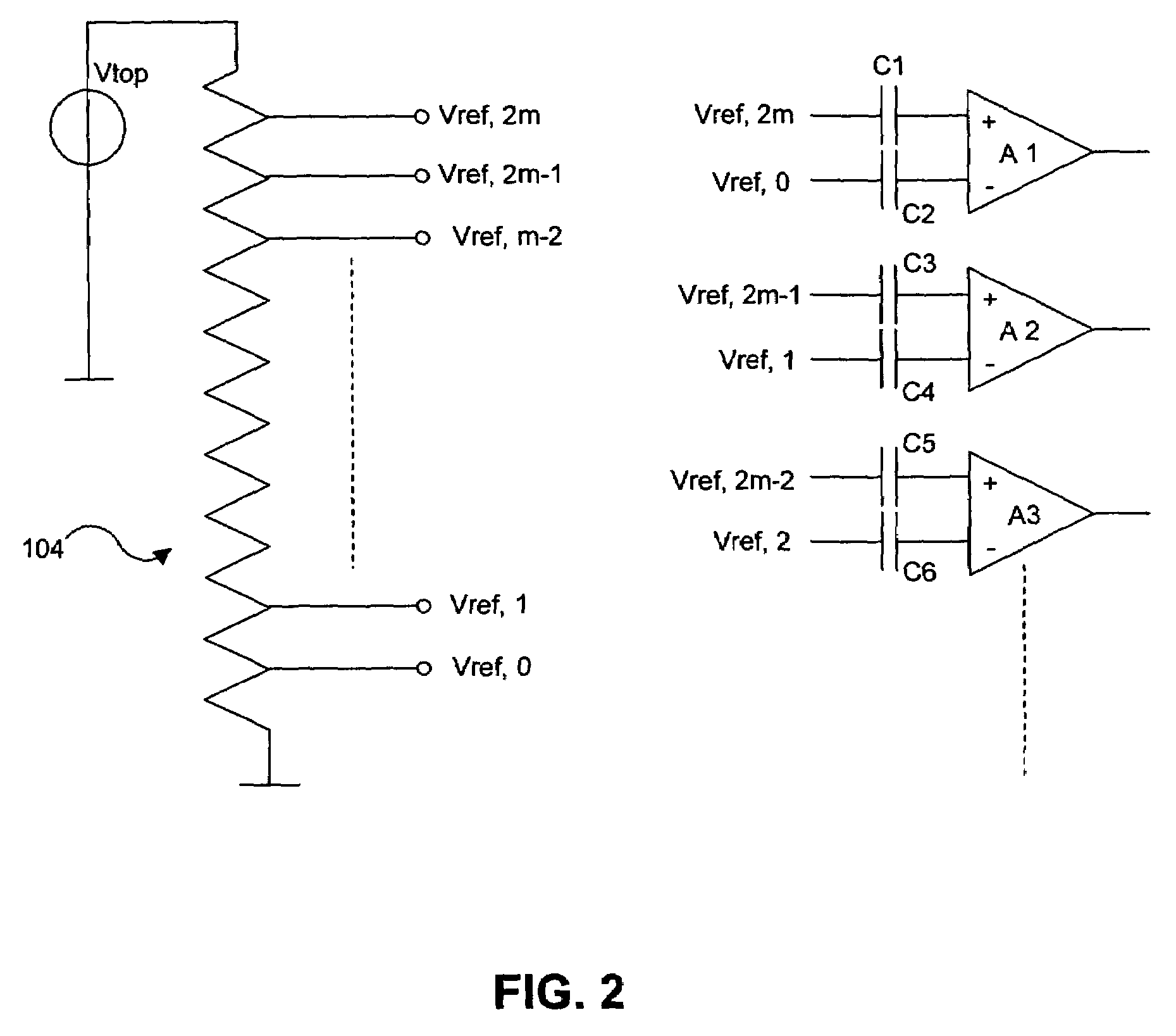

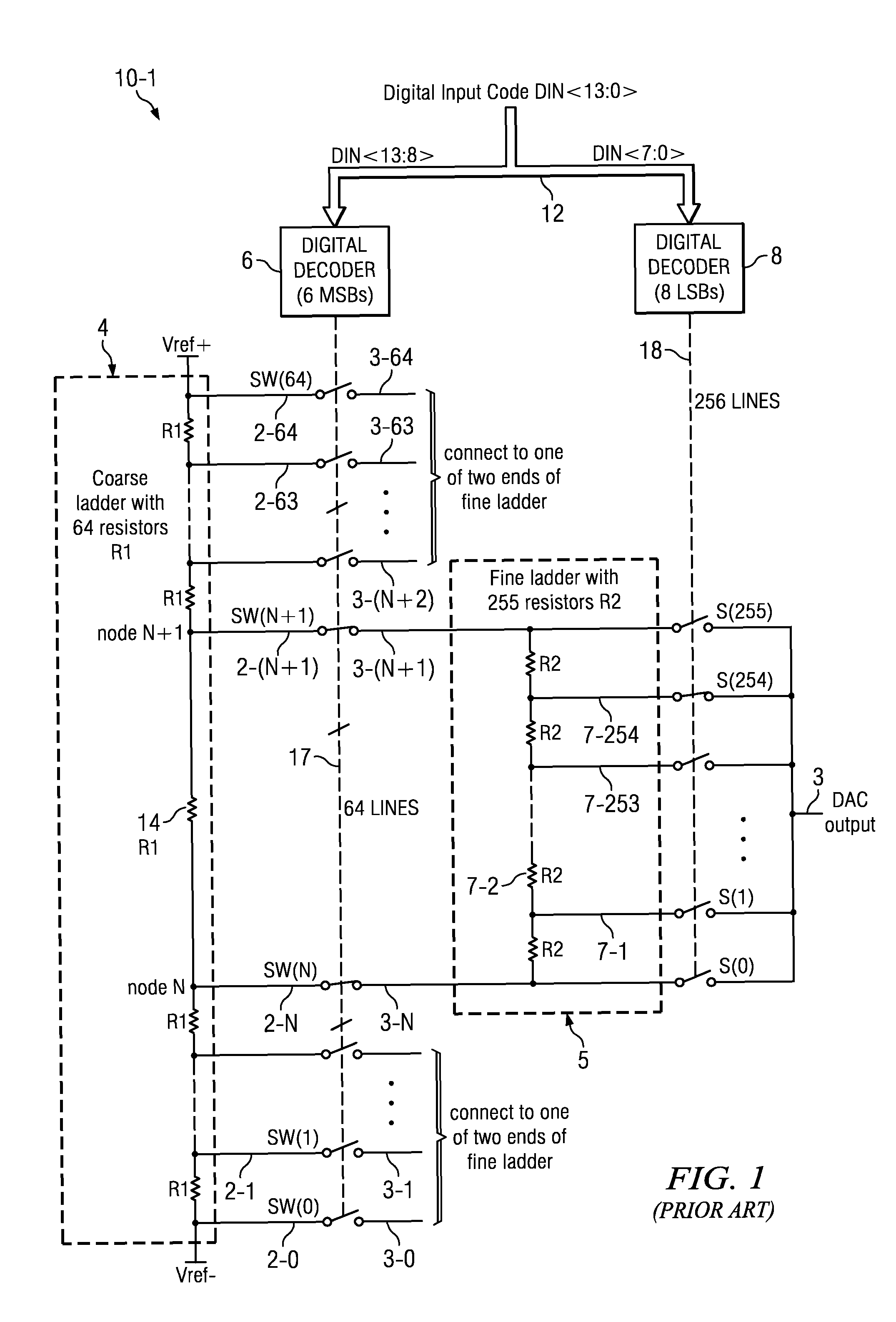

Resistor ladder interpolation for subranging ADC

An analog to digital converter includes a resistive ladder outputting a plurality of reference voltages and a coarse ADC receiving the reference voltages and a voltage input. A plurality of coarse comparators receive an output of the coarse ADC. A switch matrix receives an output of the coarse ADC and the reference voltages. The switch matrix inputs a plurality of control signals for selecting at least two voltage subranges. A fine ADC receives the two voltage subranges and the voltage input. A plurality of fine comparators receive an output of the fine ADC. An encoder converts outputs of the coarse and fine comparators to a digital representation of the voltage input. The voltage subranges are adjacent. Each control signal includes a plurality of control lines for controlling corresponding switches. The switches are field effect transistors.

Owner:AVAGO TECH INT SALES PTE LTD

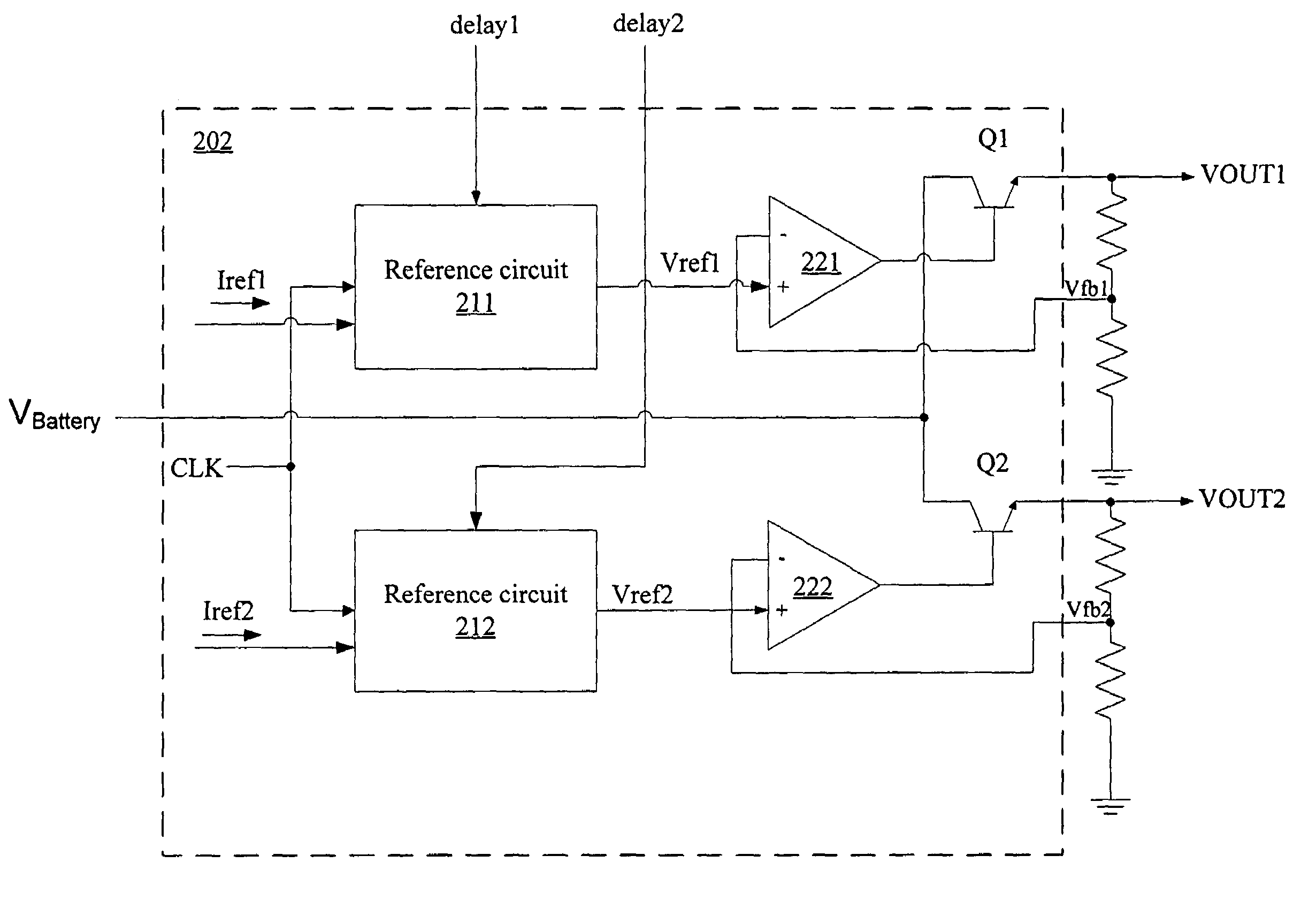

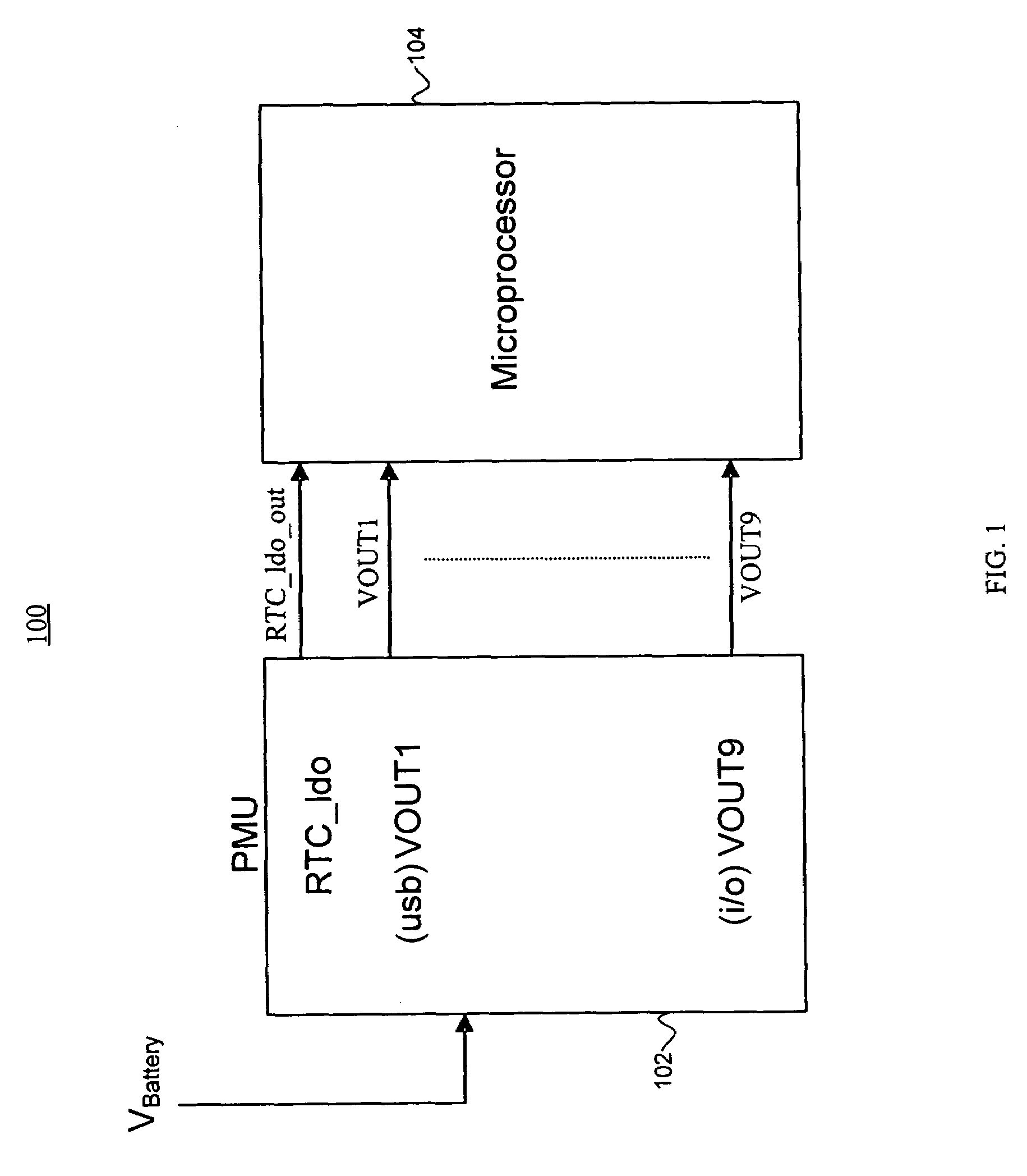

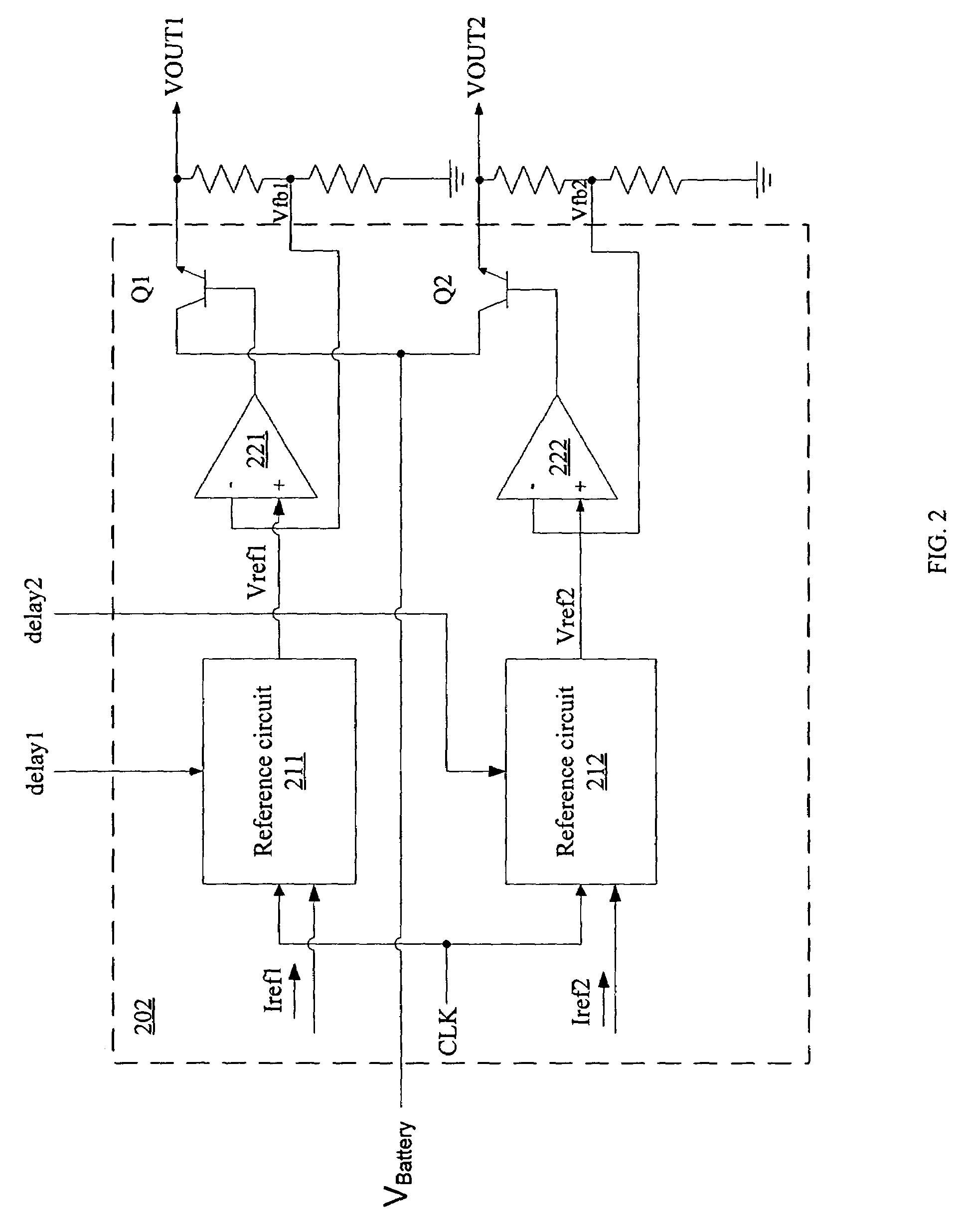

Apparatus and method for power sequencing for a power management unit

A PMU that includes LDOs is provided. The PMU also includes, for each LDO, a corresponding reference circuit that provides a reference voltage for the LDO. Further, the PMU includes a central bias circuit that provides a reference current to each of the voltage reference circuits. Each reference circuit includes a delay circuit, a counter, a binary-weighted resistor ladder, and switches coupled to the resistor ladder. In each reference circuit, the resistor ladder provides the corresponding reference voltage from the received reference current. Further, the counter controls the switches to “step up” the reference voltage in a well-defined manner during the power-up sequence. The reference voltage is stepped up from a minimum voltage to a final reference voltage by one least significant bit at each clock pulse. Also, the delay circuits are employed to control when each reference voltage begins to increase from the minimum voltage.

Owner:NAT SEMICON CORP

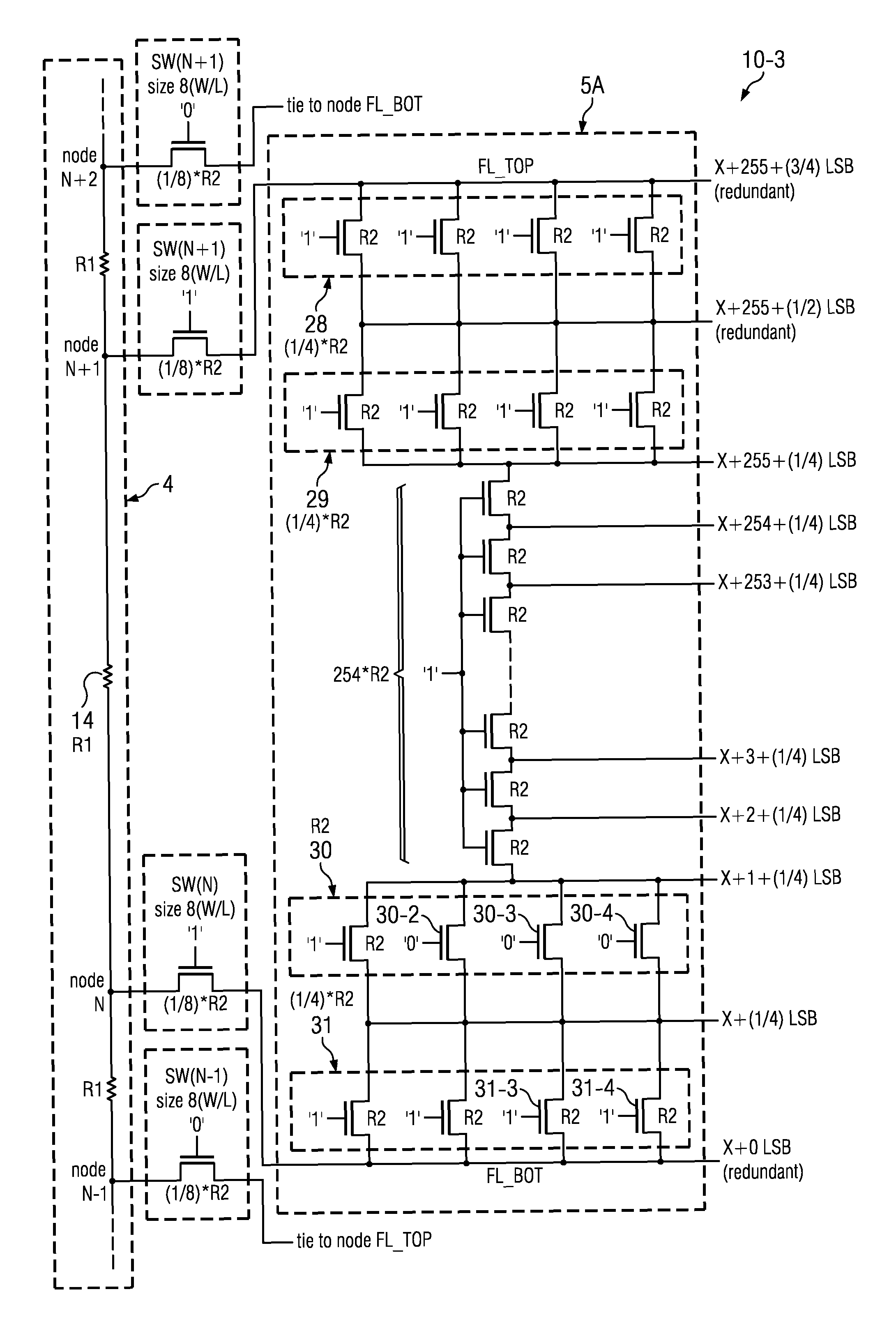

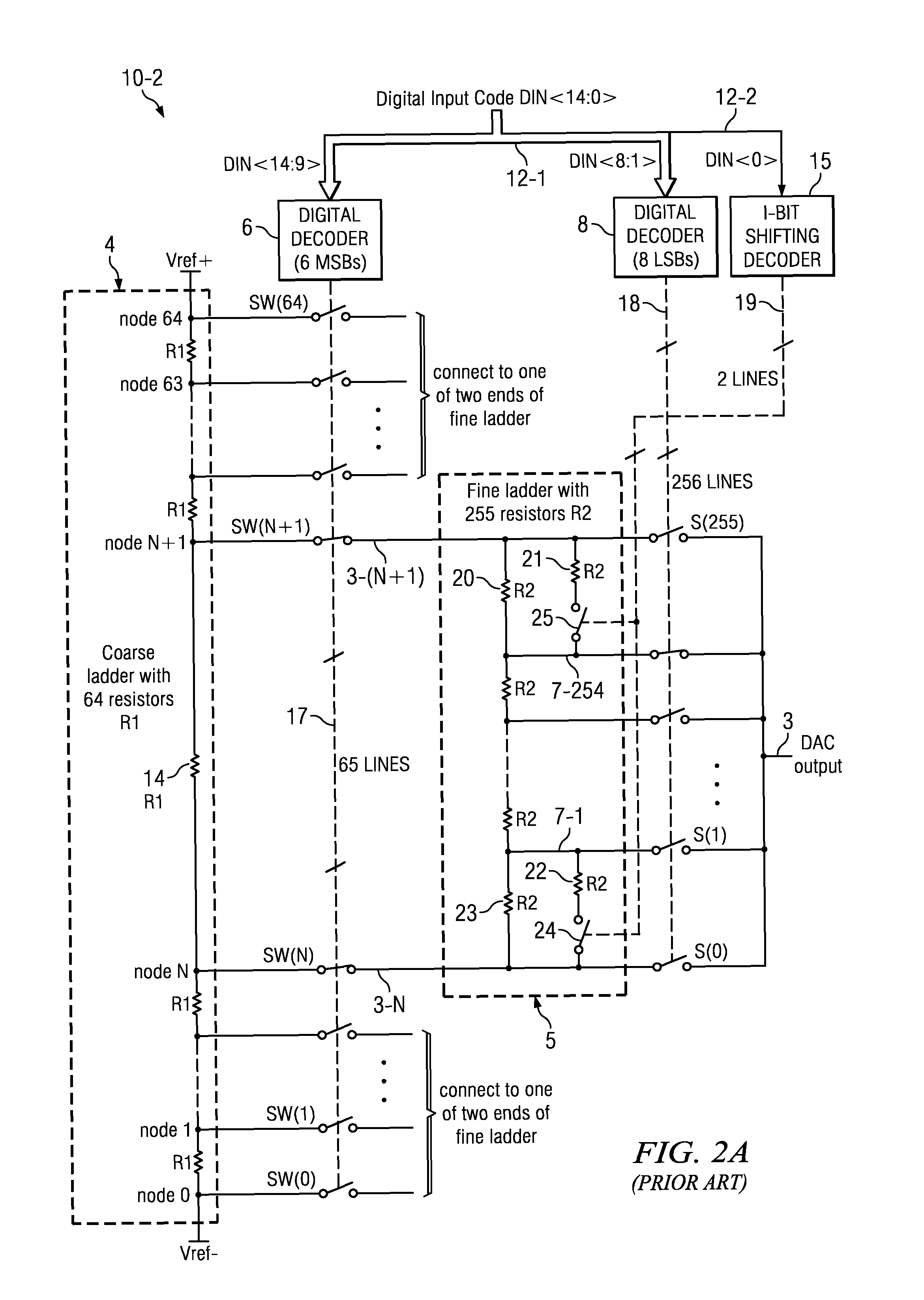

Signal level shift circuit and method for dual resistor ladder digital-to-analog converters

ActiveUS8618971B1Improve accuracyImprove resolutionElectric signal transmission systemsDigital-analogue convertorsElectrical conductorDigital analog converter

A dual resistor ladder DAC includes a coarse ladder including a plurality of coarse ladder resistors and a fine ladder including a plurality of MOS transistors coupled between first and second conductors. A first group of parallel-connected bit-shifting transistors is coupled between the first and third conductors. A second group of parallel-connected MOS bit-shifting transistors is coupled between the third and top conductors. A third group of parallel-connected bit-shifting transistors is coupled between bottom and fourth conductors. A fourth group of parallel-connected bit-shifting transistors is coupled between the second and fourth conductors. Parallel-connected bit-shifting transistors are turned either on or off in response to a plurality of bit-switching bits of a binary number to be converted. One of the bottom, first, second, third, and top conductors is coupled to a DAC output conductor in response to the plurality of bit-switching bits.

Owner:TEXAS INSTR INC

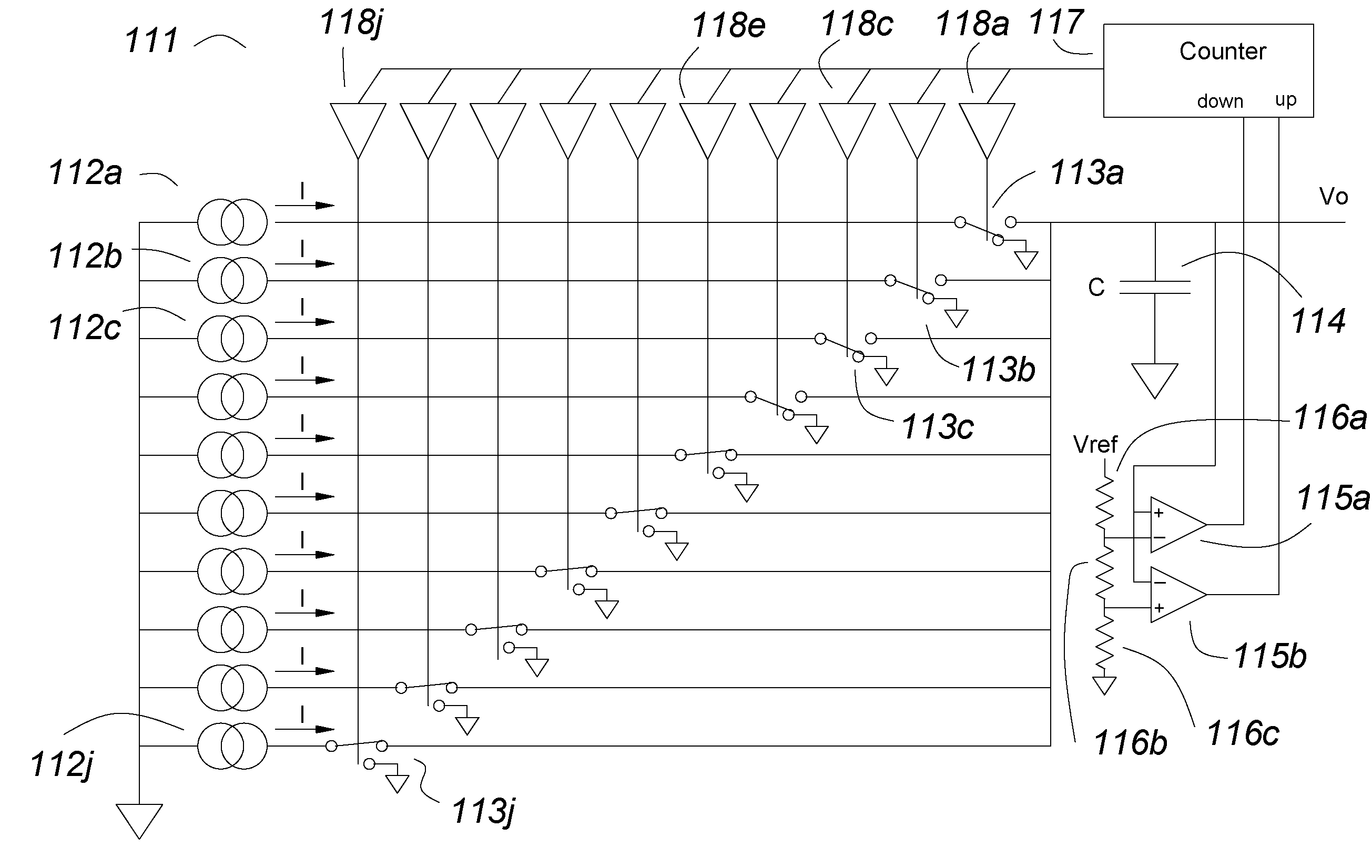

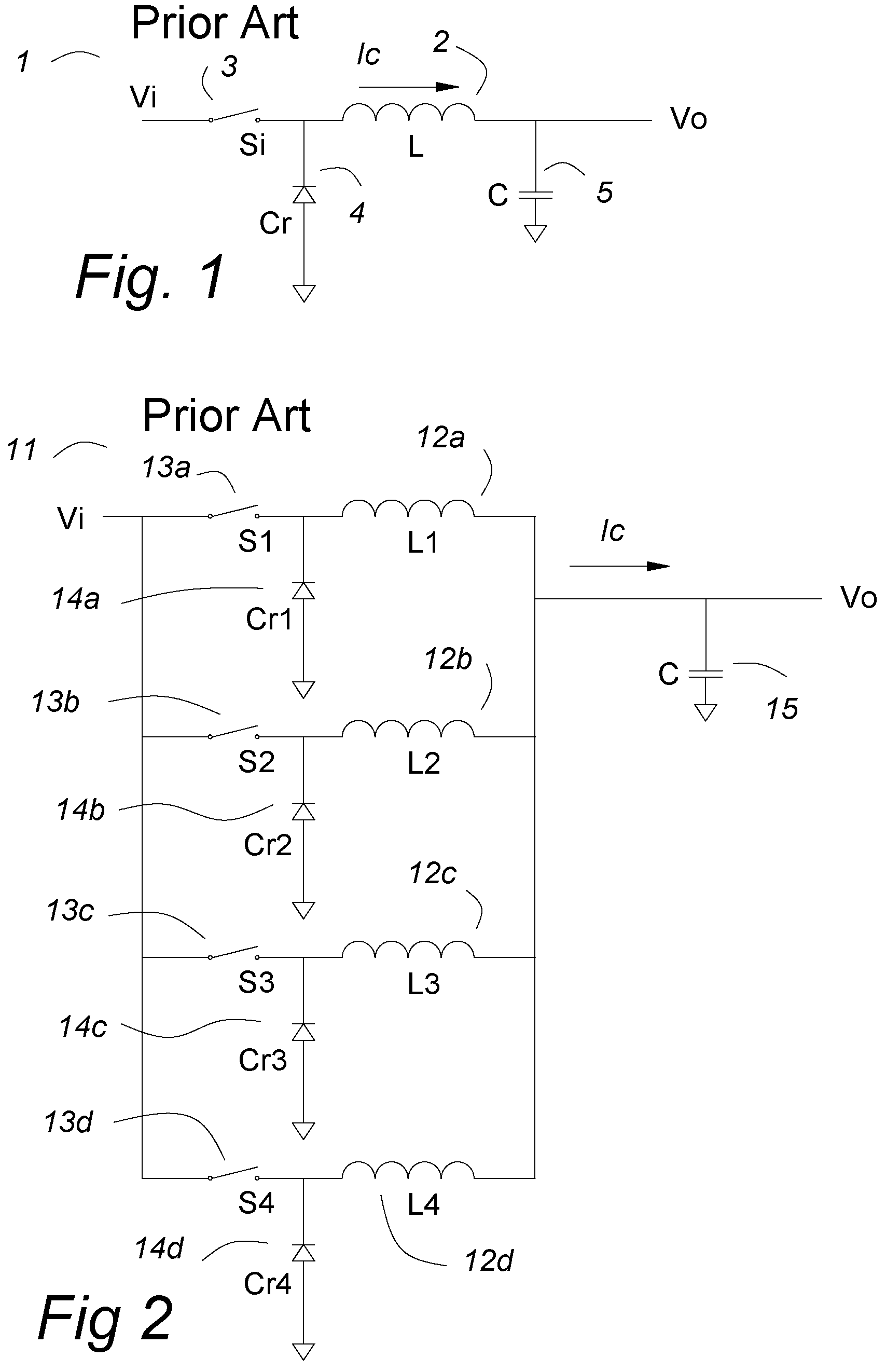

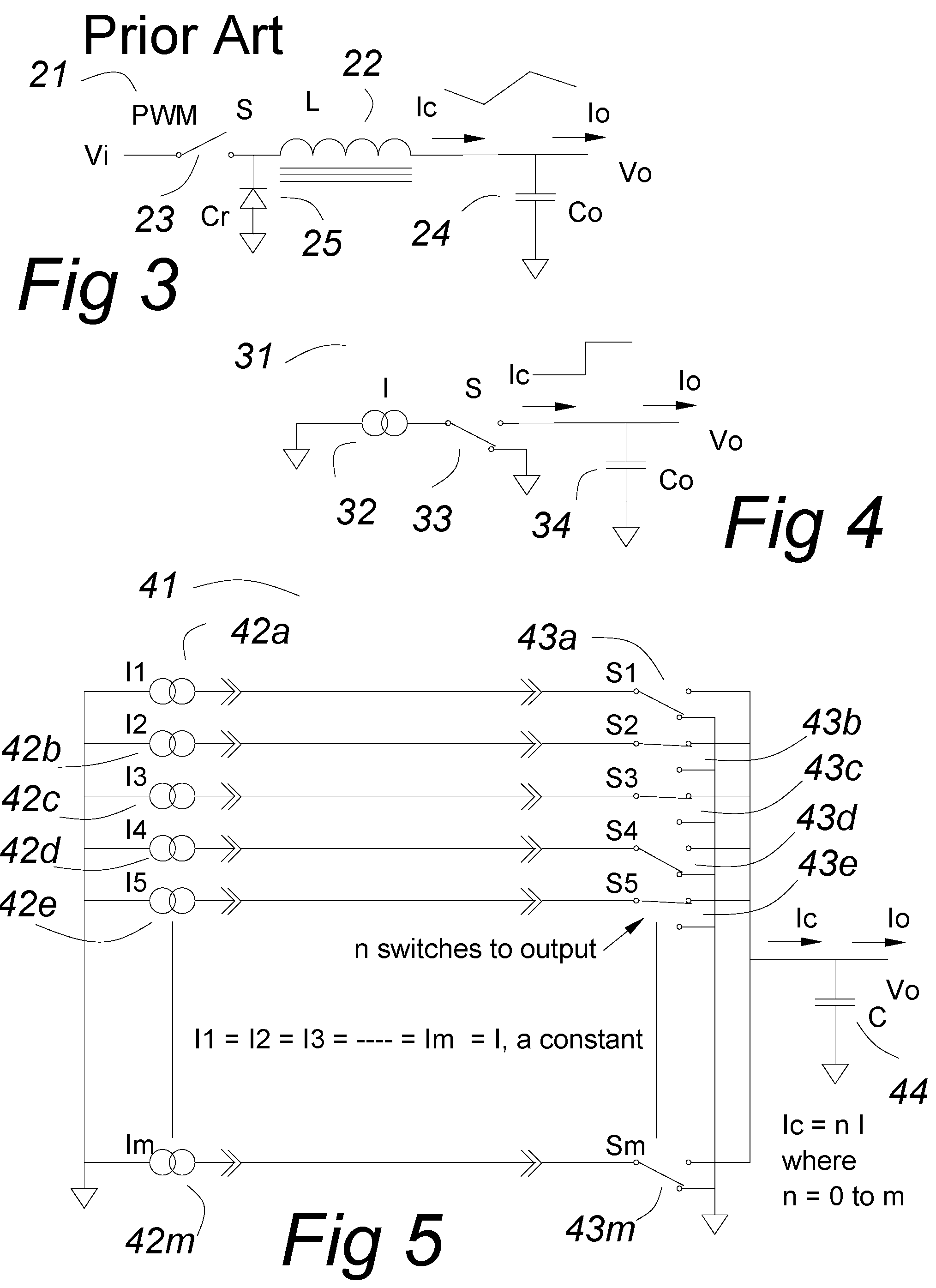

Switched-current power converter

InactiveUS6979982B2Minimizes change of energySolve the real problemDc-dc conversionElectric variable regulationElectrical resistance and conductanceSwitched current

In a switched-current power converter, a plurality of constant current sources provide equal currents to a plurality of switch pairs that may direct the several currents either to the return or to the output capacitors and the load. In another embodiment of the invention, internal switches may short circuit the several current sources and a plurality of switches may switch the several currents to the output capacitor and the load when the internal switches are not short circuits. A voltage control circuit is shown in which a resistor ladder network is the references for a number of comparators which directly control the plurality of switches. An alternative voltage control circuit uses two comparators and an up-down counter to control the switches.

Owner:HERBERT EDWARD

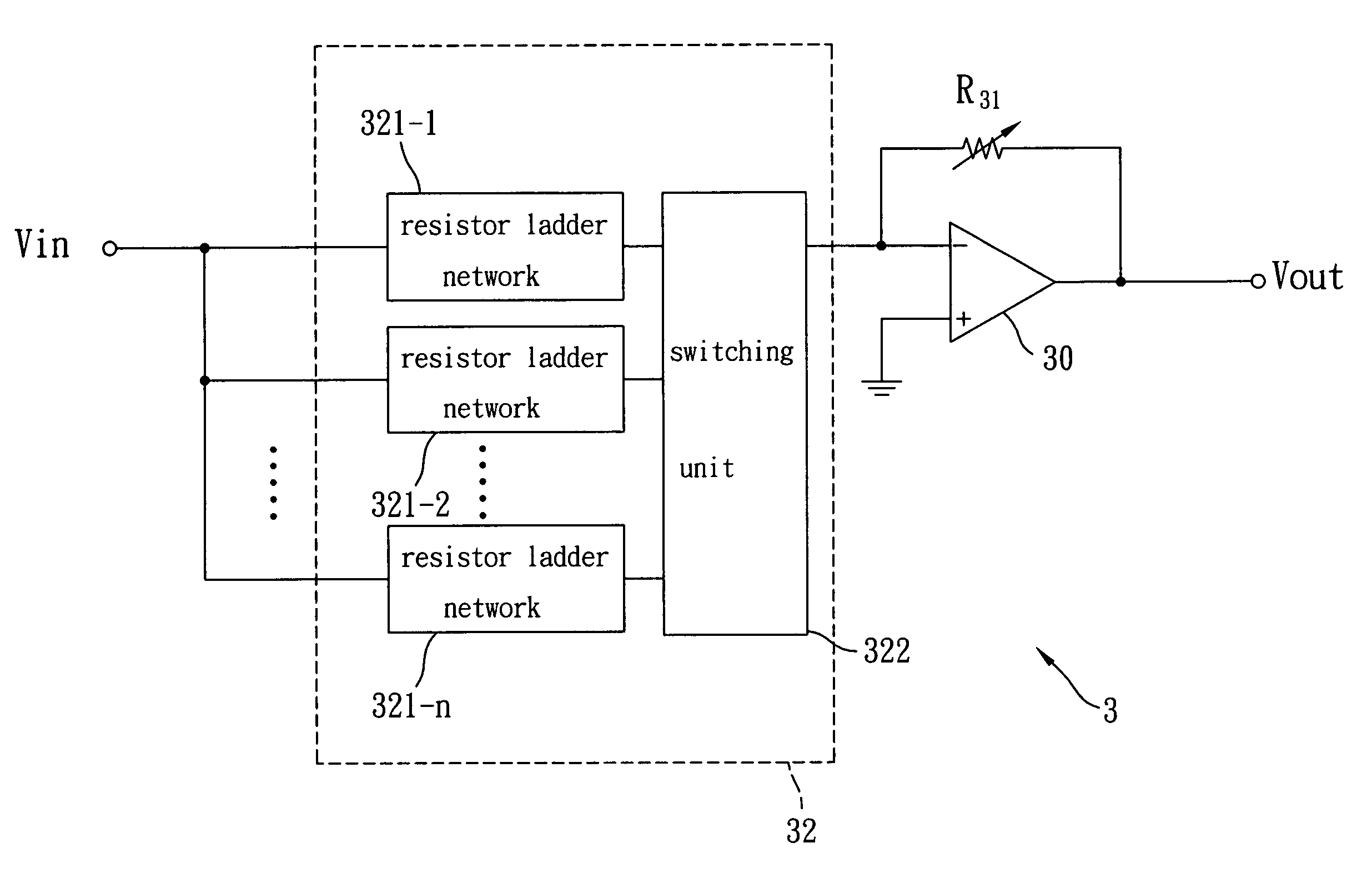

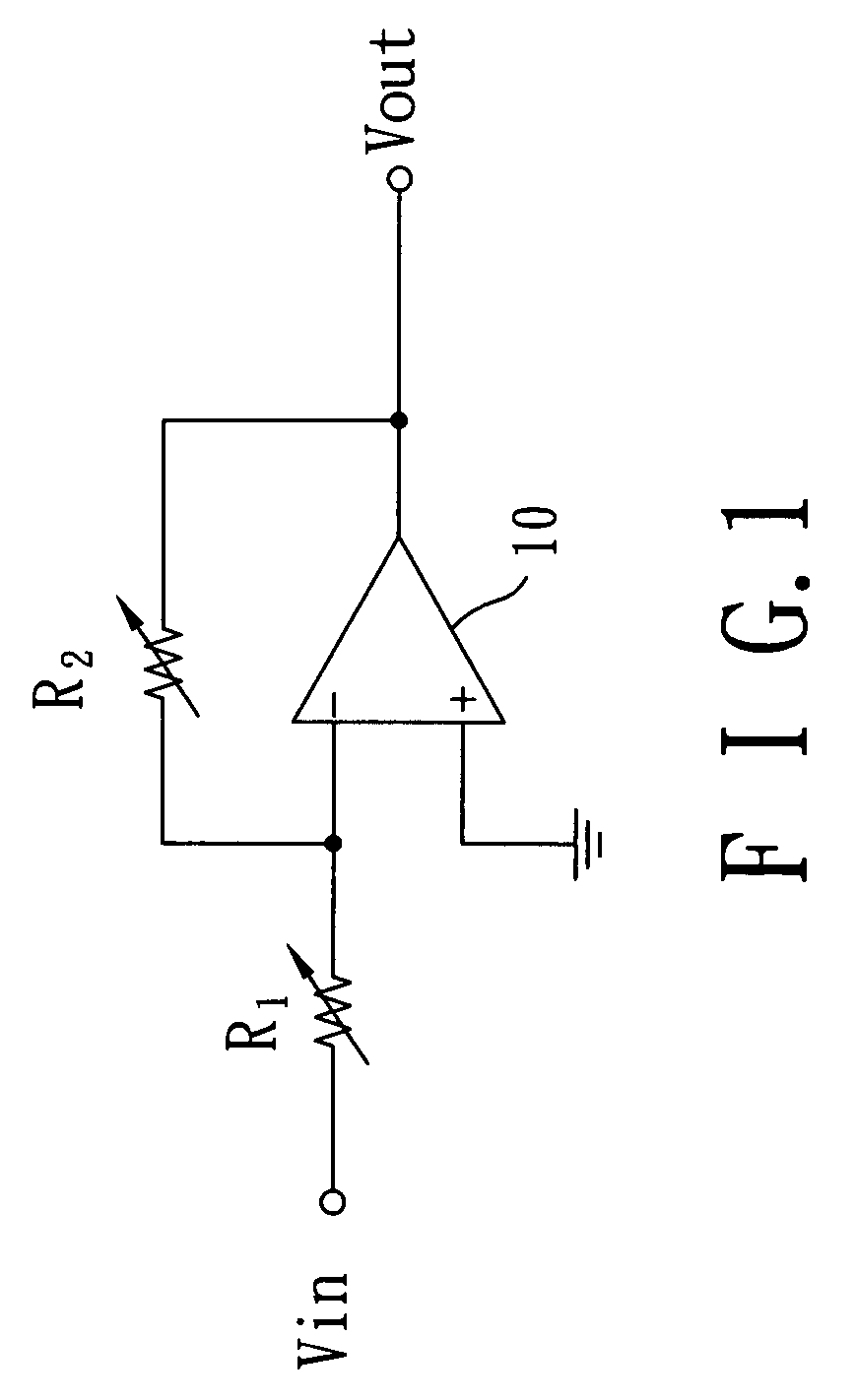

Variable gain amplifying circuit

A variable gain amplifying circuit, which applies a resistor ladder to obtain a more precise gain, is disclosed. The amplifying circuit includes an input, an operational amplifier (op-amp), a resistor unit and a feedback resistor. The feedback resistor is coupled between an output and an inverting input of the op-amp. The resistor unit includes at least one resistor ladder. The resistor unit further includes a switching unit for controlling whether the at least one resistor ladder is coupled between the input of the amplifying circuit and the inverting input of the op-amp. A differential amplifying circuit for more precise gain adjustment is also disclosed.

Owner:REALTEK SEMICON CORP

Conversion of a discrete-time quantized signal into a continuous-time, continuously variable signal

ActiveUS9276602B1Overcome limitationsLimit can be overcomeElectric signal transmission systemsParallel/series conversionMulti bandAnalog signal

Provided are, among other things, systems, apparatuses, methods and techniques for converting a discrete-time quantized signal into a continuous-time, continuously variable signal. An exemplary converter preferably includes: (1) multiple oversampling converters, each processing a different frequency band, operated in parallel; (2) multirate (i.e., polyphase) delta-sigma modulators (preferably second-order or higher); (3) multi-bit quantizers; (4) multi-bit-to-variable-level signal converters, such as resistor ladder networks or current source networks; (5) adaptive nonlinear, bit-mapping to compensate for mismatches in the multi-bit-to-variable-level signal converters (e.g., by mimicking such mismatches and then shifting the resulting noise to a frequently range where it will be filtered out by a corresponding bandpass (reconstruction) filter); (6) multi-band (e.g., programmable noise-transfer-function response) bandpass delta-sigma modulators; and / or (7) a digital pre-distortion linearizer (DPL) for canceling noise and distortion introduced by an analog signal bandpass (reconstruction) filter bank.

Owner:PAGNANELLI FAMILY TRUST

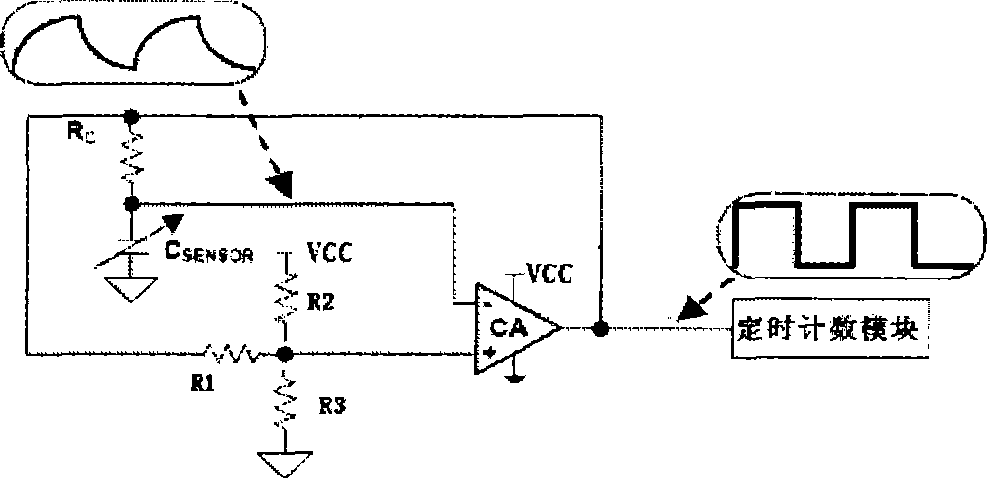

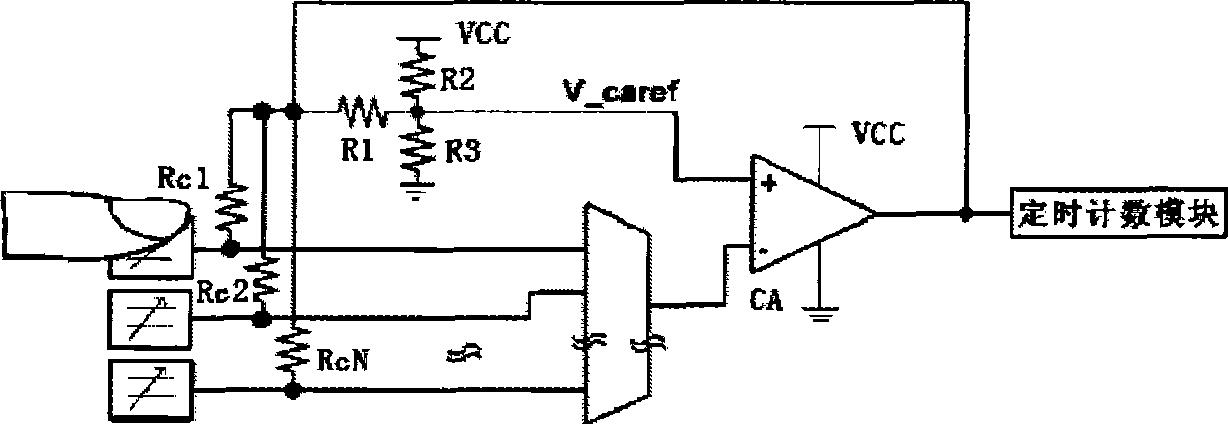

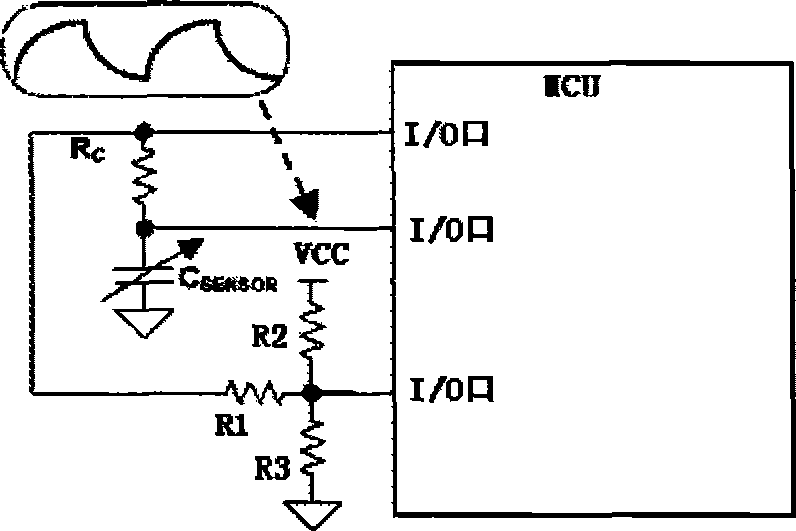

Capacitor induction type touch press-key and measuring method for touch press-key capacitor

InactiveCN101499794AImprove dust resistanceLow costResistance/reactance/impedenceElectronic switchingCapacitanceLight touch

The invention relates to a capacitive sensitive type touch key based on MCU and a measuring method for the capacitance of the touch key. The touch keys are distributed on a PCB printed circuit and are respectively connected with a negative signal input end of a comparator and one end of a resistor RC; the other end of the RC is respectively connected with an output end of the comparator, a signal end of a timing counting module and one end of a R1 in a resistor ladder network; and the other end of the R1 is connected with a positive signal input end of the comparator. The invention has the advantages that (1) the capacitance touch sensitive technology is adopted to design the touch keys, the cost is low and the special sensor is not needed; (2) the power consumption is lower; (3) the sensitive type light touch can realize the output of the signals; (4) the realizing mode can be diverse and can realize positioning of precision; (5) the touch key can replace various mechanical keys, switches and proximity detectors; (6) the structure is simple and the wear resistance is good; and (7) as the traditional key is not used, the touch sensitive key can adopt a whole seamless panel, the dust prevention effect is excellent and the reliability of the product is improved.

Owner:LIERDA SCI & TECH GRP

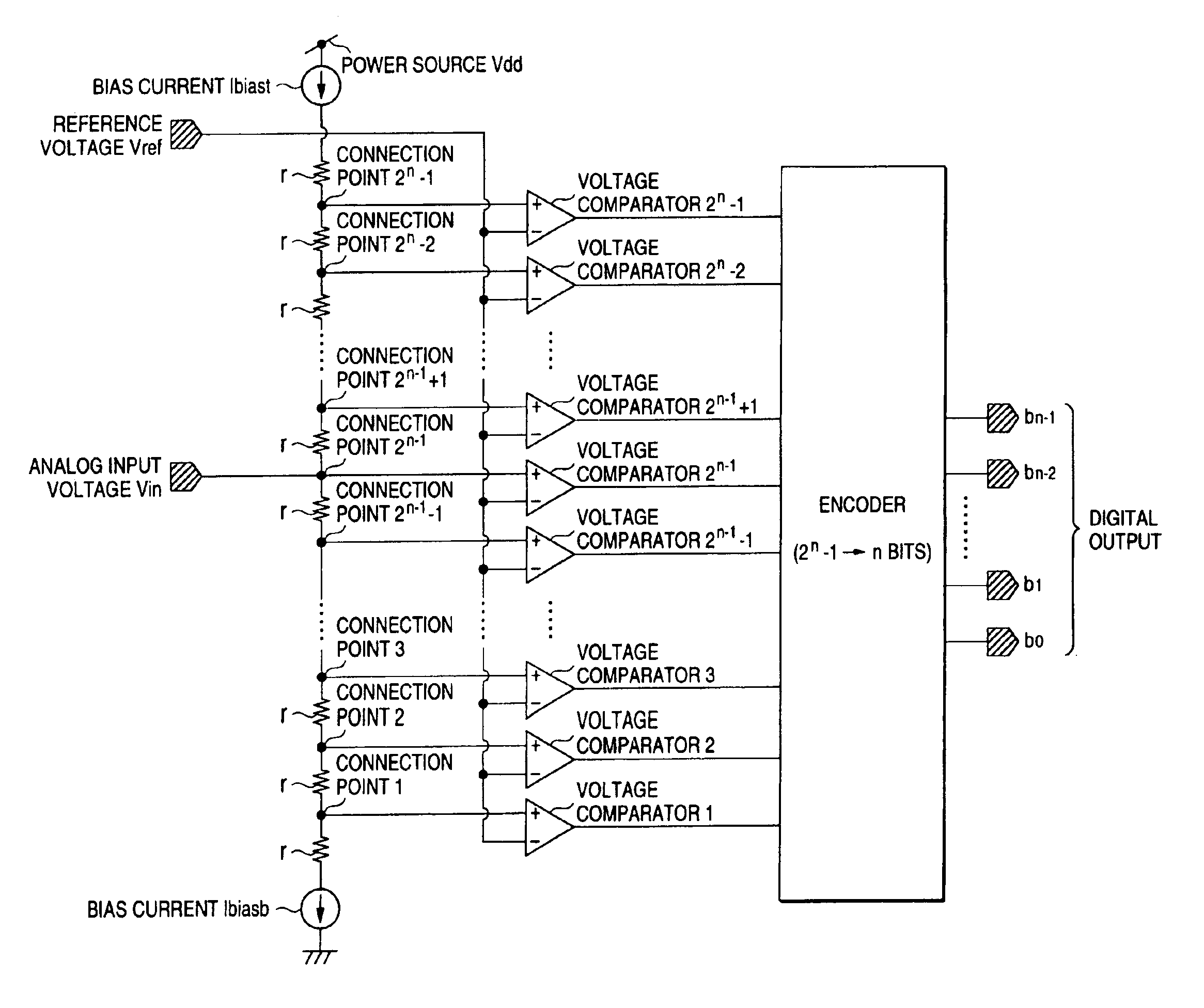

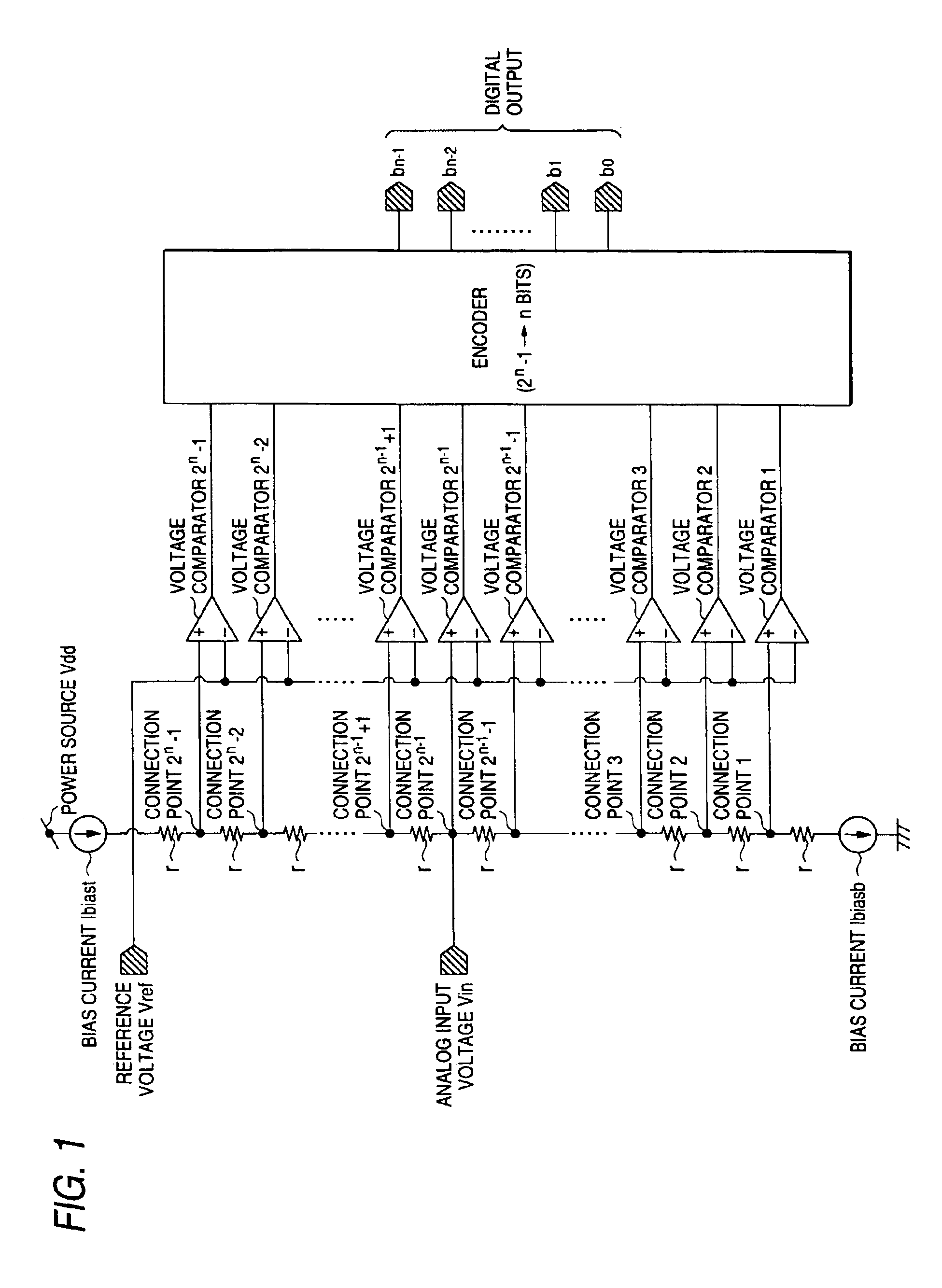

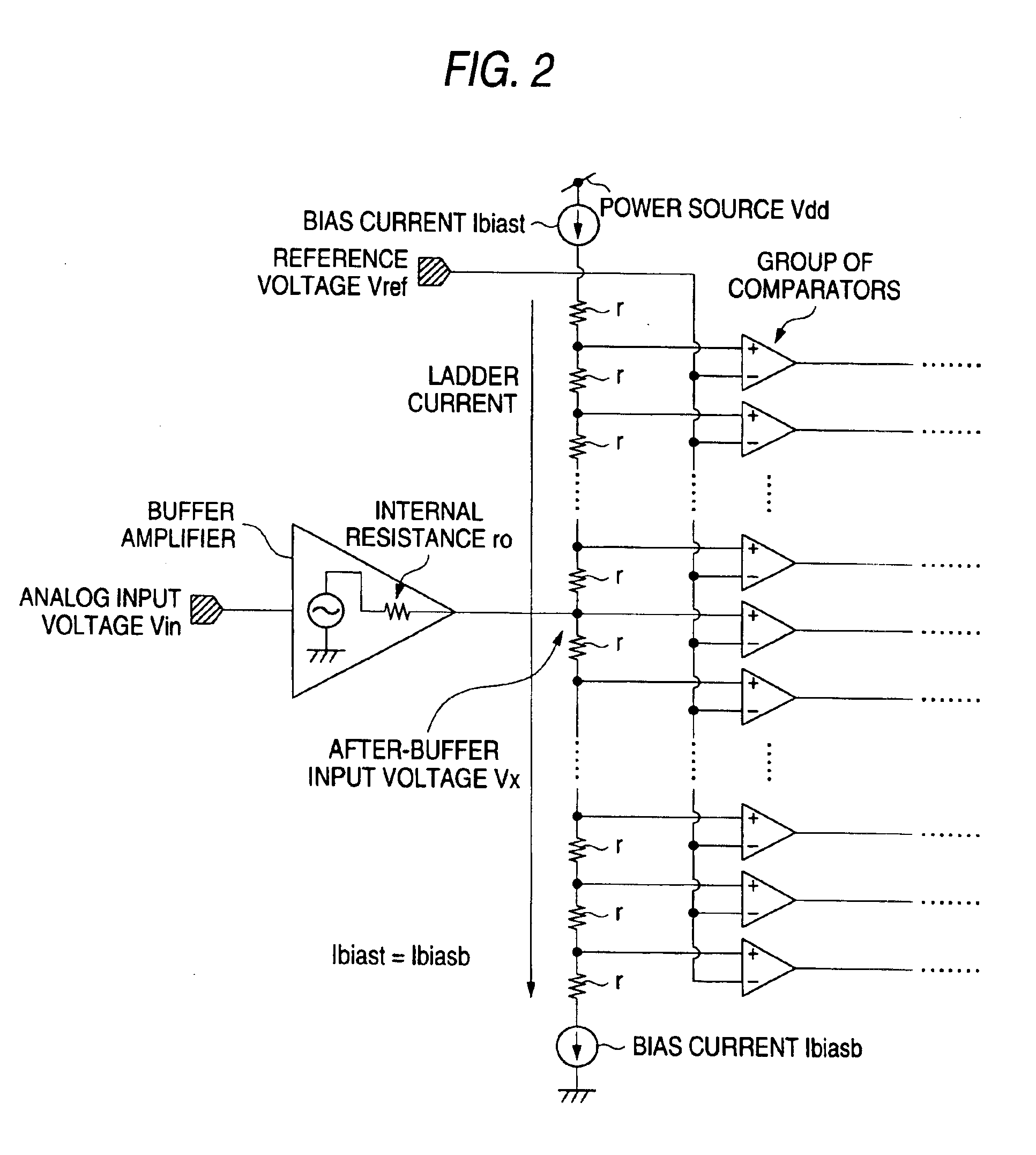

Analog to digital converter with voltage comparators that compare a reference voltage with voltages at connection points on a resistor ladder

InactiveUS6963298B2Consumes less electric powerSmall circuit scaleElectric signal transmission systemsAnalogue-digital convertersElectrical resistance and conductanceEngineering

An AD converter which uses no buffer for receiving the input signals or uses the buffer having relaxed requirements concerning the range of input signals and the output impedance. Voltage at the connection points of a resistor ladder in which a plurality of resistor elements are connected in series, are compared with a reference voltage by a plurality of voltage comparators, a first current circuit is provided on the high potential side of the resistor ladder, a second current circuit is provided on the low potential side thereof, and analog input voltages are fed by providing an input terminal at any place of the resistor ladder except both ends thereof.

Owner:RENESAS ELECTRONICS CORP