Non-volatile memory circuit and semiconductor device

A non-volatile storage and circuit technology, which is applied in the manufacture of semiconductor devices, circuits, semiconductor/solid-state devices, etc., can solve the problems of increased circuit size, increased chip size, and increased manufacturing costs, and achieve reduced manufacturing costs. The effect of solving cost and inventory problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

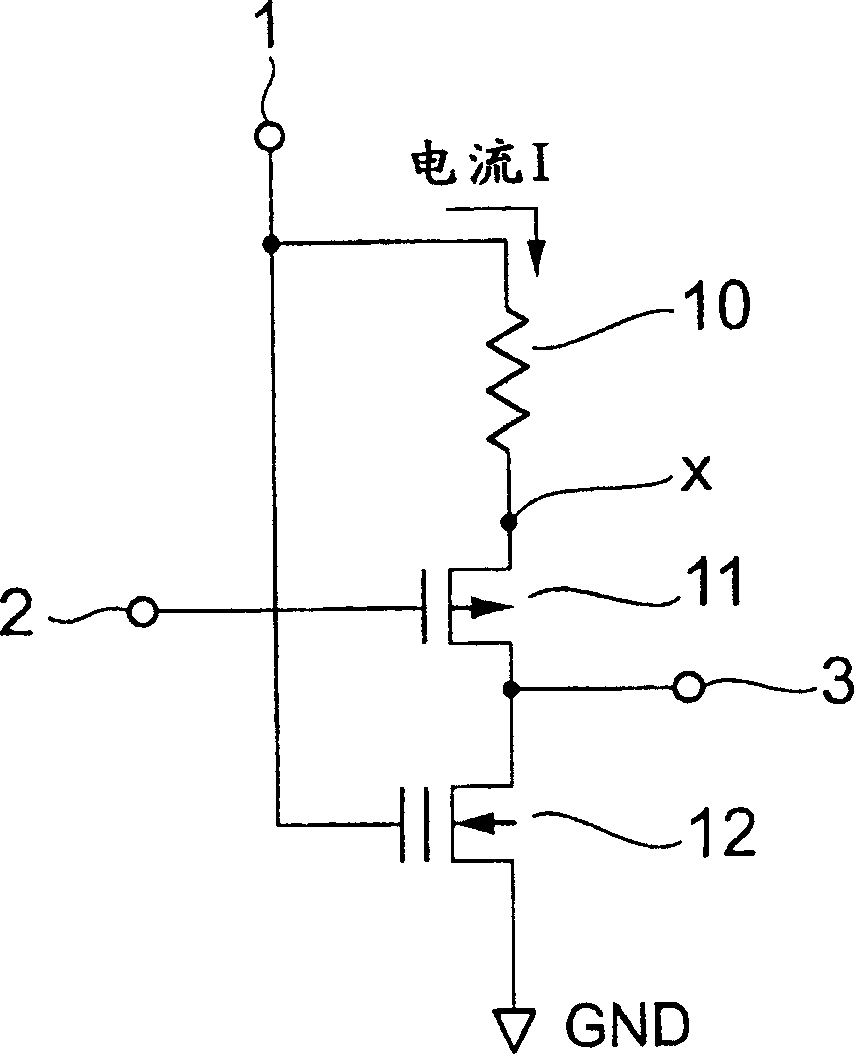

[0024] figure 1 The EPROM read / write circuit according to the present invention is shown. The resistor 10, the PMOS transistor 11, and the EPROM 12 are connected in series with each other between the power supply voltage terminal 1 and the GND terminal. The gate of the PMOS transistor 11 is connected to the write control terminal 2 and the gate of the EPROM 12 is connected to the power supply voltage terminal 1.

[0025] In order to perform writing to the EPROM 12, an optimum voltage difference for writing is required between the gate terminal and the drain terminal of the EPROM 12. Therefore, the voltage Vw that is most suitable for writing in terms of EPROM 12 characteristics is applied to the power supply voltage terminal 1.

[0026] In addition, when the PMOS transistor 11 is in an on state, a current I [A] flows between the source and drain of the EPROM. The resistor 10 sets an optimal voltage value at which the current is injected into the floating gate of the EPROM 12. Wh...

Embodiment 2

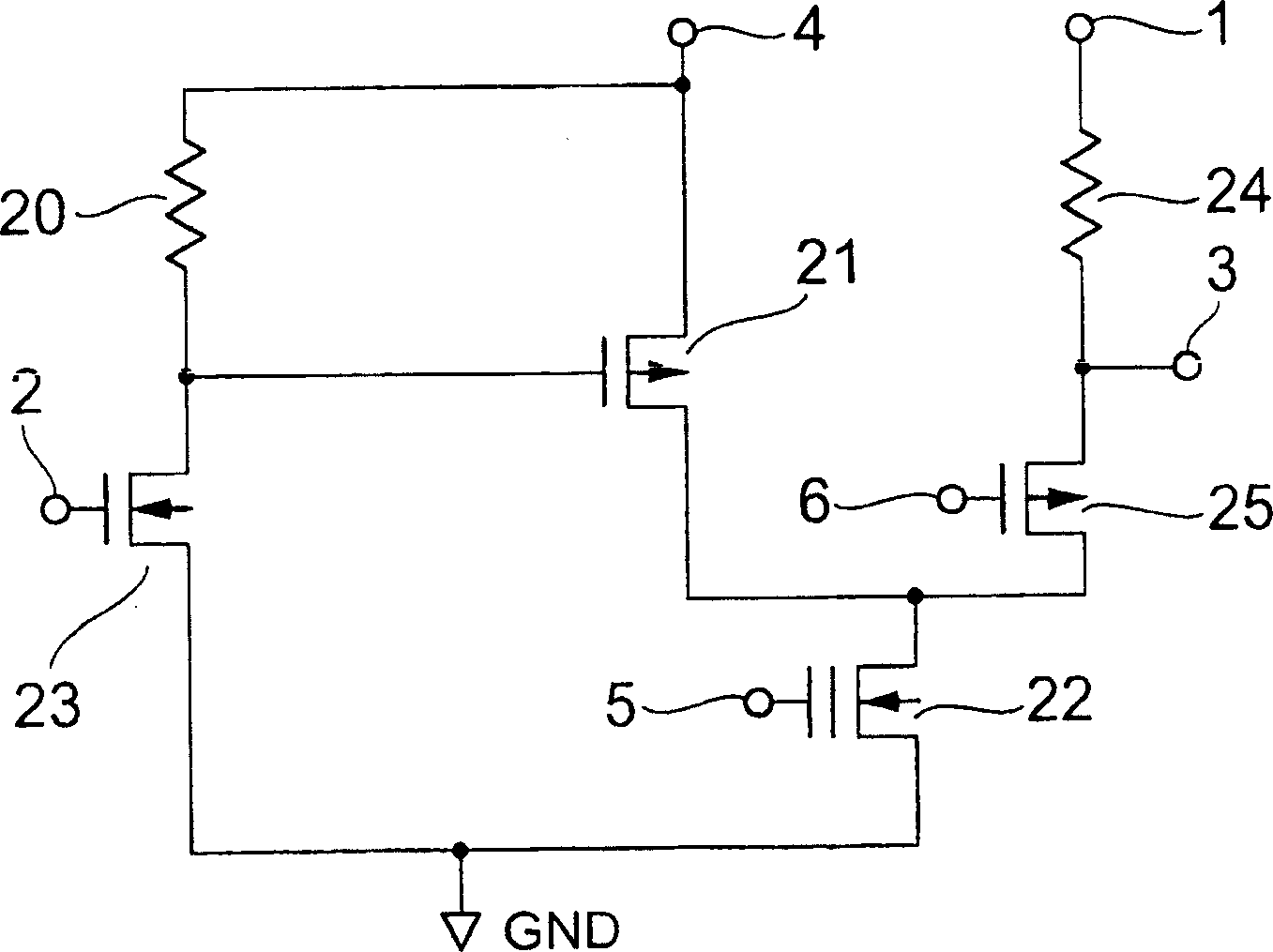

[0035] Figure 5 It is a circuit diagram of the EPROM read / write circuit of the present invention for the trimming circuit. Figure 5 The trimming circuit in is composed of a storage circuit 50 and a voltage divider resistor network 51. The voltage dividing resistor network 51 is composed of resistors and MOS switches connected to both ends of these resistors. The storage circuit 50 includes figure 1 The number of EPROM read / write circuits shown corresponds to the number of resistors constituting the voltage divider resistor network 51. The gate terminal of each MOS switch is connected to figure 1 The EPROM read / write circuit in the output voltage terminal 3 is connected. The voltage Vr is applied to the power supply voltage terminal, and the potential of Vr is the same as when the EPROM is read.

[0036] The data output of the storage circuit corresponding to the storage state of the EPROM is supplied to the gate of each MOS switch, thereby performing on / off control of the MOS ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More