Semiconductor package and semiconductor device

a semiconductor and semiconductor technology, applied in the field of semiconductor devices, can solve the problems of high mold cost and dramatic increase in production cost, and achieve the effect of reducing production cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

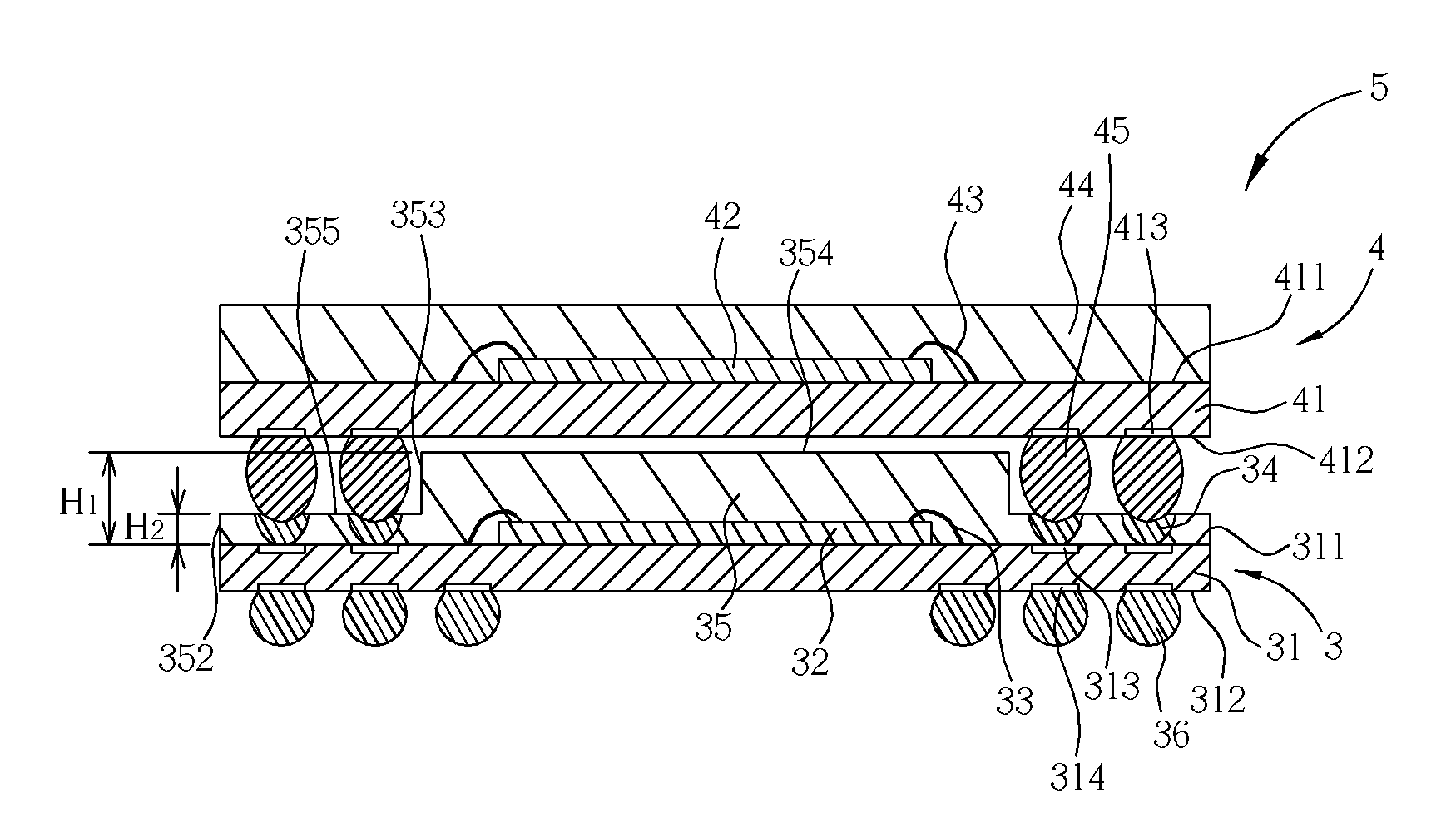

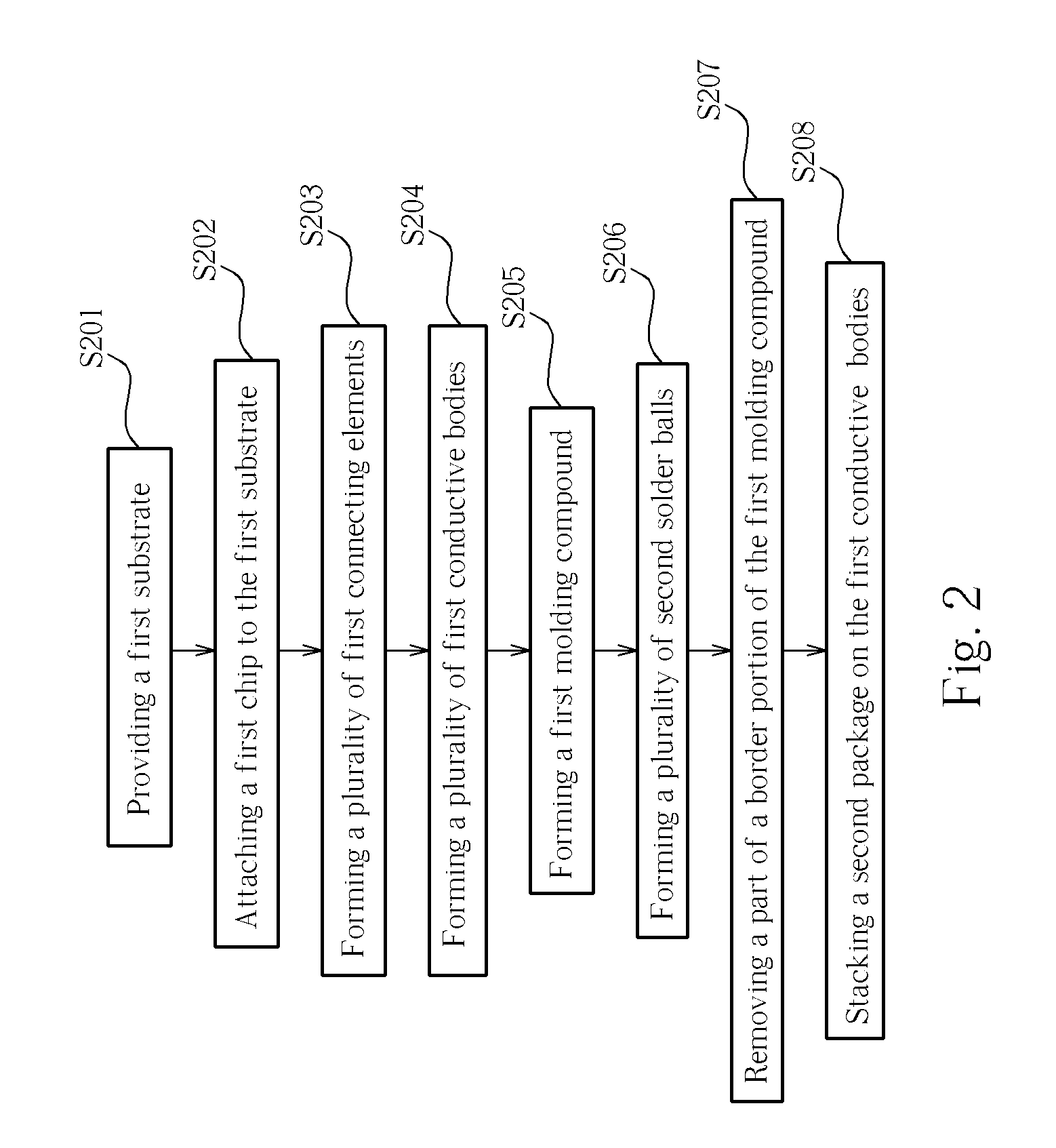

[0015]Please refer to FIG. 2 showing a flow chart of the method of making a semiconductor device according to the present invention. Also refer to FIG. 3. In Step S201, a first substrate 31 is provided. The first substrate 31 has a first surface 311, a second surface 312, a plurality of first pads 313, and a plurality of second pads 314. The first pads 313 are on the first surface 311, and the second pads 314 are on the second surface 312. In Step S202, a first chip 32 is attached to the first surface 311 of the first substrate 31. In this embodiment, a first chip 32 is attached to the first surface 311 of the first substrate 31. In Step S203, a plurality of first connecting elements (such as a plurality of first conductive wires 33) electrically connect the first chip 32 and the first surface 311 of the first substrate 31. In Step 204, a plurality of first conductive bodies (such as a plurality of first solder balls 34) are formed on the first pads 313 on the first surface 311 of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More