Patents

Literature

30results about How to "Lower interconnect resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

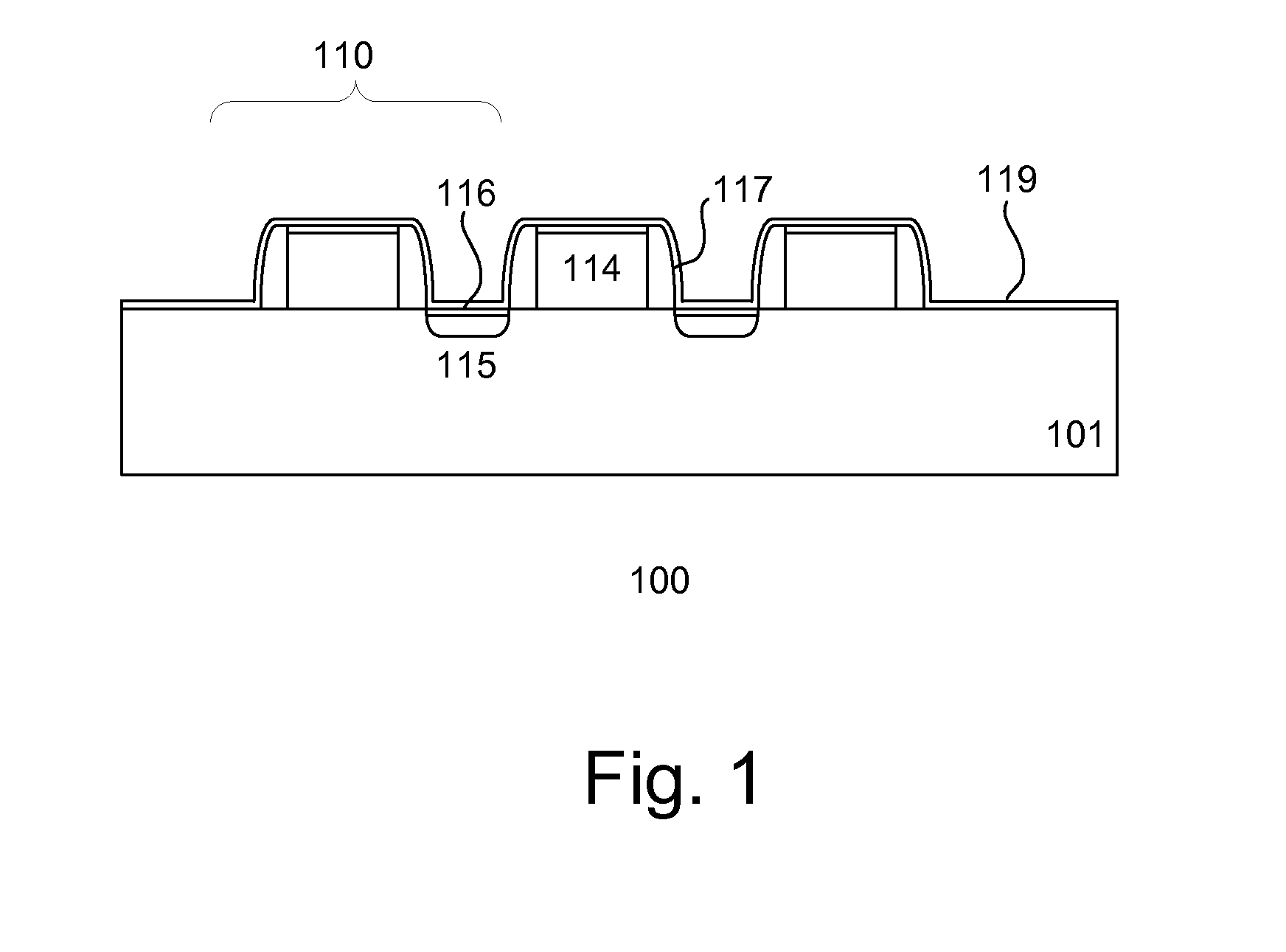

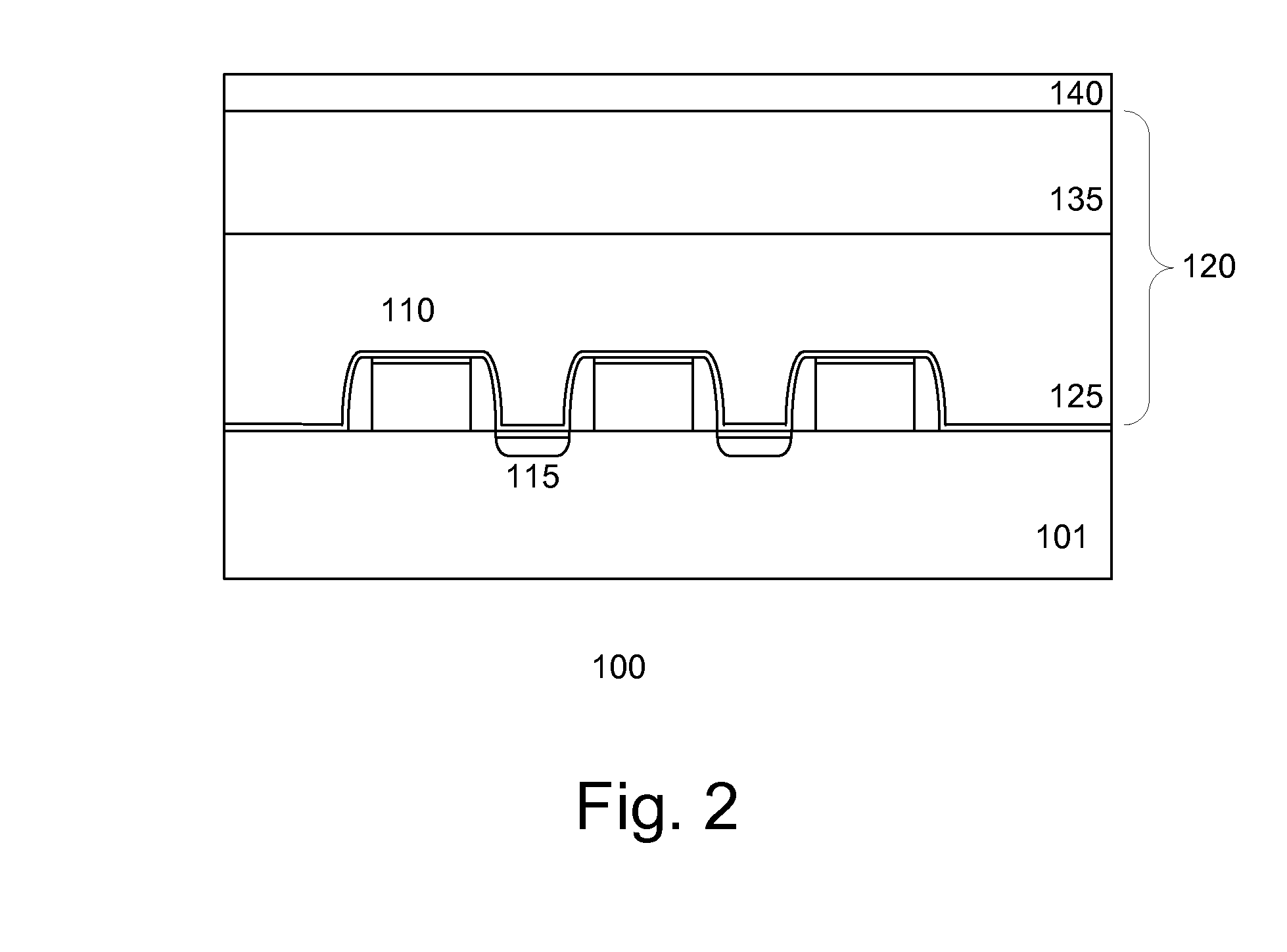

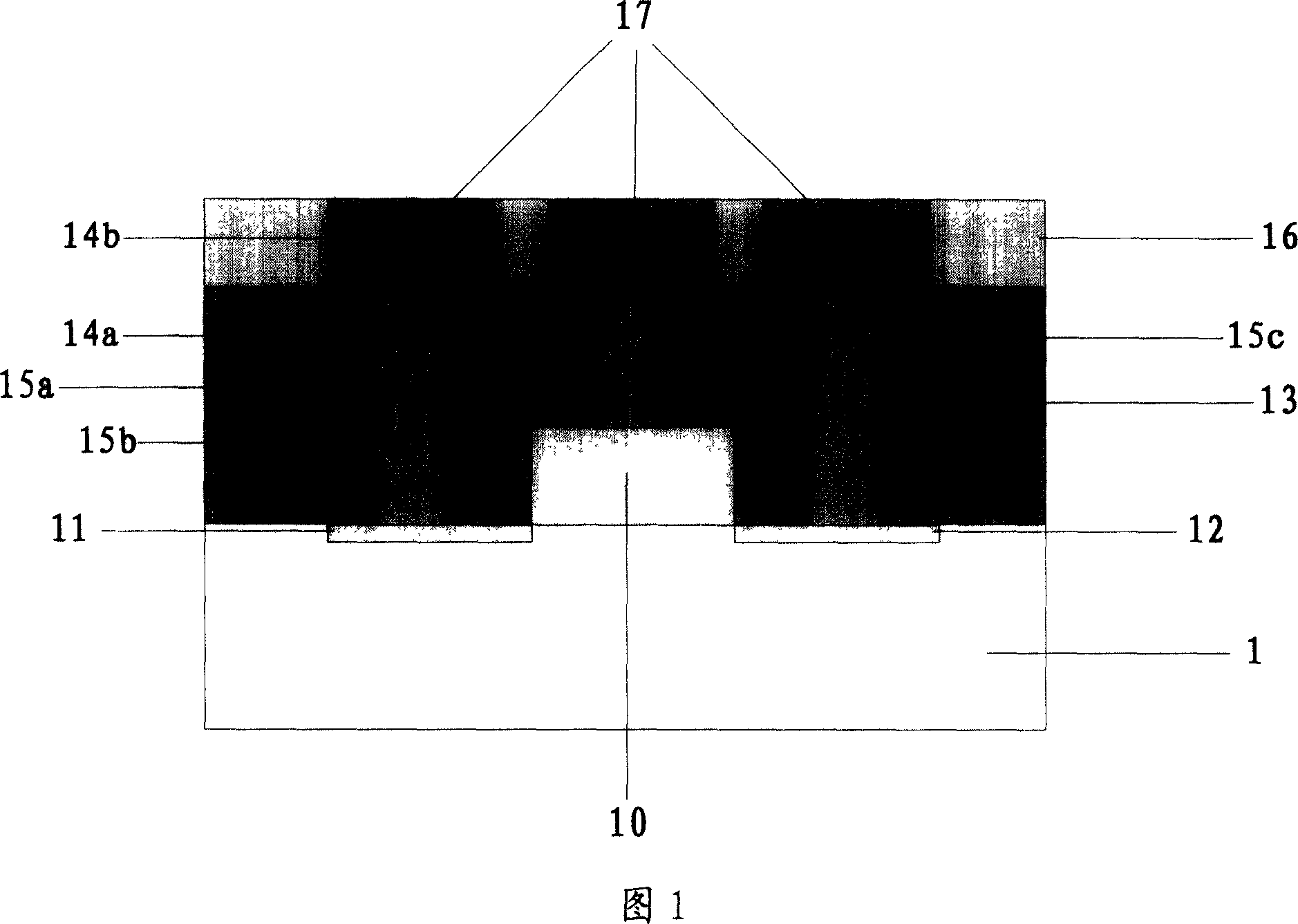

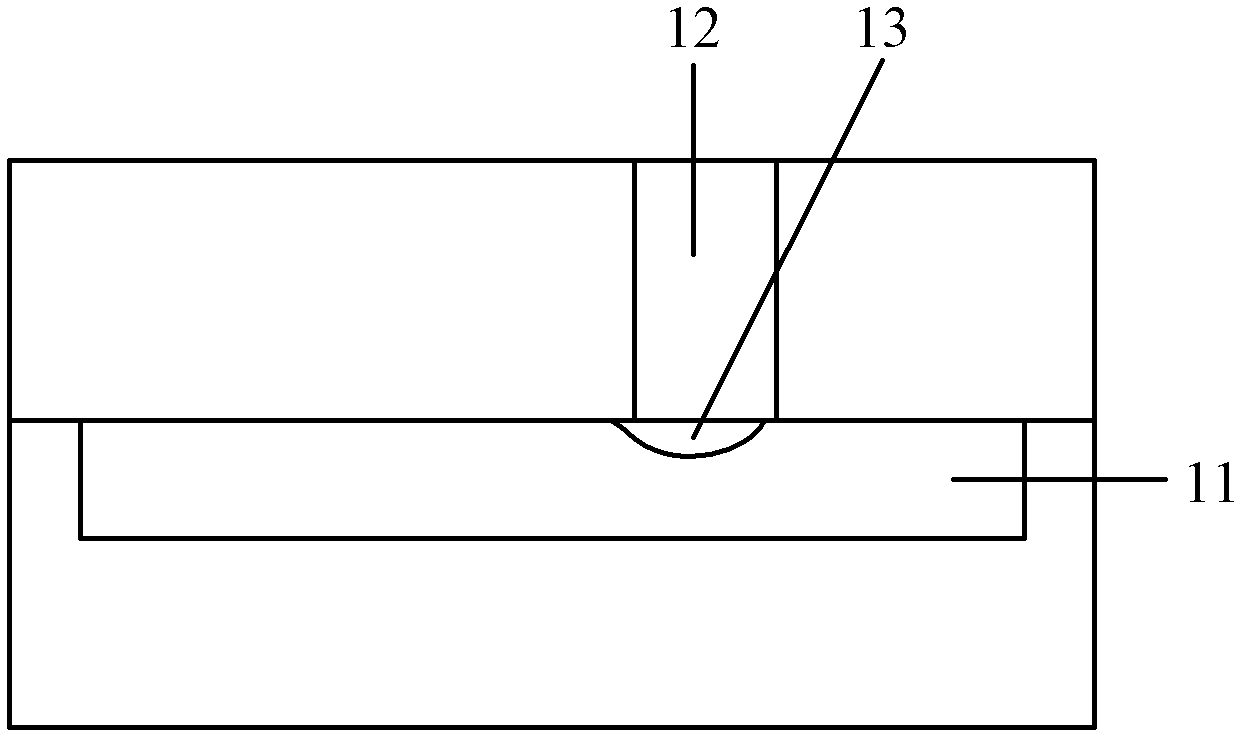

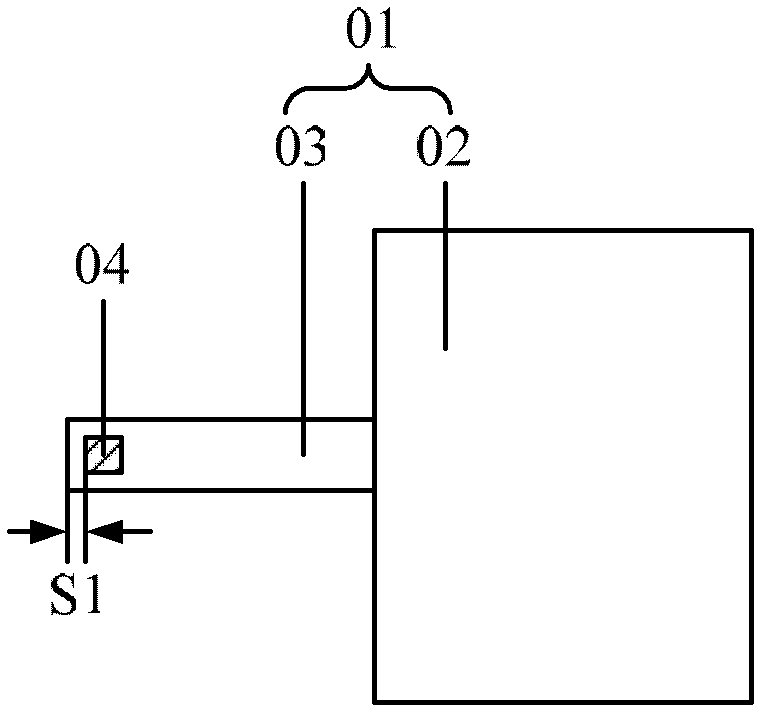

Semiconductor device and method of manufacturing thereof

InactiveUS20100001409A1Increase the cross-sectional areaLower interconnect resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

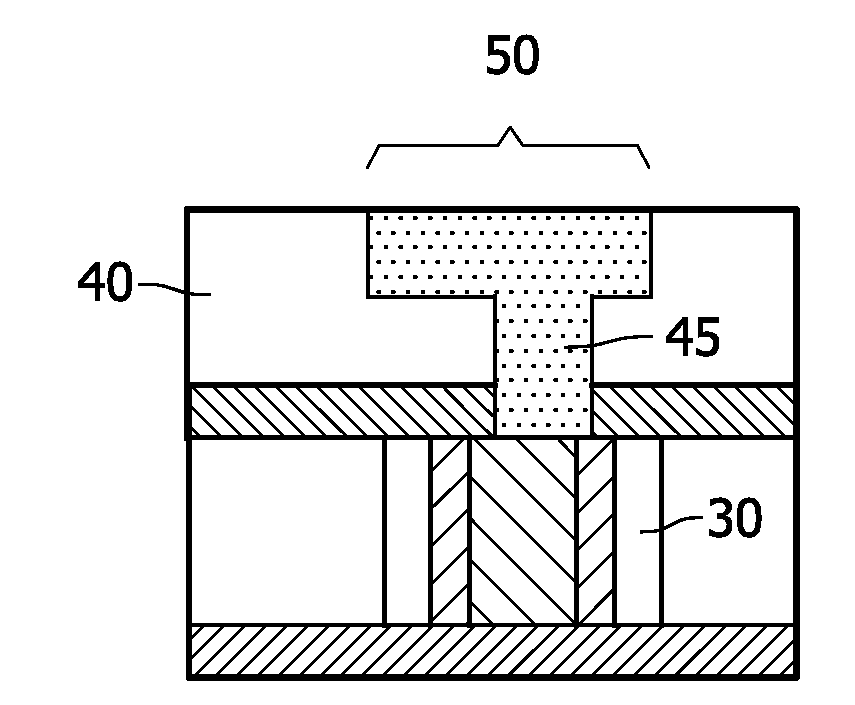

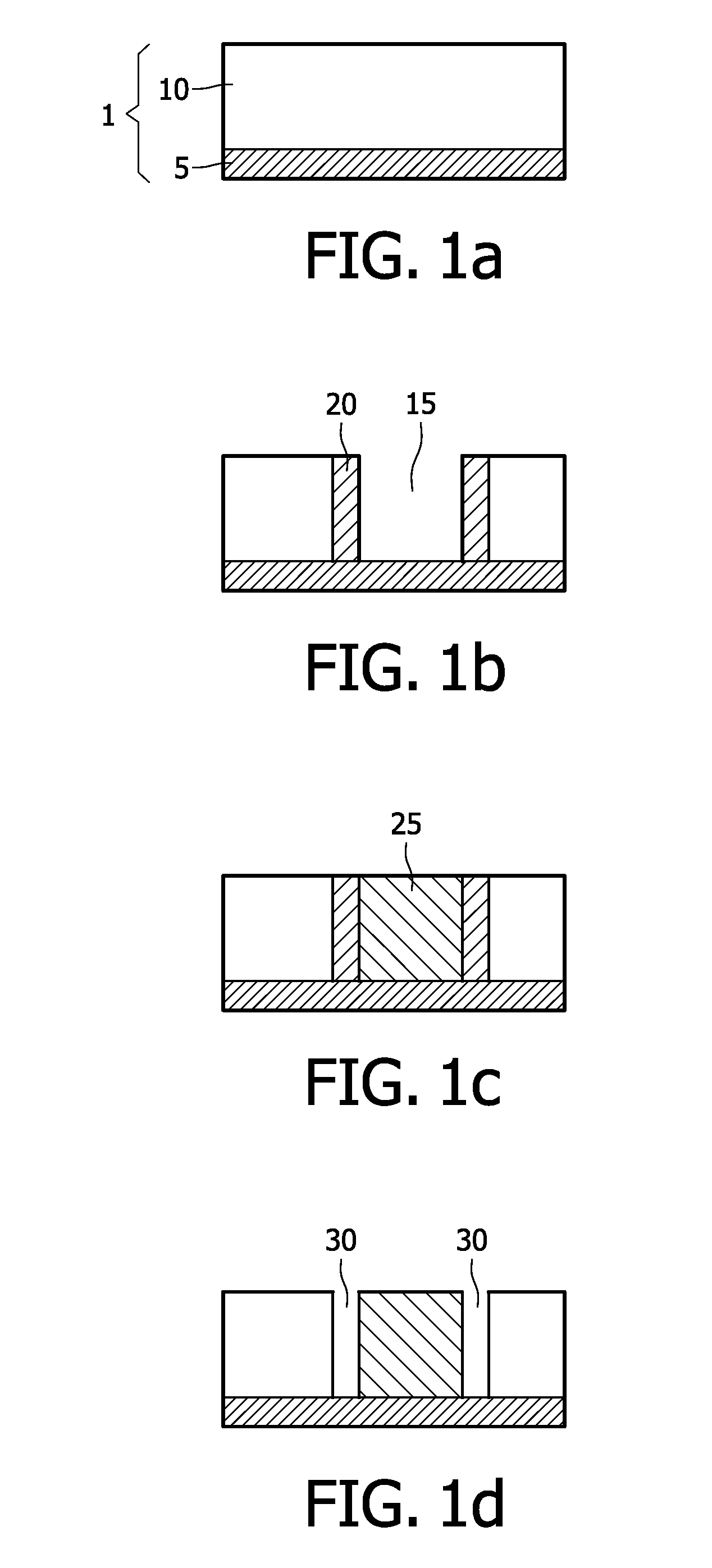

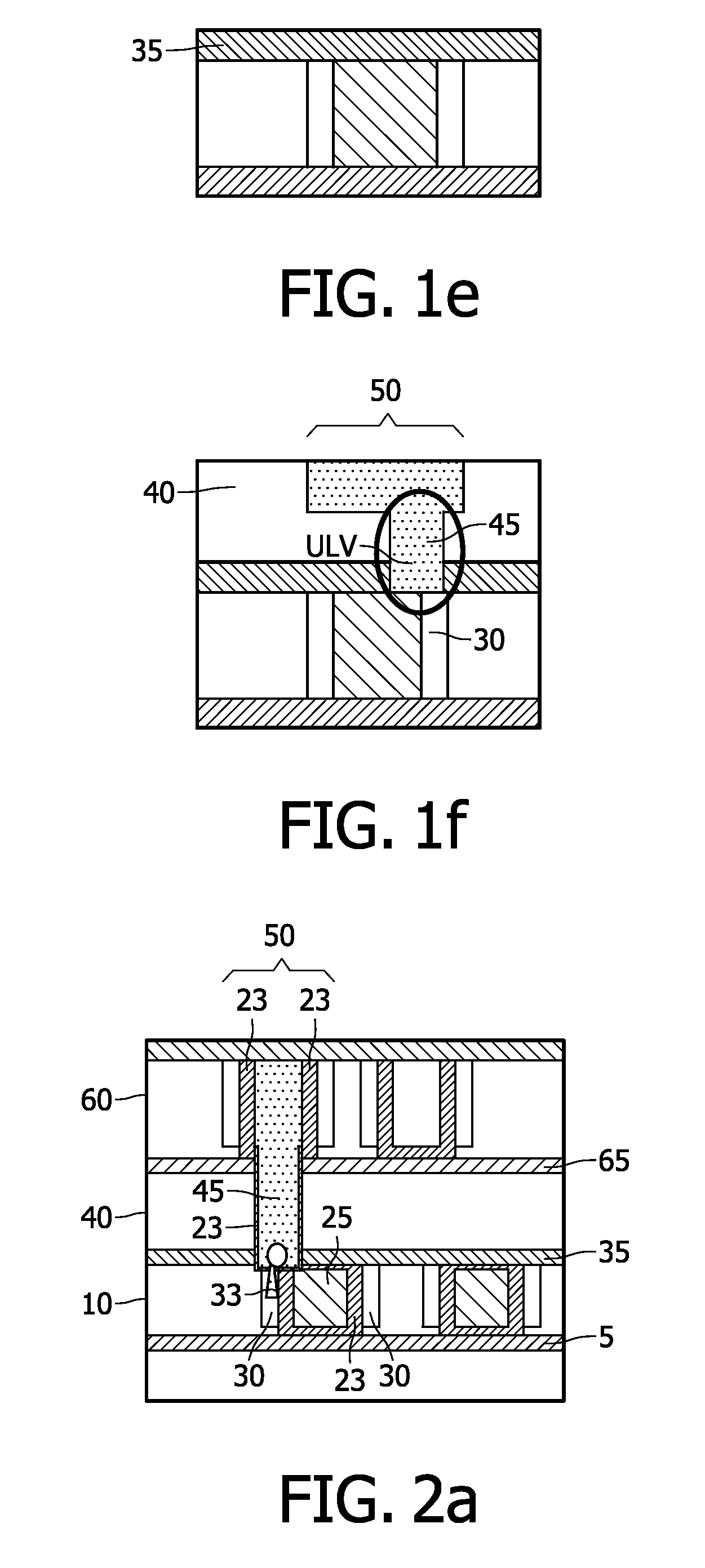

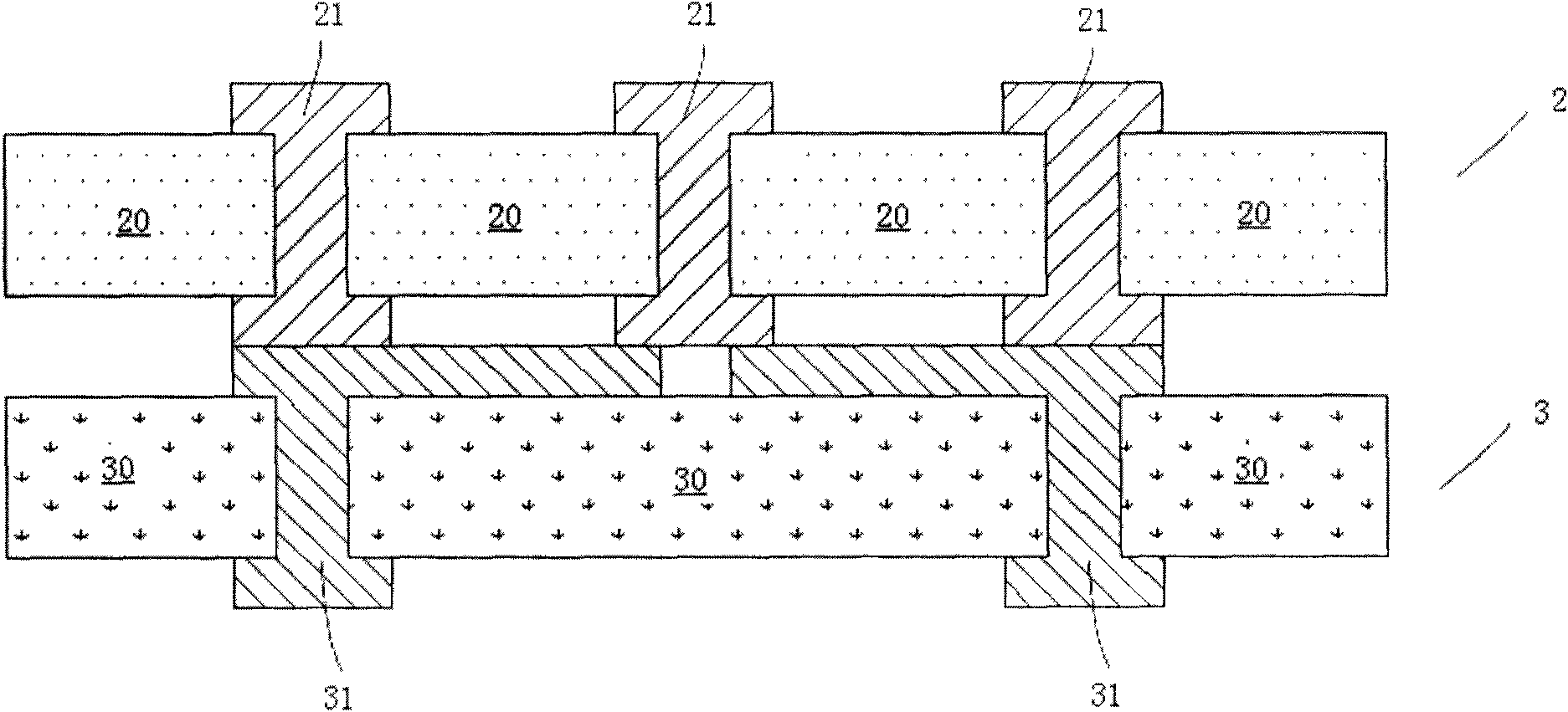

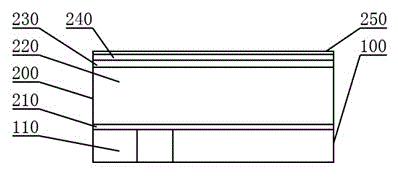

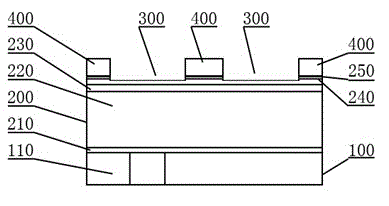

The invention relates to a semiconductor device comprising: a substrate (1), the substrate (1) comprising a body (5), the body (5) having a surface, the substrate (1) being provided with an insulating layer (10) on the surface of the body (1);—a conductor (25) with insulating sidewall spacers (22) located in the insulating layer (10), the conductor (25) having a current-flow direction during operation, the conductor (25) having a first width, the insulating sidewall spacers (22) each having a second width being smaller than the first width of the conductor (25), the first width and the second width being measured in a direction perpendicular to the current-flow direction of the conductor (25) and parallel to said surface, the conductor (25) having a first top surface extending parallel to said surface, the insulating sidewall spacers (22) having a second top surface, and airgaps (30) located in the insulating layer (10) adjacent to the insulating sidewall spacers (22), characterized in that the first top surface coincides with the second top surface, and in that the airgaps (30) extend from the surface of the body (5) to said first and second top surface. The invention further relates to a method of manufacturing such a semiconductor device. The semiconductor device according to the invention enables a lower resistance of the conductor while still providing a tolerance for unlanded vias.

Owner:NXP BV

Damascene Contact Structure for Integrated Circuits

ActiveUS20080076244A1Lower interconnect resistanceImprove barrier propertySemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingPhysicsEtching selectivity

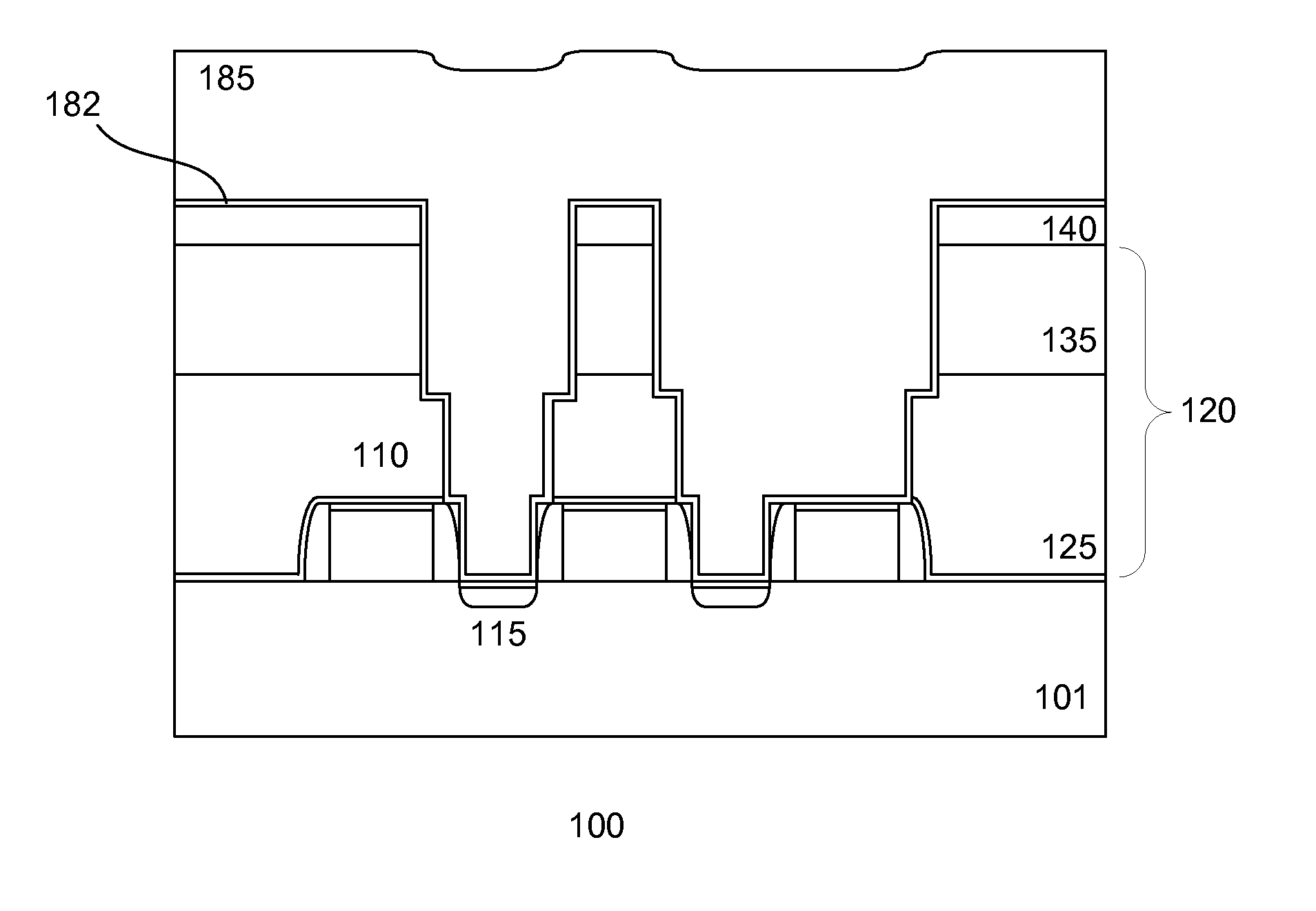

Interconnects for integrated circuits, such as damascene structures are formed using a hard mask. The hard mask is formed from, for example, high-k dielectric material such as hafnium oxide or other materials having high etch selectivity to the interconnect dielectric material. This enables a thin mask to etch vias and trenches in the interconnect dielectric layer, avoiding the problems associated with the use of thick mask layers, such as contact hole striations and small depth of focus, which can result in shorts or opens.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

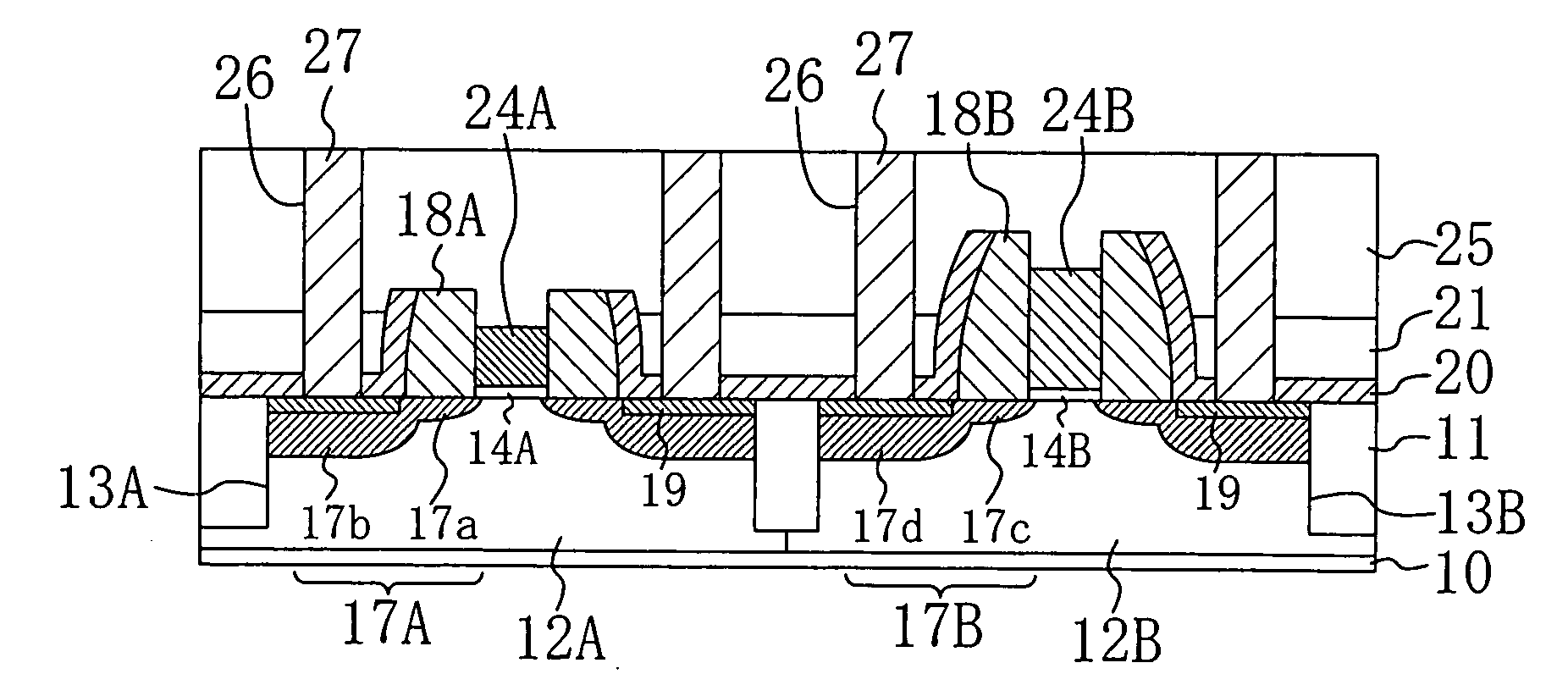

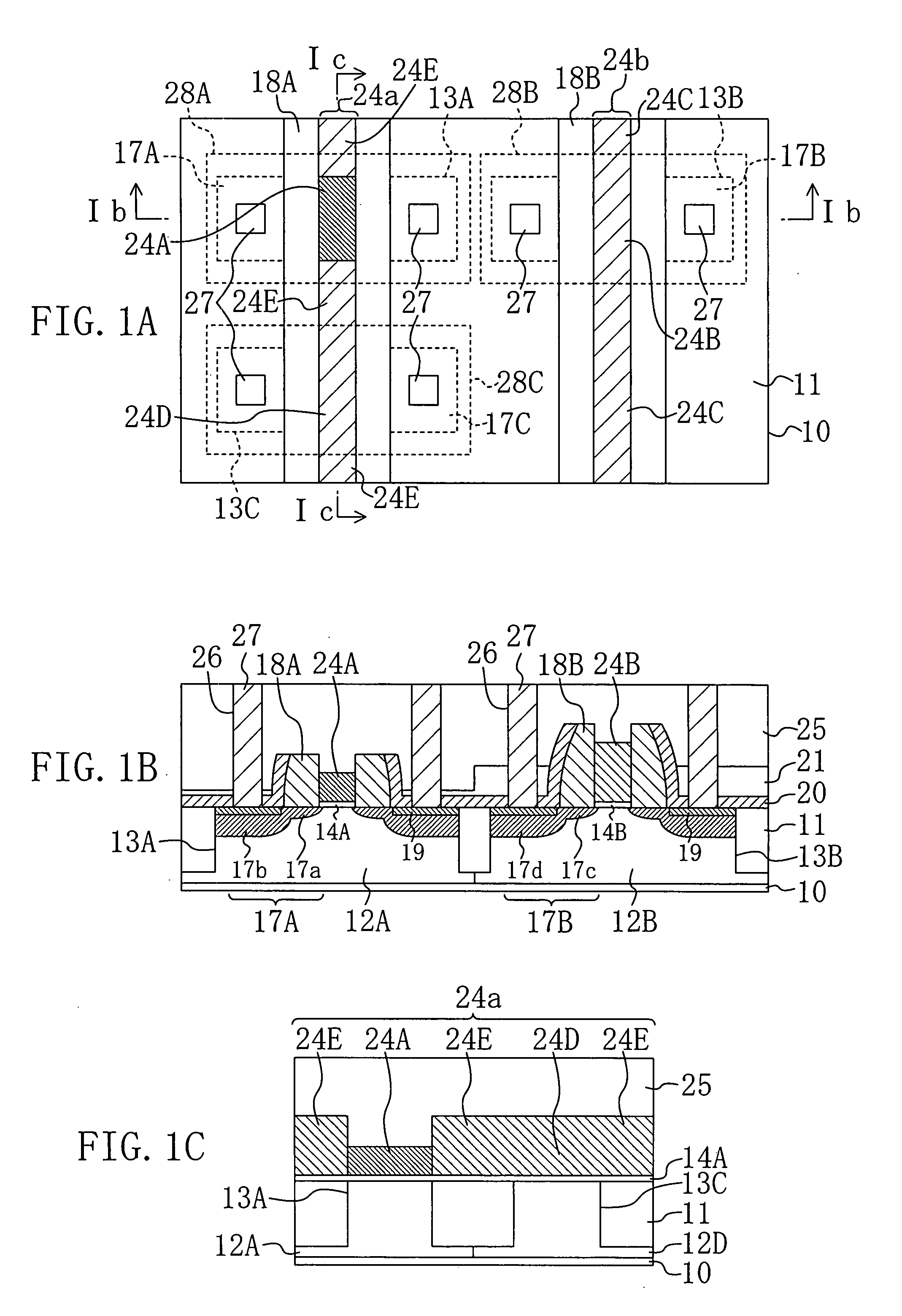

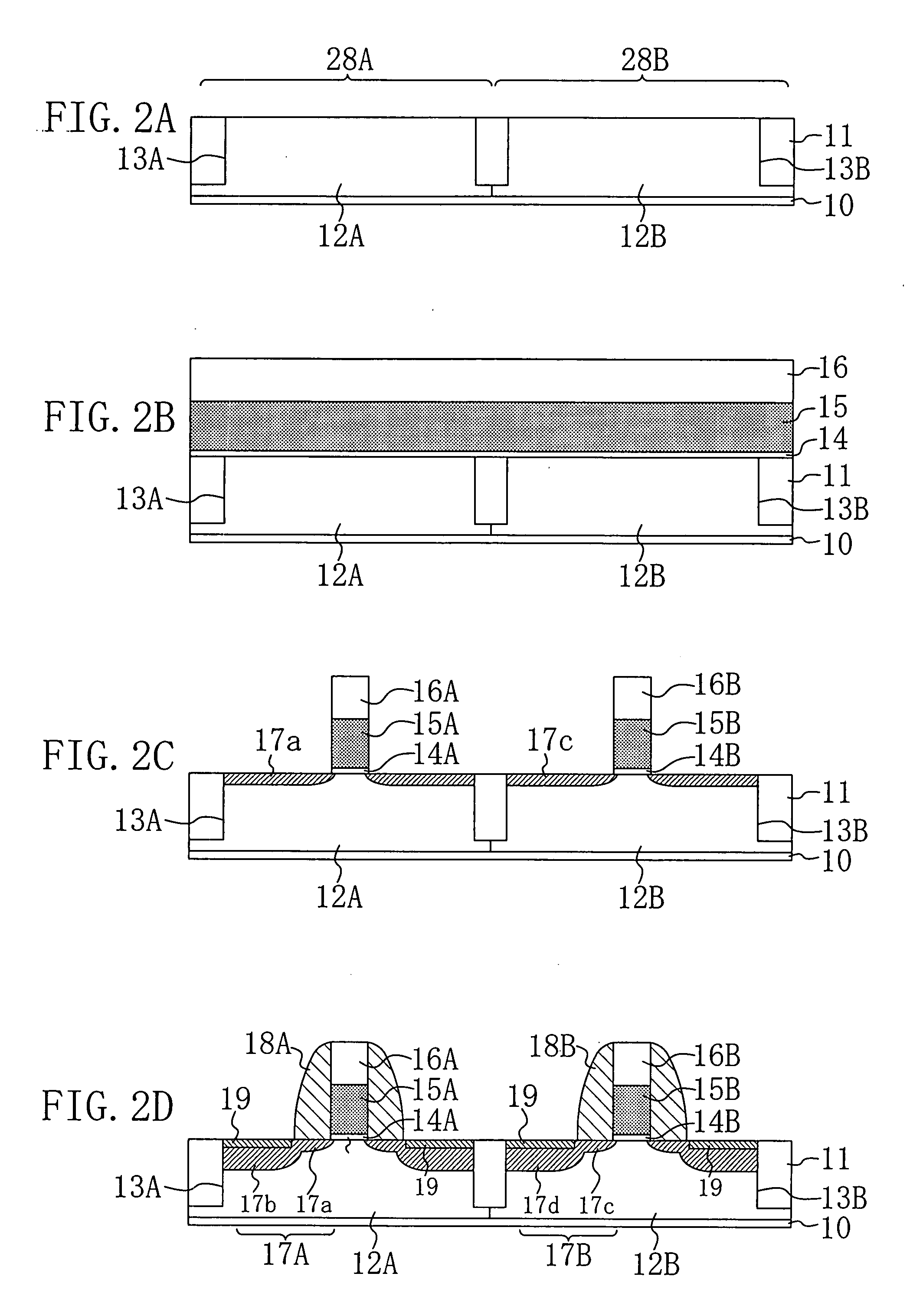

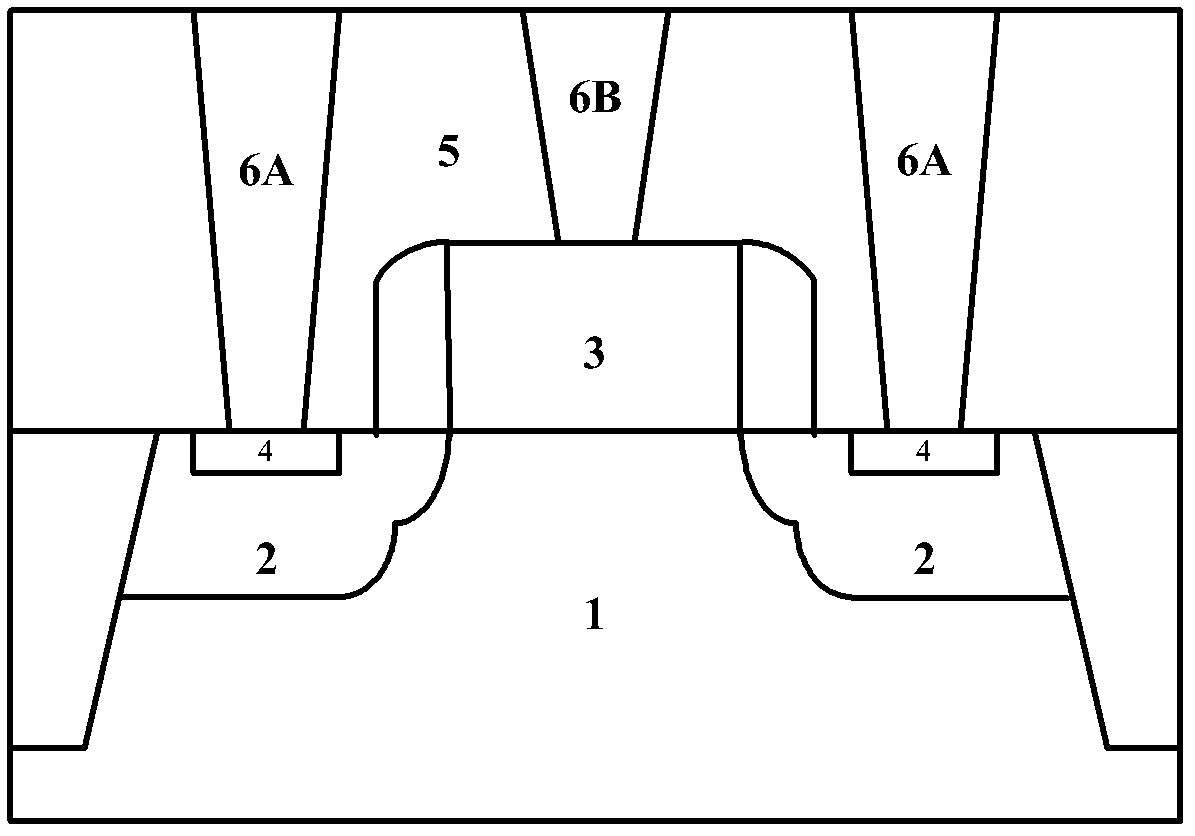

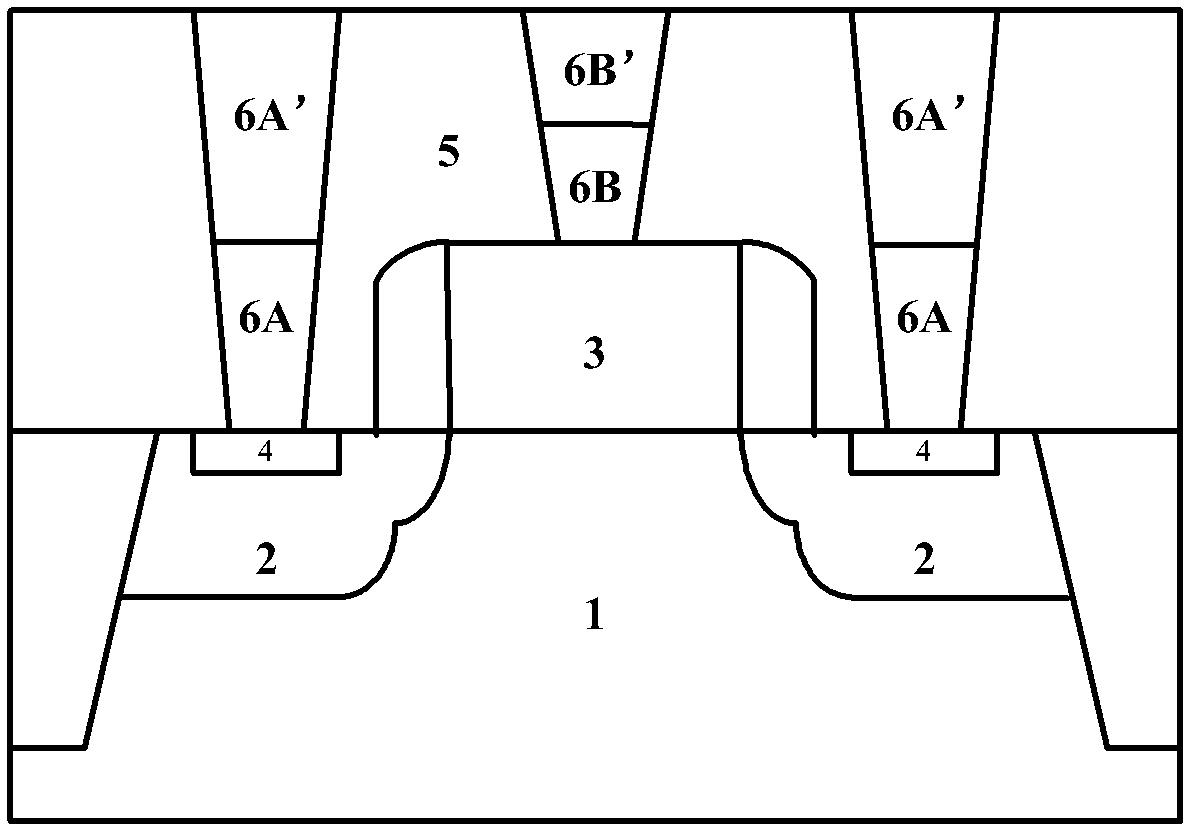

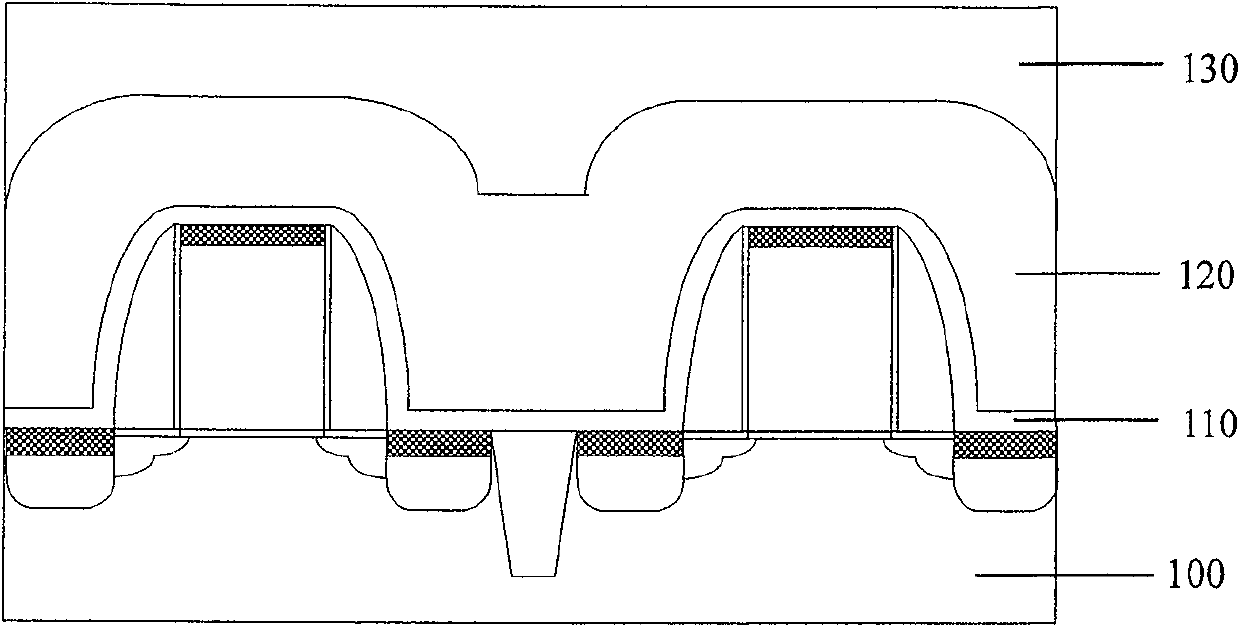

Semiconductor device and method for fabricating the same

InactiveUS20080128825A1Reduce thicknessLower interconnect resistanceTransistorSemiconductor/solid-state device manufacturingSiliconSemiconductor

A p-type MIS transistor includes a first gate insulating film formed on a first active region; and a first fully silicided gate pattern that is obtained by fully siliciding a silicon film, is formed to extend over the first active region with the first gate insulating film sandwiched therebetween, and includes a first fully silicided gate electrode provided on the first active region and a first fully silicided gate line provided on the isolation region. The first fully silicided gate pattern includes, along a gate width direction, a portion having a first thickness and including the first fully silicided gate electrode and portions each having a second thickness larger than the first thickness and respectively disposed on both sides of the portion having the first thickness.

Owner:PANASONIC CORP

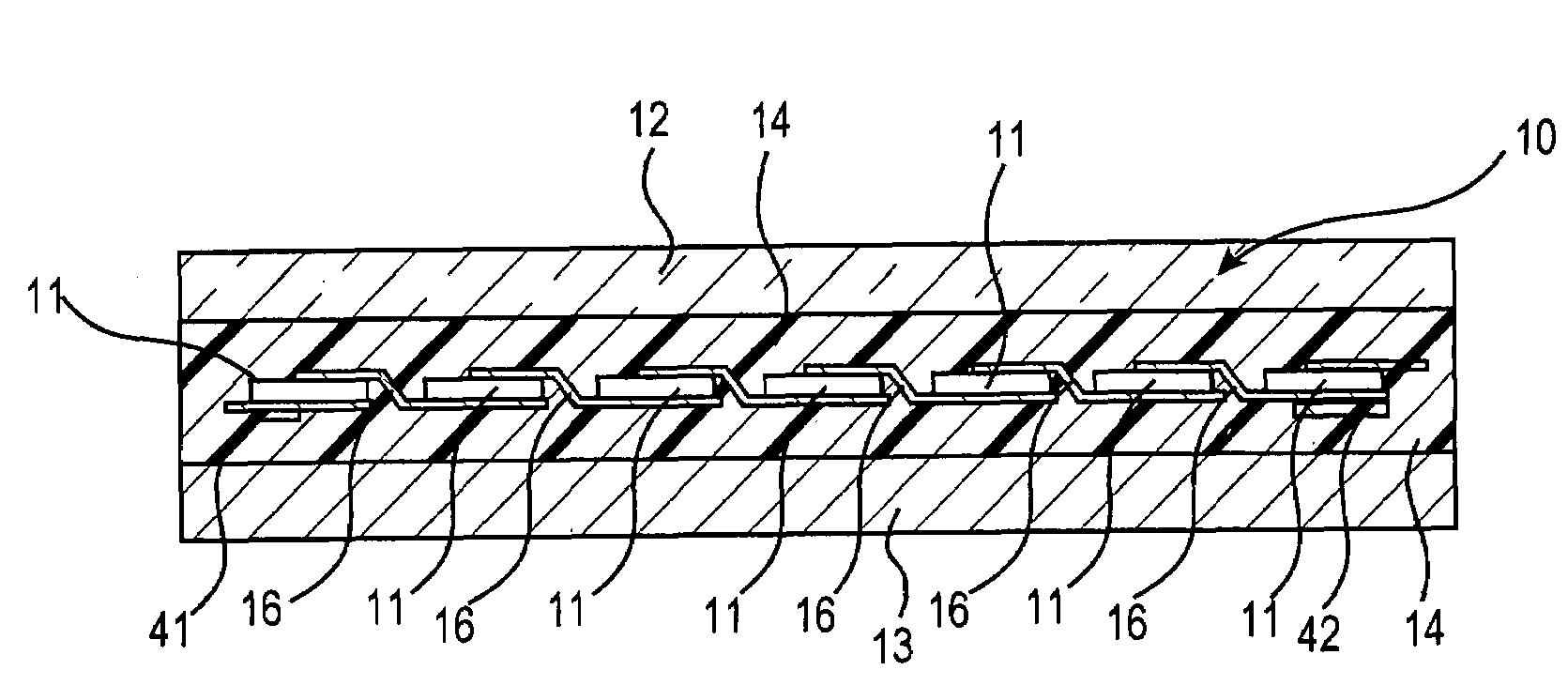

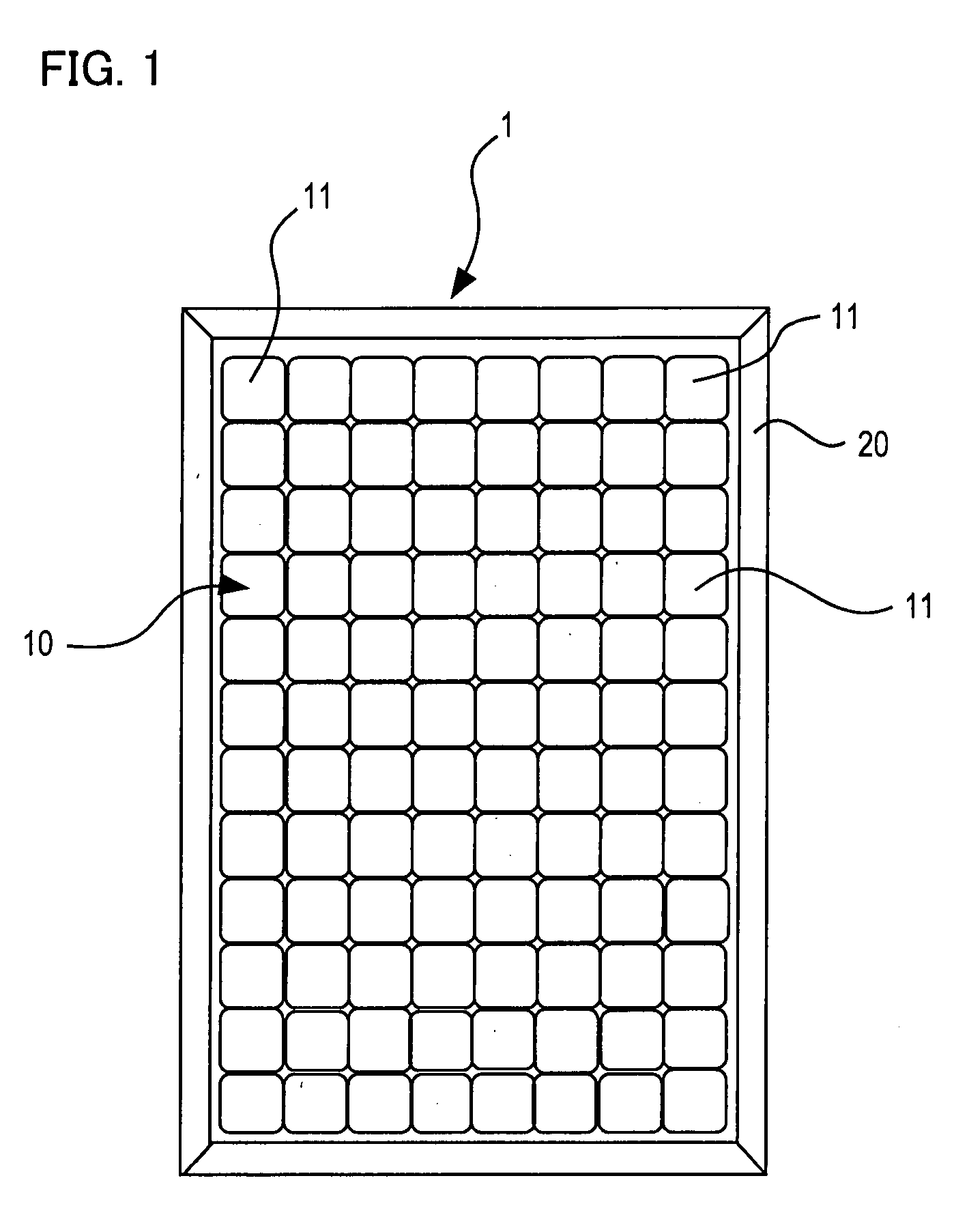

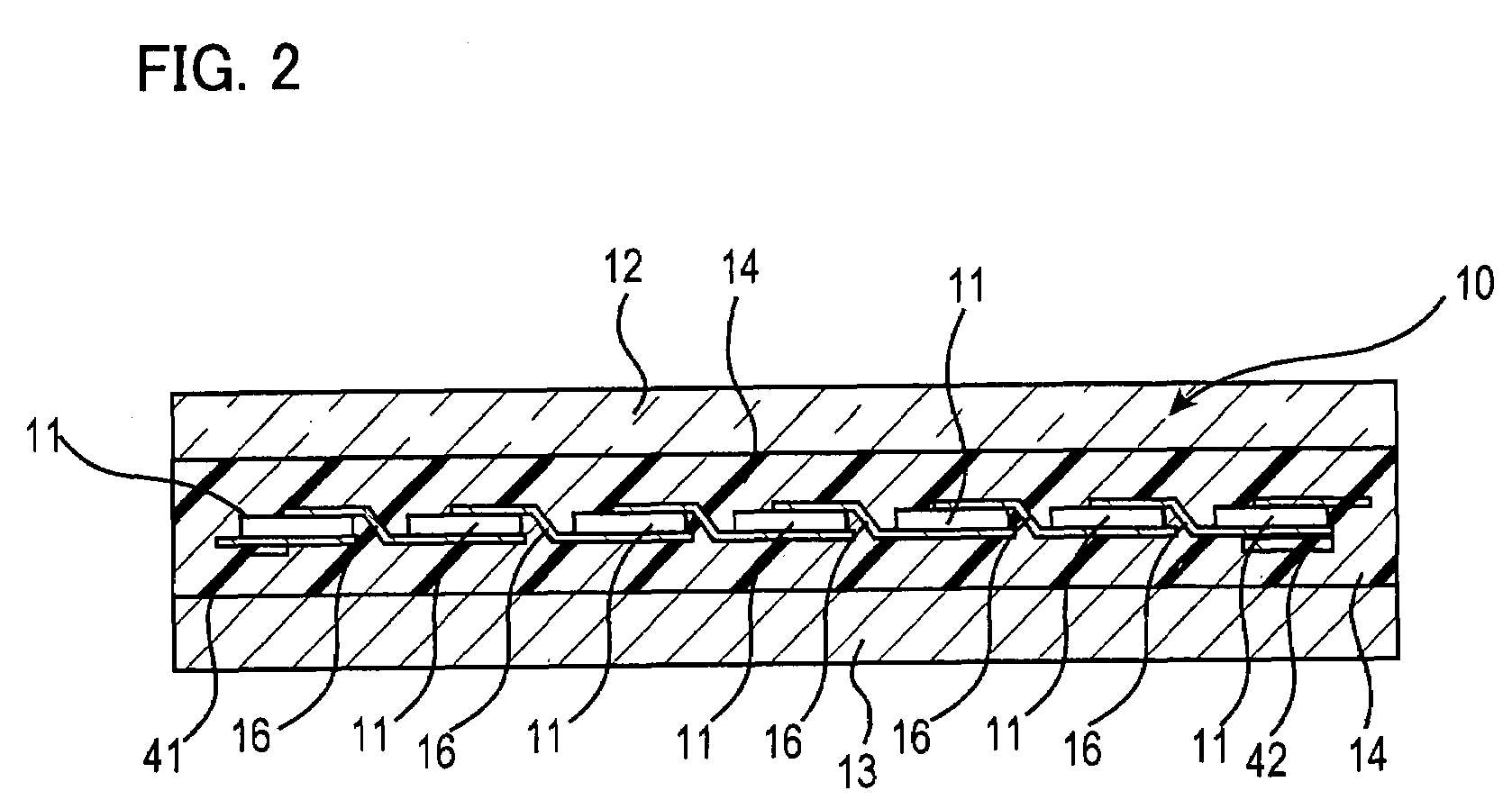

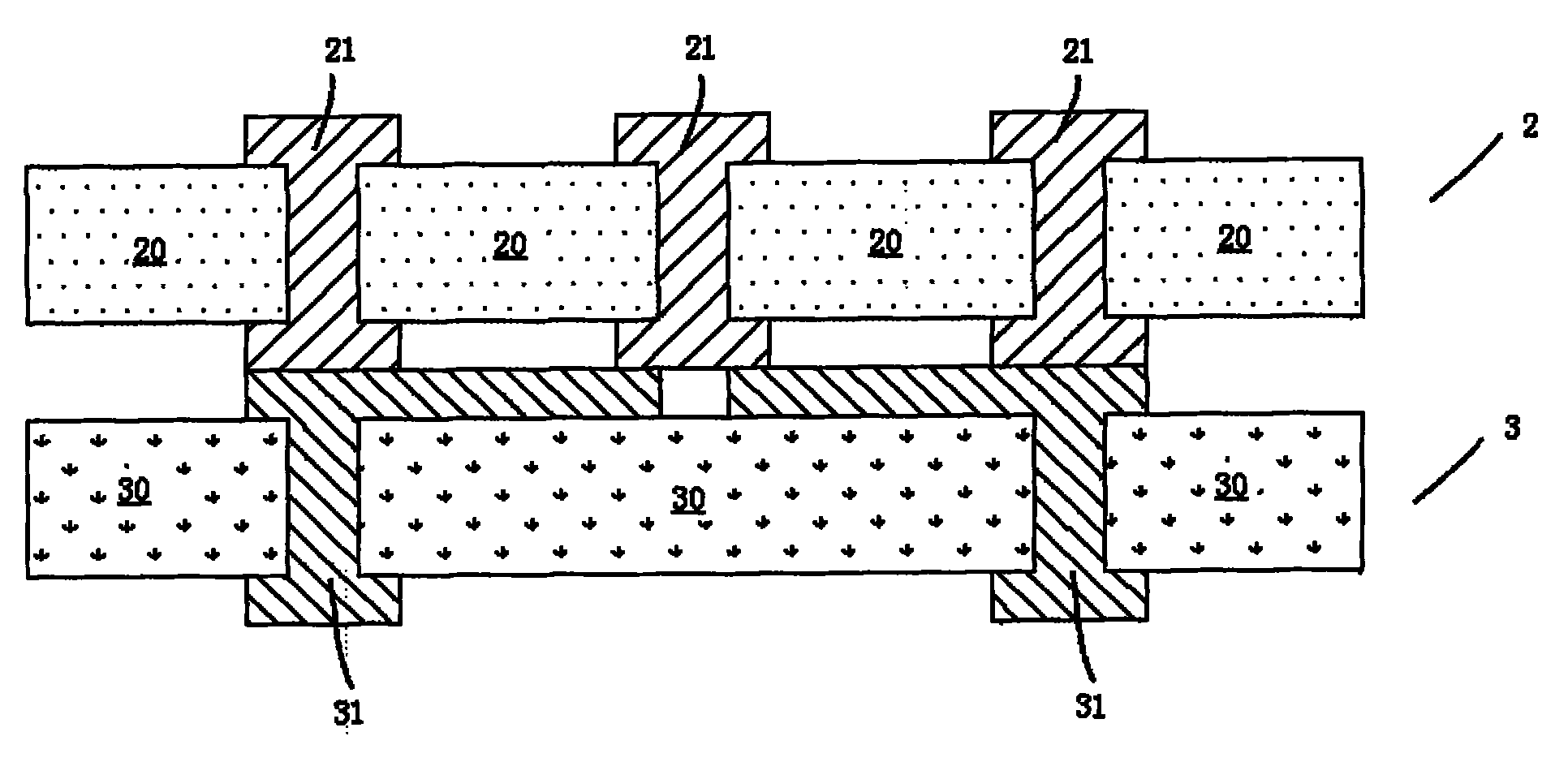

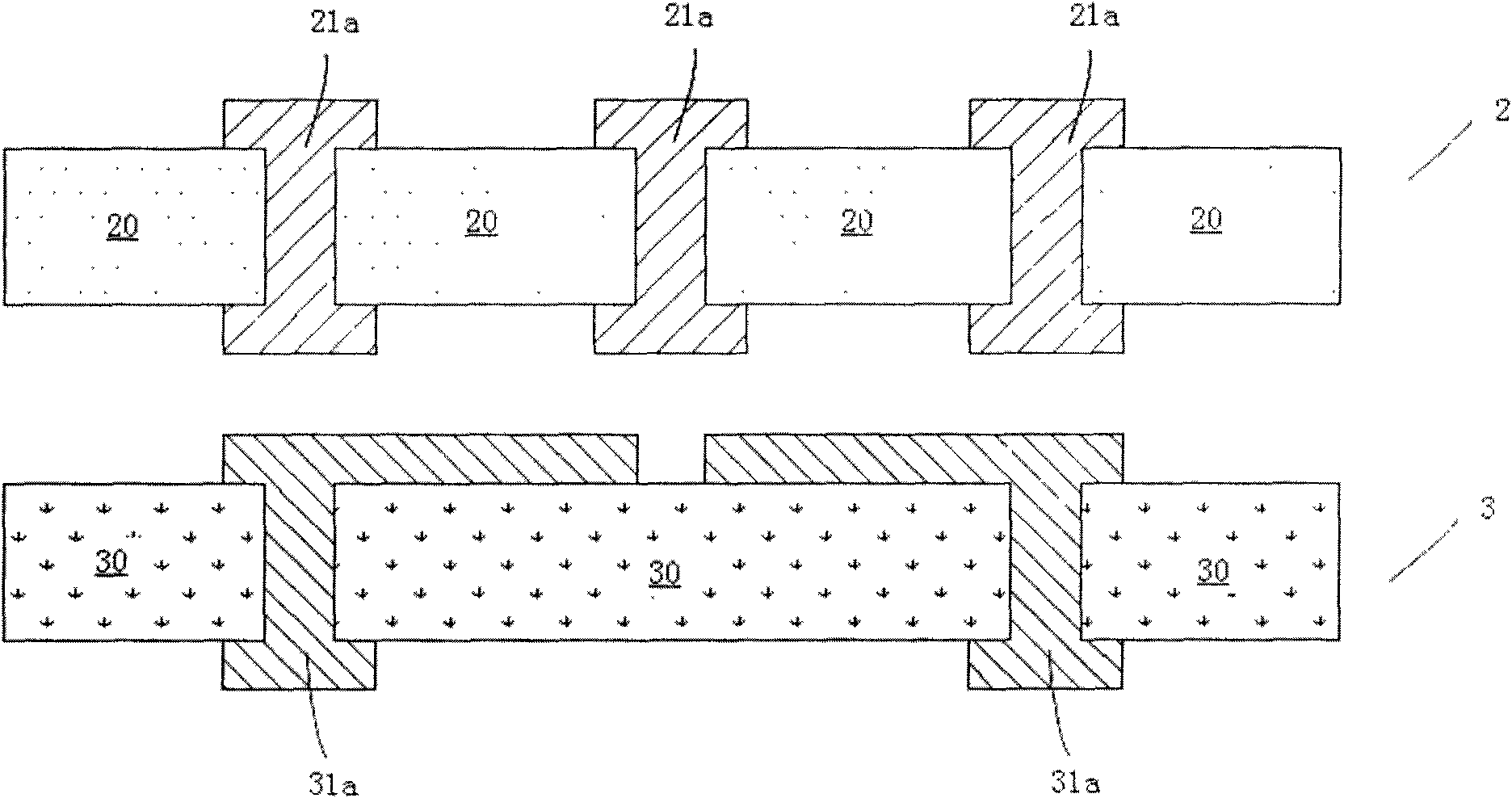

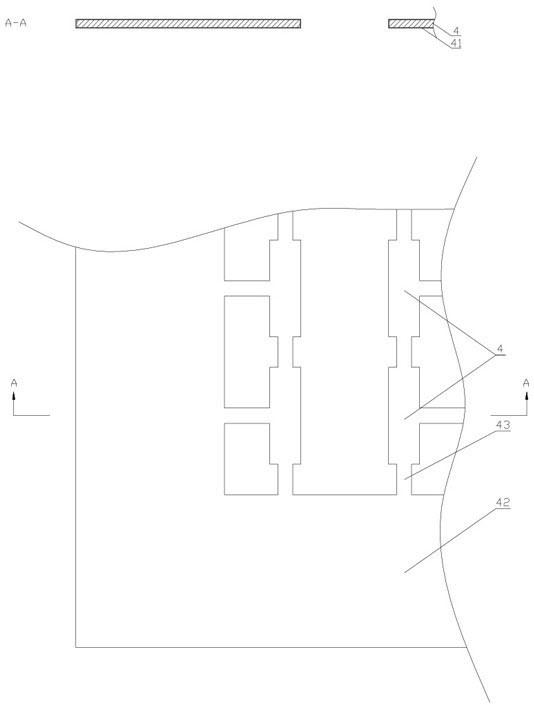

Photovoltaic module

ActiveUS20070227580A1Reduced footprintImproves module efficiencyPV power plantsPhotovoltaic energy generationInterconnectorEngineering

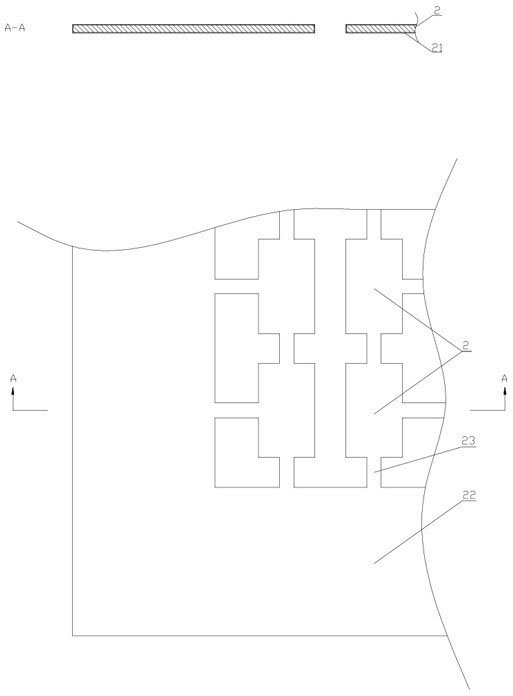

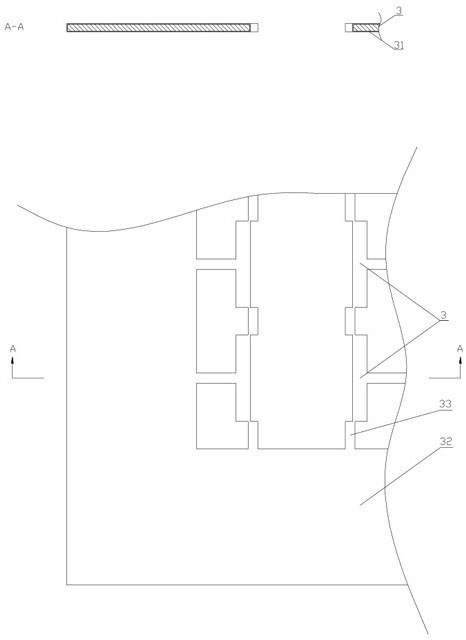

It is an object of the present invention to provide a photovoltaic module capable of reducing an area occupied by interconnectors. The photovoltaic module of the present invention comprises light-transmitting substrate, strings including a plurality of solar cells interconnected through tab connector, and rear surface member. A plurality of the strings is electrically connected through interconnectors and arranged on a rear surface side so as not to overlap each other. The photovoltaic module is sealed with a sealant between the light-transmitting substrate and the rear surface member.

Owner:SANYO ELECTRIC CO LTD

Electroplating copper solution and electroplating method for wafer-level packaging super TSV copper interconnection material

ActiveCN110541179AImprove reliabilityExcellent deep platingSemiconductor/solid-state device manufacturingSemiconductor devicesSulfurChloride

The invention discloses an electroplating copper solution and electroplating method for a wafer-level packaging super TSV copper interconnection material. The electroplating copper solution comprises,according to the concentration, 100-250 g / L of concentrated copper sulfate pentahydrate, 40-80 g / L of concentrated sulfuric acid, 30-50 mg / L of chloride ions, 1-5 mg / L of 3-sulfur-isothiourea propanesulfonic acid inner salt, 50-100 mg / L nonylphenol polyoxyethylene ether, 40-80 mg / L of phenazine dye and the balance DI pure water; the components are uniformly mixed to form the electroplating coppersolution; before electroplating, the wafer is subjected to vacuum treatment by a pretreatment solution; the pretreatment solution is DI pure water, and the wafer is vacuumized by using DI pure waterin vacuum equipment for 5-10 min after the wafer is mounted by an electroplating hanger; and after vacuumizing, electroplating is carried out in the electroplating copper solution. The super TSV growsin the bottom-up form, so that the problems of voids, cracks and the like of existing super TSV are solved, and the defects of unstable signal transmission, large resistance, excessive power loss andthe like due to voids can be effectively avoided.

Owner:SHENZHEN CHENGGONG CHEM

Silicon slice alignment method for silicon through hole interconnection

InactiveCN101814453AHigh precisionHigh speedSemiconductor/solid-state device detailsSolid-state devicesInterconnectionSilicon chip

The invention belongs to the technical field of high-integration encapsulation, and particularly discloses a silicon slice alignment method for silicon through hole interconnection. The method comprises that: stacked and interconnected upper and lower silicon slices are aligned and corrected by adopting an electric method when a plurality of silicon slices are stacked and interconnected, so the alignment precision of the silicon slices can be improved and the interconnected resistance can be reduced. The integrated circuit chip manufactured by the method has the performance of high speed and low power consumption.

Owner:FUDAN UNIV

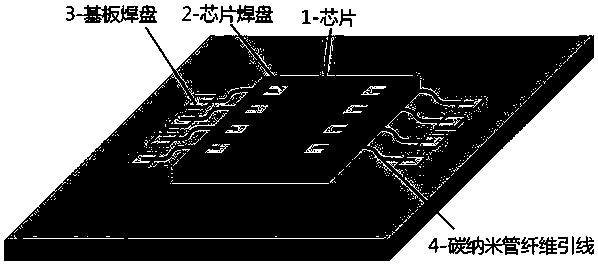

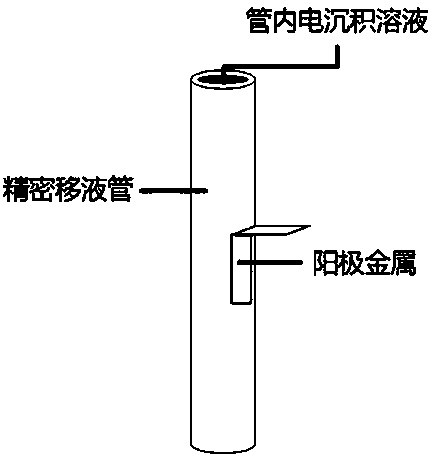

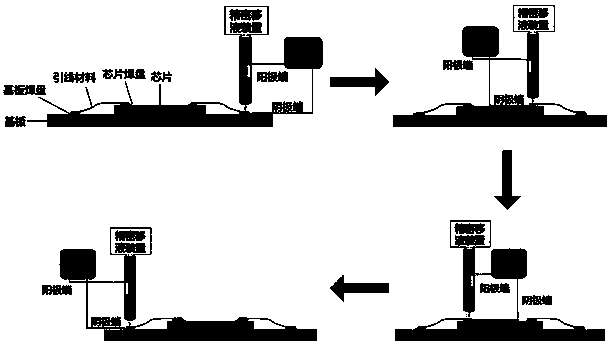

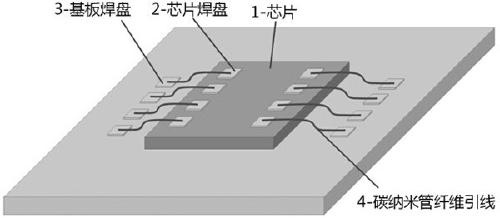

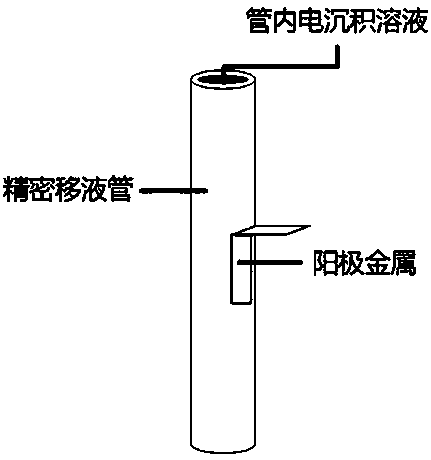

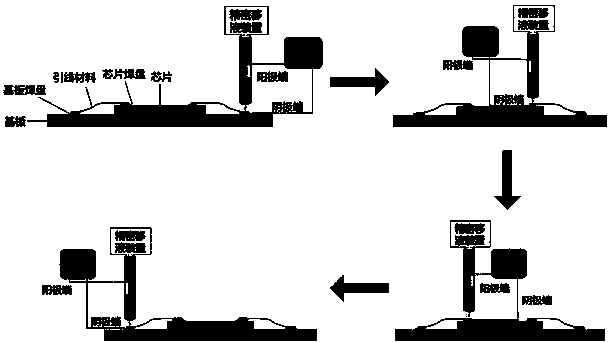

Lead bonding method based on rapid local electrodeposition

ActiveCN108054108AImprove conductivityBroaden your optionsSolid-state devicesSemiconductor/solid-state device manufacturingMicro nanoMetal coating

The invention relates to a wire bonding method based on rapid local electrodeposition, and belongs to the technical field of lead connection. The method comprises the following steps of selecting a novel lead material to be bonded and modifying the novel lead material; placing the lead material on the surface of a bonding pad through a micro-nano operation platform, ensuring that the lead is in good contact with the surface of the bonding pad; and selecting the caliber of a local electrodeposition precise pipette and the type of an anode metal in the pipette to ensure good contact between an electroplating cathode end probe and the bonding pad; forming a metal coating which completely coats the lead material on the surface of the bonding pad through a local electrodeposition method; and cleaning the entire device after the bonding of the electrodeposition leads on the surface of the bonding pad. Compared with a traditional lead bonding process, the method disclosed by the invention hasthe advantage that reliable lead bonding of the novel lead material can be realized, heating connection is not needed in the whole bonding process, and the whole bonding process is free of thermal damage and mechanical damage. The method is simple in technological process and high in bonding speed, and is suitable for various bonding pad materials and wide in connection layer metal variety selection range.

Owner:HARBIN INST OF TECH

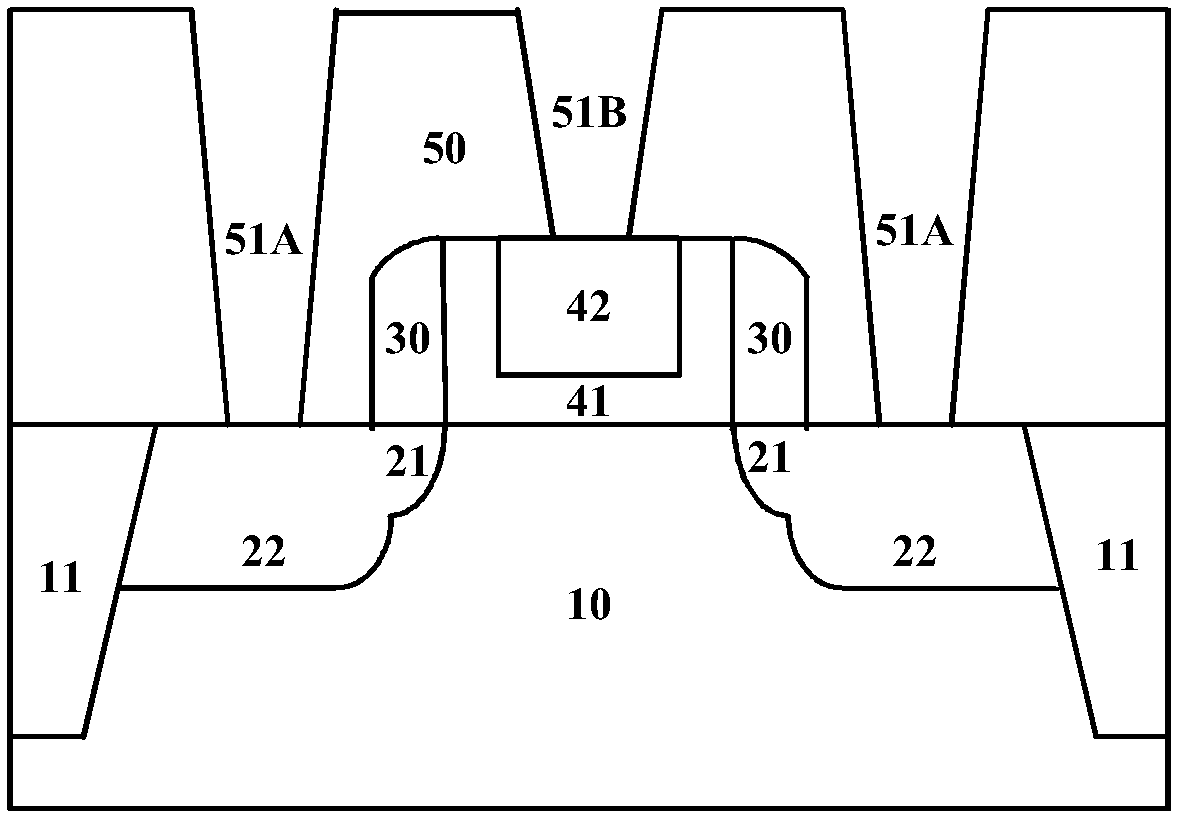

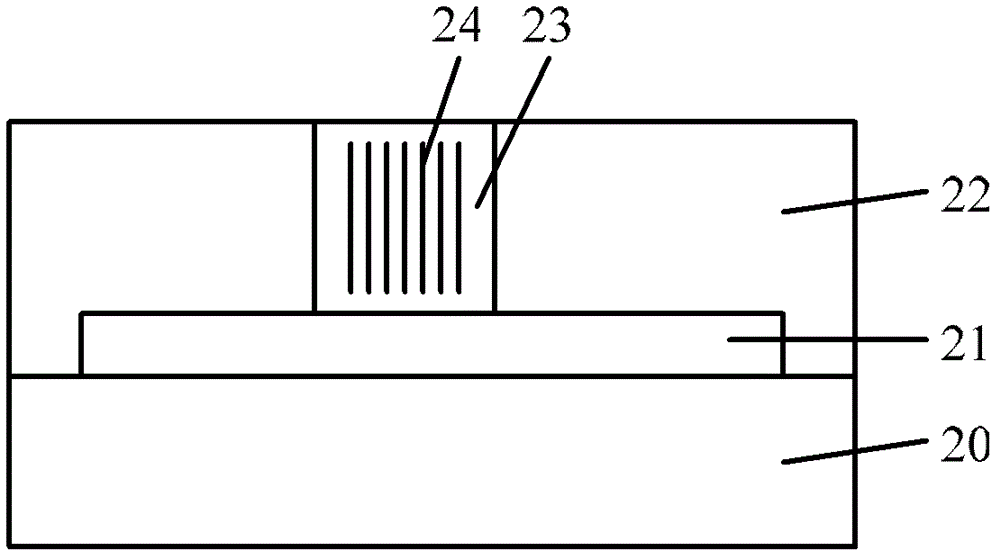

Metal oxide semiconductor field effect transistor (MOSFET) with lifted silicide source drain contact and manufacture method thereof

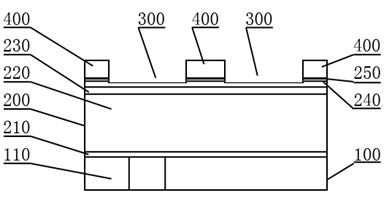

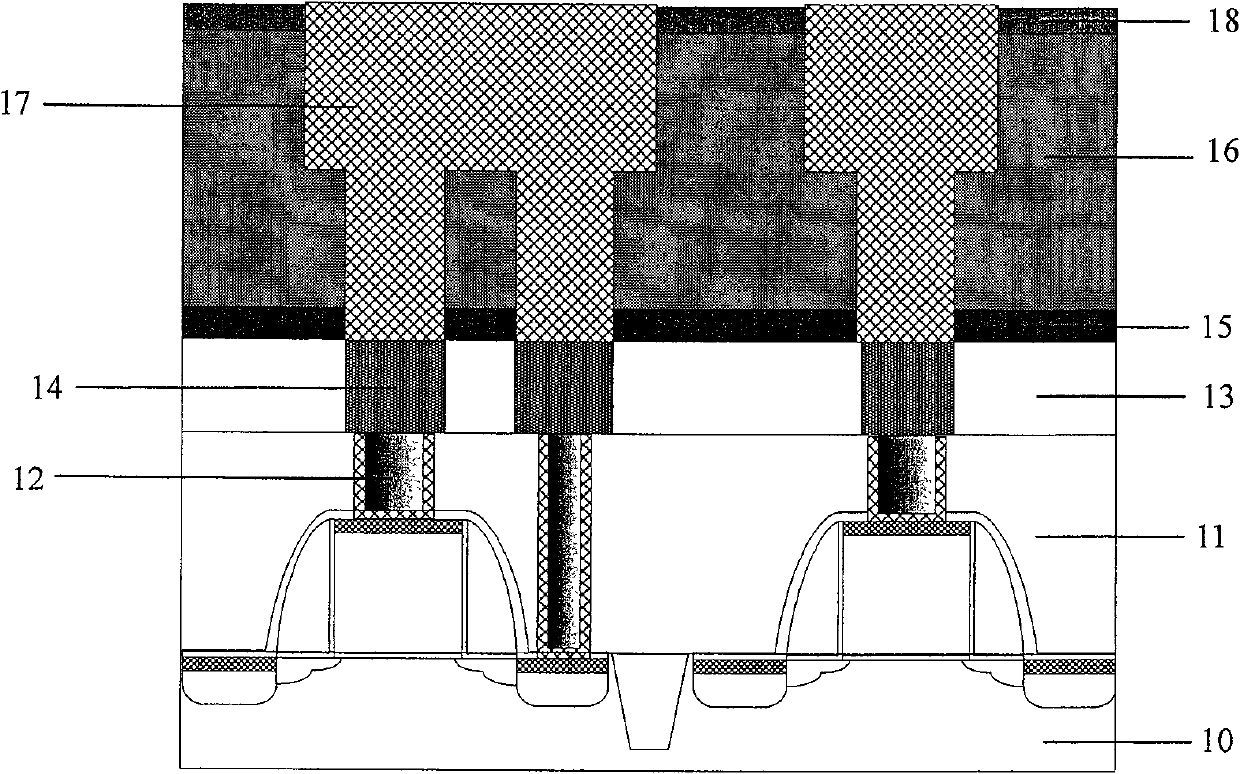

InactiveCN103137668AReduce dosageLower interconnect resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorMOSFET

The invention discloses a semi-conductor device which comprises a substrate, a source drain region in the substrate, a grid stacking structure on the substrate, a grid lateral wall, first metal silicide in the source drain region, contact plugs arranged above the source drain region and the grid stacking structure respectively and an interlayer dielectric layer. The semi-conductor device is characterized in that second metal silicide is arranged on the first metal silicide and the grid stacking structure, and the contact plugs are contacted with the second metal silicide. By means of the semi-conductor device, by lifting the first metal silicide, the first metal silicide is higher than the surface of the source drain region, and use amount of W in a contact hole is reduced. Interconnection resistance is greatly reduced, Cu diffusion can be effectively resisted, and the electrical performance of the device is effectively improved on the whole.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

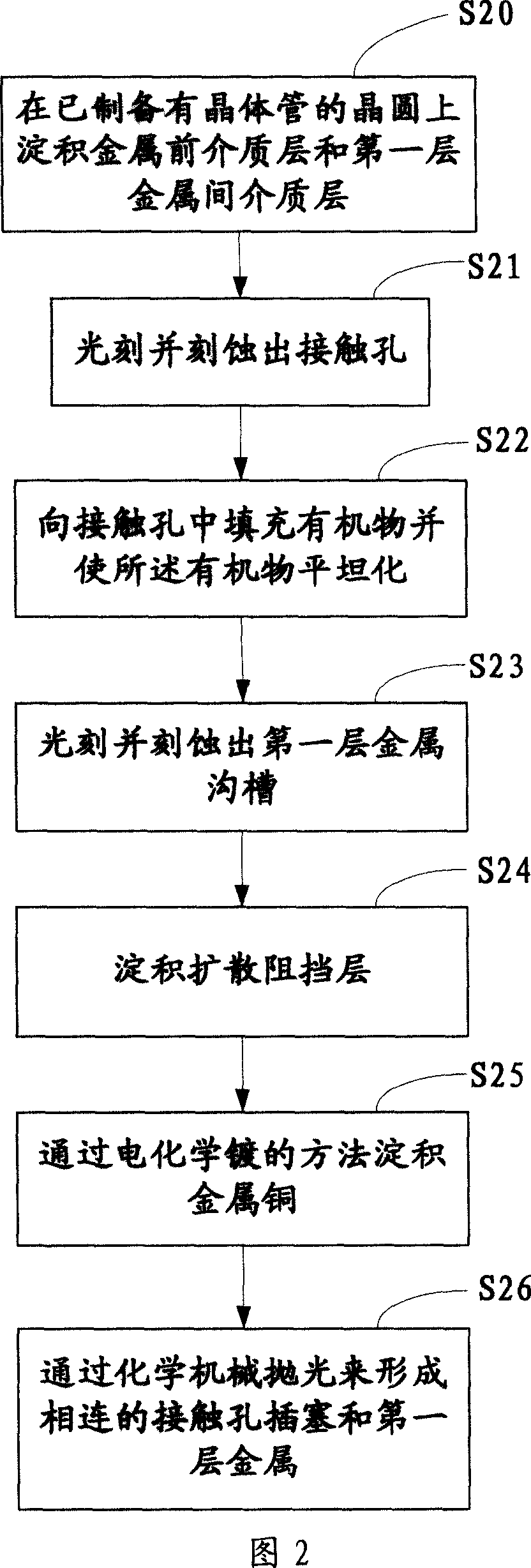

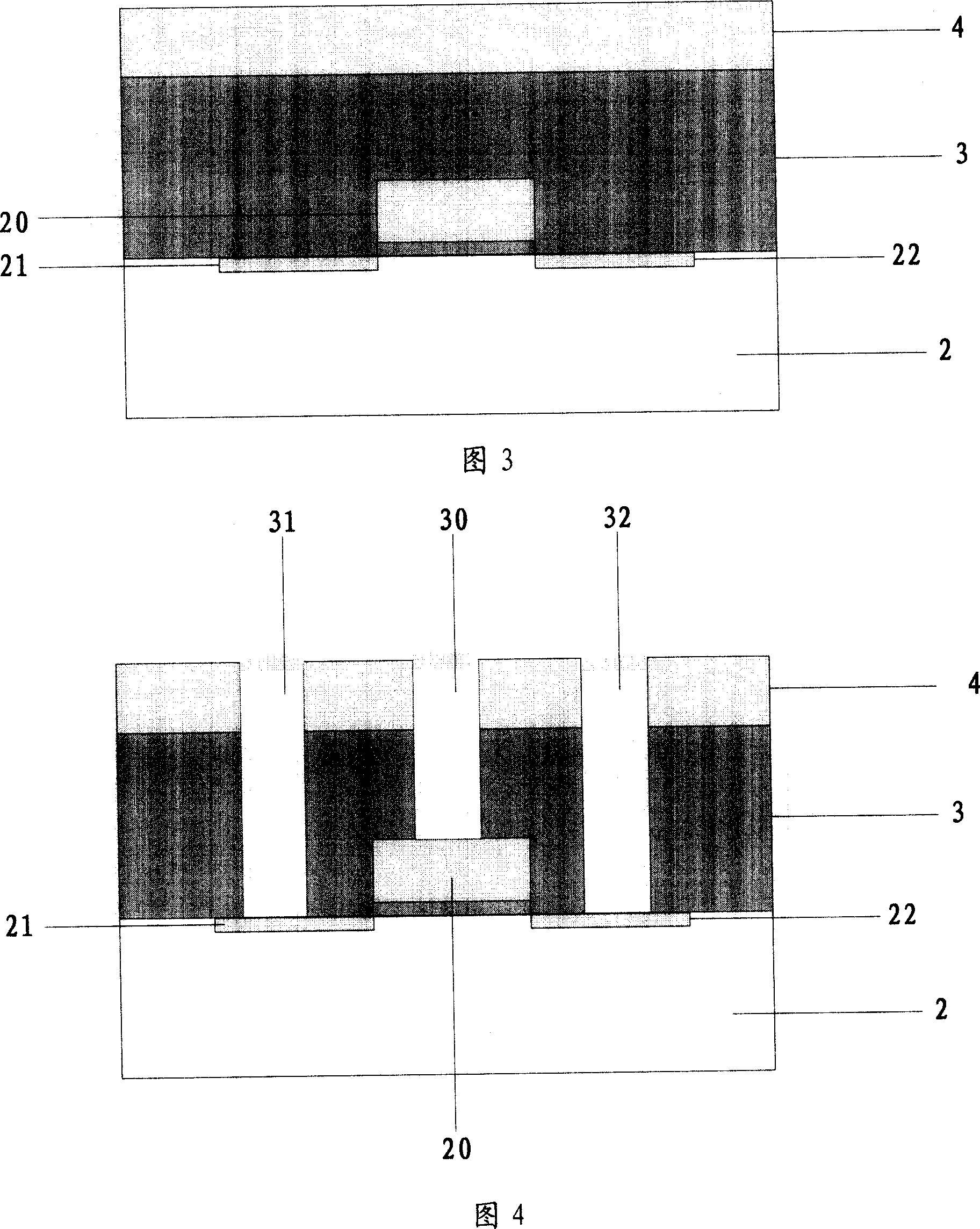

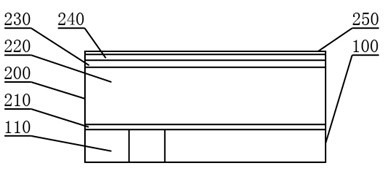

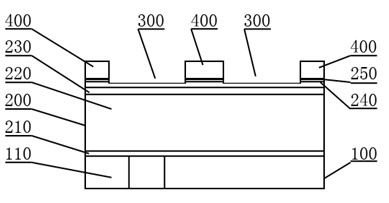

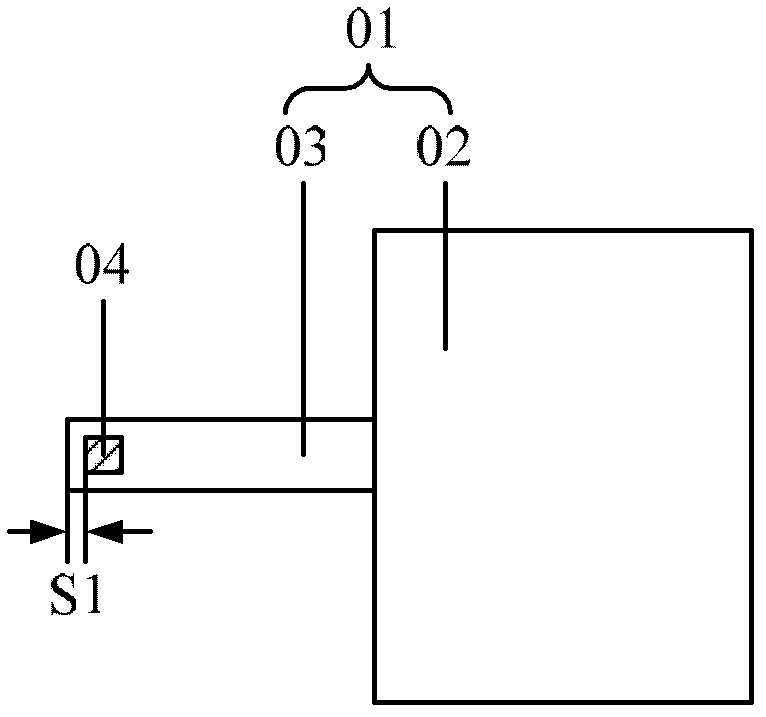

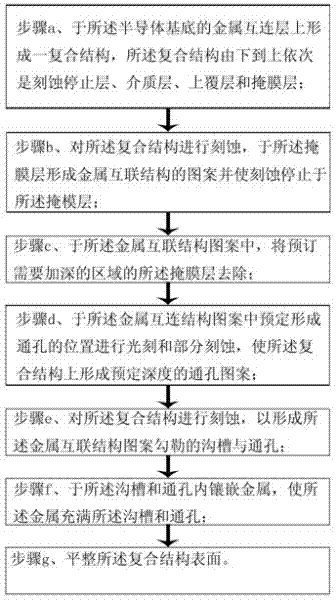

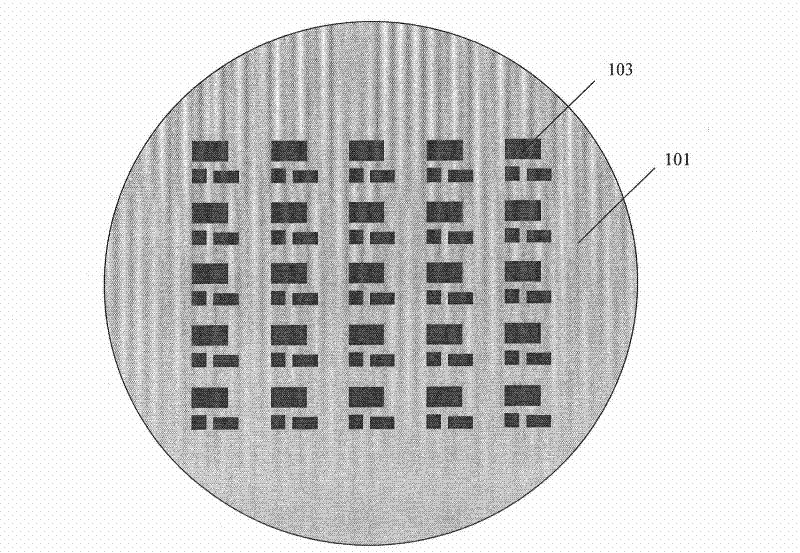

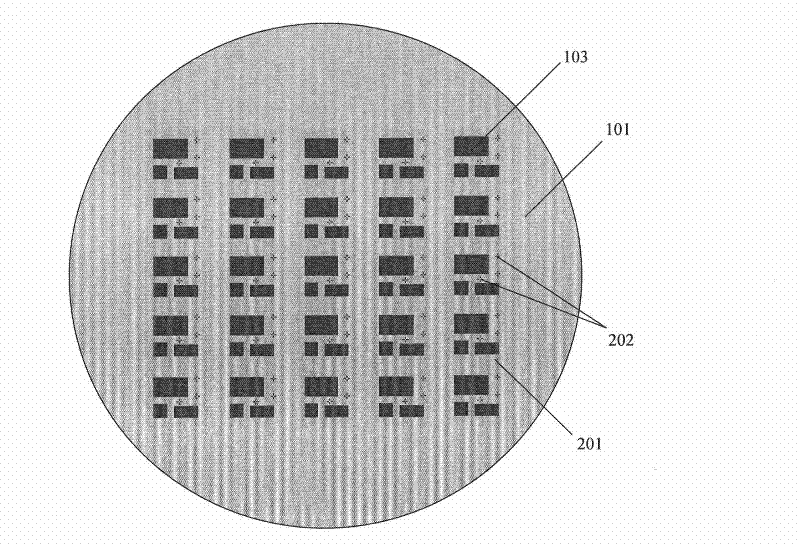

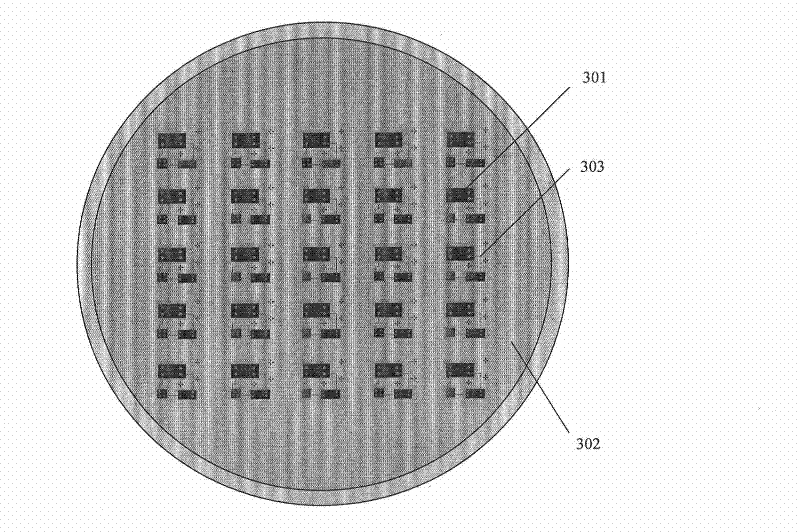

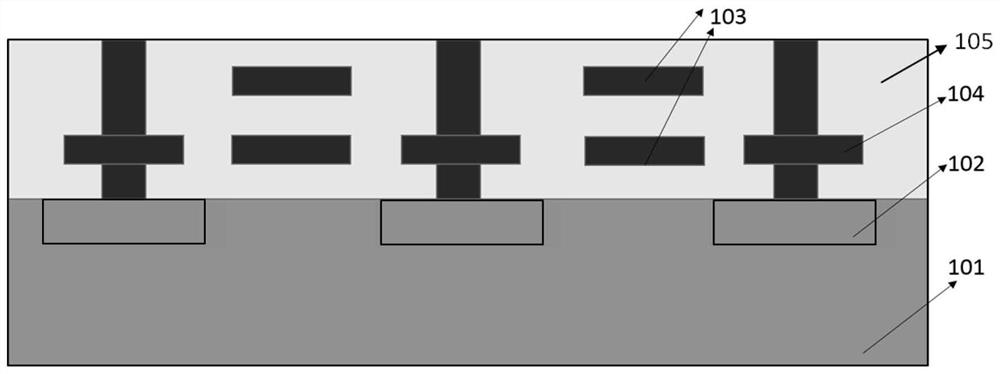

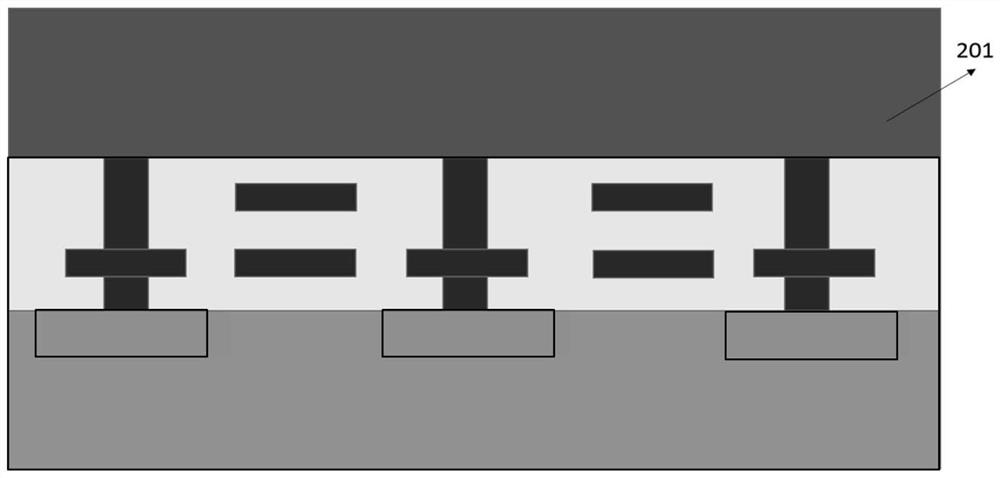

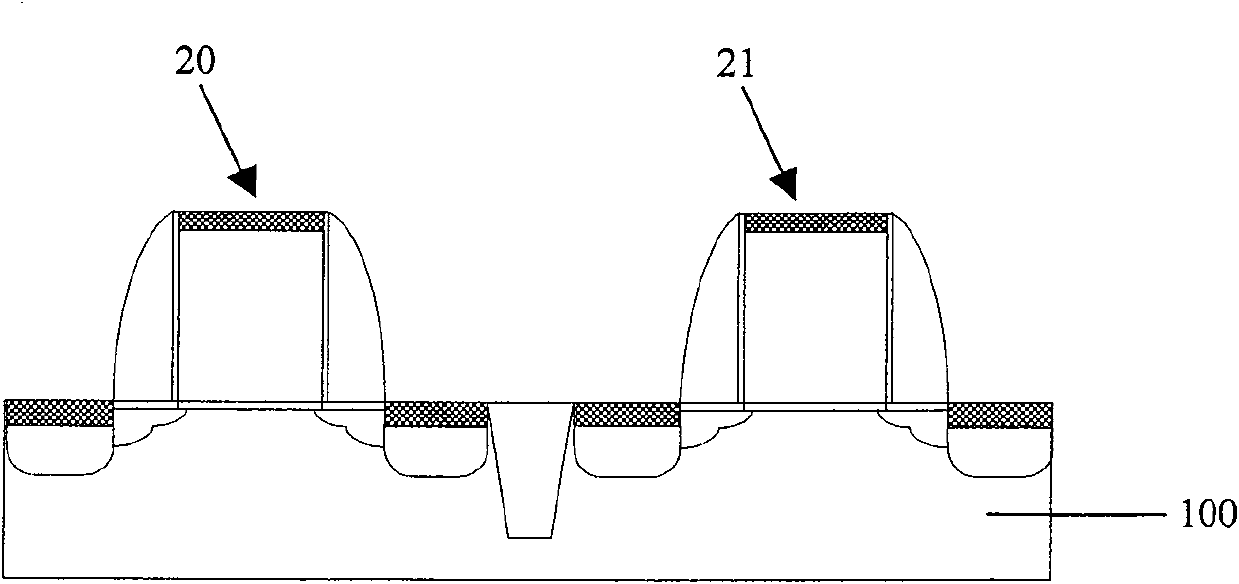

A making method of the contact hole plug and layer 1 metal

InactiveCN101017792ALower Interconnect ResistanceMeeting the ever-decreasing demands of feature sizesSemiconductor/solid-state device manufacturingCompound (substance)Diffusion barrier

The related preparation method for contact hole plug and first layer metal comprises: on the wafer with transistor, depositing metal front-media layer and the first metal intermediate layer; photo etching the contact hole, filling the hole with organic, and flattening the organic; photo etching the first metal groove, depositing the diffusion-barrier layer, electrochemical depositing copper, and chemical-mechanical polishing to form the plug and first layer metal. This invention overcomes defects in prior art, reduces product size, and simplifies procedure for higher efficiency.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

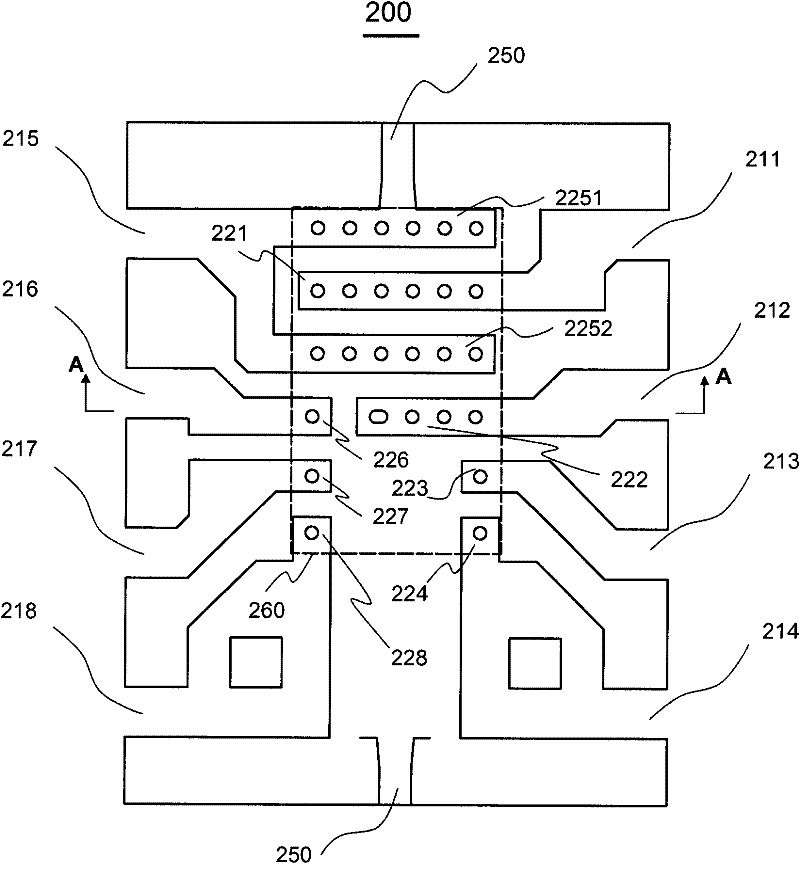

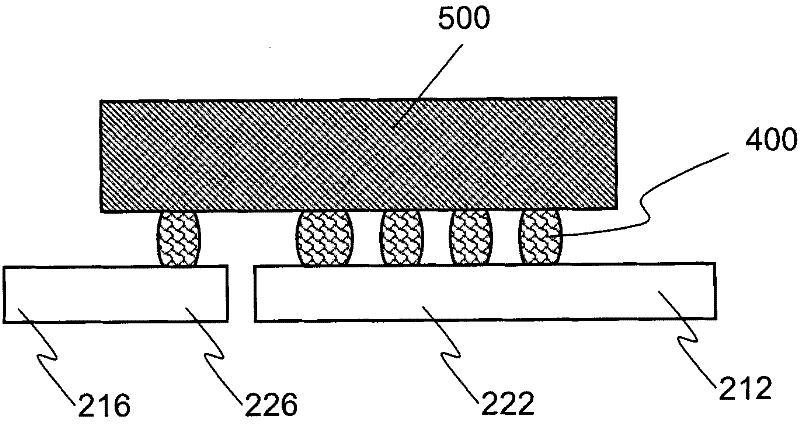

Inverted lead frame and packaging structure thereof

InactiveCN102332440ACompact structureLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

The invention provides an inverted lead frame and a packaging structure thereof, belonging to the technical field of chip packaging. The inverted lead frame comprises a first area part corresponding to a position at which a chip to be packaged is placed. The pins of the lead frame are arranged in the first area part at a position corresponding to the position of the pad of the chip on the approximately same plane. The lead frame has the advantages that the structure is simple and compact, the cost is low, the size of the packaging structure formed by the lead frame is small and the packaging requirement of high-output-current chips can be satisfied especially.

Owner:WUXI CHINA RESOURCE MICRO ASSEMBLY TECH

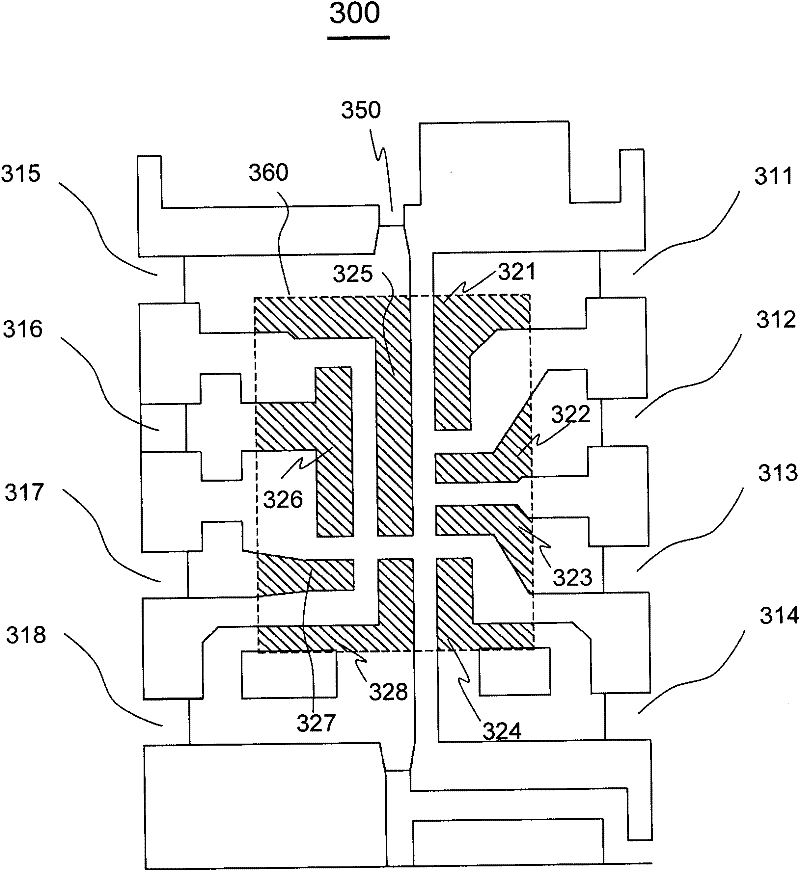

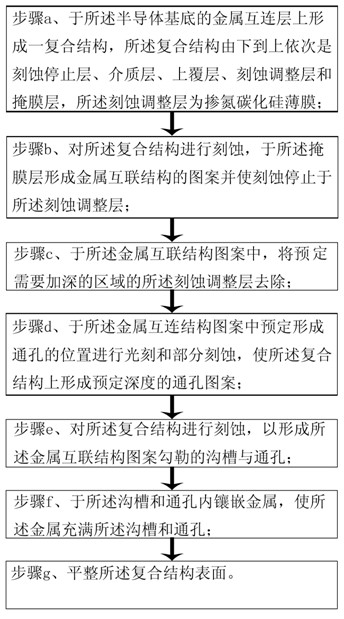

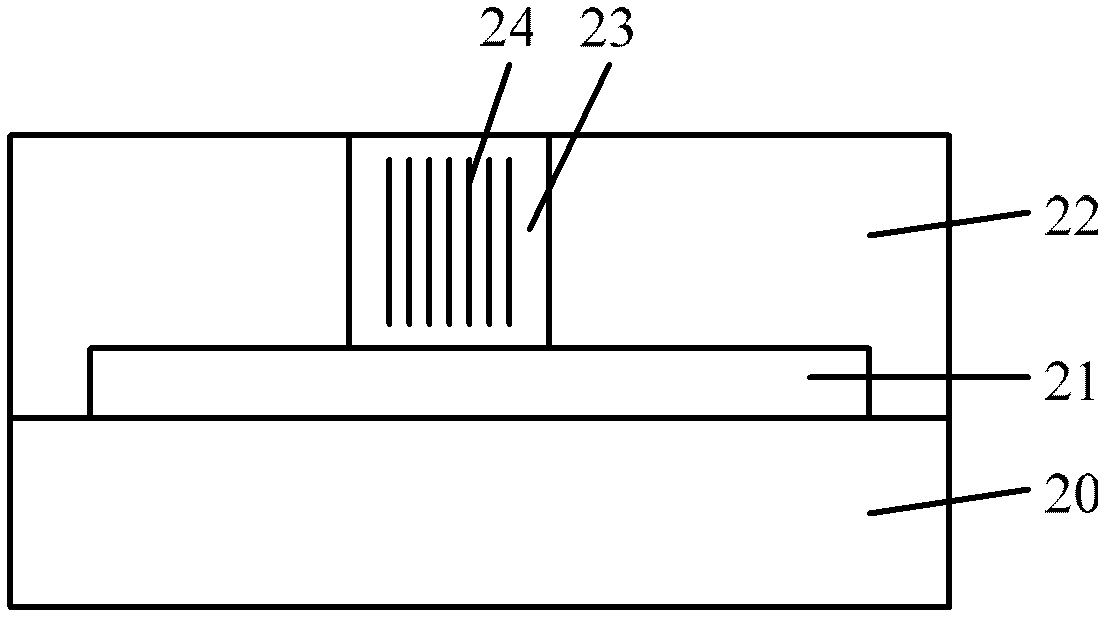

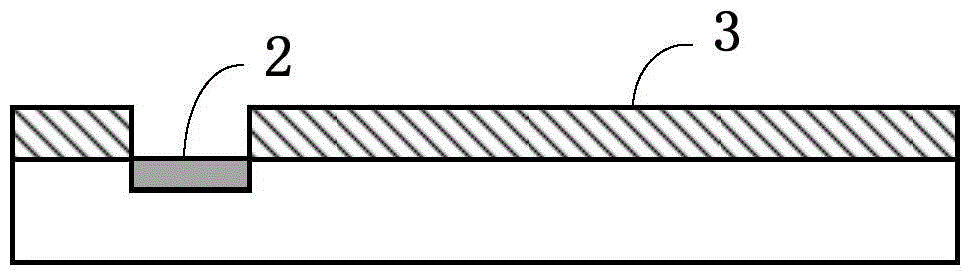

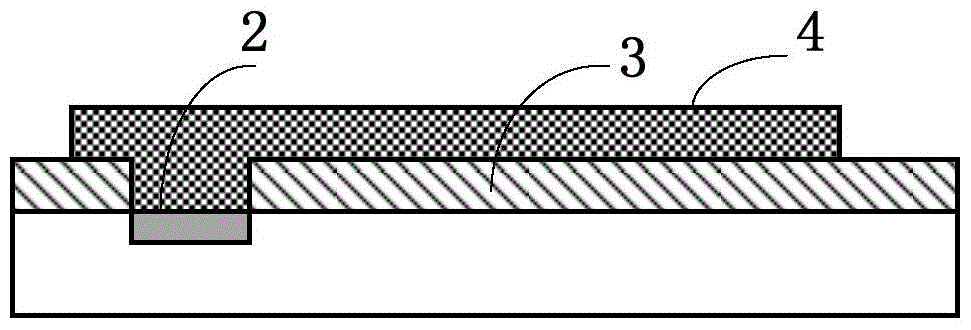

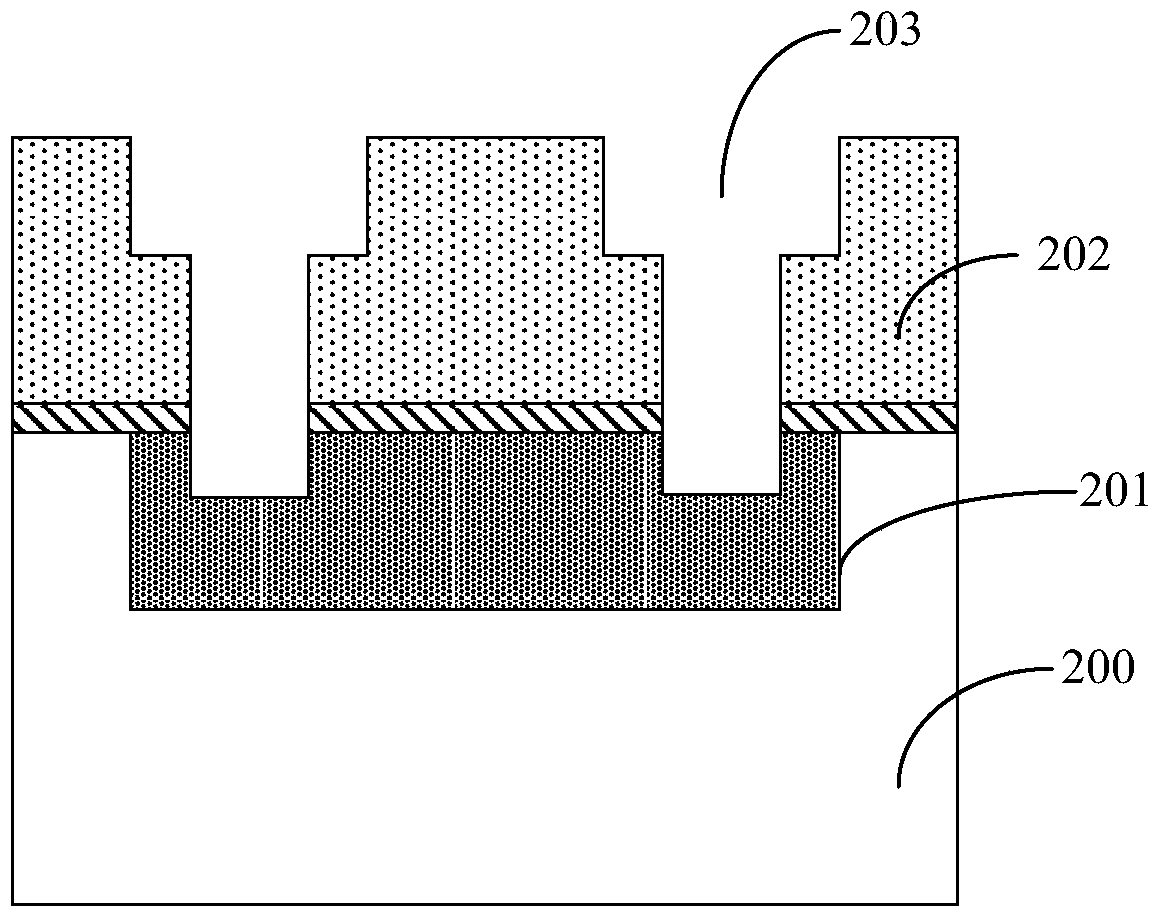

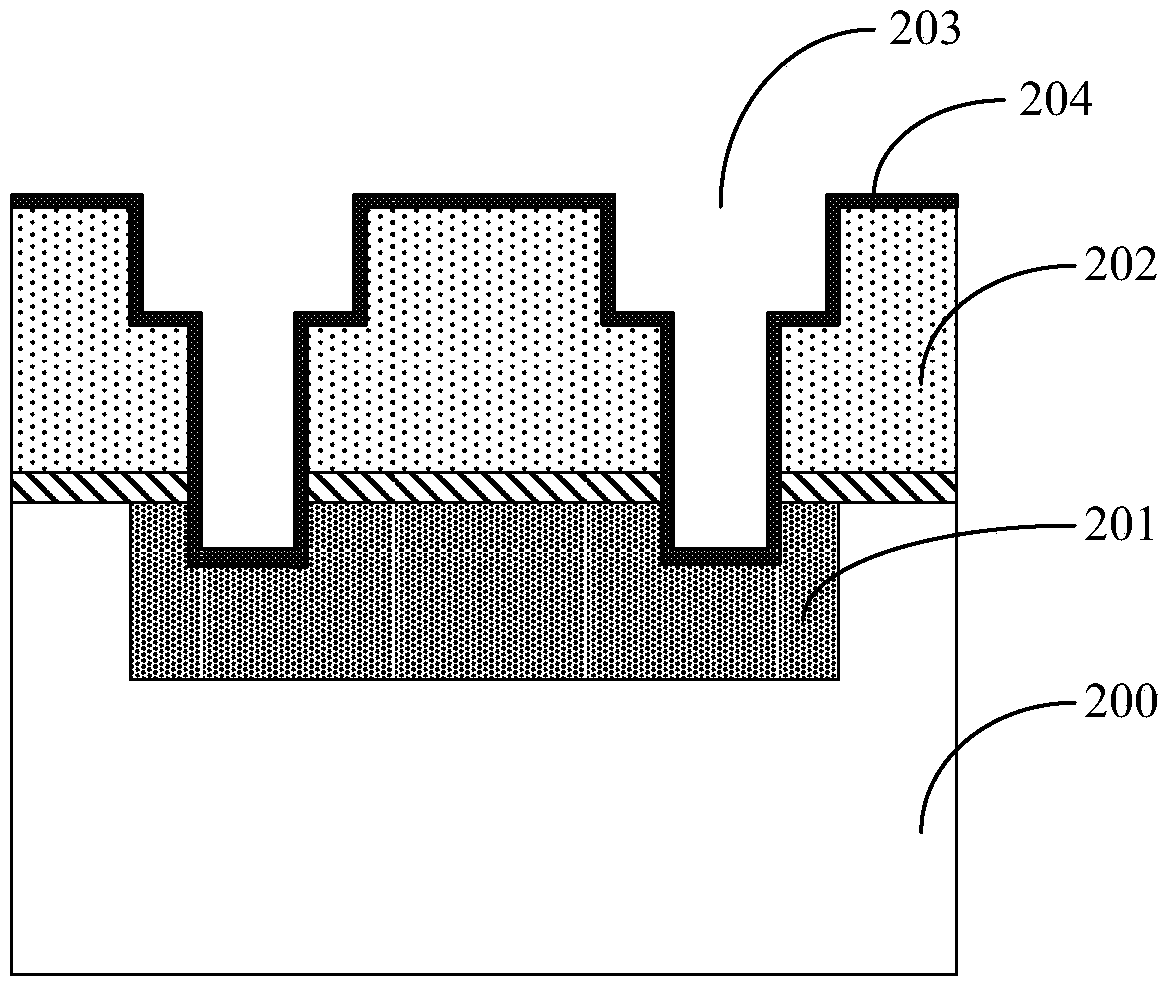

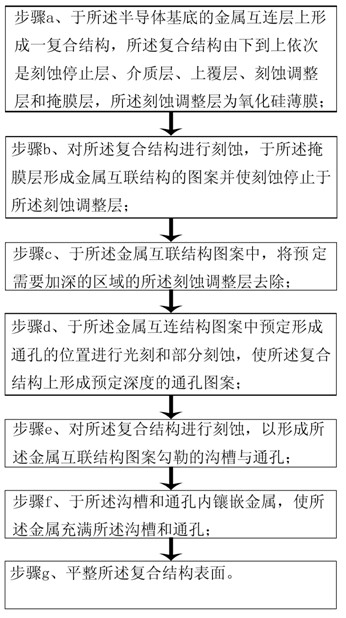

Method for realizing high-performance copper interconnection by using upper mask

InactiveCN102569178ALower resistanceReduce signal delaySemiconductor/solid-state device manufacturingCopper interconnectMetal interconnect

The invention discloses a method for realizing high-performance copper interconnection by using an upper mask. The upper mask comprises a semiconductor substrate in a metal interconnecting layer, wherein a composite structure is formed on the metal interconnecting layer of the semiconductor substrate; the composite structure consists of an etching stop layer, a medium layer, an upper coating layer, an etching adjusting layer and a mask layer from bottom to top; and the etching adjusting layer is a nitrogen-doped silicon carbide thin film. The method has the advantages that: according to the technical flow and the method provided by the invention, the depth of a copper interconnecting line ditch is selectively changed by using the added nitrogen-doped silicon carbide to etch a depth-adjusting layer, so the square resistance of a copper interconnecting line which is in accordance with a condition in a specific area is reduced, and the aim of selectively reducing chip interconnecting resistance is fulfilled. According to the application of the method, the interconnecting resistance can be reduced to the great extent on the premise that the overall copper interconnection depth is not changed, the process difficulty is not increased, and the size of a technical window is not reduced, the signal delay of a chip is reduced, the loss is reduced, and the overall performance of a chip is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

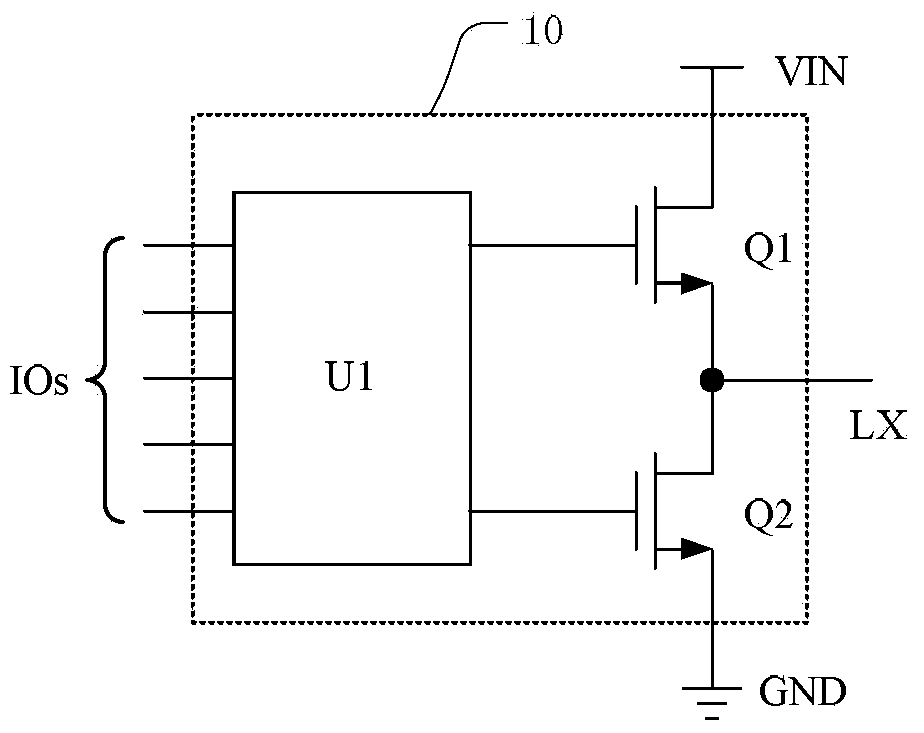

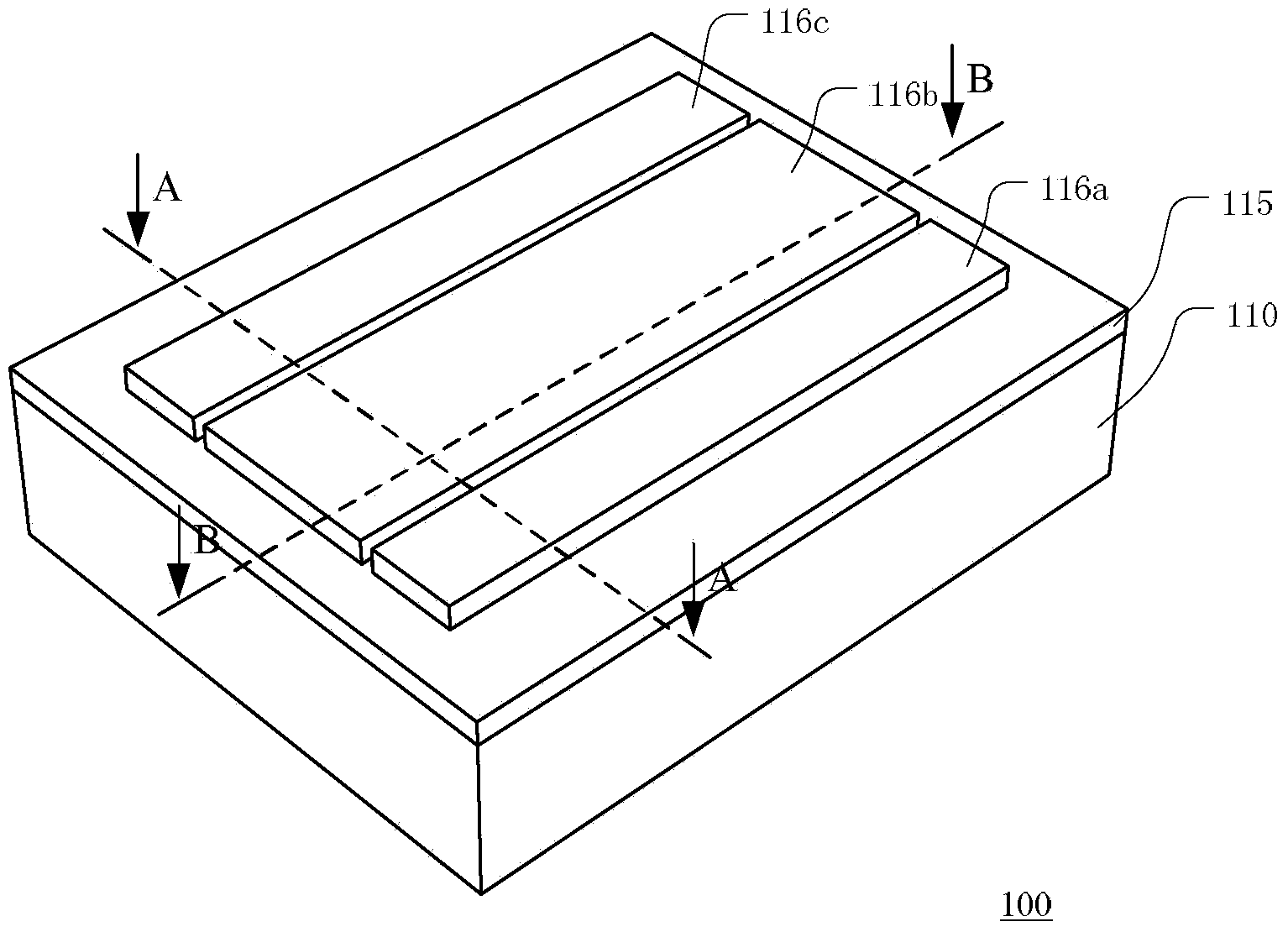

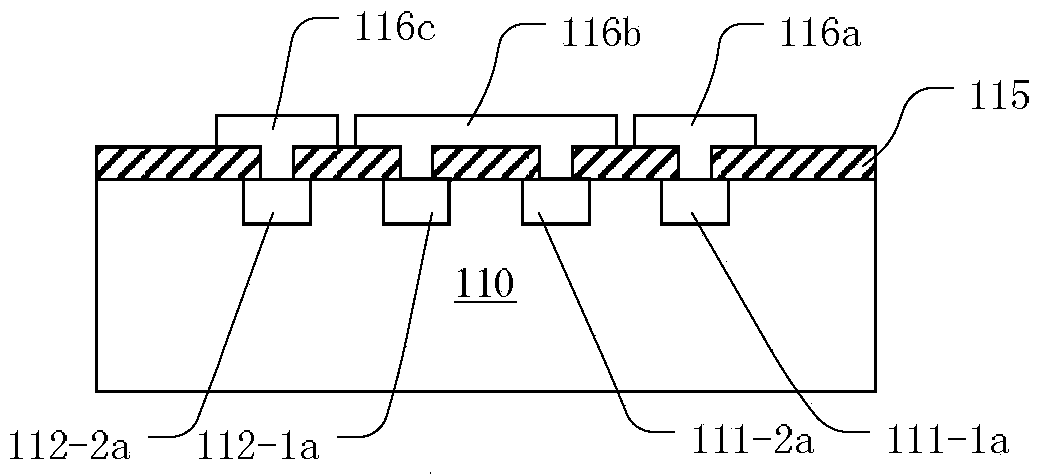

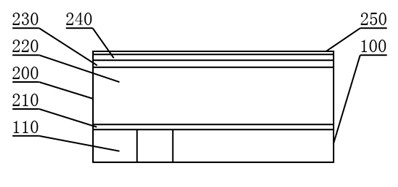

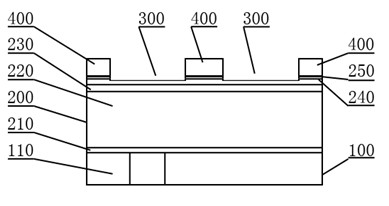

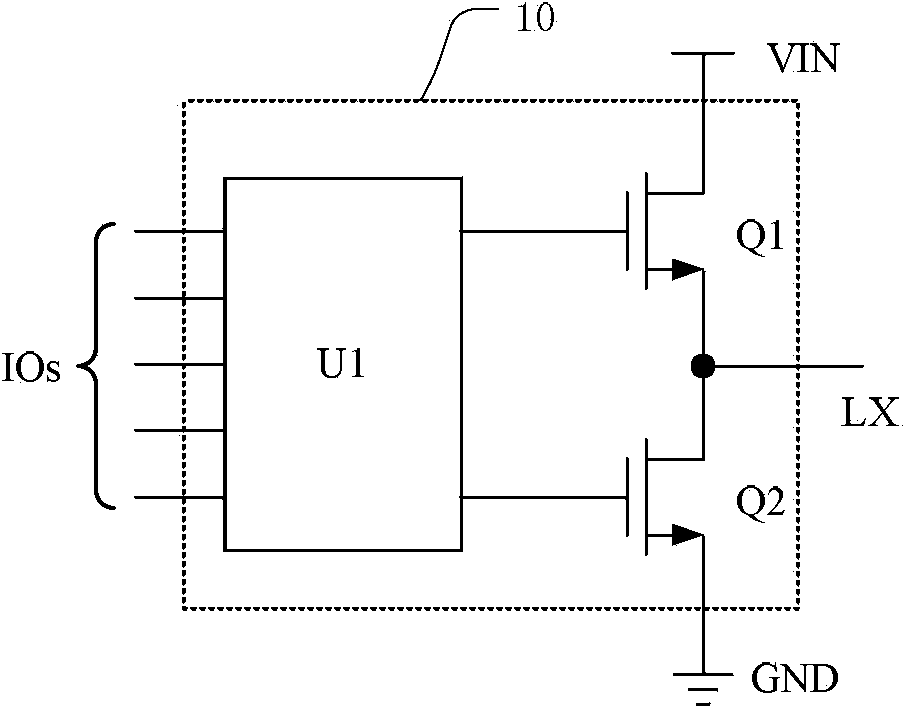

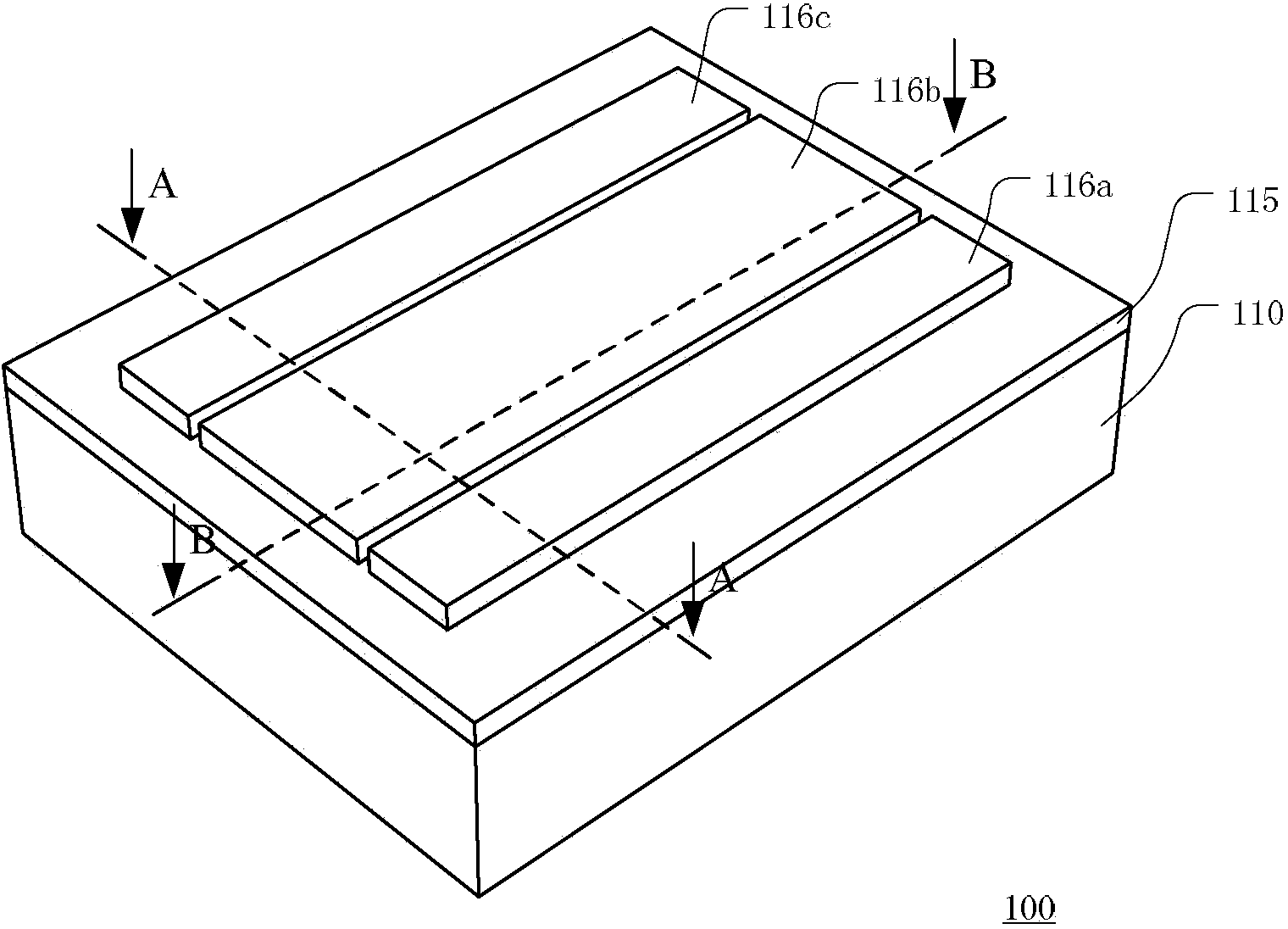

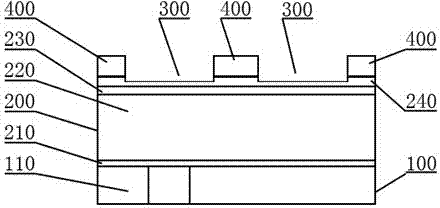

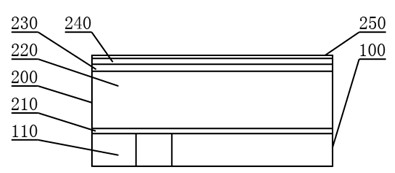

Integrated circuit module and packaging assembly thereof

ActiveCN103985694ASimple designAchieve standardizationSemiconductor/solid-state device detailsSolid-state devicesInsulation layerElectrical polarity

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

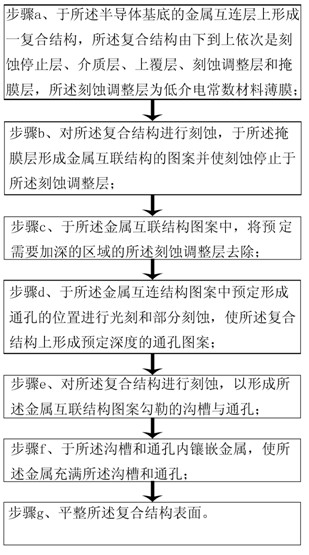

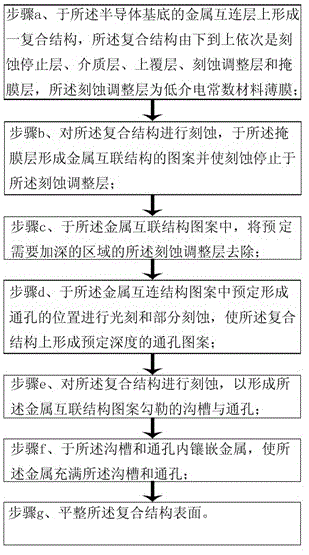

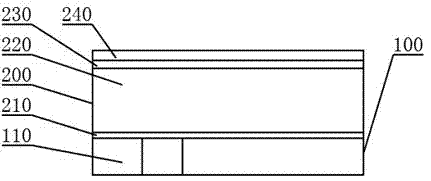

Method for achieving high-performance copper interconnection by utilizing upper mask

ActiveCN102446843ALower resistanceLower interconnect resistanceSemiconductor/solid-state device manufacturingCopper interconnectMetal interconnect

The invention discloses a method for achieving high-performance copper interconnection by utilizing an upper mask. The method is characterized in that a semiconductor substrate with a metal interconnection layer is arranged, wherein a composite structure is formed on the metal interconnection layer of the semiconductor substrate and comprises an etch stop layer, a dielectric layer, an upper coating, an etch adjustment layer and a mask layer from bottom to top in sequence; and the etch adjustment layer is made of a low dielectric constant material film. The invention has the following beneficial effects: through the process flow and method disclosed by the invention, the added low dielectric constant material etch depth adjustment layer is utilized to selectively change the depth of the grooves of copper interconnection lines, thus reducing the square resistance of the copper interconnection lines which conform to the conditions and are arranged in the specific region, and further achieving the aim of selectively reducing the chip interconnection resistance; and by utilizing the method, the interconnection resistance can be furthest reduced on the premises of not changing the overall copper interconnection depth, not increasing the process difficulty and not reducing the process window, thus reducing the signal delay of the chips, reducing the losses and improving the overall performance of the chips.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Integrated circuit module

InactiveCN103824838ASimple designAchieve standardizationSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceElectrical polarity

The invention discloses an integrated circuit module which comprises a semiconductor unpacked chip, a first insulating layer and power buses with the number of i, wherein the semiconductor unpacked chip comprises a plurality of electronic devices which are divided into m groups; each electronic device comprises electrodes with the number of n, wherein the electrodes have different polarities, and m and n are integers which are more than 1; the first insulating layer is arranged above the surface of the semiconductor unpacked chip; the power buses with the number of i are respectively arranged at a plane extending part on the first insulating layer and a plurality of vertical channel parts of the electrodes passing through a first insulating layer connector, wherein i is an integer which is more than 1 and less than or equal to m*n; at least one of the power buses with the number of i is used for electrically connecting the electrodes of at least two electronic devices; and all the power buses with the number of i are respectively taken as an external connection terminal. After the integrated circuit module is adopted, a lead frame of a finger-shaped pin can be avoided being used, so that the design of the lead frame is simplified, an interconnection resistor is reduced, and the heat dissipation is improved.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

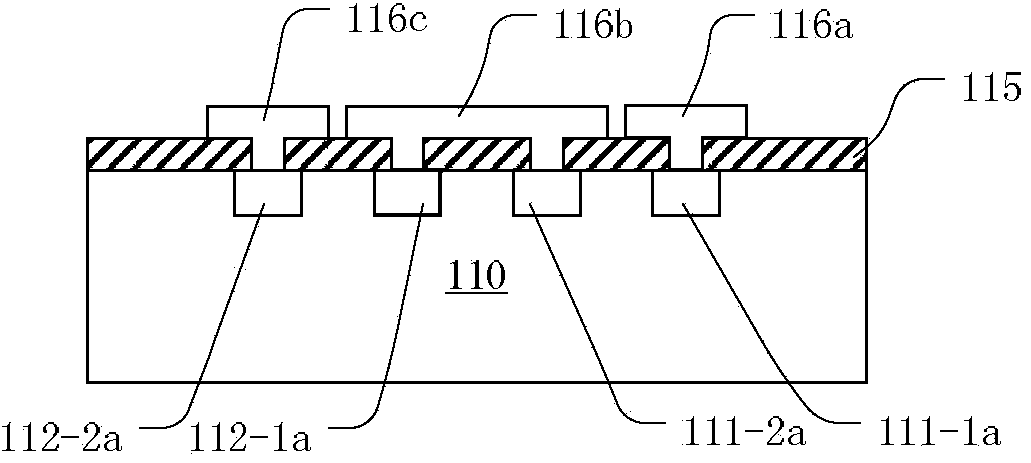

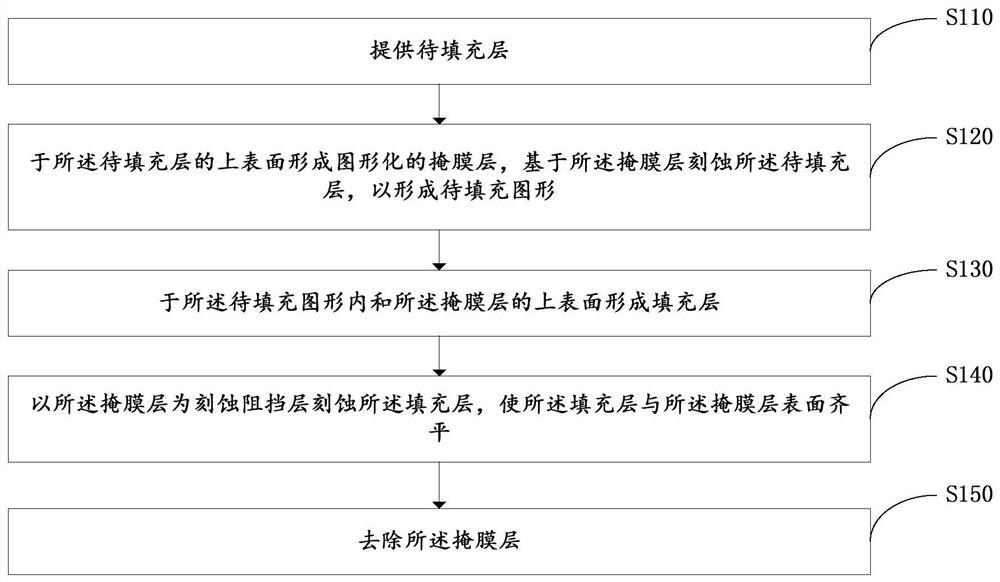

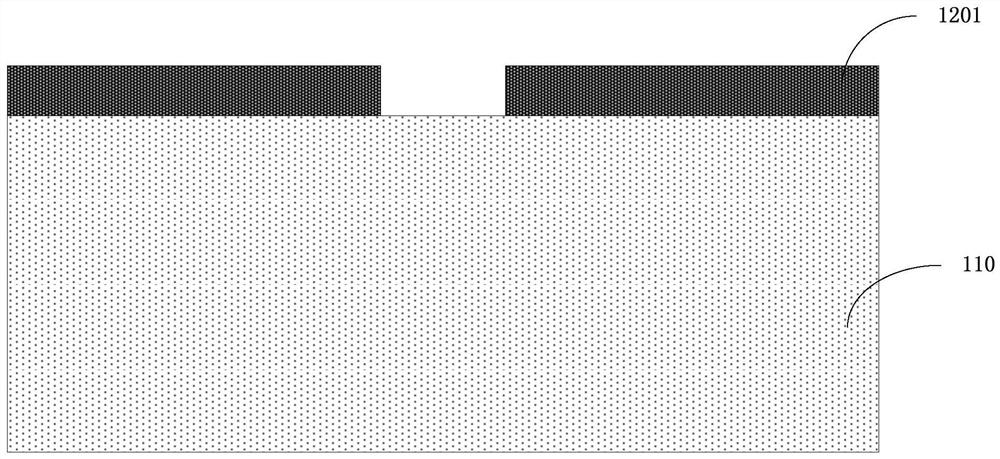

Semiconductor device and preparation method thereof

PendingCN113380699AAvoid defectsSmall mean free pathSemiconductor/solid-state device detailsSolid-state devicesDevice materialMaterials science

The invention discloses a semiconductor device and a preparation method thereof. The preparation method of the semiconductor device comprises the following steps: providing a to-be-filled layer; forming a patterned mask layer on the upper surface of the to-be-filled layer, and etching the to-be-filled layer based on the mask layer to form a to-be-filled pattern; forming a filling layer in the to-be-filled pattern and on the upper surface of the mask layer; etching the filling layer by taking the mask layer as an etching barrier layer, so that the filling layer is flush with the surface of the mask layer; and removing the mask layer. The mask layer is used as the etching barrier layer to etch the filling layer, so that the filling layer is flush with the surface of the mask layer, the redundant filling layer can be prevented from being removed in a mechanical mode, and defects are avoided.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Interconnection structure of semiconductors and formation method

ActiveCN103187395ANo relative misalignmentHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureInterconnection

The invention discloses an interconnection structure of semiconductors and a formation method. The interconnection structure of the semiconductors comprises a metal interconnecting layer including a metal layer and a first metal protrusion connected with the edges of the metal layer and a conductive plug arranged on the surface of the first metal protrusion, wherein the distance between the conductive plug and the point of the first metal protrusion is larger than the minimum design size. When the temperature of the semiconductor interconnection structure drops from high manufacturing technique temperature to room temperature, the portions, corresponding to the parts from the conductive plug to the point of the first metal protrusion and from the conductive plug to the metal edge, of the first metal protrusion shrink, produced stresses are cancelled out, and thus the positions of the conductive plug and the metal protrusion do not missed relatively, and no gaps are formed at the contacting position of the conductive plug and the metal protrusion.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A Method of Realizing High Performance Copper Interconnection Using Upper Mask

ActiveCN102446843BLower resistanceLower interconnect resistanceSemiconductor/solid-state device manufacturingCopper interconnectMetal interconnect

The invention discloses a method for realizing high-performance copper interconnection by using an upper mask, comprising a semiconductor substrate with a metal interconnection layer, wherein a composite structure is formed on the metal interconnection layer of the semiconductor substrate from bottom to top The etching stop layer, the dielectric layer, the overlying layer, the etching adjustment layer and the mask layer are in sequence, and the etching adjustment layer is a thin film of low dielectric constant material. The beneficial effects of the present invention are: through the technological process and method of the present invention, the added low dielectric constant material is used to etch the depth adjustment layer, and the depth of the copper interconnection groove is selectively changed, so that the qualified specific The square resistance of the copper interconnection wires in the area is reduced, thereby achieving the purpose of selectively reducing the interconnection resistance of the chip. Through the application of the present invention, the interconnection resistance can be reduced to the greatest extent without changing the overall copper interconnection depth, without increasing the difficulty of the process, and without narrowing the process window, thereby reducing the signal delay of the chip, reducing loss, and improving the overall performance of the chip. performance.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

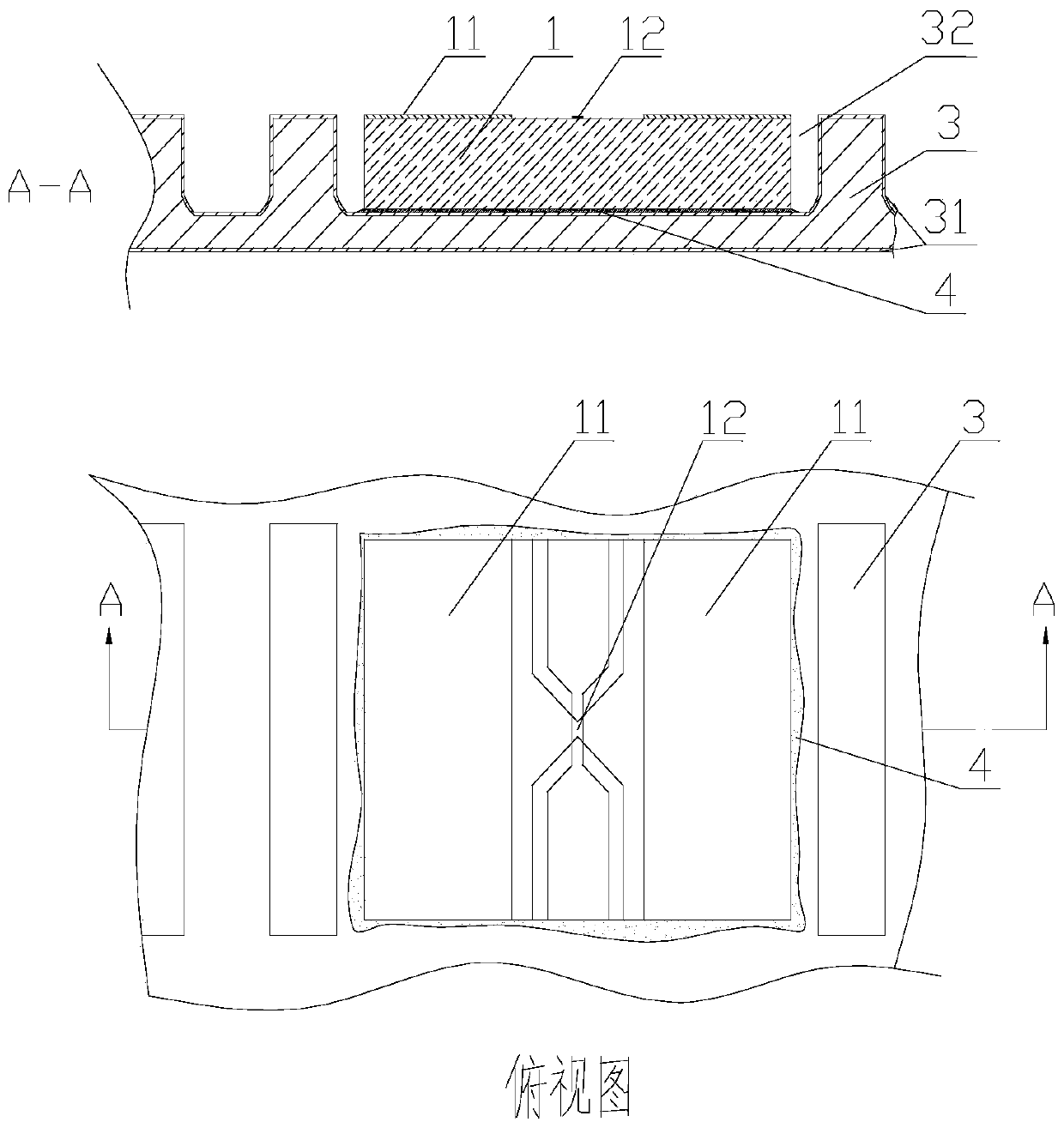

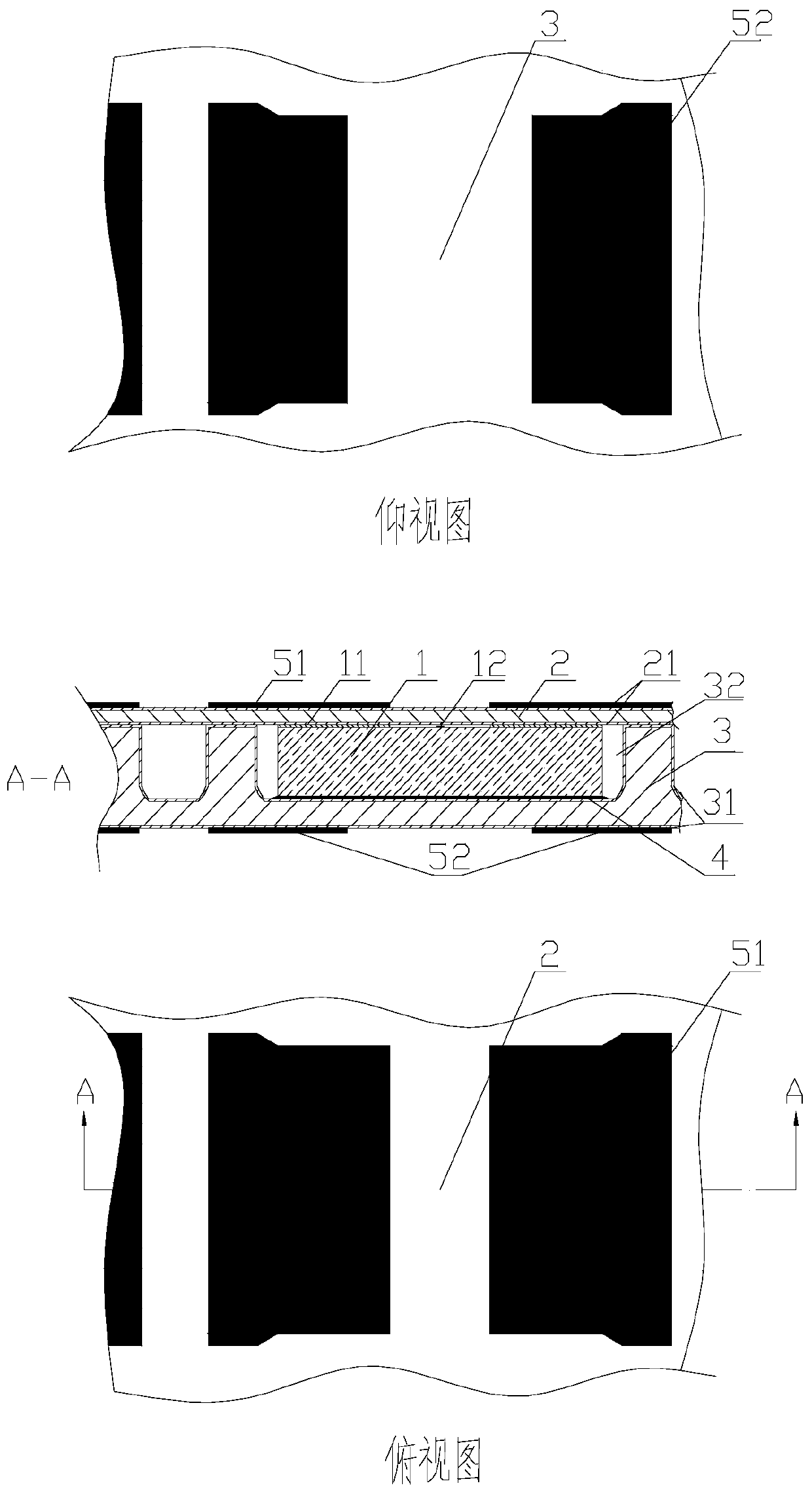

A Surface Mount Type Semiconductor Resistance Bridge Package Structure

ActiveCN108447632BPackage structure is simpleSimple structureResistor terminals/electrodesSemiconductor/solid-state device detailsEpoxySurface mounting

The invention discloses a surface mounting type semiconductor resistance bridge encapsulation structure. The encapsulation structure comprises a semiconductor resistance bridge chip, three layers of metal electrodes and an insulating glue layer; two leading end bonding pads of the semiconductor resistance bridge chip respectively have a solder plating coating layer; and every metal electrode has asolder plating coating layer. The leading end bonding pads of the semiconductor resistance bridge chip and the top metal electrode are thermocompression-bonded through the solder plating coating layers, the top metal electrode and the top metal electrode are thermocompression-bonded through the solder plating coating layers, and the middle metal electrode and the bottom metal electrode are thermocompression-bonded through the solder plating coating layers; and the semiconductor resistance bridge chip and the bottom metal electrode are bond-reinforced through epoxy and other insulating glues.The encapsulation structure uses the molded metal plate thermocompression-bonded structure with three solder plating coating layers to substitute substrate and chip bonding, metal leading wire bondingand encapsulation structure in the semiconductor resistance bridge, so the encapsulation structure has the advantages of simple structure, low encapsulation interconnection resistance, thinness in encapsulation, few encapsulation process steps, small device investment, and is suitable for thin and standardized surface mounting, low-cost and high-reliability requirements of the semiconductor resistance bridges in automobile airbags, automobile emergency hammers and digital electronic detonators.

Owner:JACAL ELECTRONICS WUXI

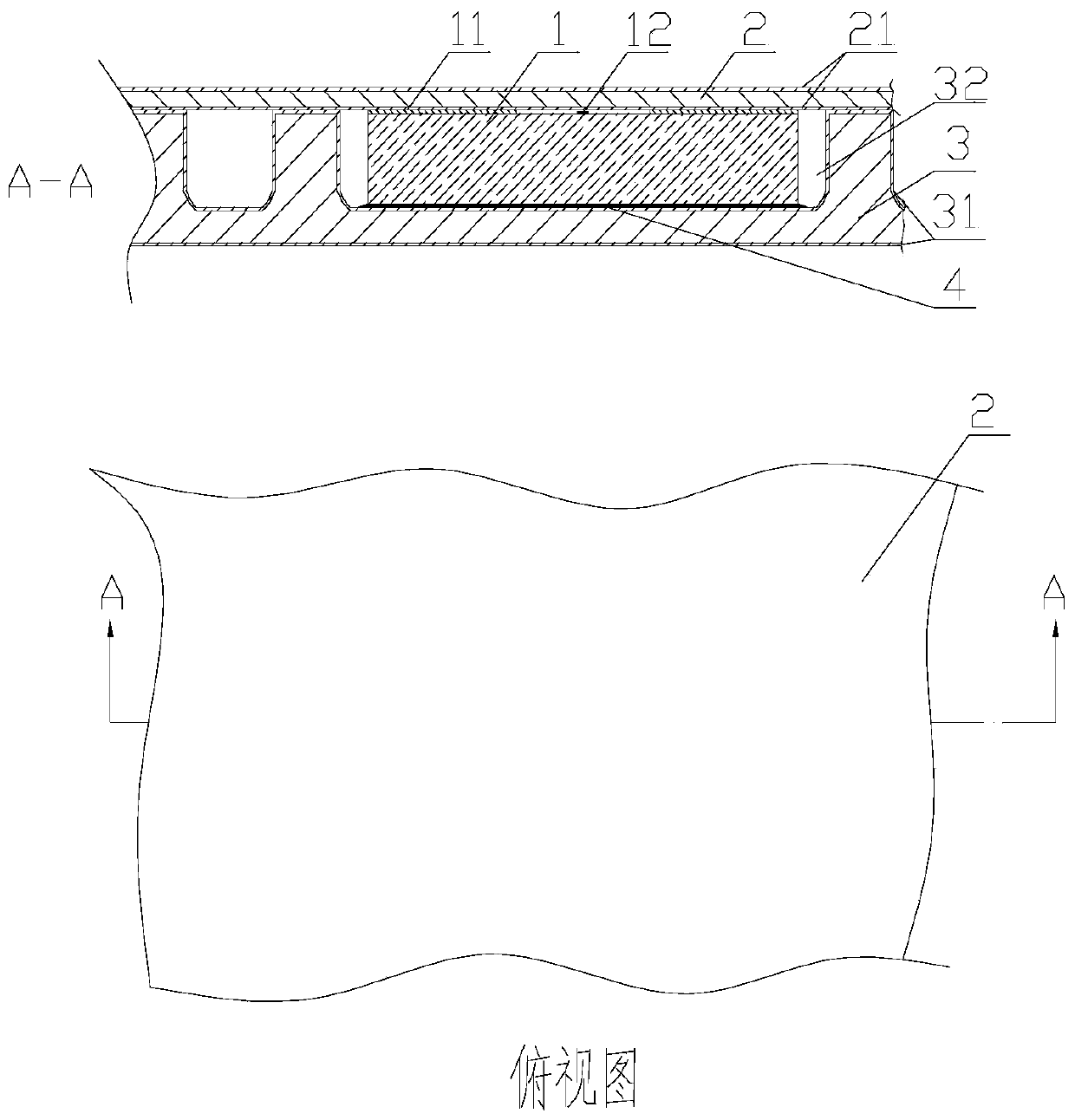

A semiconductor resistance bridge packaging structure and process

ActiveCN108447840BPackage structure is simpleThin packageSemiconductor/solid-state device detailsSolid-state devicesEtchingMetallic electrode

The invention discloses a semiconductor resistance bridge packaging structure and process. The packaging structure is a two-layer structure, and comprises a semiconductor resistance bridge chip, two welding pieces, two electrodes and a layer of reinforcing insulation glue. The two leading-out terminal soldering pads of the semiconductor resistance bridge chip are subjected to sputtering, evaporation and other processes to form solder layers; the copper or copper alloy plate with a certain thickness is etched out of the core cavity through a wet-process semi-etching process, and the solder layers are plated thereon, the semiconductor resistance bridge chip is bonded in the core cavity of the semiconductor resistance bridge chip through the insulating glue, the large board soldering pieces with the solder layers and the two leading-out terminal soldering pads of the resistance bridge chip are welded to the electrodes through heating and pressurizing; a photoresist coats on the surface after the welding and an etching region is exposed and developed; etching is carried out in the wet etching liquid, so that the large board soldering pieces and the semi-etching large boards are disconnected to form two soldering pieces and two electrodes of the semiconductor resistance bridge; finally, the photoresist film, is removed and the product is obtained by inspection and testing. The packaging structure is of a two-layer structure, the packaging structure is simple, the interconnection resistance of the packaging structure is lower, and the external impact resistance is stronger; andthe metal wire bonding, encapsulation and cutting and packaging processes in the semiconductor resistance bridge packaging are replaced by a wet etching process and a heating and pressurizing weldingprocess, so that the packaging efficiency is higher.

Owner:JACAL ELECTRONICS WUXI

A semiconductor structure with redistribution layer and its manufacturing method

ActiveCN104659015BHighly integratedImprove layout flexibilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

The invention discloses a semiconductor structure with a heavy wiring layer and a manufacturing method thereof. The semiconductor structure with the heavy wiring layer comprises a chip with an active surface, a first connecting pad and a second connecting pad which are positioned on the active surface, a passivation layer positioned on the active surface, and the heavy wiring layer positioned on the passivation layer, wherein the heavy wiring layer is electrically connected with the first connecting pad and the second connecting pad which are used for educing electrodes of an element inside the chip, and a part of the second connecting pad is exposed as an interconnecting welding area for achieving interconnection with the outside so as to enable an interconnecting welding area originally at the first connecting pad of the chip to be rearranged at the exposed second connecting pad and directly used as the interconnecting welding area, so that the integration degree and the layout flexibility of the chip are improved and the interconnecting resistance during chip packaging is reduced; the semiconductor structure with the heavy wiring layer is relatively simple, so that reduction in manufacturing processes and reduction in production cost are facilitated.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

Method for realizing high-performance copper interconnection by upper mask

ActiveCN102456618ALower resistanceReduce signal delaySemiconductor/solid-state device manufacturingCopper interconnectMetal interconnect

The invention discloses a method for realizing a high-performance copper interconnection by an upper mask, comprising a semiconductor substrate with a metal interconnection layer, wherein a compound structure is formed on the metal interconnection layer of the semiconductor substrate, and orderly comprises an etching stop layer, a dielectric layer, an overlying layer and a mask layer from bottom to top. The method for realizing a high-performance copper interconnection by an upper mask disclosed by the invention has the following advantage that: via the technique process and method disclosed by the invention, an added titanium nitride metal hard mask is used as an etching depth adjustment layer for selectively changing the depth of the ditch of a copper interconnection line, so as to reduce the square resistance of the copper interconnection line in a specific area satisfying conditions, thereby realizing a purpose of selectively reducing a chip interconnection resistance. Via the application of the method disclosed by the invention, the interconnection resistance can be furthest reduced on the premise that the whole copper interconnection depth is not changed, the technique difficulty is not increased, and the technique window is not reduced, thereby reducing the signal delay of a chip, reducing loss, and improving the whole performance of the chip.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A Wire Bonding Method Based on Rapid Local Electrodeposition

ActiveCN108054108BImprove conductivityBroaden your optionsSolid-state devicesSemiconductor/solid-state device manufacturingElectricityLead bonding

The invention relates to a wire bonding method based on rapid local electrodeposition, which belongs to the technical field of wire connection. The method is as follows: select the new lead material to be bonded and modify it; place the lead material on the surface of the pad through the micro-nano operation platform to ensure good contact between the lead and the surface of the pad; select local electrodeposition The caliber of the precision pipetting dripping tube and the type of anode metal in the dripping tube ensure good contact between the probe at the cathode end of the electroplating and the pad; a metal coating that completely covers the lead material is formed on the surface of the pad by a local electrodeposition method; all soldering is completed After electrodeposition and wire bonding on the pad surface, the overall device is cleaned. Compared with the traditional wire bonding process, the present invention can realize reliable wire bonding of new lead materials. The whole bonding process does not require heating connection, no thermal damage and mechanical damage, simple process flow, fast bonding speed, and is suitable for various The pad material and the connection layer metal have a wide range of options, etc.

Owner:HARBIN INST OF TECH

Metal diffusion barrier layer structure and forming method thereof

PendingCN112133675ALower interconnect resistanceReduce thicknessSemiconductor/solid-state device manufacturingElectrical resistance and conductanceCopper wire

The invention discloses a metal diffusion barrier layer structure. The metal diffusion barrier layer structure comprises an adhesion layer, a molybdenum disulfide barrier layer, a seed crystal layer and a wire layer which are sequentially formed in a groove or a hole from outside to inside, wherein the molybdenum disulfide barrier layer is formed by permeating sulfur into the copper-molybdenum alloy seed crystal layer and reacting the sulfur with molybdenum in the copper-molybdenum alloy seed crystal layer. The three-dimensional molybdenum disulfide layer is used for replacing traditional tantalum nitride to serve as the metal diffusion barrier layer, the thickness of the barrier layer can be greatly reduced, the proportion of wire metal is increased, good electrical conductivity is achieved, and therefore the metal interconnection resistance can be greatly reduced on the whole, the electromigration resistance of the copper wire is improved, and the problems of groove coverage rate, process compatibility and the like due to introduction of a two-dimensional material in a subsequent process are effectively solved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

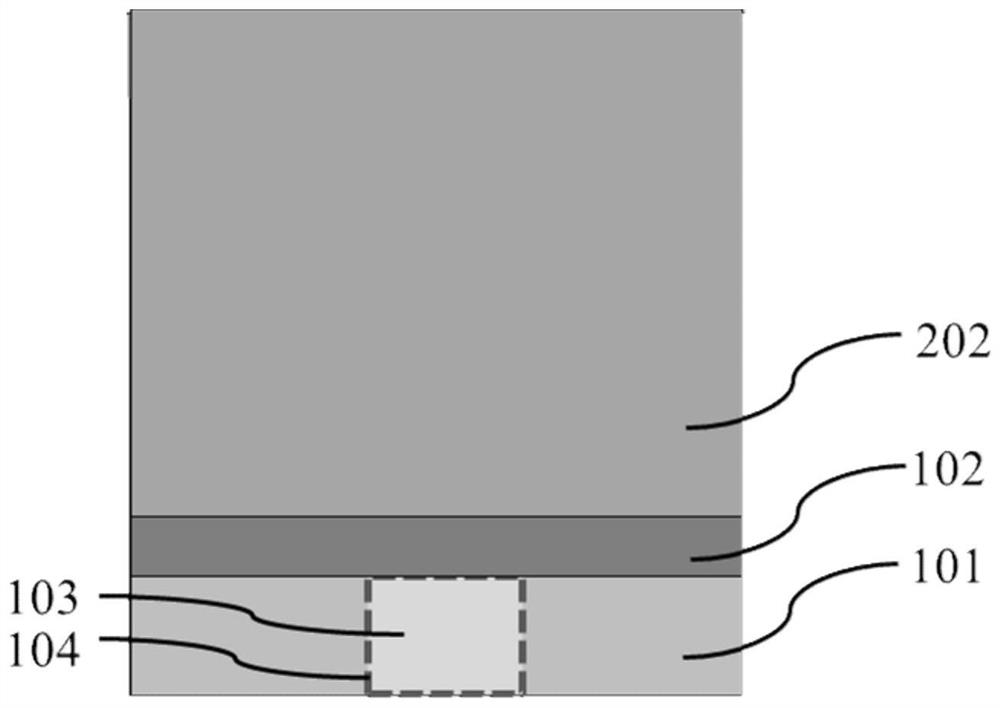

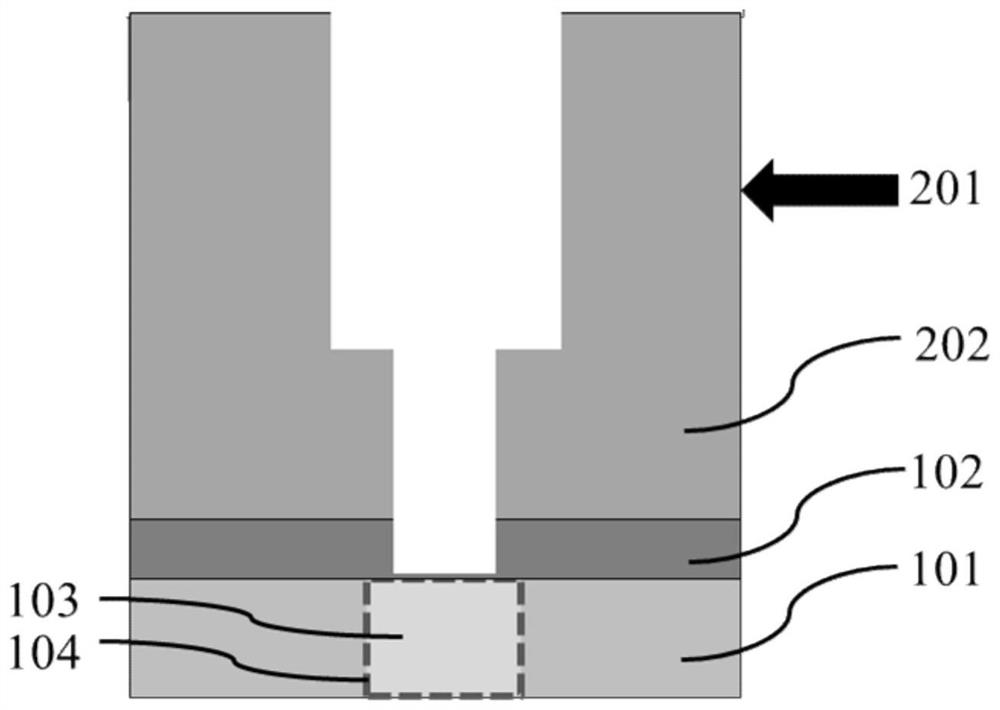

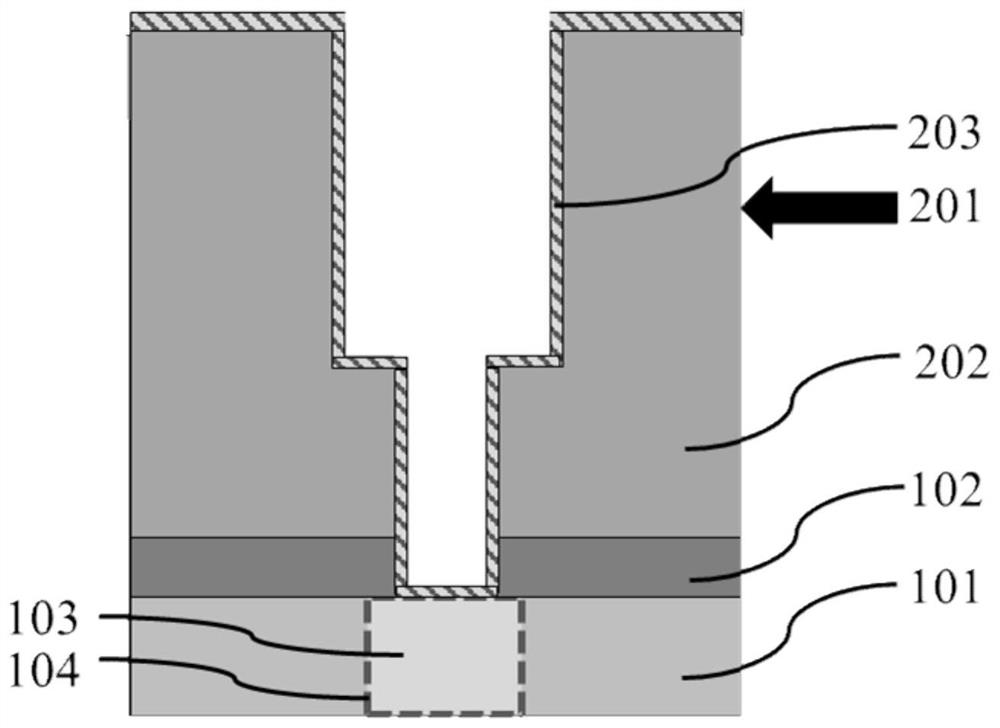

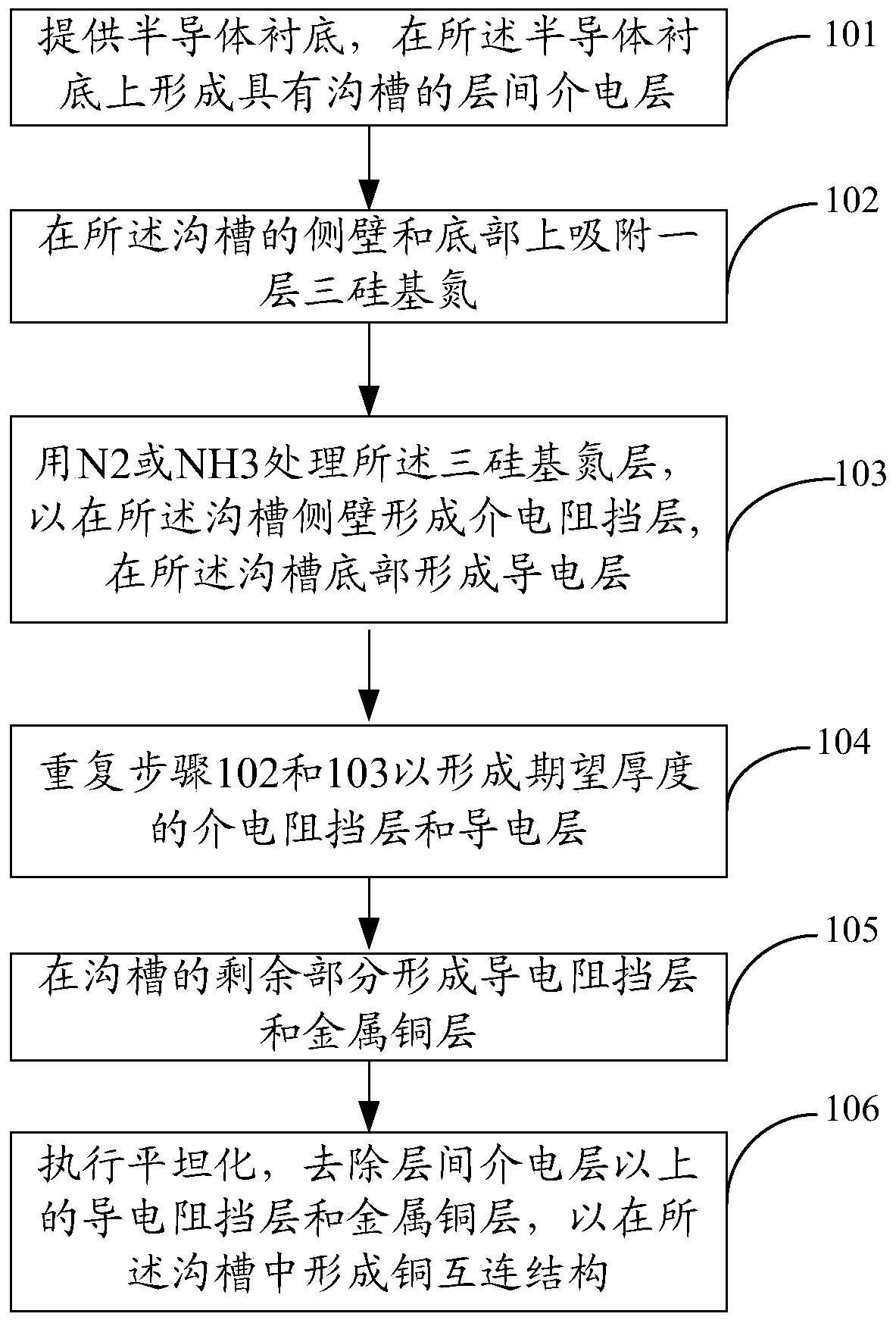

Manufacturing method of copper interconnection structure, copper interconnection structure and electronic device

ActiveCN106505031BPrevent proliferationReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDielectric layer

The invention provides a copper interconnection structure manufacturing method, copper interconnection structure and electronic device wherein the manufacturing method comprises: providing a semiconductor substrate; forming on the semiconductor substrate an interlayer dielectric layer with groove; forming on the side wall of the groove a dielectric barrier layer; forming on the dielectric barrier layer a conductive barrier layer; and filling copper into the remaining part of the groove to form the copper interconnection structure. According to the copper interconnection structure manufacturing method provided by the invention, through the use of two barrier layers of the dielectric barrier layer and the conductive barrier layer, it is possible to ensure certain resistance capability and prevent copper from spreading to the dielectric barrier layer; and at the same time, it is possible to properly reduce the thickness of the conductive barrier layer so that the thickness of the copper layer for interconnection is increased in relative, therefore, further reducing the interconnection resistance and increasing the optical performance of a component.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for realizing high-performance copper interconnection by using upper mask

InactiveCN102569177ALower resistanceReduce signal delaySemiconductor/solid-state device manufacturingCopper interconnectMetal interconnect

The invention discloses a method for realizing high-performance copper interconnection by using an upper mask. The upper mask comprises a semiconductor substrate with a metal interconnecting layer, wherein a composite structure is formed on the metal interconnecting layer of the semiconductor substrate; the composite structure consists of an etching stop layer, a medium layer, an upper coating layer, an etching adjusting layer and a mask layer from bottom to top; and the etching adjusting layer is a silicon oxide thin film. The method has the advantages that: according to the technical flow and the method provided by the invention, the depth of a copper interconnecting line ditch is selectively changed by using the added silicon oxide to etch a depth-adjusting layer, so the square resistance of a copper interconnecting line which is in accordance with a condition in a specific area is reduced, and the aim of selectively reducing chip interconnecting resistance is fulfilled. According to the application of the method, the interconnecting resistance can be reduced to the great extent on the premise that the overall copper interconnection depth is not changed, the process difficulty is not increased, and the size of a technical window is not reduced, the signal delay of a chip is reduced, the loss is reduced, and the overall performance of a chip is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Multilayer interconnection packaging structure of silica-based embedded microwave multi chip module and manufacturing method

InactiveCN101656244BRealize planar interconnectionRealize multilayer interconnect structureSemiconductor/solid-state device detailsSolid-state devicesLead bondingOrganic polymer

The invention provides a multilayer interconnection packaging structure of an embedded microwave multi chip with a silicon chip as a substrate and a manufacturing method. The invention is characterized by utilizing the low-cost silicone chip as the chip embedded substrate and using wire bonding and ball mounting technology to prepare gold bumps, realizing short-distance interconnection between microwave chips, using a low-k liquid or colloidal polymer as a dielectric layer, realizing the multilayer interconnection structure of a metal / organic polymer by combining wafer level processing technics such as photoetching, electroplating, chemical mechanical polishing and the like and realizing system integration of active and passive devices. The whole packaging structure has higher packaging integration and lower high-frequency transmission loss. The structure can effectively integrate varied function device units, reduce the interconnection loss among the devices and improve the properties of the whole module while improving the density and integration of packaging and reducing the cost of packaging.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

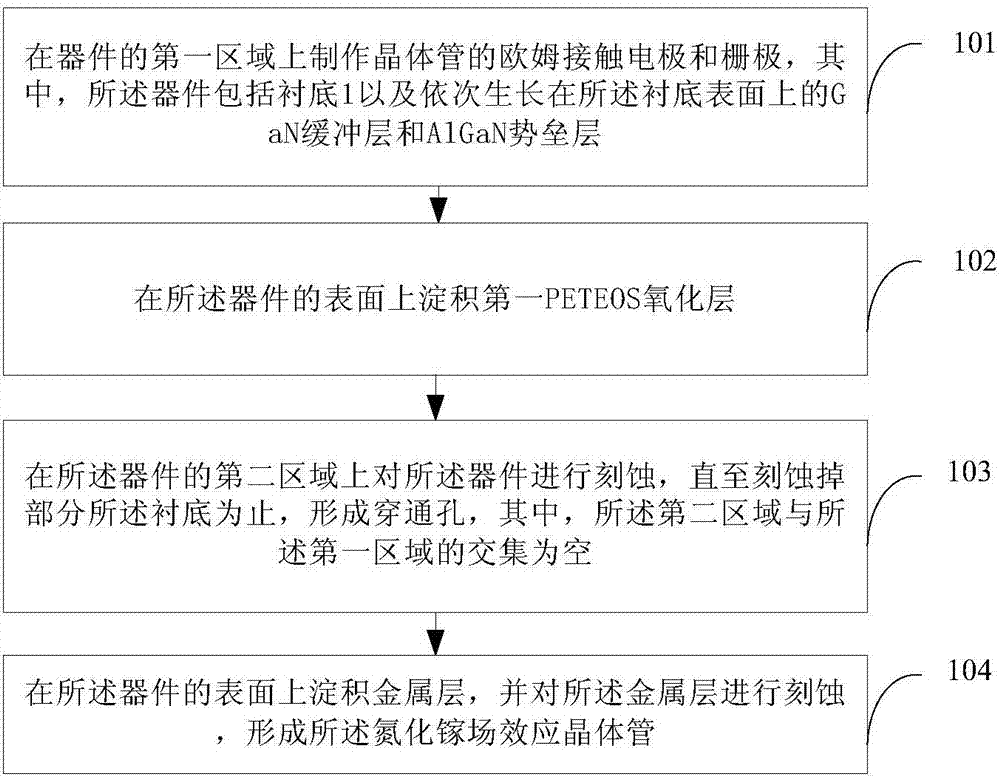

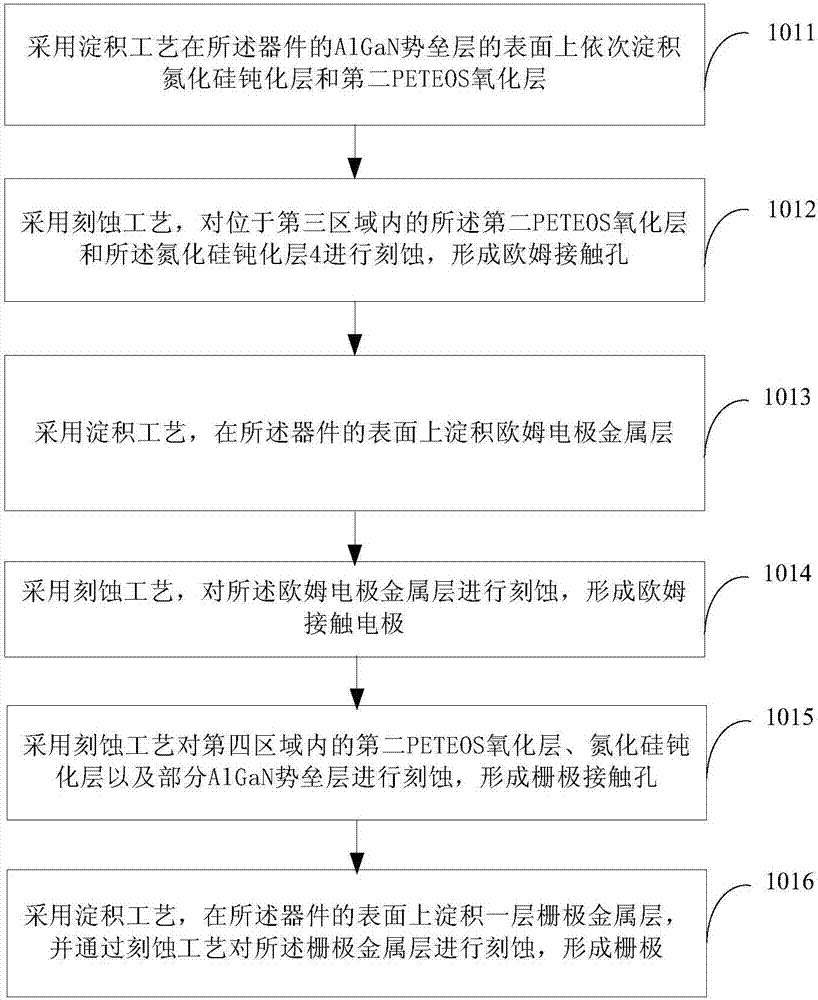

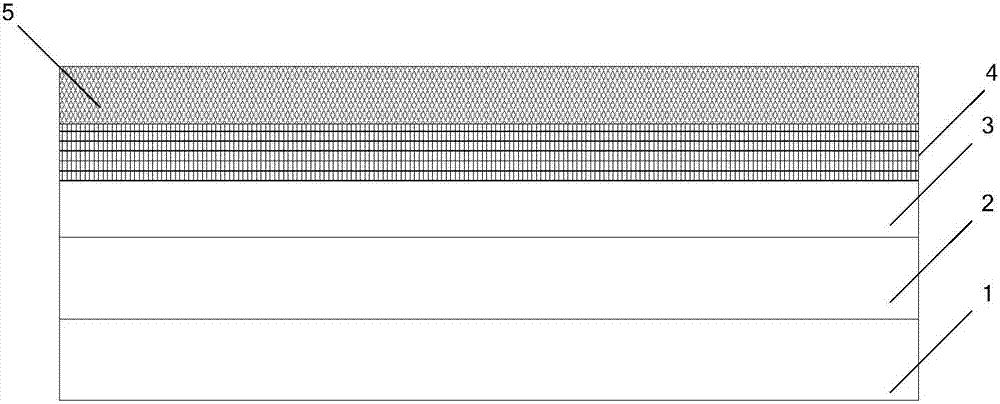

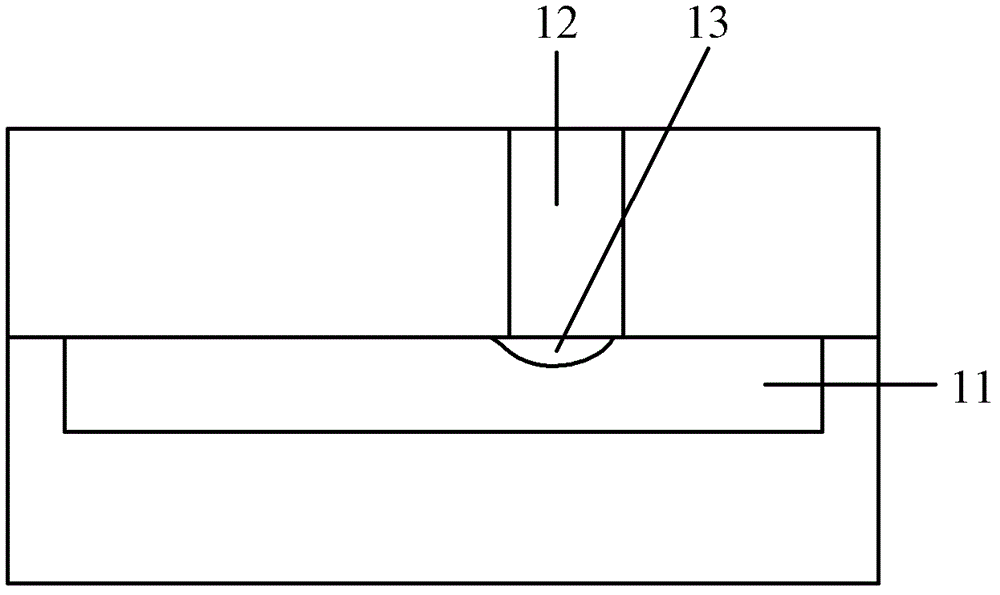

Method for manufacturing gallium nitride field effect transistor

InactiveCN107230630AImprove performanceEase the electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactInterconnection

The embodiment of the invention provides a manufacturing method of the gallium nitride field effect transistor, the method comprises the following steps: firstly, manufacturing an ohmic contact electrode and a grid electrode of a transistor on a first region of a device, wherein the device comprises a substrate and a GaN buffer layer and an AlGaN barrier layer which are sequentially grown on the surface of the substrate; depositing a first PETEOS oxide layer on the surface of the device; etching the device on a second region of the device until a part of the substrate is etched off to form a through hole, wherein the intersection of the second area and the first area is empty; and finally depositing a metal layer on the surface of the device, and etching the metal layer to form the gallium nitride field effect transistor. The electric field between the drain electrode and the grid electrode is relieved, the interconnection resistance and the parasitic inductance of the source electrode are reduced, and the performance of the gallium nitride field effect transistor is improved.

Owner:PEKING UNIV +2

Semiconductor interconnect structure and method of forming

ActiveCN103187395BNo relative misalignmentHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureInterconnection

The invention discloses an interconnection structure of semiconductors and a formation method. The interconnection structure of the semiconductors comprises a metal interconnecting layer including a metal layer and a first metal protrusion connected with the edges of the metal layer and a conductive plug arranged on the surface of the first metal protrusion, wherein the distance between the conductive plug and the point of the first metal protrusion is larger than the minimum design size. When the temperature of the semiconductor interconnection structure drops from high manufacturing technique temperature to room temperature, the portions, corresponding to the parts from the conductive plug to the point of the first metal protrusion and from the conductive plug to the metal edge, of the first metal protrusion shrink, produced stresses are cancelled out, and thus the positions of the conductive plug and the metal protrusion do not missed relatively, and no gaps are formed at the contacting position of the conductive plug and the metal protrusion.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Metal diffusion barrier layer structure and forming method thereof

PendingCN112133674AReduce thicknessLower self-resistanceSemiconductor/solid-state device manufacturingElectrical resistance and conductanceTantalum nitride

The invention discloses a metal diffusion barrier layer structure. The metal diffusion barrier layer structure sequentially comprises a first metal layer, a first graphene layer, a second metal layerand a second graphene layer which cover the inner wall surface of a groove or a hole, wherein the first graphene layer and the second graphene layer are respectively formed on the interfaces of the first metal layer and the second metal layer and the interfaces of the second metal layer and the third metal layer by injecting carbon into the second metal layer for doping and carrying out heat treatment so as to replace traditional tantalum nitride to be used as metal diffusion prevention layers, so that the thickness of the barrier layer can be greatly reduced; the proportion of the metal wirelayer on the conductive section is increased, the metal interconnection resistance can be greatly reduced on the whole, the electromigration resistance of the wire is improved, the process integrationis simple, and the method is compatible with the CMOS process. The invention further discloses a forming method of the metal diffusion barrier layer structure.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

Metal connecting structure, semiconductor device and its manufacturing method

ActiveCN100517640CSimple manufacturing processLower interconnect resistanceSemiconductor/solid-state device detailsSolid-state devicesCopperMedia layer

The invention discloses a manufacturing method of a metal connecting structure, which comprises that: a first medium layer is deposited on the surface of a semiconductor substrate; a second medium layer is deposited on the surface of the first medium layer; with the dual damascene technique, a copper dual-damascene connecting structure is formed between the first medium layer and the second medium layer. The method of the invention can reduce the resistance of the metal connecting structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1