Method for realizing high-performance copper interconnection by upper mask

A high-performance, copper interconnect technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to solve problems such as unfavorable etching process etched morphology and size, reduced interconnect reliability, and difficult to fully fill. , to achieve the effect of reducing chip interconnect resistance, increasing process difficulty, and reducing interconnect resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

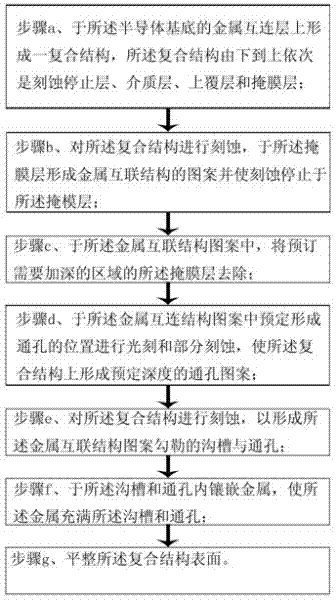

[0045] Such as figure 1 As shown, a method for realizing high-performance copper interconnection by using an upper mask in the present invention includes a semiconductor substrate 100 with a metal interconnection layer 110, and includes the following specific steps:

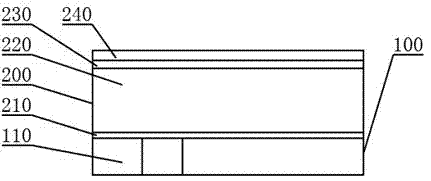

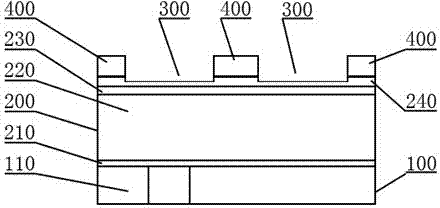

[0046] Such as figure 2 As shown, in step a, a composite structure 200 is formed on the metal interconnection layer 110 of the semiconductor substrate 100. The composite structure 200 includes an etch stop layer 210, a dielectric layer 220, an upper cladding layer 230 and a mask layer in sequence from bottom to top. 240.

[0047] Wherein the etching stop layer 210 is a nitrogen-doped silicon carbide layer, and its formation method can be chemical vapor deposition; the dielectric layer 220 can be fluorine-doped silicon oxide gla...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More