A Surface Mount Type Semiconductor Resistance Bridge Package Structure

A technology of packaging structure and resistance bridge, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, resistor shells/packaging shells/potting, etc. Consistency is poor and other problems, to achieve the effect of simple structure, fewer packaging process steps, and low interconnection resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0025] Embodiment: a kind of size is 2.00mm * 1.20mm * 0.50mm (1206 type) surface mounted semiconductor resistance bridge packaging structure:

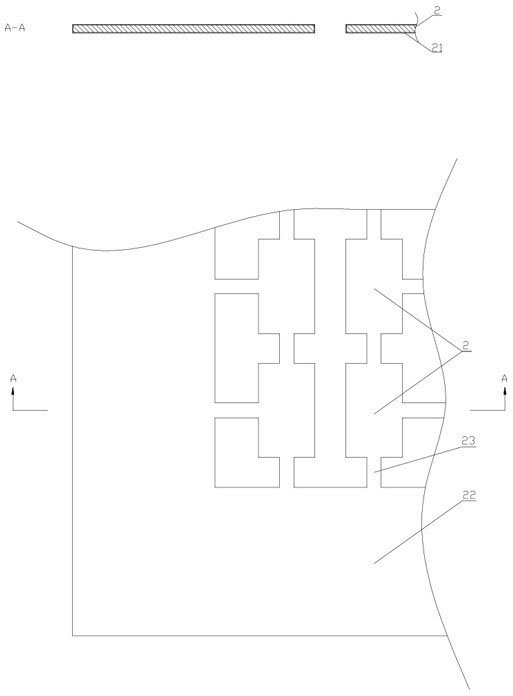

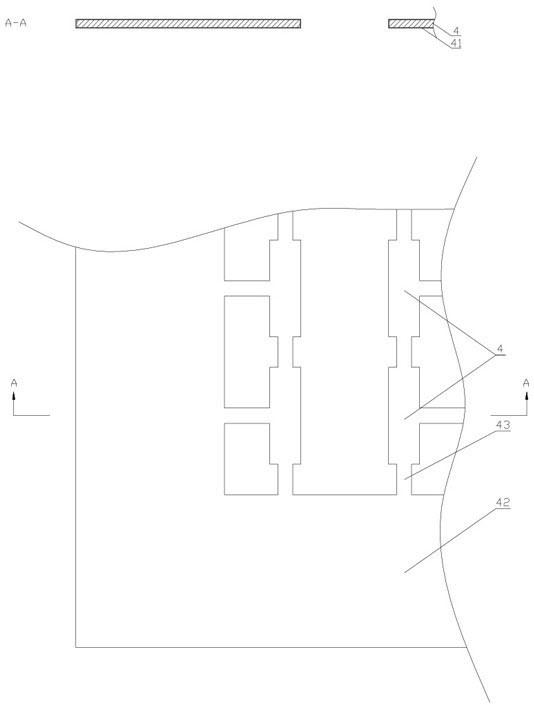

[0026] First, the metal electrode 2 and the metal electrode 4 are stamped or etched using a 100 μm thick C194 copper foil plated with (8±4) μm tin on the surface; the size of the metal electrode 2 is 1.25mm×0.80mm, such as figure 1 ; The size of the metal electrode 4 is 1.25mm × 0.40mm, such as image 3 ;

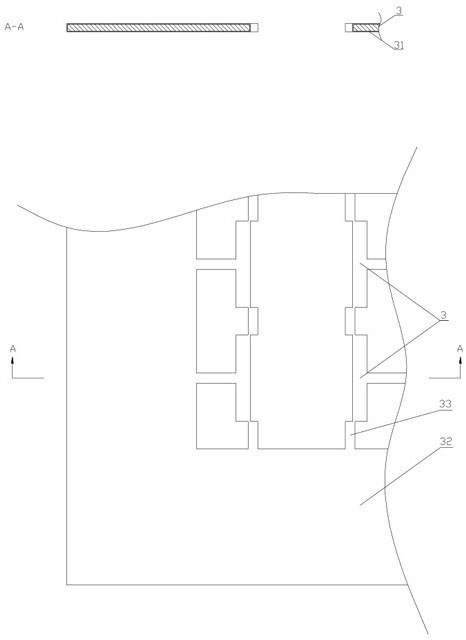

[0027] The metal electrode 3 is stamped or etched with a 300 μm thick C194 copper foil plated with (8±4) μm tin on the surface, and the size of the metal electrode 2 is 1.25mm×0.30mm, such as figure 2 .

[0028] Next, the middle layer metal electrode 3 is aligned and stacked on the bottom metal electrode 4, and a 300 μm thick 1.30mm×1.25mm semiconductor resistance bridge chip is loaded into the middle layer metal electrode 3, and then the top layer metal electrode 2 is aligned and stacked on it, and then Use a pressurized heat ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More