Manufacturing method of copper interconnection structure, copper interconnection structure and electronic device

A technology of copper interconnection structure and manufacturing method, which is applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of device electrical performance degradation, interconnection resistance increase, RC delay increase, etc., to improve electrical performance, Effect of Reducing Interconnect Resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

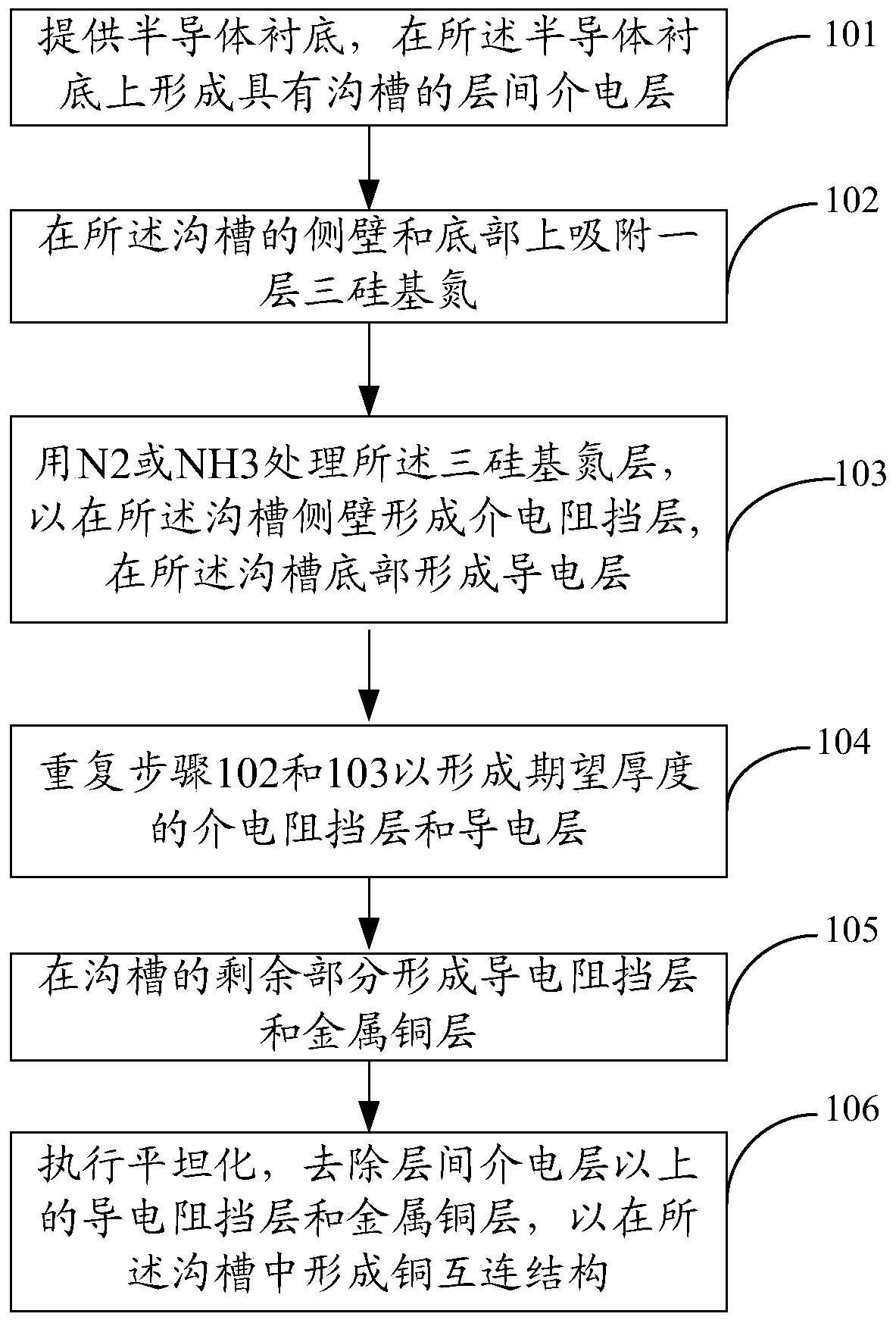

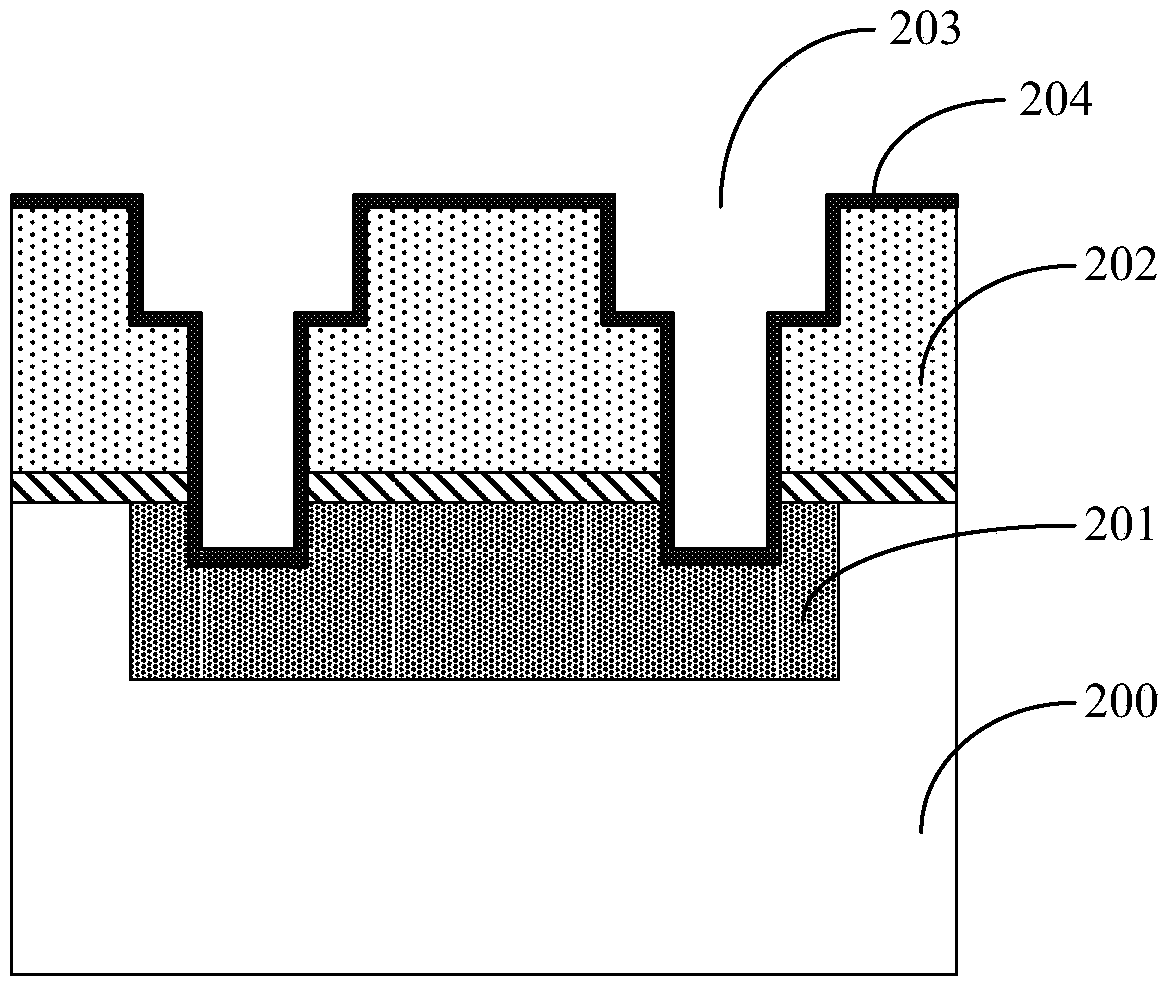

[0033] The following will refer to figure 1 as well as Figure 2A ~ Figure 2F A method for fabricating a copper interconnection structure according to an embodiment of the present invention is described in detail.

[0034] First, step S101 is performed to provide a semiconductor substrate on which an interlayer dielectric layer having a trench is formed.

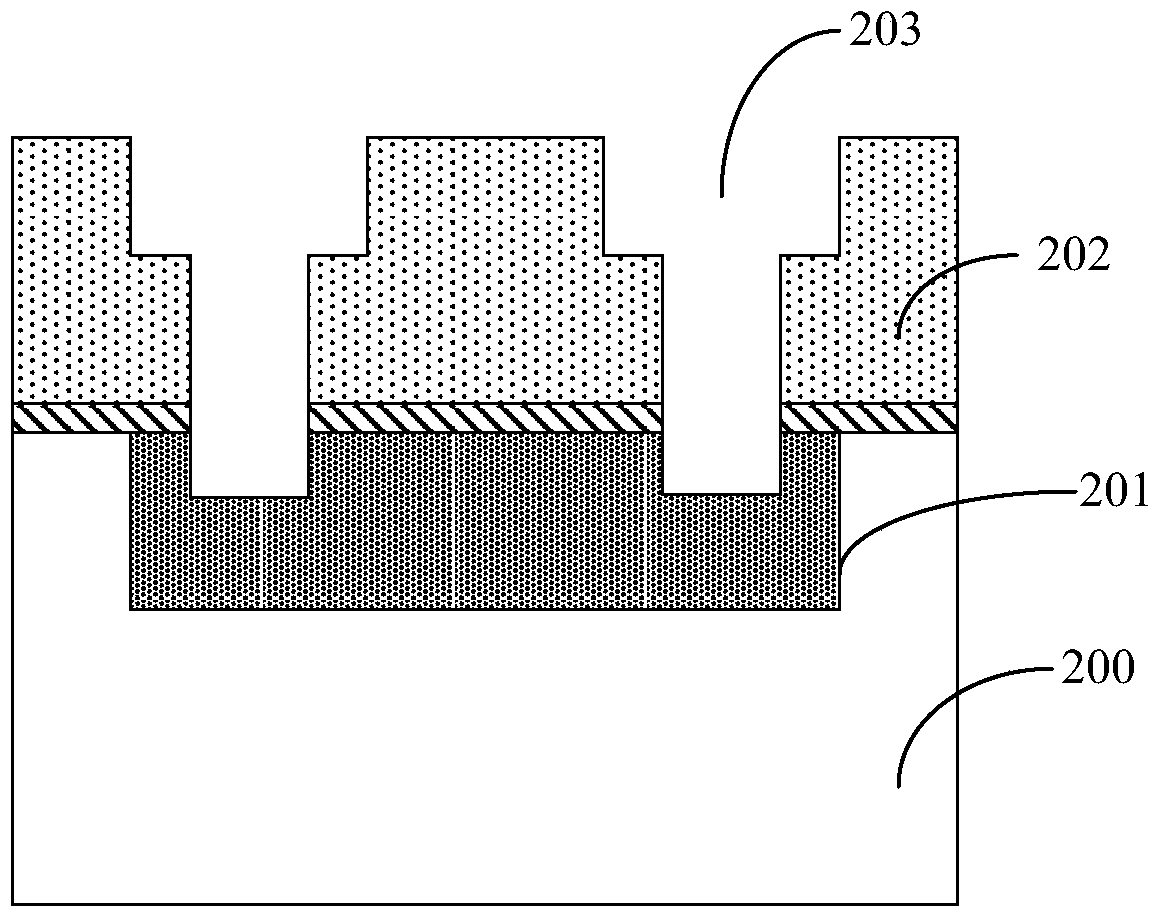

[0035] Such as Figure 2A As shown, a semiconductor substrate 200 is provided on which an interlayer dielectric layer 202 having a trench 203 is formed.

[0036]The semiconductor substrate 200 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multilayer structures composed of these semiconductors etc. or silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI), and germanium-on-insulator (GeOI). Devices, such as NMOS and / or PMOS, can be ...

Embodiment 2

[0050] The present invention also provides a semiconductor device manufactured by the method described in Embodiment 1 or 2, which includes: a semiconductor substrate 300, an interlayer dielectric layer 301 with a groove formed on the semiconductor substrate 300 , a dielectric barrier layer 302, a conductive barrier layer 303, and a copper layer 304 filling the remaining part of the trench are sequentially formed on the sidewall of the trench.

[0051] Wherein, the semiconductor substrate 300 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multiple semiconductors composed of these semiconductors. The layer structure or the like may be silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI), and germanium-on-insulator (GeOI). Devices, such as NMOS and / or PMOS, can be formed on the semiconduc...

Embodiment 3

[0055] The present invention further provides an electronic device including the aforementioned semiconductor device.

[0056] The electronic device also has the above-mentioned advantages due to the higher performance of the included semiconductor devices.

[0057] The electronic device can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV, VCD, DVD, navigator, camera, video camera, recording pen, MP3, MP4, PSP, etc. It is an intermediate product with the above-mentioned semiconductor device, for example: a mobile phone motherboard with the integrated circuit, etc.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More