A semiconductor resistance bridge packaging structure and process

A technology of packaging structure and resistance bridge, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of poor dimensional consistency, low packaging efficiency, high packaging cost, and achieve resistance to external shocks. Strong, simple packaging structure, high packaging efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

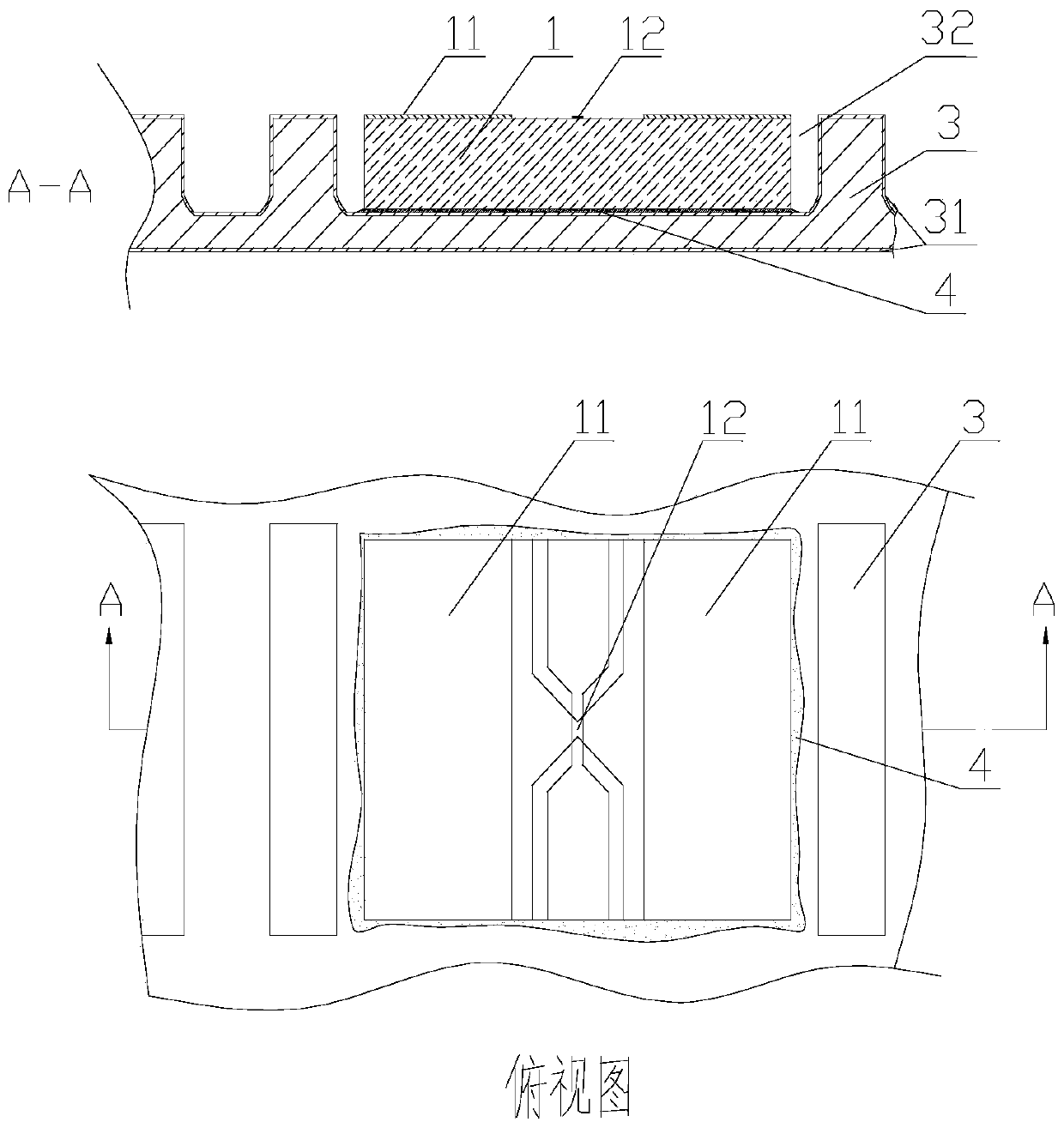

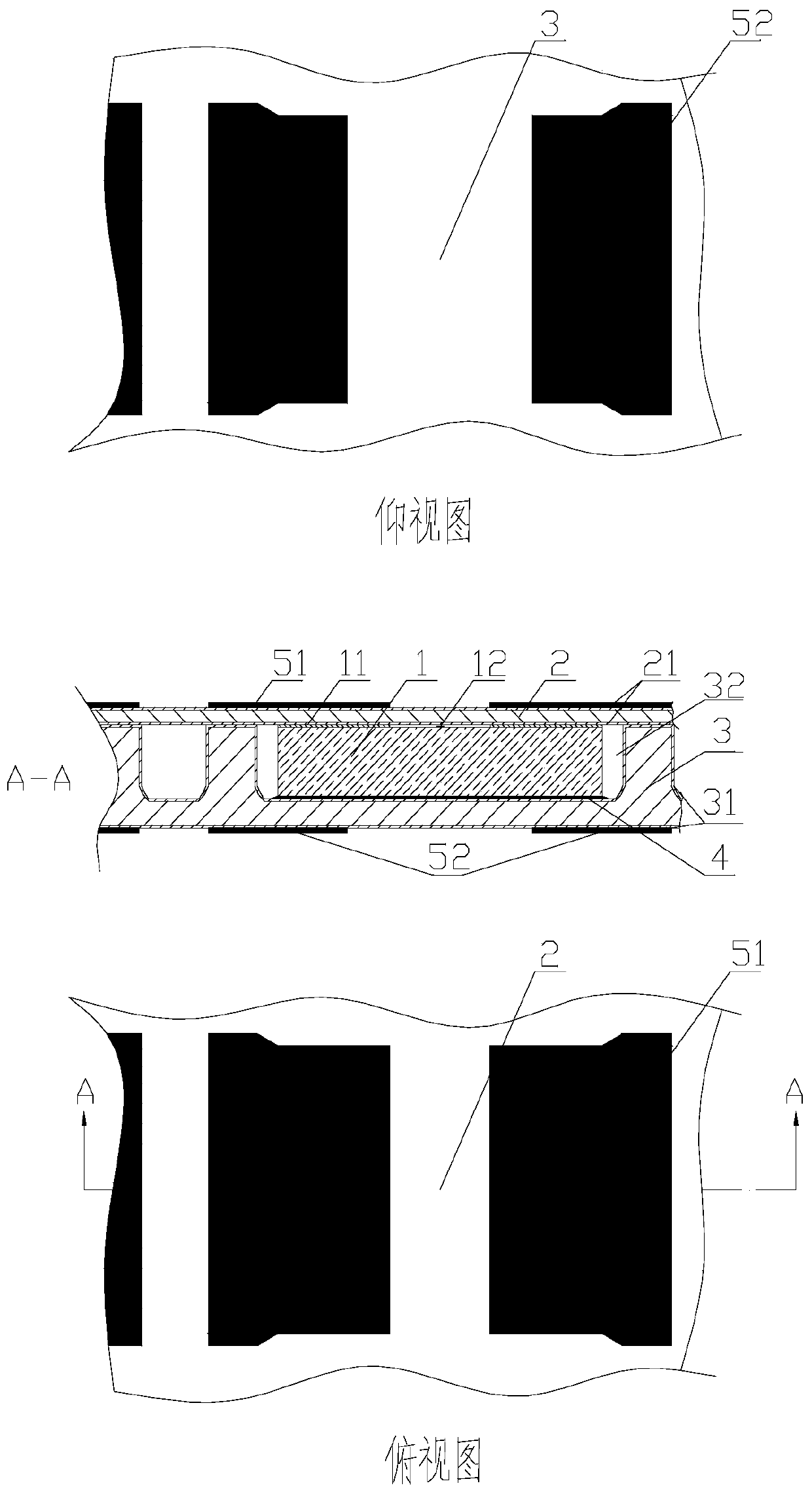

[0031] Embodiment: a kind of size is 2.00mm * 1.20mm * 0.50mm (1206 type) surface mounting semiconductor resistance bridge packaging structure and packaging process, comprising the following steps:

[0032] First, thin the semiconductor resistance bridge wafer to 340 μm; paste a 20 μm thermosetting high-temperature epoxy resin DAF film on the semiconductor resistance bridge wafer with a DAF film laminating machine as the insulating adhesive layer 4; use the semiconductor resistance bridge wafer as Cut and separate the 1.20mm×1.10mm×0.30mm semiconductor resistance bridge chip 1 by emery wheel dicing machine; use the online thermosetting chip loading machine to put the semiconductor resistance bridge chip 1 into the 0.45mm thick C194 copper plate and etch the cavity depth 0.35mm mm, with a size of 1.50mm×1.20mm on the electrode 4, the resistance bridge chip 1 and the electrode 3 are firmly bonded, such as figure 1 ;

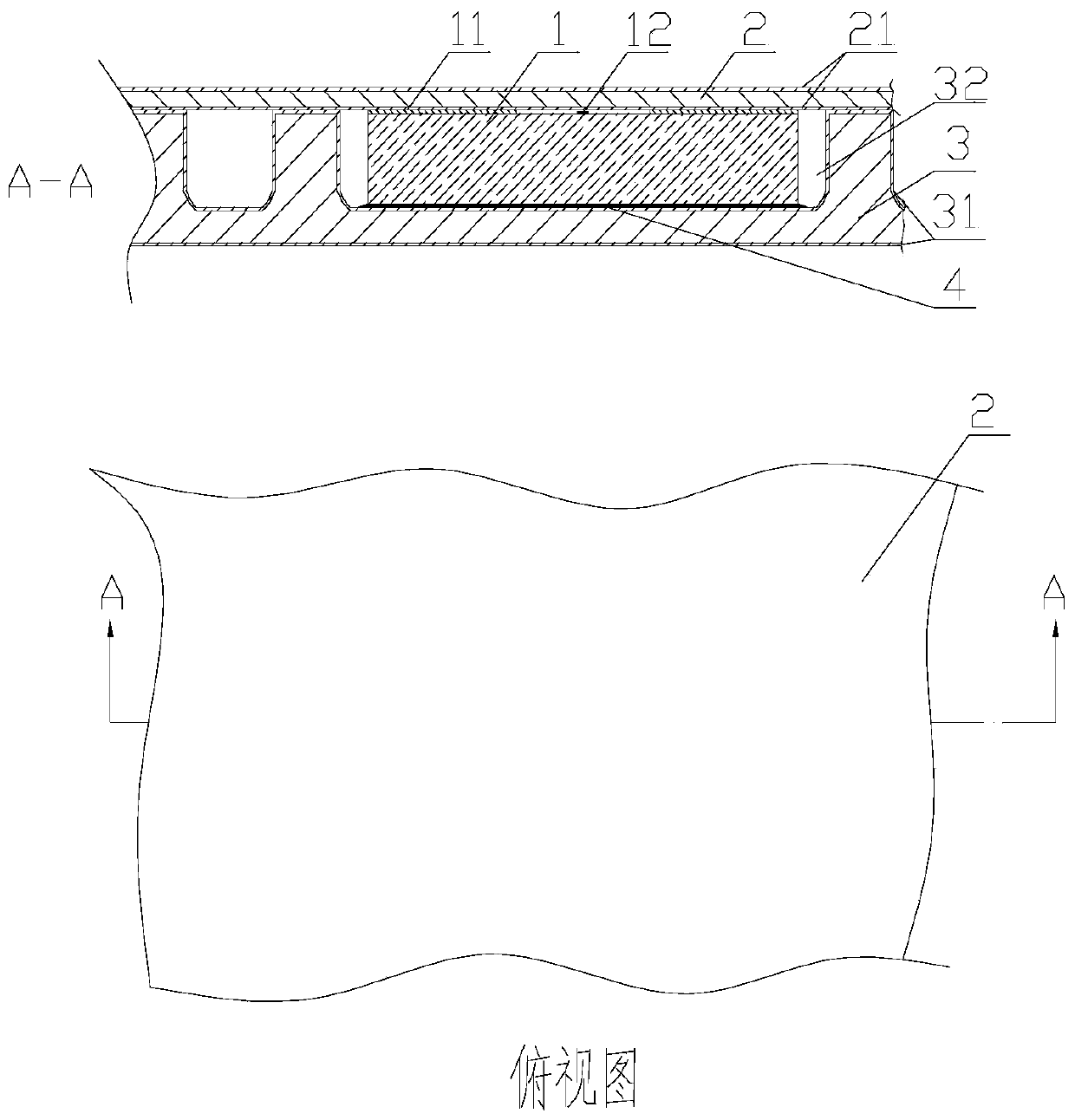

[0033] Secondly, use a C194 copper foil with a thickness of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More