Silicon slice alignment method for silicon through hole interconnection

A technology of silicon wafer alignment and through-silicon vias, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve the problems affecting the working frequency of chips and the interconnection resistance of silicon wafers, and achieve low power consumption , high-speed power consumption, and the effect of reducing interconnect resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] An exemplary embodiment of the present invention will be described in detail below with reference to the accompanying drawings. The reference figure is a schematic diagram of an idealized embodiment of the present invention, and the following embodiments are only illustrative, and the present invention is not limited by the following embodiments.

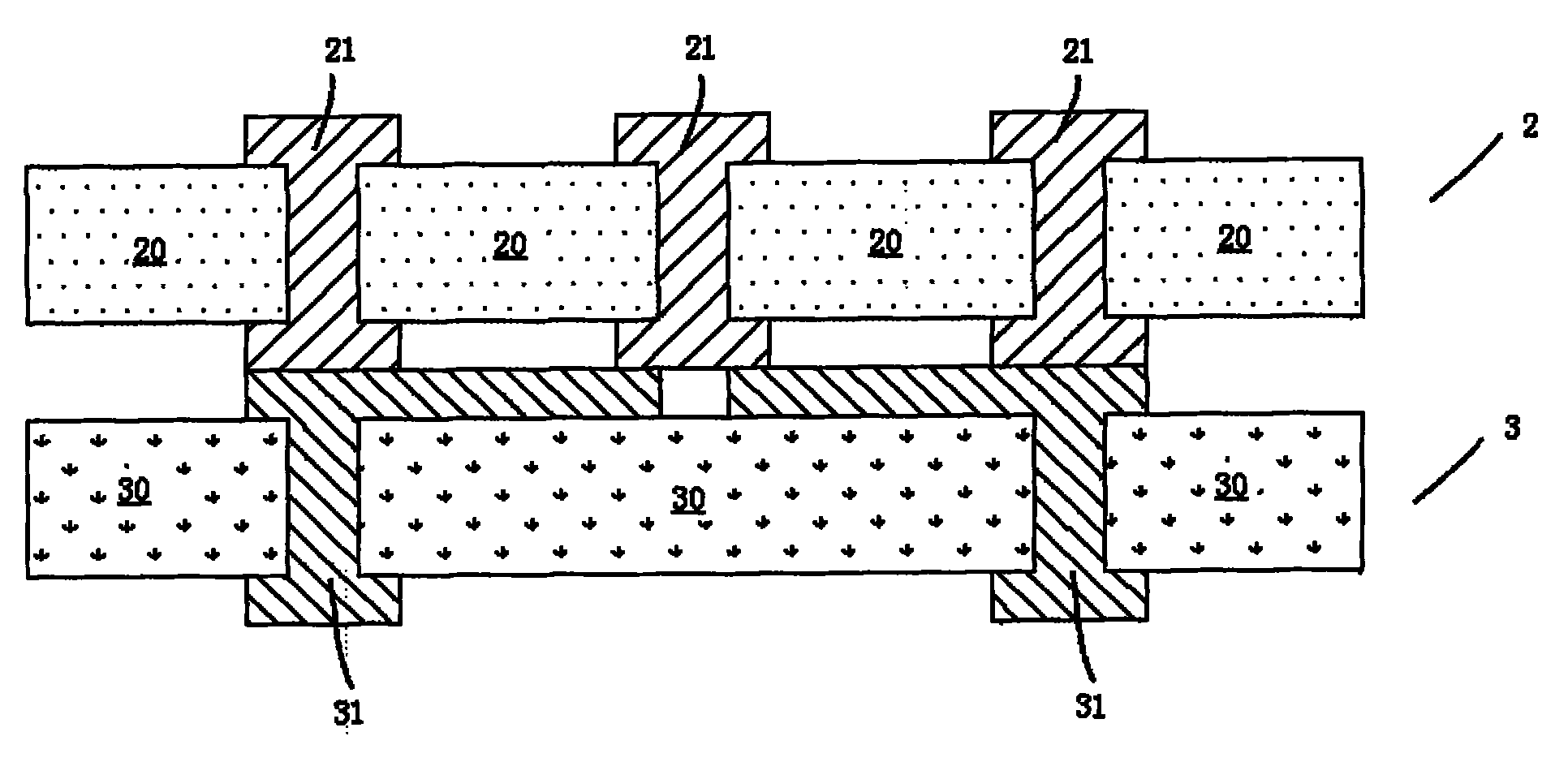

[0017] Provide two silicon wafers with TSV structures and interconnection solder joints completed, and FIG. 1 is a side view of the provided silicon wafers. As shown in Figure 1, in the silicon wafer 2, 20 is the silicon part, 21 is the through-silicon hole and the interconnection pad; in the silicon wafer 3, the 30 is the silicon part, and the 31 is the through-silicon hole. holes and interconnect solder joints.

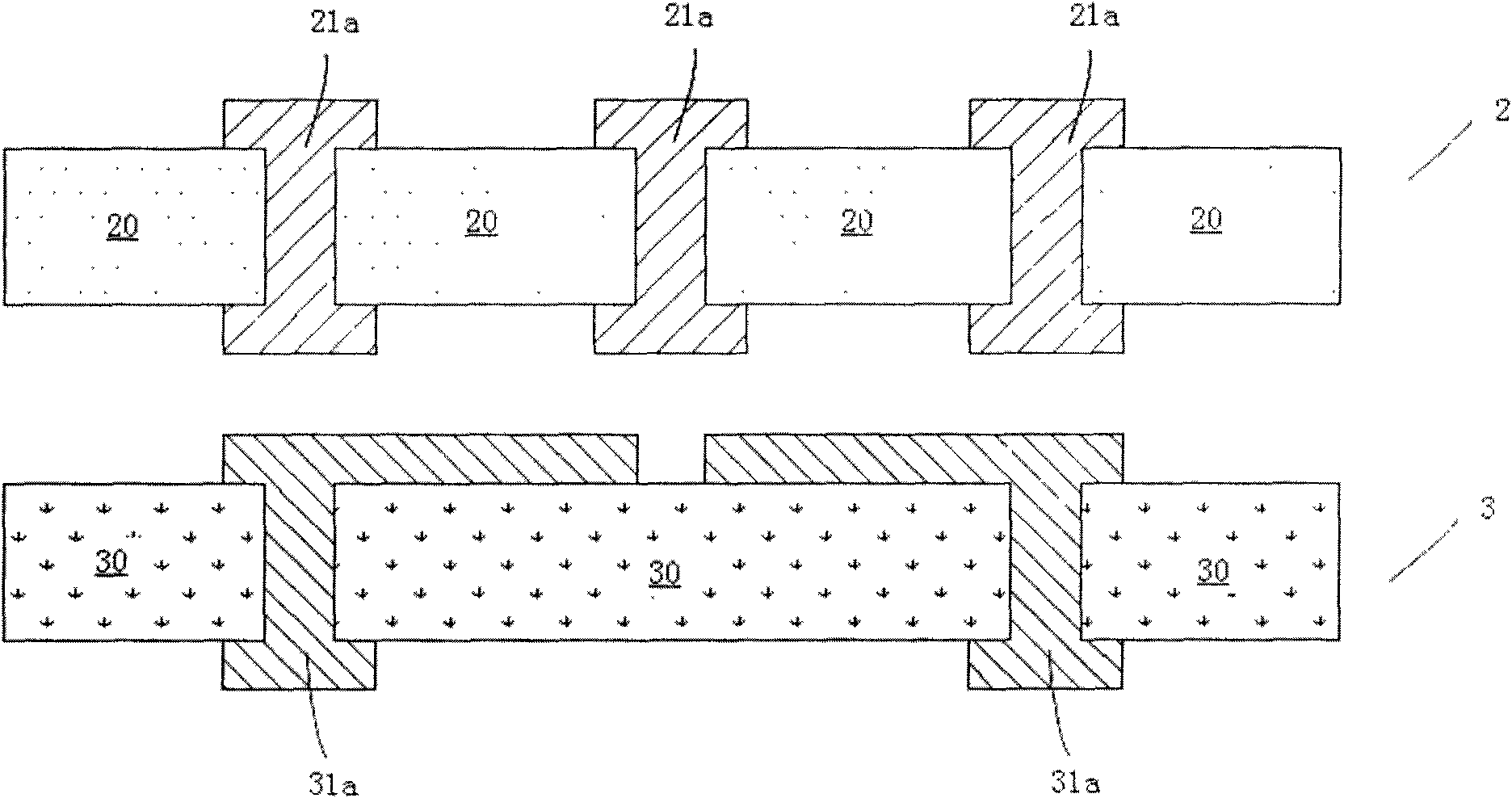

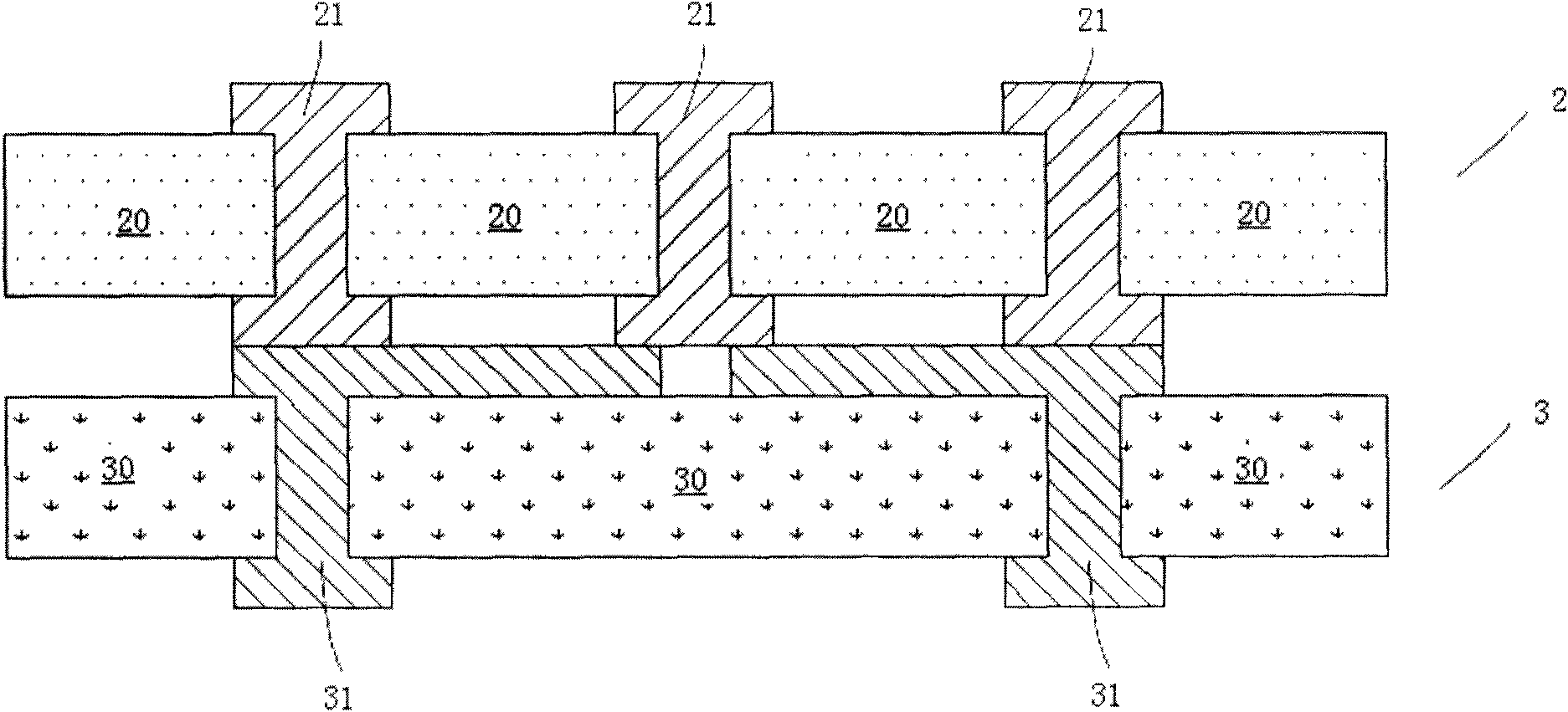

[0018] Next, silicon wafer 2 and silicon wafer 3 are stacked and interconnected, as shown in FIG. 2 .

[0019] When the silicon wafer 2 and the silicon wafer 3 are in contact, there may be misalignment between th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More