Preparing method of p-type stannous oxide ditch film transistors

A thin-film transistor and tin oxide technology, which is applied in semiconductor/solid-state device manufacturing, ion implantation plating, coating, etc., can solve the problems of low field effect mobility, high preparation difficulty, and high preparation cost, and achieve high field Effect mobility, simple preparation process, and reduced difficulty of device preparation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

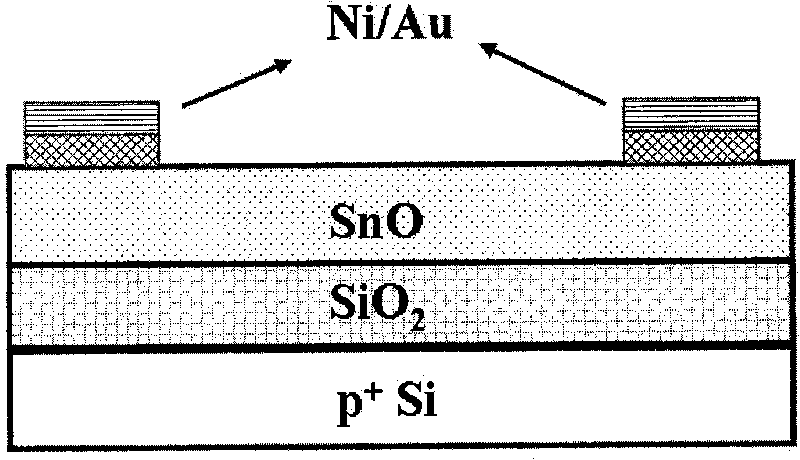

[0035] This example describes the SiO 2 p-type SnO channel thin film transistor with bottom gate structure prepared on / Si substrate (such as image 3 shown), and a comparative analysis of the performance of transistors annealed at 300°C to 450°C was performed.

[0036] Step 1: Select Commercially Purchased Thermally Oxidized Silicon Wafer SiO 2 / p + -Si(100) as substrate with SiO 2 layer as a gate dielectric layer with a thickness of 190nm, while p-type highly doped p + -Si substrate can also be used as gate electrode;

[0037] Step 2: Using electron beam evaporation equipment and tin oxide evaporation material, deposit a 100nm stannous oxide amorphous film on the gate dielectric layer at room temperature, and then perform thermal annealing treatment in an Ar gas atmosphere, and the annealing temperature is 300 ℃~ 450℃, one temperature point per 50℃, annealing time is 10min;

[0038] Step 3: Ni / Au source electrode and Ni / Au drain electrode are prepared by electron beam ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More