Patents

Literature

53 results about "Sequence memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

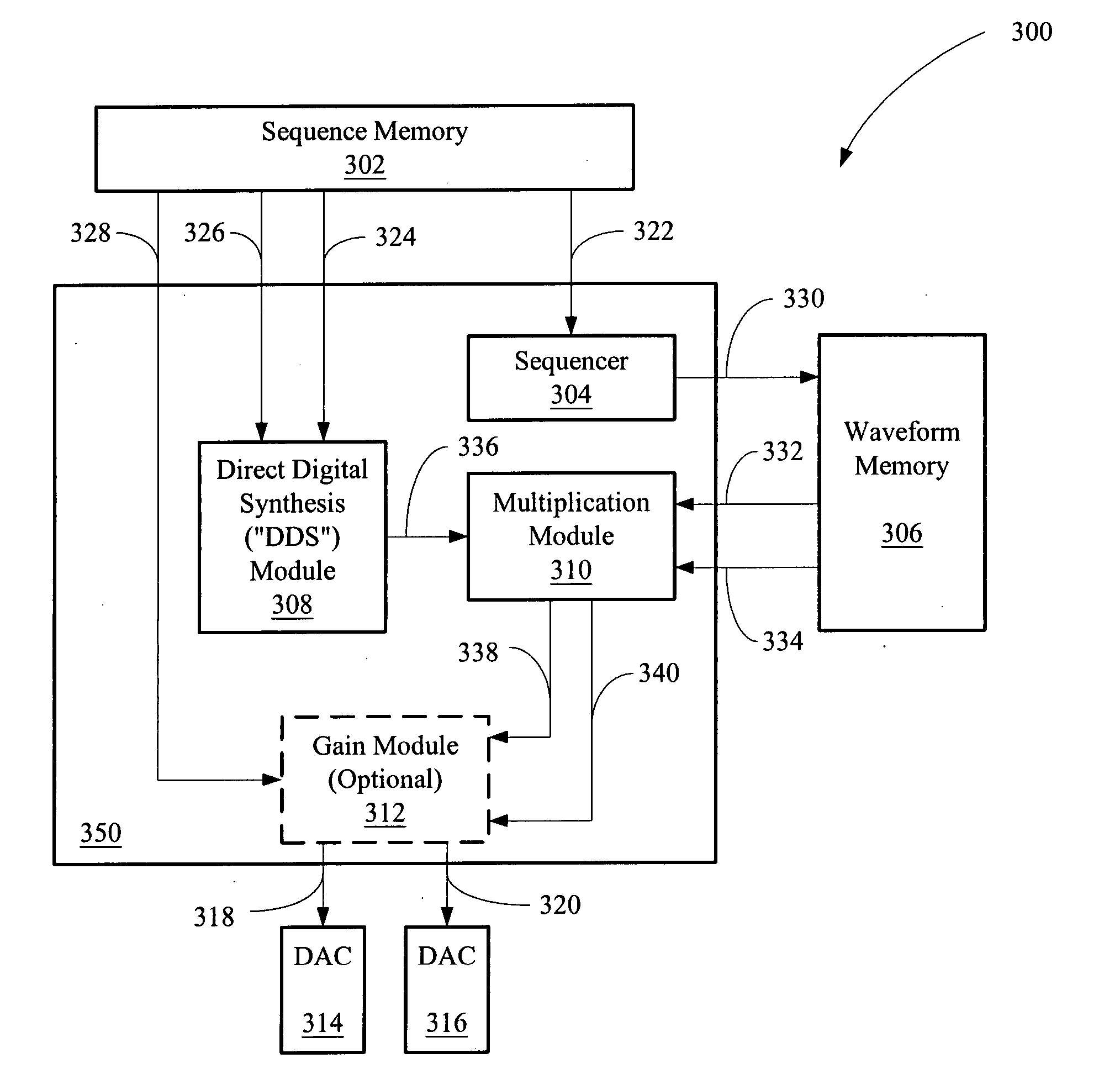

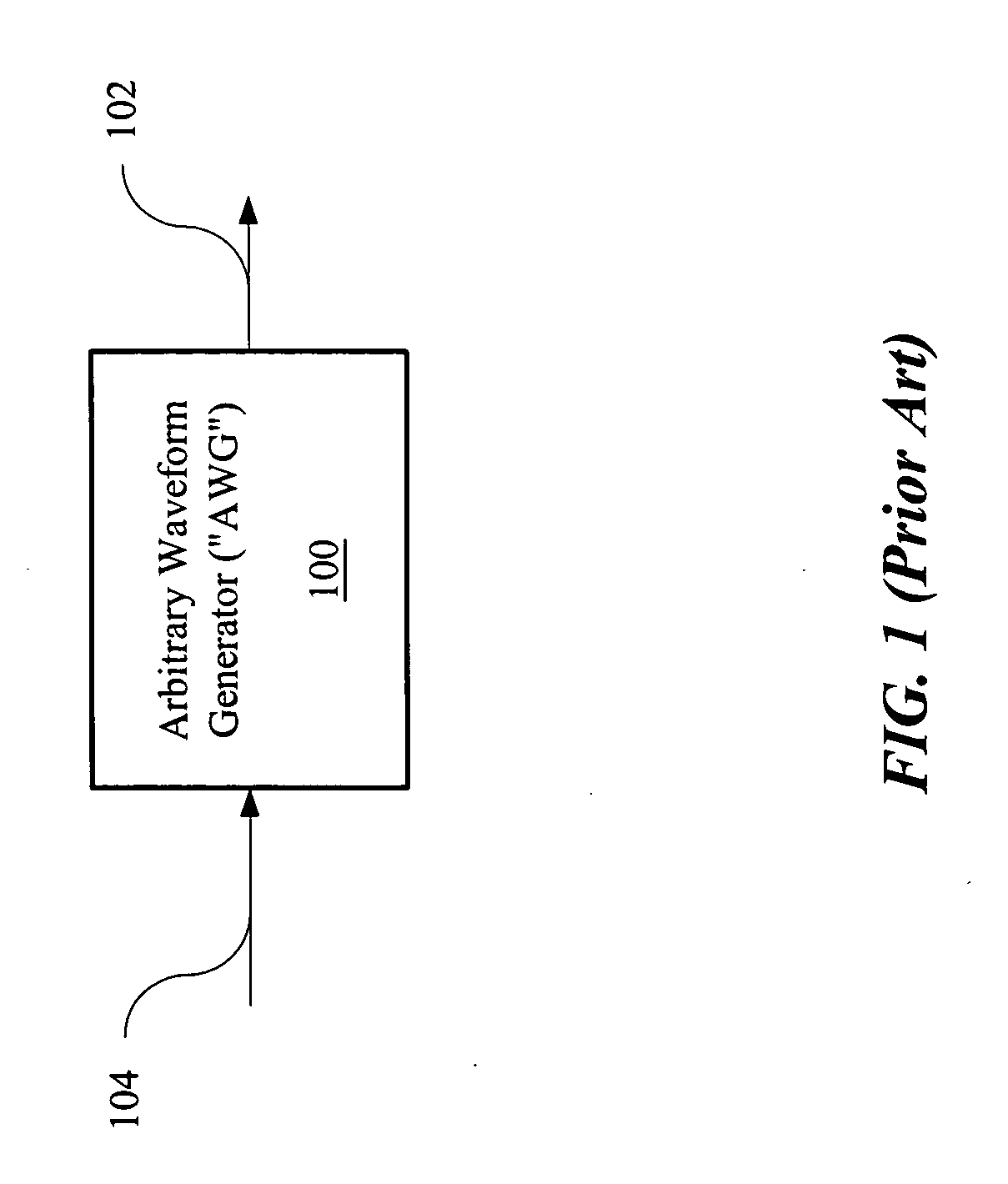

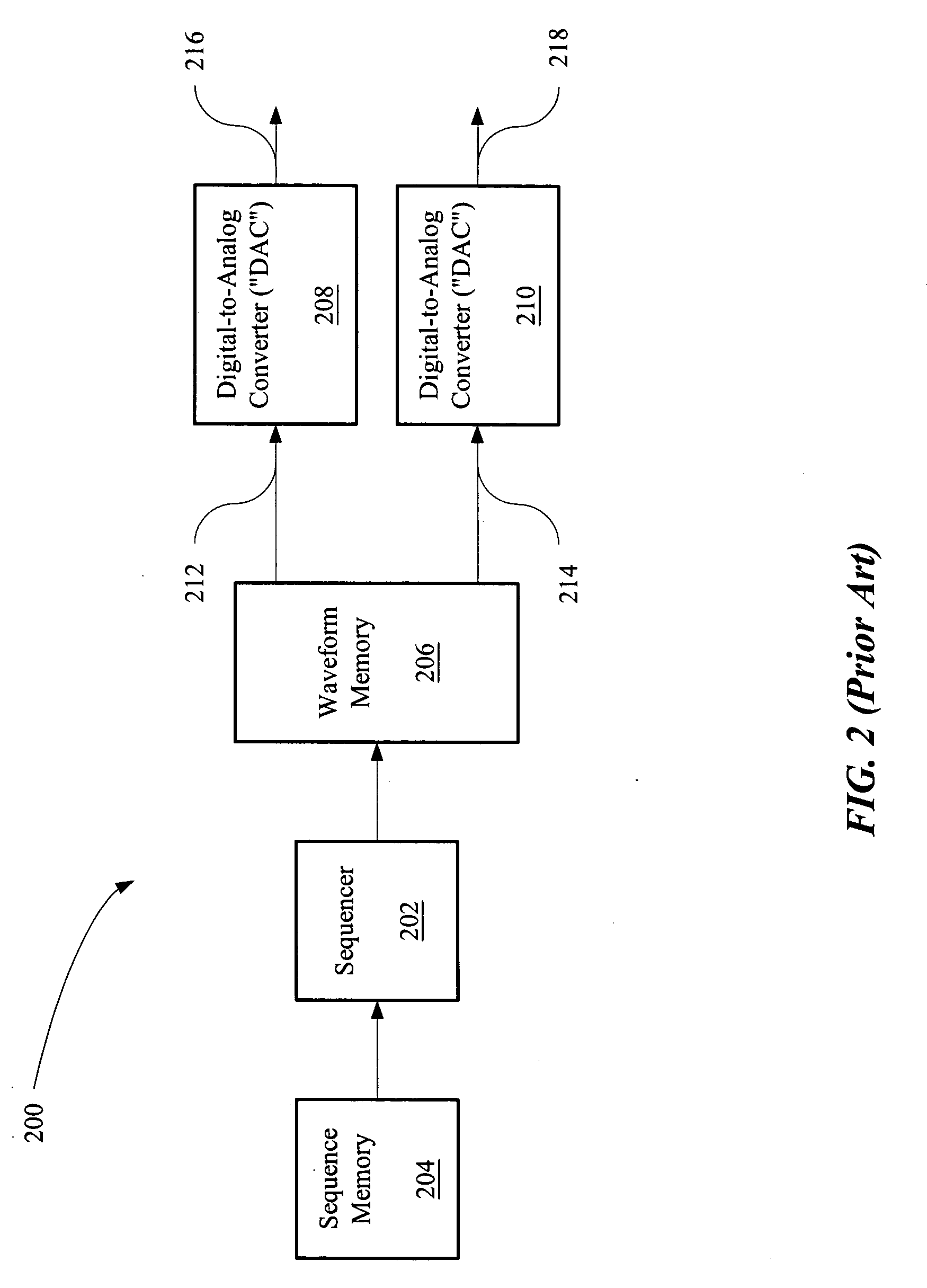

Advanced arbitrary waveform generator

InactiveUS20070067123A1Digital variable displayDigital data processing detailsSequence memoryComputer science

An advanced arbitrary waveform generator (“AAWG”) for producing an arbitrary waveform is disclosed. The AAWG may include a direct digital synthesis (“DDS”) module in signal communication with a sequence memory and a multiplication module in signal communication with both the DDS module and a waveform memory, where the multiplication module receives signal waveform data from the waveform memory and multiplies the received signal waveform data with a DDS output signal to produce the arbitrary waveform signal.

Owner:AGILENT TECH INC

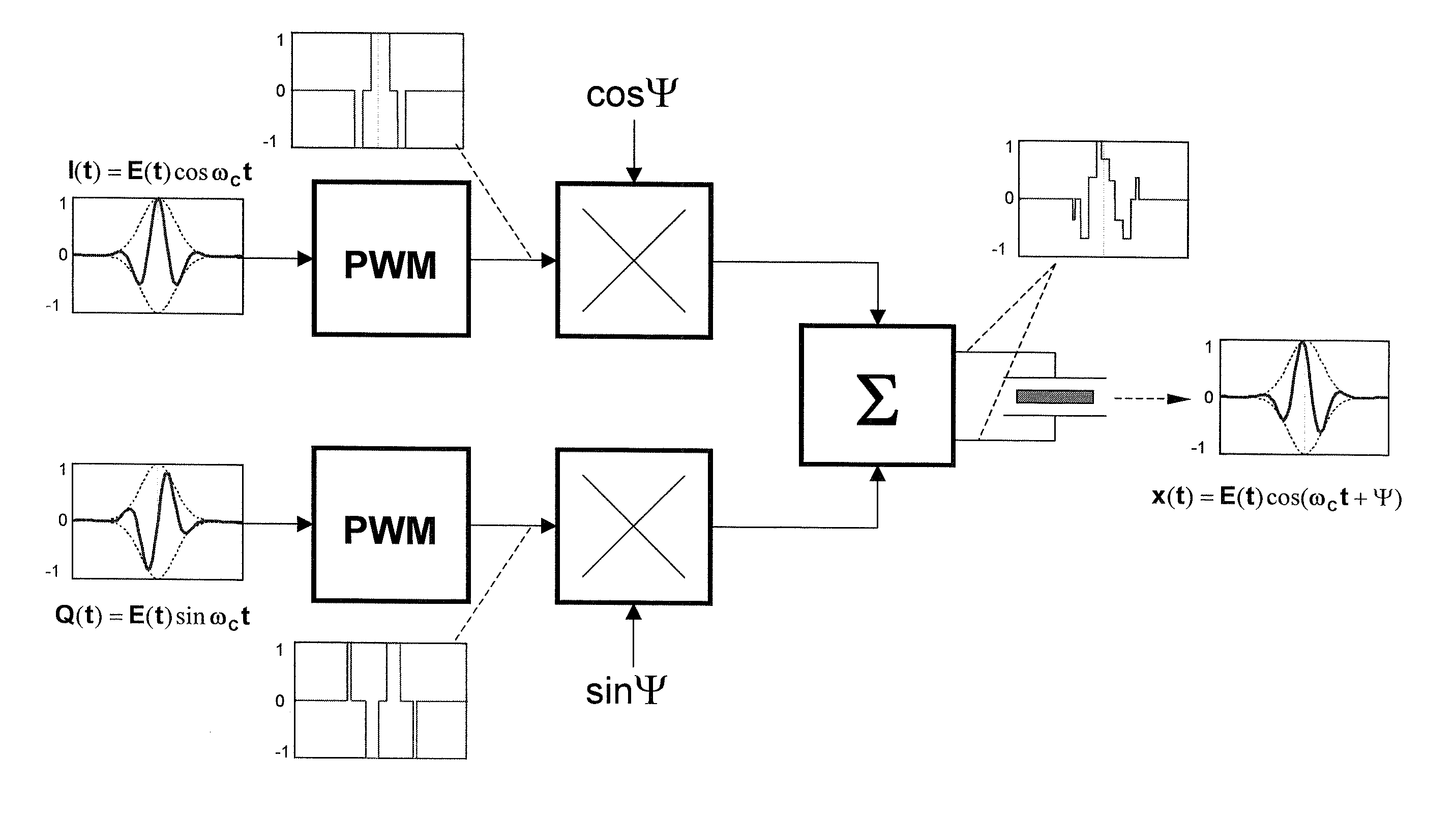

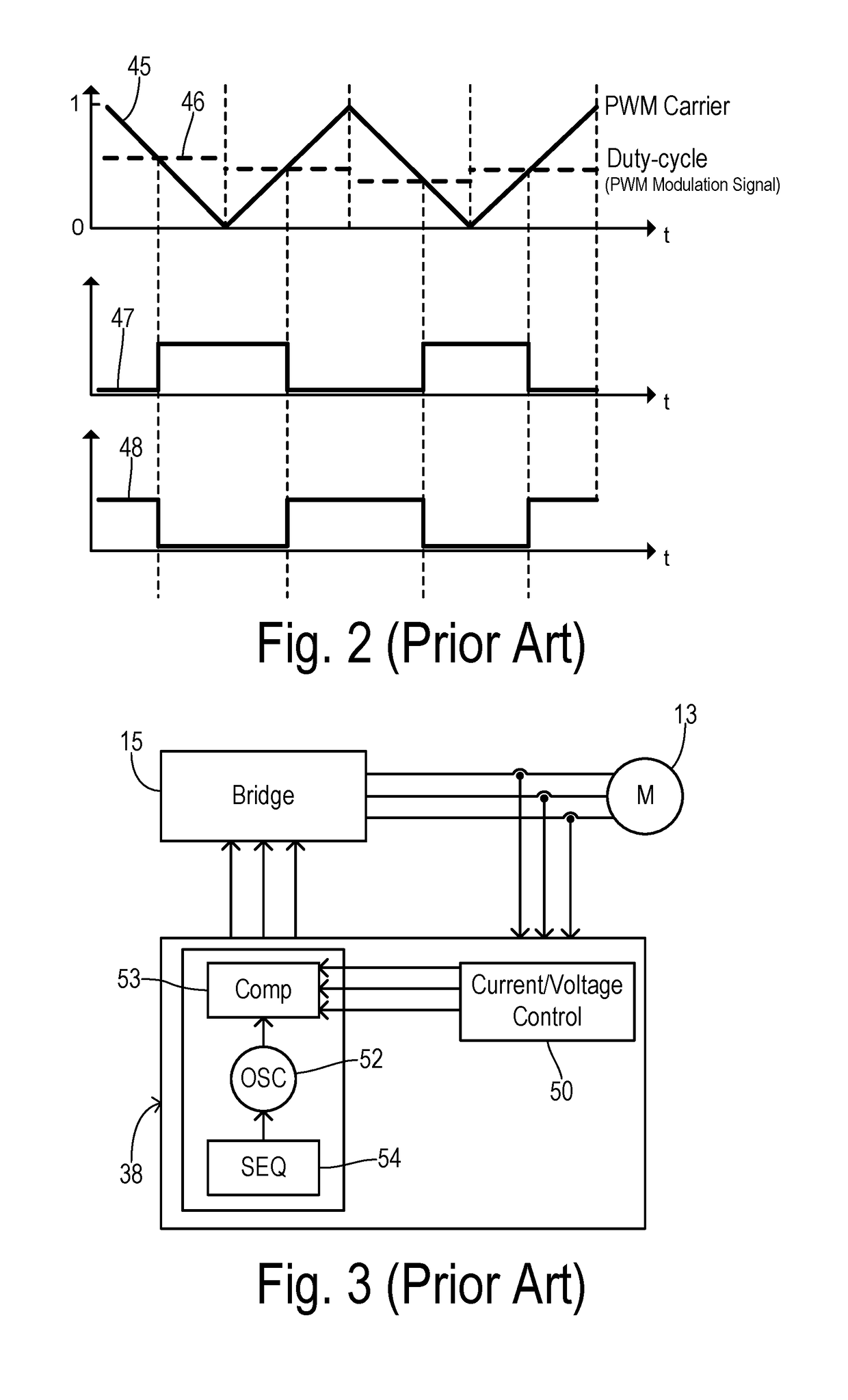

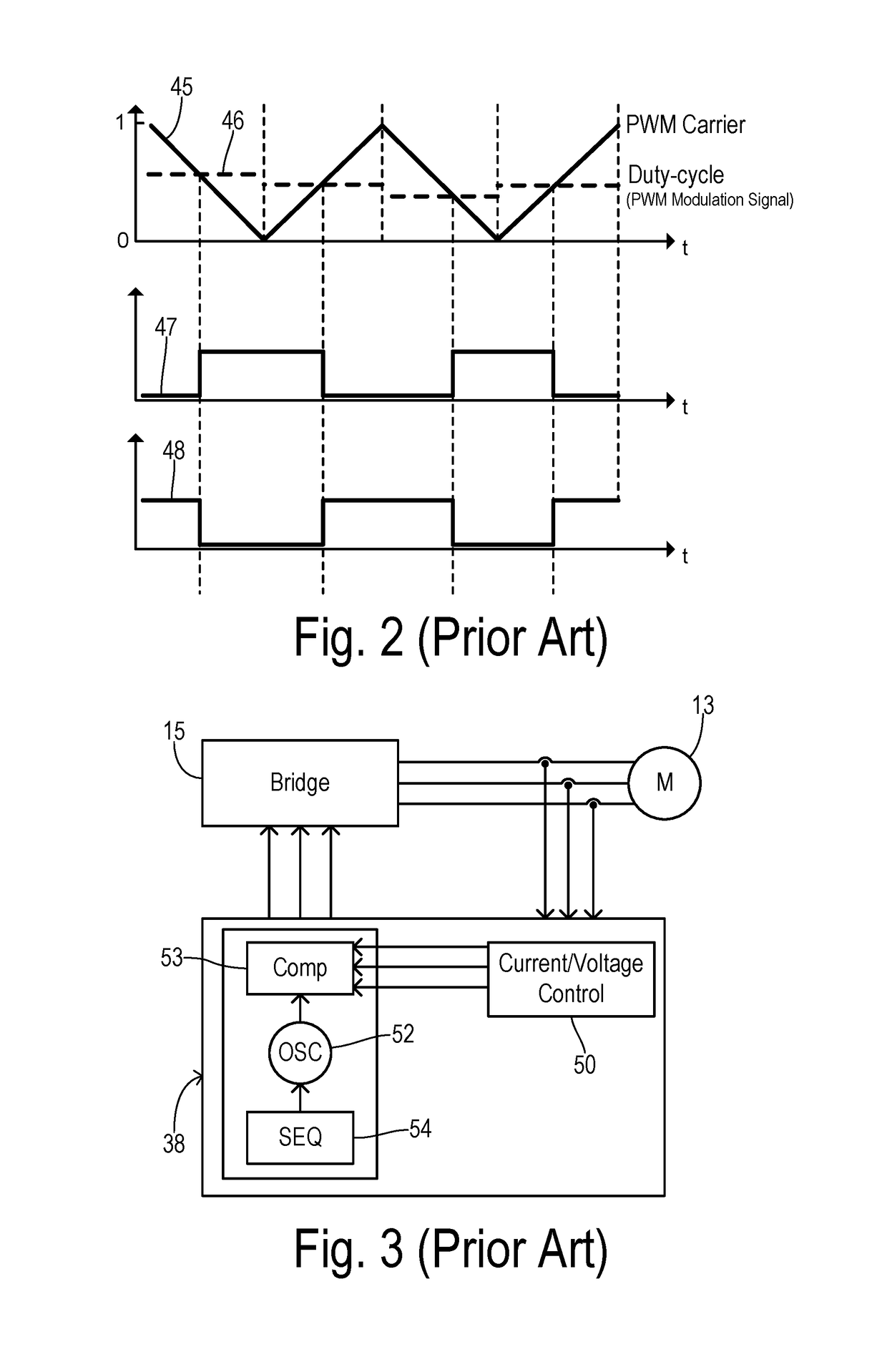

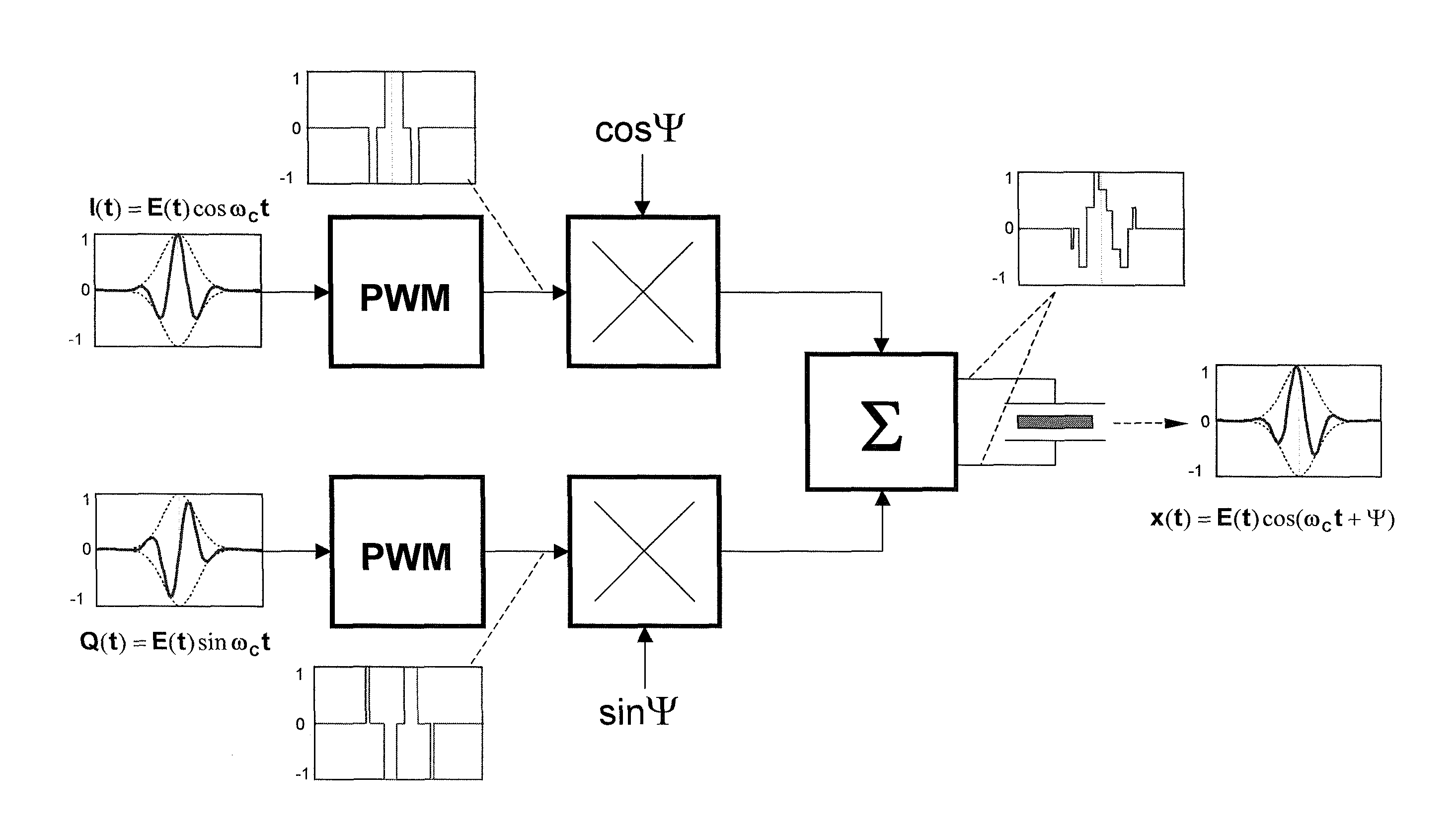

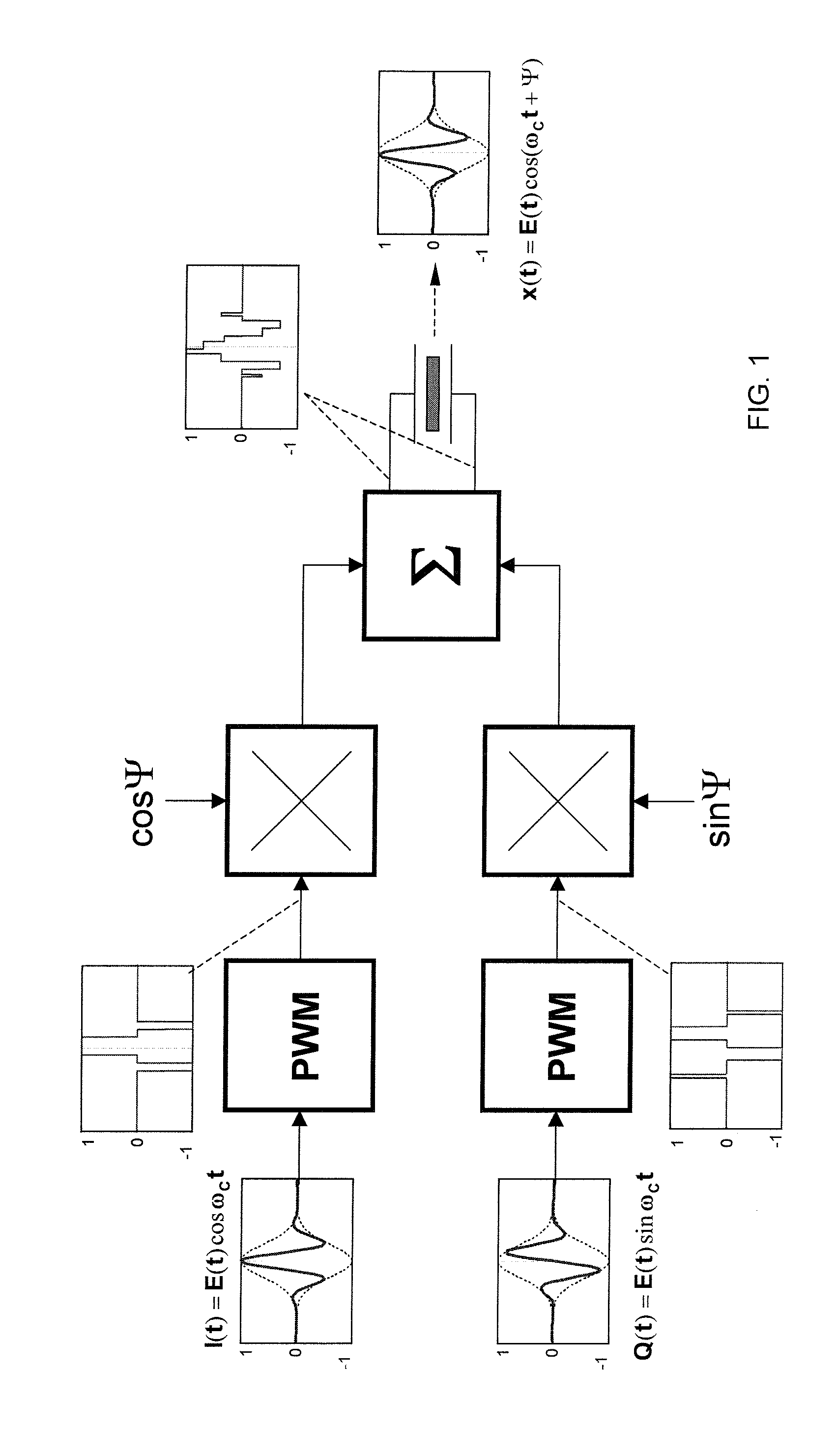

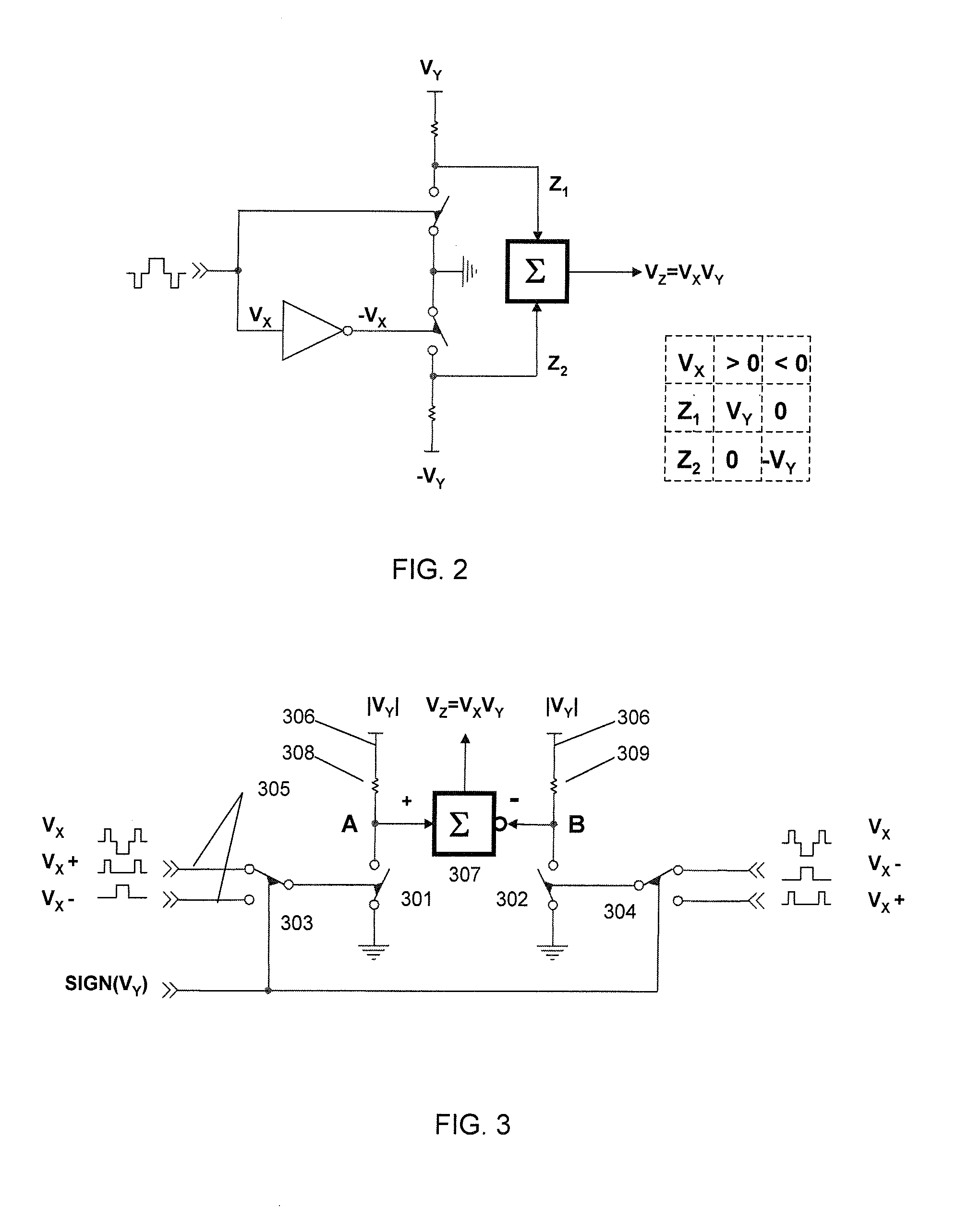

Ultrasound transmit beamformer integrated circuit and method

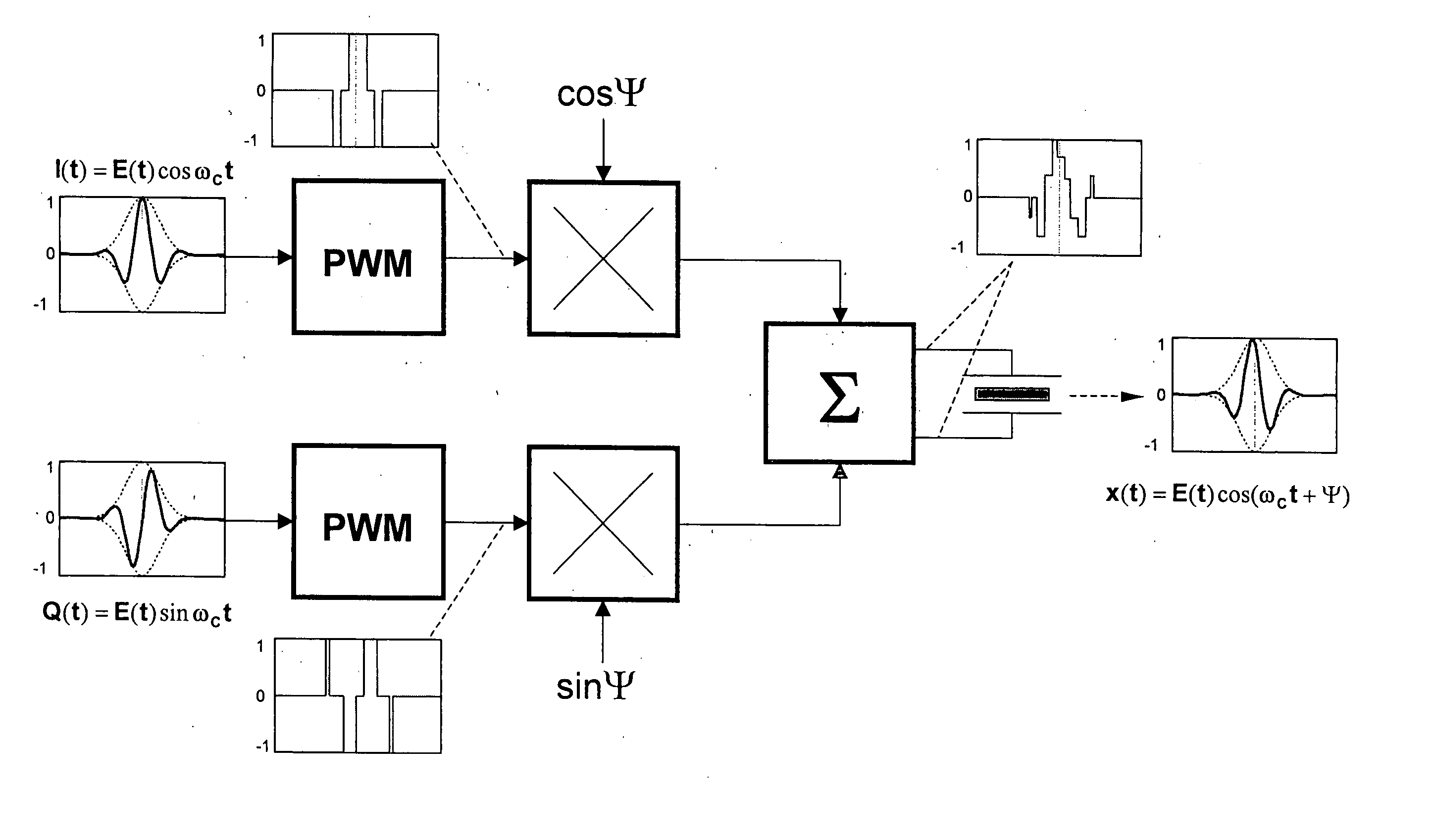

ActiveUS20050033168A1Compact implementationLow costUltrasonic/sonic/infrasonic diagnosticsWave based measurement systemsPulse envelopeSonification

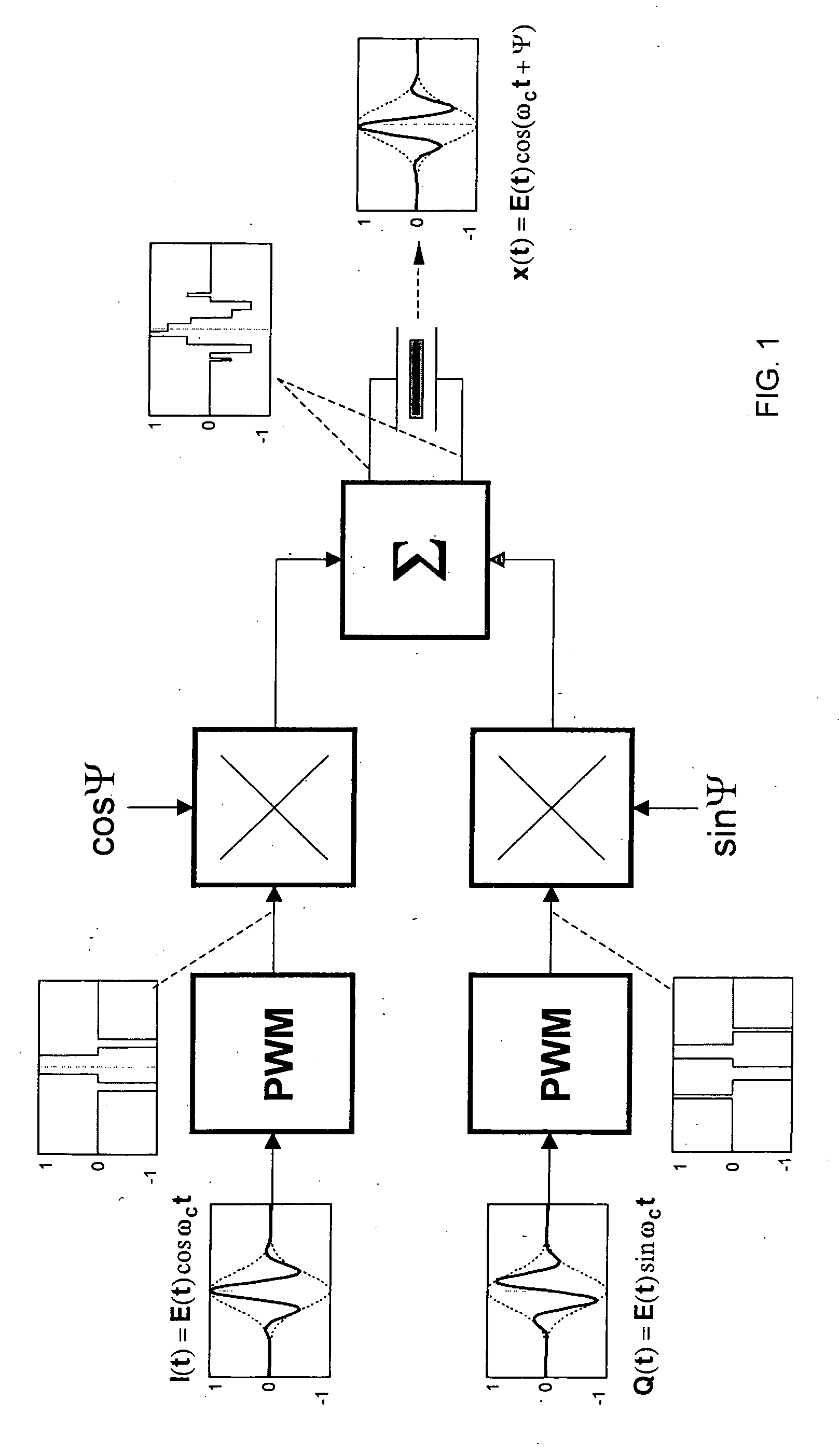

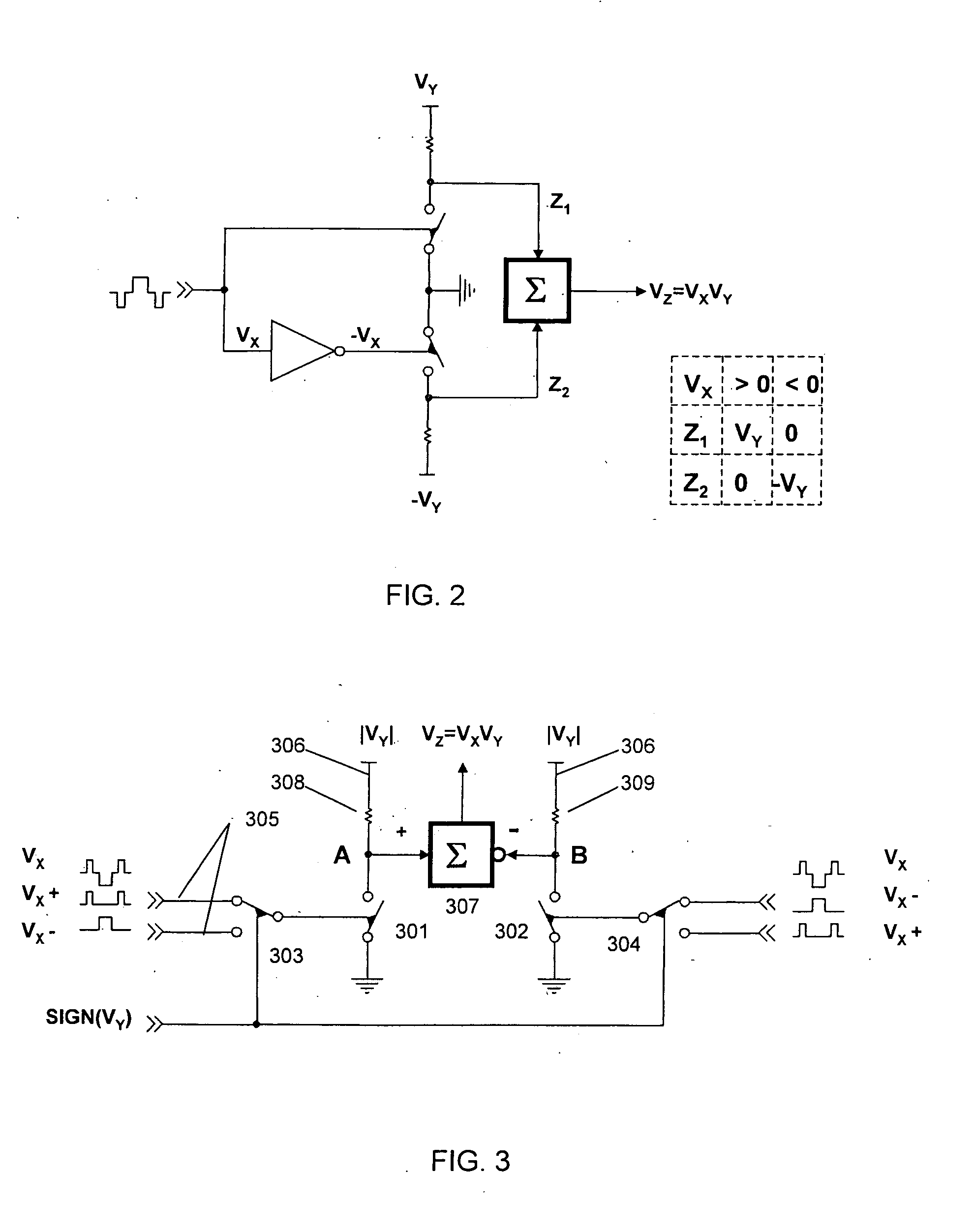

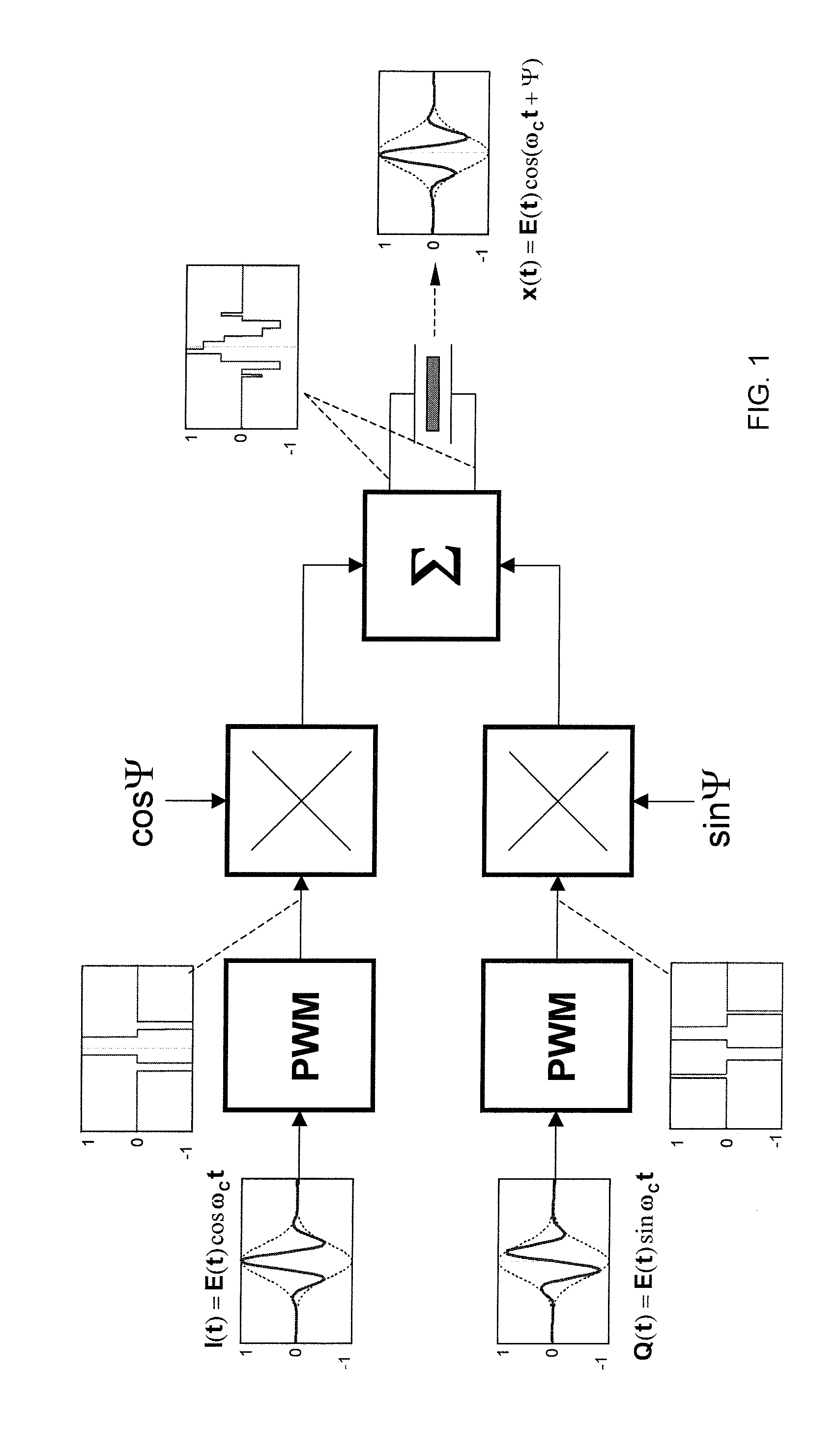

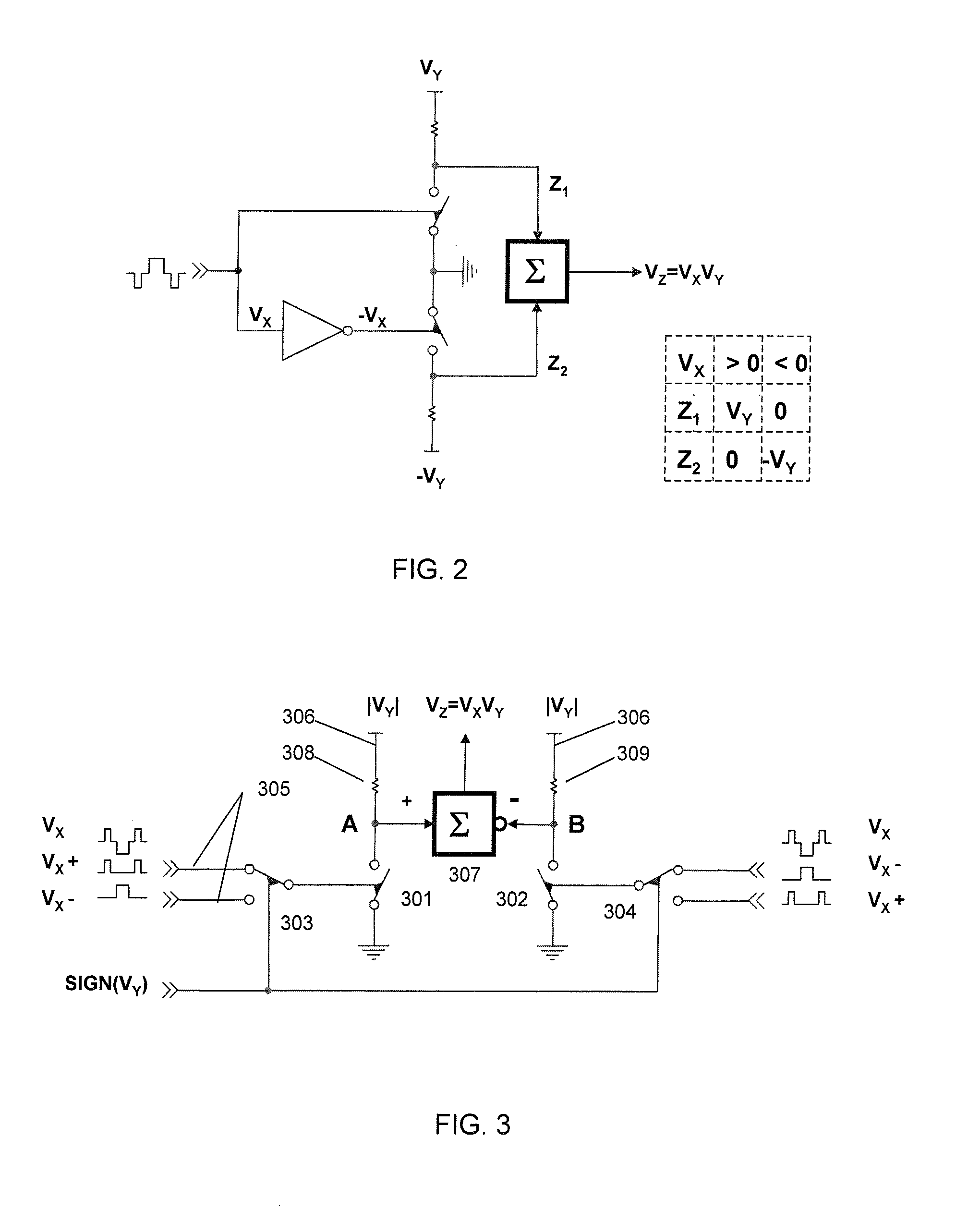

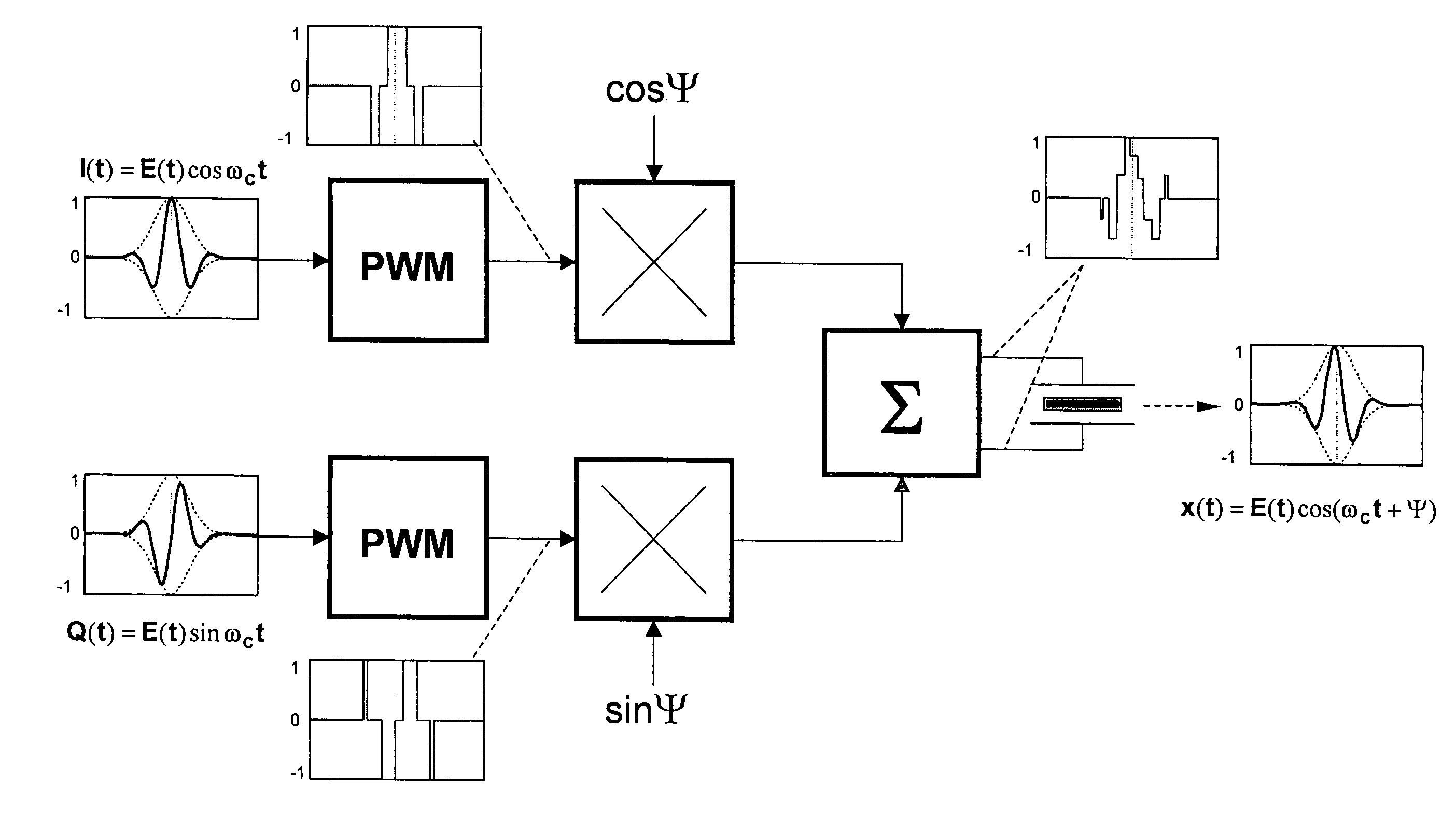

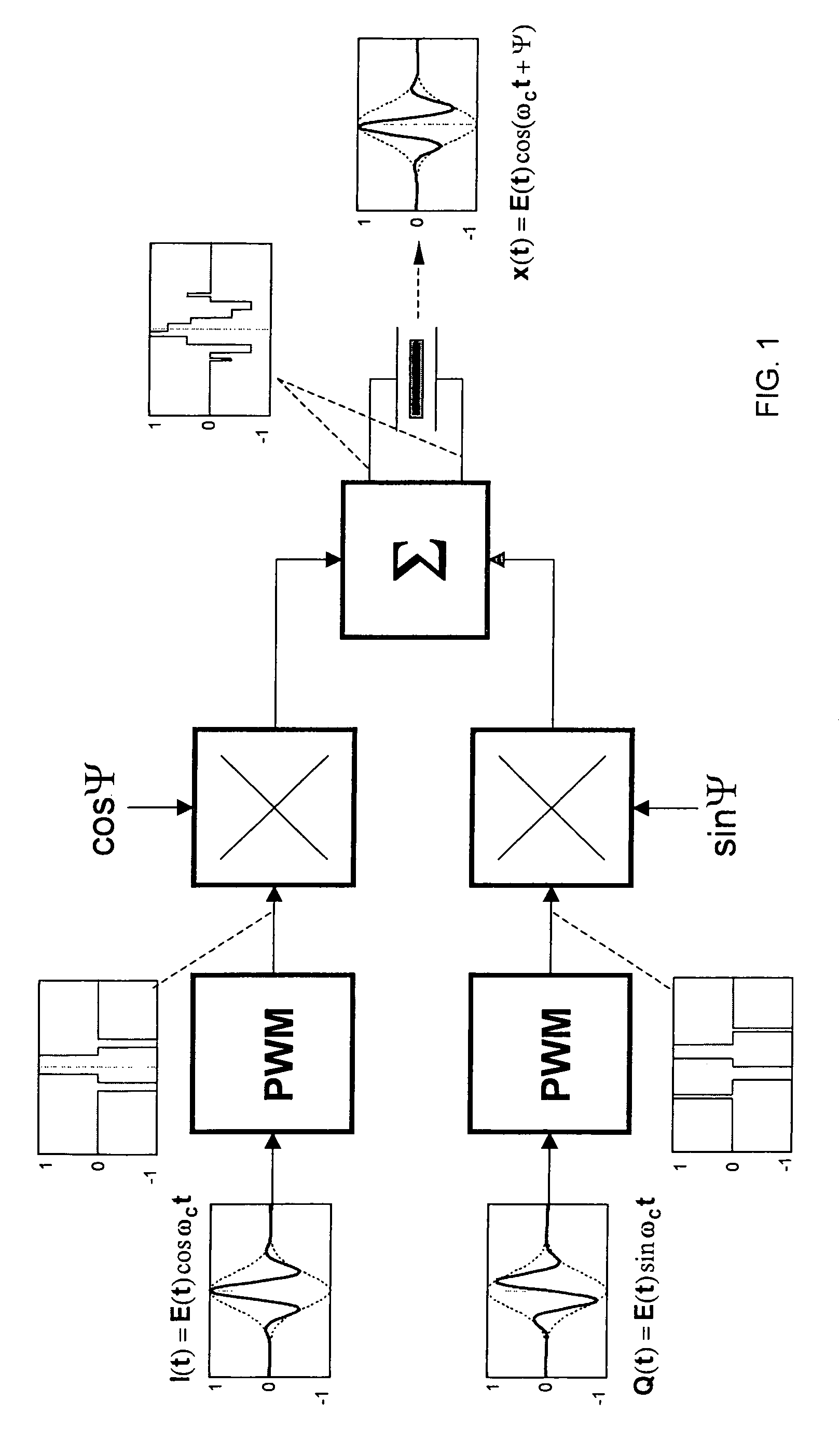

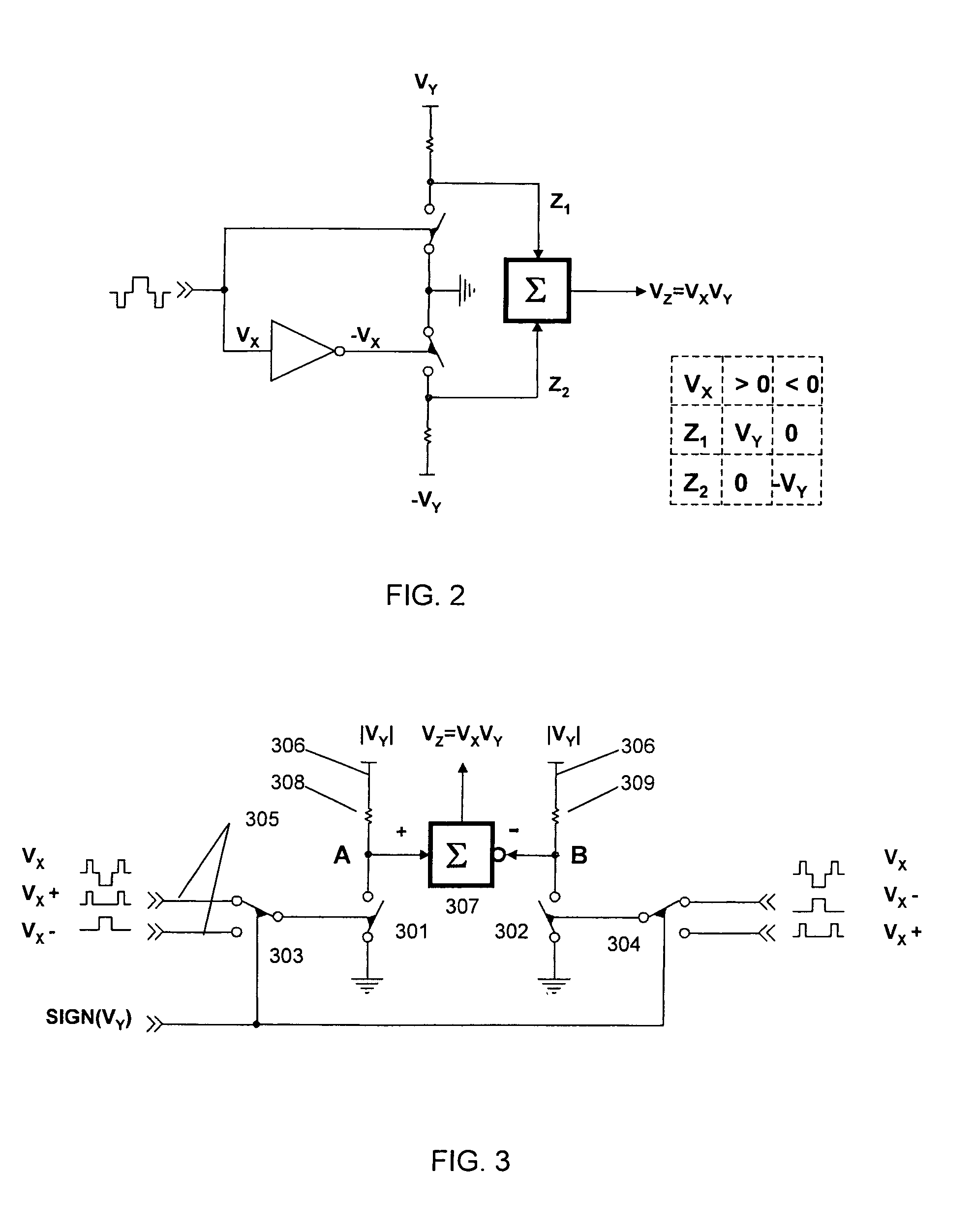

The invention provides a novel method of transmit beamforming, which allows compact analog implementation of complex digital algorithms without compromising their features. It is aimed to support envelope shaping, apodization, and phase rotation per channel and per firing. Each of three embodiments represents a complete transmit channel driven by pulse-width modulated (PWM) waveforms stored in a conventional sequence memory. PWM signals controls the transmit pulse envelope (shape) by changing the duty cycle of the carrier. Beamformation data are loaded prior to a firing via serial interface. Under the direction of a controller, the circuitry allows high precision (beyond sampling rate) phase rotation of the carrier. It also provides transmit apodization (aperture weighting), which maintains an optimal trade-off among low sidelobe level and widening of the mainlobe. Implementing such an IC, the manufacturing cost of a high-end ultrasound system can be reduced. Equally, the proposed solution makes the benefits of digital transmit beamformers available to midrange and entry-level machines since it merely requires a modified programming of the sequence memory.

Owner:MICROCHIP TECH INC

System and method for judging memory leak

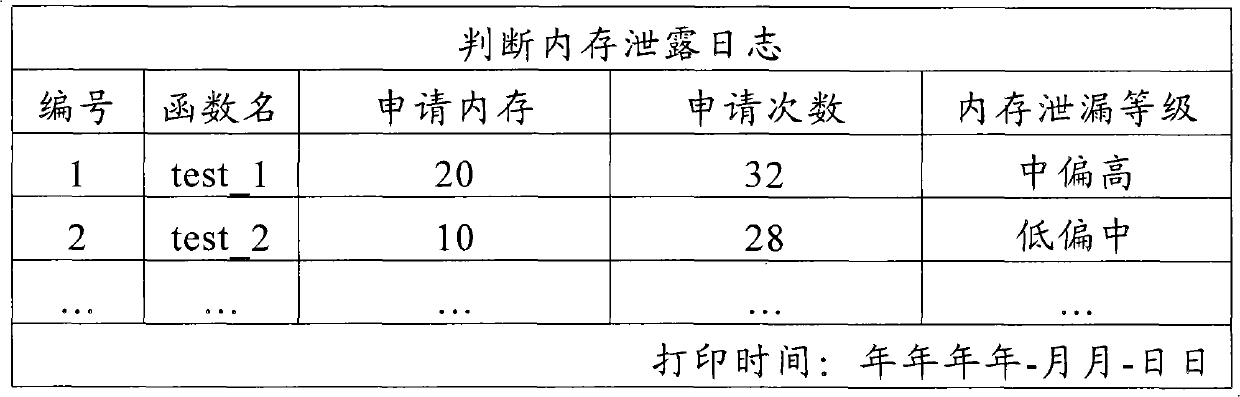

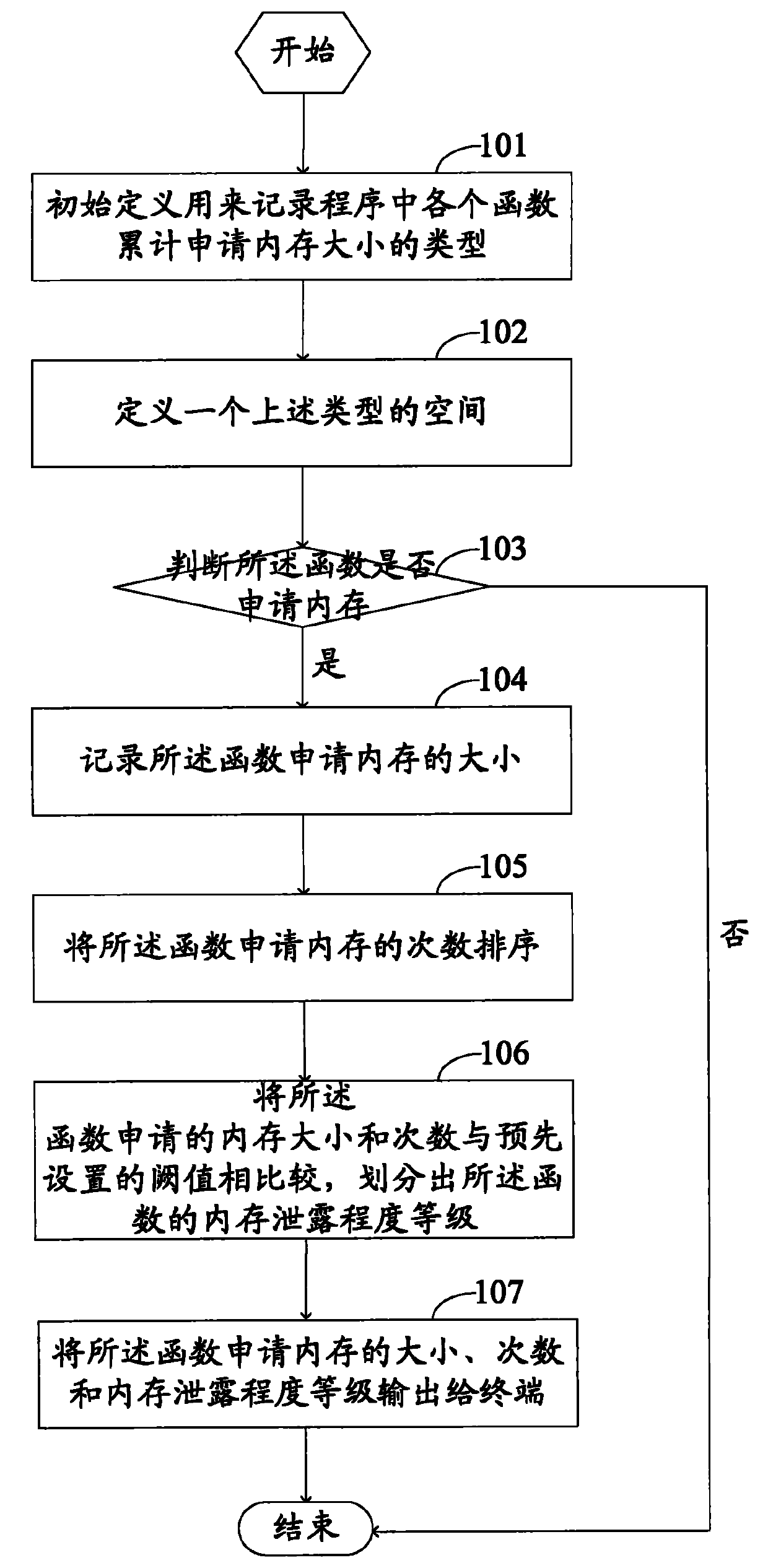

The invention provides a method for judging memory leak, comprising the following steps of: when a function application memory is judged aiming at each function in a program, accumulating the memory capacity and the application times of the named function application; when a function release memory is judged, reducing the released memory capacity from the memory capacity of the named function accumulated application and reducing release memory times from accumulated application times; sequencing the memory capacity and the times of the function application in different names in a descending mode by using the memory capacity as priority; ensuring and outputting a level of a memory leak degree according to the memory capacity and the times of the function accumulated application in different names; in addition, the invention provides a system for realizing the method in order to sequence memory distribution and information release according to the memory application times and liberate a programmer from large fussy analytical work.

Owner:BEIJING HAITAI FANGYUAN HIGH TECH

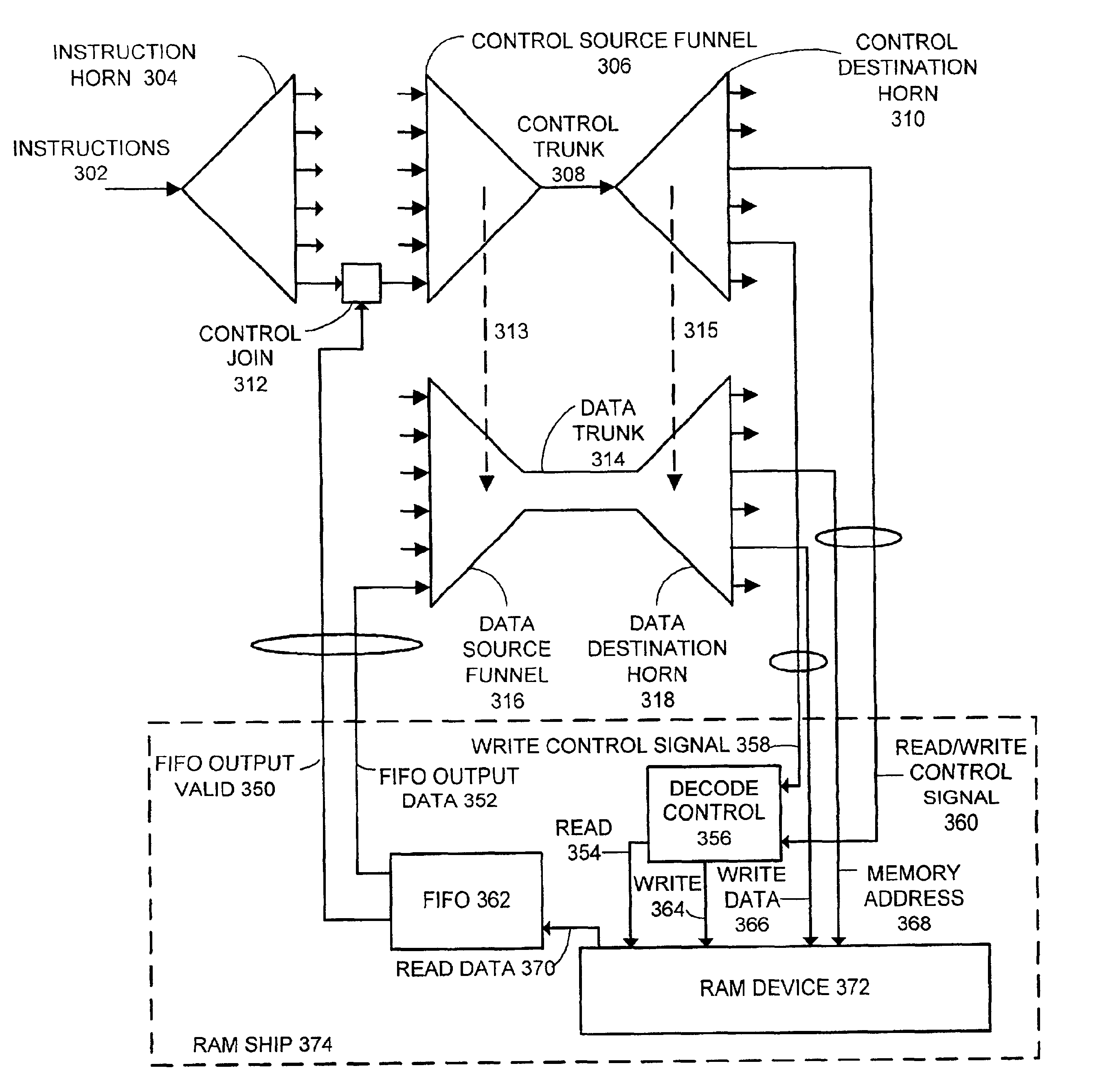

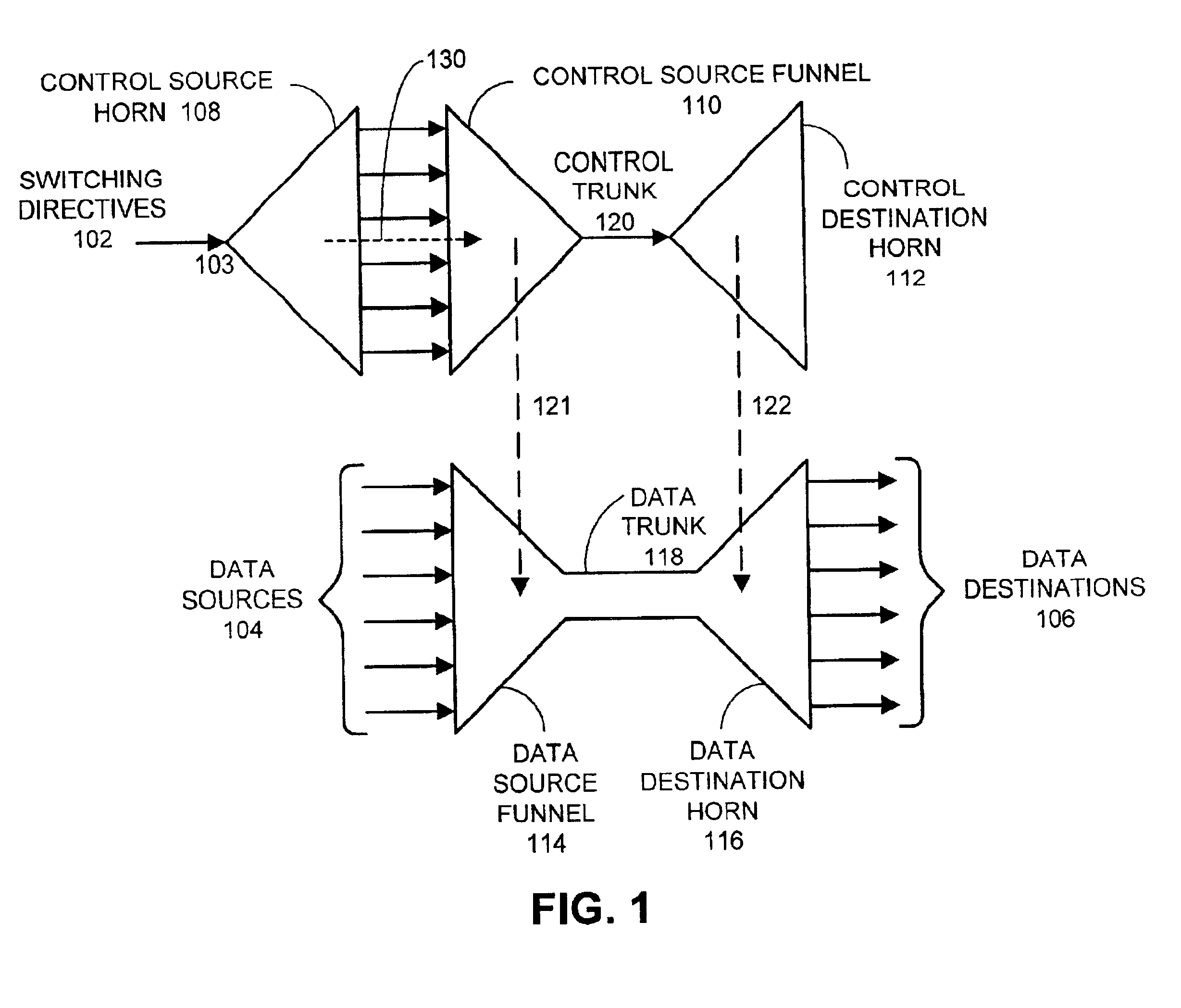

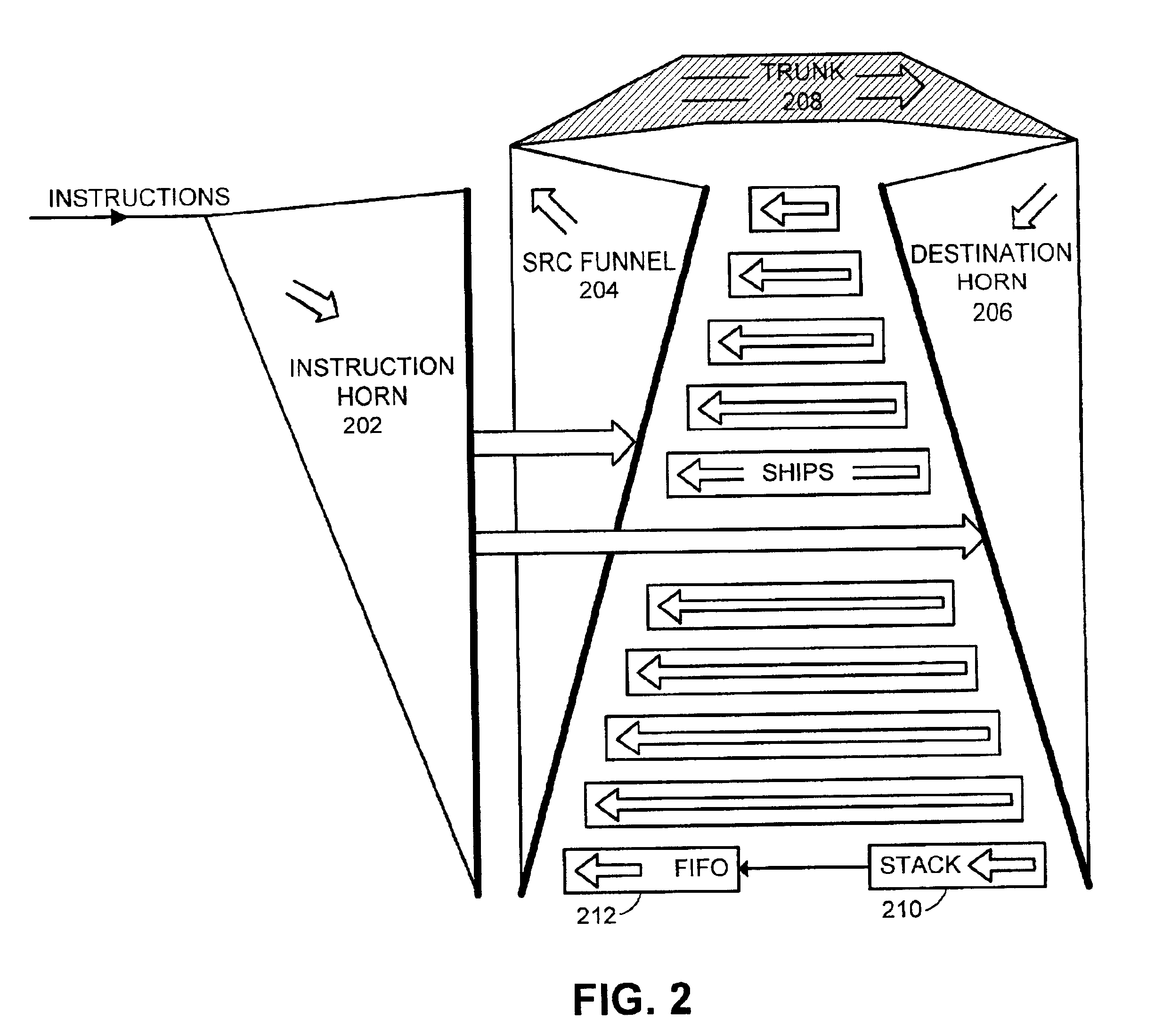

Apparatus and method for sequencing memory operations in an asynchronous switch fabric

InactiveUS6882645B2Easy to implementElectronic switchingData switching by path configurationRandom access memorySequence memory

One embodiment of the present invention provides a system that facilitates implementing a memory mechanism within an asynchronous switch fabric. The system includes a memory device, which does not preserve first-in, first-out semantics such as a random access memory or a stack. The system also includes a data destination horn, for routing data from a trunk line to a plurality of destinations. The memory device is one destination of the plurality of destinations. The system further includes a data source funnel, for routing data from a plurality of sources into the trunk line. The memory device is a source of the plurality of sources.

Owner:ORACLE INT CORP

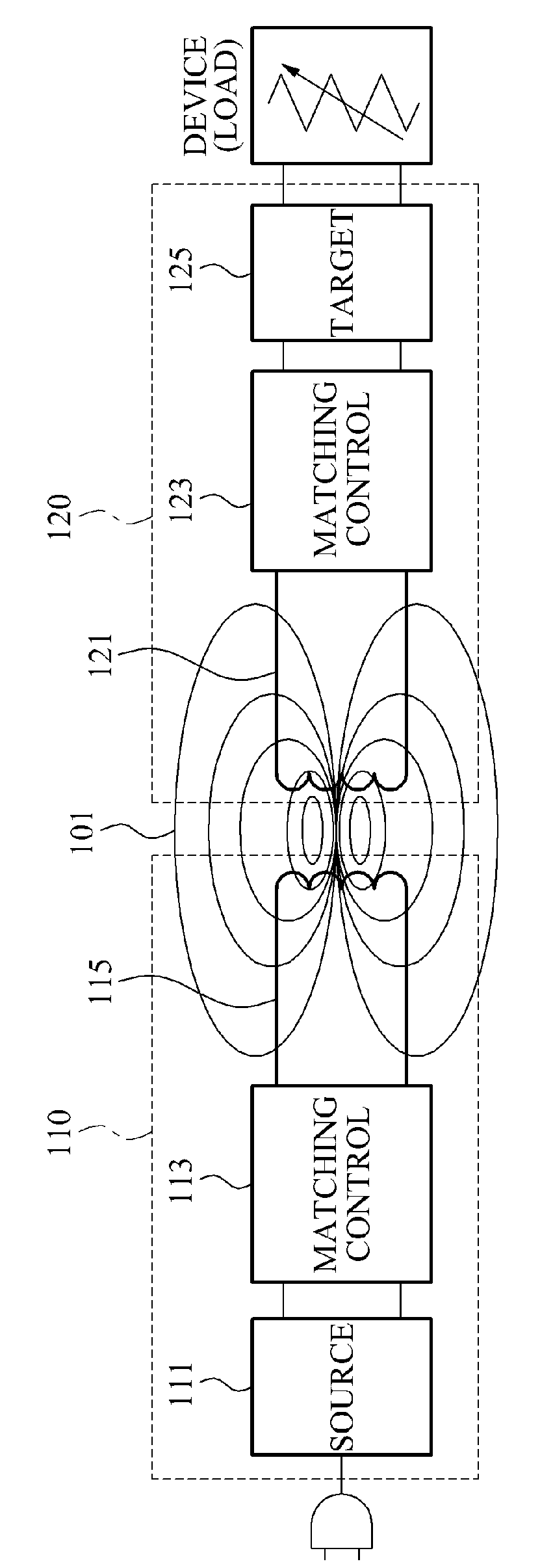

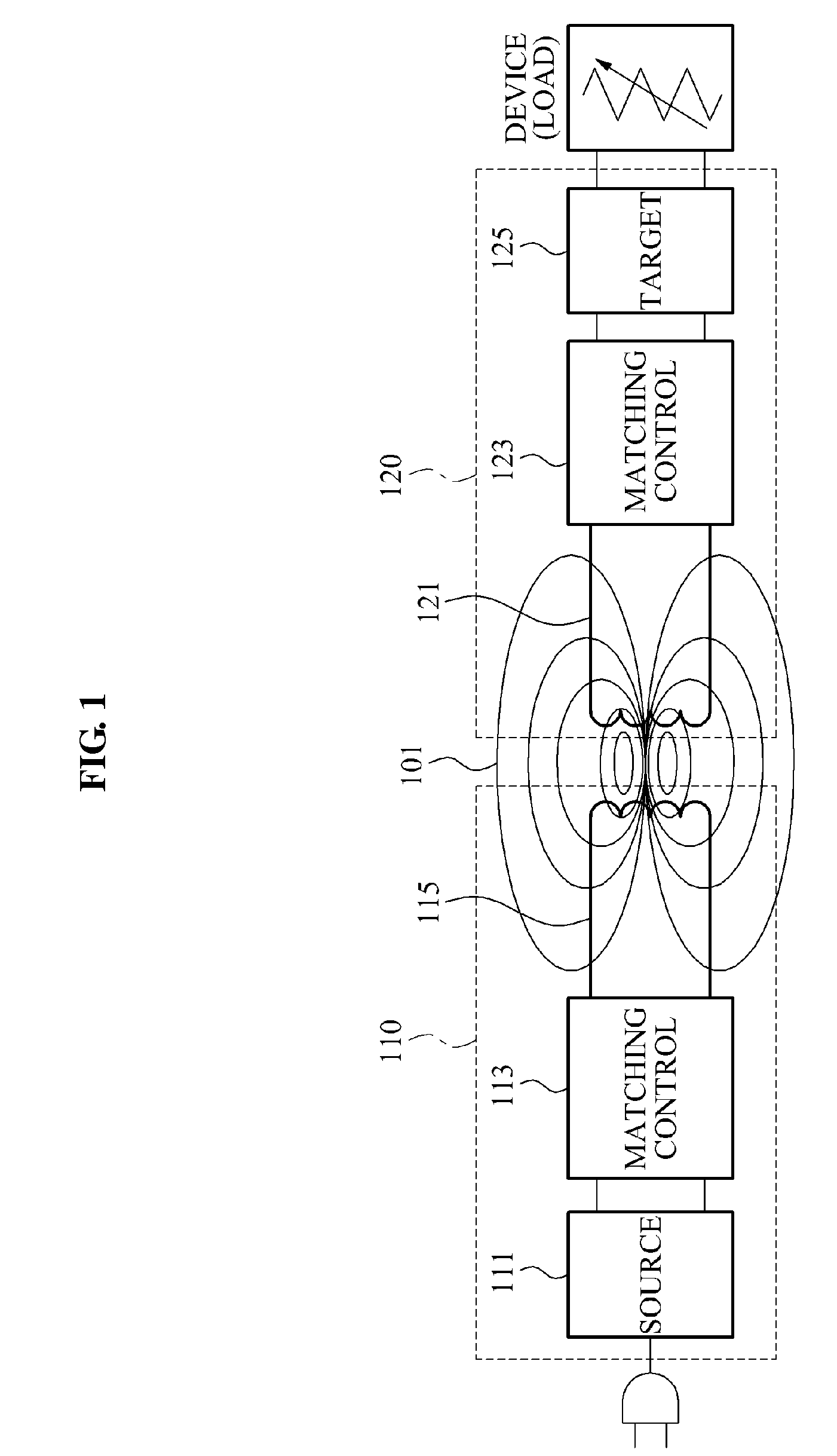

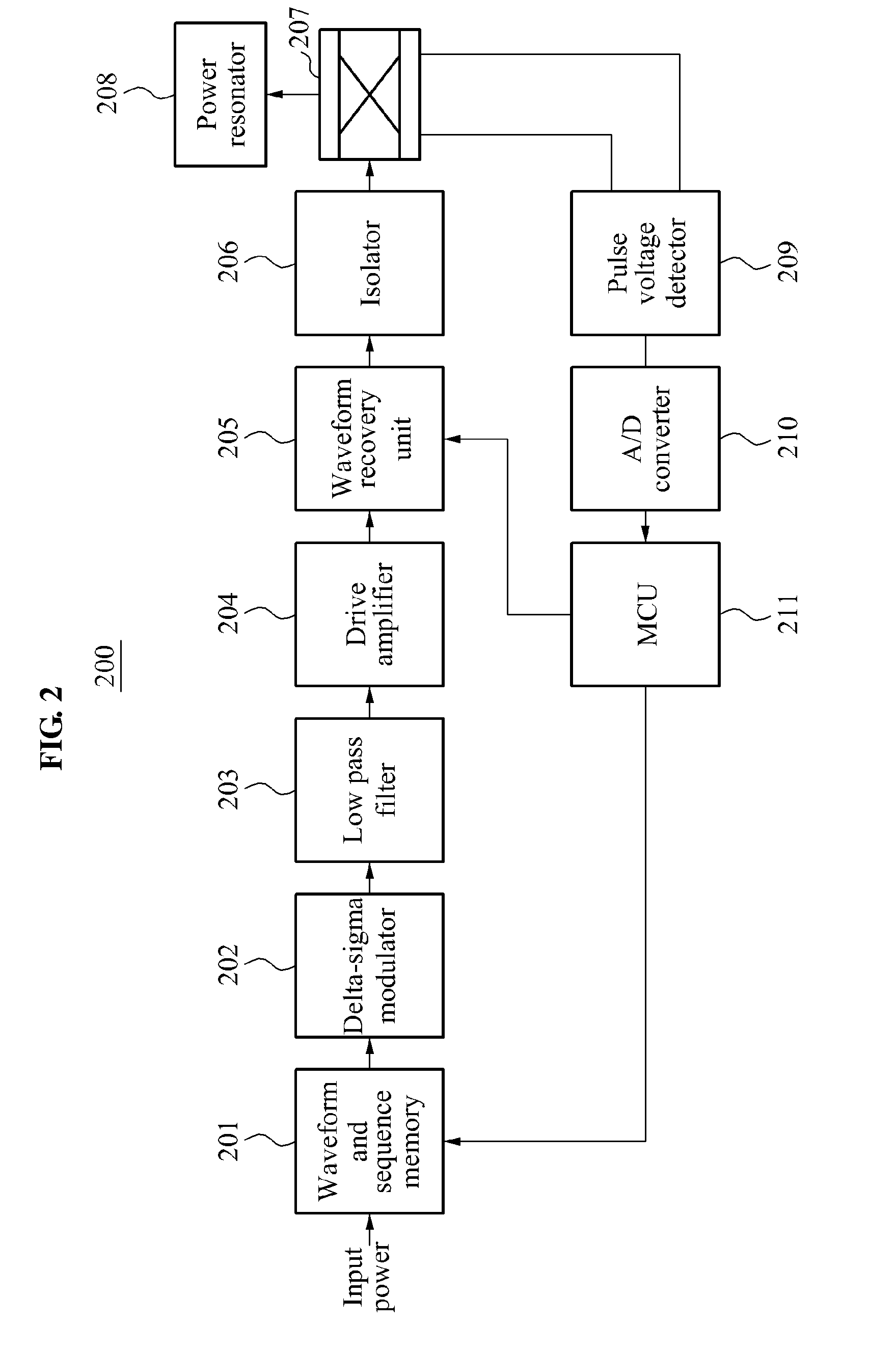

Resonance power generator

A resonate power generator is provided. The resonate power generator may include a waveform and sequence memory to record a predetermined waveform and a predetermined sequence, a delta-sigma modulator to delta-sigma modulate an output signal of the waveform and sequence memory, and a waveform recovery unit to receive, as an input, an output radio frequency (RF) signal of the delta-sigma modulator, and to convert the input into a waveform in a form of an impulse.

Owner:SAMSUNG ELECTRONICS CO LTD

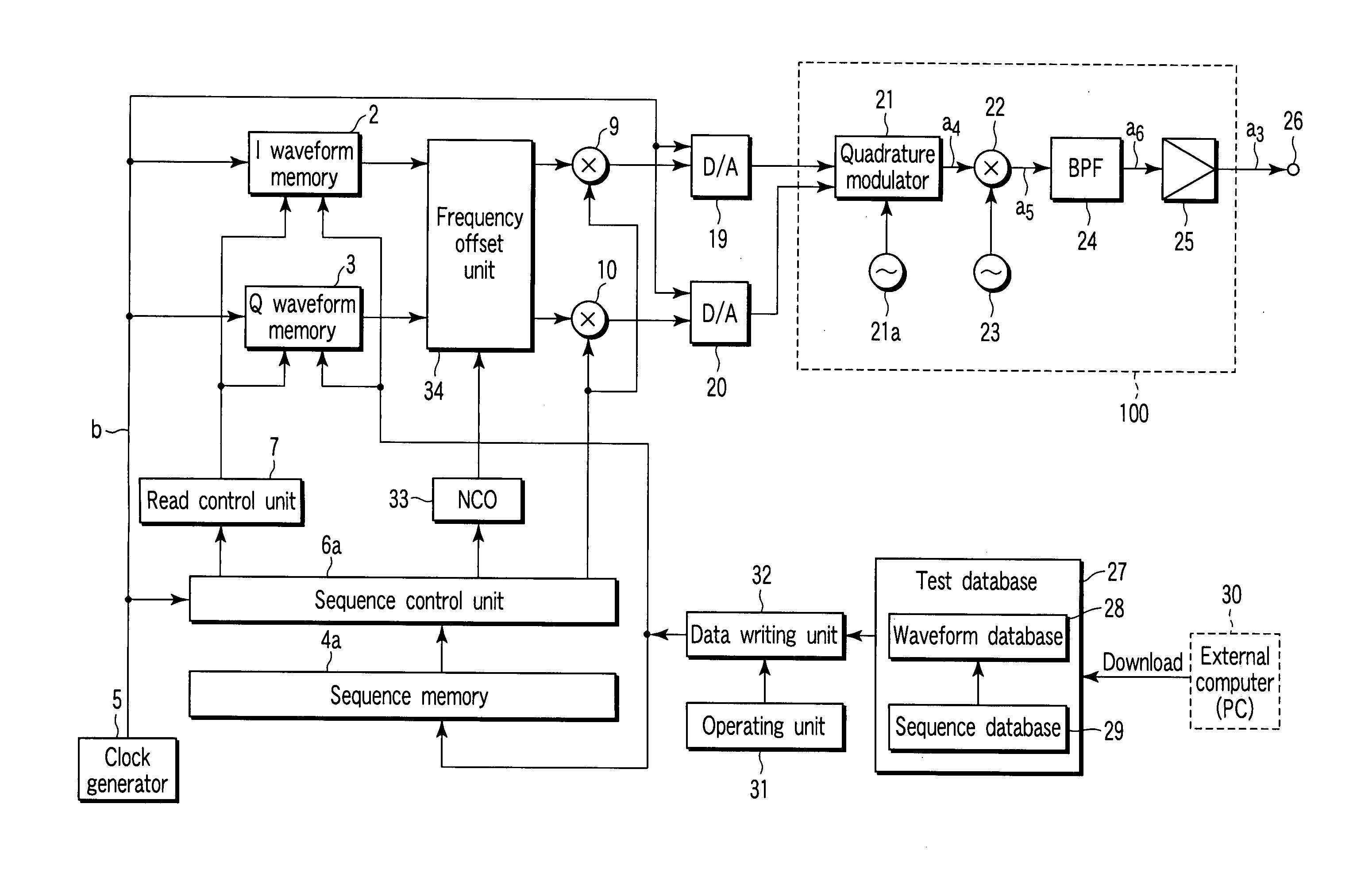

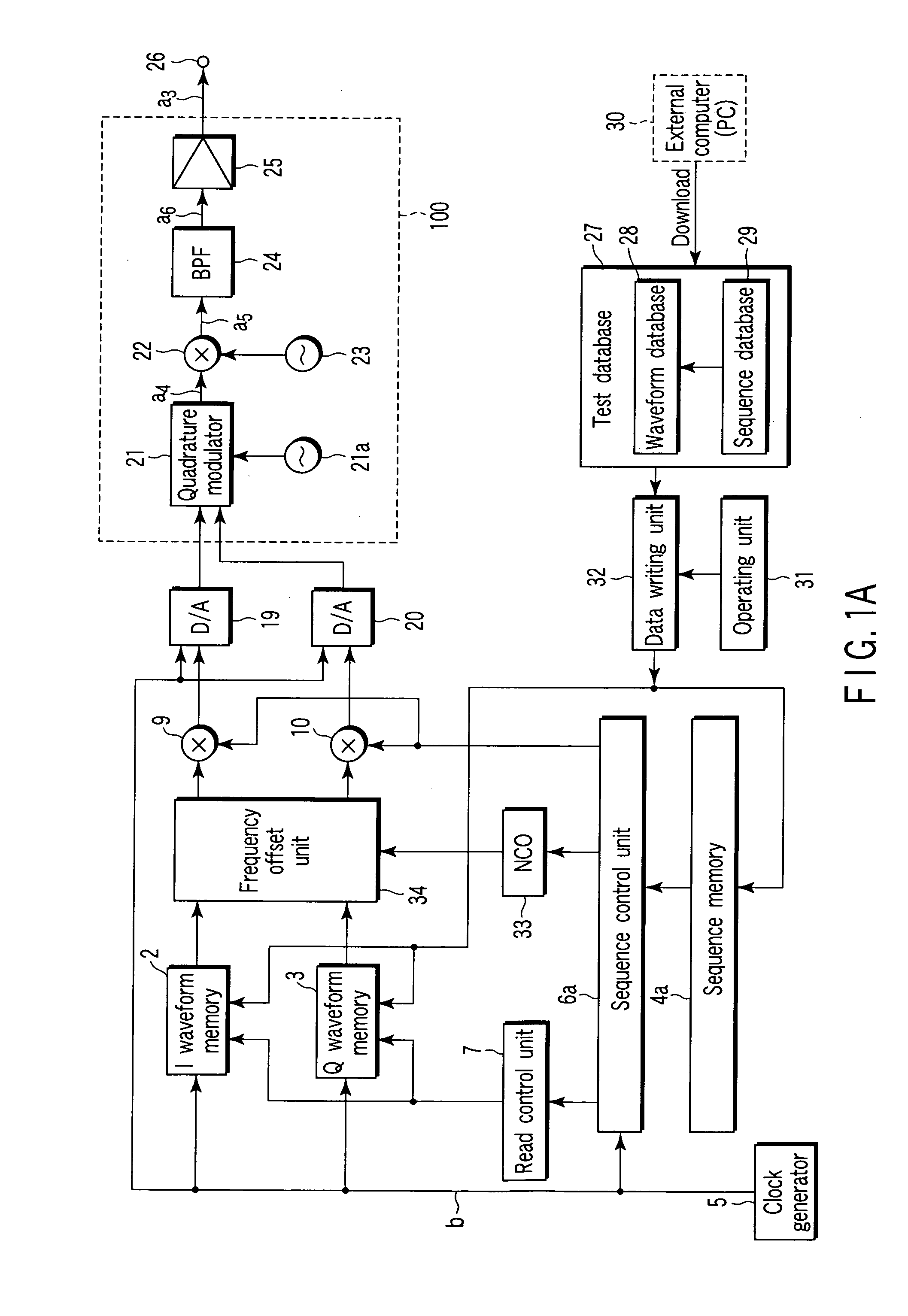

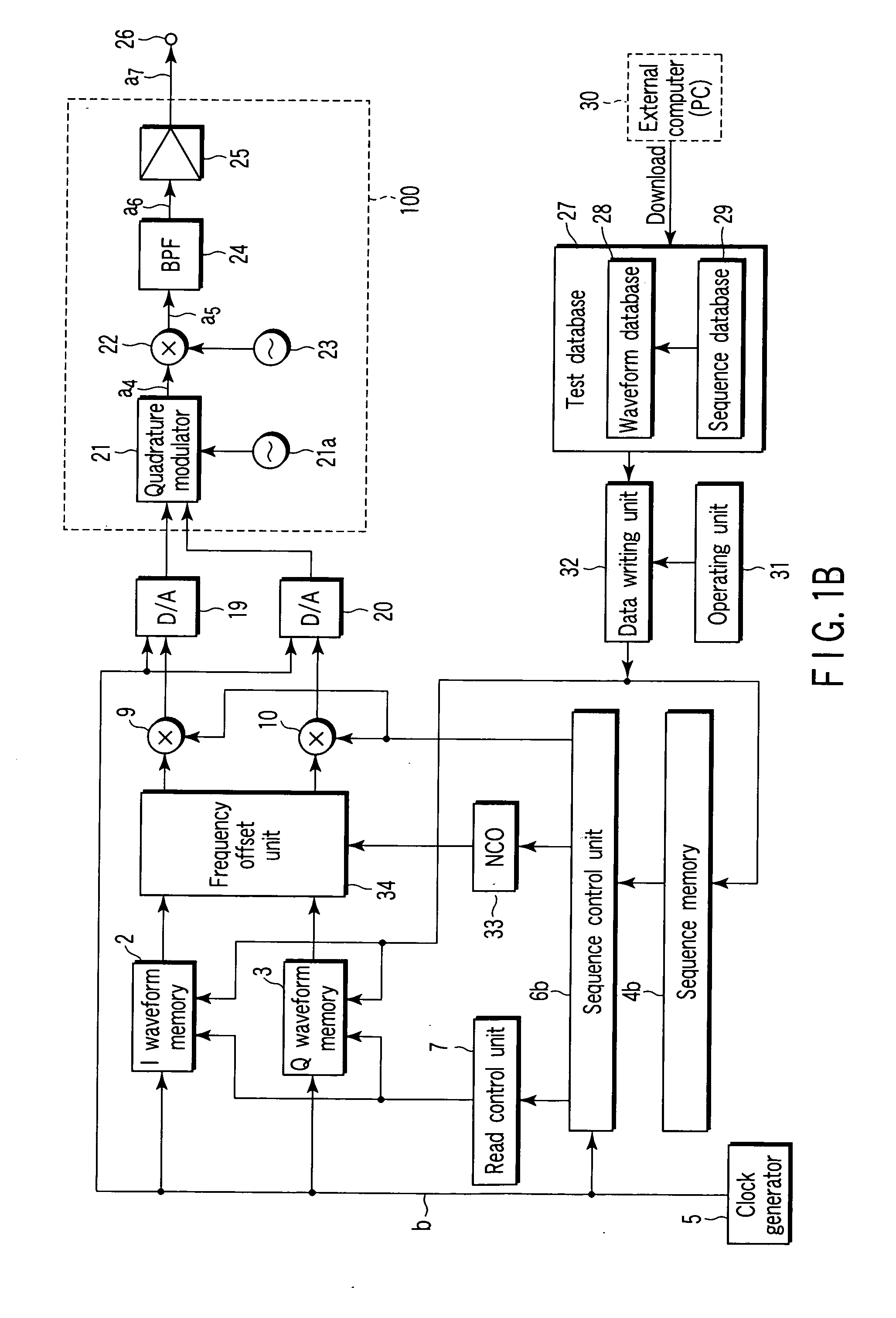

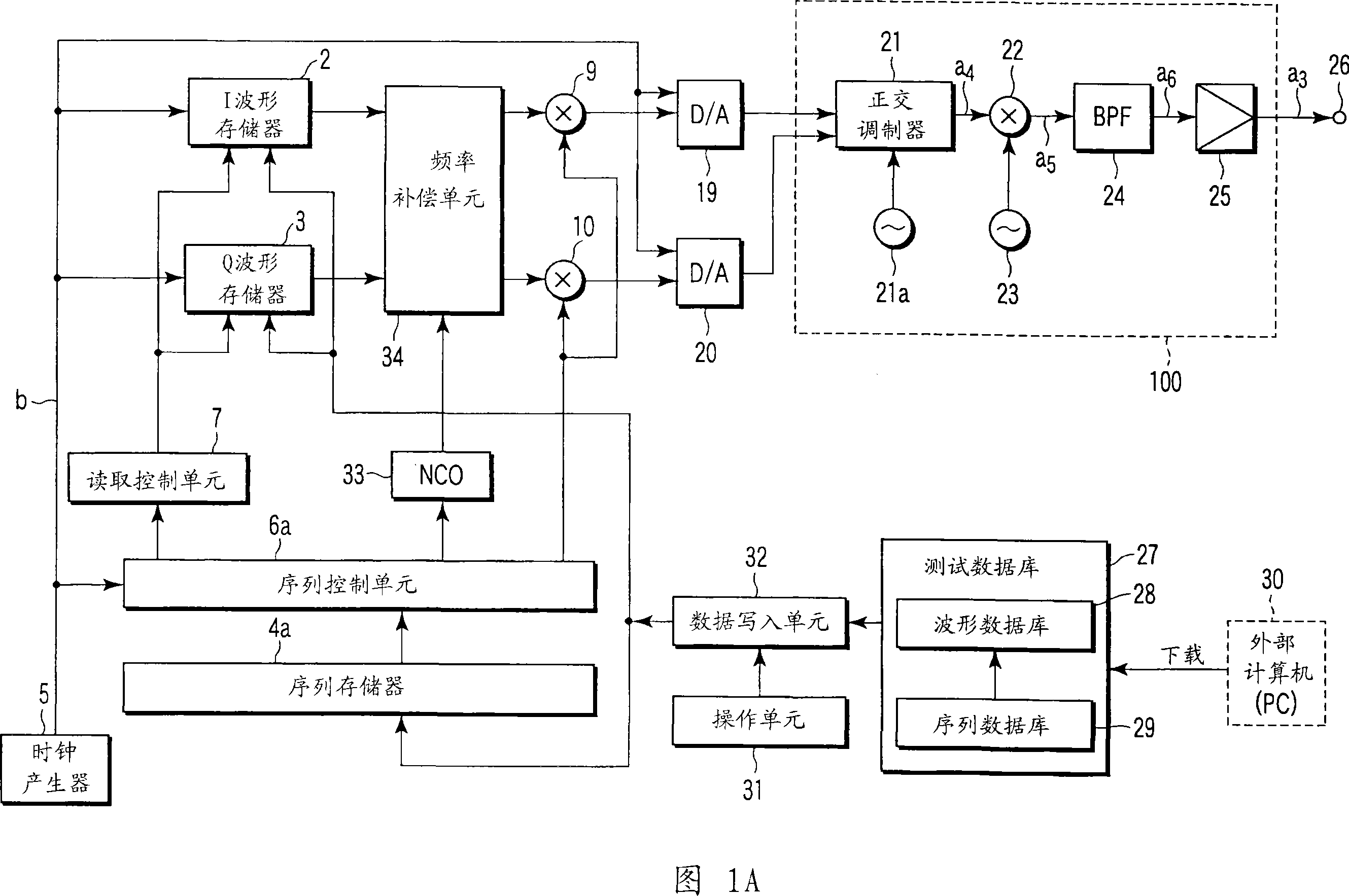

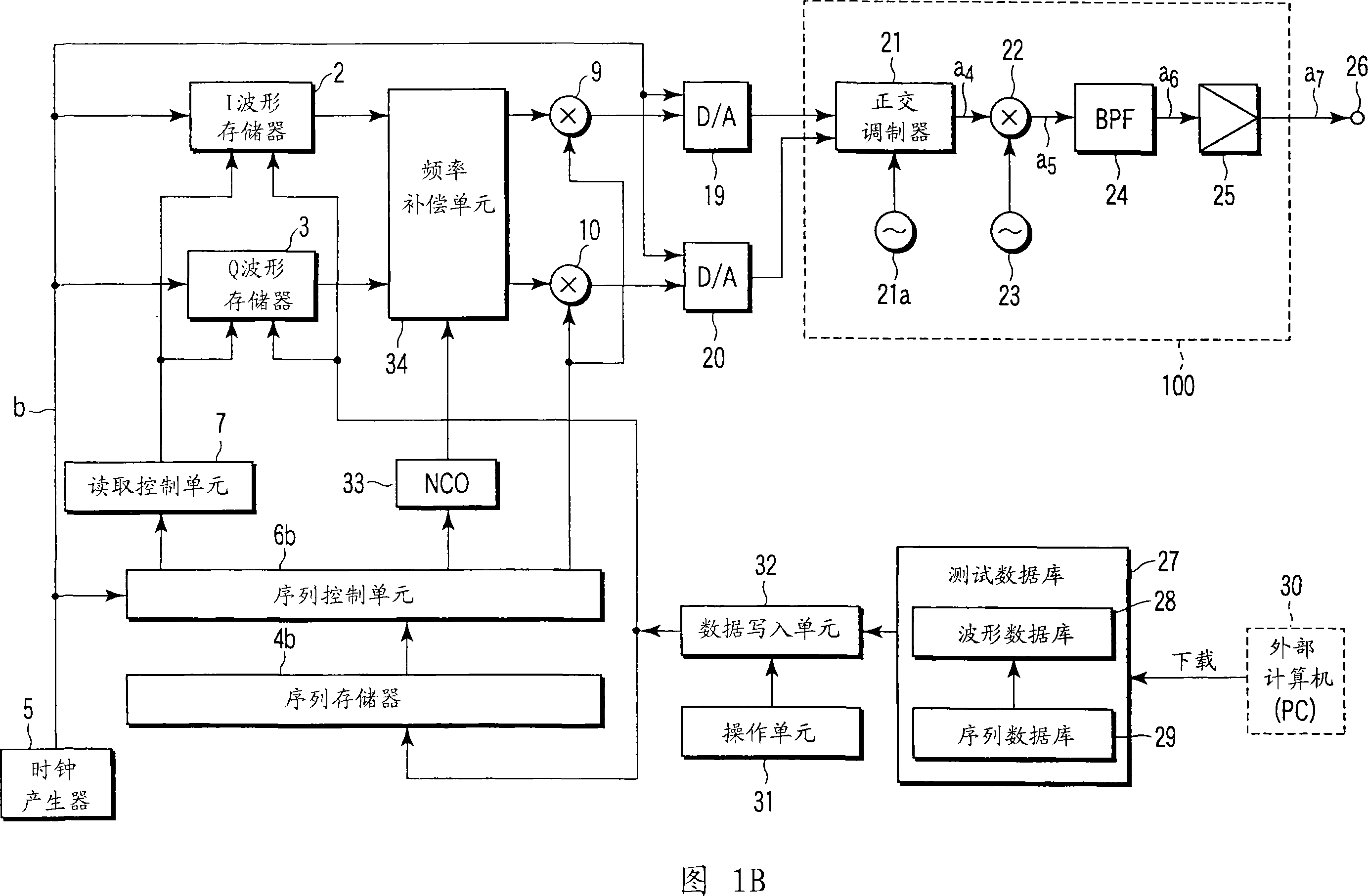

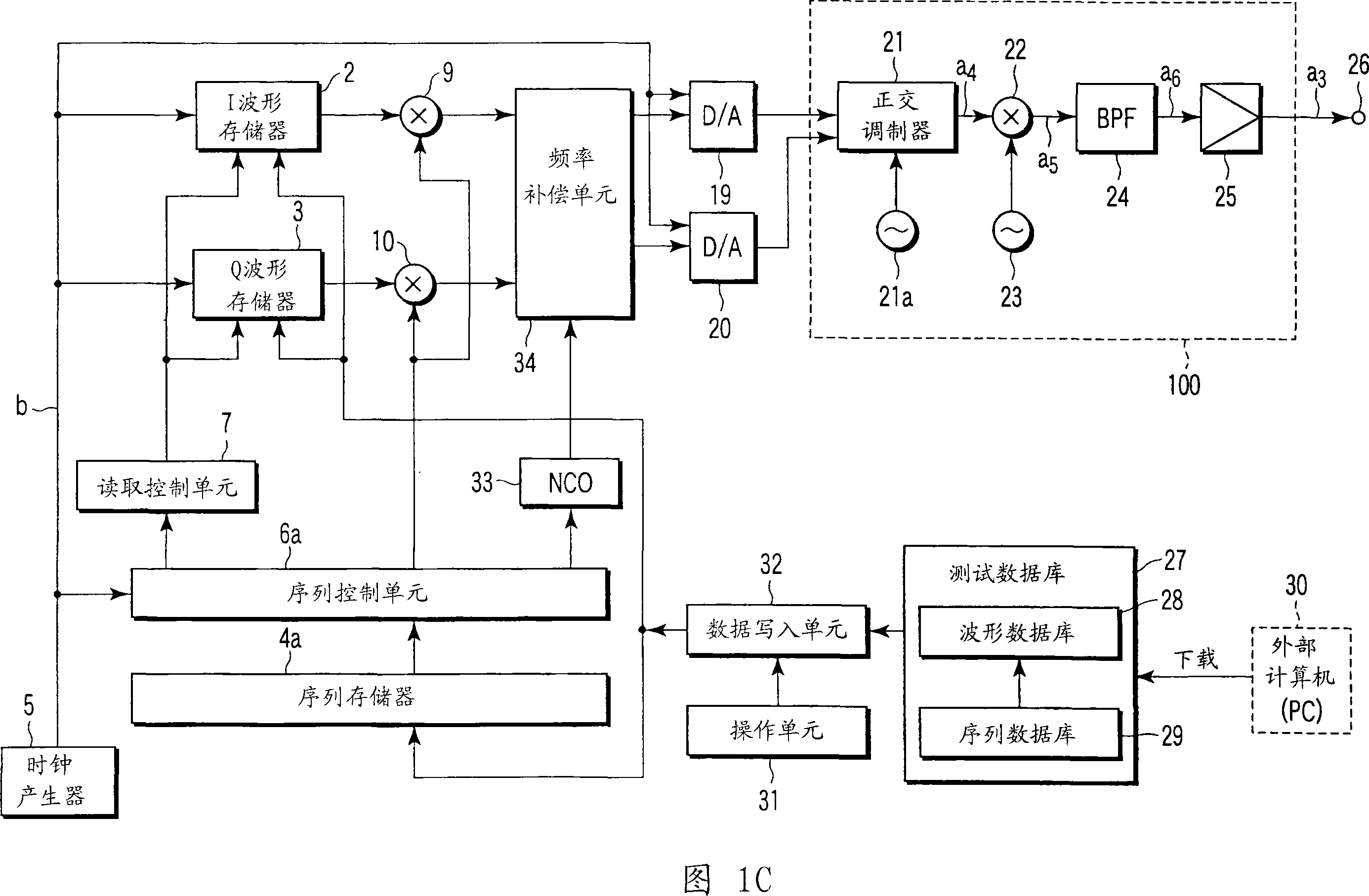

Test Signal Generating Apparatus for Communications Equipment and Test Signal Generating Method for Communications Equipment

InactiveUS20080291987A1Reduce stepsMinimal memory capacityTransmission monitoringLine-transmission monitoring/testingDigital analog converterSequence memory

A test signal generating apparatus for communications equipment sequentially uses first and second sequence information which are stored in a sequence memory for storing the first sequence information including a reading order and read addresses of unit data including I and Q waveform data, and desired signal levels to be set to the unit data, and the second sequence information including frequency offsets. Consequently, the test signal generating apparatus provides frequency offsets at a plurality of steps every predetermined frequency intervals by using a predetermined carrier frequency as a reference, with respect to the I and Q waveform data at a digital stage up to digital-to-analog converters, and outputs a test signal in the frequency hopping system.

Owner:ANRITSU CORP

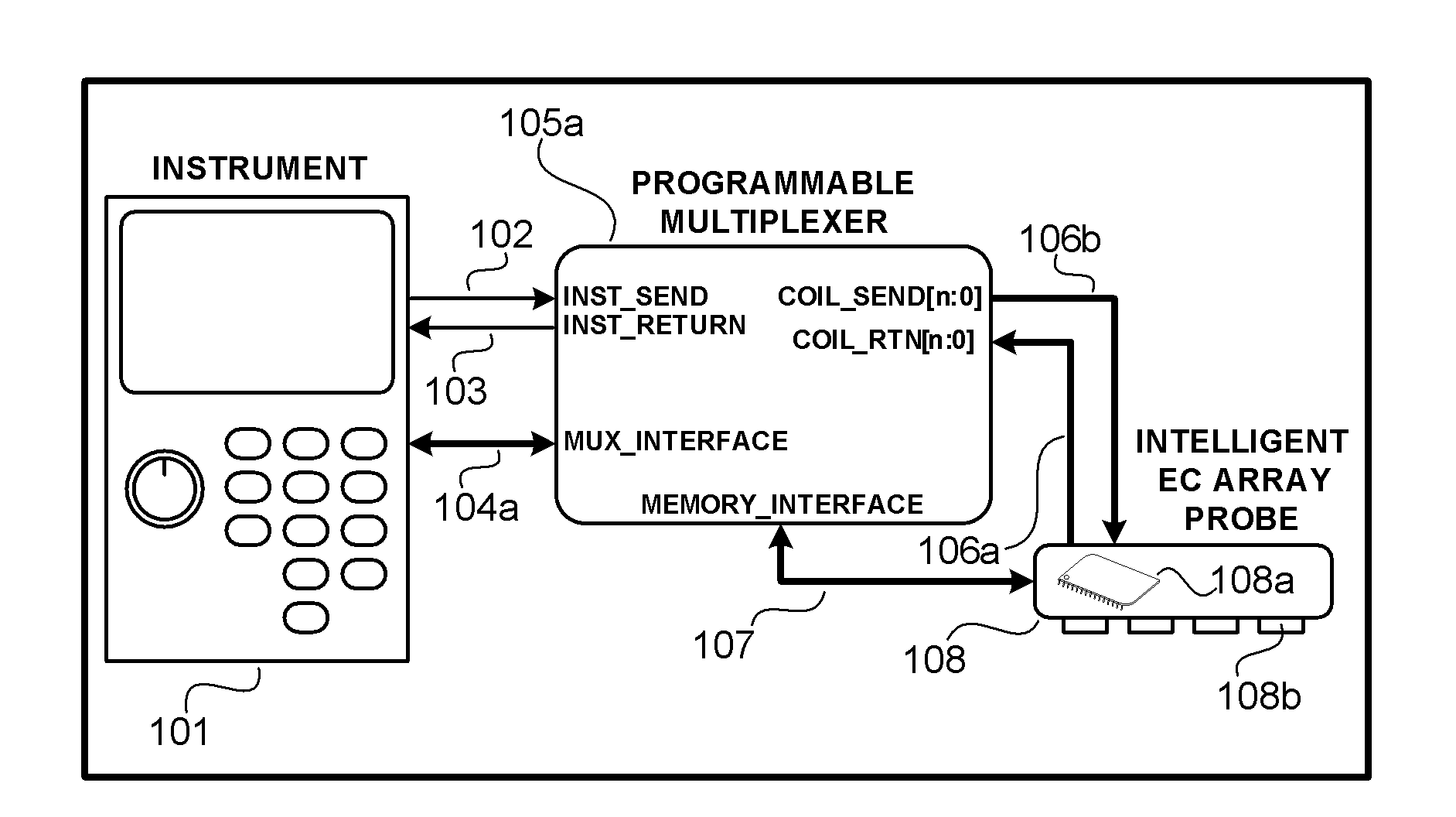

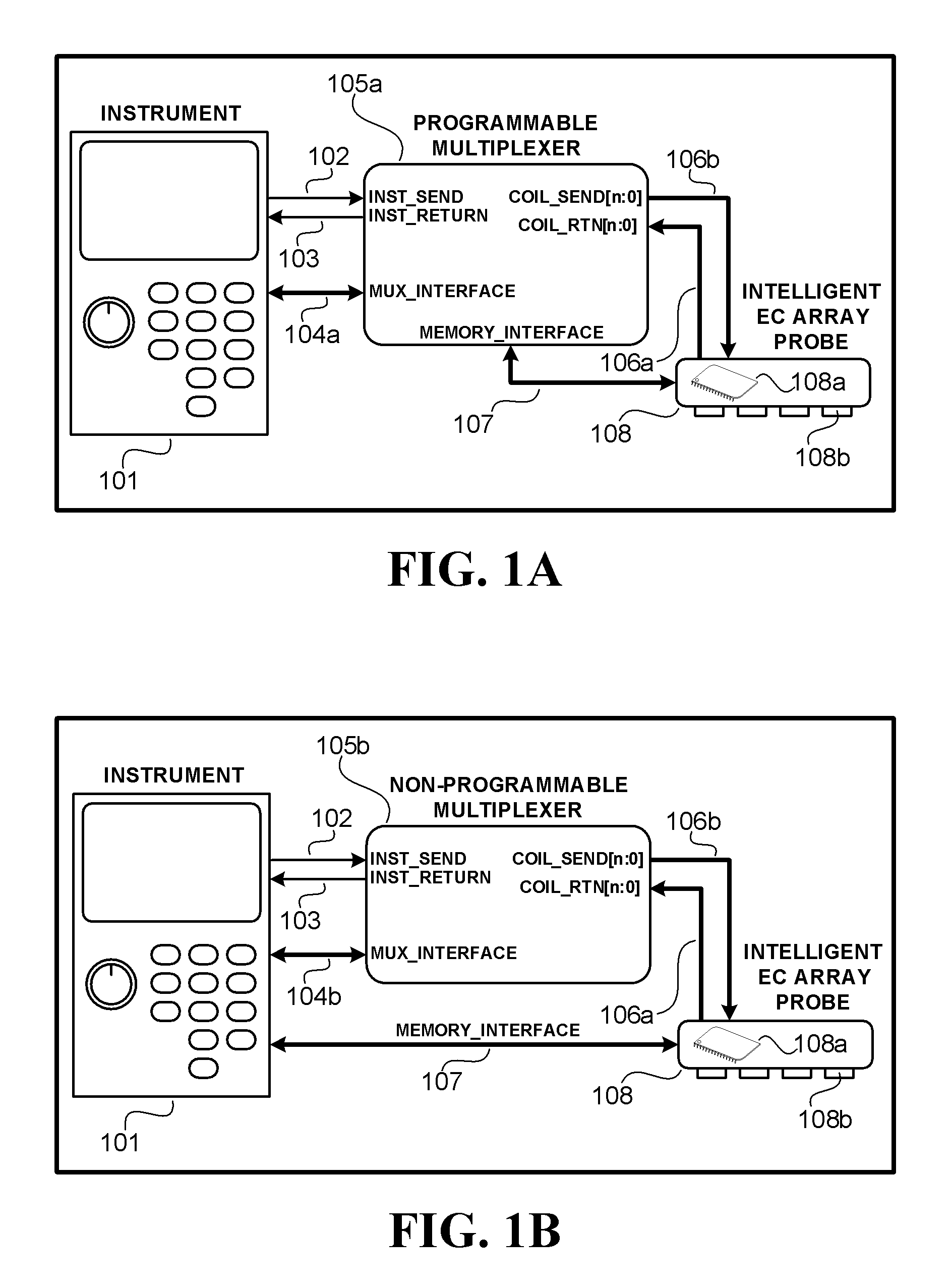

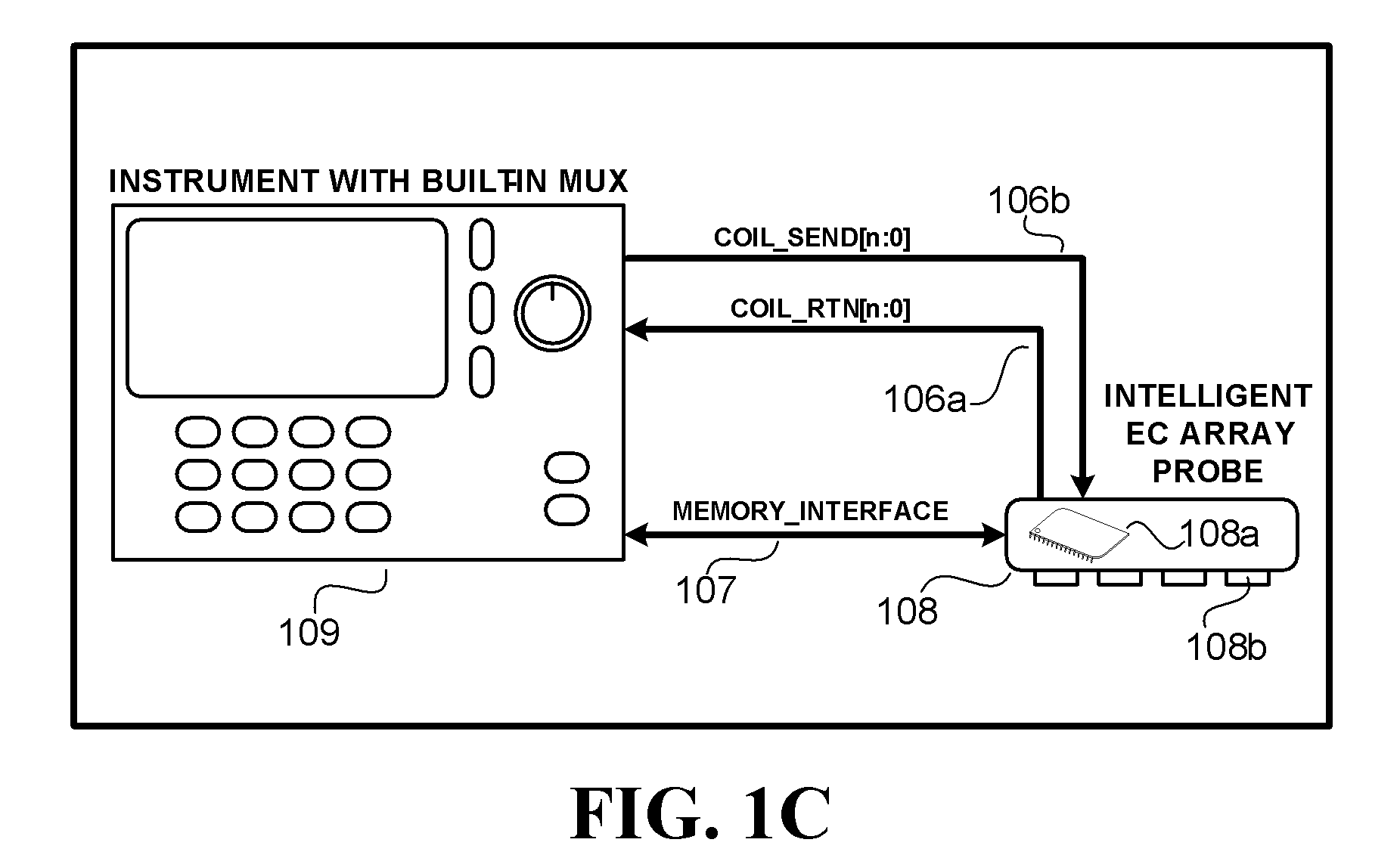

Intelligent eddy current array probe with embedded firing sequence memory

ActiveUS20090243605A1Good flexibilityMagnetic property measurementsMaterial magnetic variablesSequence memoryEddy current

An intelligent eddy current array probe comprising a plurality of coil elements and an embedded non-volatile memory element is disclosed. Prior to coupling the intelligent eddy current array probe to an NDI system, a data table describing a desired firing sequence for the array probe within a given inspection operation is created. This data table is then stored within the embedded non-volatile memory element of the intelligent eddy current array probe such that when the array probe is coupled to the NDI system, the elements of the NDI system can load and execute the stored firing sequence without operator intervention. In this way, a plurality of intelligent eddy current array probes, each with its own firing sequence, can be used interchangeably within a single NDI system without the need for mechanical adjustments to the NDI system.

Owner:OLYMPUS NDT

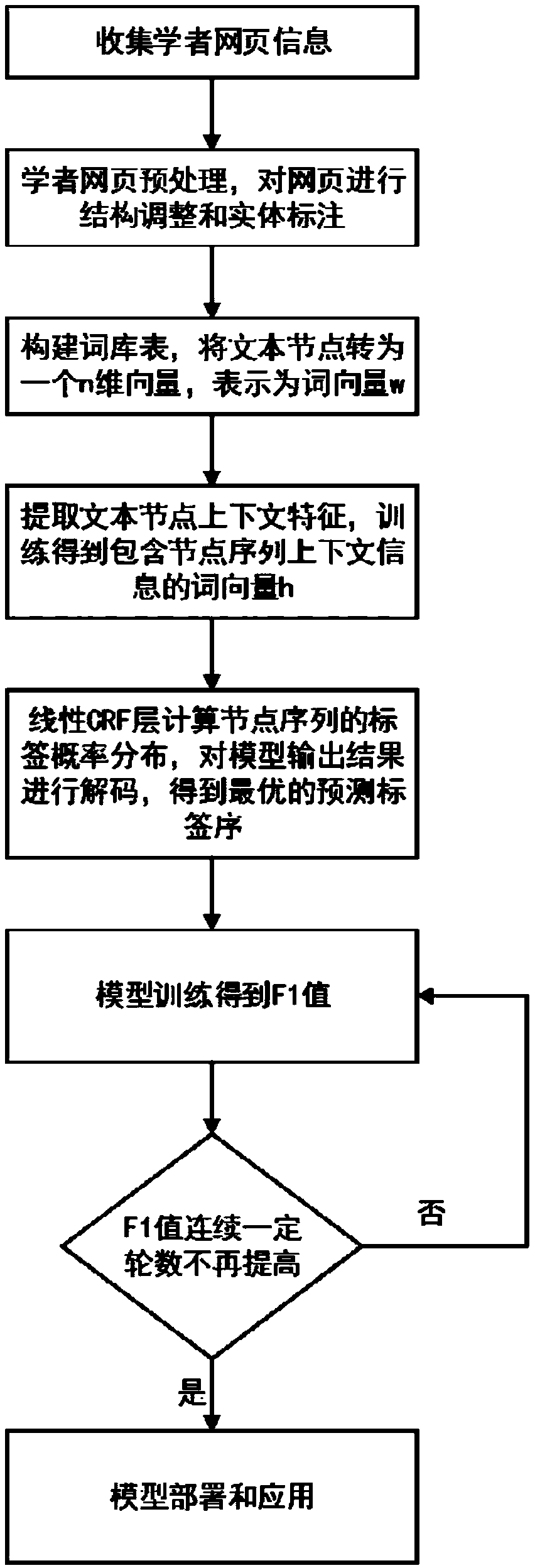

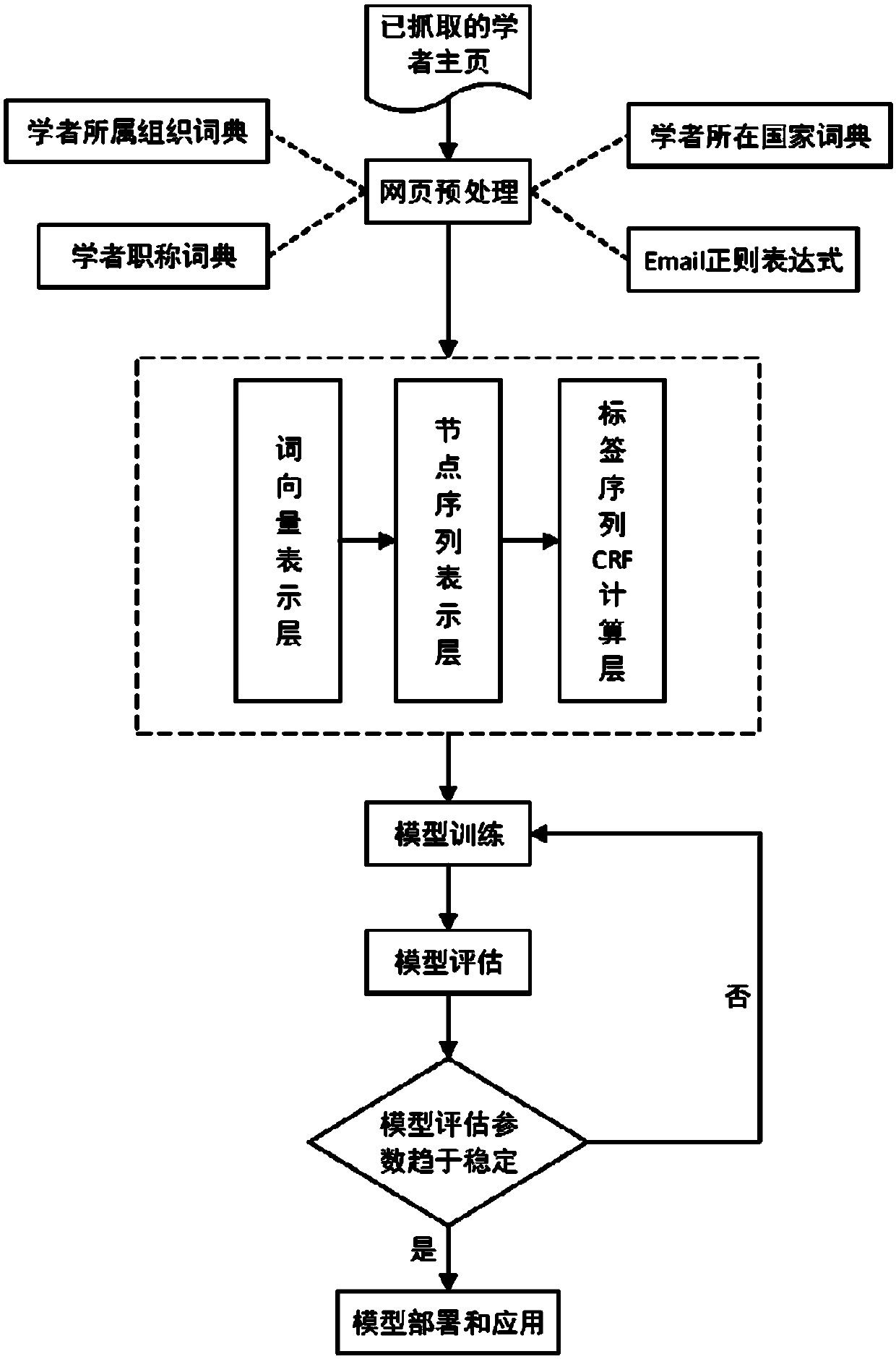

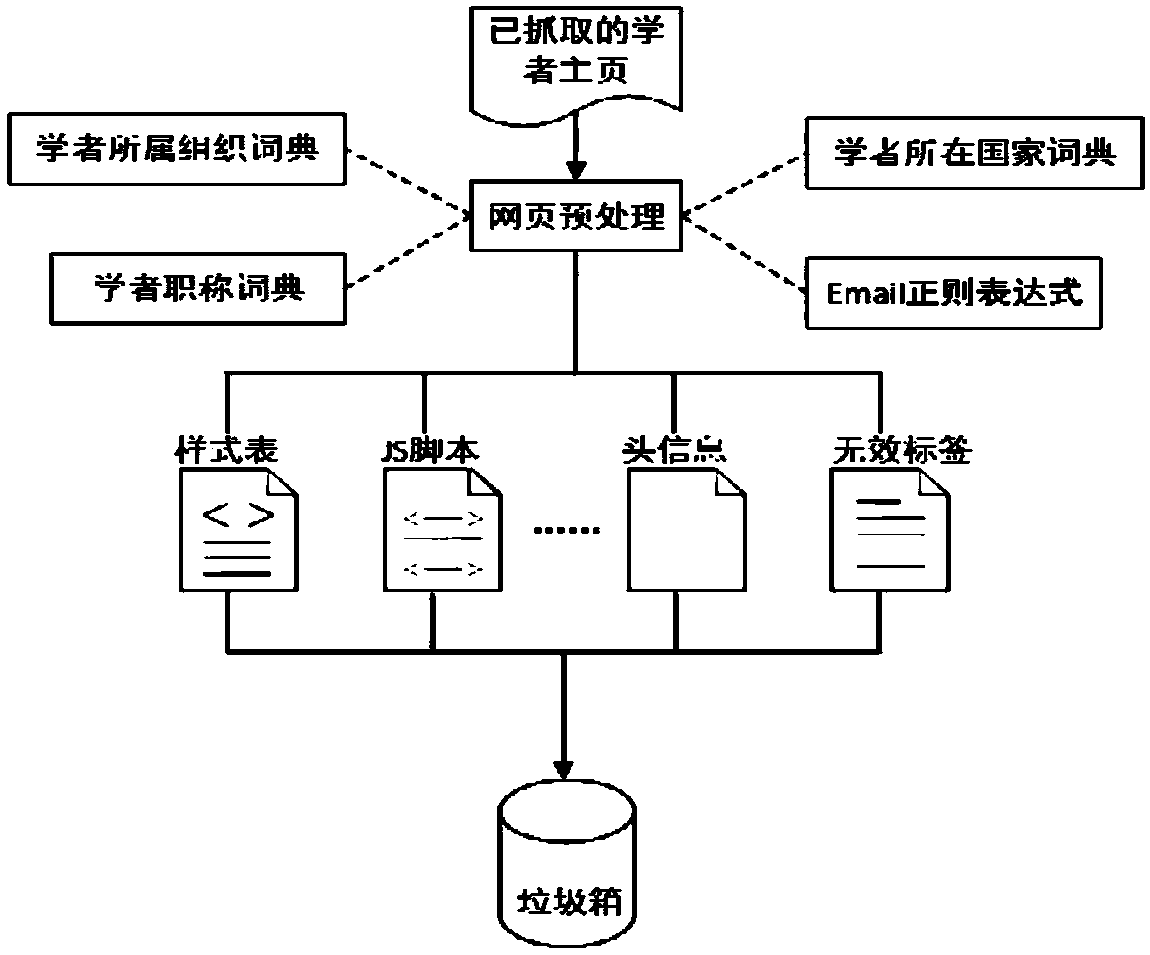

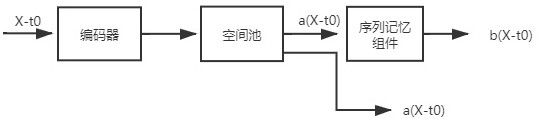

Neural network-based scholarship user portrait information extraction method and model

ActiveCN109657135ASolve long-term dependency problemsAchieve trainingDigital data information retrievalNatural language data processingSequence memoryEngineering

The invention relates to a neural network-based scholarship user portrait information extraction method, which comprises the following steps of: carrying out text preprocessing on a webpage, and carrying out structure adjustment and entity labeling on the webpage; constructing Word library tables for all the text nodes and characters thereof of the identified webpage; Extracting context features of the text nodes and the front and rear nodes, and then training a text node sequence to obtain a word vector h containing node sequence context information; And performing decoding calculation on theword vector output, correspondingly obtaining the score of each word vector on the target tag, calculating the tag probability distribution of the node sequence, decoding a model output result, obtaining an optimal prediction tag sequence when the target function is minimum, completing model construction, and performing model training. According to the method, end-to-end training of the model canbe realized, and the problem of long-term dependency between target extraction entities is effectively solved by utilizing the sequence memory characteristic of the LSTM network.

Owner:SOUTH CHINA UNIV OF TECH

Ultrasound transmit beamformer integrated circuit and method

ActiveUS20080200809A1Compact implementationLow costUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsPulse envelopeIntermediate frequency

The invention provides a novel method of transmit beamforming, which allows compact analog implementation of complex digital algorithms without compromising their features. It is aimed to support envelope shaping, apodization, and phase rotation per channel and per firing. Each of three embodiments represents a complete transmit channel driven by pulse-width modulated (PWM) waveforms stored in a conventional sequence memory. PWM signals controls the transmit pulse envelope (shape) by changing the duty cycle of the carrier. Beamformation data are loaded prior to a firing via serial interface. Under the direction of a controller, the circuitry allows high precision (beyond sampling rate) phase rotation of the carrier. It also provides transmit apodization (aperture weighting), which maintains an optimal trade-off among low sidelobe level and widening of the mainlobe. Implementing such an IC, the manufacturing cost of a high-end ultrasound system can be reduced. Equally, the proposed solution makes the benefits of digital transmit beamformers available to midrange and entry-level machines since it merely requires a modified programming of the sequence memory.

Owner:MICROCHIP TECH INC

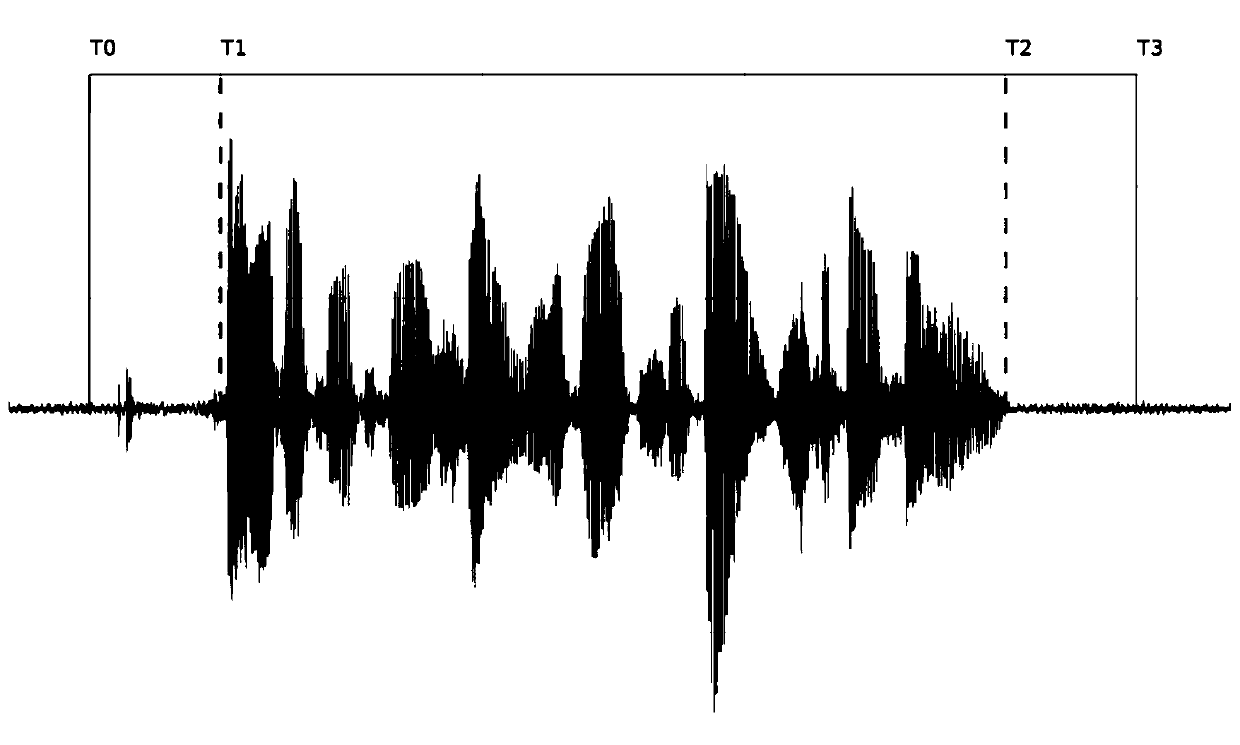

Voice wake-up detection method, device and equipment and storage medium

ActiveCN110619871AReduce occupancyReduce the number of framesSpeech recognitionHigh level techniquesMultiple frameSequence memory

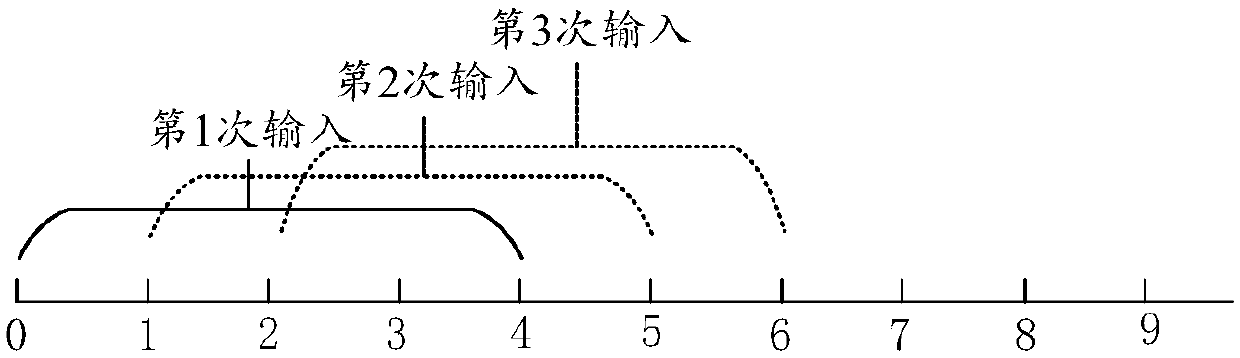

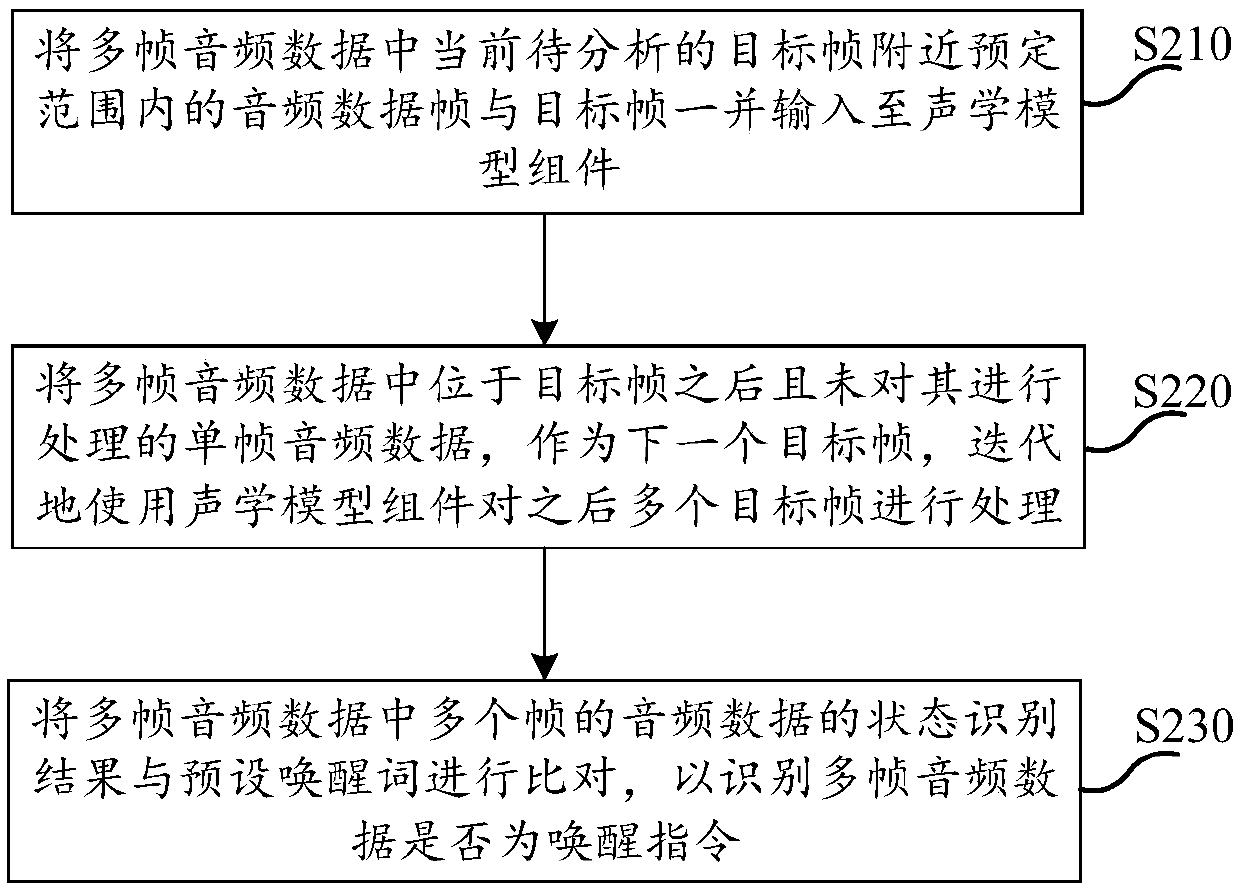

The invention provides a voice wake-up detection method and device, equipment and a storage medium. The method comprises steps of inputting an audio data frame in a preset range near a target frame inmultiple frames of audio data and a target frame into an acoustic model assembly together, wherein the acoustic model assembly is a feedforward sequence memory neural network model assembly, and theoutput of the acoustic model assembly is a state recognition result of the target frame and at least one frame of audio data in audio data frames within a predetermined range; taking a single frame ofaudio data which is located behind the target frame and does not be processed in the multiple frames of audio data as a next target frame, and iteratively using the acoustic model assembly to processa plurality of subsequent target frames; and comparing the state identification result of the audio data of the plurality of frames in the plurality of frames of audio data with a preset wake-up wordto identify whether the plurality of frames of audio data are wake-up instructions or not. Therefore, good awakening performance can be guaranteed while occupation of equipment end resources is reduced, and the requirement for real-time performance required by awakening is met.

Owner:ALIBABA GRP HLDG LTD

Memory control apparatus and method for scheduling commands

Owner:SAMSUNG ELECTRONICS CO LTD

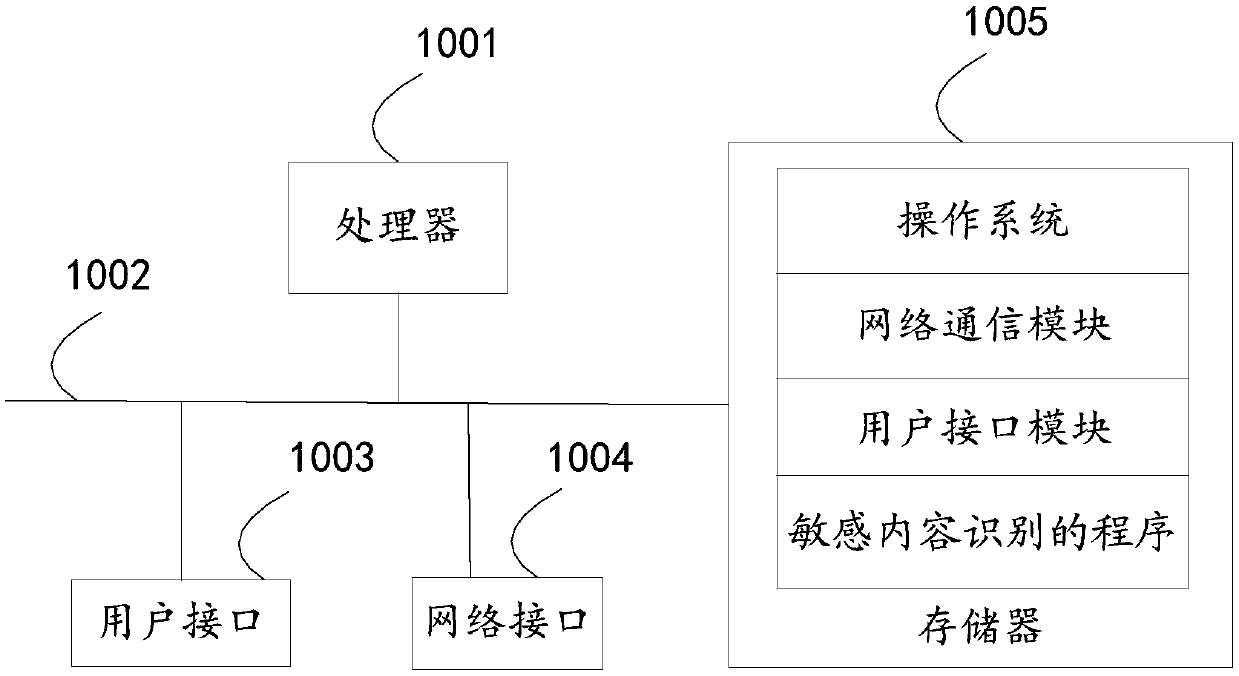

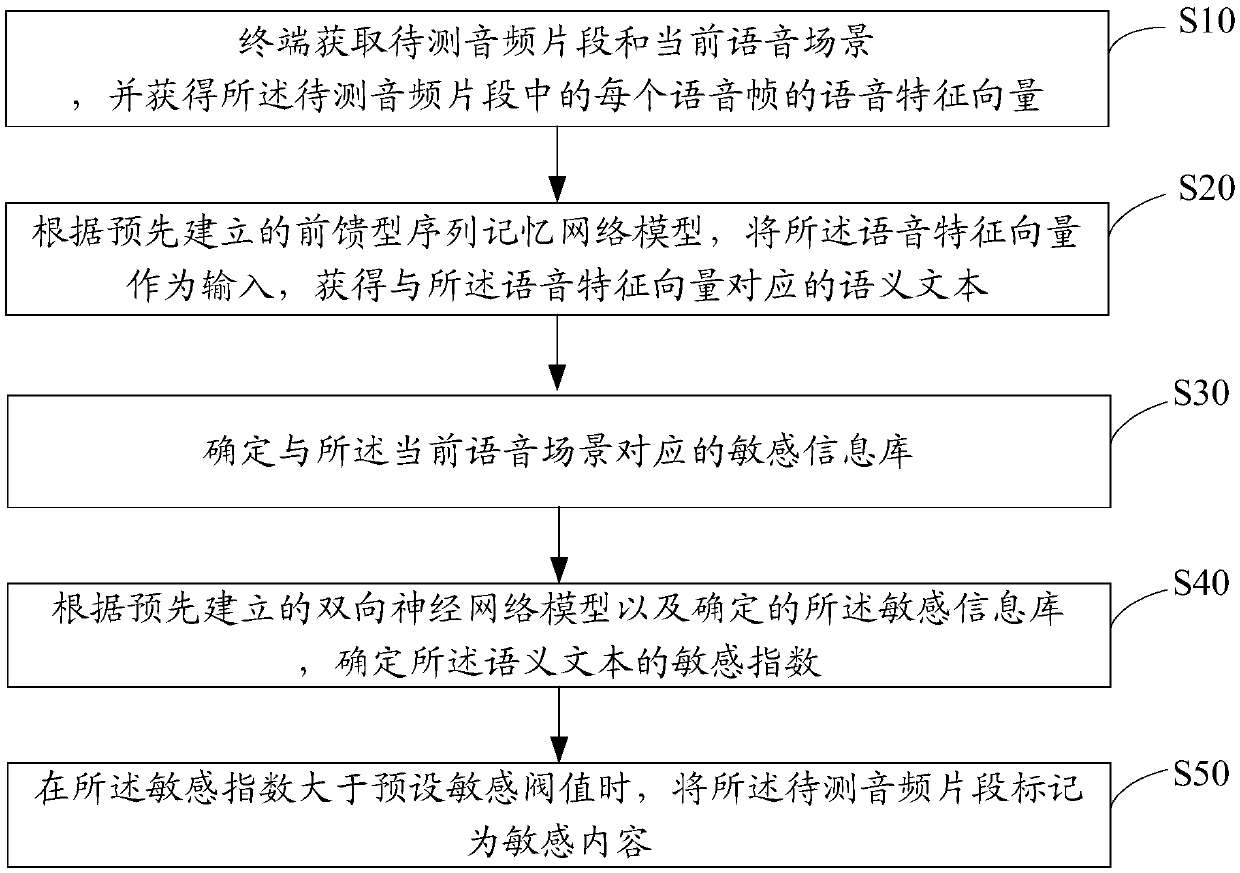

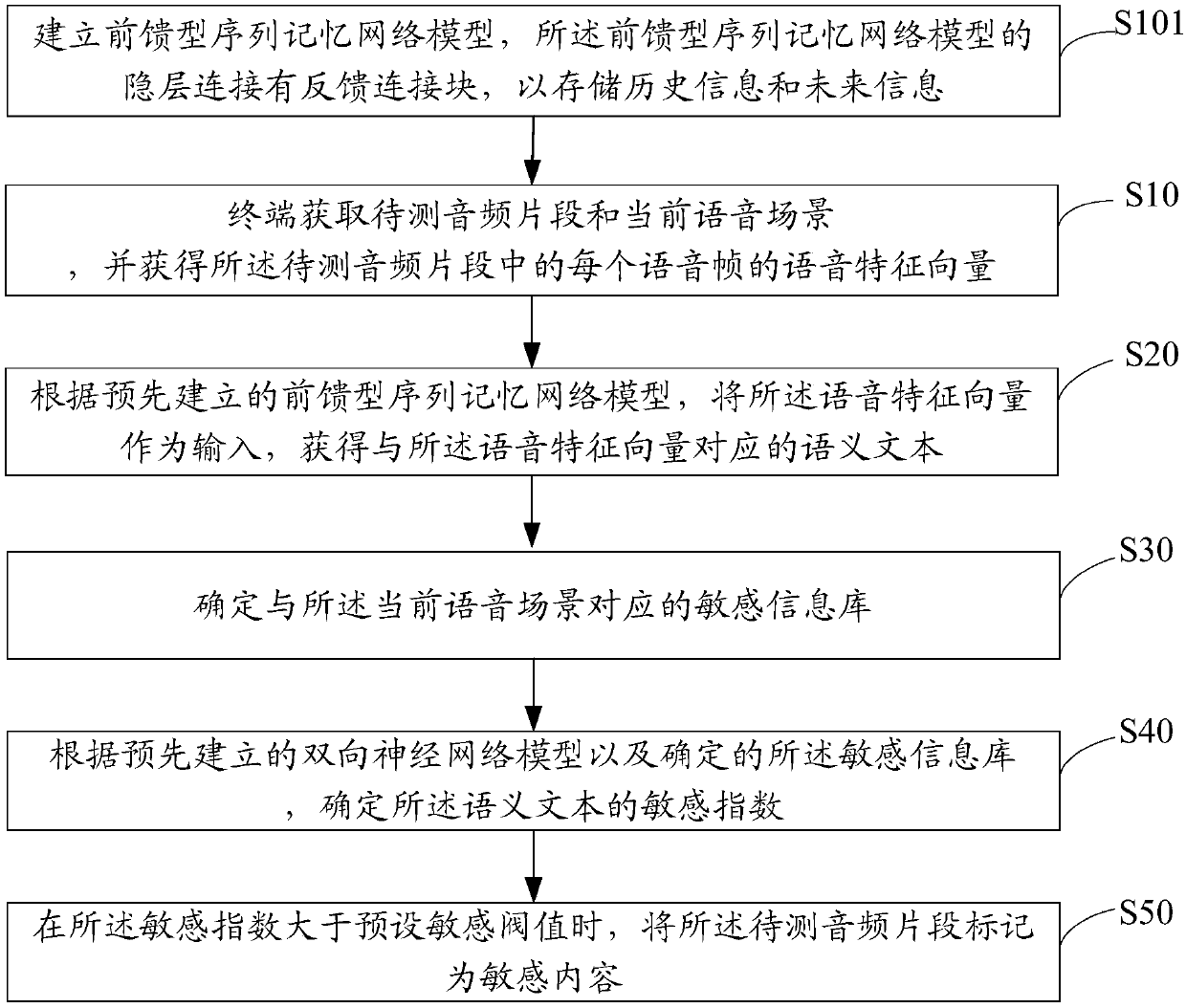

Sensitive content identification method, device and terminal based on voice analysis and medium

ActiveCN109637520AImprove accuracySolve the technical problem of inaccurate recognitionSpeech recognitionHigh level techniquesFeature vectorInformation repository

The invention discloses a sensitive content identification method, device and terminal based on voice analysis and a medium, wherein the terminal acquires an audio segment to be detected and a currentvoice scene and acquires a voice characteristic vector of each voice frame in the audio segment to be detected, according to a pre-established feedforward sequence memory network model, semantic textcorresponding to the voice feature vector is obtained by using the voice characteristic vector as an input, and a sensitive information base corresponding to the current voice scene is determined, different voice scenes correspond to different sensitive information bases, the accuracy of judging sensitive contents is improved, a sensitivity index of the semantic text is determined according to abidirectional neural network model established in advance and the determined sensitive information bases, and the semantic text is compared with the semantics of the sensitive information bases to further improve the accuracy, and the audio segment to be detected is marked as sensitive content when the sensitivity index is larger than a preset sensitivity threshold.

Owner:PING AN TECH (SHENZHEN) CO LTD

Non-volatile sequent modular memory, data storage and reading method

InactiveCN101329906AImprove read and write speedIncrease the number of repeatable reads and writesRead-only memoriesDigital storageComputer architecturePhase-change memory

The invention discloses a nonvolatile sequence module memory which is divided into a plurality of memory blocks. The data information of every memory block is assigned to a uniform address, a random writing and reading mode is adopted among all memory blocks and a sequence memory mode is adopted in the memory block. Aiming at a great deal of data memory, the memory of the invention changes the disadvantages of an RAM memory mode and proposes a set of novel nonvolatile sequence module memory and a memory and writing and reading method, thereby being capable of improving the writing and reading speed of a phase-change memory chip and writing and reading repetition times and reducing power consumption.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

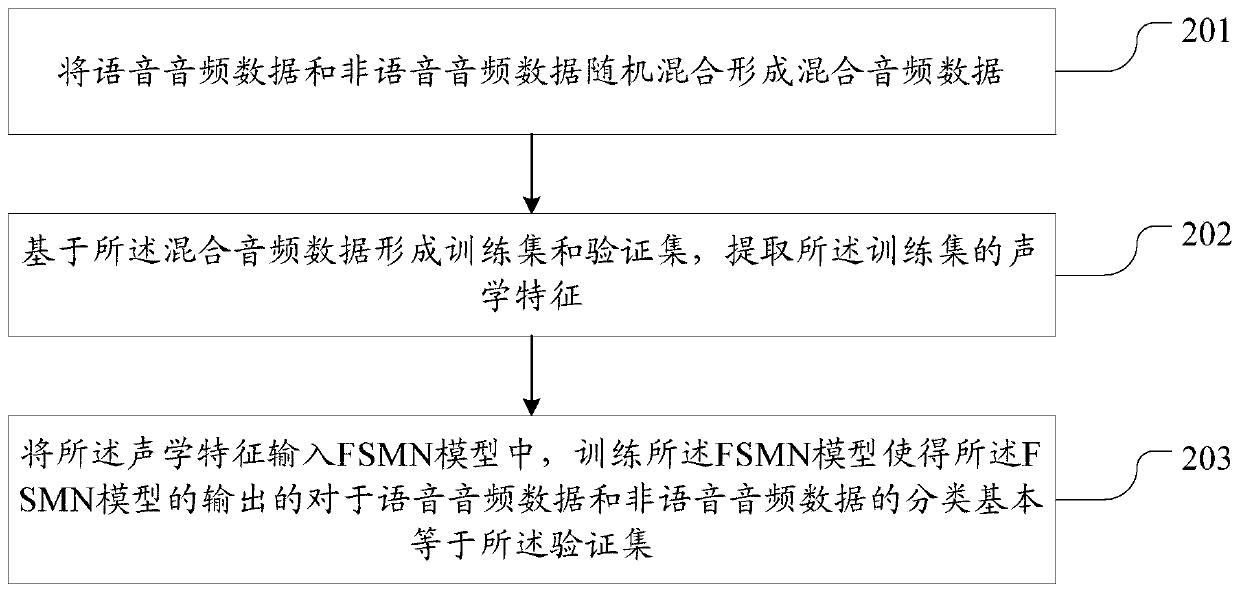

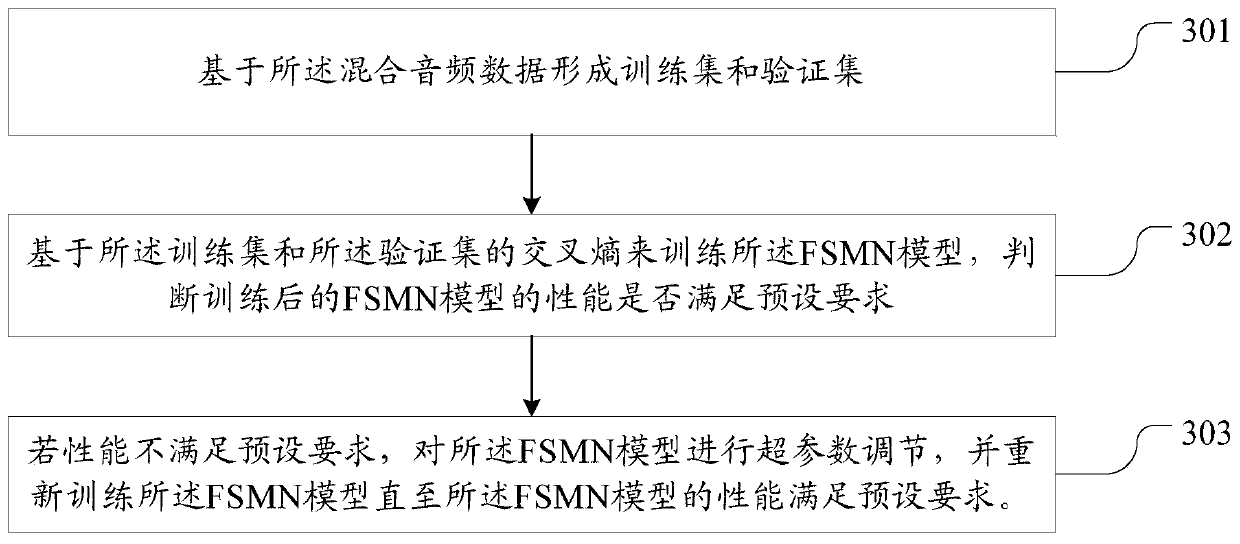

Neural network training and voice endpoint detection method and device

The invention discloses a neural network training and voice endpoint detection method and device. The method comprises the steps: randomly mixing voice audio data and non-voice audio data to form mixed audio data; extracting acoustic features of the mixed audio data; and inputting the acoustic features into an FSMN model, and training the FSMN model to enable the classification of the voice audiodata and the non-voice audio data output by the FSMN model to be basically equal to the classification of the voice audio data and the non-voice audio data in the mixed audio data. According to the method, the non-voice audio data and the voice audio data are mixed and then the mixed data are used for inputting of a feedforward sequence memory neural network to train the neural network, so that the neural network can output information that whether the audio data units belong to voice audio data or non-voice audio data and then the information can be used for voice endpoint detection, and theresult of voice endpoint detection is more accurate.

Owner:AISPEECH CO LTD

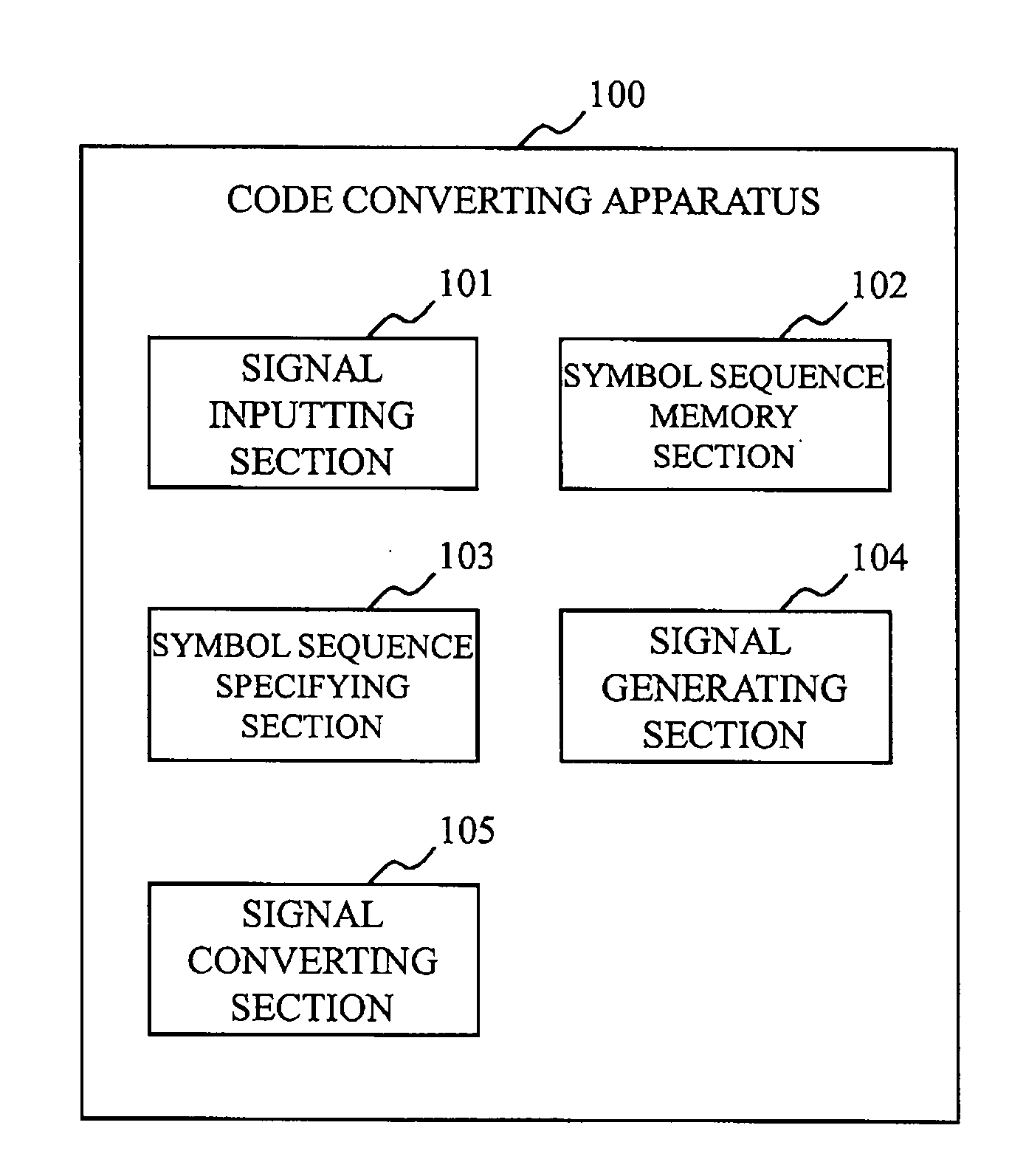

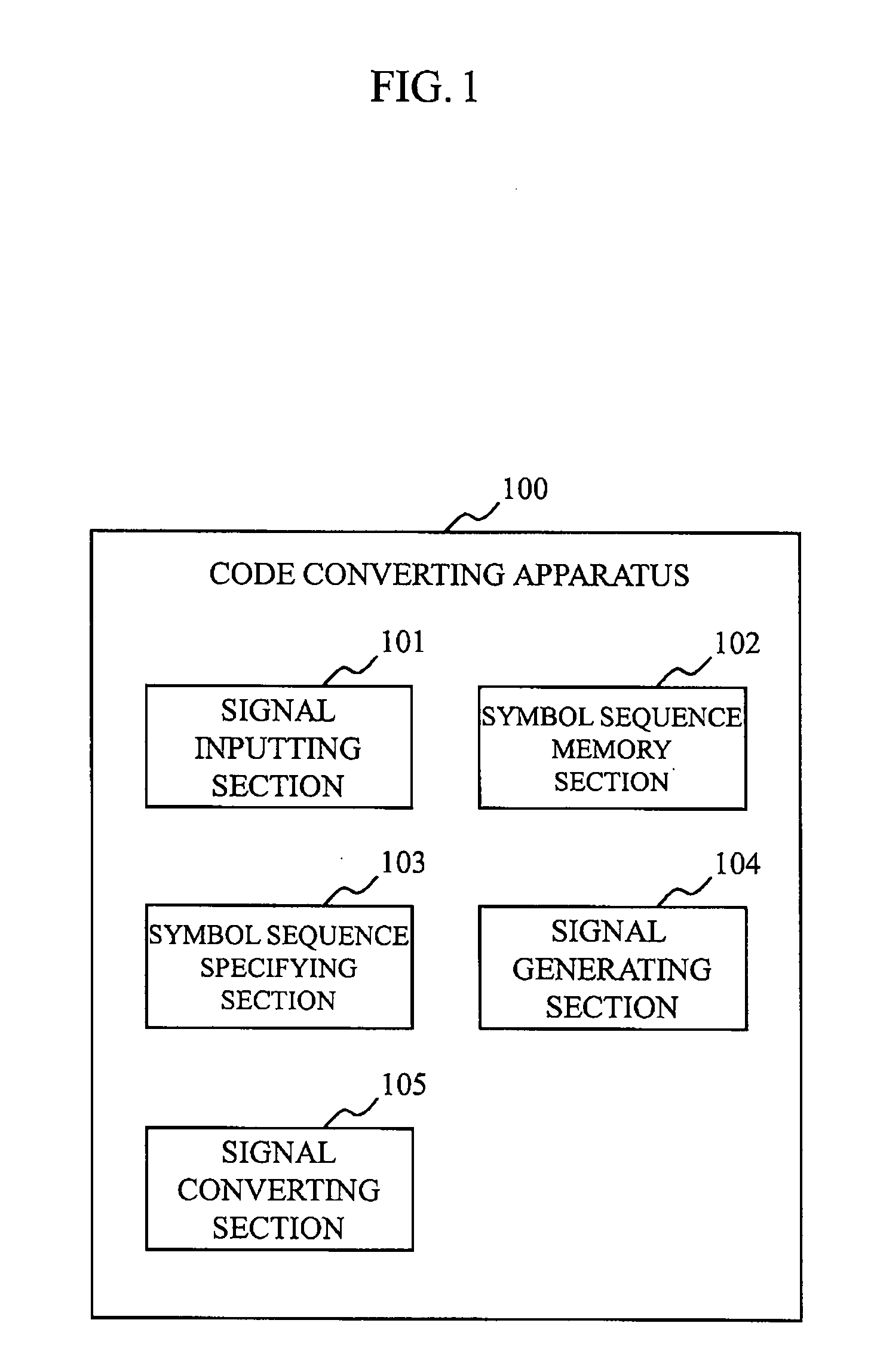

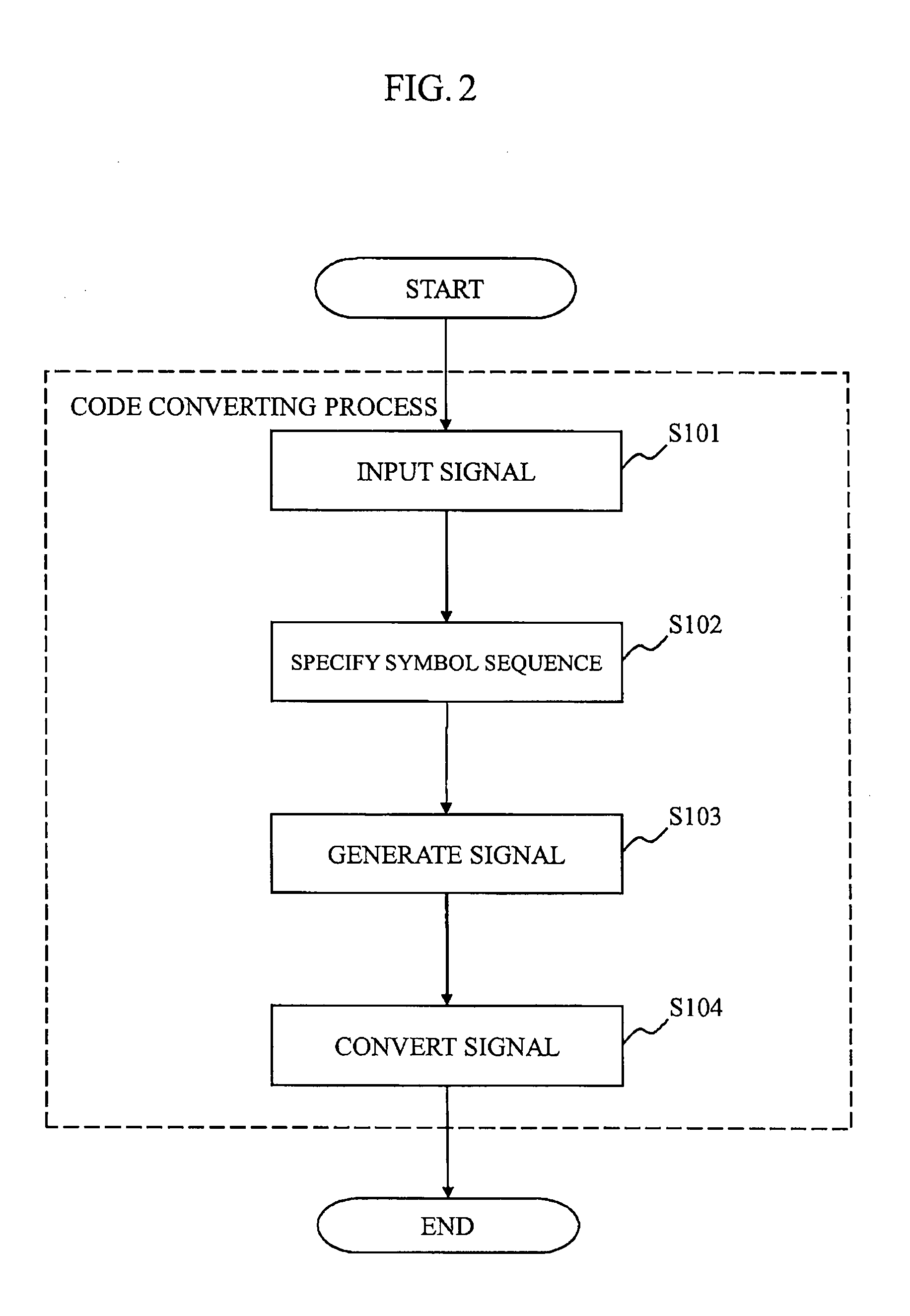

Code converting apparatus, receiver, and code converting method

InactiveUS20100290505A1Solve the excessive calculationFew calculationMultiplex code generationSatellite radio beaconingAs elementAlgorithm

A code converting apparatus is designed to estimate the incoming time and the like of a signal modulated by a spreading sequence composed of m elements in a set A having n kinds of symbols as elements accurately. A symbol sequence memory section 102 stores a converted sequence of symbols obtained by concatenating consecutive 2d symbols at the center of each sequence pattern pi composed of 4d elements in the set A. The converted sequence of symbols is structured so that d symbol immediately preceding the 2d symbols and d symbol immediately following the 2d symbols are identical to d symbol immediately preceding corresponding 2d symbols and d symbol immediately following the corresponding 2d symbols of a corresponding sequence pattern. A symbol sequence specifying section 103 specifies a matching sequence pattern for every consecutive 2d symbols in a symbol sequence obtained by assigning a symbol to the signal in a coding cycle of the spreading sequence. A signal generating section 104 adds a portion to which the 2d symbols are assigned of the signal. A signal converting section 105 concatenates each pattern signal added for each sequence pattern, in an order equivalent to an order of the 2d symbols at the center of each sequence pattern concatenated in the converted sequence of symbols.

Owner:MITSUBISHI ELECTRIC CORP

Ultrasound transmit beamformer integrated circuit and method

ActiveUS7889787B2Compact implementationLow costUltrasonic/sonic/infrasonic diagnosticsWave based measurement systemsPulse envelopeIntermediate frequency

The invention provides a novel method of transmit beamforming, which allows compact analog implementation of complex digital algorithms without compromising their features. It is aimed to support envelope shaping, apodization, and phase rotation per channel and per firing. Each of three embodiments represents a complete transmit channel driven by pulse-width modulated (PWM) waveforms stored in a conventional sequence memory. PWM signals controls the transmit pulse envelope (shape) by changing the duty cycle of the carrier. Beamformation data are loaded prior to a firing via serial interface. Under the direction of a controller, the circuitry allows high precision (beyond sampling rate) phase rotation of the carrier. It also provides transmit apodization (aperture weighting), which maintains an optimal trade-off among low sidelobe level and widening of the mainlobe. Implementing such an IC, the manufacturing cost of a high-end ultrasound system can be reduced. Equally, the proposed solution makes the benefits of digital transmit beamformers available to midrange and entry-level machines since it merely requires a modified programming of the sequence memory.

Owner:MICROCHIP TECH INC

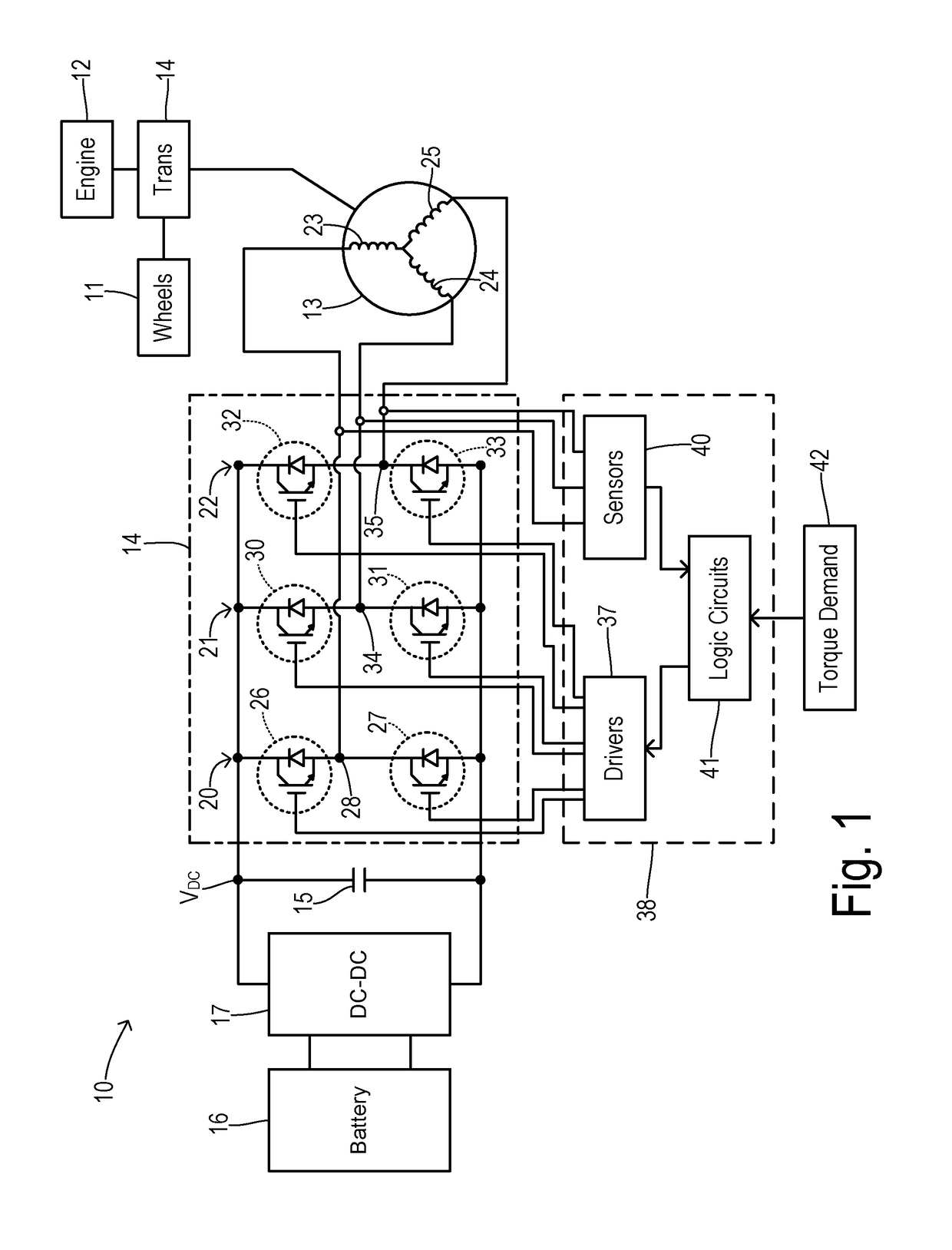

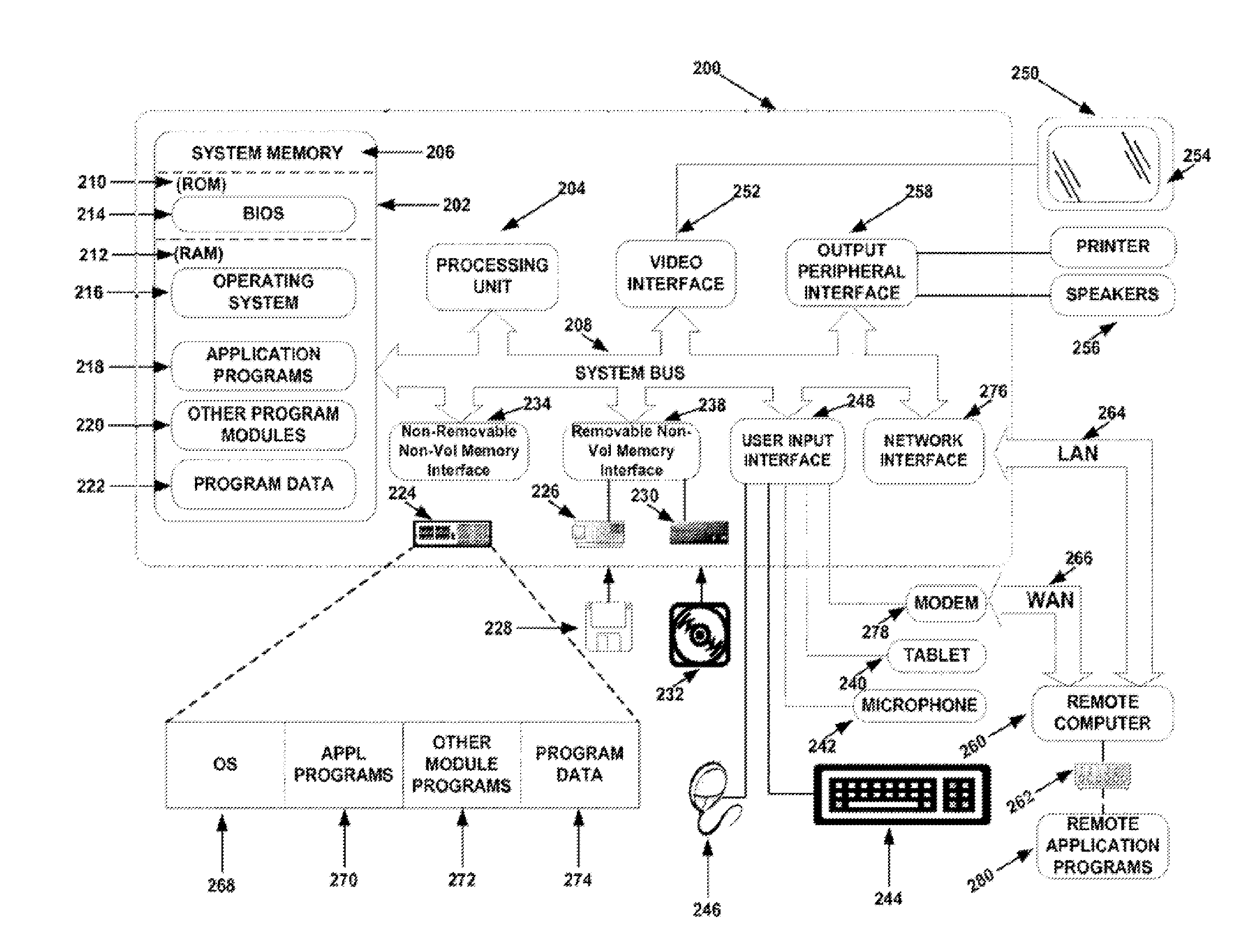

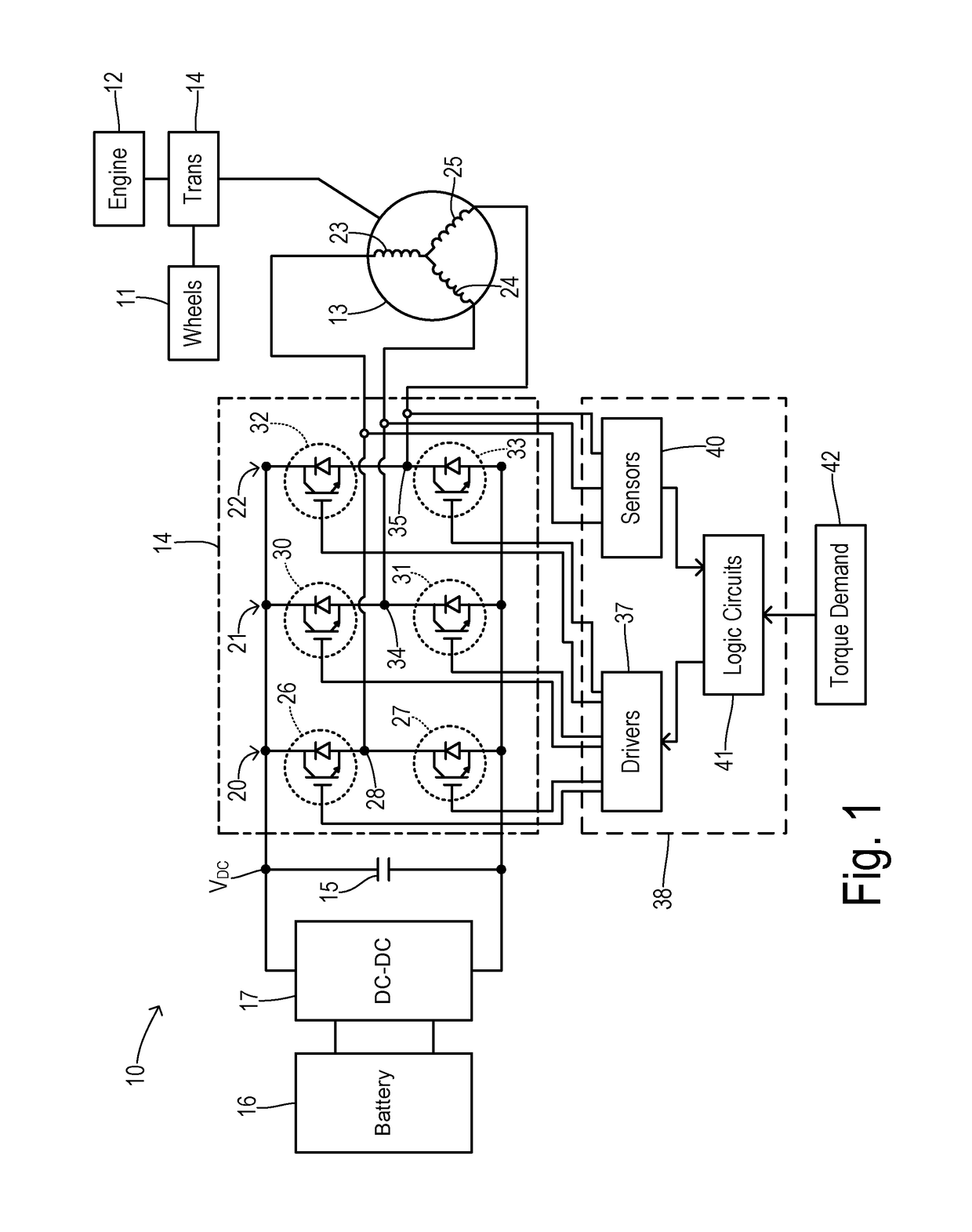

Pseudorandom pwm variation based on motor operating point

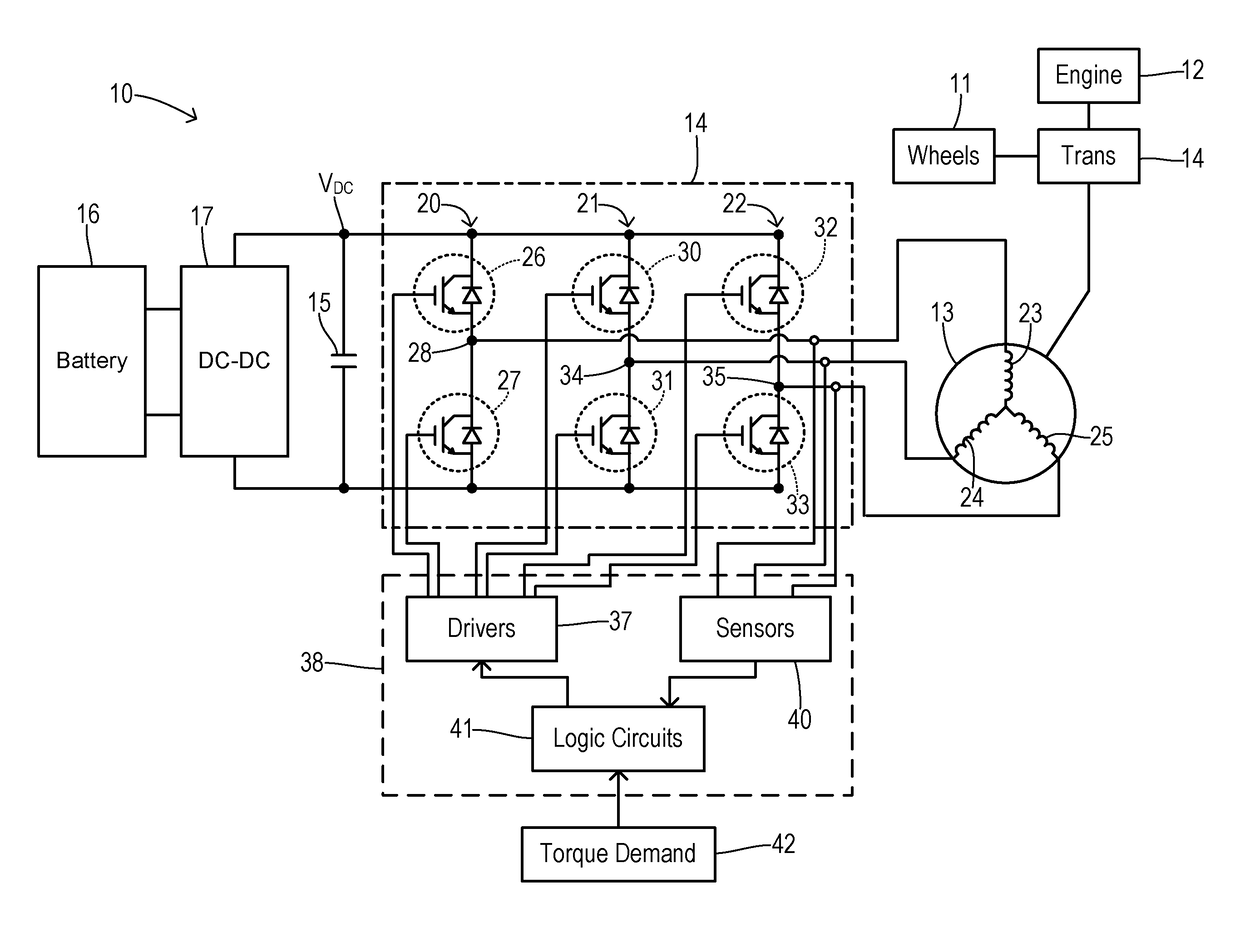

ActiveUS20180076744A1Reduce audible noiseReduce switching lossesTorque ripple controlSpeed controllerPower inverterElectricity

An electric drive for a vehicle uses an inverter circuit configured to provide a multi-phase AC drive signal to an electric machine according to a PWM drive signal. A PWM controller monitors an operating point of the electric drive and is configured to identify an operating region of the electric drive from a plurality of predetermined regions in response to the monitored operating point. A sequence memory stores a plurality of sequences, each sequence optimized for a respective one of the predetermined regions to reduce audible noise and switching losses. The PWM controller generates the PWM drive signal according to a respective sequence corresponding to the identified operating region. Thus, the reduction of audible noise and switching losses is optimized based on torque and / or speed of the motor.

Owner:FORD GLOBAL TECH LLC

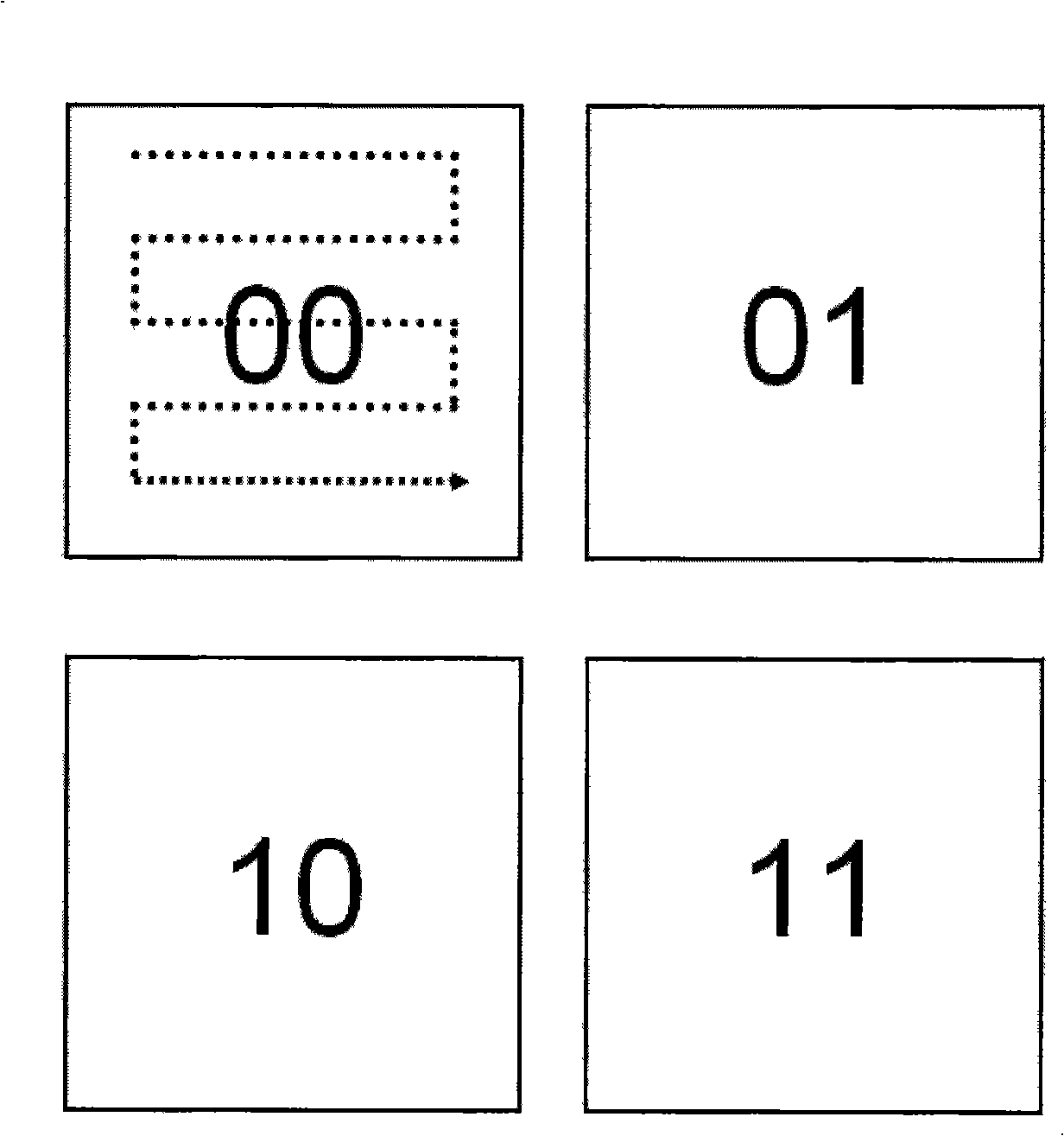

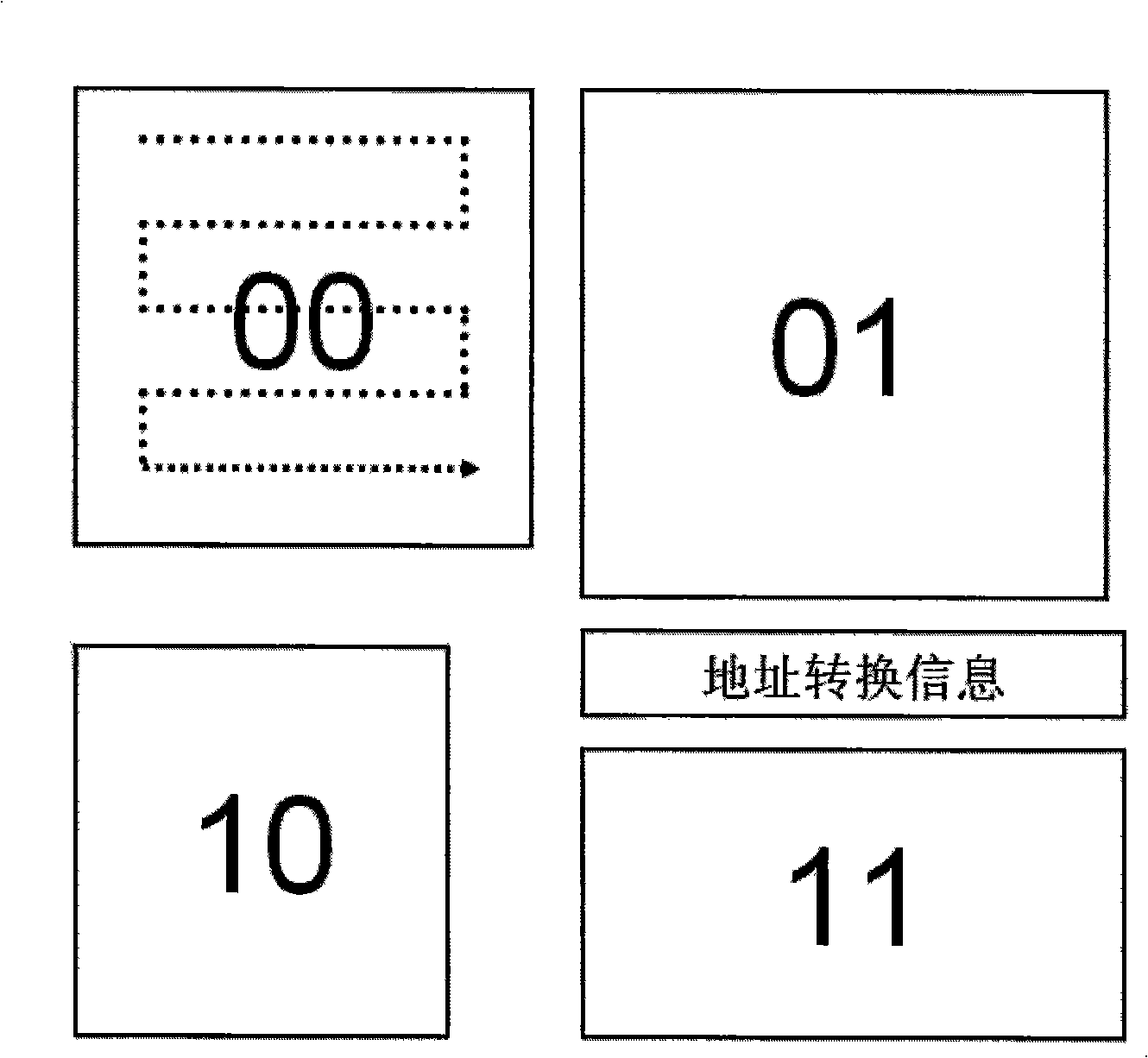

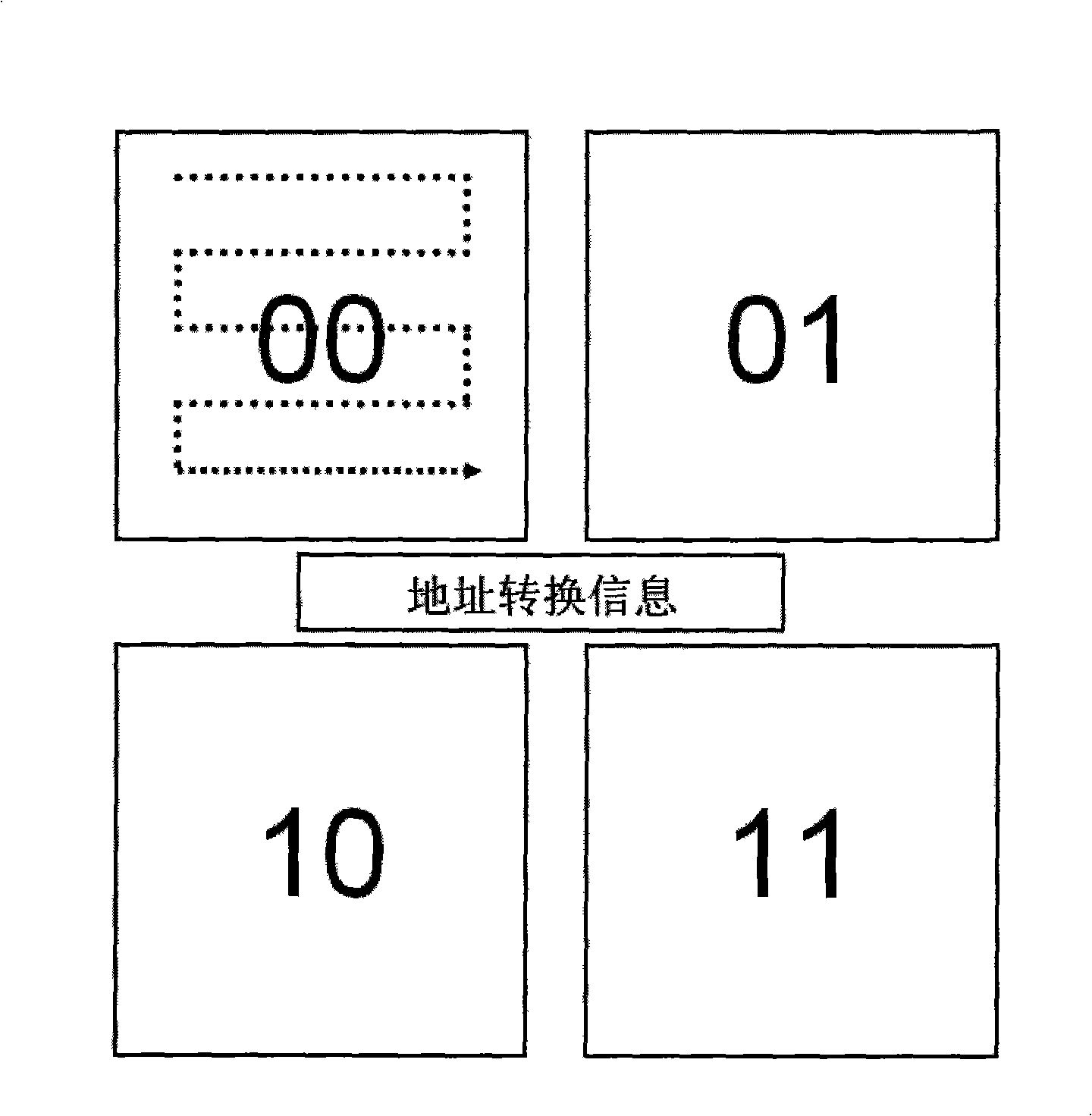

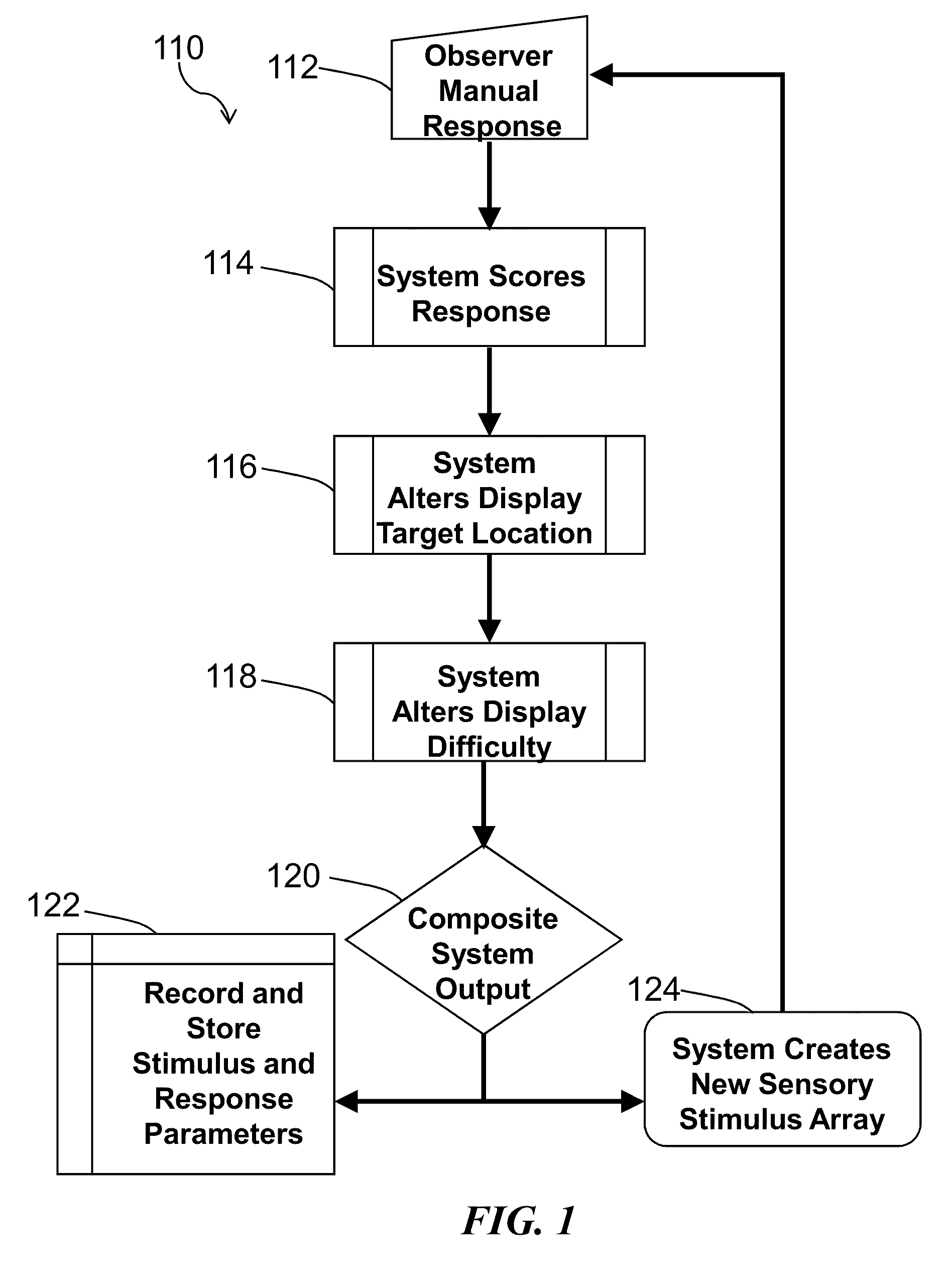

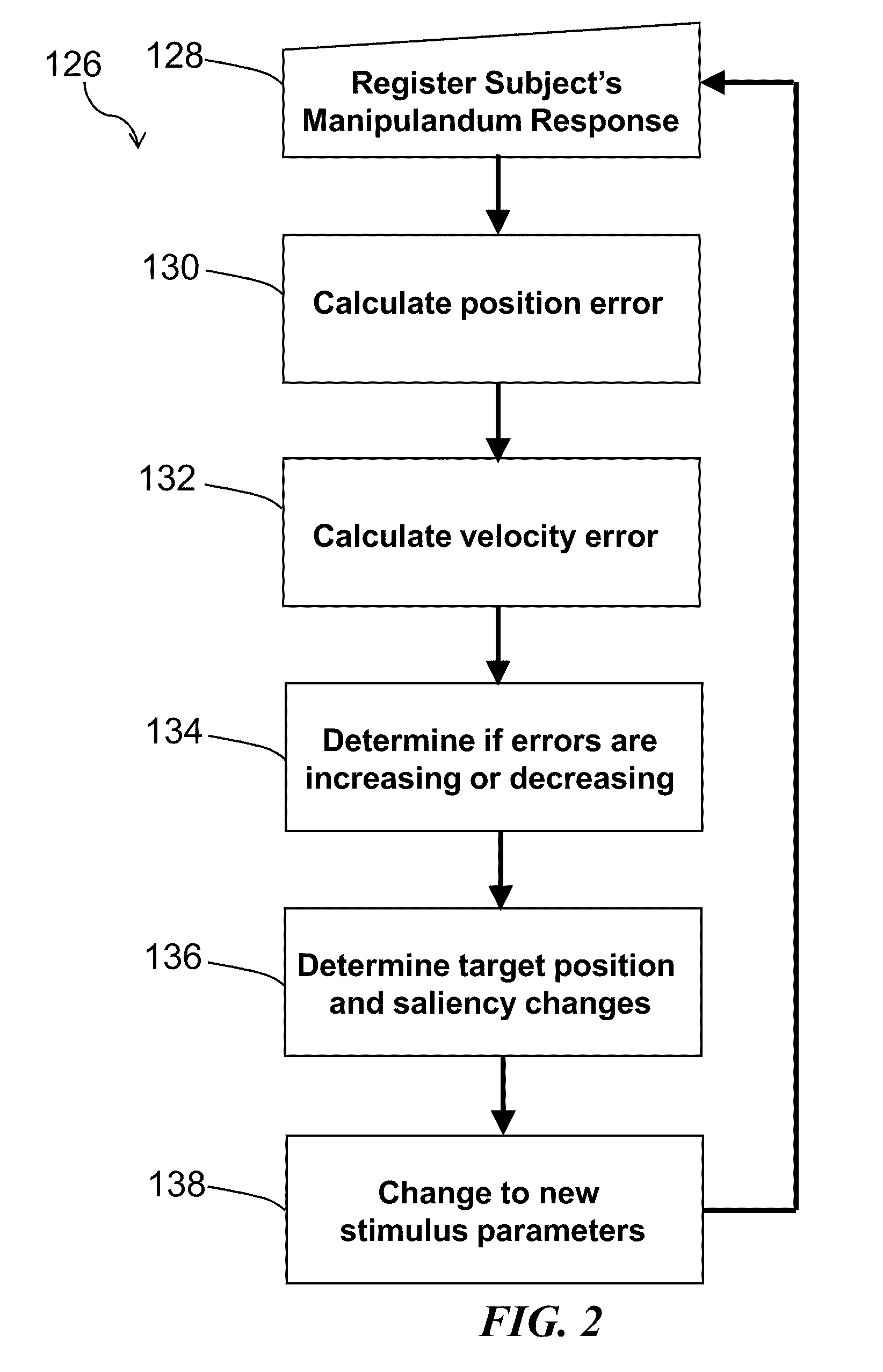

Method and system for quantitative assessment of spatial sequence memory

InactiveUS20110065077A1Improves and simplifies complex experimental paradigmImproved and simplifiedComputer-assisted medical data acquisitionMedical automated diagnosisSequence memoryDisplay device

A method is presented to address quantitative assessment of spatial sequence memory in a subject, where the method comprises the steps of: (1) presenting at least one scene to the subject on a display, the scene comprising a plurality of elements and a background; (2) modulating the saliency of a predetermined section of said scene(3) receiving feedback from the subject via at least one input device; (4) modifying the saliency of the predetermined section; (5) adjusting a functional assessment parameter relative to the scene; (6) moving the predetermined section relative to the scene; (7) receiving refined feedback from the subject via the input device; (8) quantitatively refining the refined feedback; (9) calculating a critical threshold parameter for the subject; and (10) recording the critical threshold parameter onto a tangible computer readable medium. An apparatus for quantitative assessment of spatial sequence memory of a subject comprising a display device, an input device, a control device, and a tangible computer readable medium. In its simplest sense, a quantitative profile of spatial sequence memory by psychophysical responses is generated on a tangible computer readable medium.

Owner:CEREBRAL ASSESSMENT SYST

Communication device test signal generating apparatus and communication device test signal generating method

InactiveCN101006655AReduce manufacturing costReduce workloadModulated-carrier systemsTransmission monitoringDigital analog converterSequence memory

A communication device test signal generating apparatus wherein a sequence memory stores an order in which to read unit data including I and Q waveform data; read addresses; first sequence information including a desired signal level to be set in the unit data; and second sequence information including a frequency offset, and wherein the first and second sequence information stored in the sequence memory are sequentially used to apply a plurality of steps of frequency offsets to the I and Q waveform data in a digital stage preceding a D / A converter at predetermined frequency intervals with a predetermined carrier frequency being referenced, thereby outputting the frequency hopping test signal.

Owner:ANRITSU CORP

System, method and apparatus for cardiac intervention with mr stroke detection and treatment

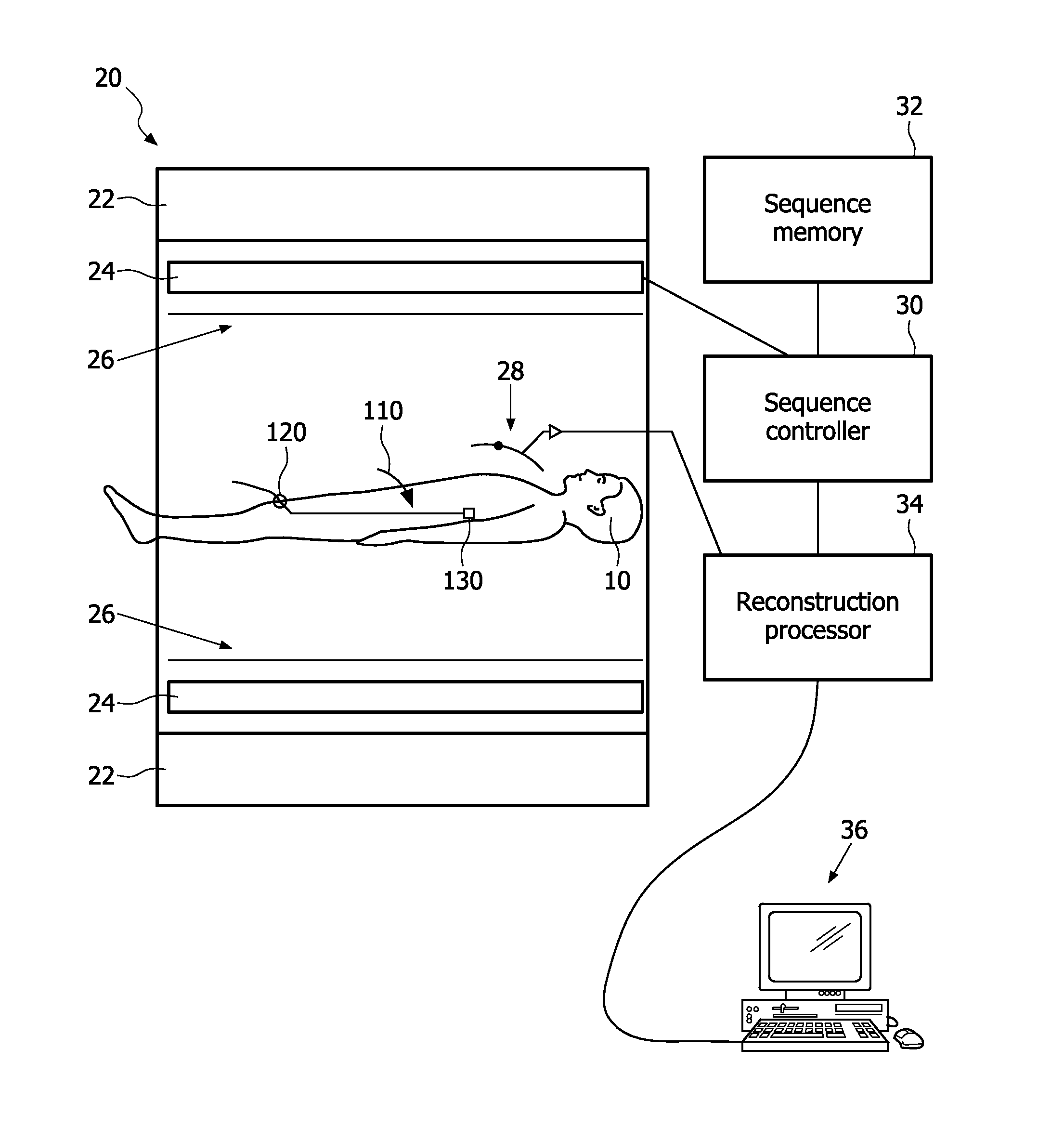

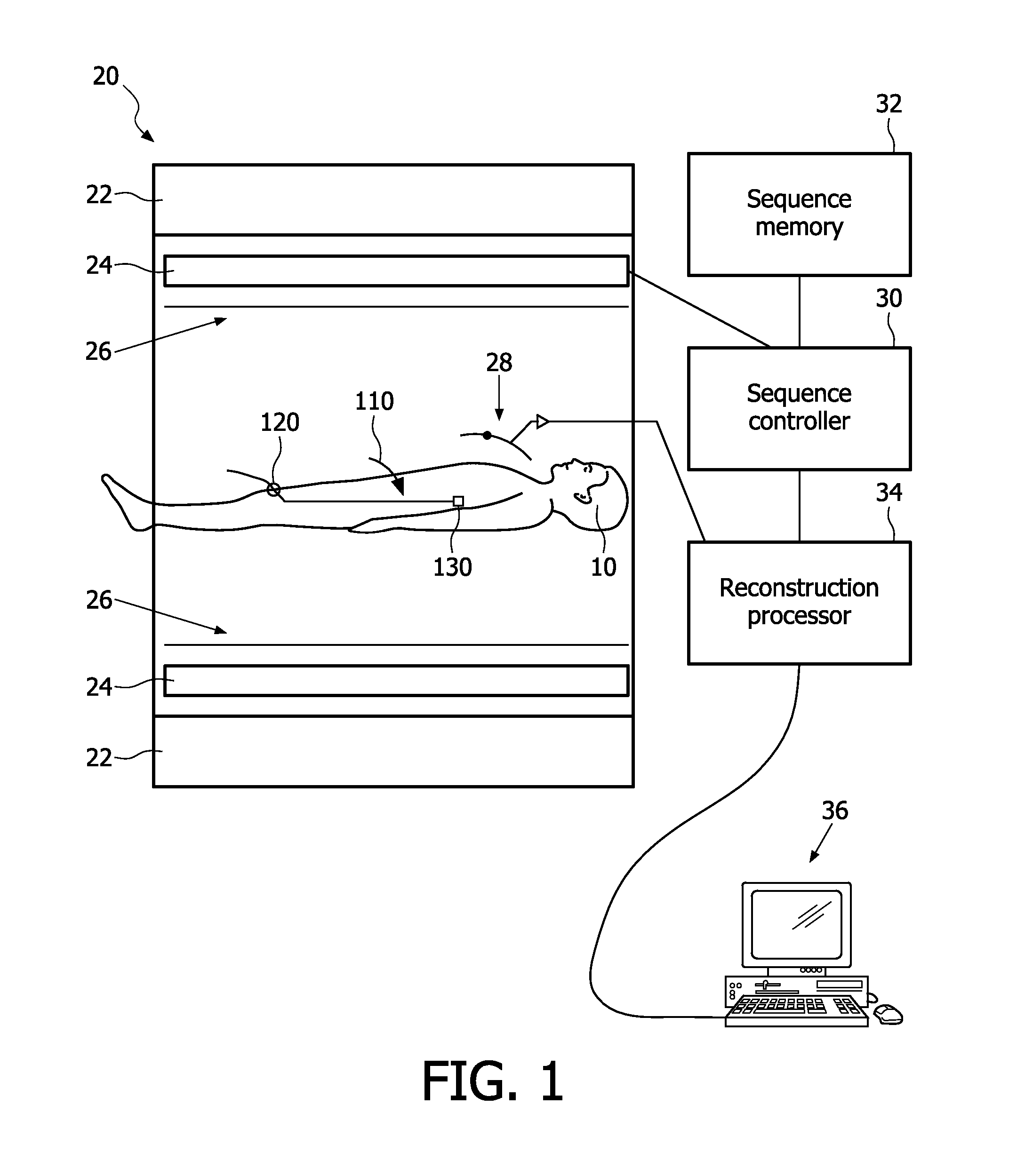

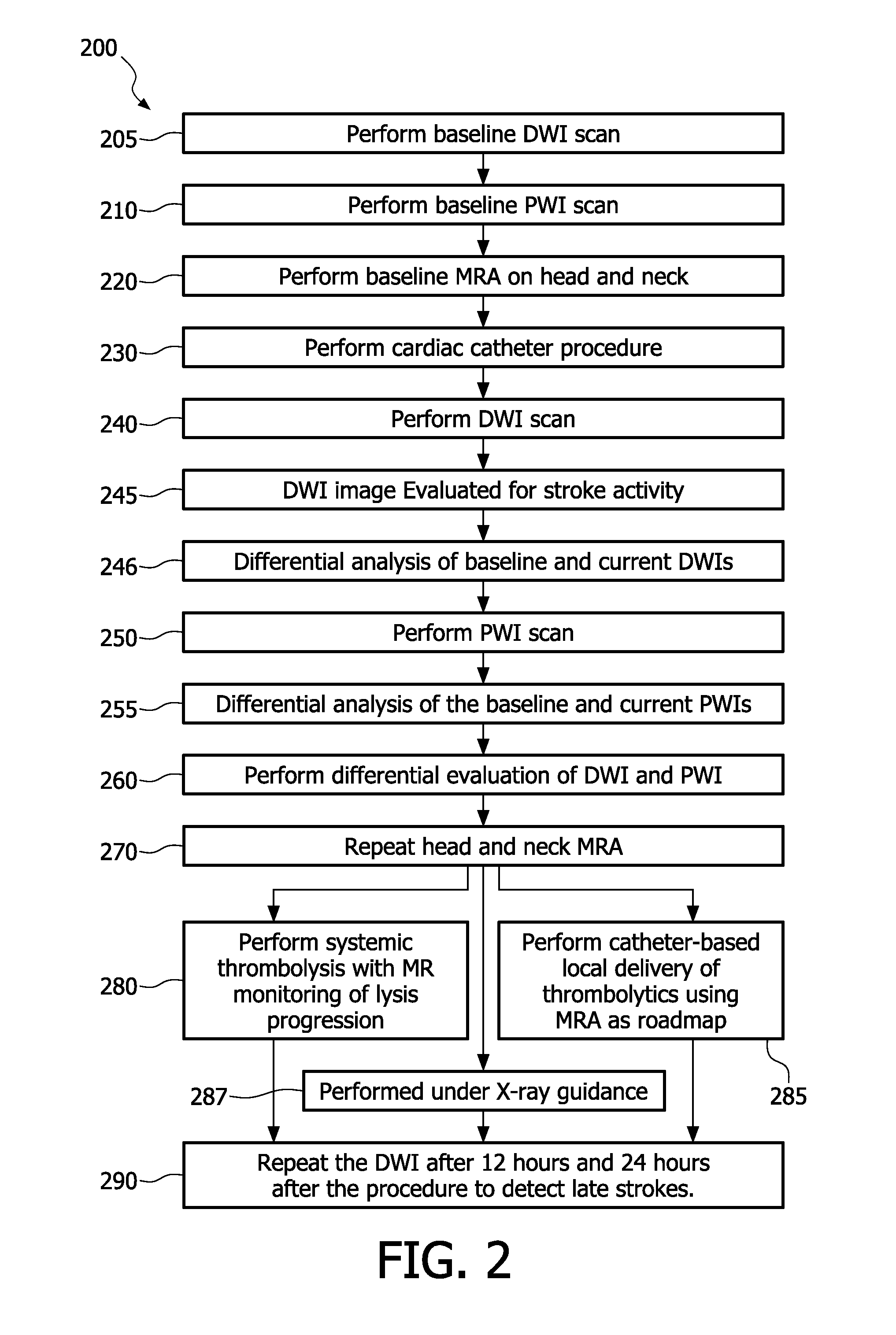

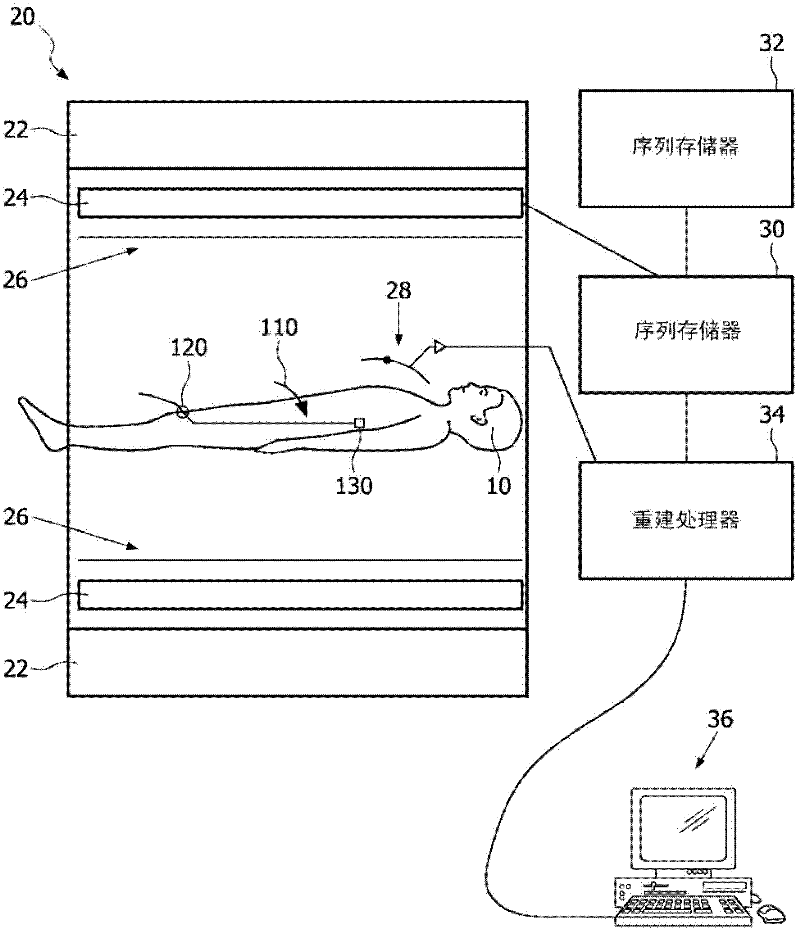

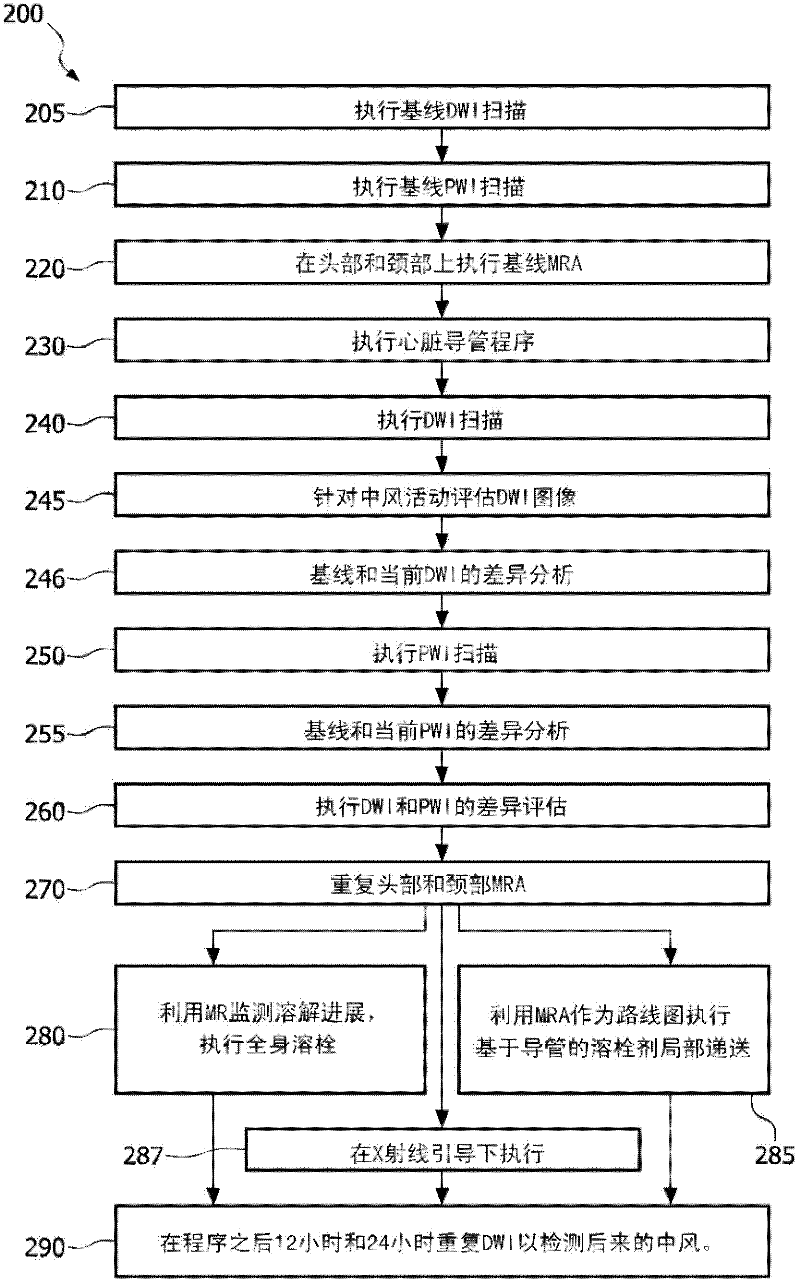

InactiveUS20110257510A1Early treatmentPreserve more brain tissueMagnetic measurementsDiagnostic recording/measuringSequence controlCatheter procedure

A system for the early detection and treatment of catheter-induced ischemic strokes includes a magnetic resonance system (20) and a processor (36). The magnetic resonance system includes a sequence controller for performing each of a plurality of imaging sequences and a sequence memory (32) which stores at least a magnetic resonance angiography (MRA) sequence, a diffusion-weighted imaging (DWI) sequence, and a perfusion-weighted imaging (PWI) sequence. The processor is programmed to control the magnetic resonance system to perform the steps of: performing the MRA sequence to generate a baseline MRA image; performing a catheter-tracking procedure to track a catheter; performing the DWI sequence after the catheter procedure to generate a diffusion-weighted image; performing the PWI sequence to generate a perfusion-weighted image; and combining the diffusion-weighted image and the perfusion-weighted image to generate a combined image for evaluating the ischemic stroke.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

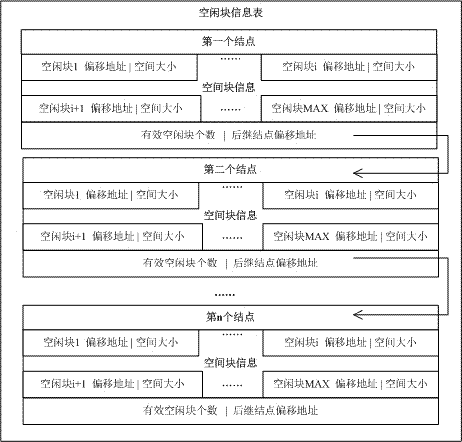

Managing method for free block of Java card

ActiveCN104778128AQuick searchDoes not affect transaction timeMemory adressing/allocation/relocationPayment architectureProgrammable read-only memoryMerge algorithm

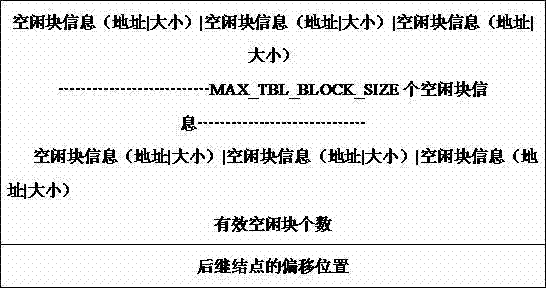

The invention relates to a managing method of a free block in an EEPROM (Electrically Erasable Programmable Read-Only Memory) memory area of a Java card, in particular to a managing method for the free block of the Java card. The method comprises the steps of managing information of free blocks in all EEPROMs for the Java card through a free block information table, distributing a space for a first node of the free block information table from the EEPROMs in advance, and applying for memory spaces for subsequent nodes from the EEPROMs when the number of the free blocks exceeds the maximum quantity stored by an existing node; when the memory space is applied for data, traversing the free block information table and selecting the free blocks of proper sizes; when the memory space occupied by the data is released, combining the released memory space to the free blocks of proper sizes according to a block ordering-by-merging algorithm, and sorting the free block information according to size; storing the free block information in a sequence memory way from small to big according to the sizes of the blocks, so that the memory positions can be quickly found out when the memory space is applied, and the executing efficiency can be greatly improved; furthermore, the operating efficiency of the Java card can be significantly improved by the Java card managing method provided by the invention.

Owner:东港股份有限公司

Memory Consistency in Graphics Memory Hierarchy with Relaxed Ordering

ActiveUS20180181489A1Facilitate mid-render computeReduce power consumptionMemory architecture accessing/allocationImage memory managementMemory hierarchySequence memory

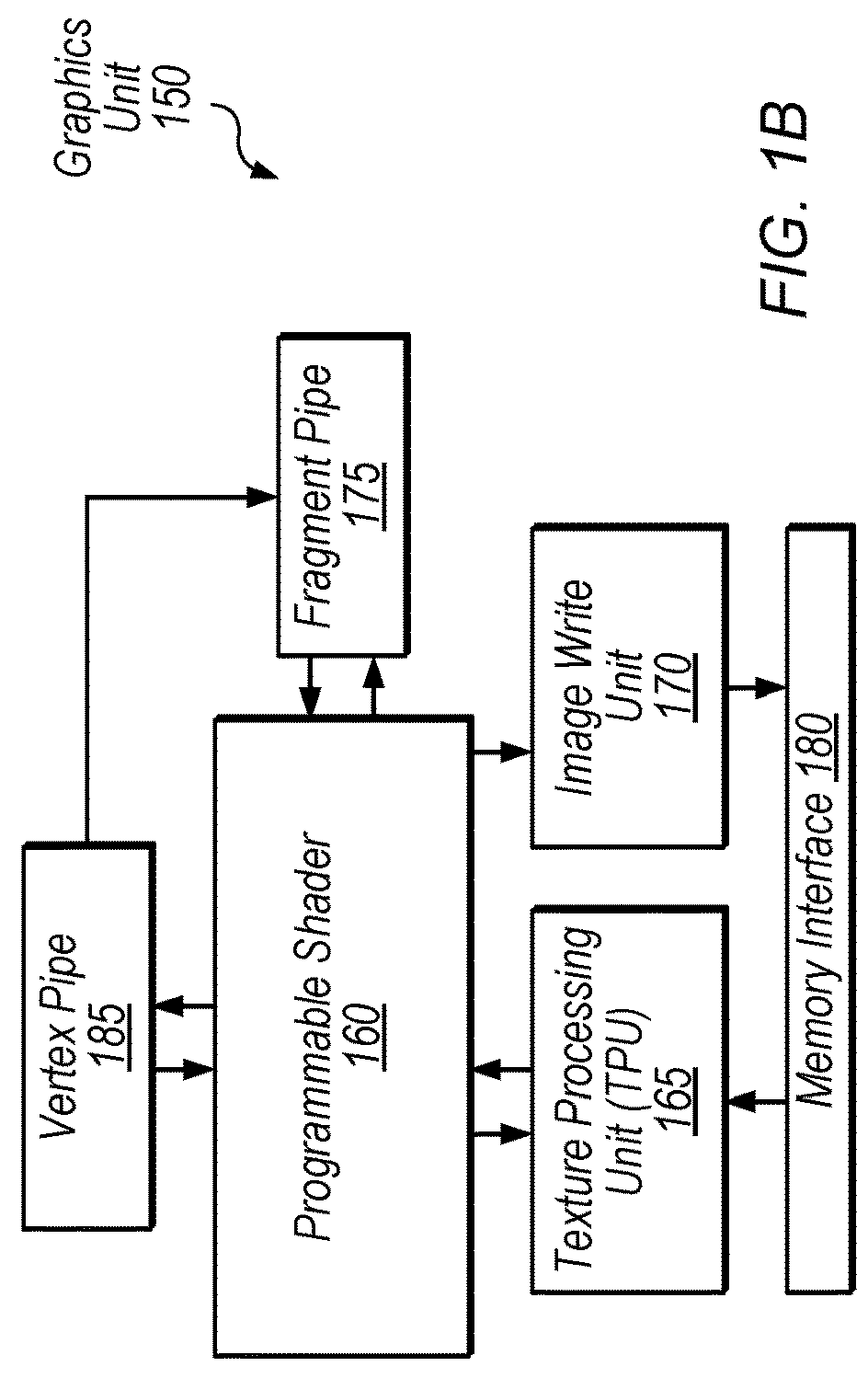

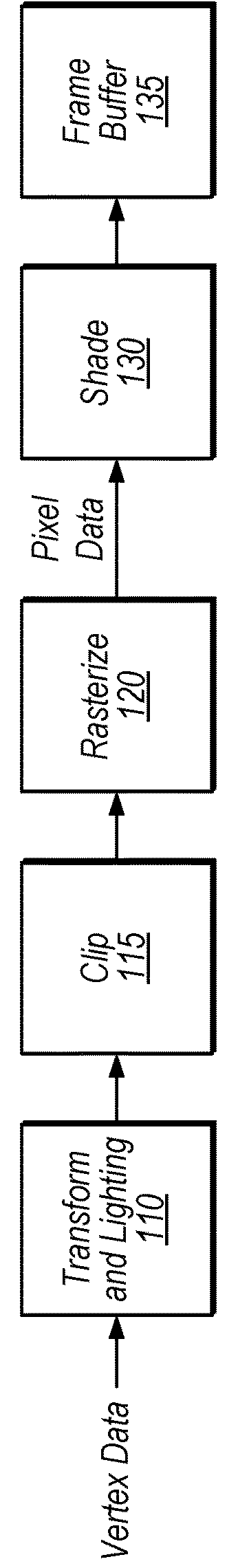

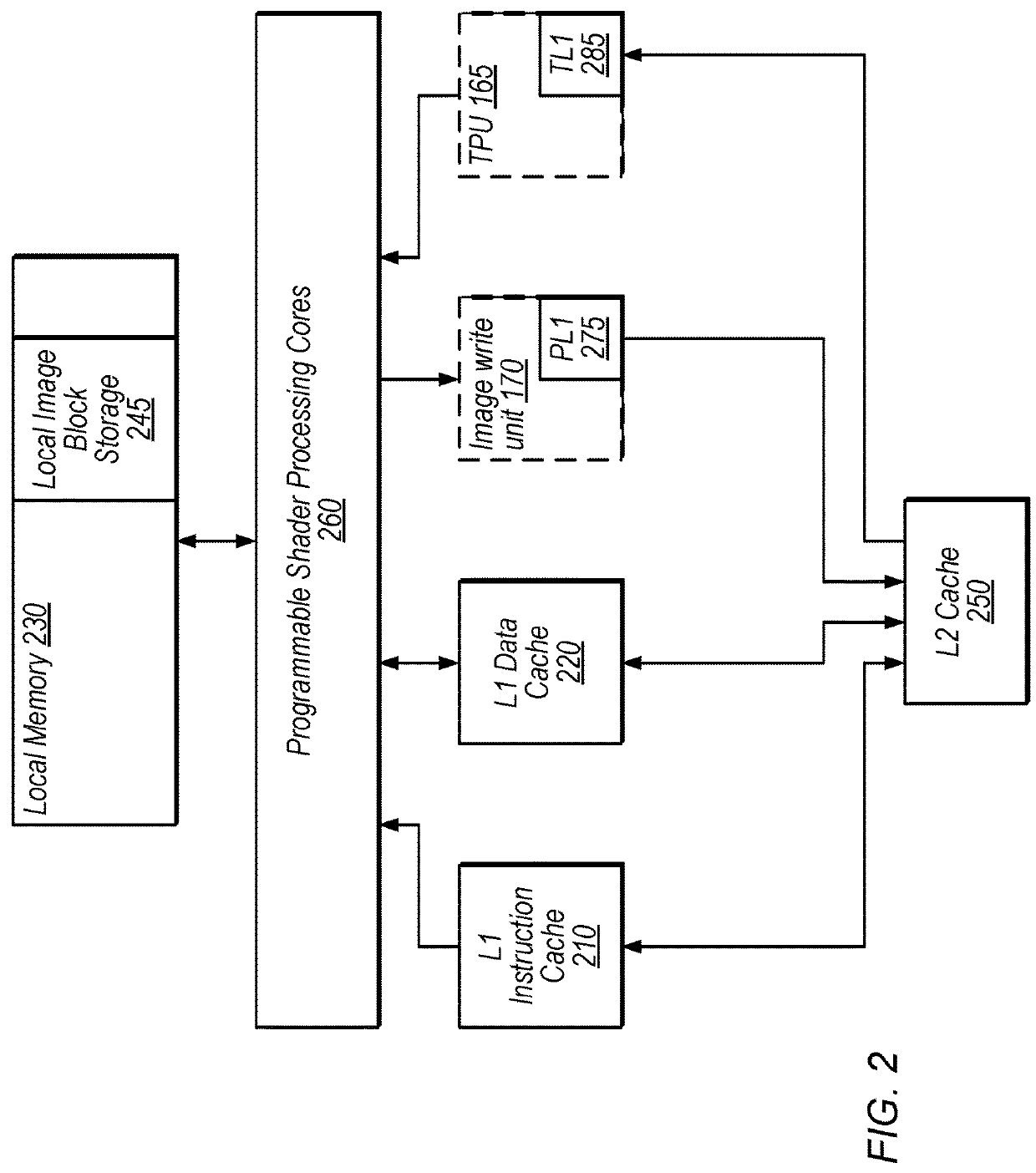

Techniques are disclosed relating to memory consistency in a memory hierarchy with relaxed ordering. In some embodiments, an apparatus includes a first level cache that is shared by a plurality of shader processing elements and a second level cache that is shared by the shader processing elements and at least a texture processing unit. In some embodiments, the apparatus is configured to execute operations specified by graphics instructions that include (1) an attribute of the operation that specifies a type of memory consistency to be imposed for the operation and (2) scope information for the attribute that specifies whether the memory consistency specified by the attribute should be enforced at the first level cache or the second level cache. In some embodiments, the apparatus is configured to determine whether to sequence memory accesses at the first level cache and the second level cache based on the attribute and the scope.

Owner:APPLE INC

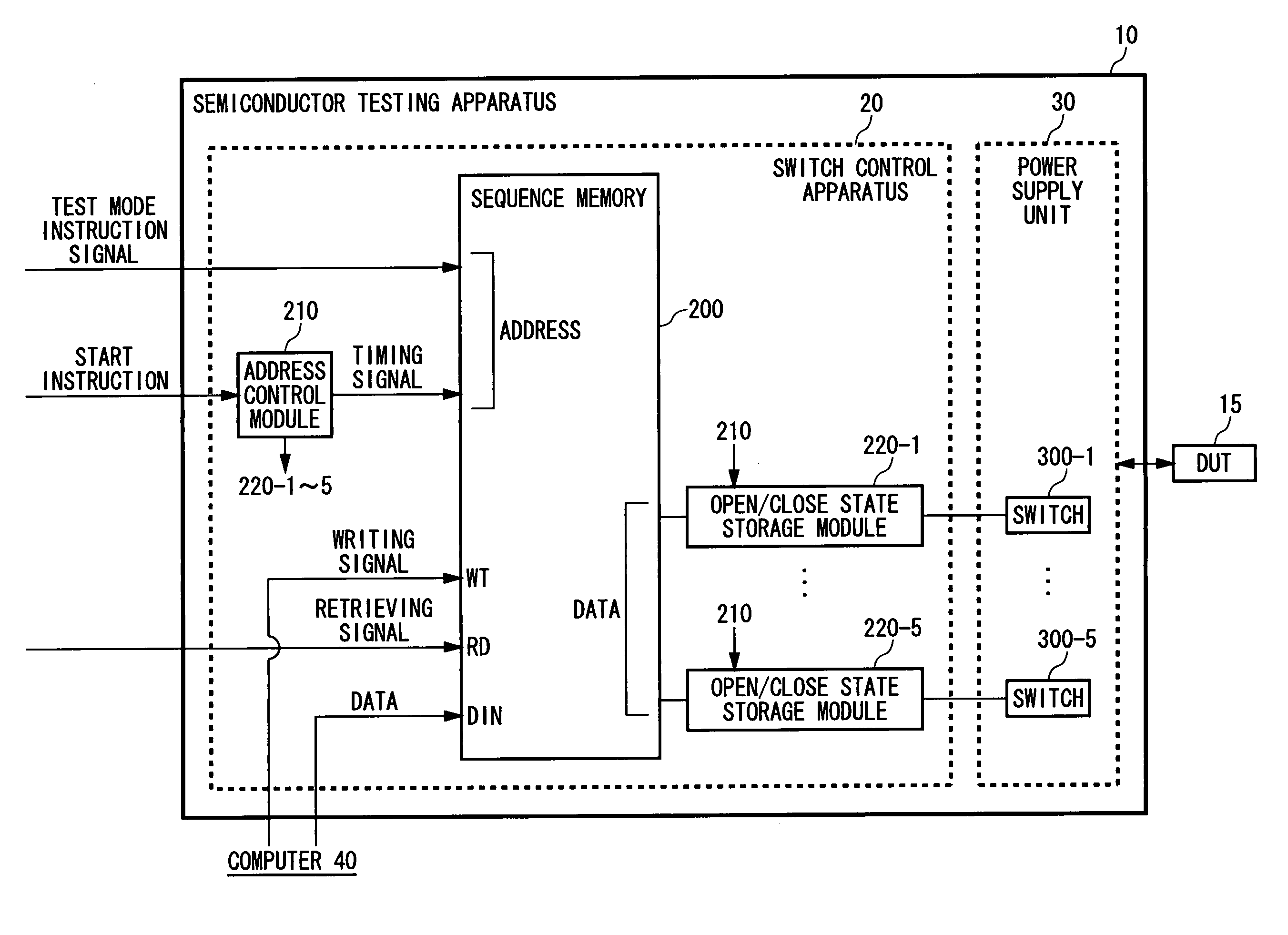

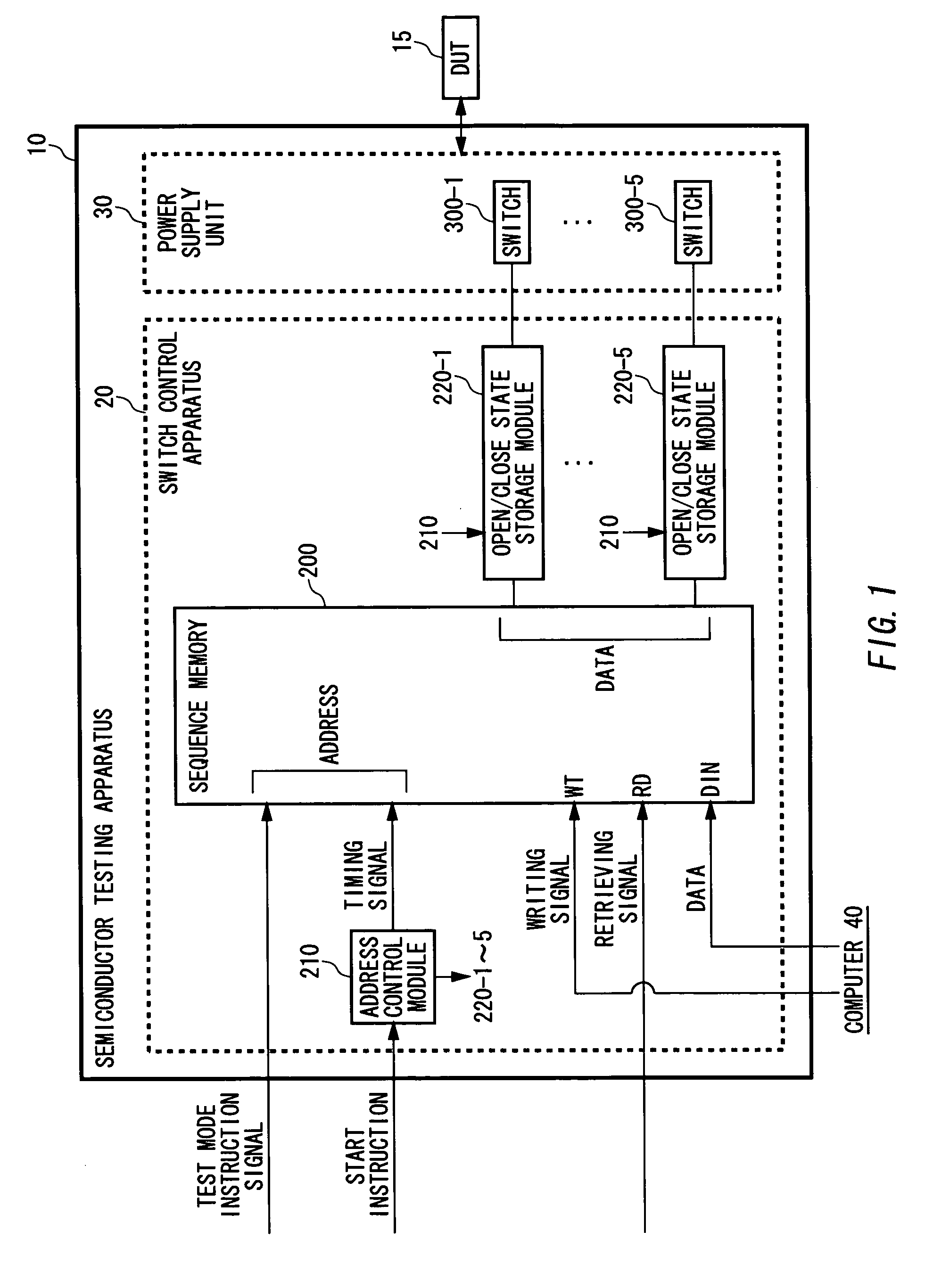

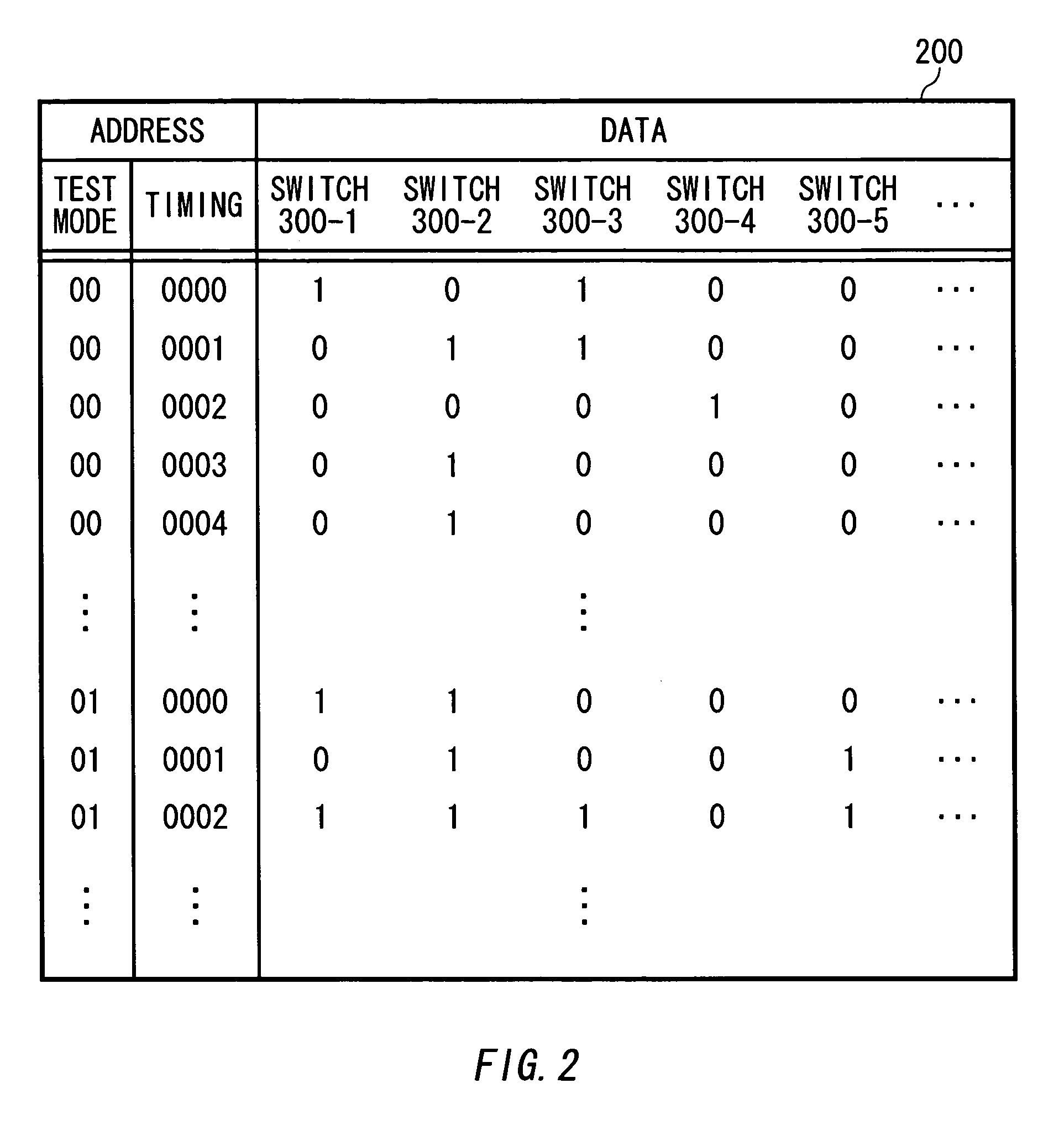

Switch control apparatus, semiconductor device test apparatus and sequence pattern generating program

ActiveUS20060208767A1Short timeElectronic circuit testingPulse train pattern monitoringDevice materialSequence memory

It is an object to properly control timing of opening and closing a switch by a circuit of simple constitution. A switch control apparatus for controlling a switch is provided, the switch control apparatus including a sequence memory for recording a sequence pattern includes open / close instruction data which instruct to open / close the switch thereon; an address control module for sequentially retrieving each of the open / close instruction data of the sequence pattern from the sequence memory; and an open / close state storage module for storing an open / close state instructed by changed open / close instruction data when the open / close instruction data retrieved by the address control module is changed, wherein the switch opens or closes in response to the open / close state stored by the open / close state storage module.

Owner:ADVANTEST CORP

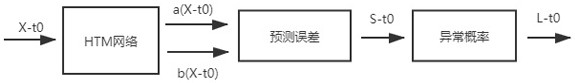

Real-time data flow anomaly detection method and system

PendingCN113254485ASolving non-automatableResolve detectionDigital data information retrievalDesign optimisation/simulationEvaluation resultAnalysis data

The invention relates to a real-time data flow anomaly detection method and system. The method comprises the following steps: firstly, for a real-time data stream, constructing a context relationship of the data stream through an HTM network, and on the basis of an abnormal condition of the analysis data, giving a preliminary evaluation result; secondly, giving error statistics for the preliminary evaluation result, and carrying out error probability model modeling on the related error statistics result; and finally, evaluating whether the data flow is normal or not by combining a preliminary evaluation result and an error statistical result, and constructing an abnormal probability detection model. According to the invention, real-time anomaly detection is carried out on the data stream based on an online sequence memory algorithm of hierarchical time memory, so that the problems of non-automation and low abnormal data detection accuracy in the existing data stream anomaly detection are solved.

Owner:福建省海峡信息技术有限公司

Pseudorandom PWM variation based on motor operating point

ActiveUS10027262B2Reduce audible noiseSpeed controllerTorque ripple controlPower inverterElectricity

An electric drive for a vehicle uses an inverter circuit configured to provide a multi-phase AC drive signal to an electric machine according to a PWM drive signal. A PWM controller monitors an operating point of the electric drive and is configured to identify an operating region of the electric drive from a plurality of predetermined regions in response to the monitored operating point. A sequence memory stores a plurality of sequences, each sequence optimized for a respective one of the predetermined regions to reduce audible noise and switching losses. The PWM controller generates the PWM drive signal according to a respective sequence corresponding to the identified operating region. Thus, the reduction of audible noise and switching losses is optimized based on torque and / or speed of the motor.

Owner:FORD GLOBAL TECH LLC

Systems, methods and devices for cardiac intervention with mr stroke detection and treatment

InactiveCN102264290AEarly treatmentDiagnostic recording/measuringSensorsCatheter procedureBlood tube

A system for early detection and treatment of catheter-induced ischemic stroke includes a magnetic resonance system (20) and a processor (36). The magnetic resonance system includes: a sequence controller for performing each of a plurality of imaging sequences; and a sequence memory (32) for storing at least a magnetic resonance angiography (MRA) sequence, a diffusion weighted imaging (DWI) sequence, and Perfusion-weighted imaging (PWI) sequences. The processor is programmed to control the magnetic resonance system to perform the steps of: performing an MRA sequence to generate a baseline MRA image; performing a catheter tracking procedure to track the catheter; performing a DWI sequence after the catheter procedure to generate a diffusion-weighted image; performing a PWI sequence to generate a perfusion-weighted image; and combine the diffusion-weighted image and the perfusion-weighted image to generate a combined image for evaluating ischemic stroke.

Owner:KONINK PHILIPS ELECTRONICS NV

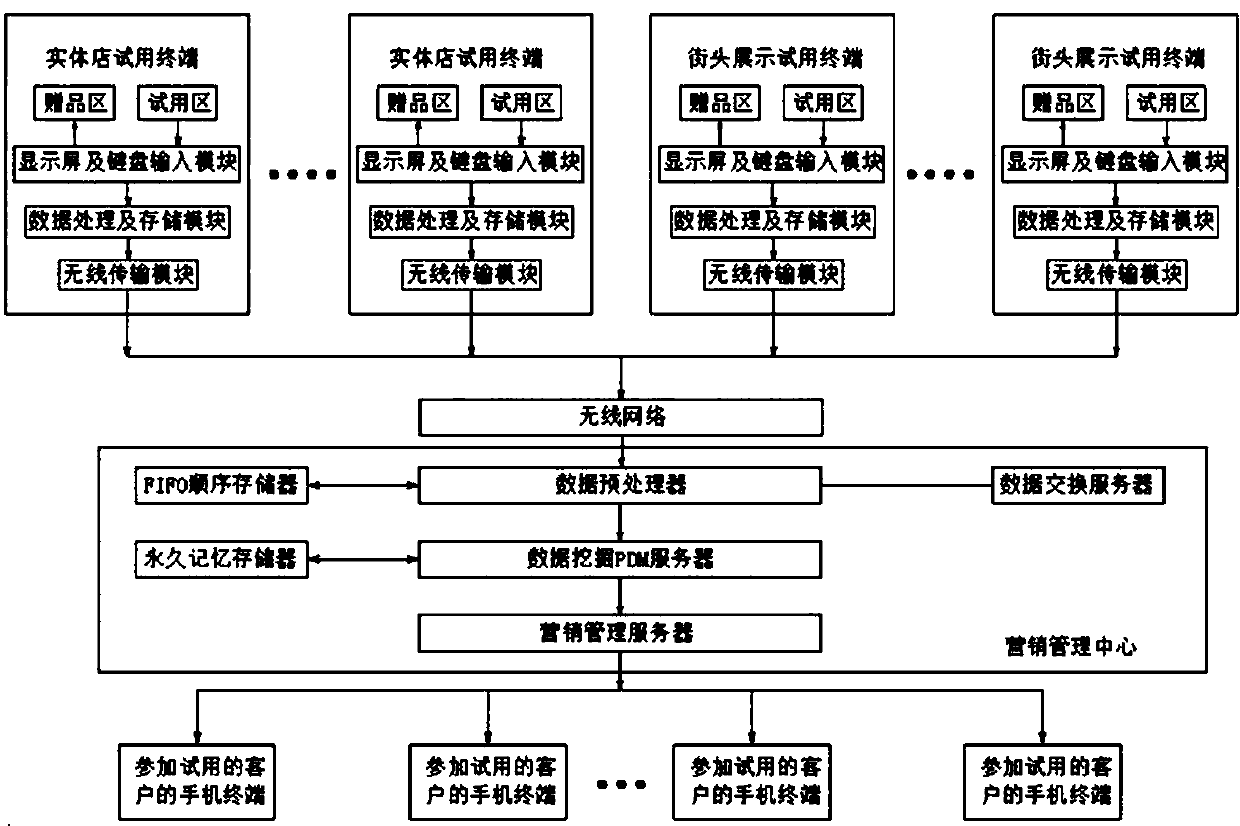

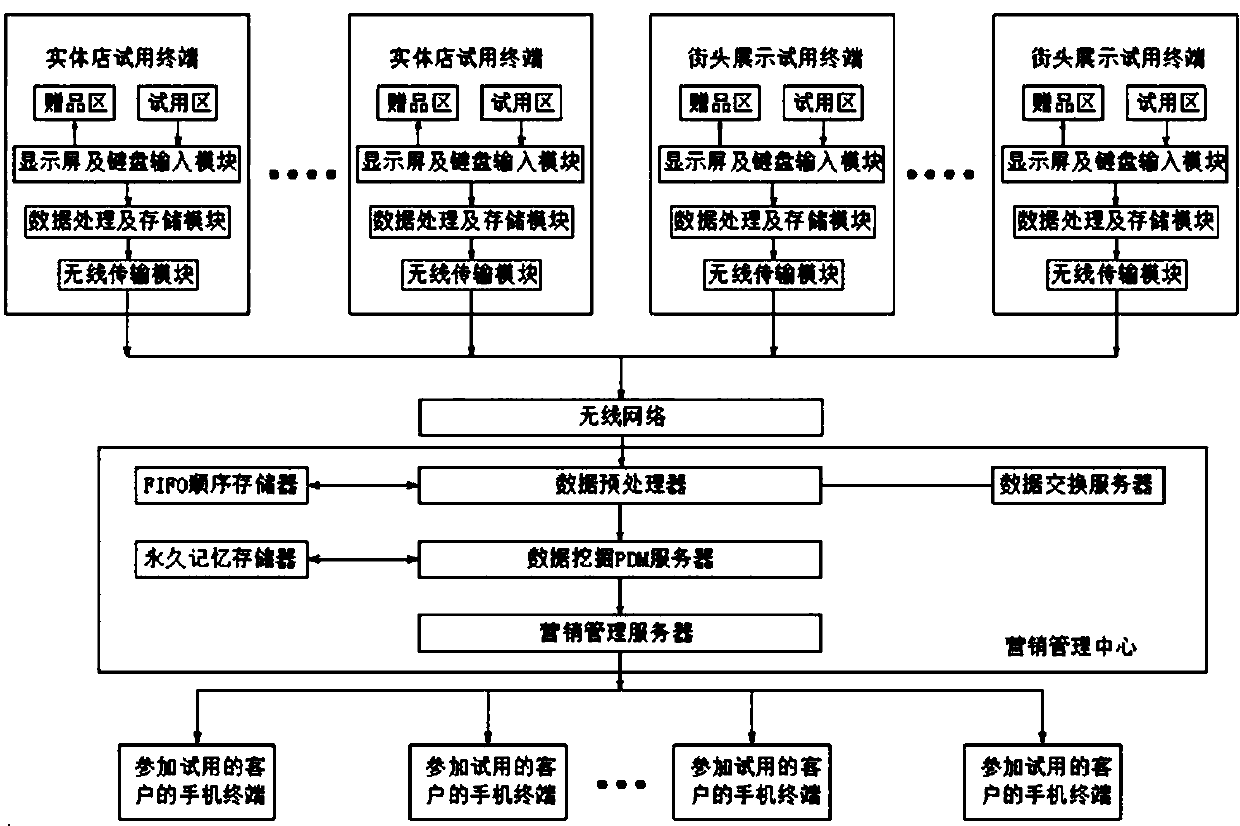

E-commerce trial evaluation and recommendation system based on user requirements

InactiveCN109961302ANarrow your searchAvoid blind salesCustomer communicationsBuying/selling/leasing transactionsMaterial resourcesData pre-processing

The invention relates to an e-commerce trial evaluation and recommendation system based on user requirements. The system is characterized by being composed of a physical store trial terminal, a streetdisplay trial terminal, a marketing management center and a mobile phone terminal, and the physical store trial terminal and the street display trial terminal are respectively composed of a trial area, a keyboard input and display module, a gift area, a data processing and storage module and a wireless transmission module; the marketing management center is composed of a data preprocessor, a datamining PDM server, an FIFO sequence memory, a data exchange server, a marketing management server and a permanent memory. And the marketing management server is connected with a mobile phone terminalof a customer who participates in trial through a mobile communication network. The system solves the problem that the existing e-commerce enterprise has few means of attracting consumers and miningnew customers and is poor in efficiency, and compared with the existing telephone marketing means, the system takes the user requirements as a fundamental starting point, avoids the blindness, improves the return rate, and saves the manpower and material resources.

Owner:济宁市任城区电子商务发展研究院

Ultrasound transmit beamformer integrated circuit and method

ActiveUS9116229B2Compact implementationLow costUltrasonic/sonic/infrasonic diagnosticsMultiplex communicationPulse envelopeIntermediate frequency

The invention provides a novel method of transmit beamforming, which allows compact analog implementation of complex digital algorithms without compromising their features. It is aimed to support envelope shaping, apodization, and phase rotation per channel and per firing. Each of three embodiments represents a complete transmit channel driven by pulse-width modulated (PWM) waveforms stored in a conventional sequence memory. PWM signals controls the transmit pulse envelope (shape) by changing the duty cycle of the carrier. Beamformation data are loaded prior to a firing via serial interface. Under the direction of a controller, the circuitry allows high precision (beyond sampling rate) phase rotation of the carrier. It also provides transmit apodization (aperture weighting), which maintains an optimal trade-off among low sidelobe level and widening of the mainlobe. Implementing such an IC, the manufacturing cost of a high-end ultrasound system can be reduced. Equally, the proposed solution makes the benefits of digital transmit beamformers available to midrange and entry-level machines since it merely requires a modified programming of the sequence memory.

Owner:MICROCHIP TECH INC

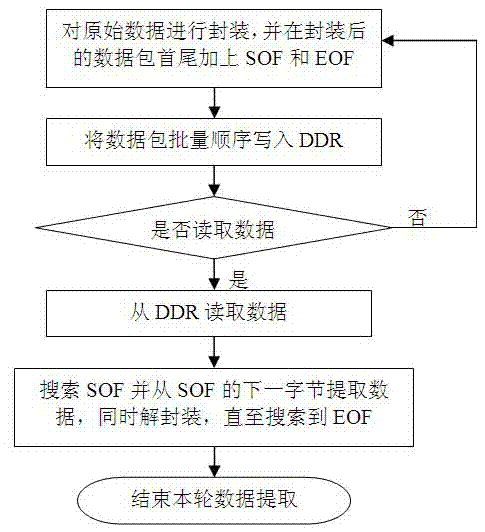

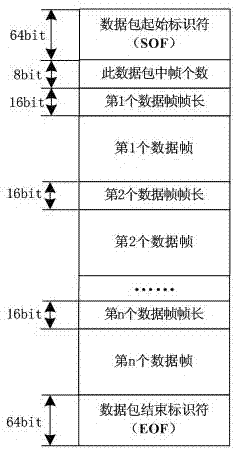

A method of improving the reading and writing rate of ddr memory

ActiveCN102629235BImprove read and write speedImprove management efficiencyMemory systemsData streamNetwork packet

Owner:重庆重邮汇测电子技术研究院有限公司

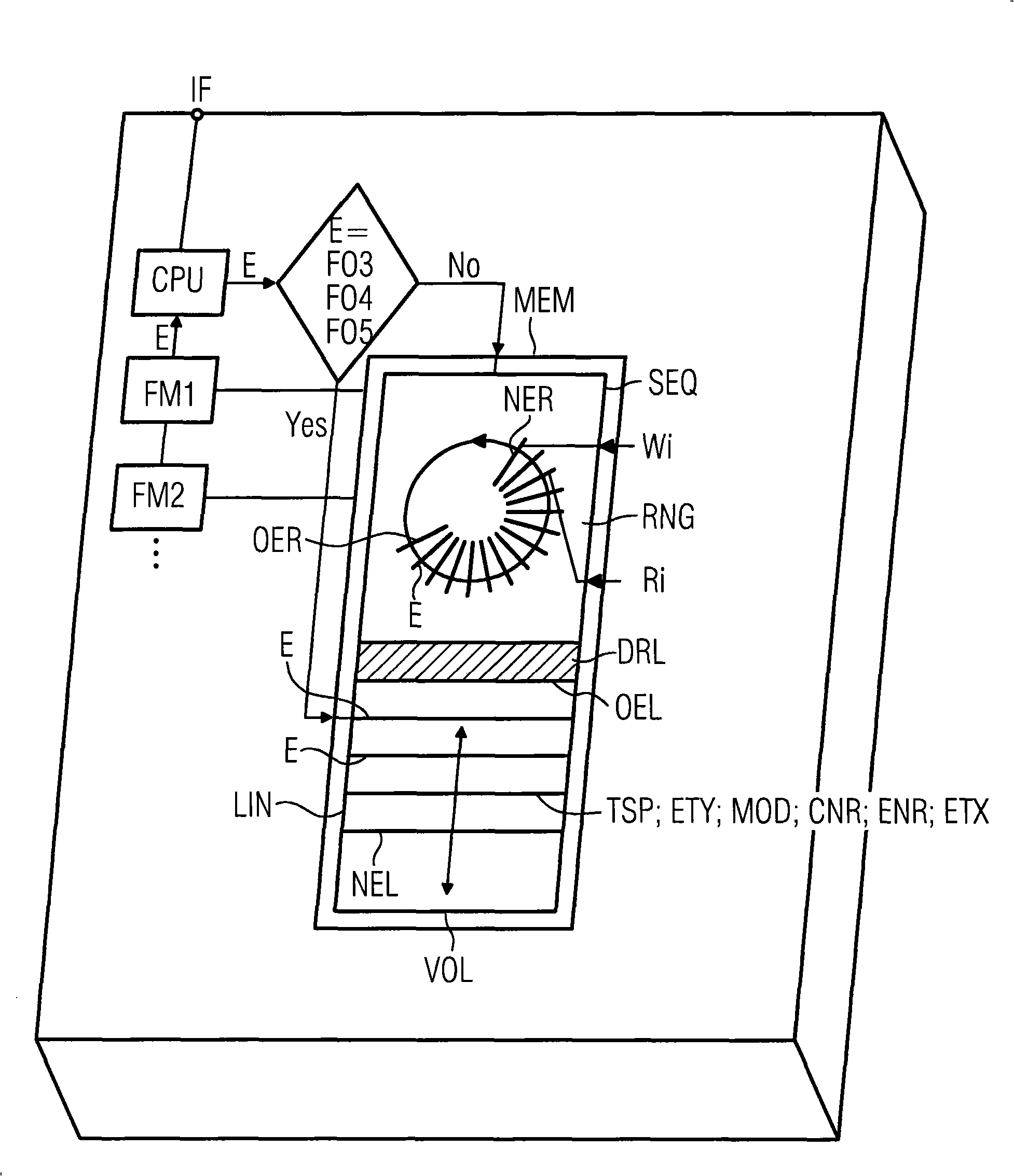

Data processing arrangement and the operation mode thereof

InactiveCN101268495AFully textualizedReliable masteryRegistering/indicating working of vehiclesSequence memoryOperation mode

The invention relates to a data processing arrangement, in particular to a tachograph (DTCO) for a motor vehicle comprising a control device (CPU) and at least one memory (MEM). The aim of said invention is to better guarantee the traceability of an error arising during the data processing arrangement operation. According to said invention, at least one partial area of the memory (MEM) is embodied in the form of a sequence memory (SEQ) and a control device (CPU) is constructed in such a way that sequences of the data processing arrangement or of the tachograph (DTCO) are recorded in the sequence memory (SEQ), wherein the sequence memory (SEQ) is provided with at least one ring memory (RNG) which is organised in such a way an oldest input (OER) is overwritten by a new input (NER), respectively.; Said invention makes it possible to record a plurality of sequential events leading to a substantial error in the sequence memory (SEQ) in such a way the size of the memory (MEM) is increased within economically acceptable limits during a long operation of the arrangement.

Owner:VDO AUTOMOTIVE