CMOS devices with a single work function gate electrode and method of fabrication

a technology of gate electrodes and work functions, applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of compromising sce, affecting the work function of transistors, and having a threshold voltage that is too high,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] A novel device structure and its method of fabrication are described. In the following description, numerous specific details are set forth, such as specific materials, dimensions and processes, etc. in order to provide a thorough understanding of the present invention. In other instances, well-known semiconductor processes and manufacturing techniques have not been described in particular detail in order to not unnecessarily obscure the present invention.

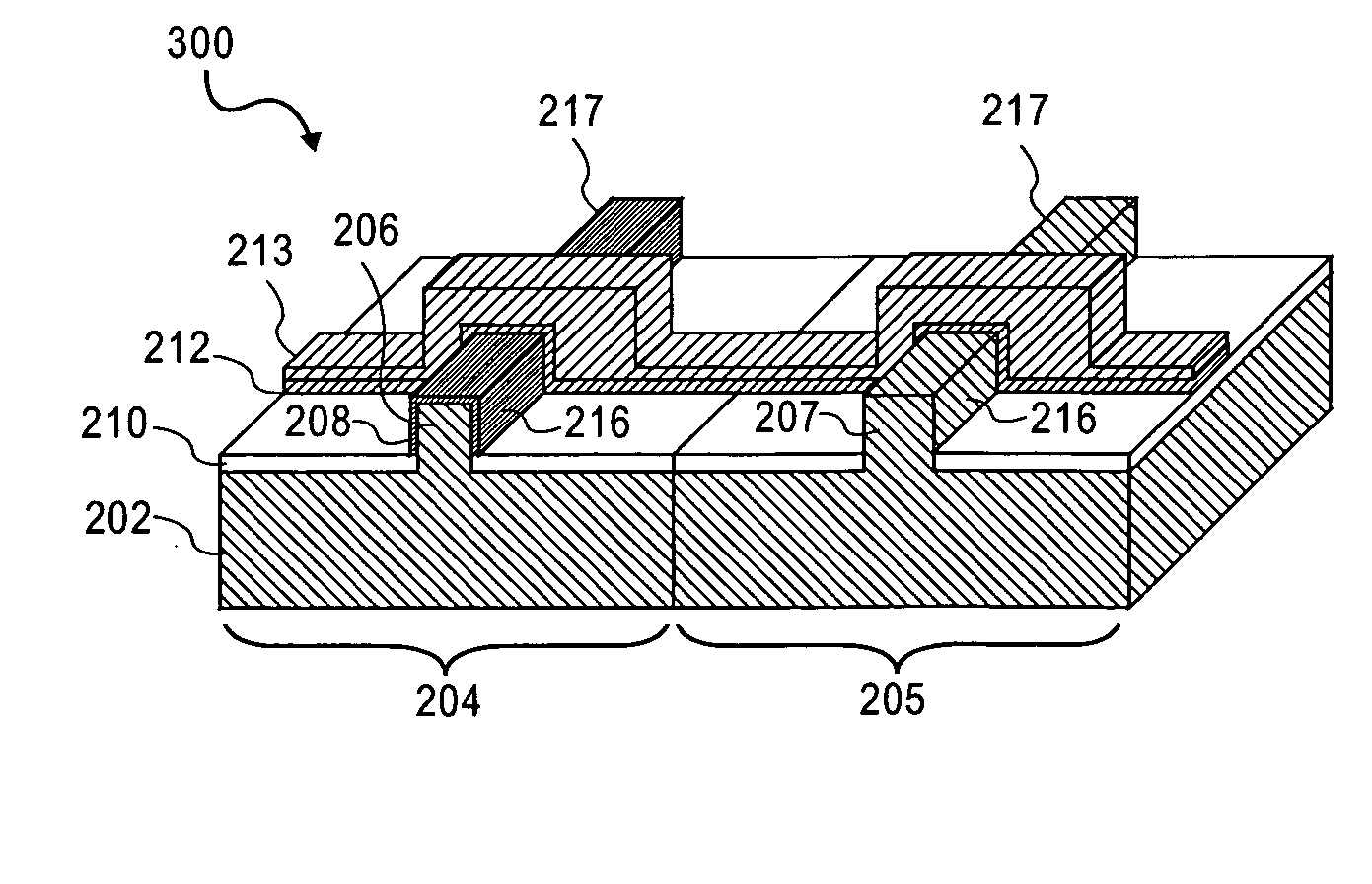

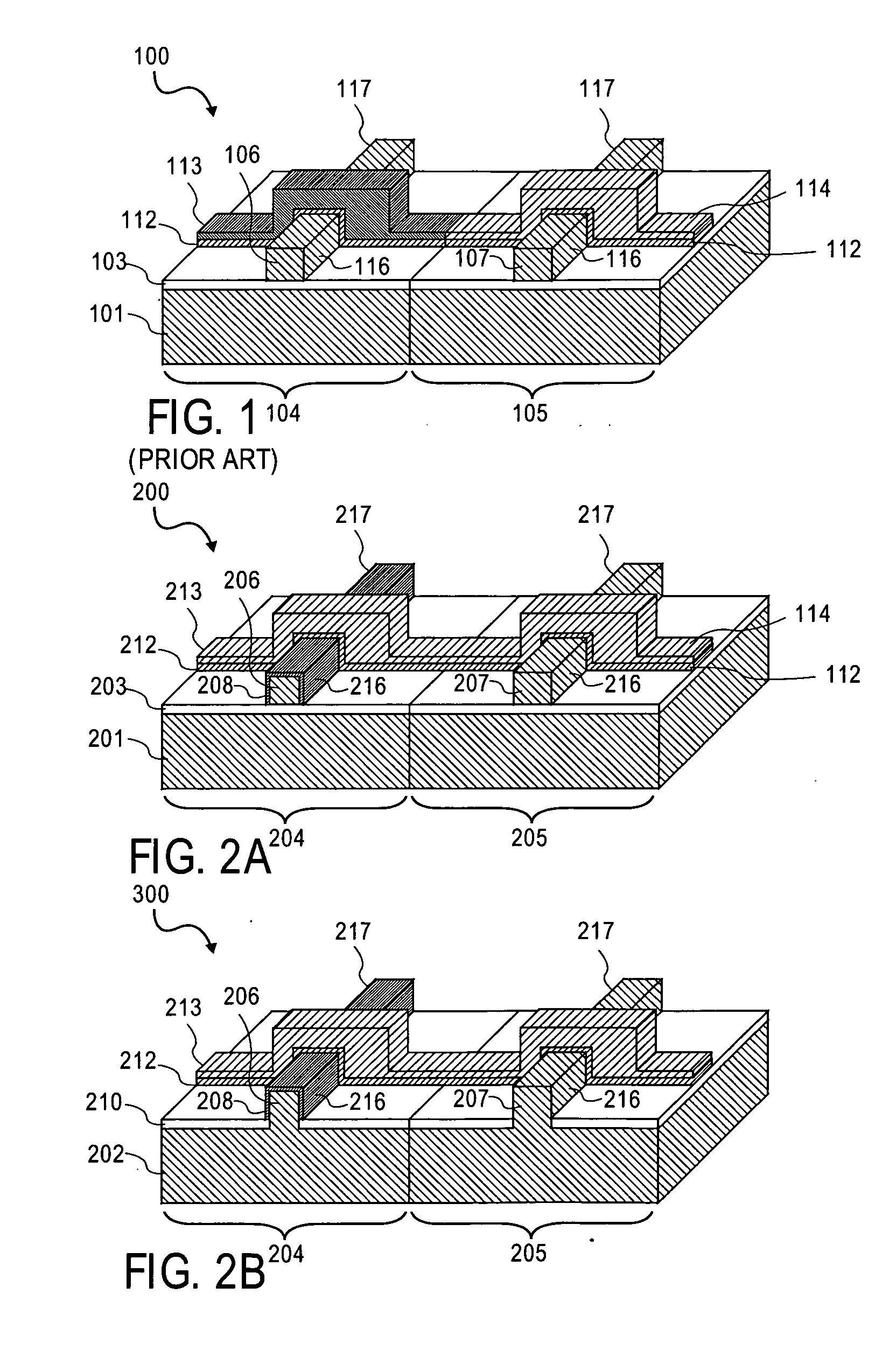

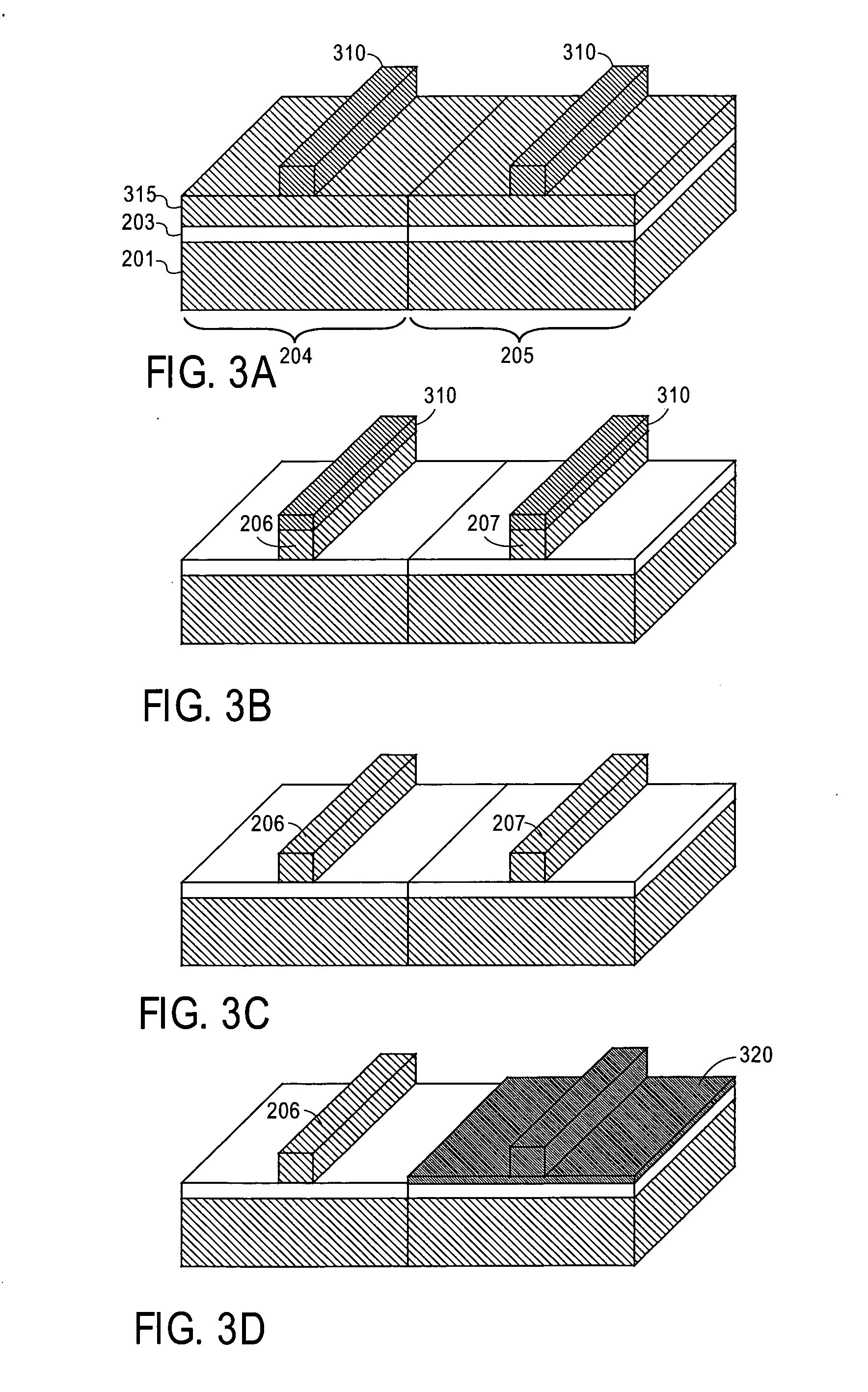

[0015] Embodiments of the present invention include complementary (pMOS and nMOS) transistors having semiconductor channel regions which have been band gap engineered to achieve a low threshold voltage. In particular embodiments, the complementary devices utilize the same material having a single work function as the gate electrode. Engineering the band gap of the semiconductor transistor channels rather than engineering the work function of the transistor gate metal for the individual pMOS and nMOS devices avoids the manuf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More