Patents

Literature

77results about How to "High density packaging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

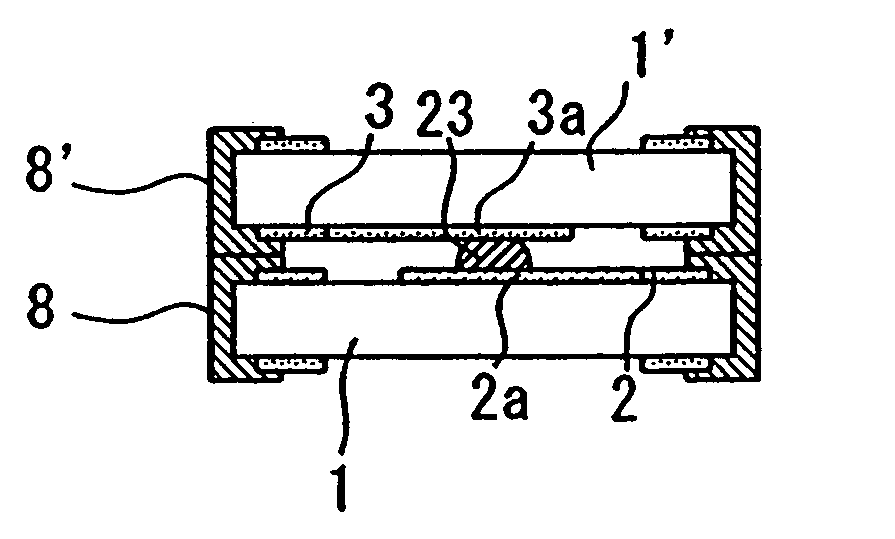

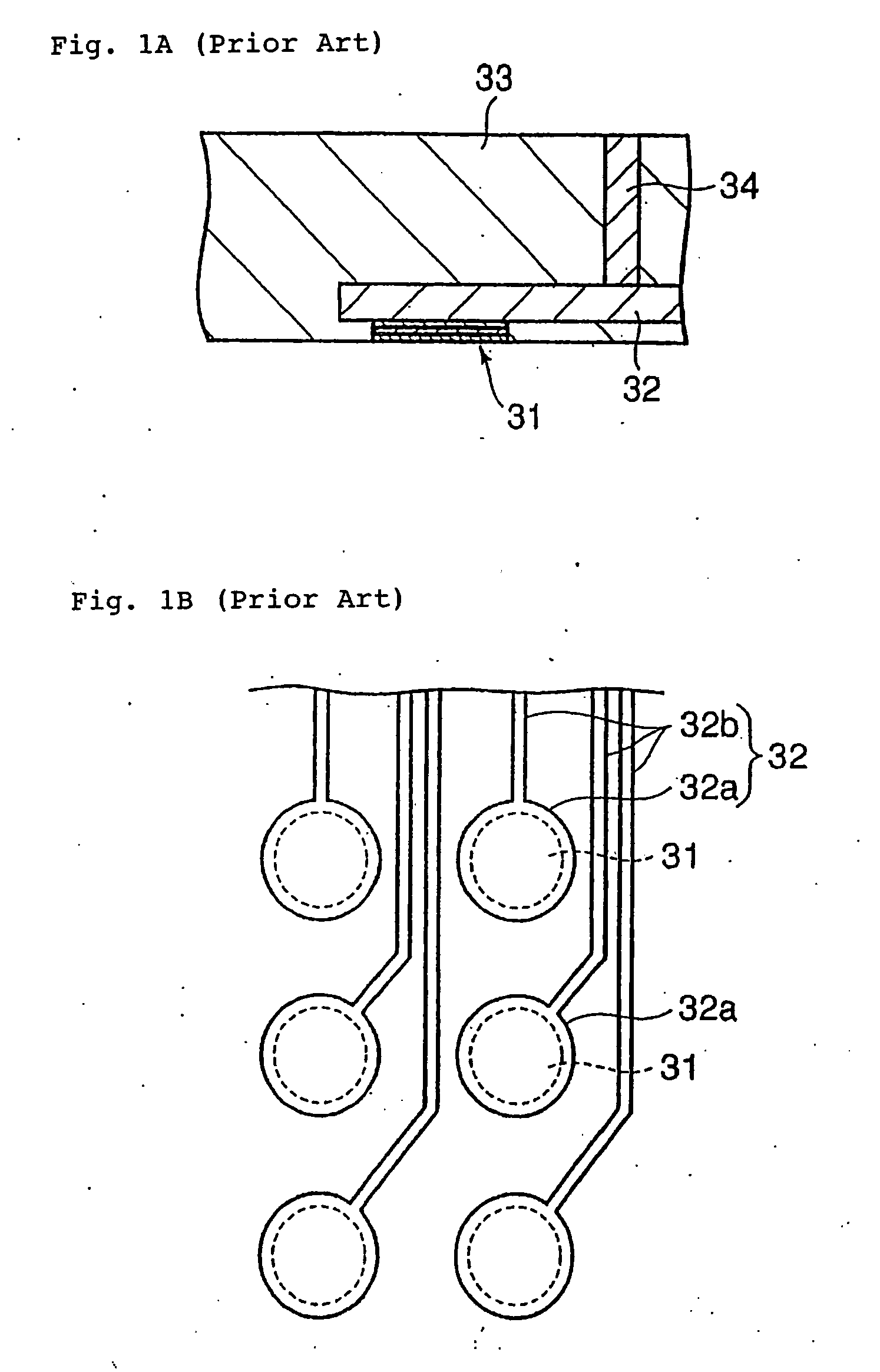

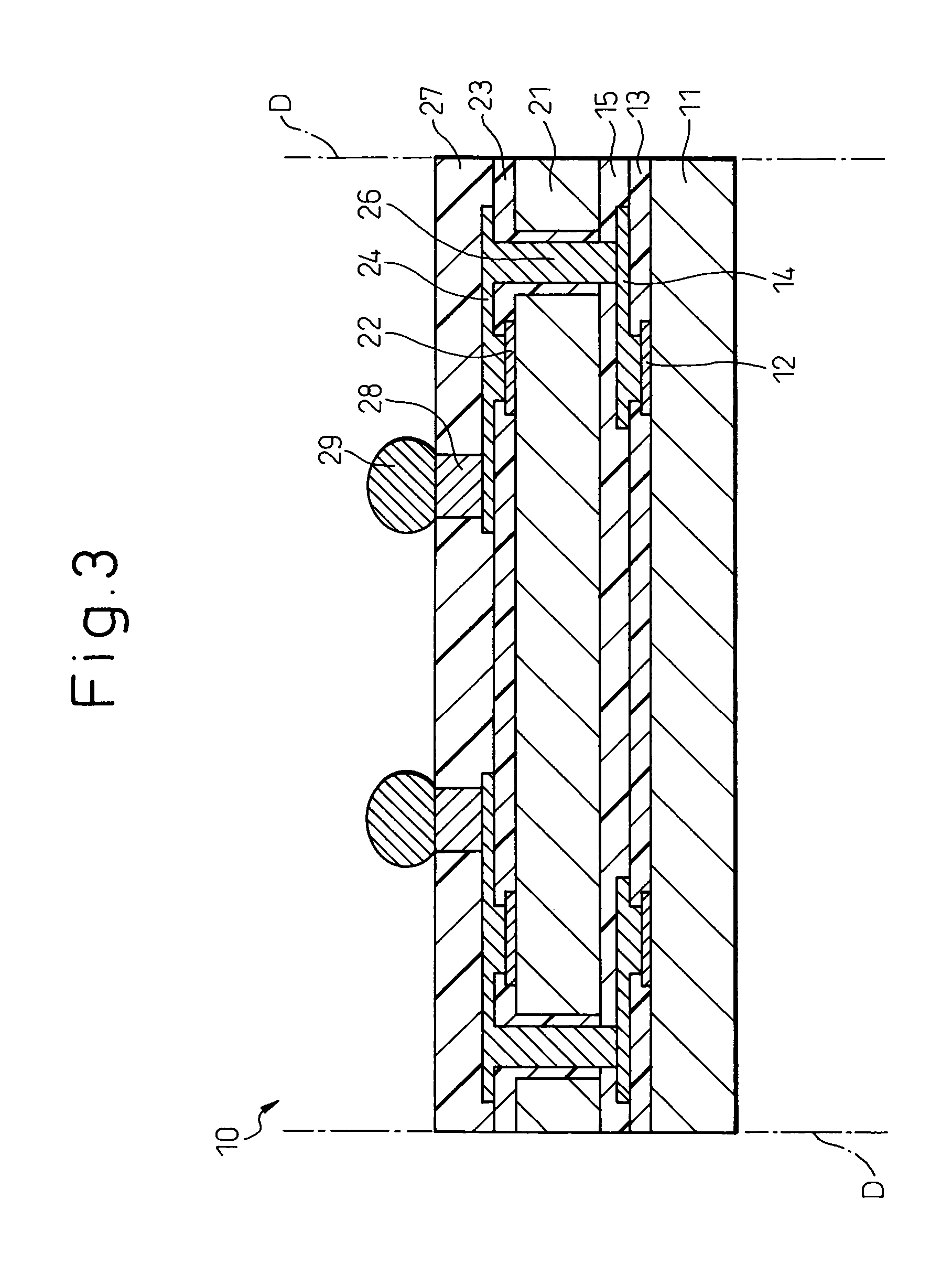

Semiconductor device having densely stacked semiconductor chips

InactiveUS6984885B1High-density packagingSemiconductor/solid-state device detailsSolid-state devicesInsulation layerLead bonding

In a semiconductor chip having electrodes formed on the top surface, and electrodes or an insulation layer formed on the back surface, the top-surface electrodes are loop-connected with the back-surface electrodes by wire bonding, or, the top-surface electrodes are connected with the back-surface electrodes or an insulation layer by conductive clip, or by deposited conductive materials. The semiconductor chips thus produced are stacked, and wires, conductive clips, or conductive materials are connected and fixed to each other to produce a stacked semiconductor device in which semiconductor chips of the same size are densely packaged. Thus, a semiconductor device is provided which enables high-density packaging of semiconductor chips even of the same size.

Owner:RENESAS ELECTRONICS CORP

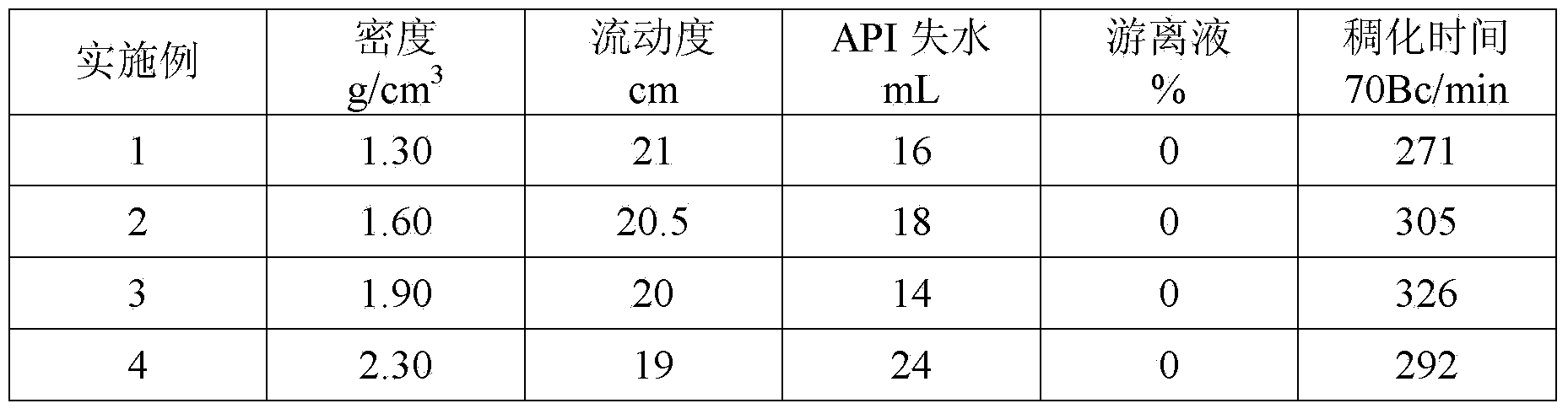

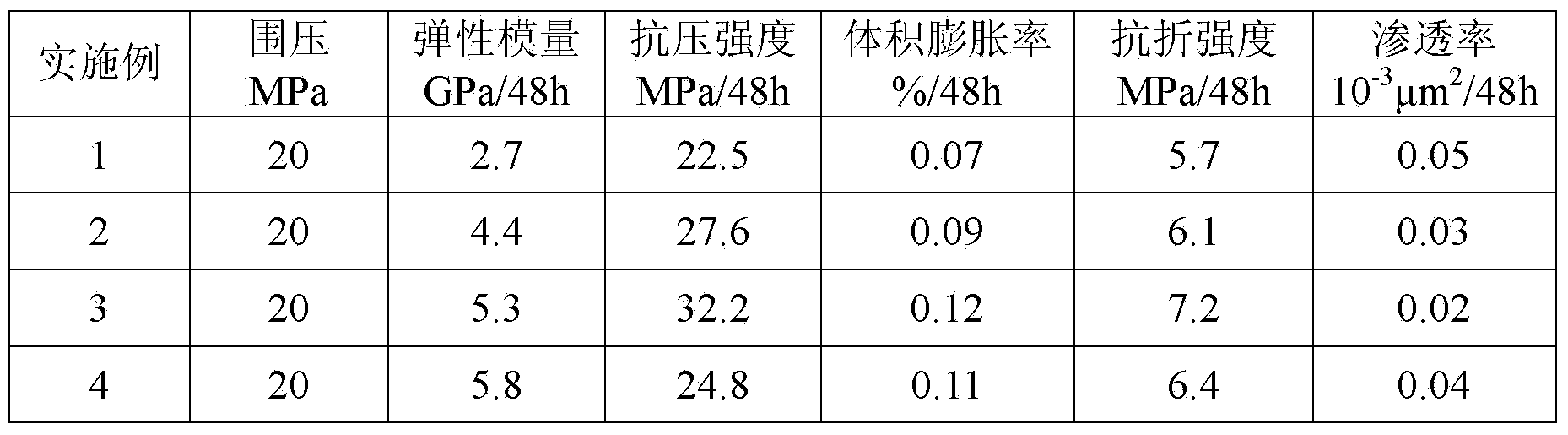

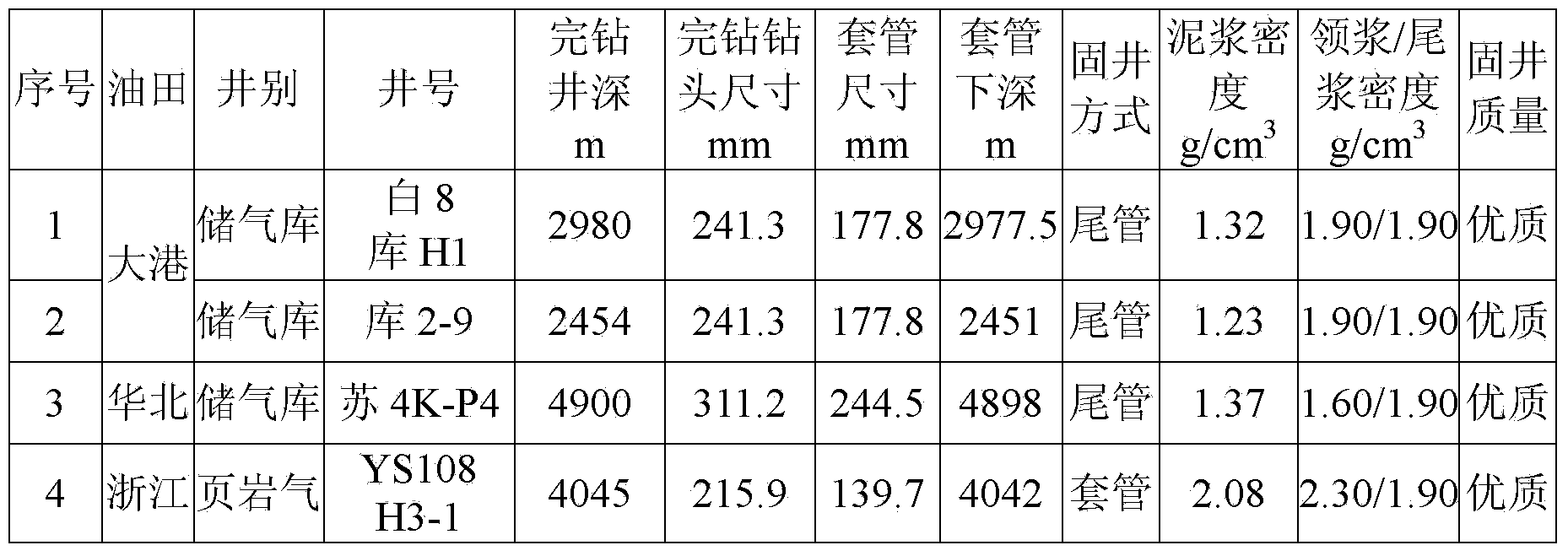

Expanded flexible well cementing grout and preparation method thereof

ActiveCN104371678ALow elastic modulusLower transfer coefficientDrilling compositionHorizontal wellsVolumetric Mass Density

The invention provides an expanded flexible well cementing grout and a preparation method thereof. The grout comprises the following components in parts by weight: 100 parts of cement, 6-14 parts of toughening material, 3-80 parts of reinforcing material, 8-120 parts of density modifier, 0.5-2.5 parts of suspension stabilizer, 20-40 parts of high-temperature stabilizer, 35-100 parts of distilled water, 0.5-2 parts of dispersant, 0.5-4 parts of fluid loss agent, 0.3-4 parts of retarder, 0.1-2 parts of foam inhibitor and 0.1-2 parts of defoamer. The invention further provides a preparation method of the expanded flexible well cementing grout. The grout has good sedimentation stability; and the set cement has the characteristics of micro expansion, high strength and low elasticity modulus, and can avoid the phenomena of micro cracks, micro annuluses, even fracture and the like caused by cement sheaths in subsequent operation of gas storage wells, shale gas wells, dense oil-gas horizontal wells and the like, thus realizing good zonal isolation and providing a technical support for long-term, safe and effective operation of oil-gas wells.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

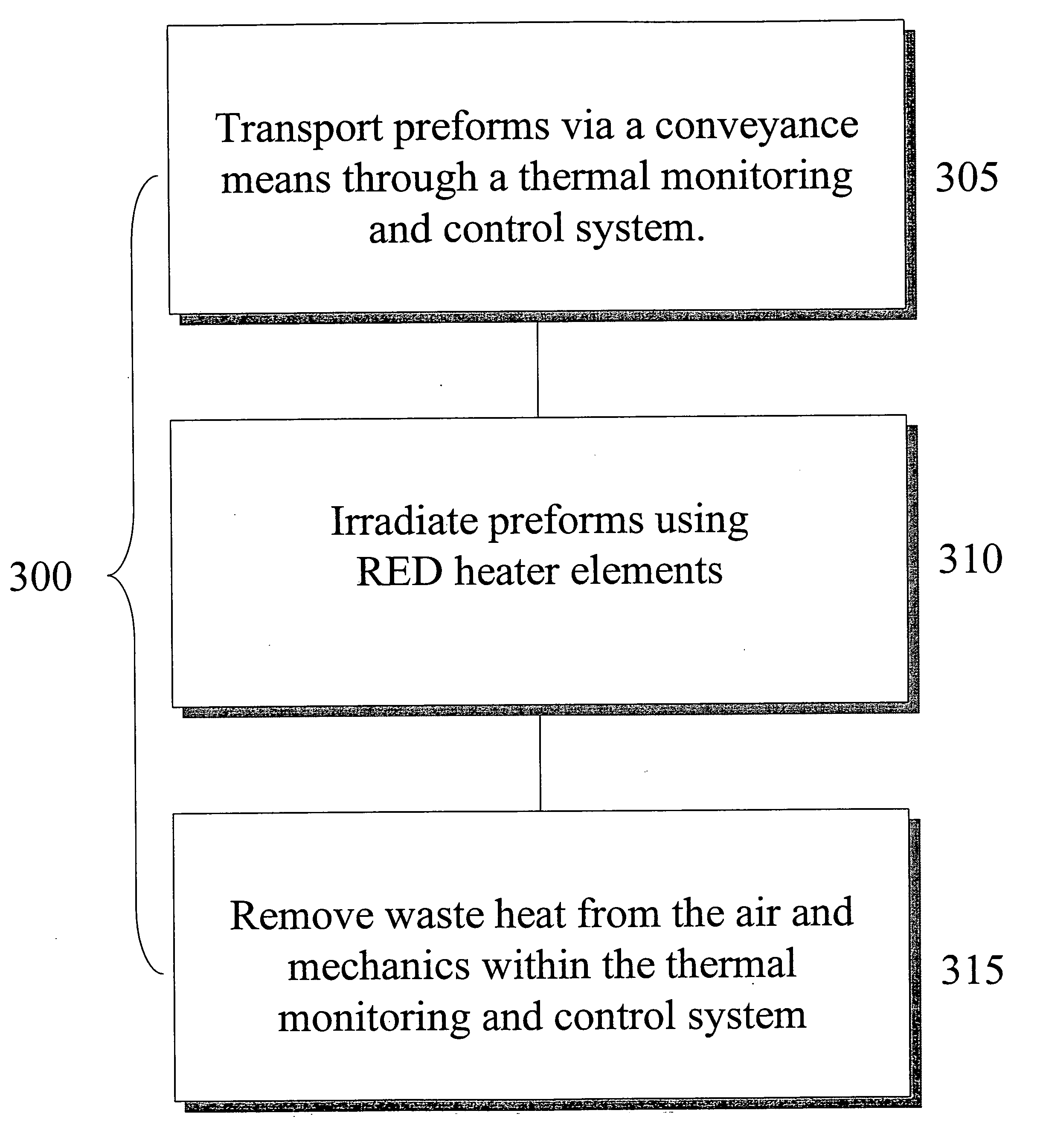

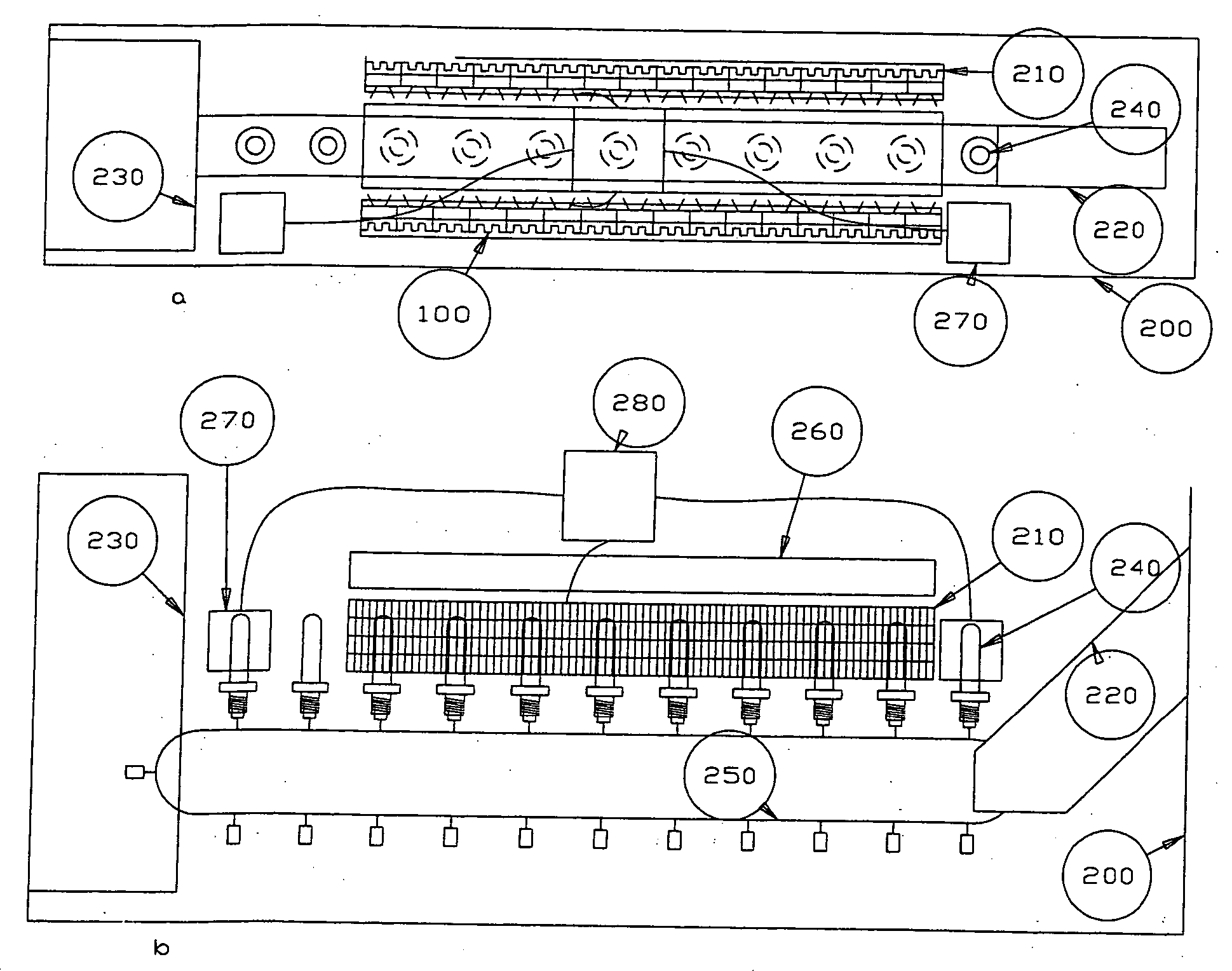

Method and system for wavelength specific thermal irradiation and treatment

ActiveUS20060118983A1Energy efficiencyMaintain abilityFood processingSolid-state devicesLength waveIrradiation

A system for direct injection of selected thermal-infrared (IR) wavelength radiation or energy into articles for a wide range of processing purposes is provided. These purposes may include heating, raising or maintaining the temperature of articles, or stimulating a target item in a range of different industrial, medical, consumer, or commercial circumstances. The system is especially applicable to operations that require or benefit from the ability to irradiate at specifically selected wavelengths or to pulse or inject the radiation. The system is particularly advantageous when functioning at higher speeds and in a non-contact environment with the target.

Owner:PRESSCO IP LLC

Method and system for wavelength specific thermal irradiation and treatment

ActiveUS20060280825A1Energy efficiencyMaintain abilityFood processingSolid-state devicesLength waveThermal infrared

A system for direct injection of selected thermal-infrared (IR) wavelength radiation or energy into articles for a wide range of processing purposes is provided. These purposes may include heating, raising or maintaining the temperature of articles, or stimulating a target item in a range of different industrial, medical, consumer, or commercial circumstances. The system is especially applicable to operations that require or benefit from the ability to irradiate at specifically selected wavelengths or to pulse or inject the radiation. The system is particularly advantageous when functioning at higher speeds and in a non-contact environment with the target.

Owner:PRESSCO IP LLC

Super-high-performance cement base repairing material and preparing method thereof

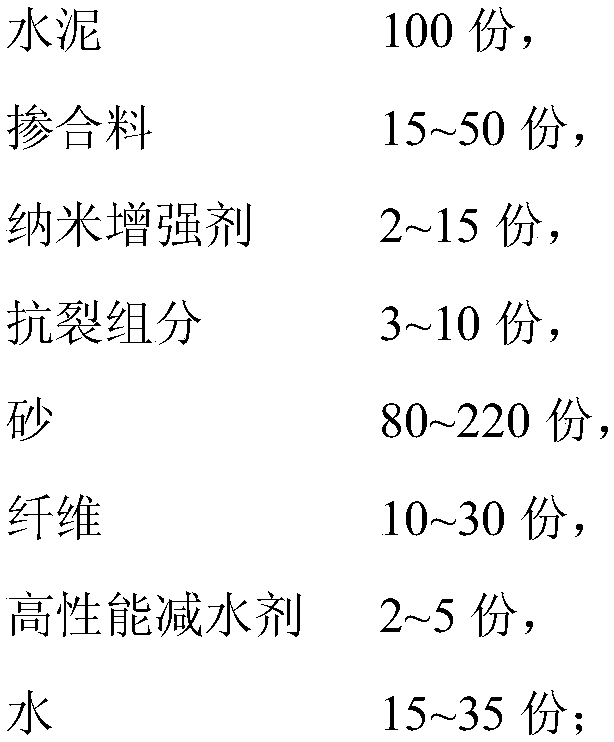

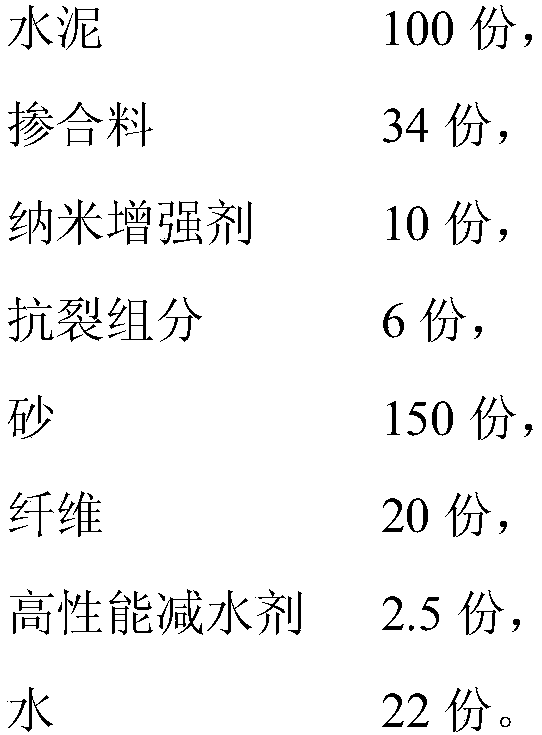

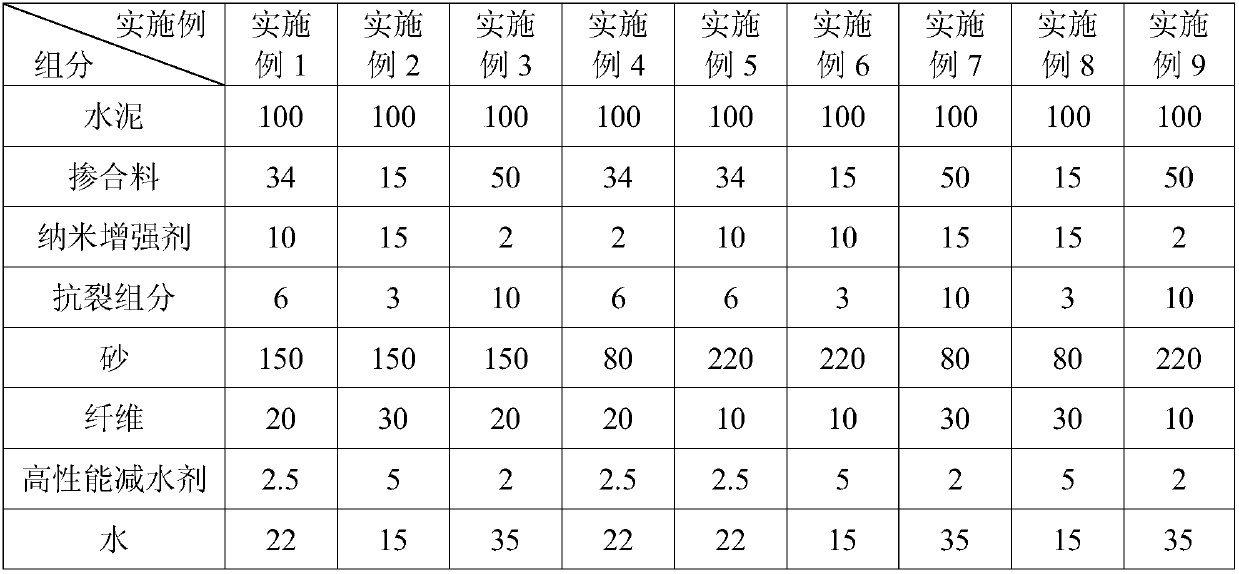

The invention discloses a super-high-performance cement base repairing material and a preparing method thereof. The repairing material is prepared from, by mass, 100 parts of cement, 15-50 parts of admixture, 2-15 parts of nanometer reinforcing agent, 3-10 parts of crack resistance component, 80-220 parts of sand, 10-30 parts of fiber, 2-5 parts of high-performance water reducing agent and 15-35 parts of water. The super-high-performance cement base repairing material has super-high tensile strength, bending resistance and adhesive strength and extremely low shrinkage performance, and has excellent construction performance, high elasticity modulus and super-high durability. The material has effects of repairing, reinforcing, seepage preventing, preventing and the like, and therefore the service life of the repairing material and a structure is prolonged. In addition, the material can be used as a joint material of a structural joint.

Owner:JIANGSU SOBUTE NEW MATERIALS

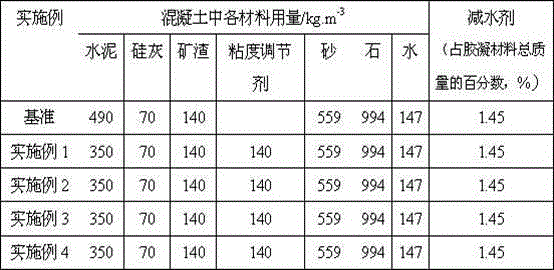

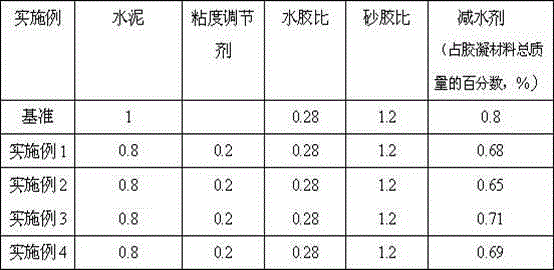

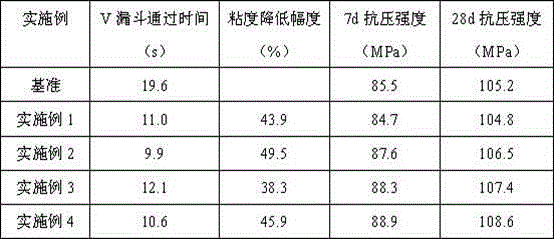

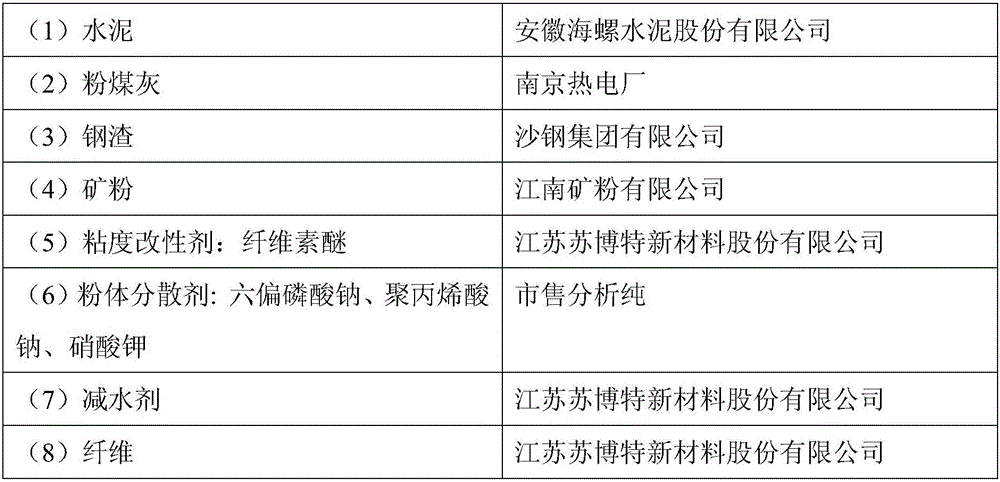

Viscosity modifier for high or ultrahigh-strength concrete

The invention relates to a viscosity modifier for high or ultrahigh-strength concrete. The viscosity modifier comprises the following substances in percentage by weight: 2-10% of silica fume, 10-20% of pulverized coal ash, 2-3% of exciting agent and 67-86% of ultrafine powder. The viscosity modifier added into the high or ultrahigh-strength concrete at a ratio of 10-30% can reduce the viscosity of the concrete by 25-60%. By optimizing the particle size distribution of cementitious materials, the bulk density can be increased, the thicknesses of water film layers on the surfaces of particles in a cementitious system can be increased, the adsorption efficiency of a water reducing agent can be improved, the use amount of the water reducing agent can be reduced, and the viscosity of an aqueous solution in concrete can be lowered. Due to the morphology of powder particles and the action of charges on the surfaces of the powder particles, the interaction force of the particles can be reduced, the viscosity of the concrete can be lowered, and the strength of the concrete can not be affected. The viscosity modifier can be also used for a mortar system with low water-cement ratio.

Owner:JIANGSU SOBUTE NEW MATERIALS +1

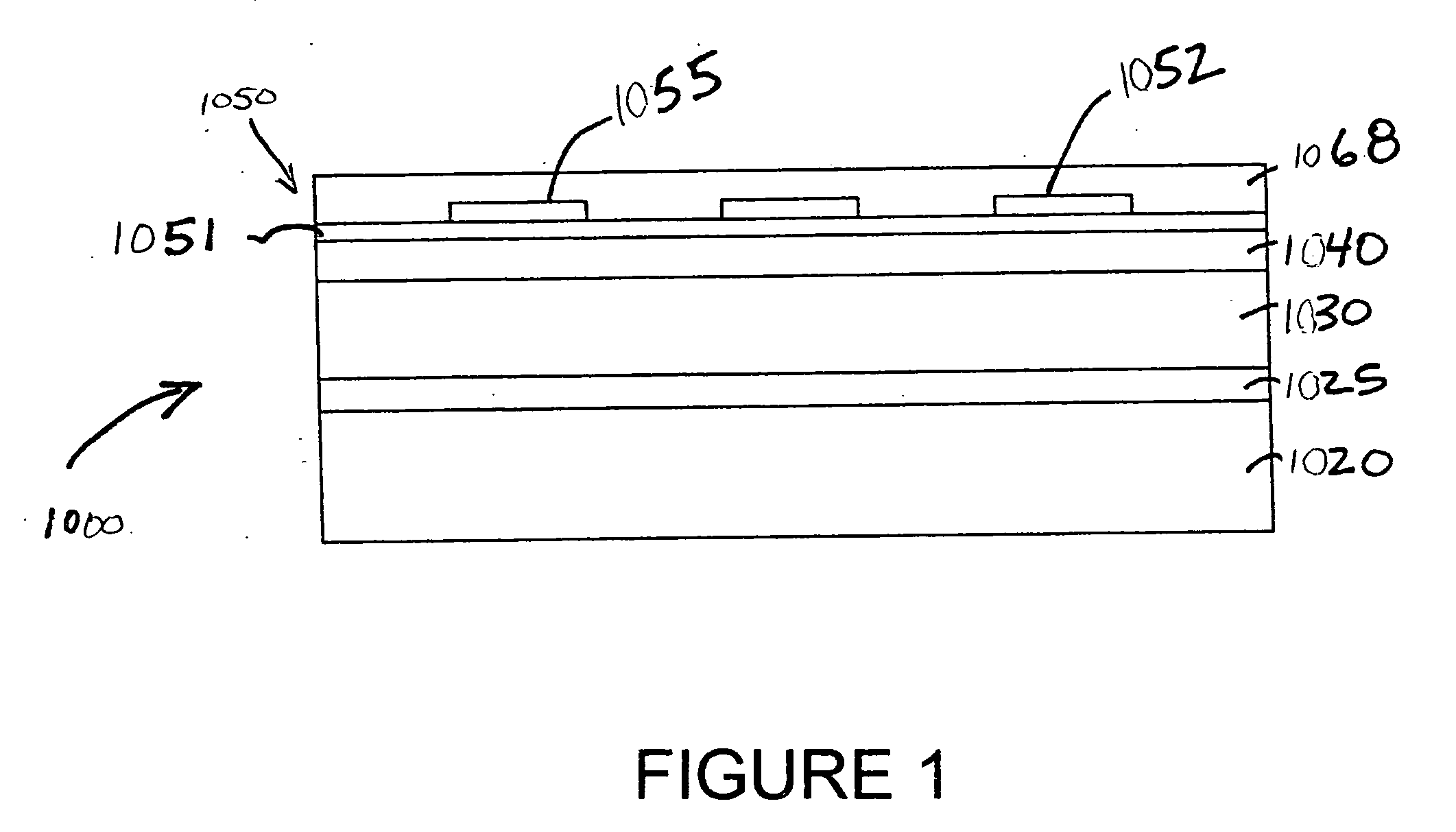

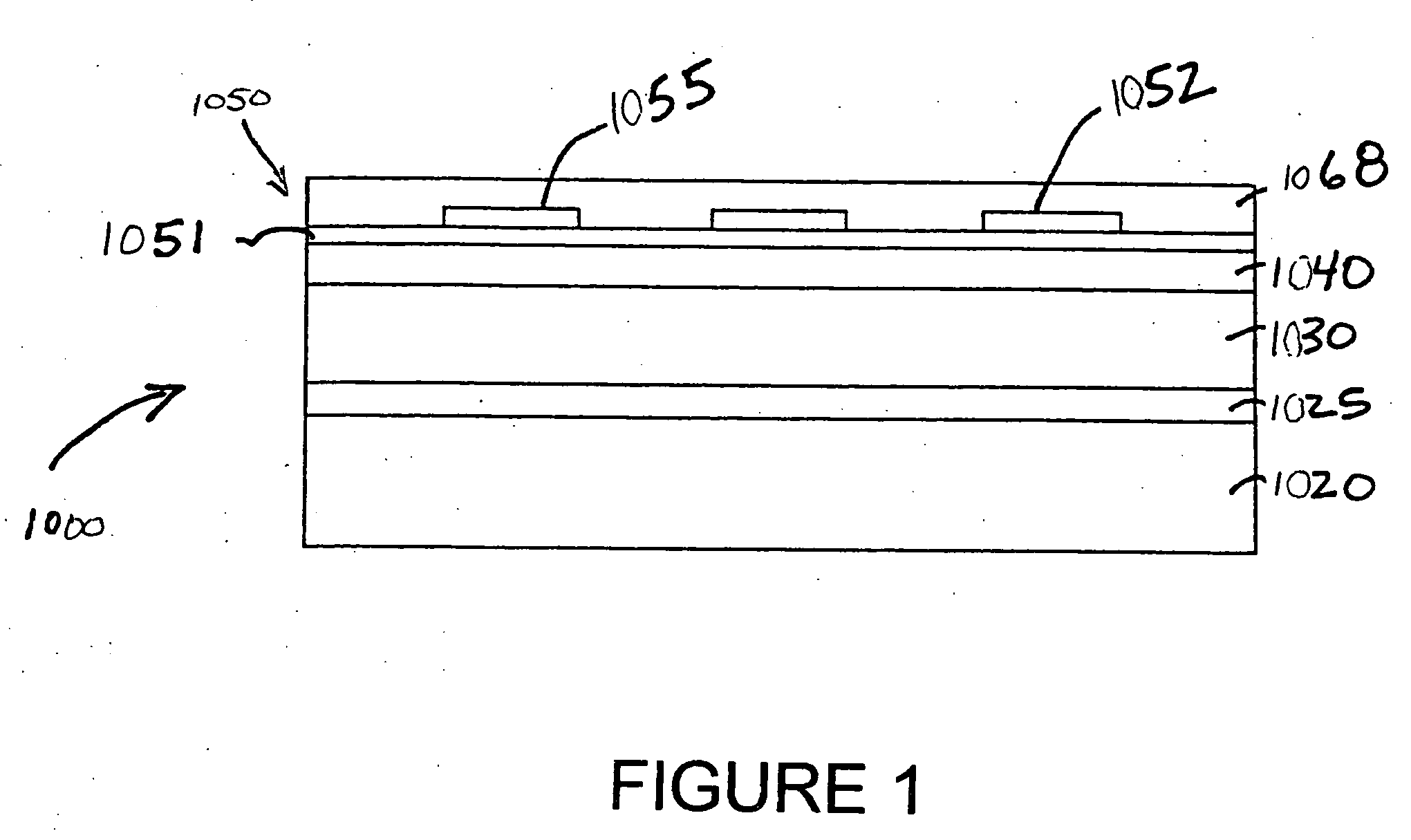

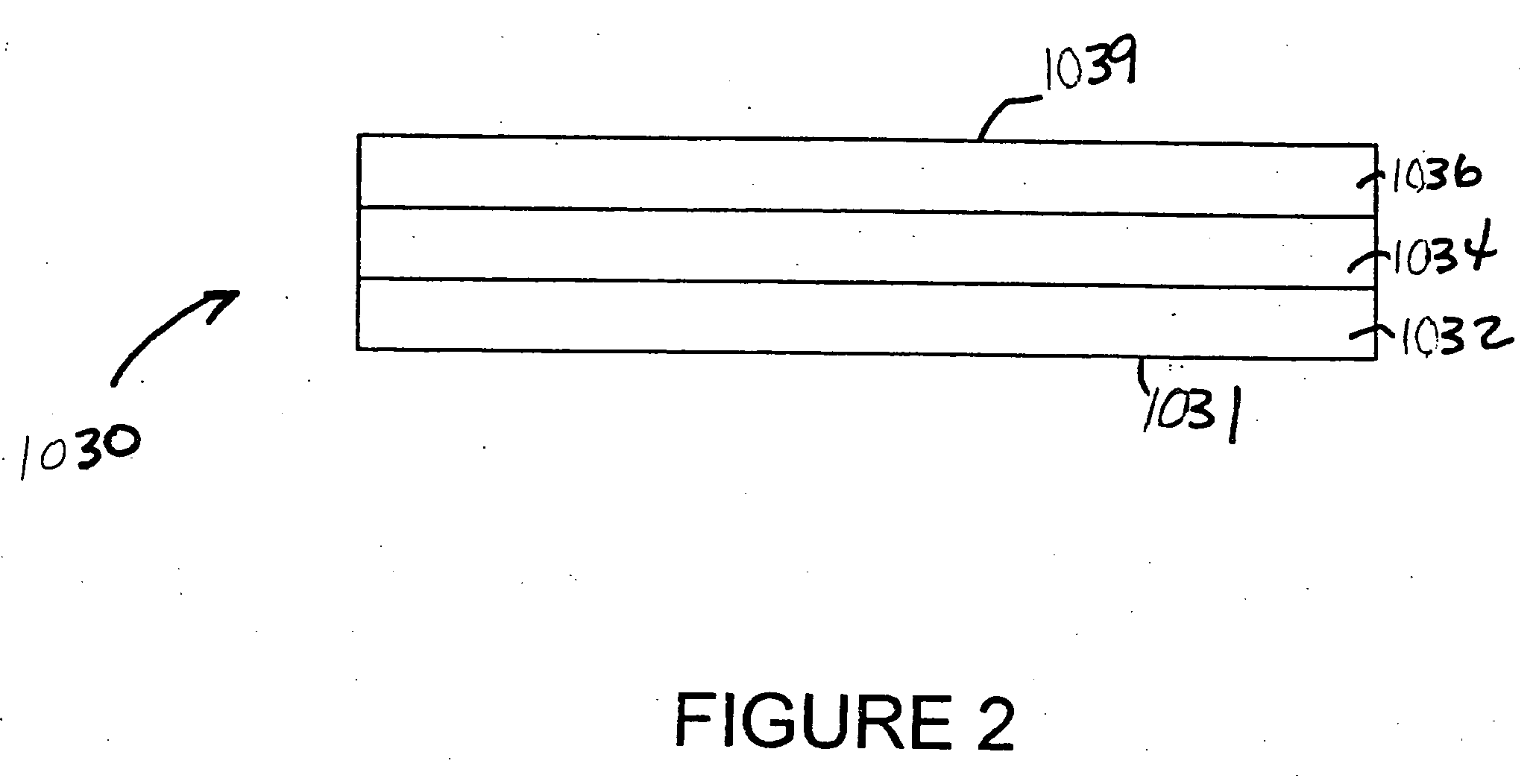

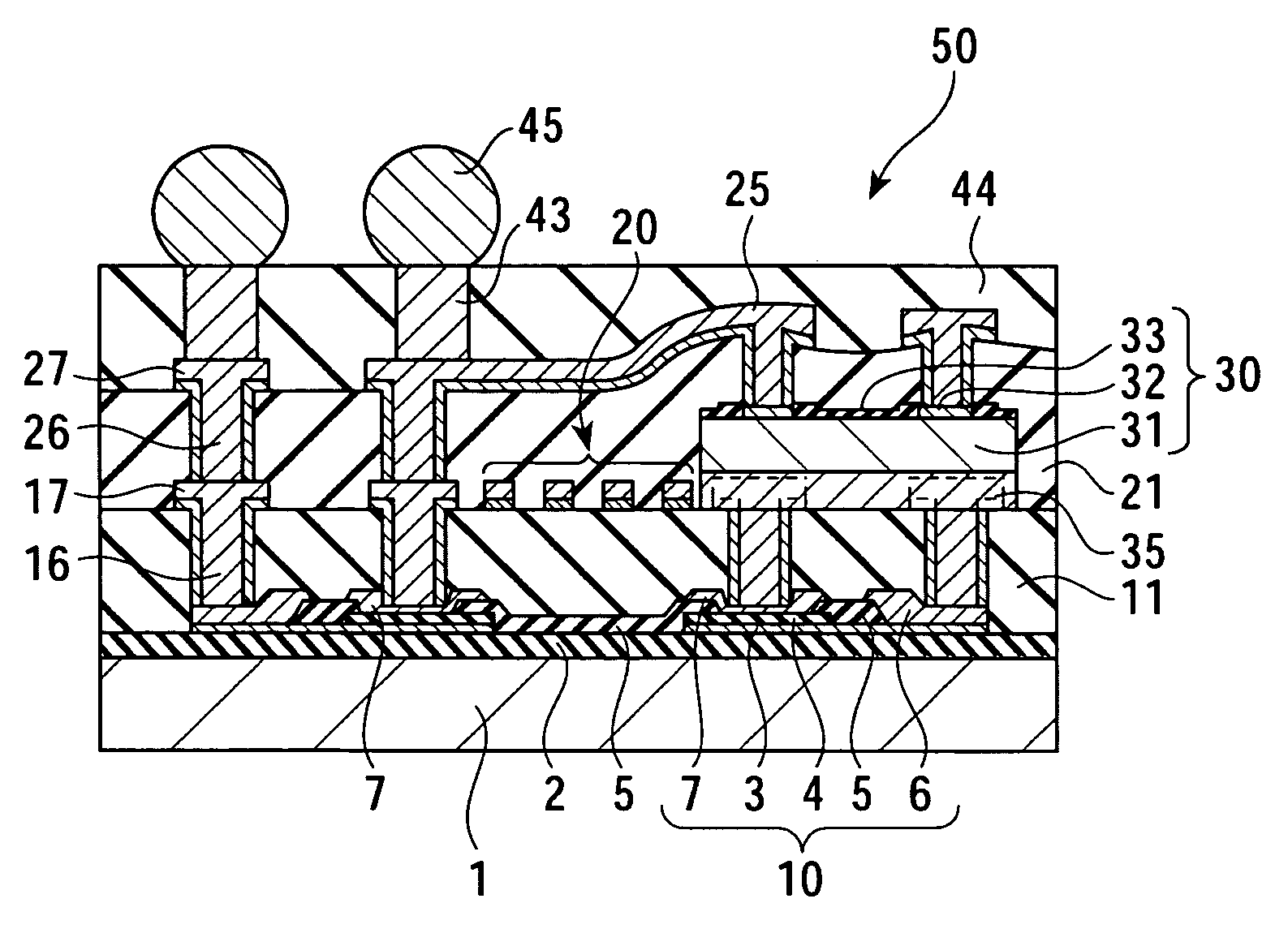

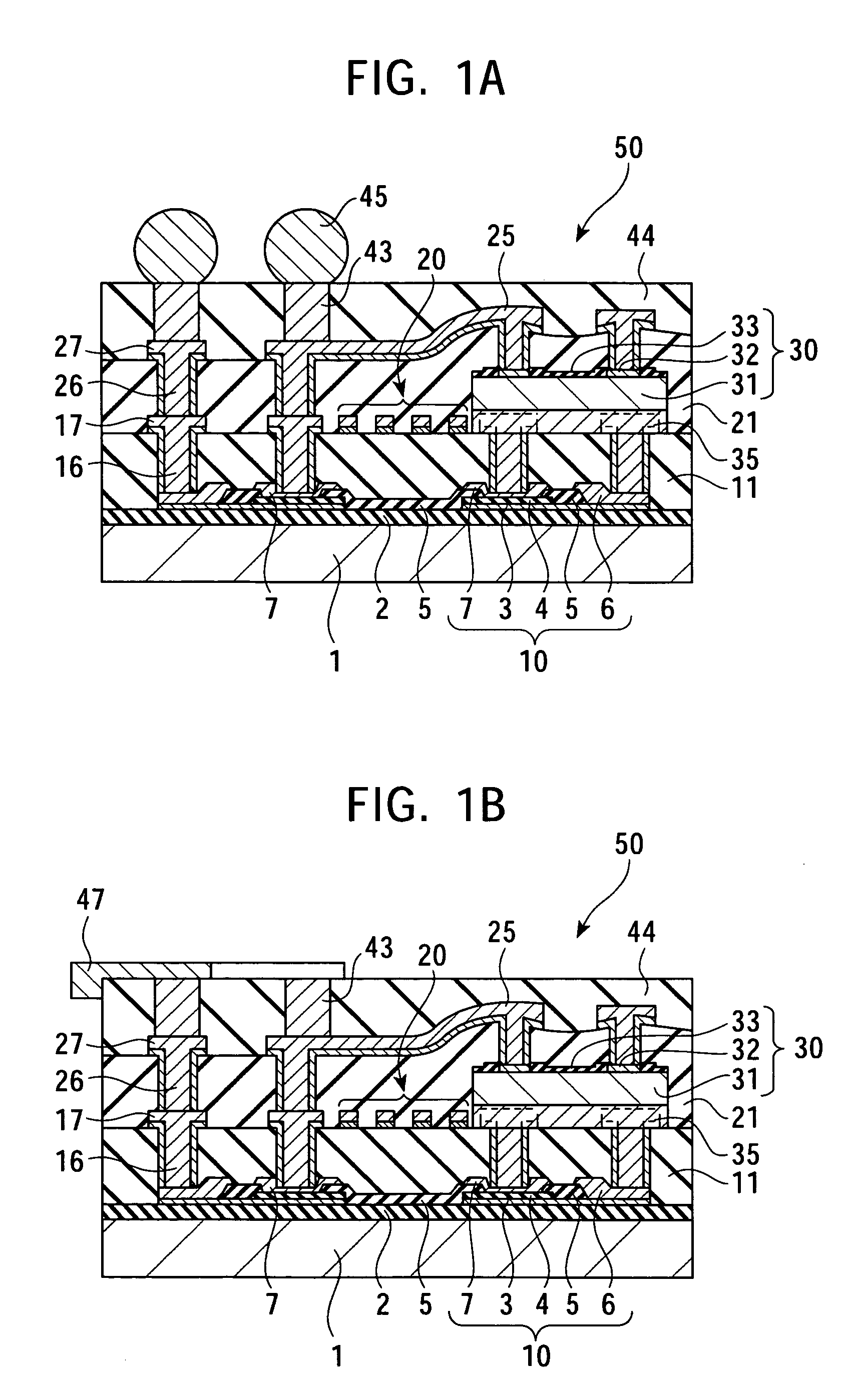

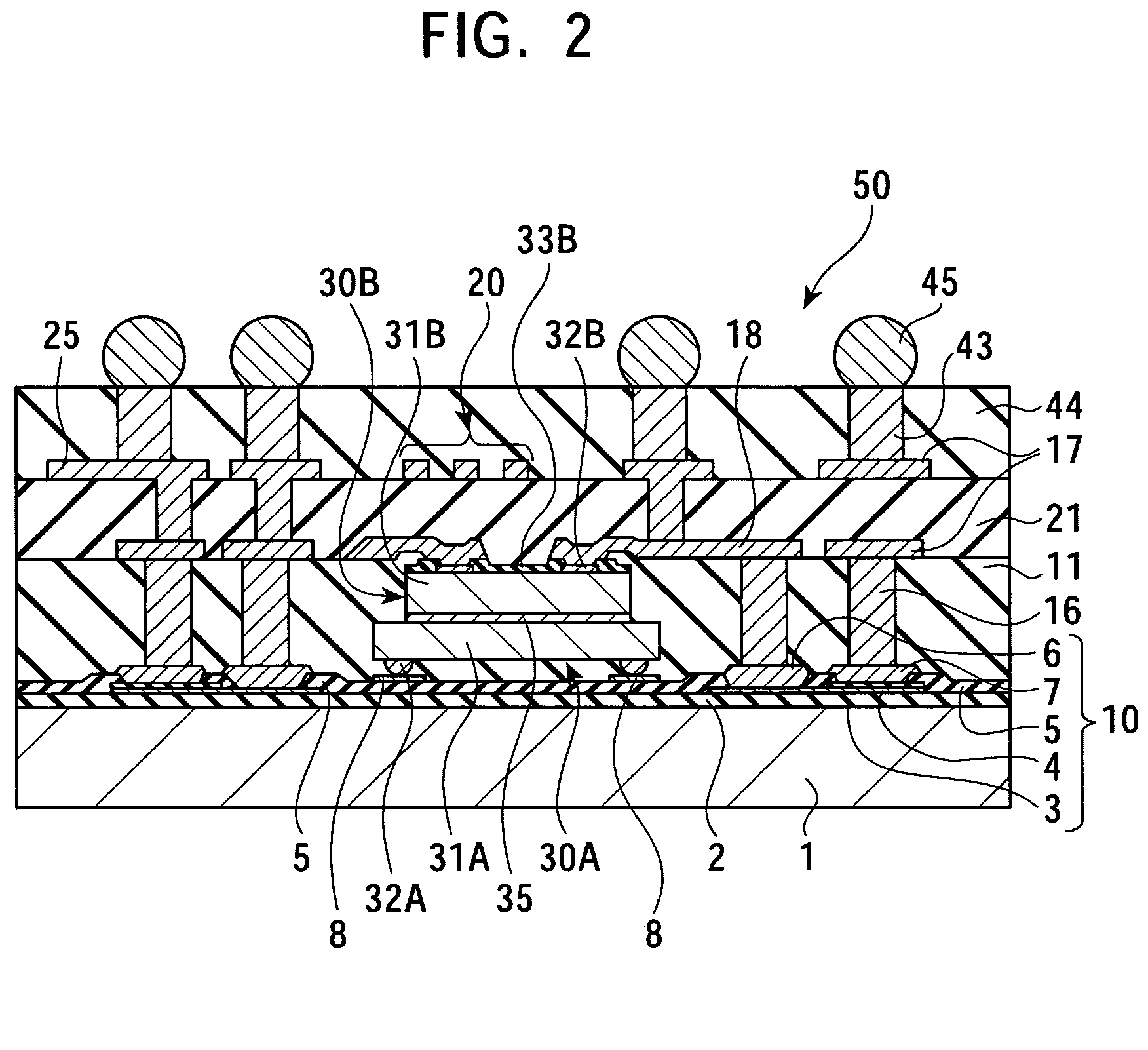

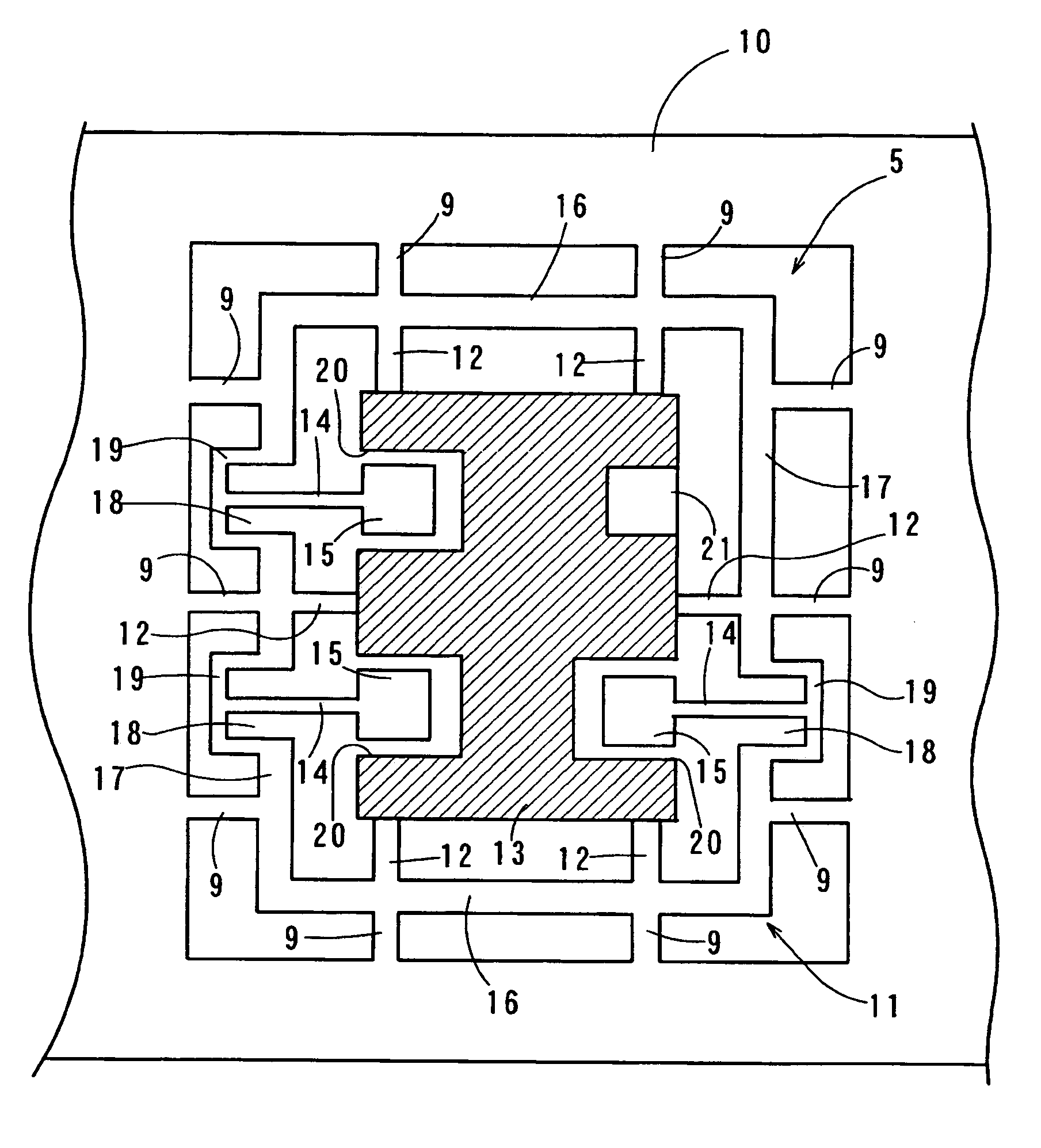

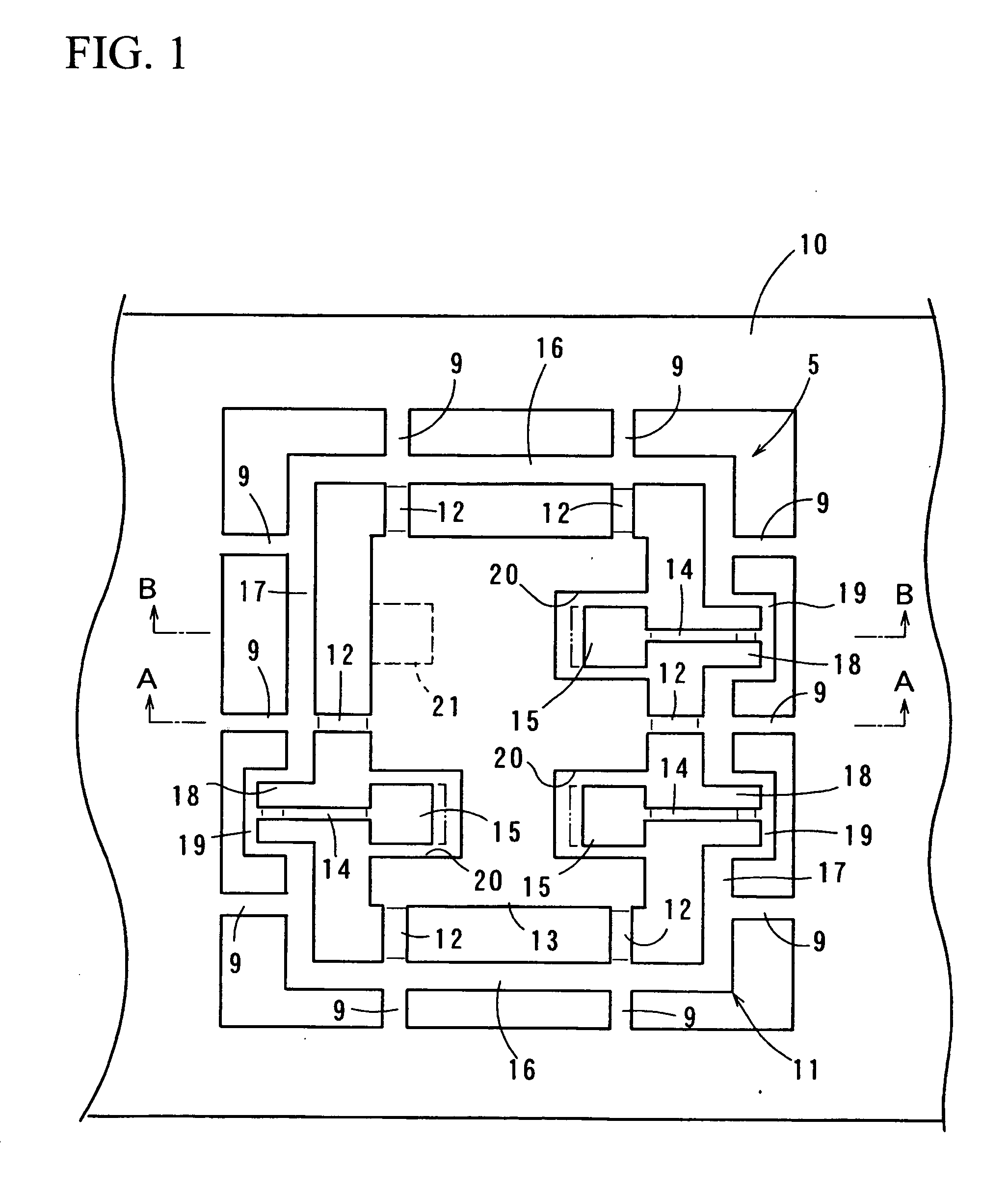

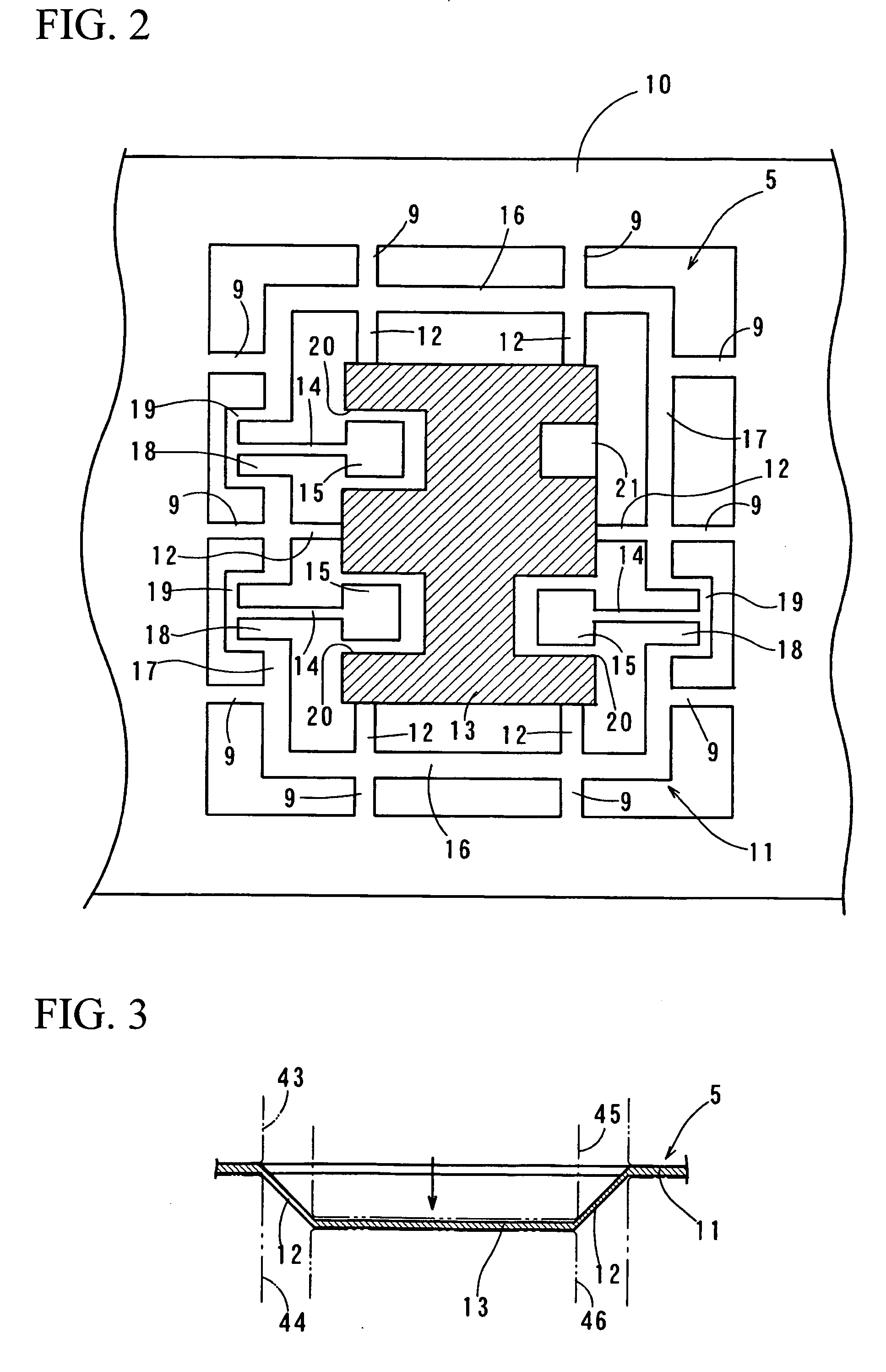

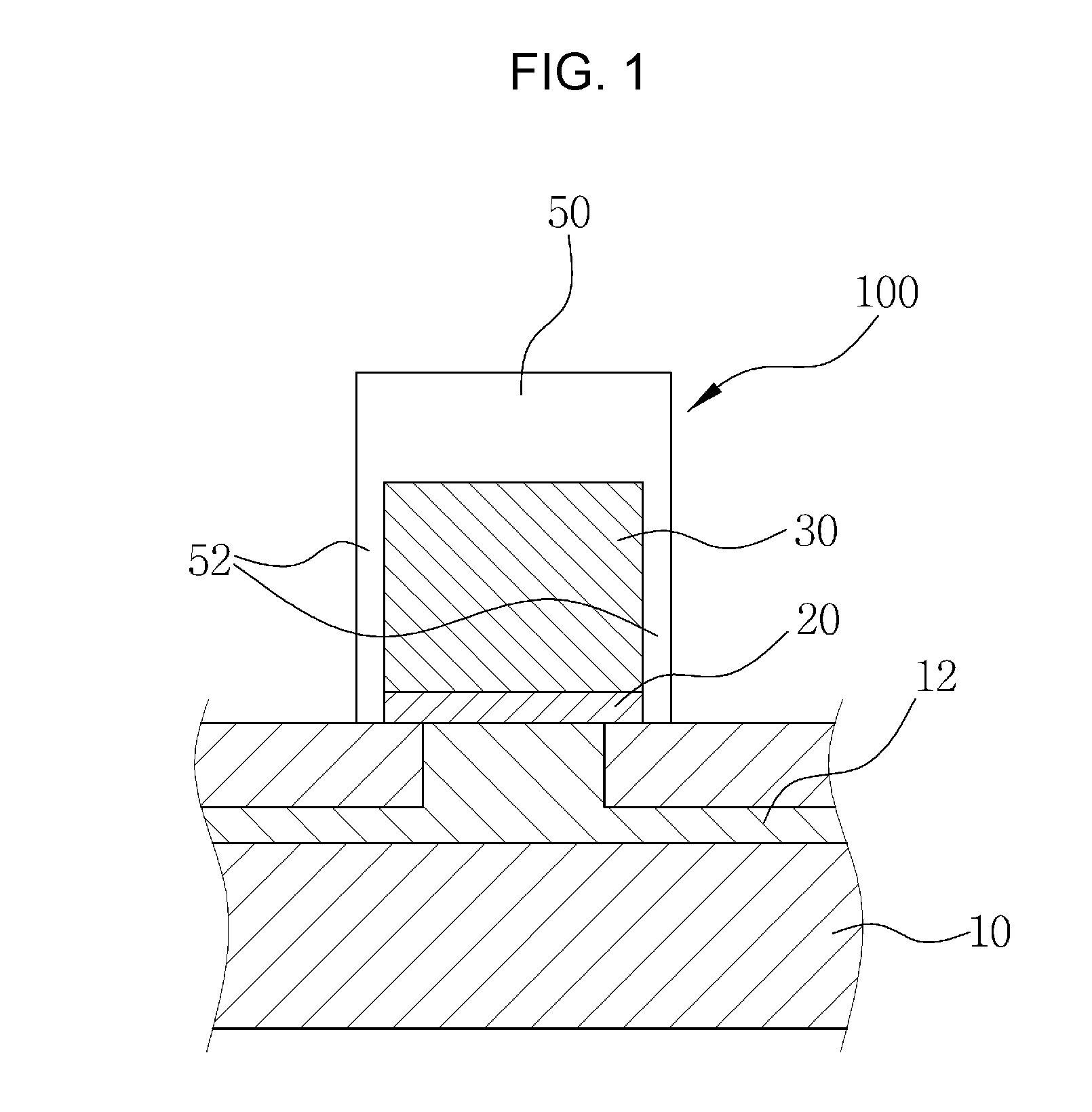

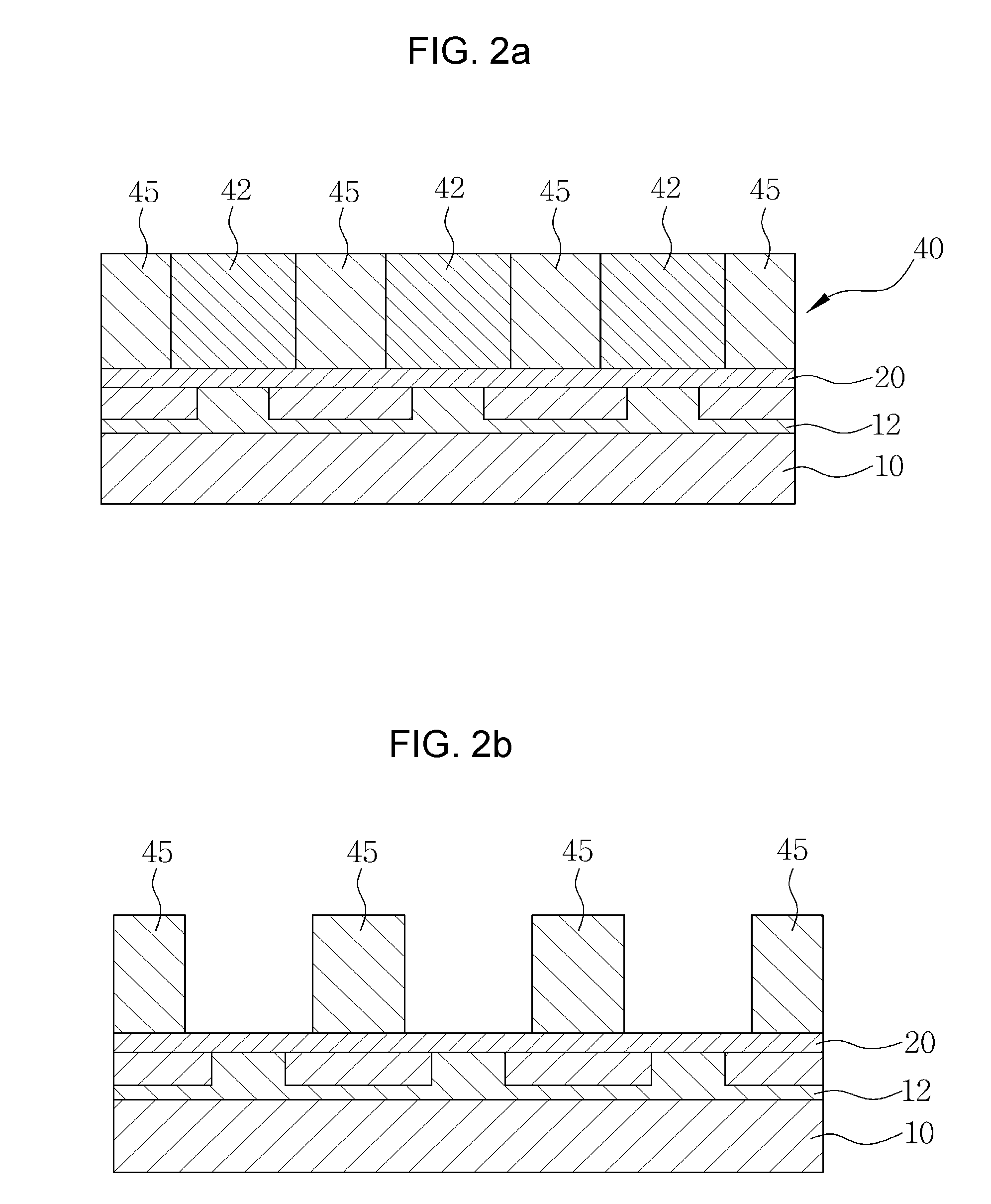

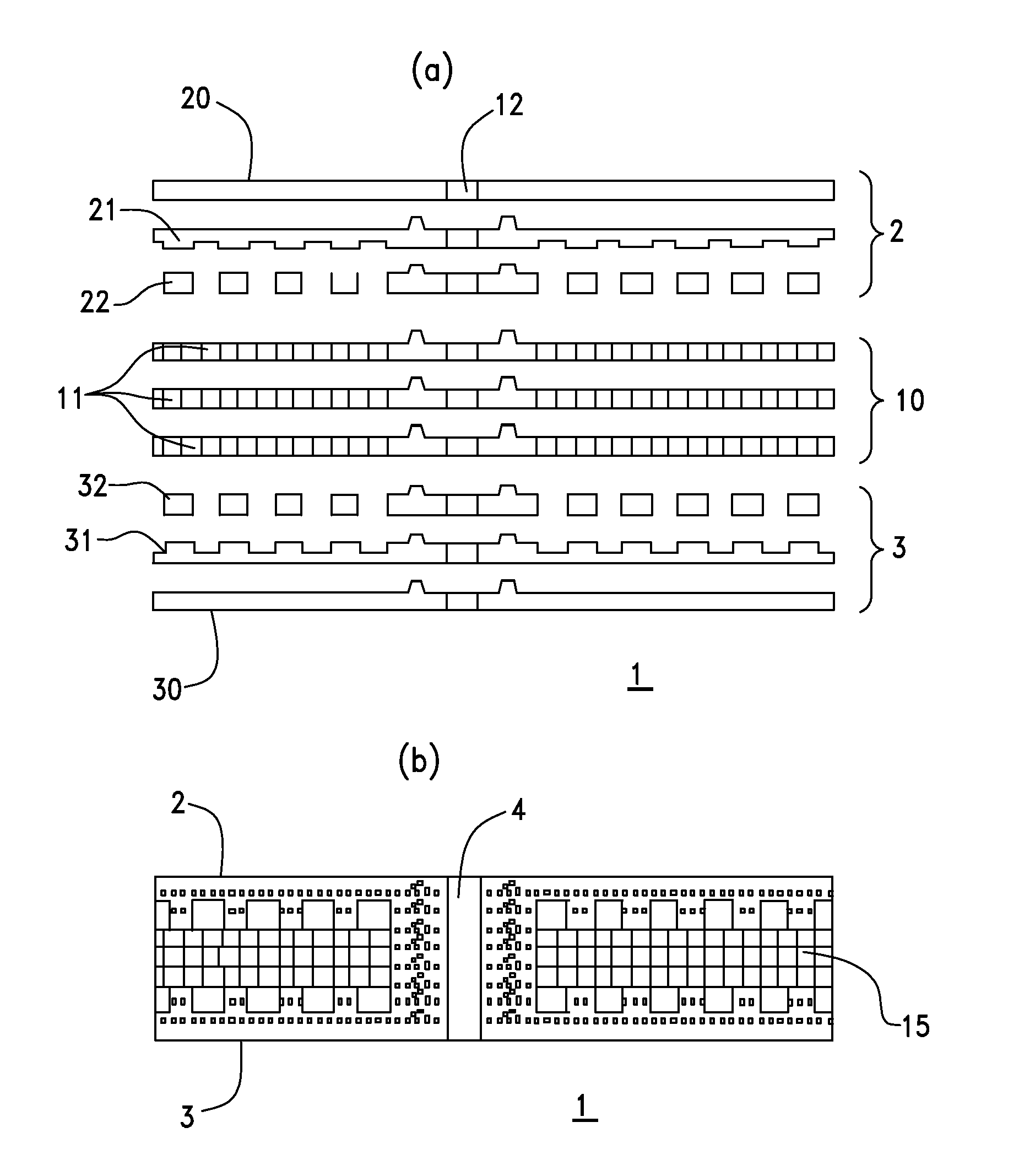

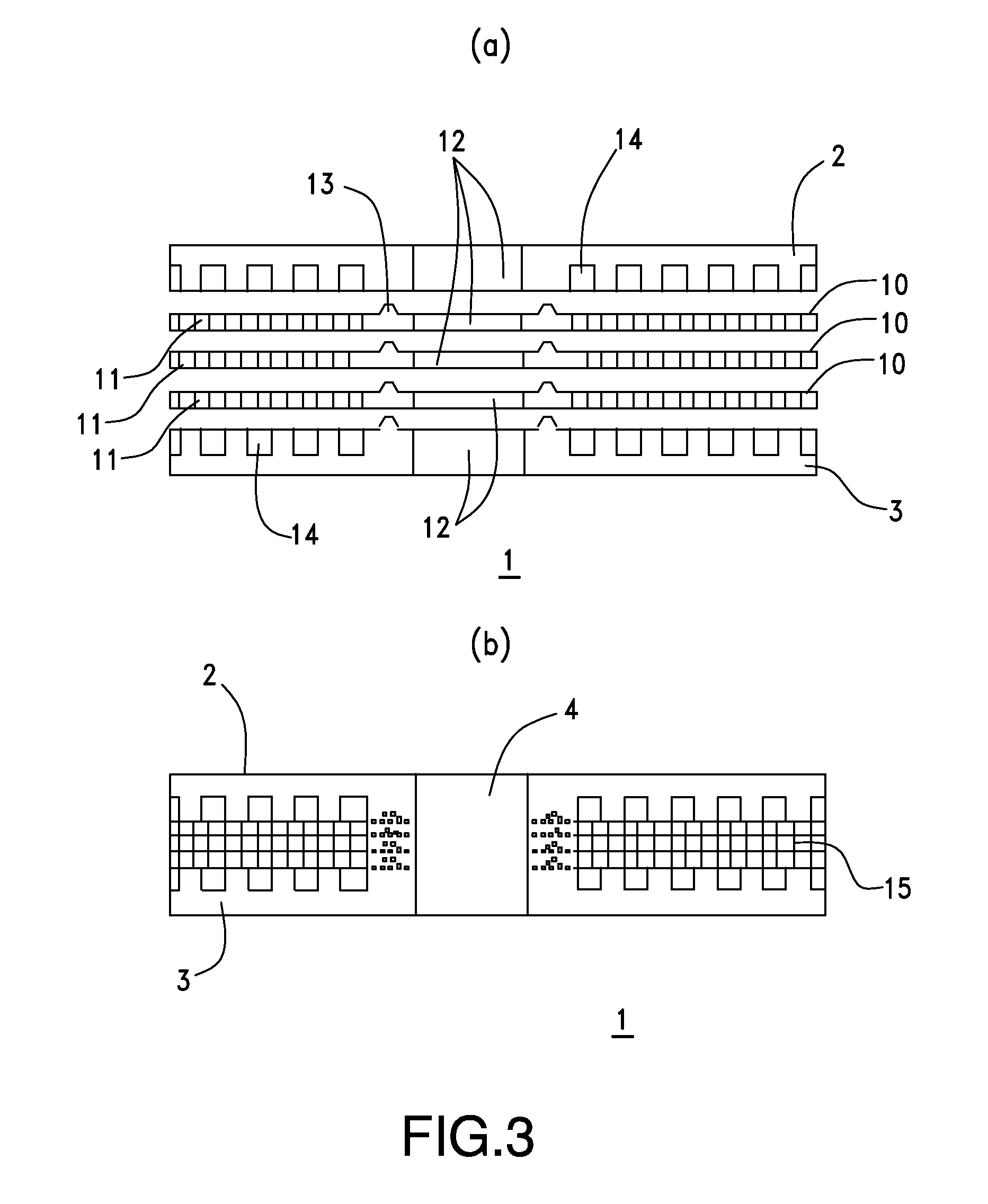

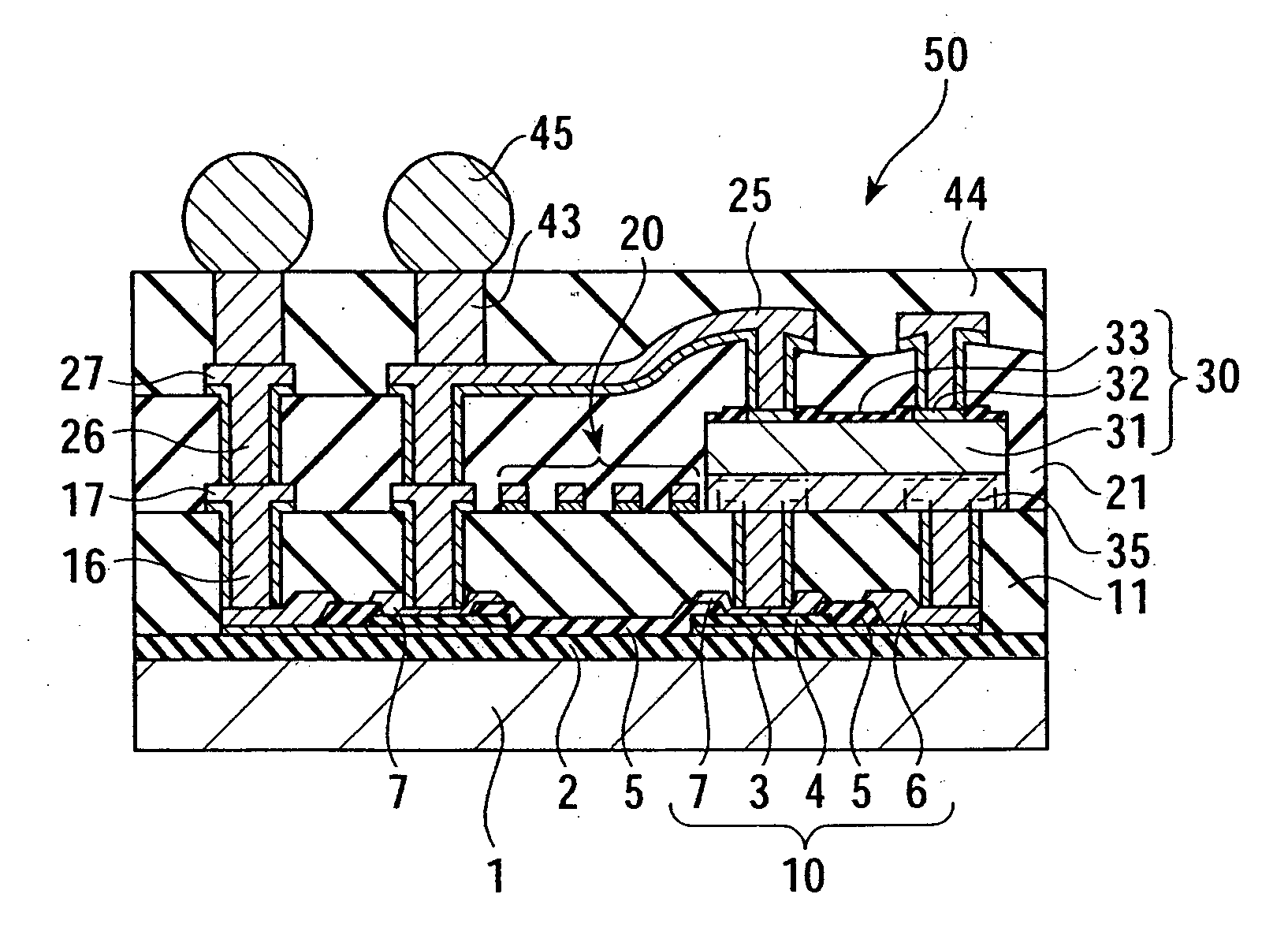

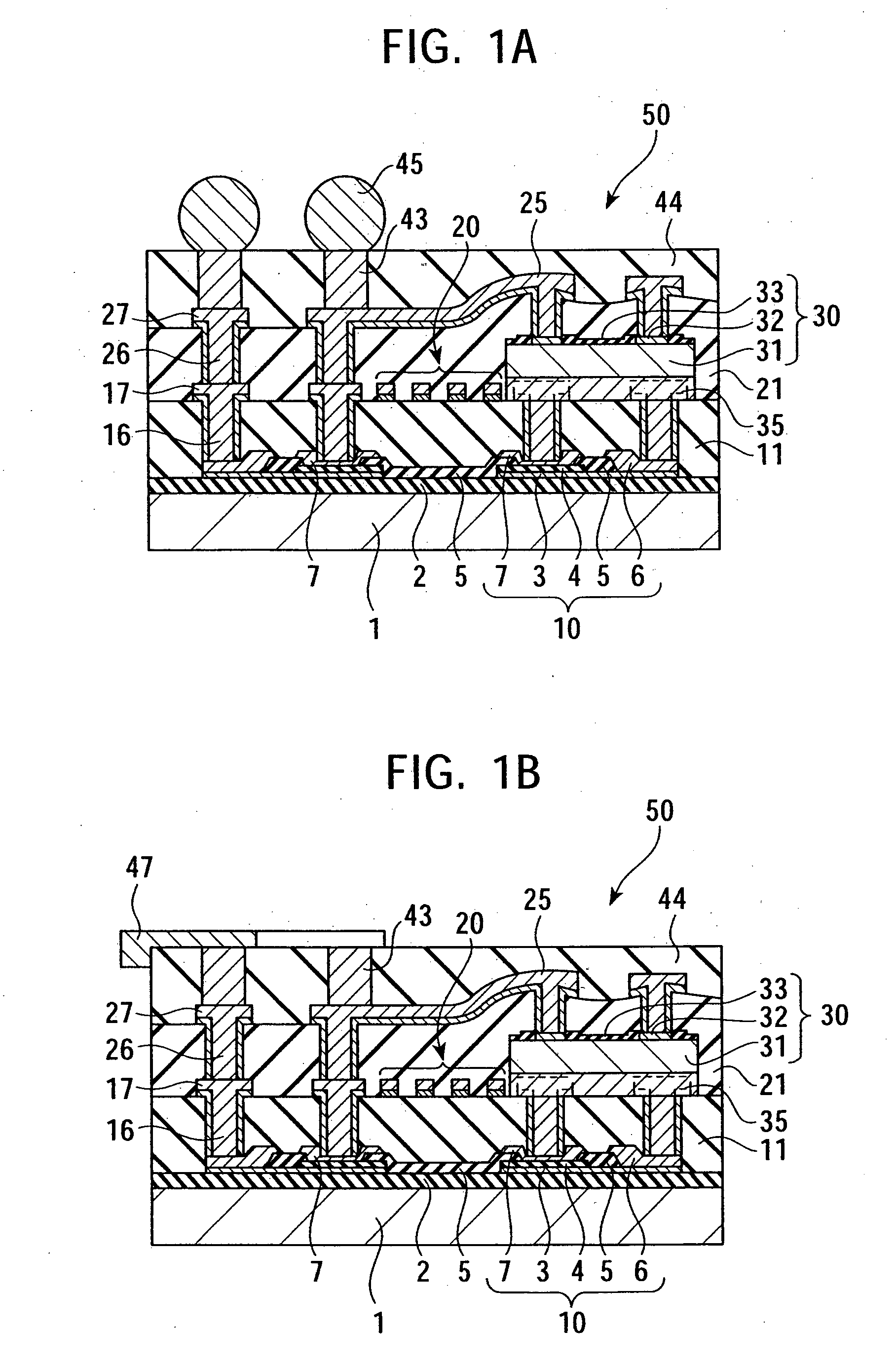

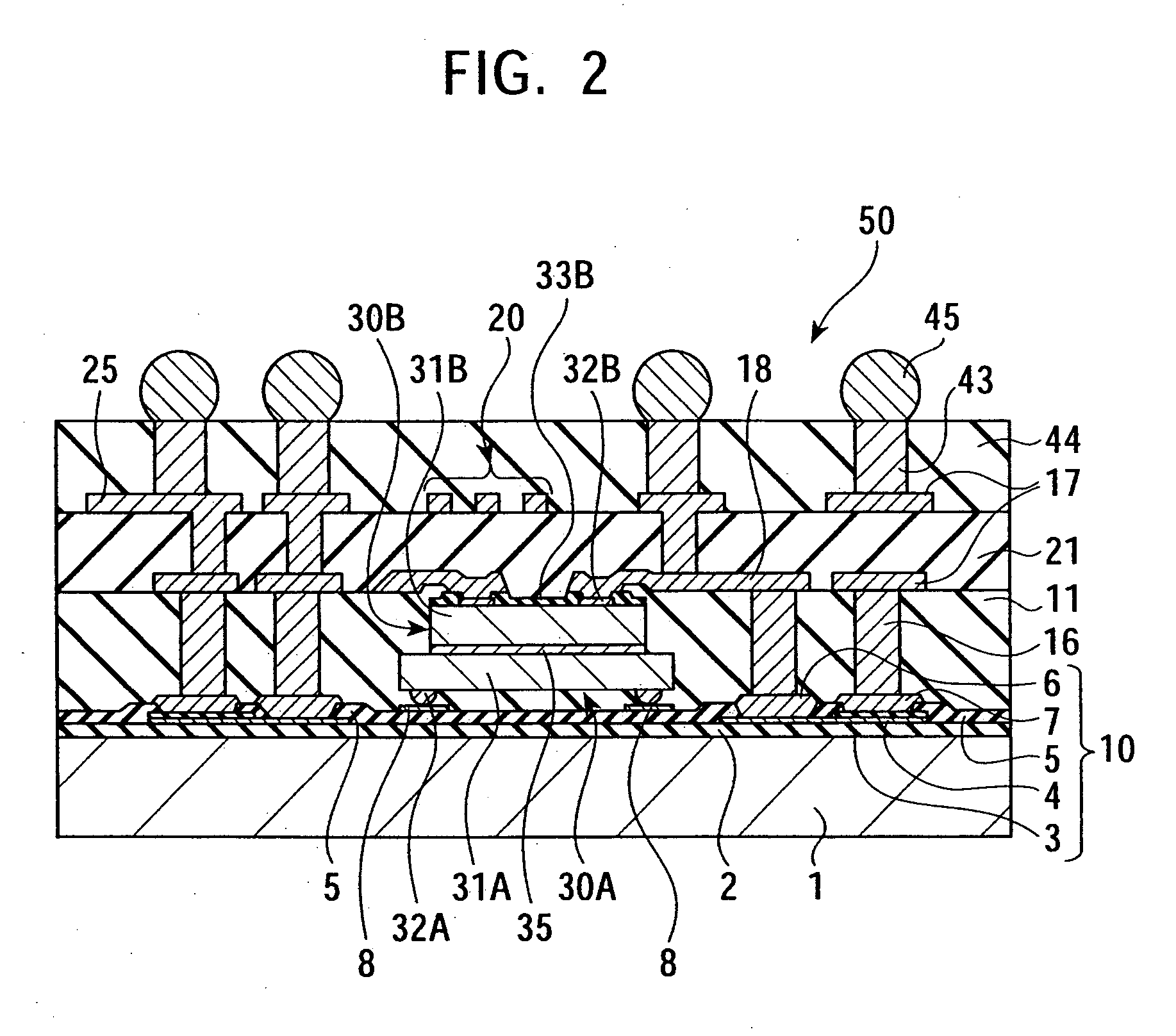

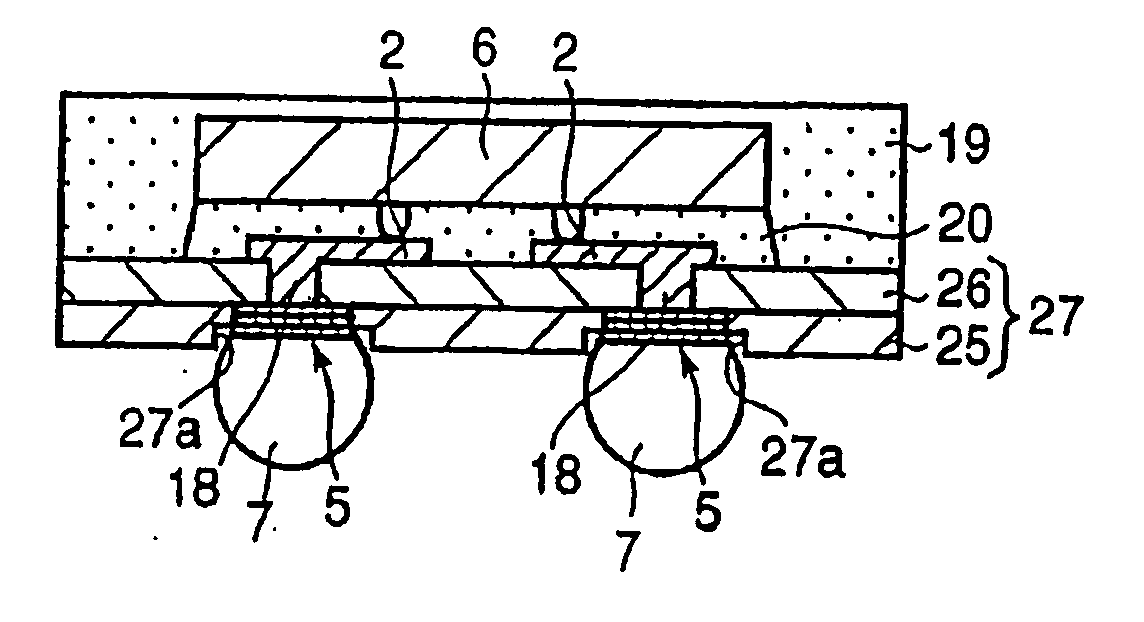

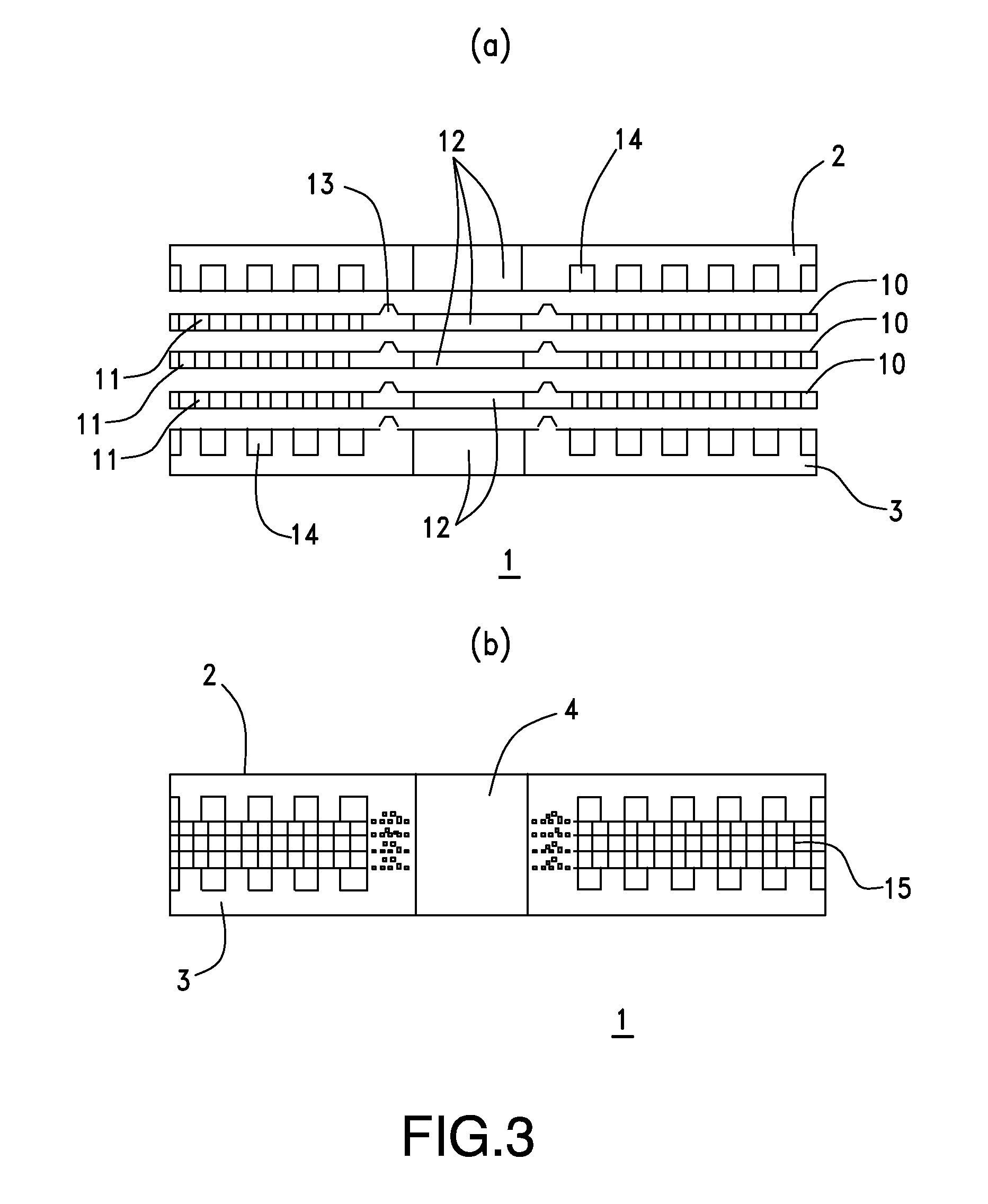

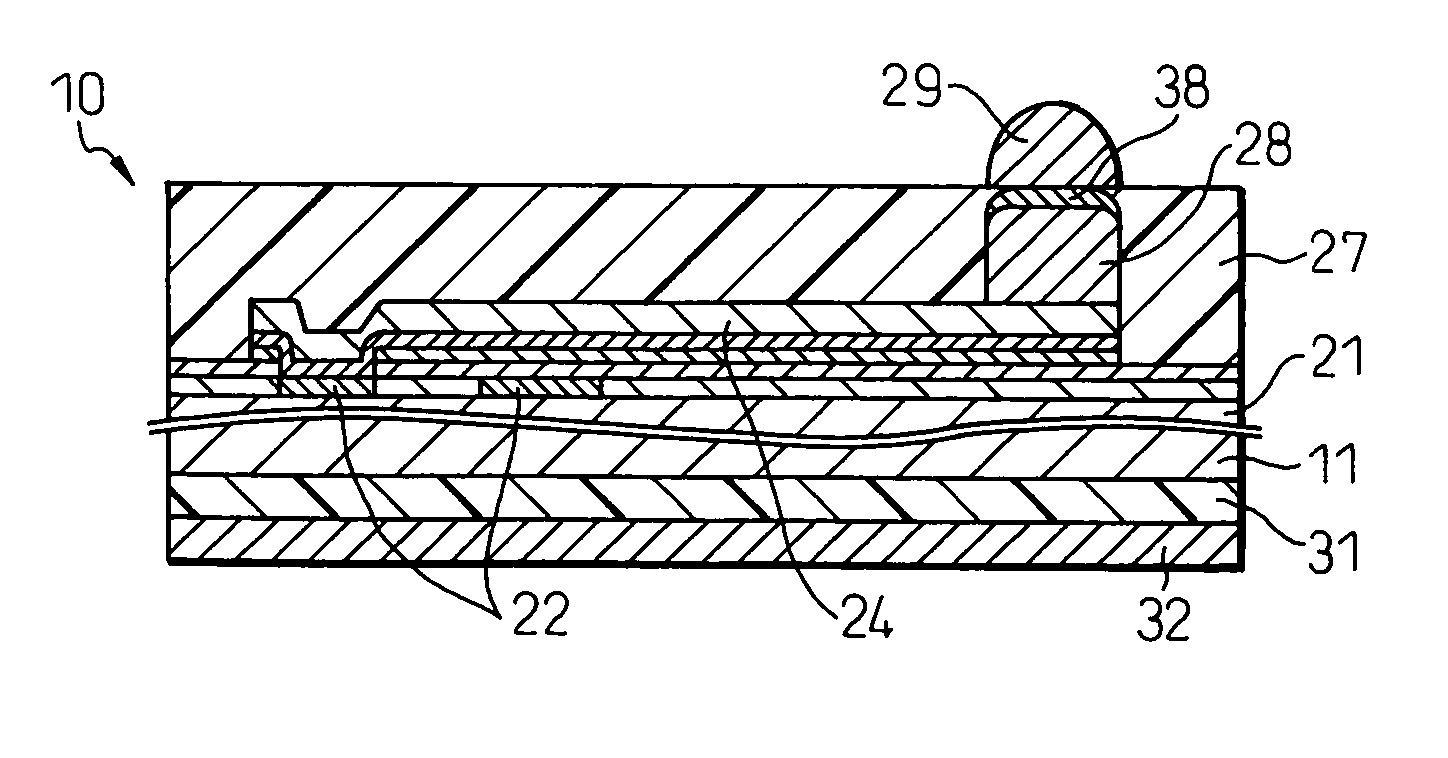

Semiconductor device, package structure thereof, and method for manufacturing the semiconductor device

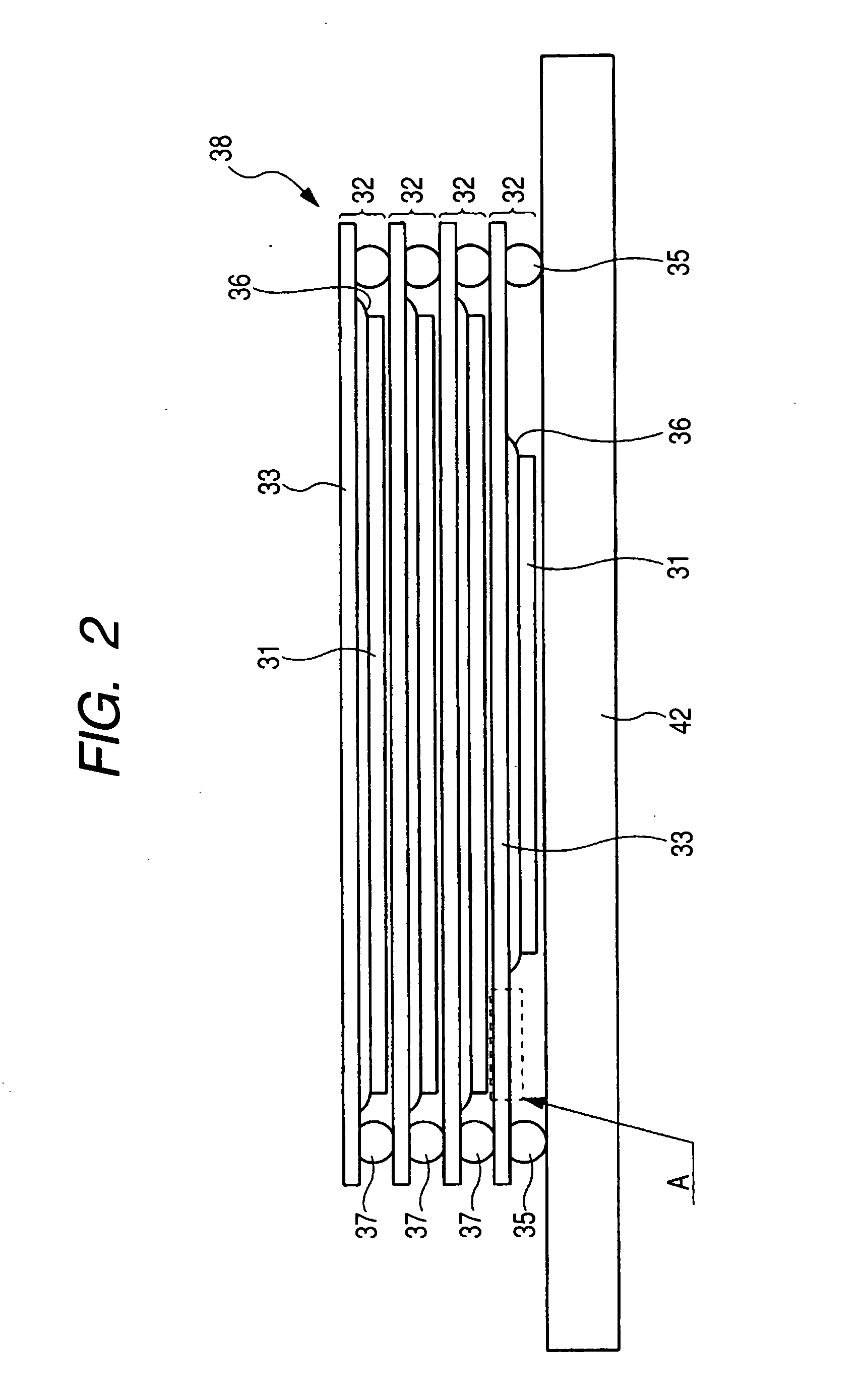

ActiveUS7208832B2High densitySmall thicknessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInductor

A semiconductor device includes a plurality of insulating layers laminated on a substrate to cover passive elements such as a capacitor, an inductor, and the like, and to fix an IC chip in a face up state in one of the insulating layers. The insulating layers have similar structures in each of which the passive element or the semiconductor chip is disposed in at the bottom, a plug is formed in the insulating layer to pass therethrough in the thickness direction for extending an electrode of one of these elements to the top surface, and a conductive layer is provided as wiring on the top surface of the insulating layer to be connected to the plugs for electrically connecting respective elements or rearranging the electrode position. Also, an insulating layer is provided on the top for protecting the semiconductor device and for providing an external connecting electrode.

Owner:SONY CORP

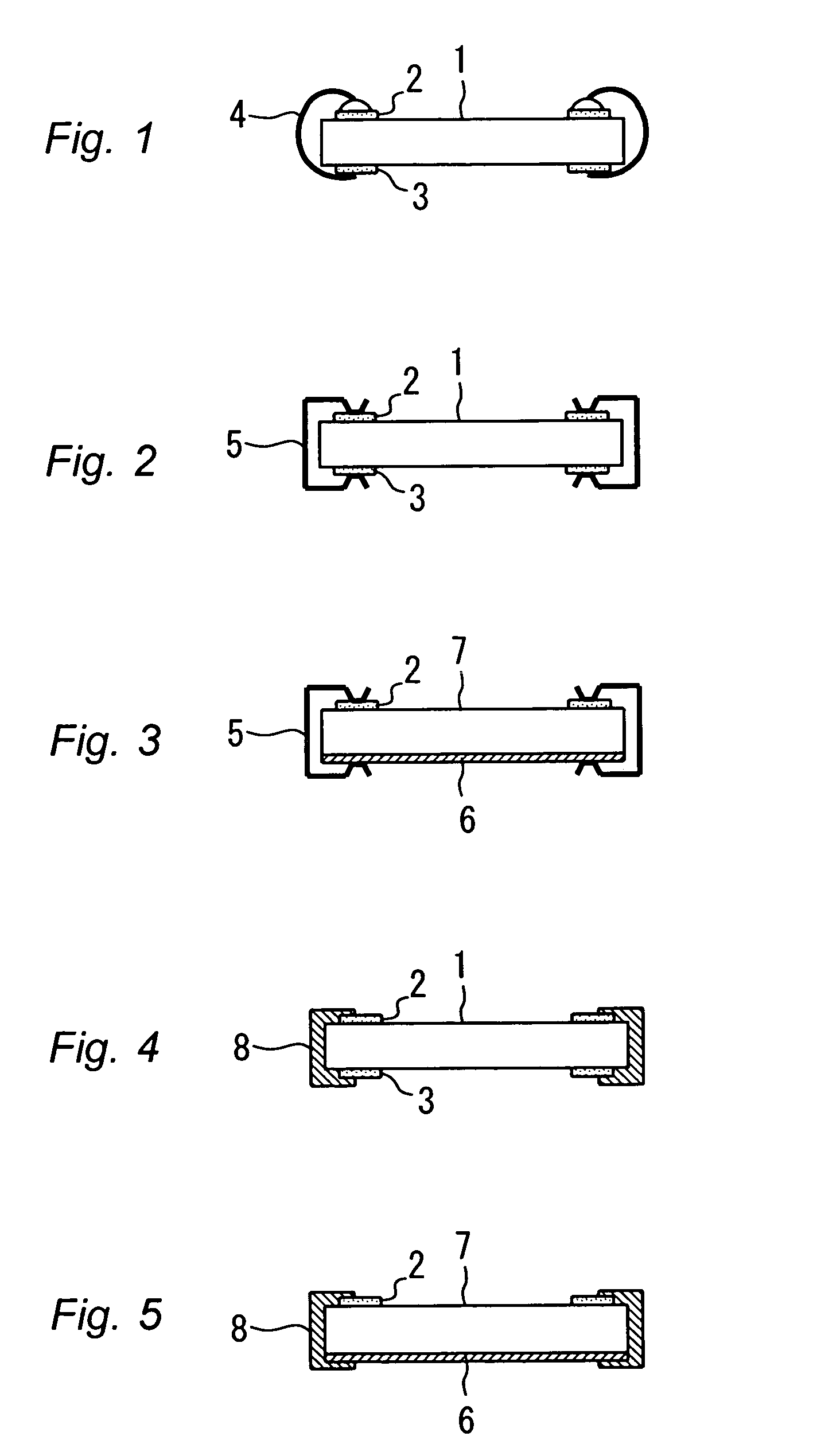

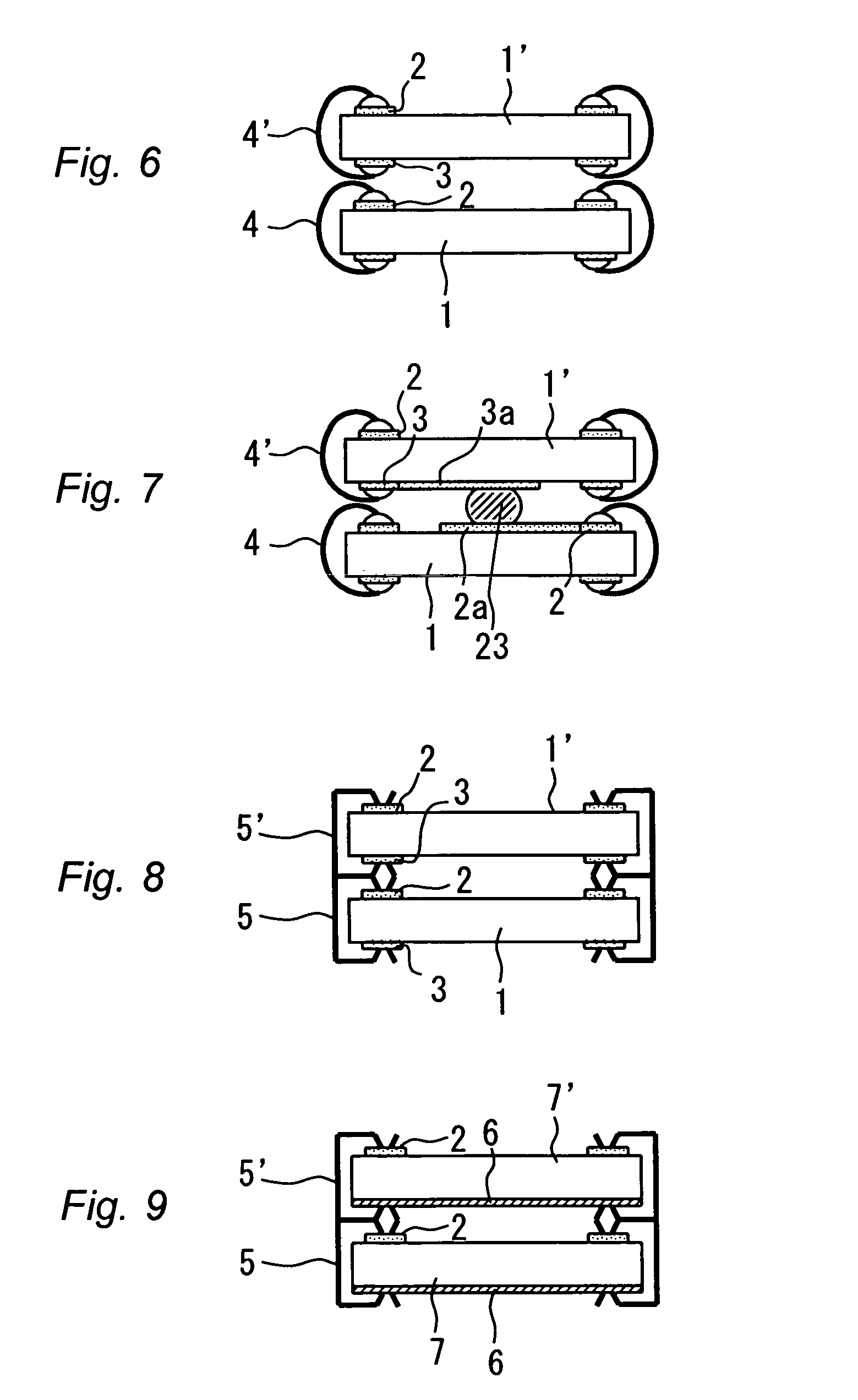

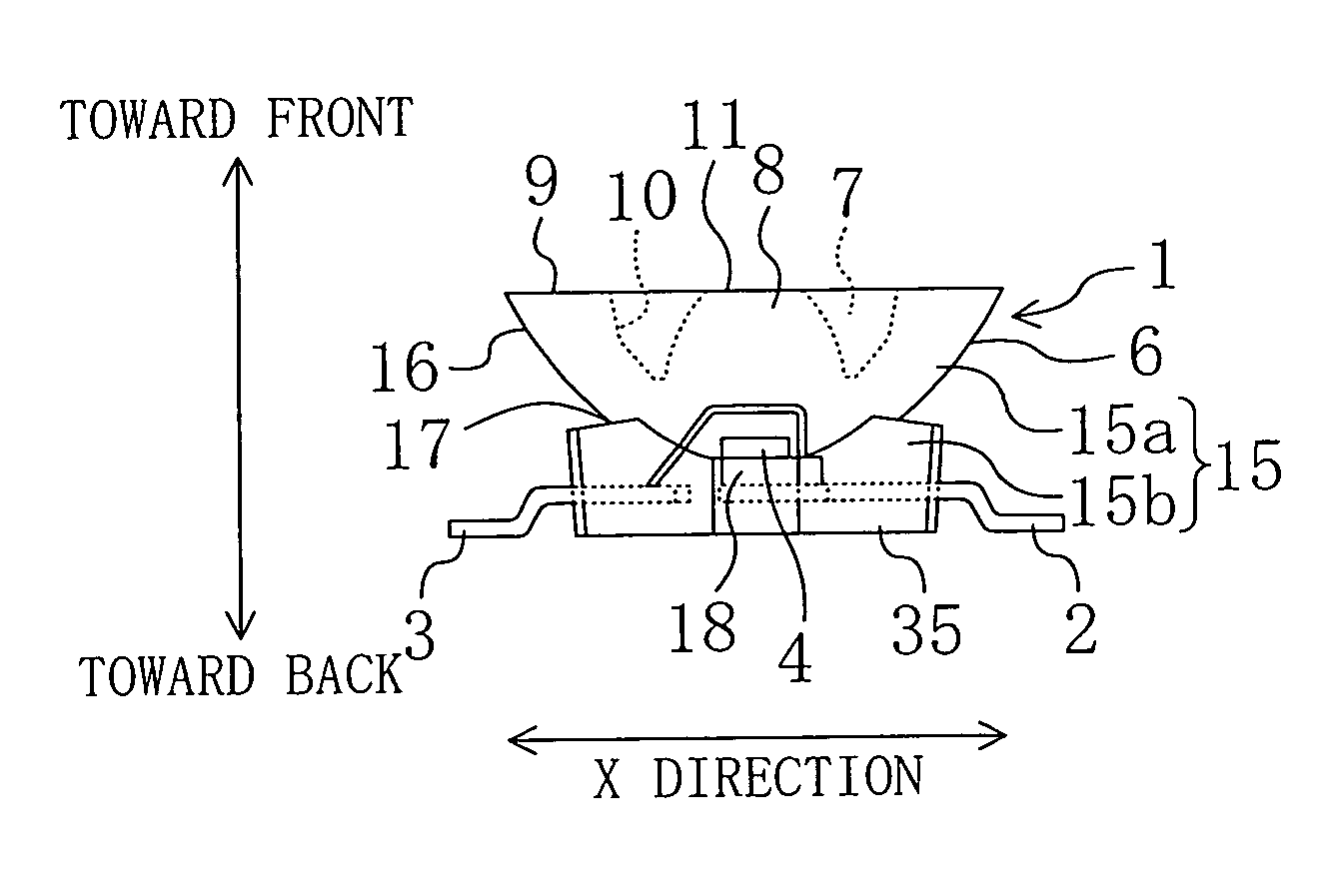

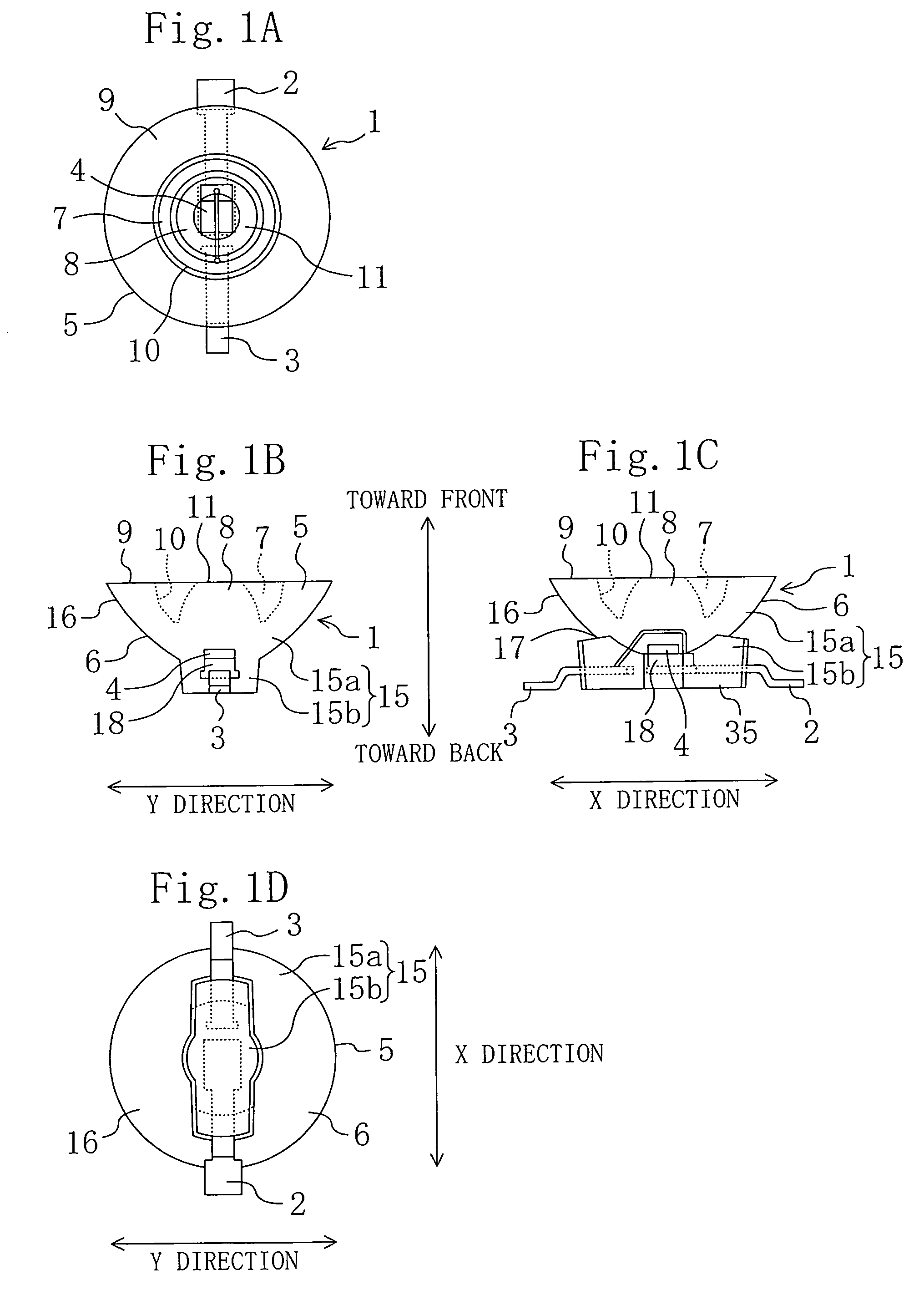

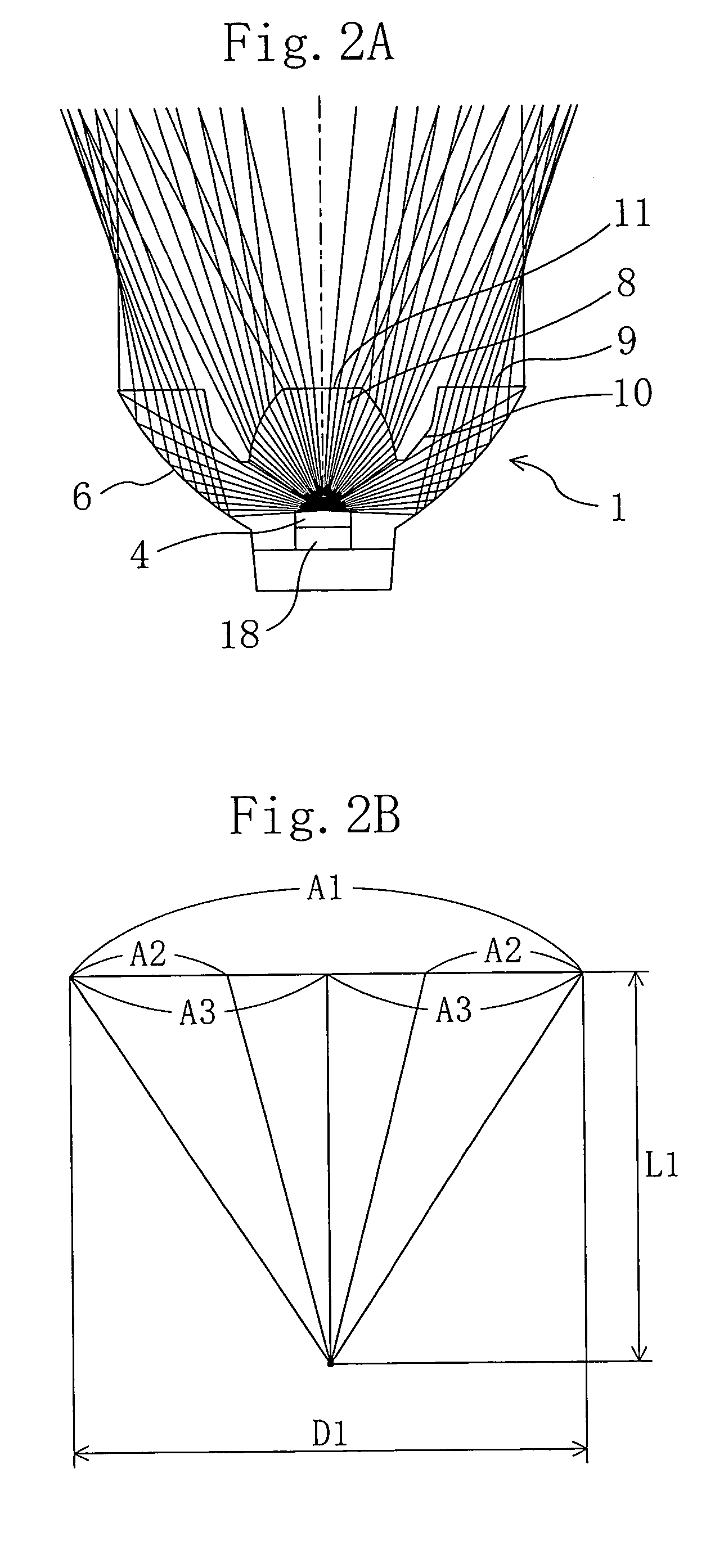

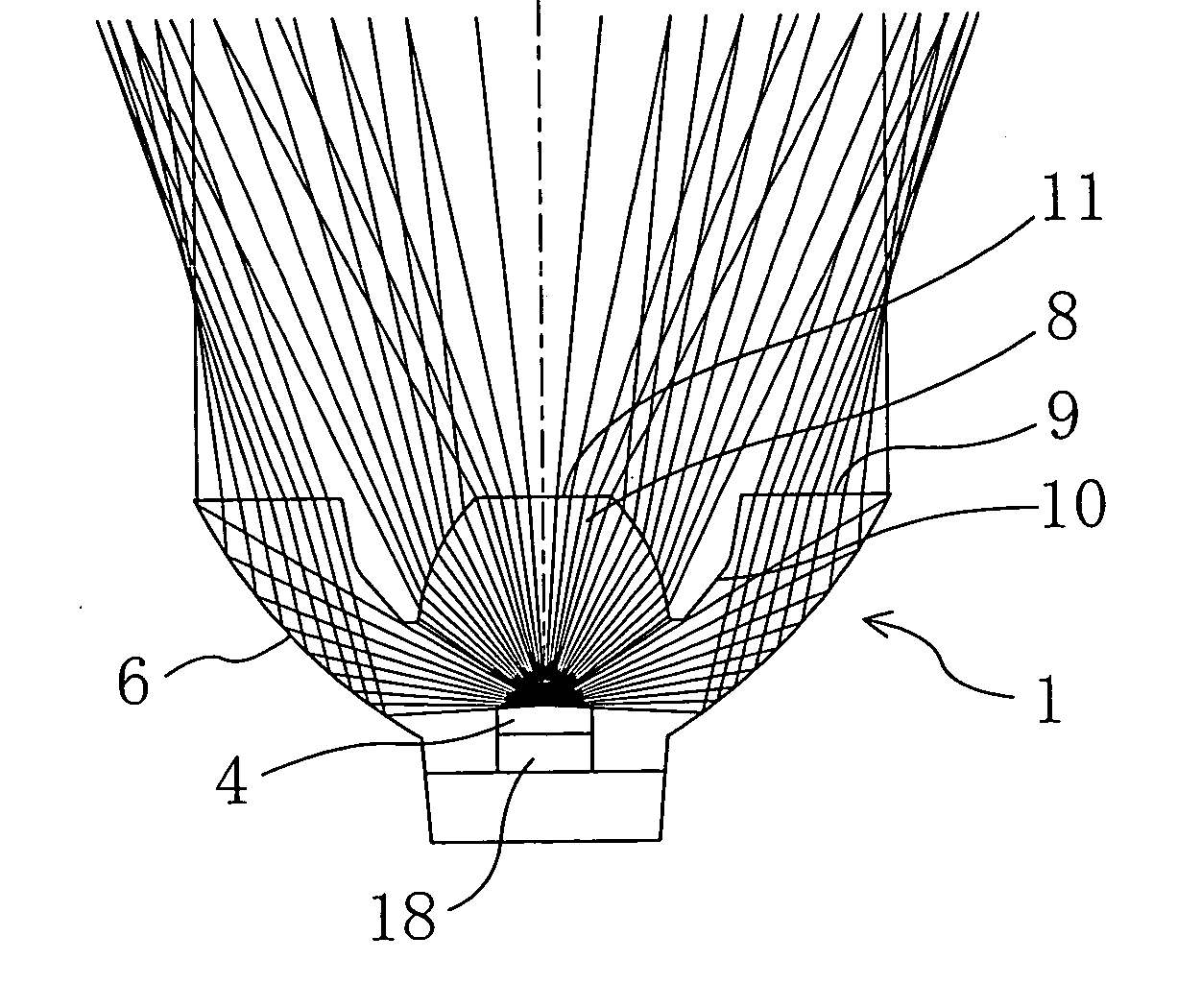

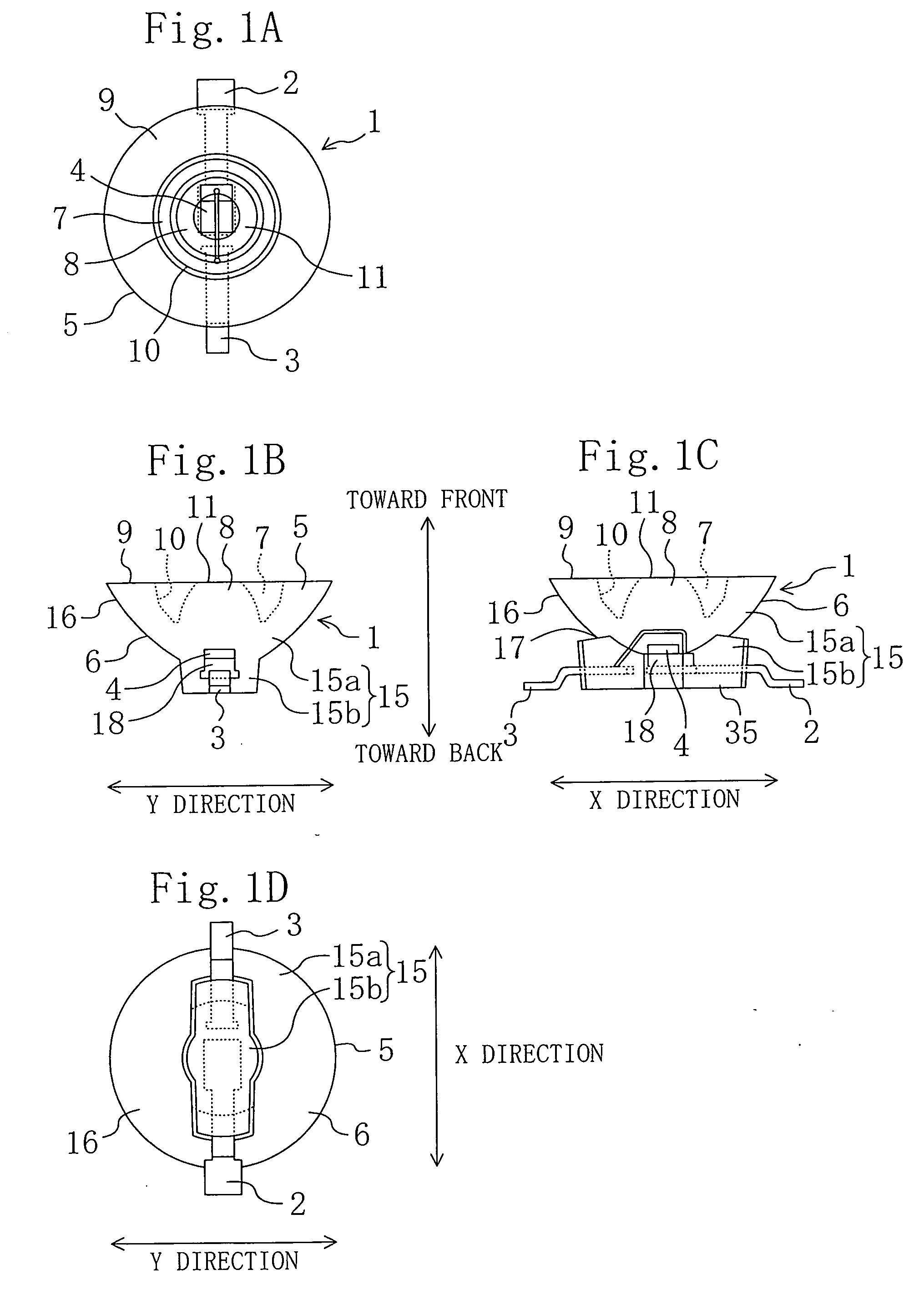

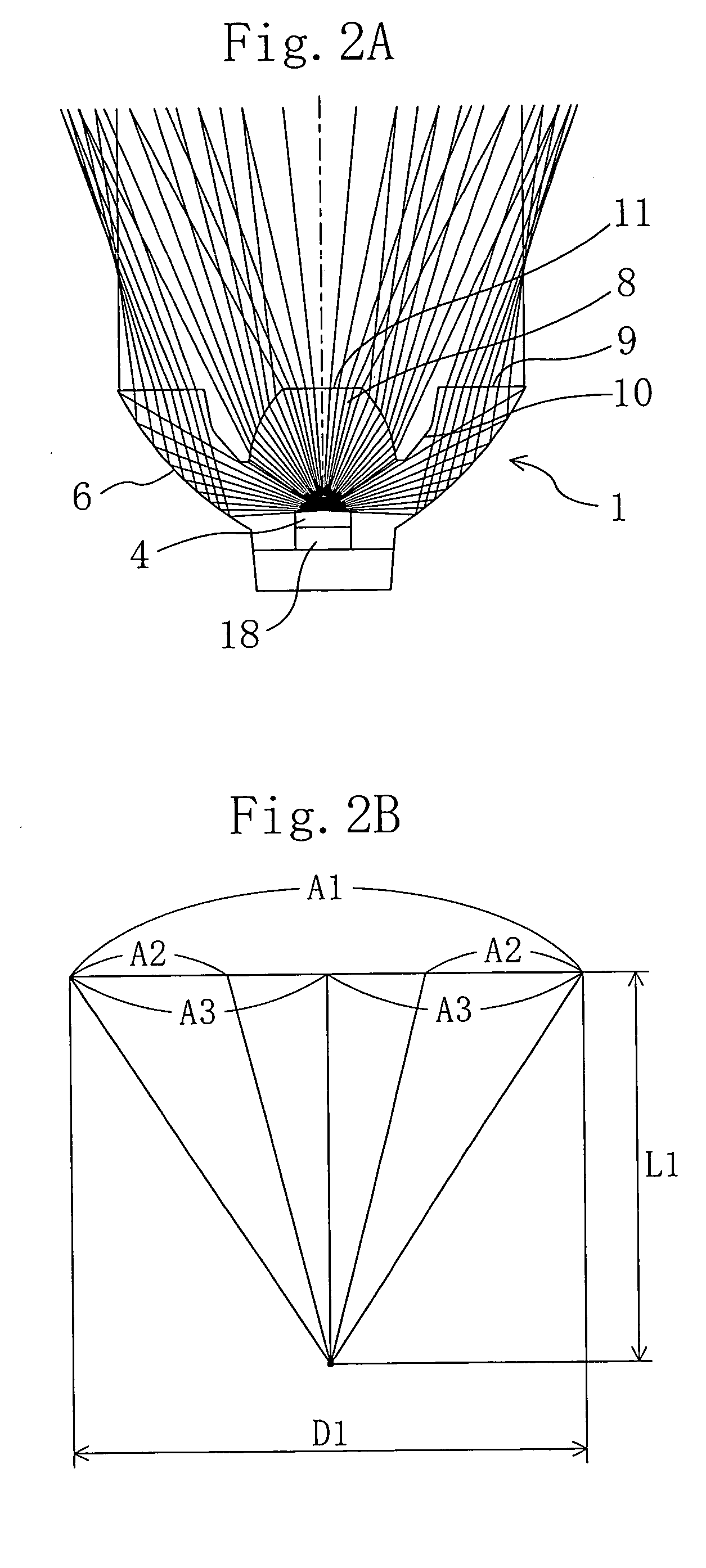

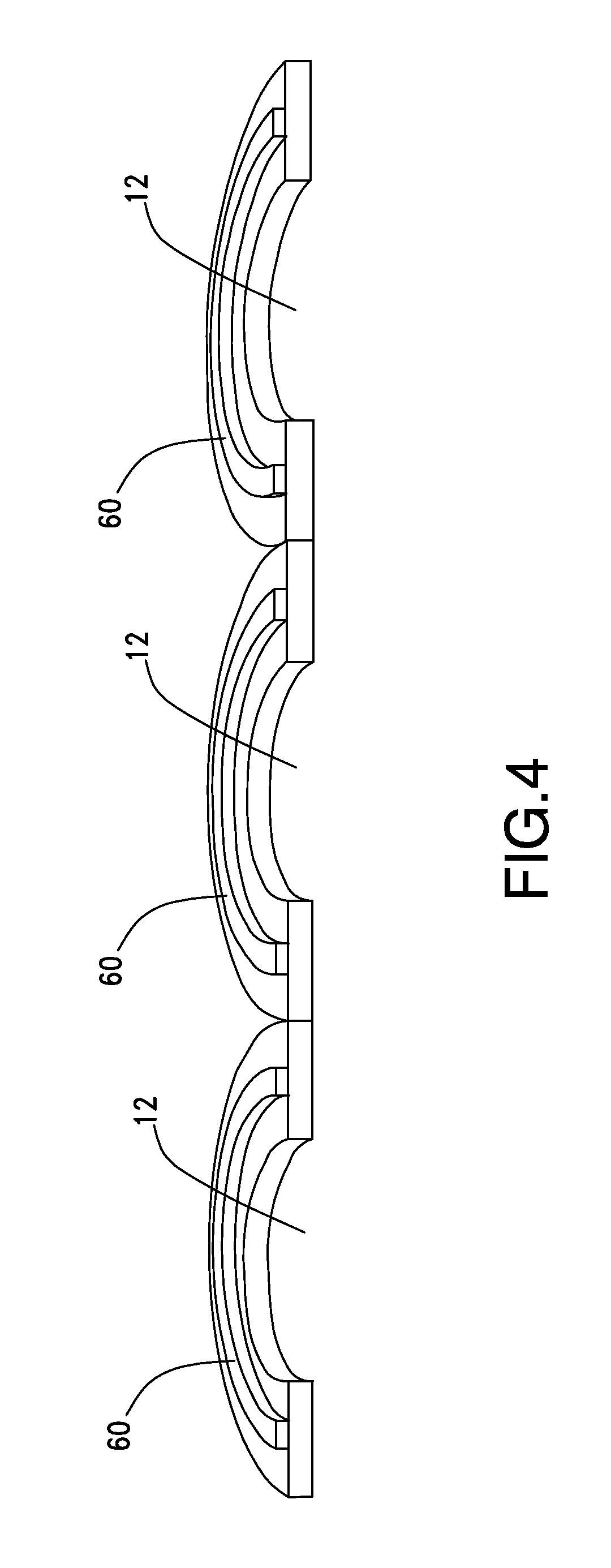

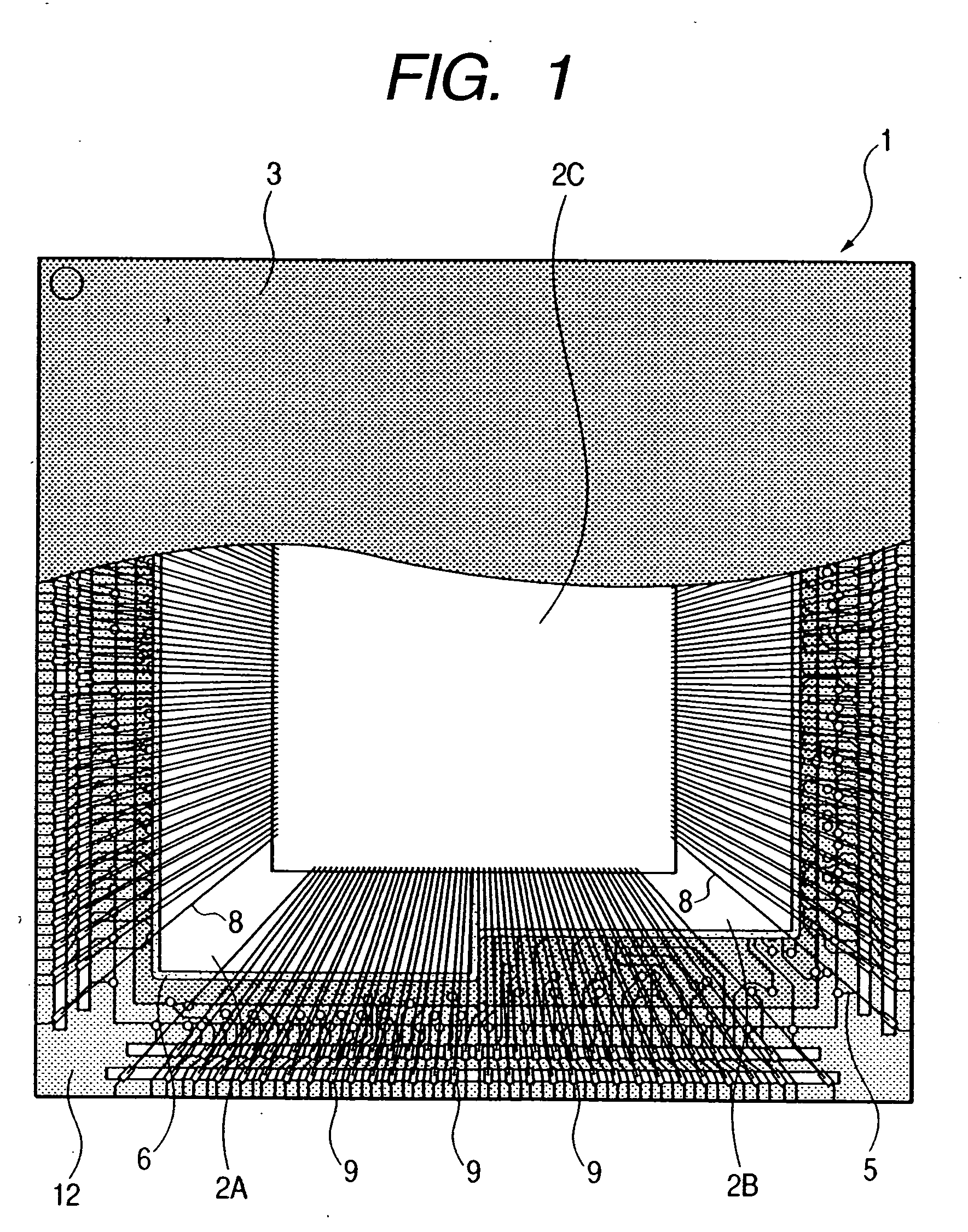

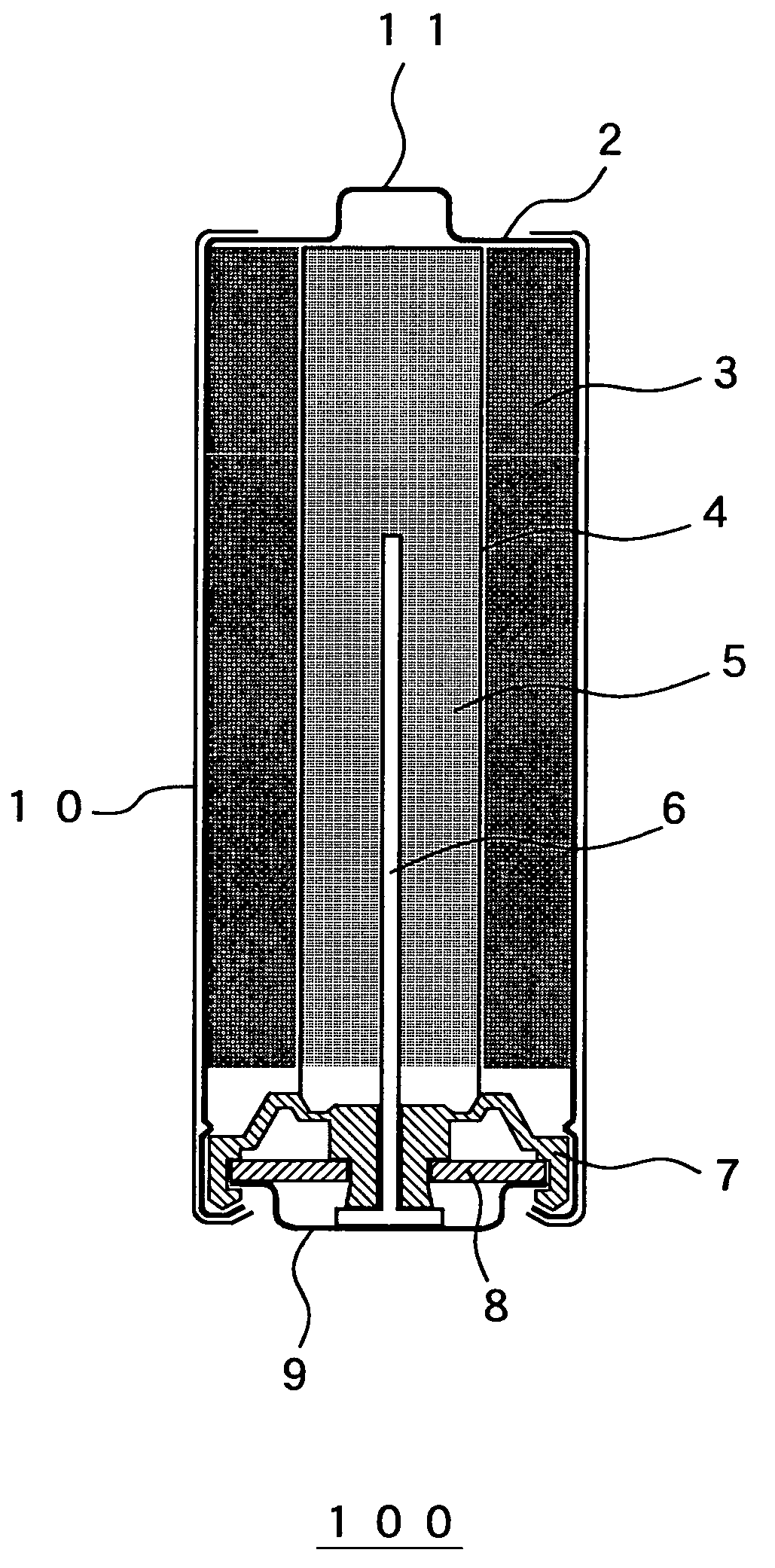

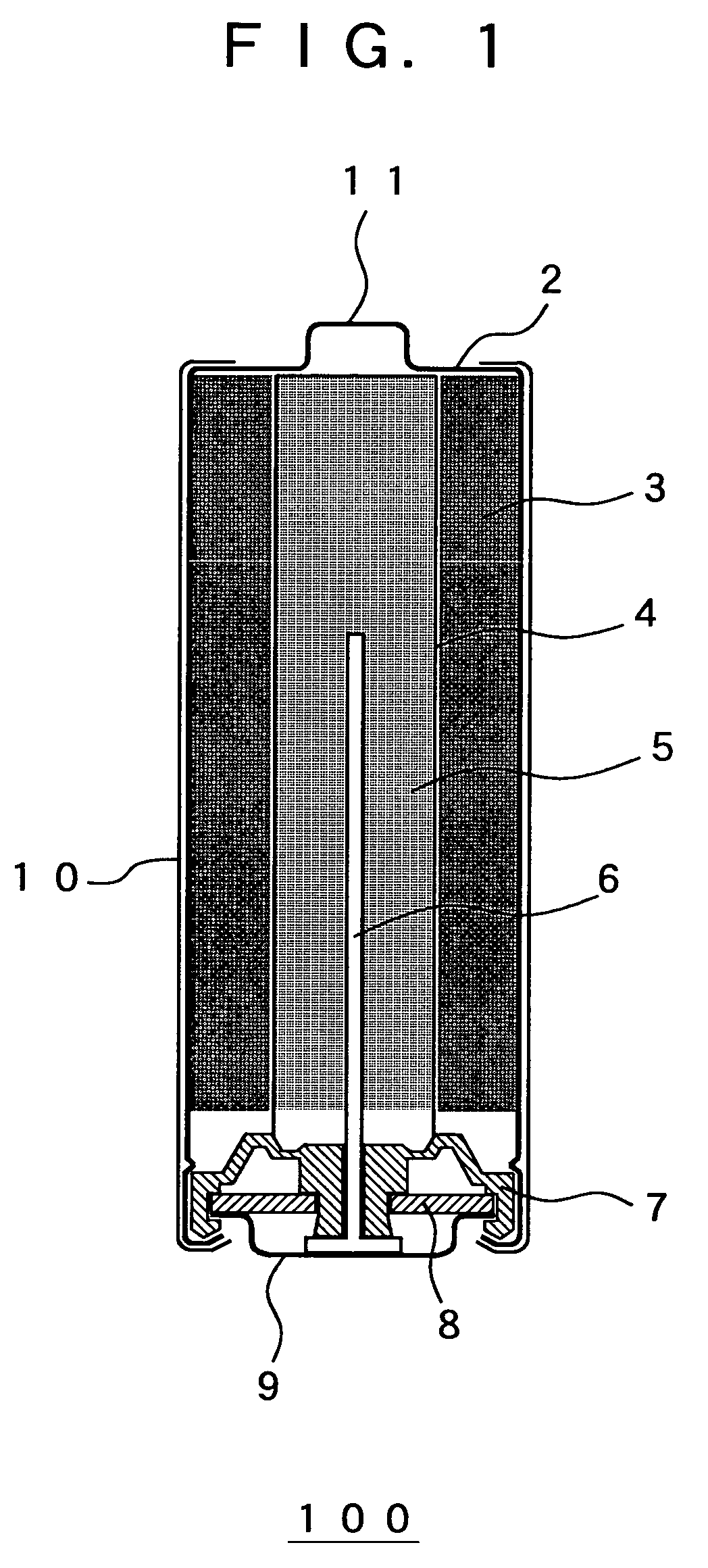

Light-emitting diode

InactiveUS7347603B2High-density packagingLaunch evenlyDischarge tube luminescnet screensLamp detailsOptical axisEngineering

A light-emitting diode 1 according to the present invention includes: a semiconductor light-emitting device 4 mounted on the surface of lead frames 2 and 3; and a transparent resin package 5 covering the front side of the semiconductor light-emitting device 4. A convex lens portion 8 for concentrating light emitted from the semiconductor light-emitting device 4 toward the front is provided in a surface part of the resin package 5. A circular flat portion 11 for diffusing light emitted from the semiconductor light-emitting device 4 toward the sides is provided in a part of the convex lens portion 8 intersecting the optical axis of the convex lens portion 8. Part of the convex lens portion 8 surrounding the circular flat portion 11 is a convex-lens side face. A recess 7 whose side wall is partly the convex-lens side face is provided to surround the convex lens portion.

Owner:PANASONIC CORP

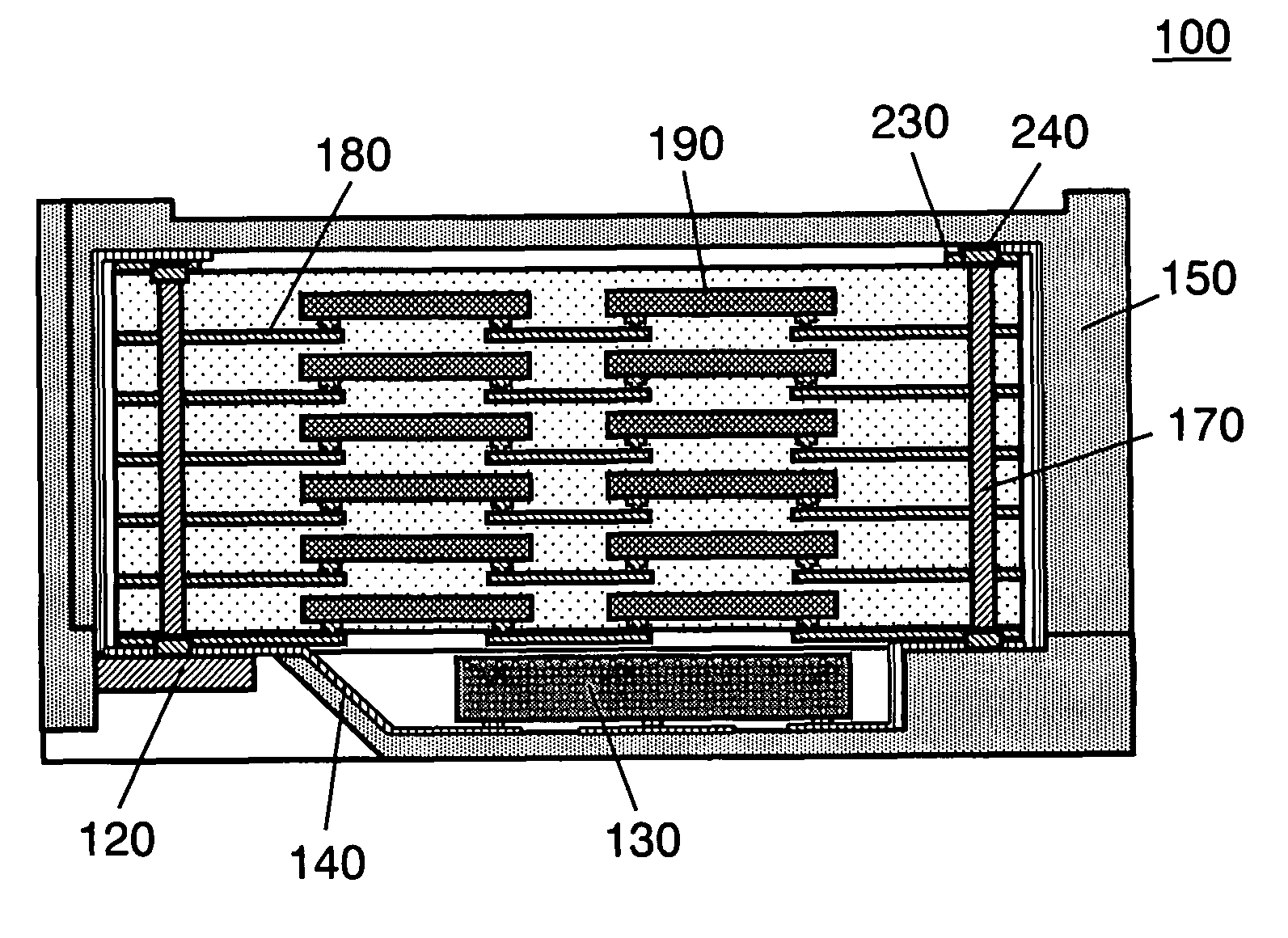

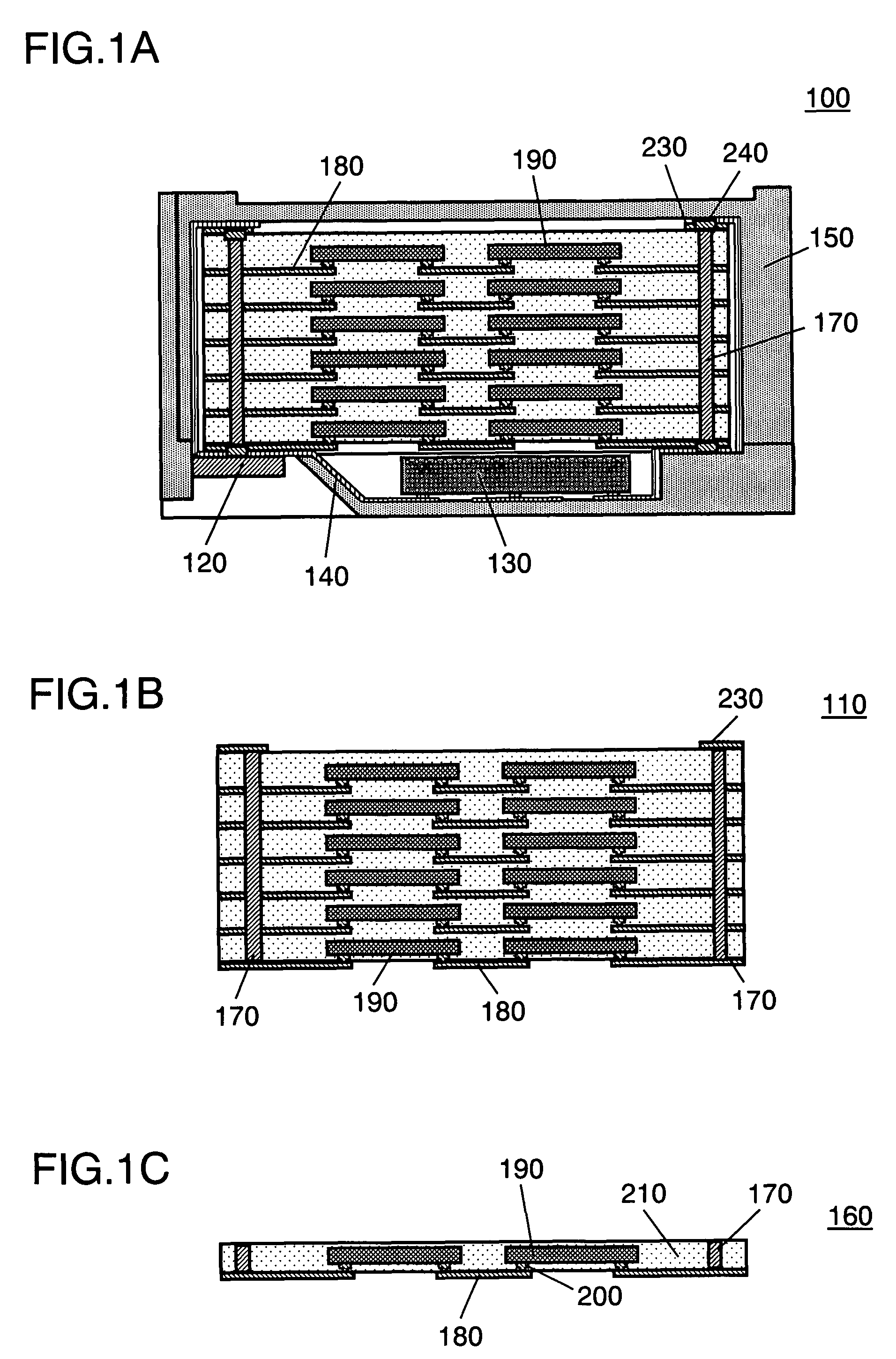

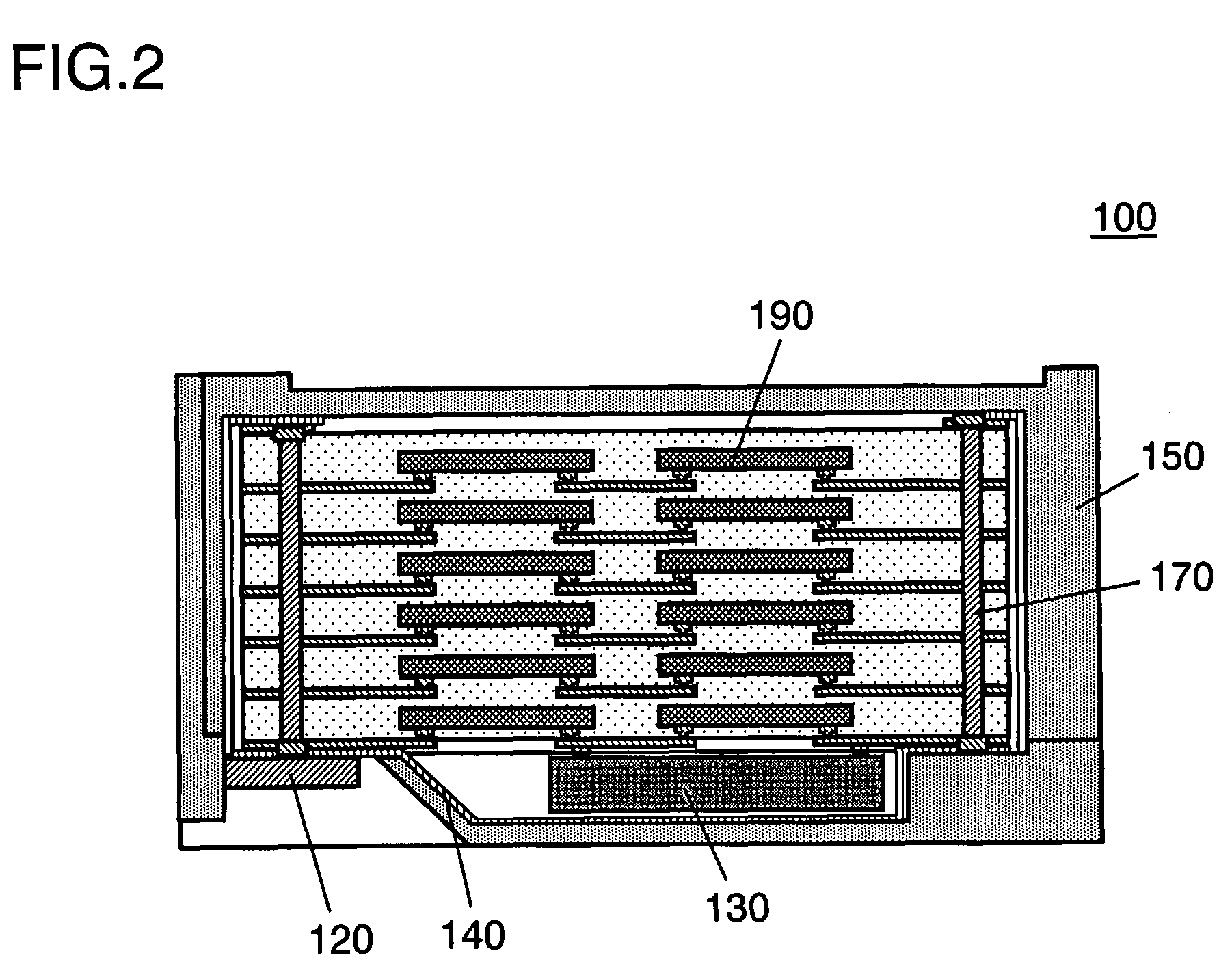

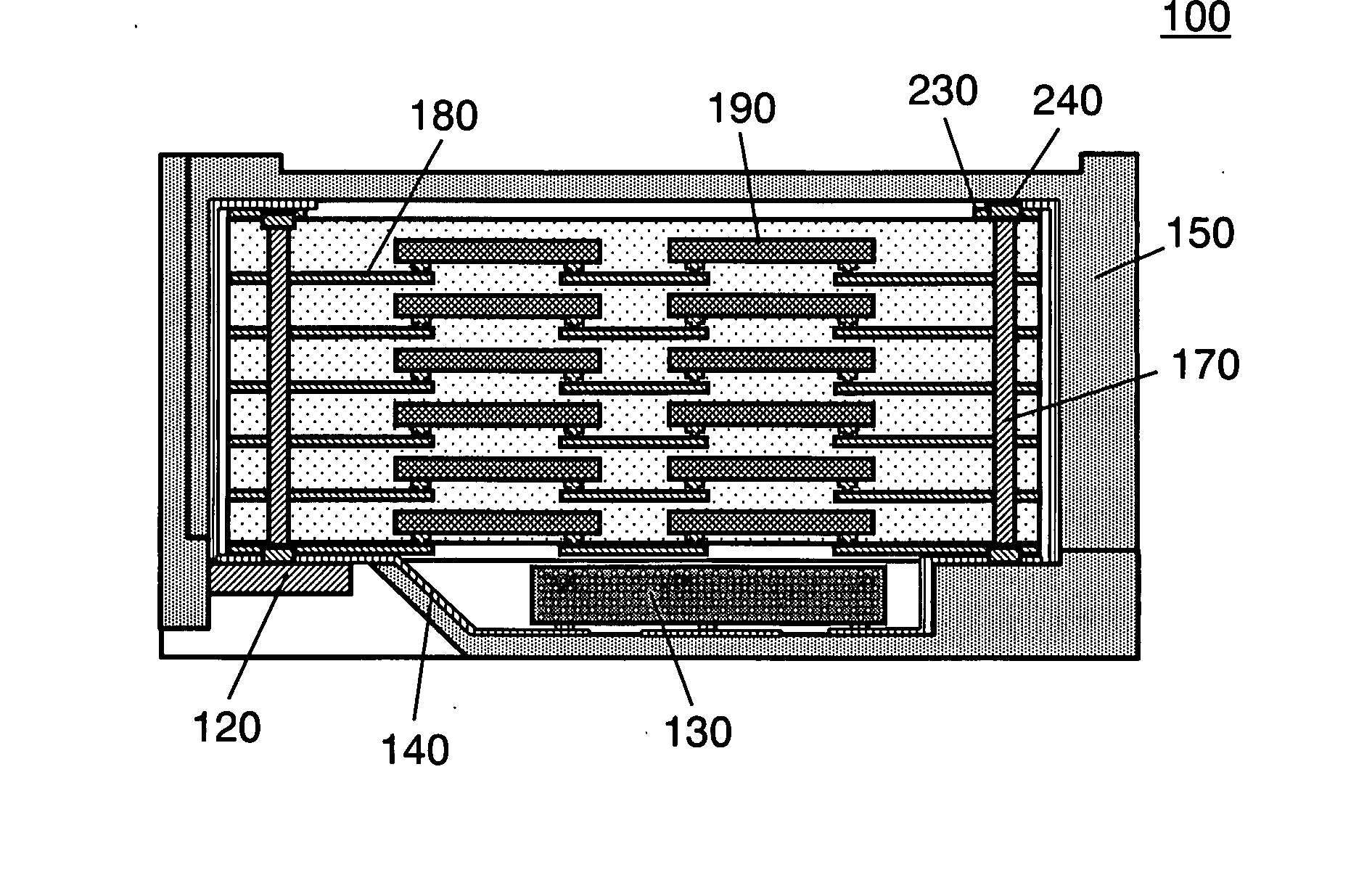

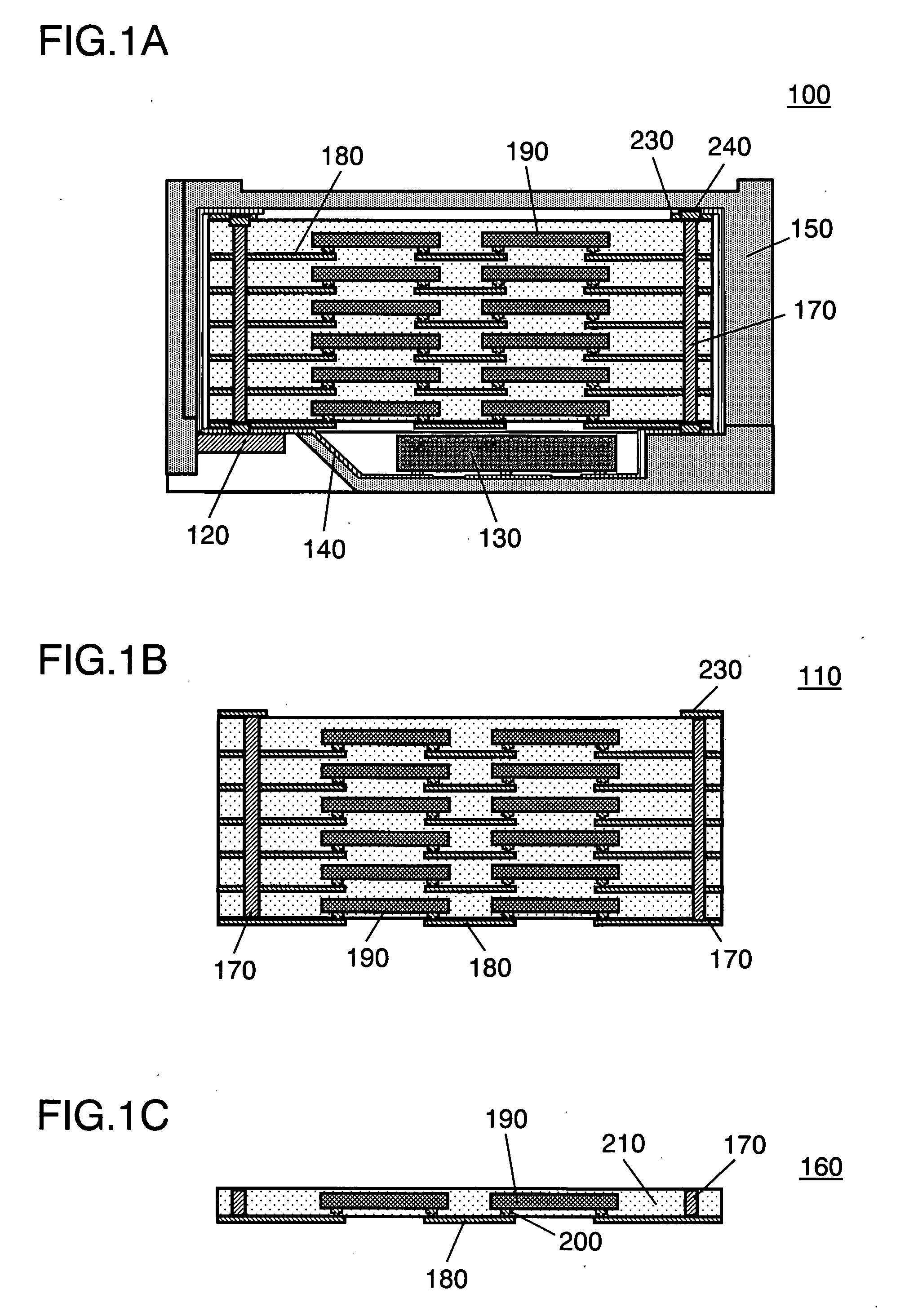

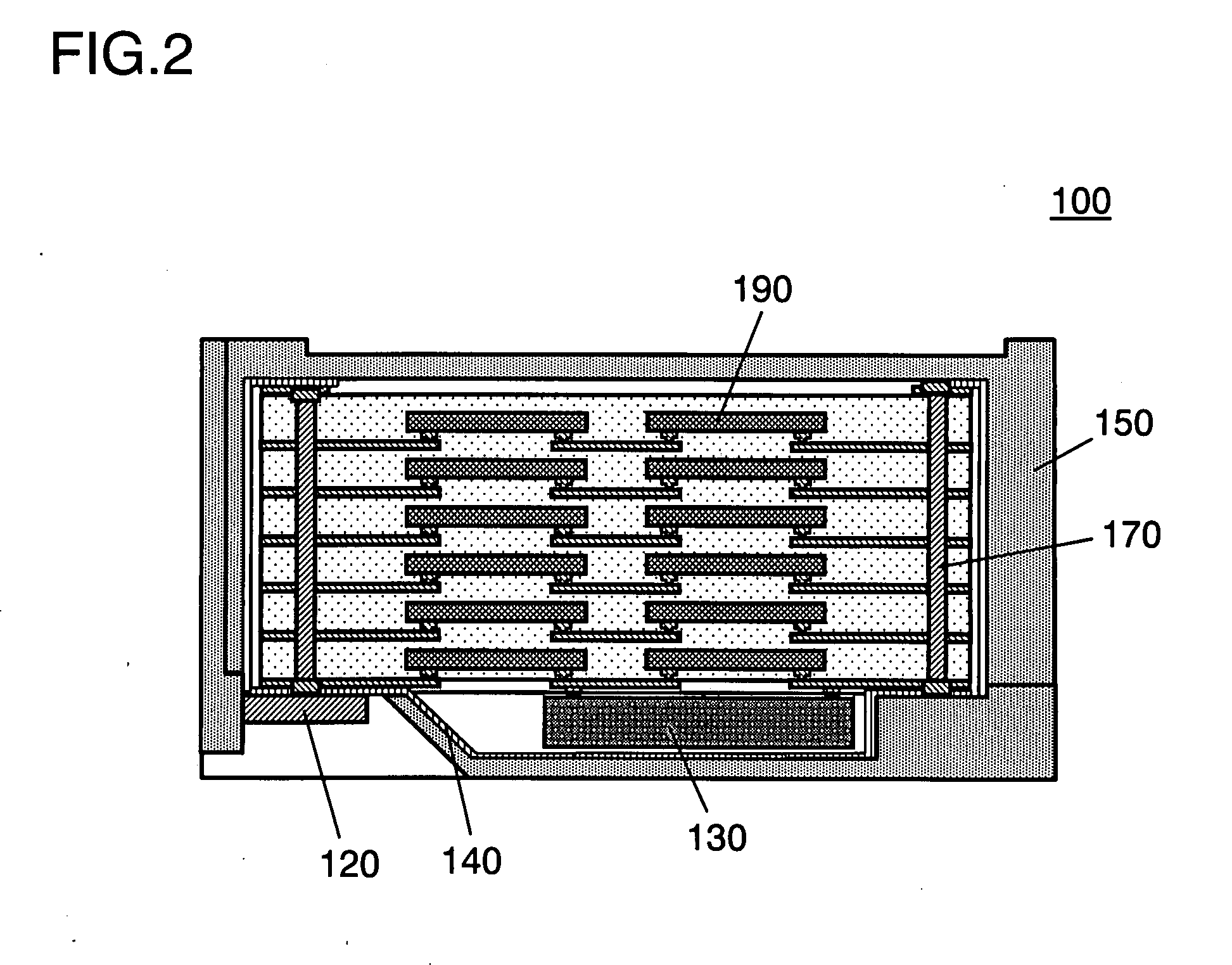

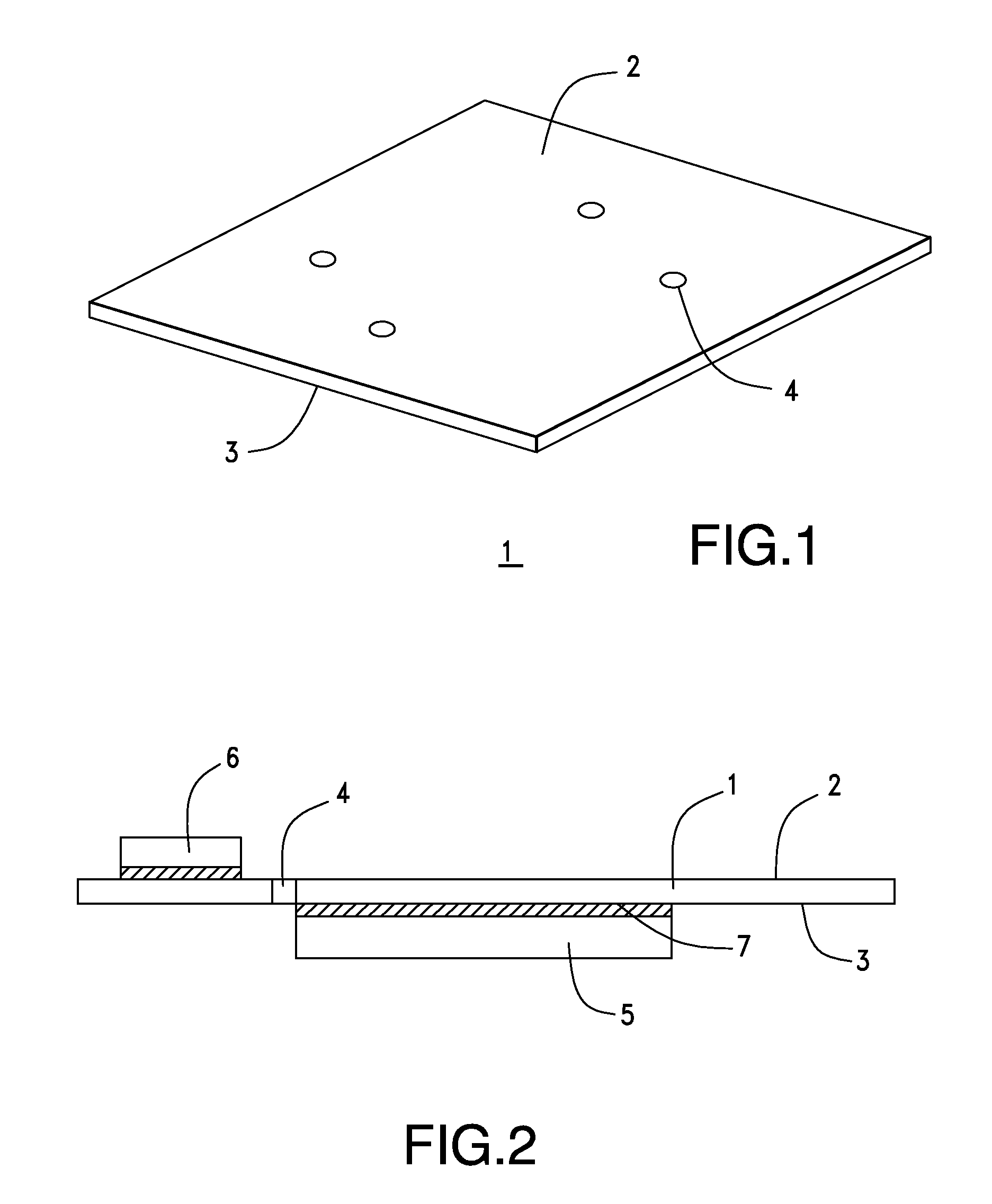

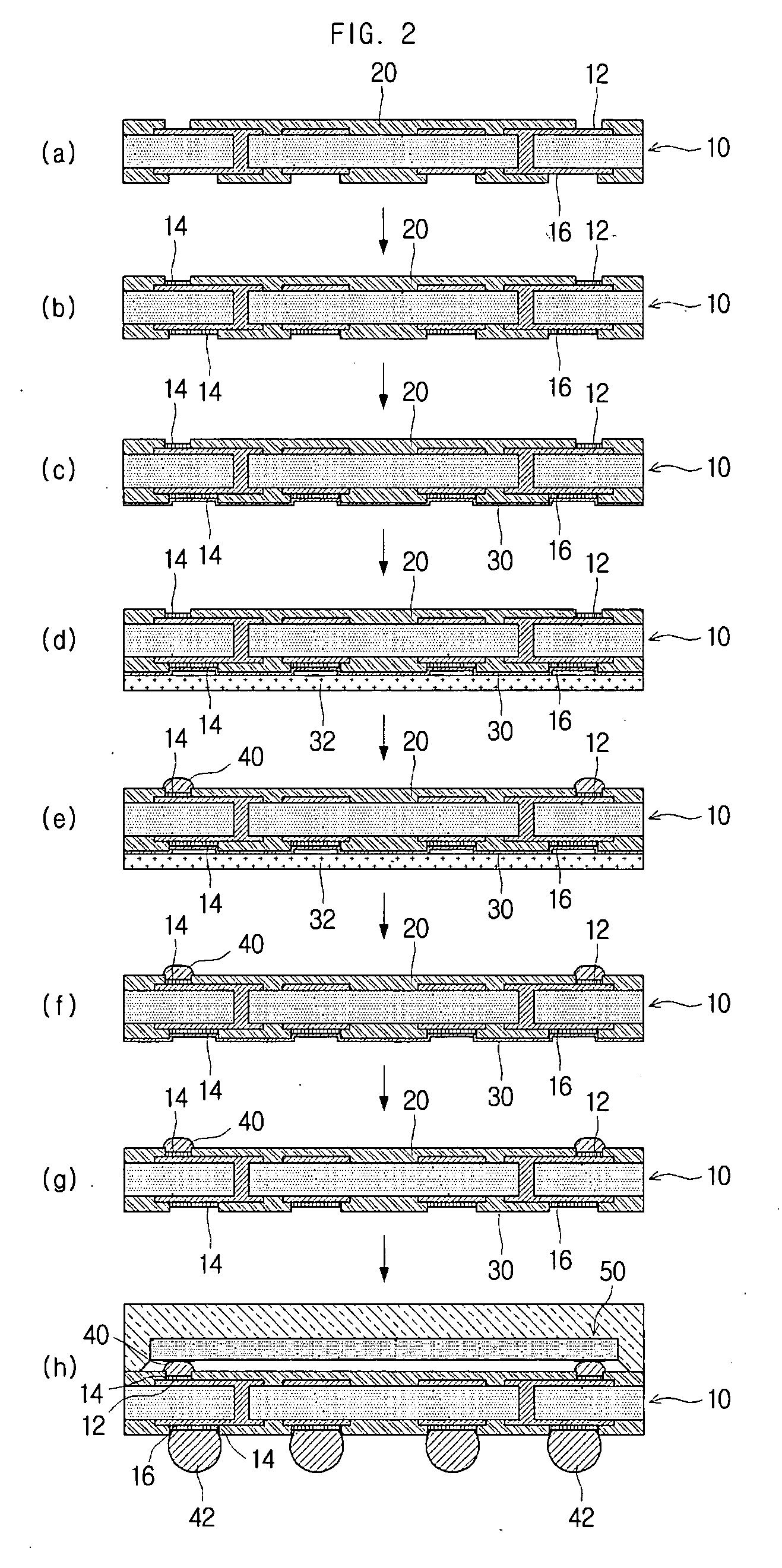

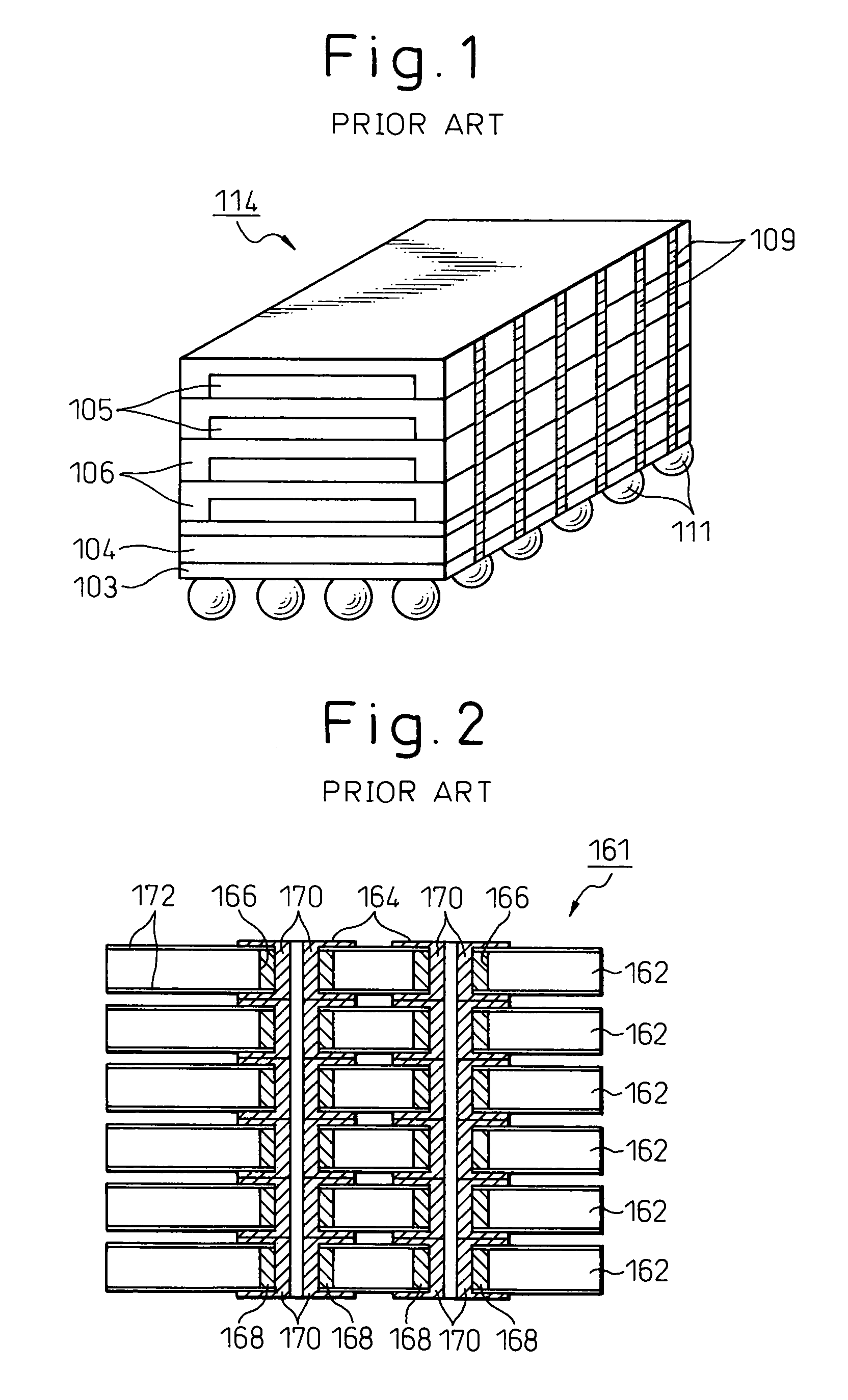

Electronic circuit device, electronic device using the same, and method for manufacturing the same

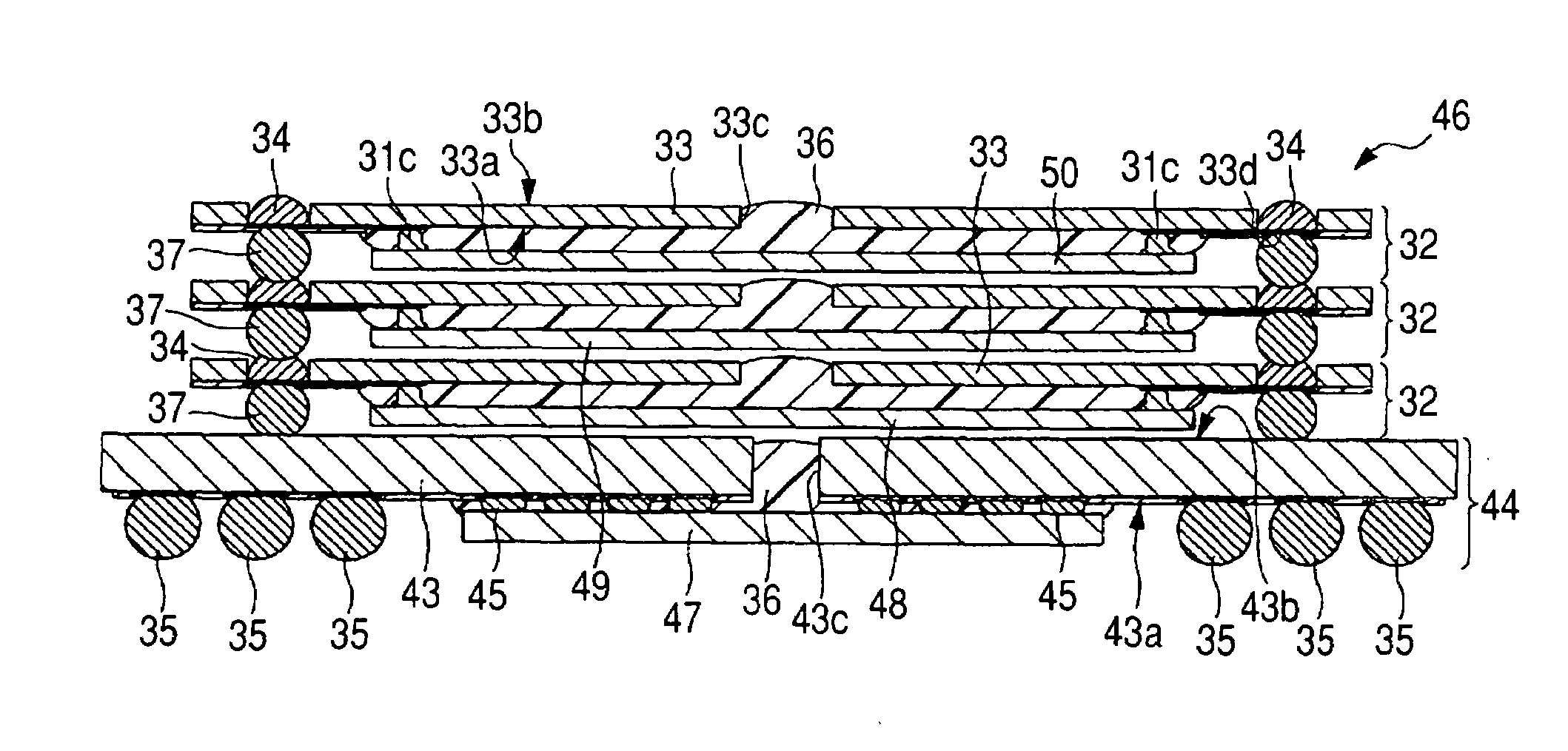

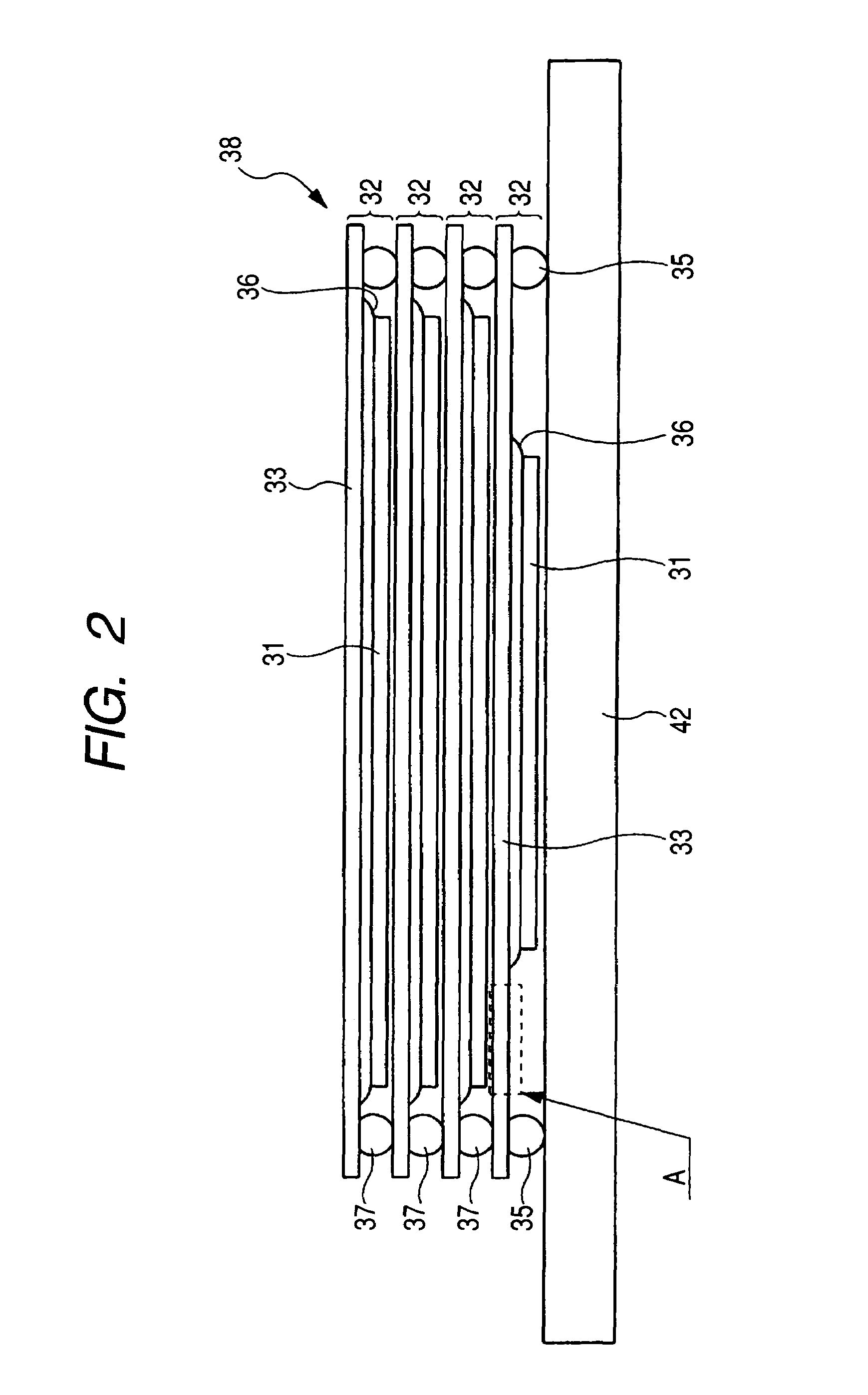

InactiveUS7768795B2High mechanical strengthImprove reliabilityDigital data processing detailsSemiconductor/solid-state device detailsElectronic componentControl circuit

Electronic circuit device (100) is structured so that a substrate module unit that are formed by stacking substrate modules made of a first resin sheet with electronic component (190) embedded thereinto is inserted into housing (150) including connecting terminal (120), control circuit (130), and first wiring pattern (140), where the substrate modules are connected to each other electrically and mechanically. This electronic circuit device (100) dispenses with a mother substrate. Further, with slimming down of a substrate module, a substrate module unit with a large number of substrate modules stacked can be loaded in a limited packaging space, thus mounting greater storage capacity and higher functionality.

Owner:PANASONIC CORP

Light-emitting diode

InactiveUS20060050526A1High-density packagingLaunch evenlyDischarge tube luminescnet screensLamp detailsOptical axisEngineering

A light-emitting diode 1 according to the present invention includes: a semiconductor light-emitting device 4 mounted on the surface of lead frames 2 and 3; and a transparent resin package 5 covering the front side of the semiconductor light-emitting device 4. A convex lens portion 8 for concentrating light emitted from the semiconductor light-emitting device 4 toward the front is provided in a surface part of the resin package 5. A circular flat portion 11 for diffusing light emitted from the semiconductor light-emitting device 4 toward the sides is provided in a part of the convex lens portion 8 intersecting the optical axis of the convex lens portion 8. Part of the convex lens portion 8 surrounding the circular flat portion 11 is a convex-lens side face. A recess 7 whose side wall is partly the convex-lens side face is provided to surround the convex lens portion.

Owner:PANASONIC CORP

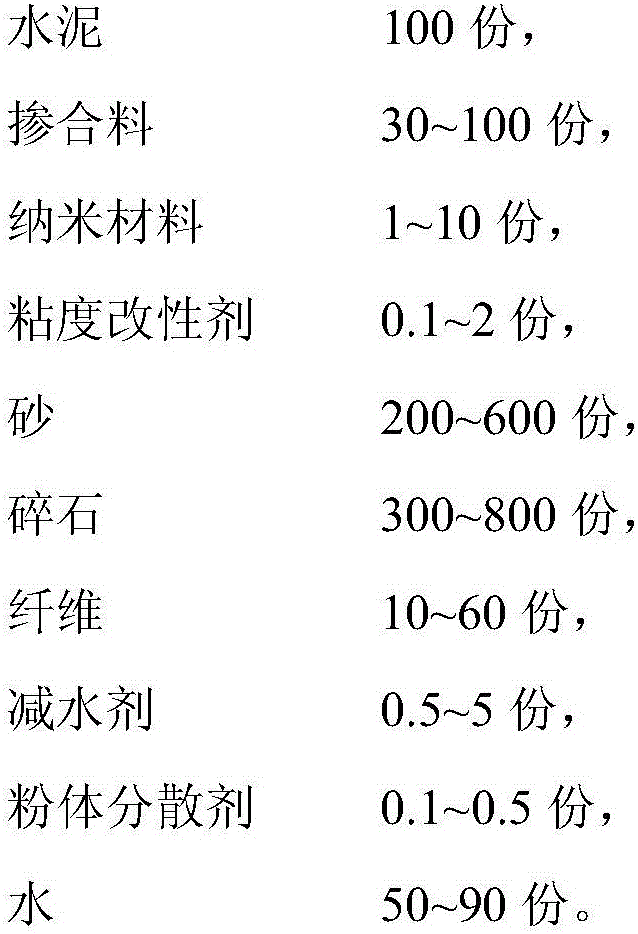

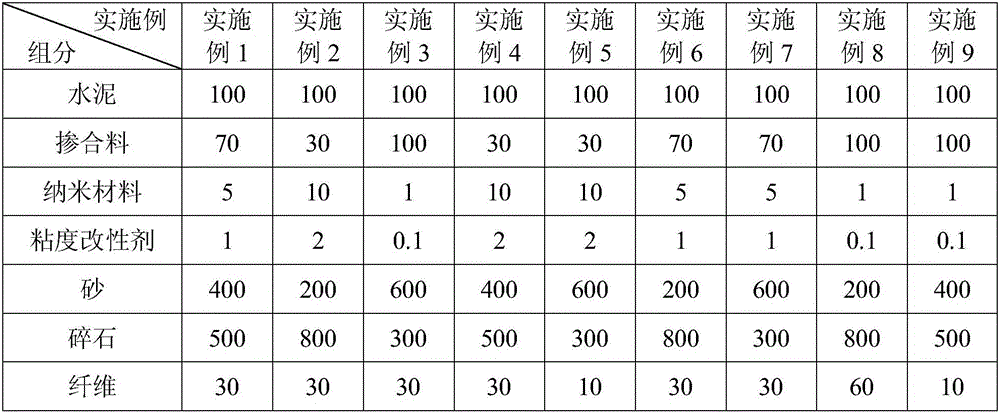

Concrete with common strength and high elastic modulus and preparation method thereof

The invention discloses concrete with common strength and high elastic modulus and a preparation method thereof. The concrete with common strength and high elastic modulus, disclosed by the invention, is prepared from the following components in parts by mass: 100 parts of cement, 30-100 parts of an admixture, 1-10 parts of a nano material, 0.1-2 parts of a viscosity modifier, 200-600 parts of sand, 300-800 parts of crushed stones, 10-60 parts of fibers, 0.5-5 parts of a water reducing agent, 0.1-0.5 part of a powder dispersant and 50-90 parts of water. After the concrete with common strength and high elastic modulus, disclosed by the invention, is subjected to standard curing or natural curing for 28d, the strength grade of the concrete is C40-C50, and the elastic modulus can reach 50GPa or more; and the concrete has excellent working performance and endurance performance.

Owner:JIANGSU SOBUTE NEW MATERIALS

Lead frame and package of semiconductor device

InactiveUS20090243058A1Small sizeHigh-density packagingSemiconductor electrostatic transducersSemiconductor/solid-state device detailsSemiconductor chipInterconnection

A lead frame including a shield plate, a main frame, interconnection arms, support arms, and terminals is sealed with a resin mold including a base portion for embedding the shield plate and a peripheral wall for embedding the interconnection arms and support arms, thus forming a package base. The interconnection arms and support arms are subjected to bending so as to depress the shield plate in position compared with the main frame. At least one semiconductor chip (e.g. a microphone chip) is mounted on the base portion just above the shield plate. A cover having conductivity is attached onto the main frame exposed on the upper end of the peripheral wall, thus completely producing a semiconductor device encapsulated in a package. A sound hole is formed in the cover or the package base so as to allow the internal space of the package to communicate with the external space.

Owner:YAMAHA CORP

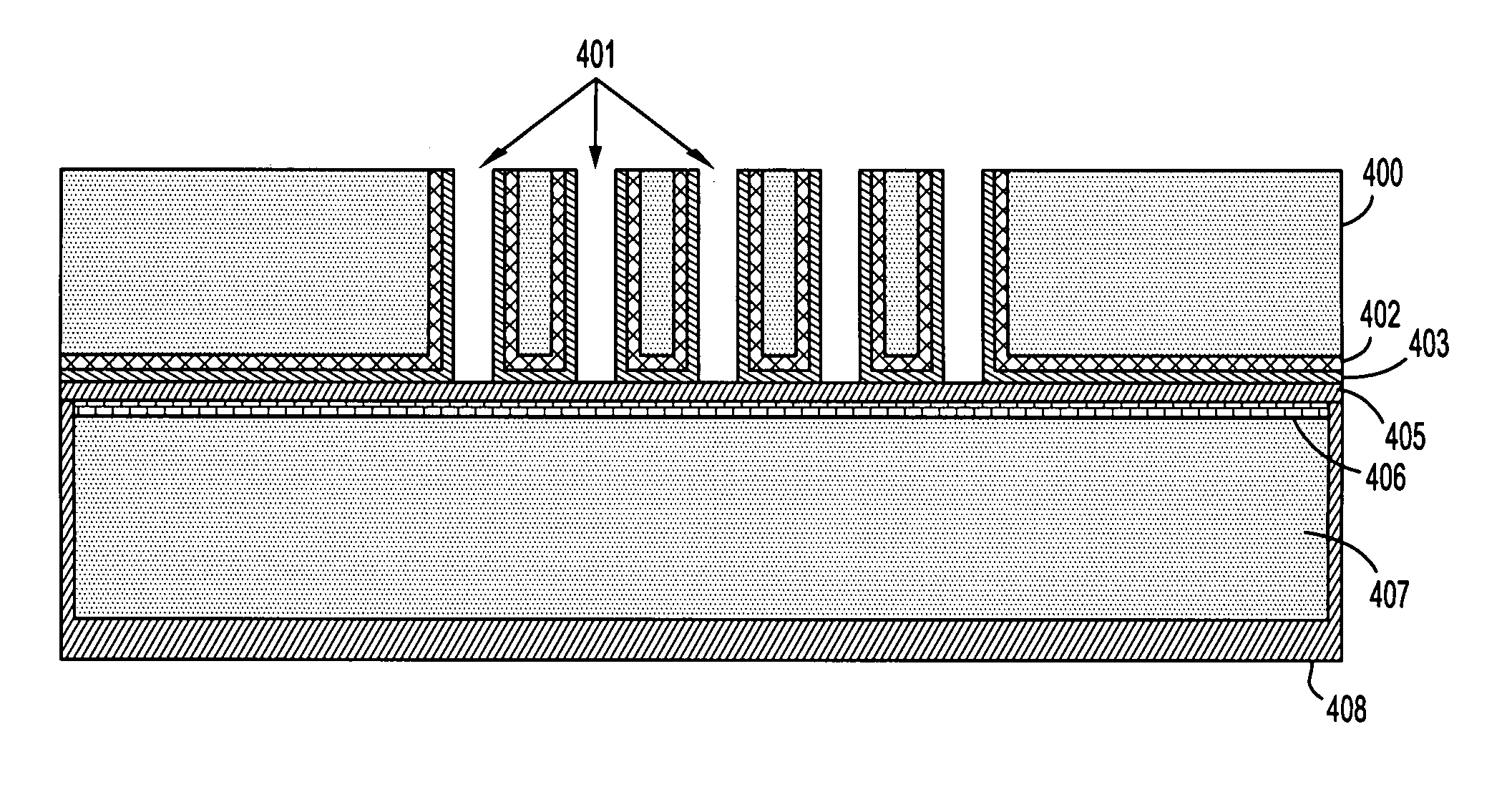

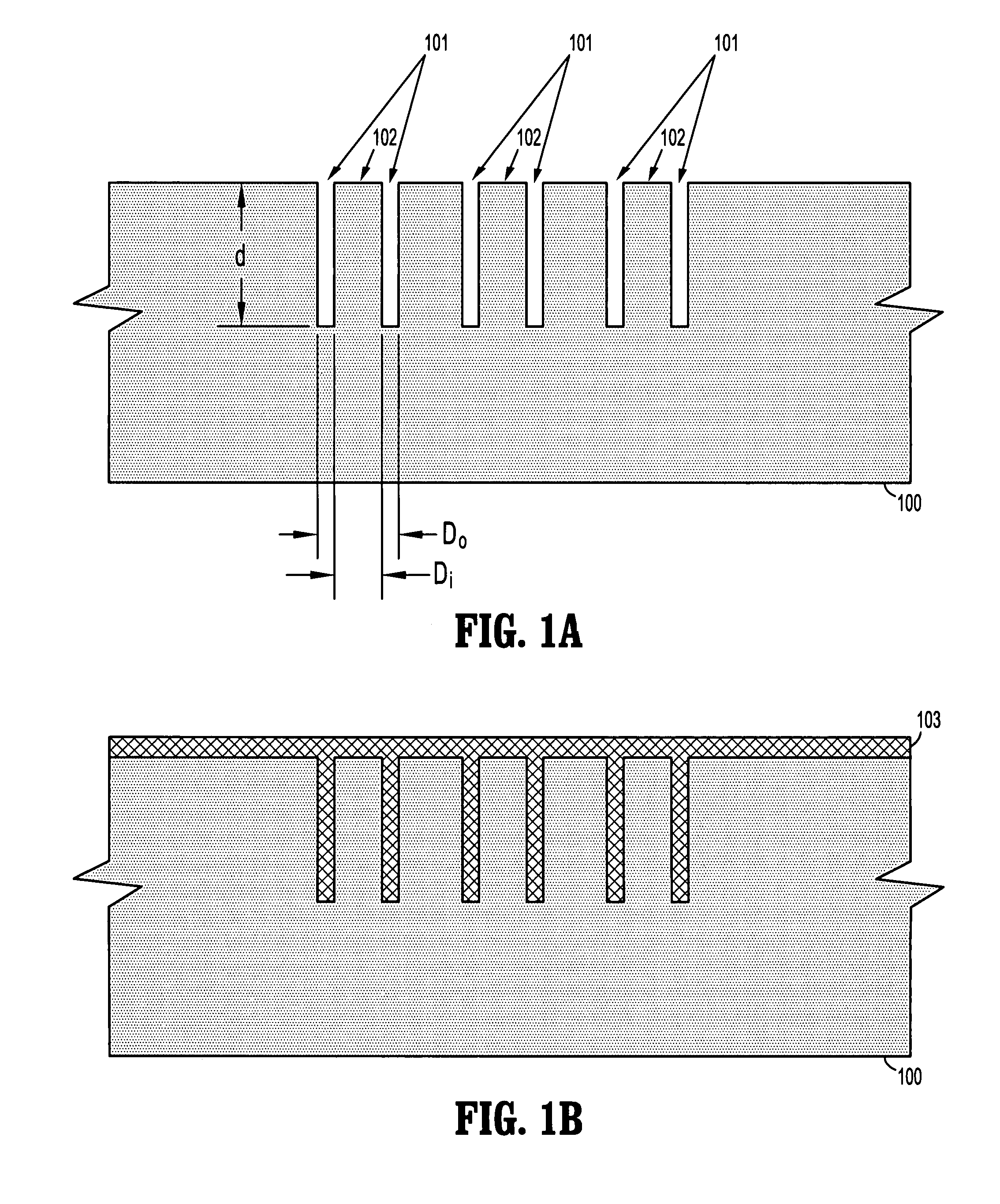

Methods for fabricating silicon carriers with conductive through-vias with low stress and low defect density

InactiveUS7863189B2High-density packagingHigh-yieldSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorMicrometer

Methods are provided for fabricating silicon carriers with conductive through-vias that allow high-yield manufacture of silicon carrier with low defect density. In particular, methods are provided which enable fabrication of silicon carries with via diameters such as 1 to 10 microns in diameter for a vertical thickness of less than 10 micrometers to greater than 300 micrometers, which are capable robust to thermal-mechanical stresses during production to significantly minimize the thermal mechanical movement at the via sidewall interface between the silicon, insulator, liner and conductor materials.

Owner:GLOBALFOUNDRIES U S INC

Copper pillar tin bump on semiconductor chip and method of forming the same

InactiveUS20090127708A1High-density packagingHigh densitySemiconductor/solid-state device detailsSolid-state devicesResistSemiconductor chip

Copper pillar tin bump on semiconductor chip comprises a copper layer composed on chip and a tin layer entirely wrapping whole outer surface of said copper layer. A method for forming of the copper pillar tin bump on semiconductor chip comprises: composing the first copper layer on said chip; applying photoresist to said first copper layer, exposing and developing a part of said photoresist, composing the copper pillar layer at the developed part of photoresist, composing the upper tin layer, removing said photoresist, removing said the first copper layer except disposing place of copper pillar layer, composing side tin layer. The minute pattern makes it possible to form a high density packaging by reducing a pitch of copper pillar tin bump. Signal delay can be reduced by low electric resistance, and underfill can be easily soaked.

Owner:HWABEAK ENG

Semiconductor device

InactiveUS20050040509A1High-density packagingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesMemory chipDevice material

For high density packaging of a semiconductor device, the semiconductor device has a multi-layer substrate, a first-stage chip connected electrically to the multi-layer substrate, other package substrates stacked in three stages on the multi-layer substrate and each connected to an underlying wiring substrate through solder balls, second-, third- and fourth-stage chips electrically connected respectively to the other package substrates, and solder balls provided on the bottom multi-layer substrate. The number of wiring layers in the bottom multi-layer substrate which has a logic chip is larger than that in the package substrates which have memory chips, whereby the semiconductor device can have a wiring layer not used for distribution of wires to the solder balls and wiring lines in the wiring layer can be used for the mounting of another semiconductor element or a passive component to attain high density packaging of the semiconductor device as a stacked type package.

Owner:RENESAS ELECTRONICS CORP

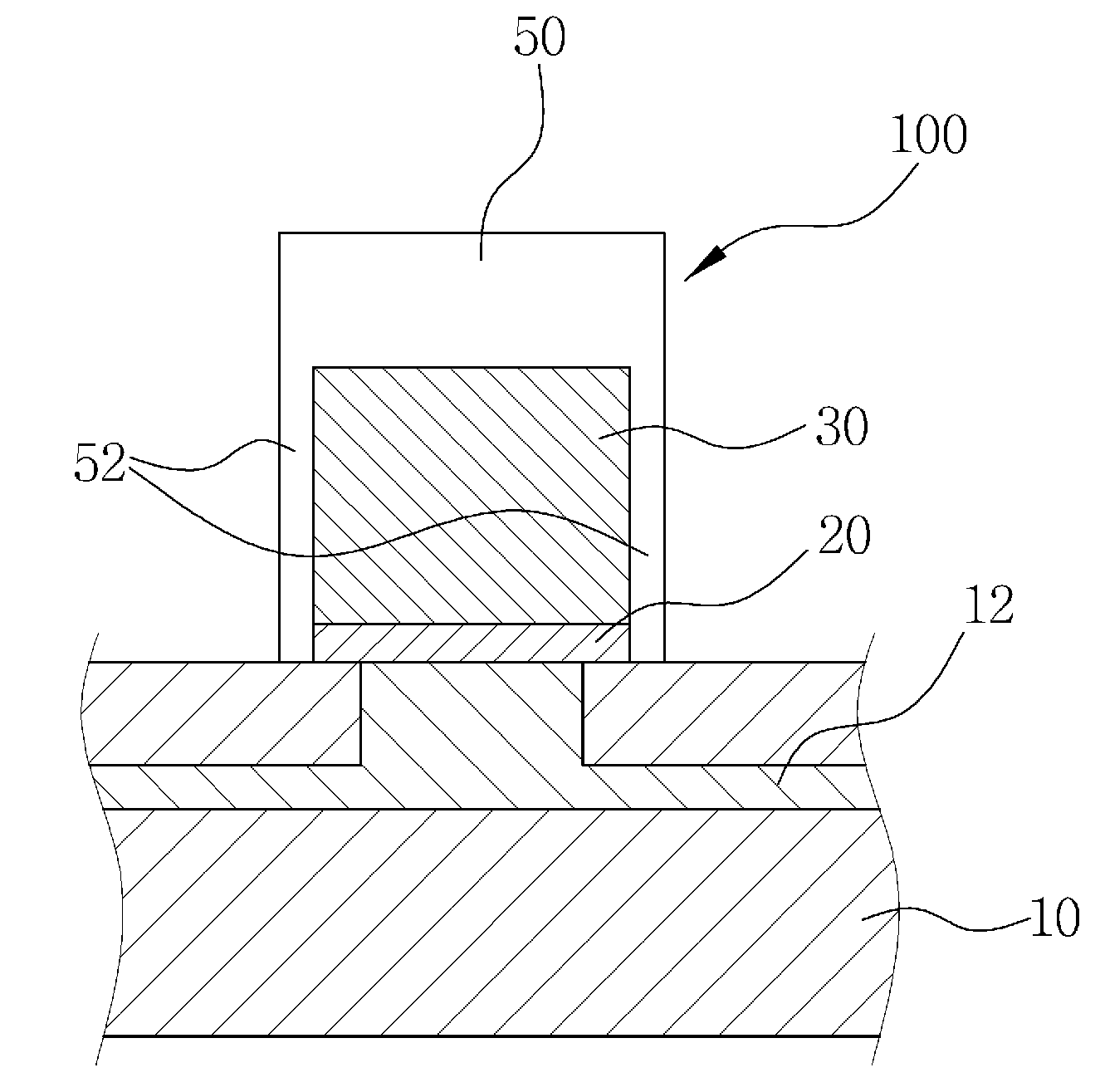

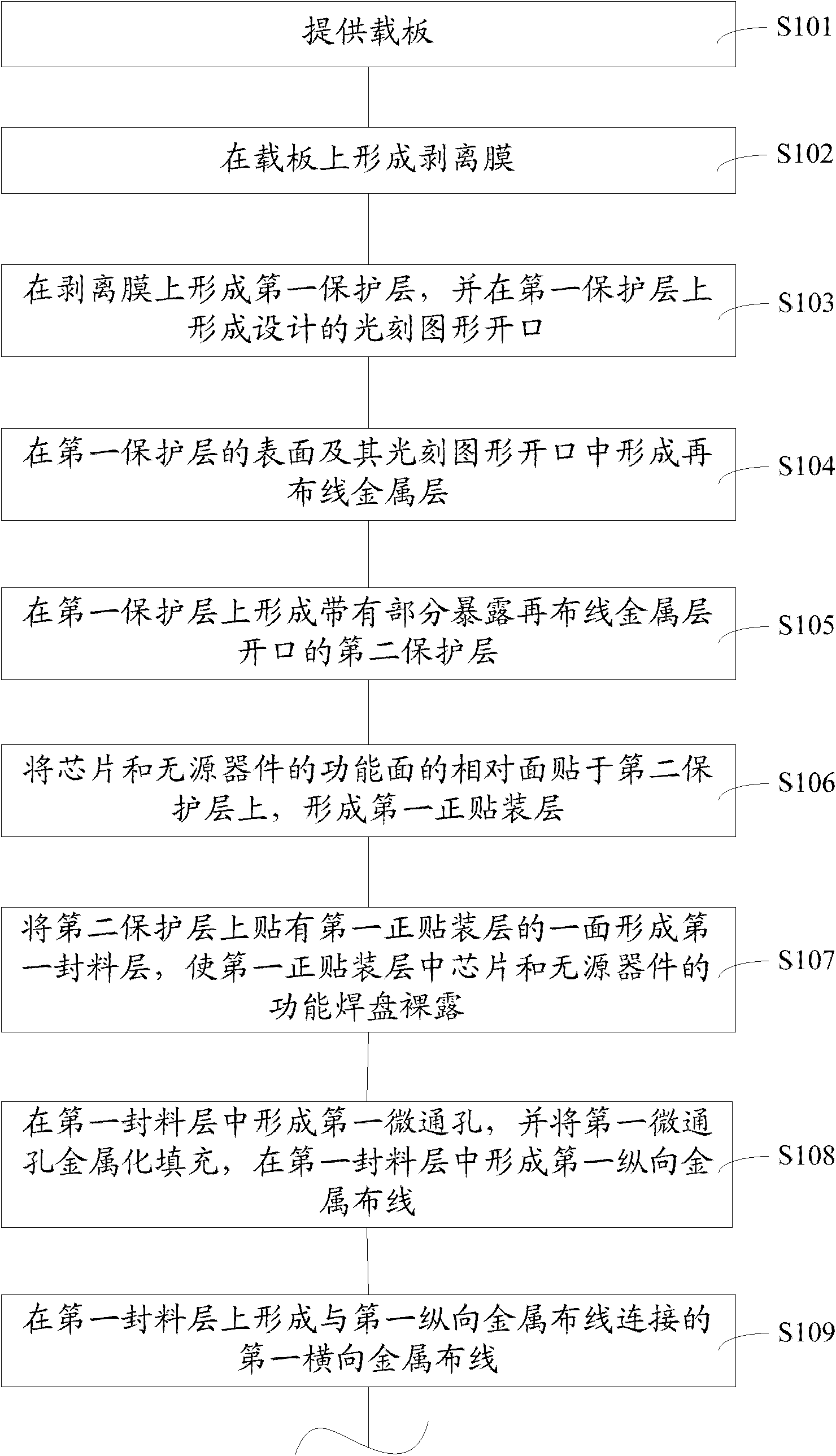

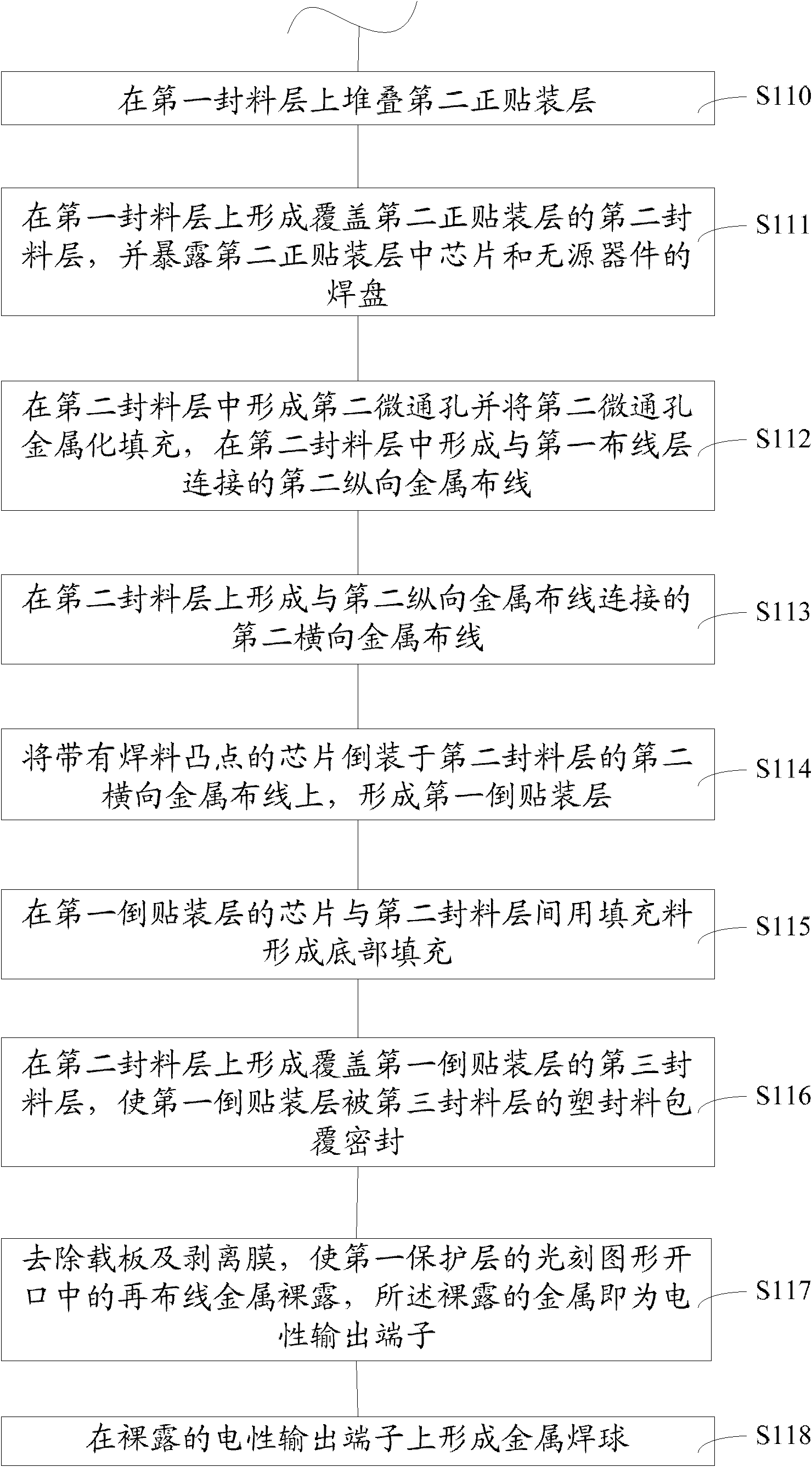

Fan-out high-density packaging method

ActiveCN102157393ALess distracting factorsComply with the trend of light, thin and shortSolid-state devicesSemiconductor/solid-state device manufacturingInterference factorEngineering

The invention relates to a fan-out high-density packaging method, which comprises the following steps of: providing a carrier plate; forming a stripping membrane on the carrier plate; forming protective layers on the stripping membrane; forming a rewiring metal layer in the protective layers; forming wiring packaging layers which are conductive with the rewiring metal layer on the protective layers; forming inversion packaging layers on the wiring packaging layers, wherein the packaging layers are connected electrically and mutually by wiring layers and welding flux salient points; removing the carrier plate and the stripping membrane, so that rewiring metal in a first protective layer is exposed; and forming a metal welded ball on the exposed rewiring metal. Compared with the prior art, the fan-out high-density packaging method has the advantages that: a final packaging product with an integral systemic function instead of a single chip function can be formed, and the resistance and inductance in a system and interference factors among chips are reduced. In addition, a complex multi-layer interconnection structure can be formed, so that the wafer system-level packaging of a higher integration level is realized.

Owner:NANTONG FUJITSU MICROELECTRONICS

Electronic Circuit Device, Electronic Device Using the Same, and Method for Manufacturing the Same

InactiveUS20080094793A1Large storage capacityFunction increaseDigital data processing detailsSemiconductor/solid-state device detailsEngineeringElectronic component

Electronic circuit device (100) is structured so that a substrate module unit that are formed by stacking substrate modules made of a first resin sheet with electronic component (190) embedded thereinto is inserted into housing (150) including connecting terminal (120), control circuit (130), and first wiring pattern (140), where the substrate modules are connected to each other electrically and mechanically. This electronic circuit device (100) dispenses with a mother substrate. Further, with slimming down of a substrate module, a substrate module unit with a large number of substrate modules stacked can be loaded in a limited packaging space, thus mounting greater storage capacity and higher functionality.

Owner:PANASONIC CORP

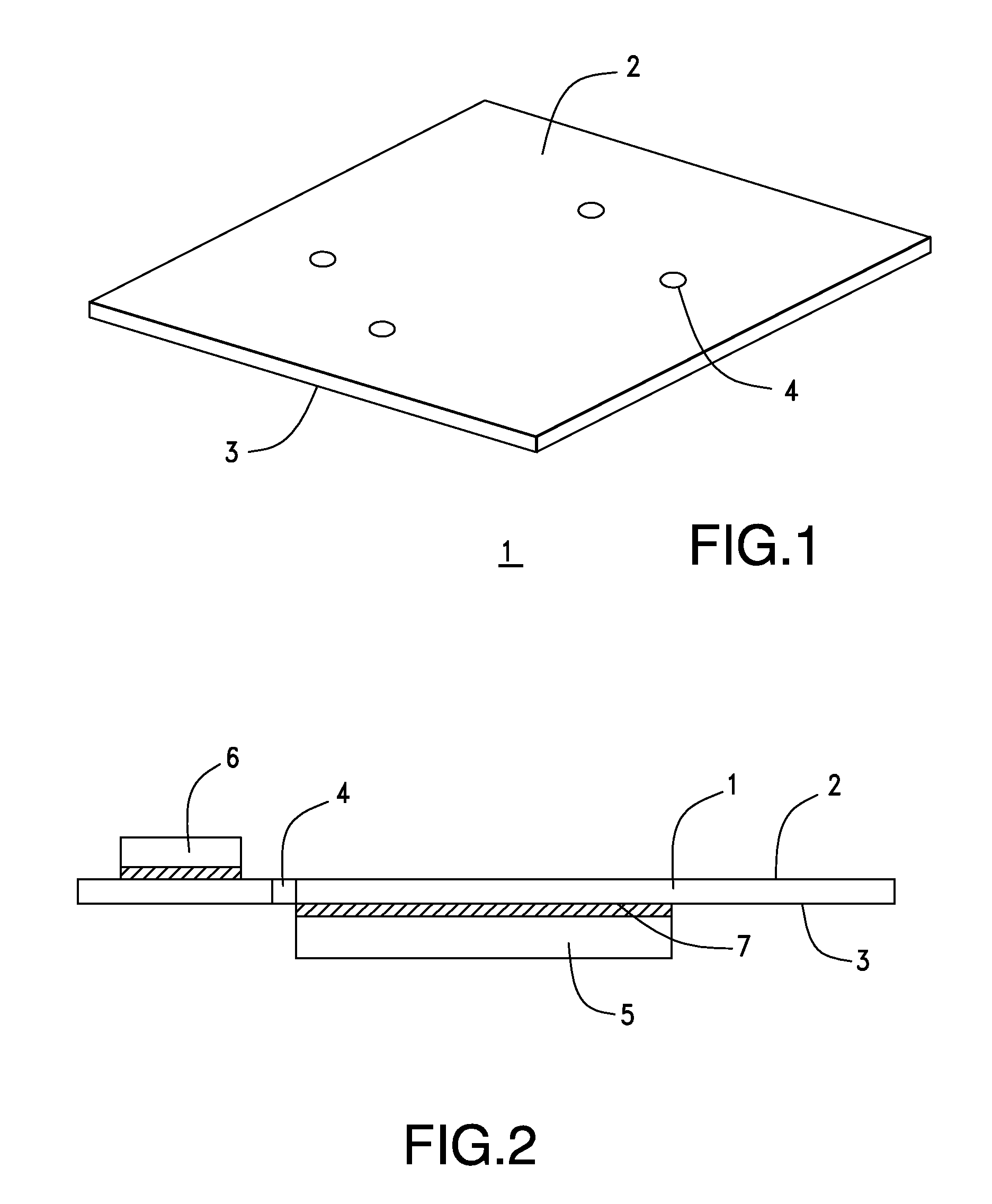

Heat pipe and circuit board with a heat pipe function

InactiveUS8611089B2Improve cooling effectIncrease speedDigital data processing detailsSemiconductor/solid-state device detailsVaporizationEngineering

A heat pipe for cooling an exothermic body by the vaporization and condensation of an enclosed cooling medium is disclosed. The heat pipe comprises a flat plate-like upper plate, a flat plate-like lower plate opposed to the upper plate, and a plurality of flat plate-like intermediate plates overlaid on each other between the upper plate and the lower plate and having internal through-holes. The internal through-holes formed in each of a plurality of the intermediate plates are adapted such that only part of each through-hole is overlapped on each other to form capillary tube paths, each having a cross-sectional area smaller than the cross-sectional area of the through-hole in the flat surface direction.

Owner:FUCHIGAMI MICRO +1

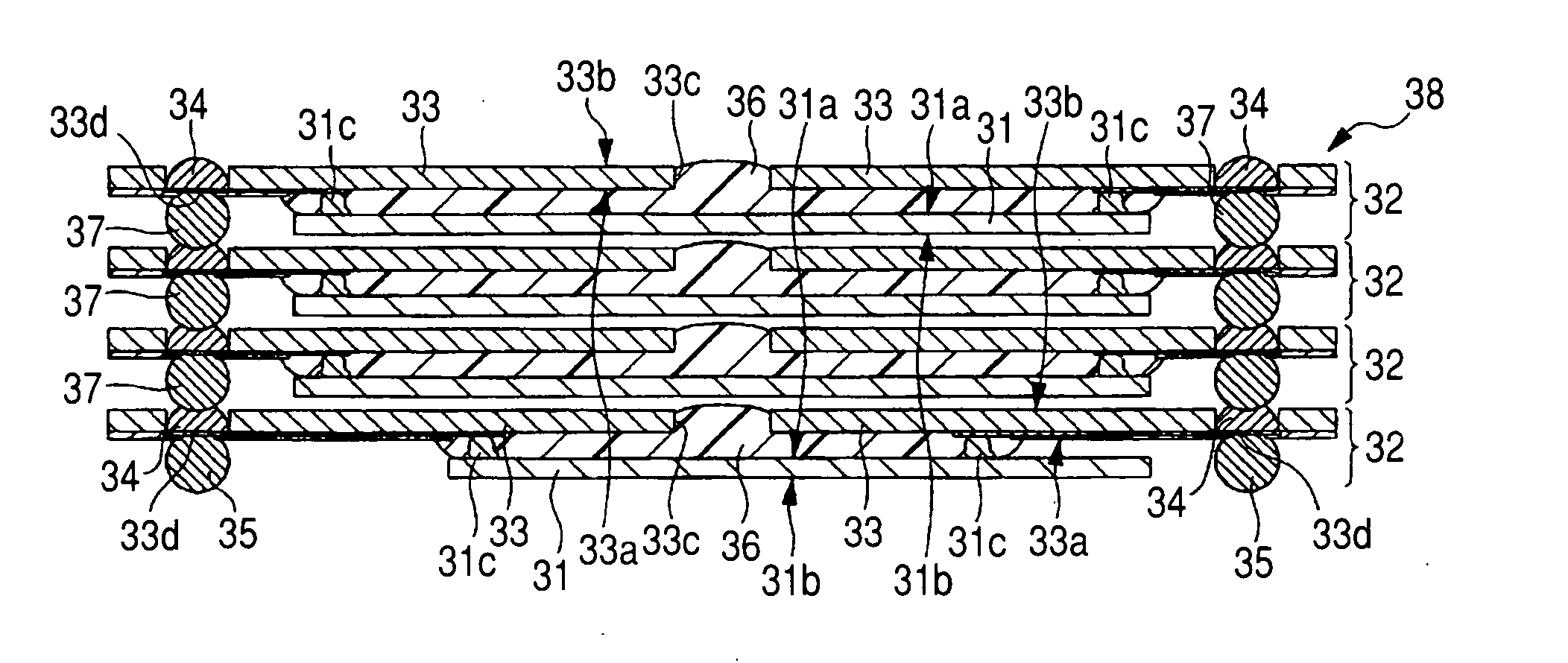

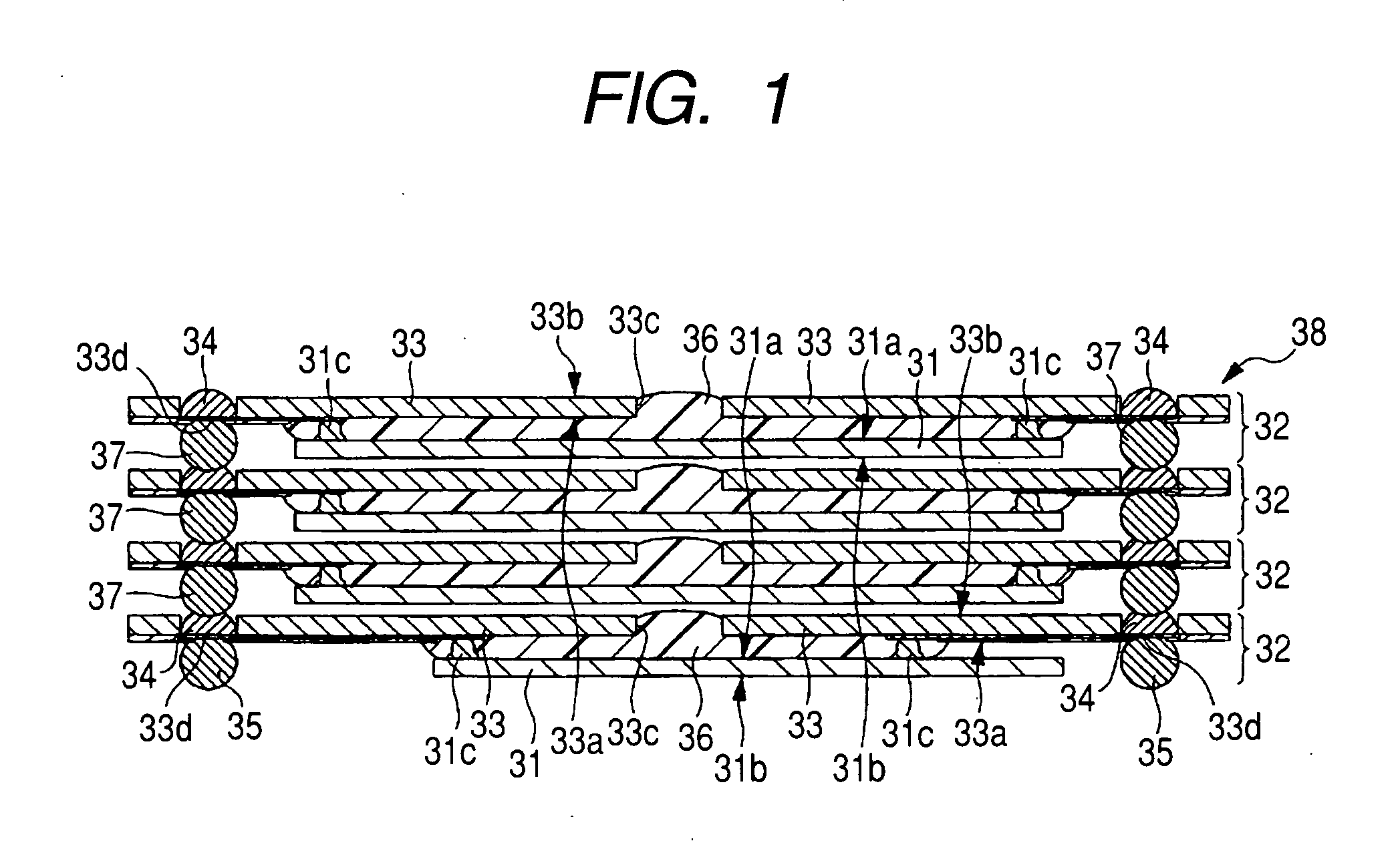

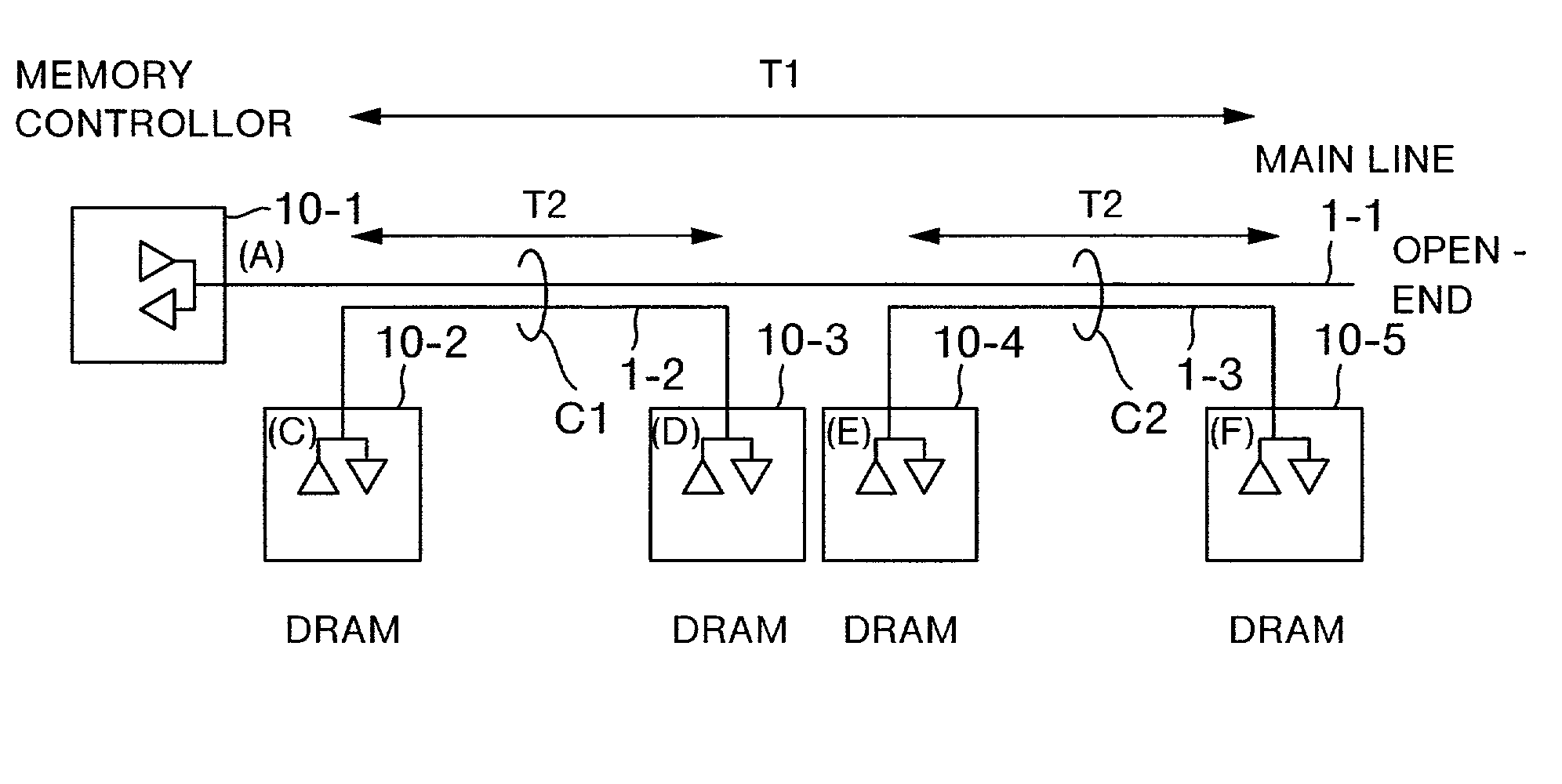

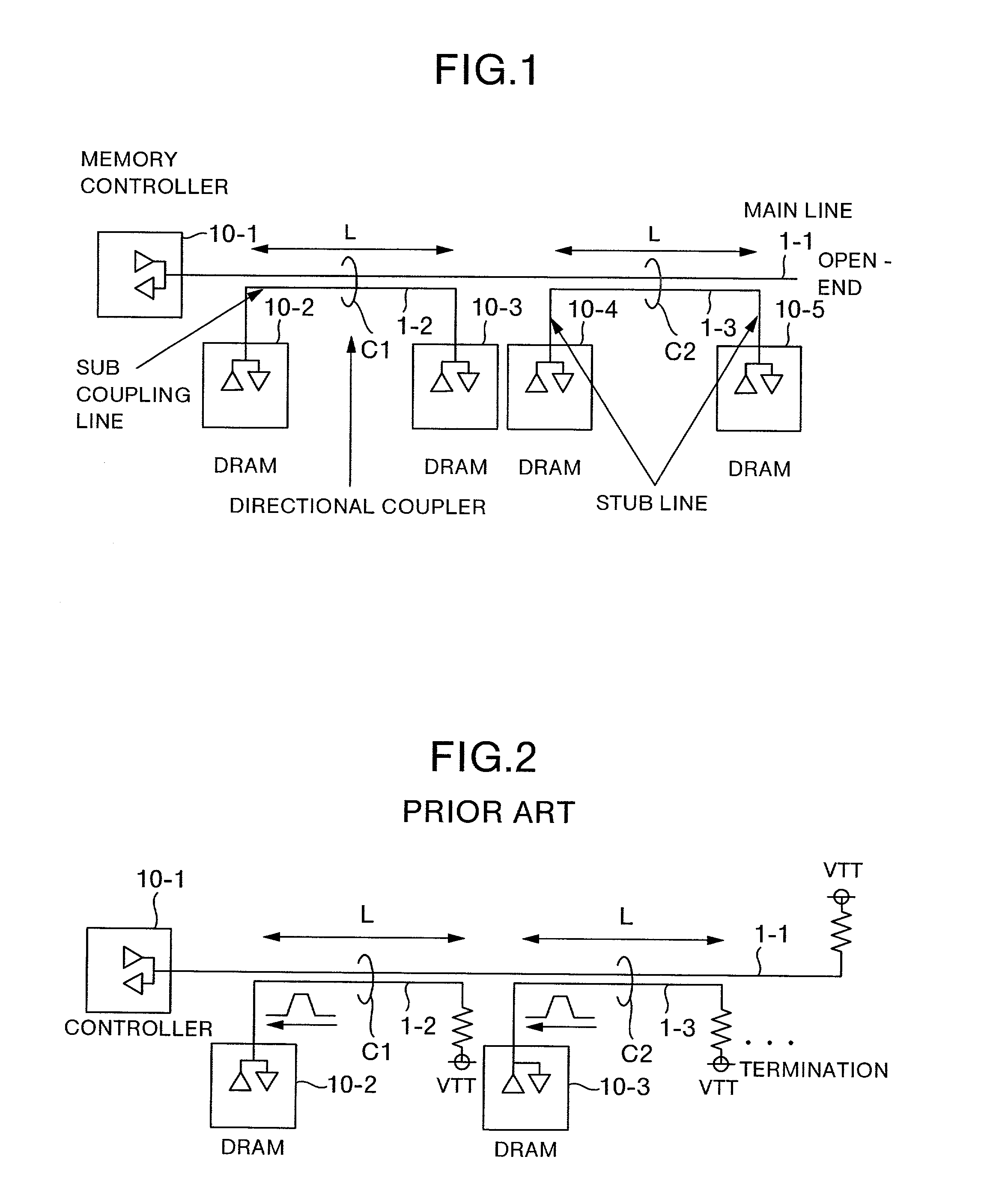

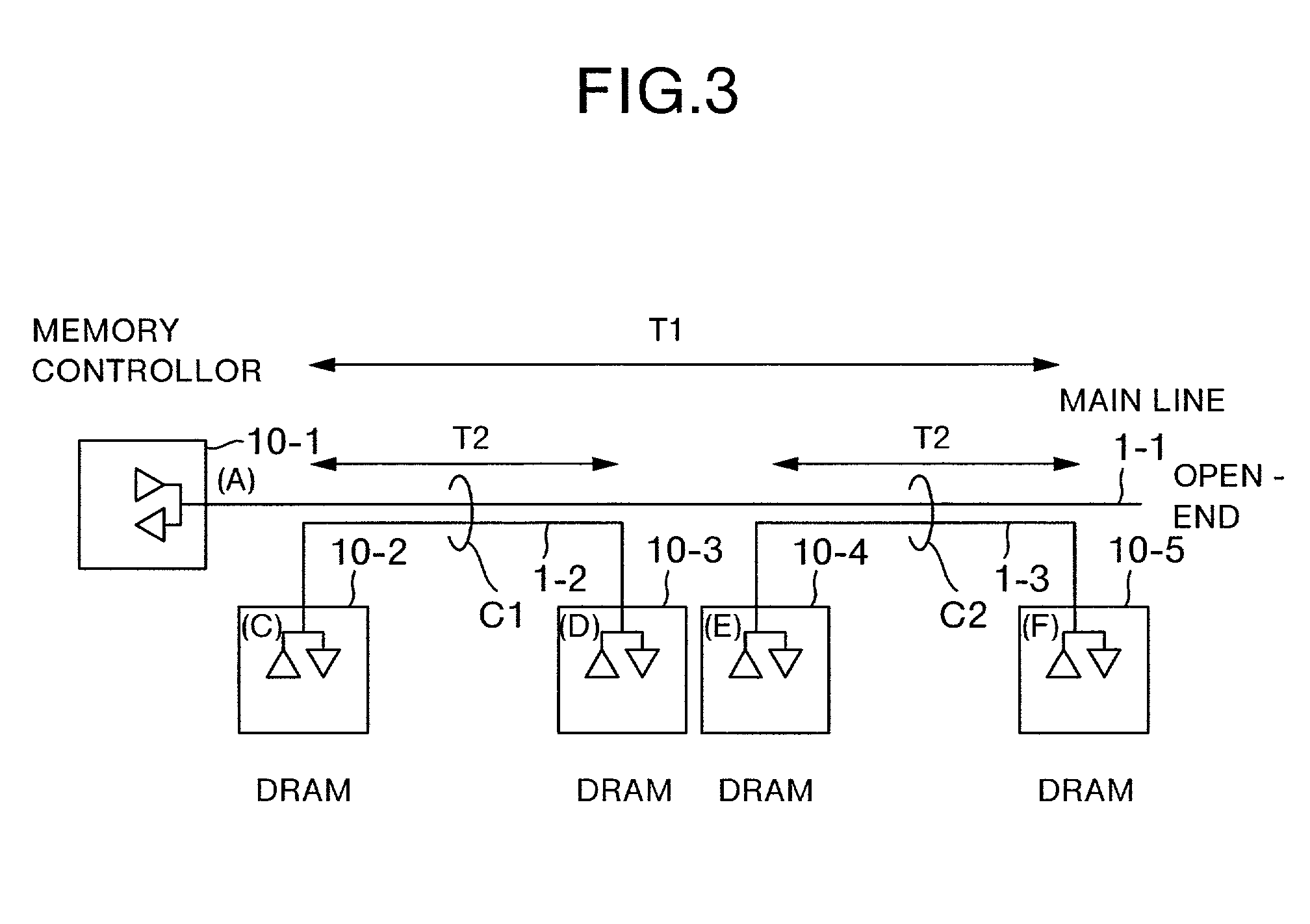

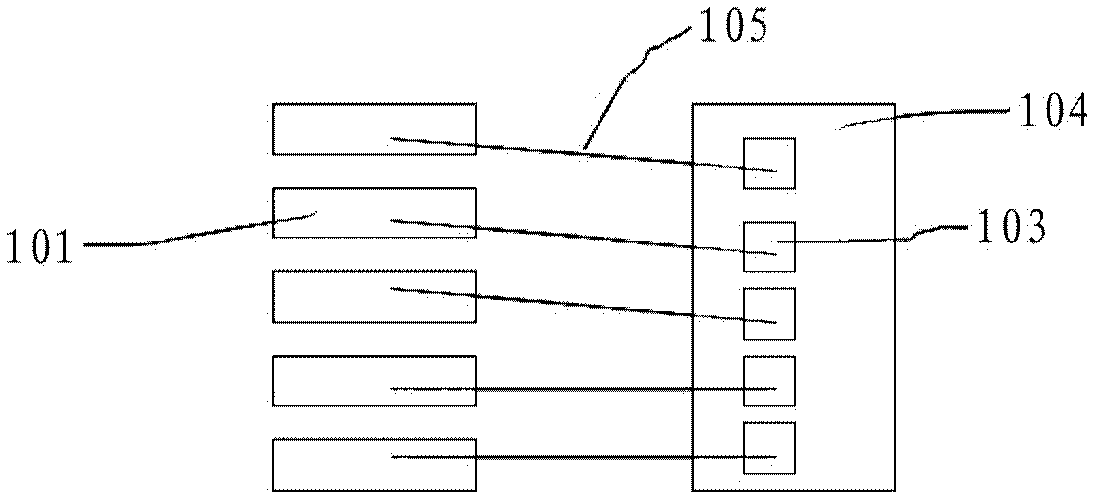

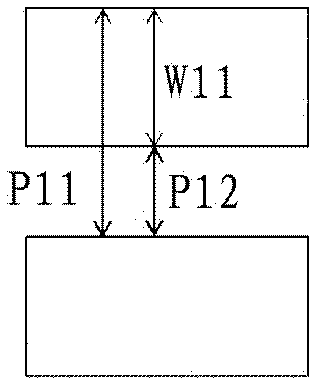

Data transmission system of directional coupling type using forward wave and reflection wave

InactiveUS6983023B2Improve performanceMemory access time be shortenSolid-state devicesDigital storageVIT signalsData transmission systems

A memory module bus system using a plurality of directional couplers to permit high-density packaging. A wiring line (main line) extending from a main controller and cooperating with a sub coupling line to form a directional coupler is open-ended or short-circuited to ensure that a forward wave and a reflection wave can be used to generate signals in opposite directions of the directional coupler. Memory modules are connected to opposite ends of the sub coupling line. The line length of the coupler can be half the pitch between the memory modules.

Owner:RENESAS ELECTRONICS CORP

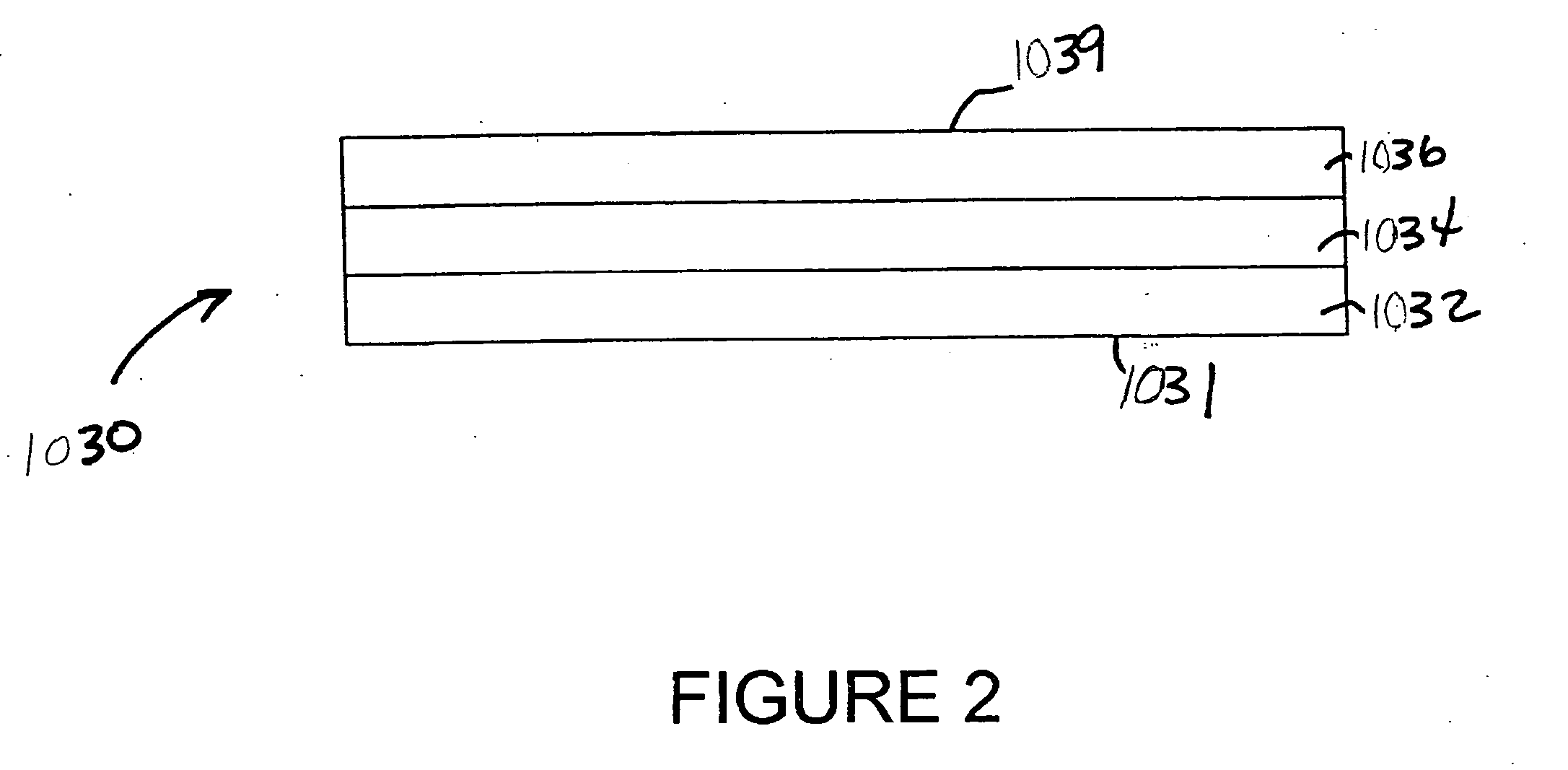

Semiconductor device, package structure thereof, and method for manufacturing the semiconductor device

InactiveUS20070152320A1High densitySmall thicknessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInductor

A semiconductor device includes a plurality of insulating layers laminated on a substrate to cover passive elements such as a capacitor, an inductor, and the like, and to fix an IC chip in a face up state in one of the insulating layers. The insulating layers have similar structures in each of which the passive element or the semiconductor chip is disposed in at the bottom, a plug is formed in the insulating layer to pass therethrough in the thickness direction for extending an electrode of one of these elements to the top surface, and a conductive layer is provided as wiring on the top surface of the insulating layer to be connected to the plugs for electrically connecting respective elements or rearranging the electrode position. Also, an insulating layer is provided on the top for protecting the semiconductor device and for providing an external connecting electrode.

Owner:SONY CORP

Semiconductor device

InactiveUS7332800B2High-density packagingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesMemory chipElectrical conductor

Owner:RENESAS ELECTRONICS CORP

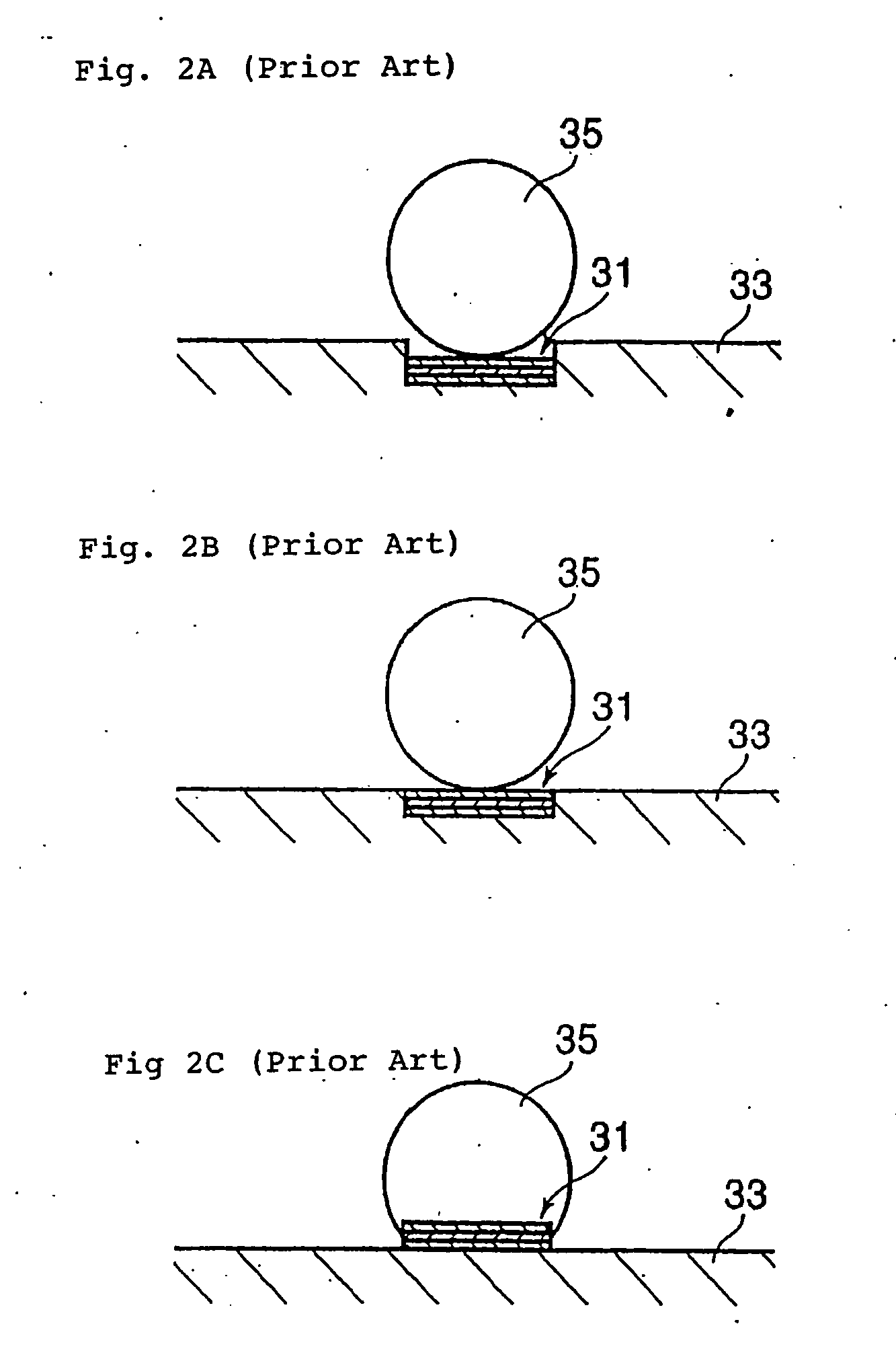

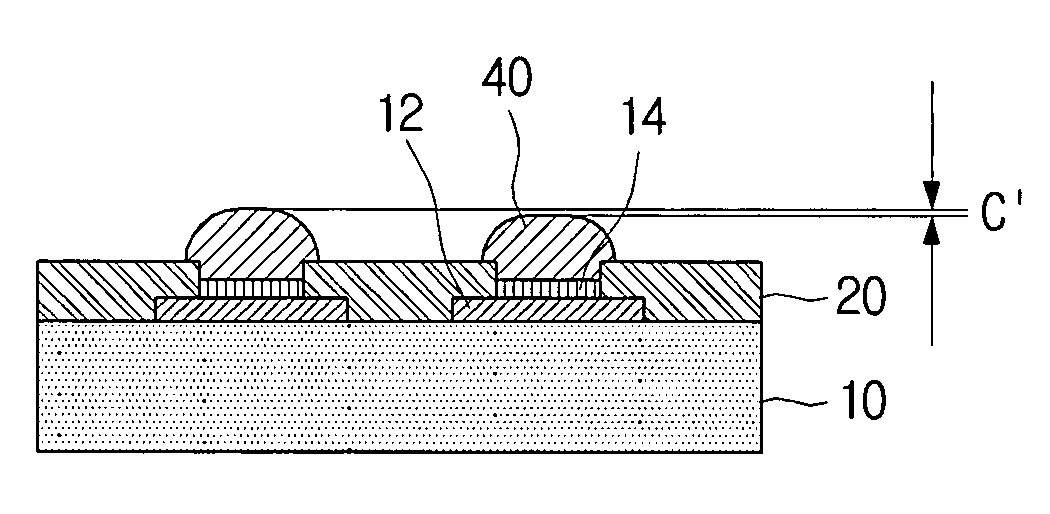

Board for mounting BGA semiconductor chip thereon, semiconductor device, and methods of fabricating such board and semiconductor device

InactiveUS20050156326A1Small tendency to breakEasilySemiconductor/solid-state device detailsPrinted circuit aspectsDevice materialSolder ball

To fabricate a semiconductor device, a pattern of recesses and lands is formed on a copper sheet as a matrix sheet, and BGA pads are formed on the lands on the copper sheet. An insulating layer is formed on the copper sheet to transfer the pattern of recesses and lands from the copper sheet to the insulating layer for thereby forming recesses in the insulating layer and placing BGA pads in the recesses in the insulating layer. Vias are formed through the insulating layer, and a conductive layer serving as circuits and interconnections is formed, the conductive layer being connected to the BGA pads by the vias. When the copper sheet is removed, the BGA pads are positioned within the recesses in the insulating layer. The BGA pads have surfaces positioned higher than the bottom of the recesses and lower than the surface of the insulating layer. A semiconductor chip is mounted on the conductive layer, and solder balls are joined to the BGA pads. Both the productivity of a process of mounting the solder balls and the bonding strength of the solder balls are increased.

Owner:KYOCERA CORP

Heat Pipe, Method For Manufacturing A Heat Pipe, And A Circuit Board With A Heat Pipe Function

InactiveUS20120106084A1Improve cooling effectIncrease speedDigital data processing detailsSemiconductor/solid-state device detailsVaporizationEngineering

A heat pipe for cooling an exothermic body by the vaporization and condensation of an enclosed cooling medium is disclosed. The heat pipe comprises a flat plate-like upper plate, a flat plate-like lower plate opposed to the upper plate, and a plurality of flat plate-like intermediate plates overlaid on each other between the upper plate and the lower plate and having internal through-holes. The internal through-holes formed in each of a plurality of the intermediate plates are adapted such that only part of each through-hole is overlapped on each other to form capillary tube paths, each having a cross-sectional area smaller than the cross-sectional area of the through-hole in the flat surface direction.

Owner:FUCHIGAMI MICRO +1

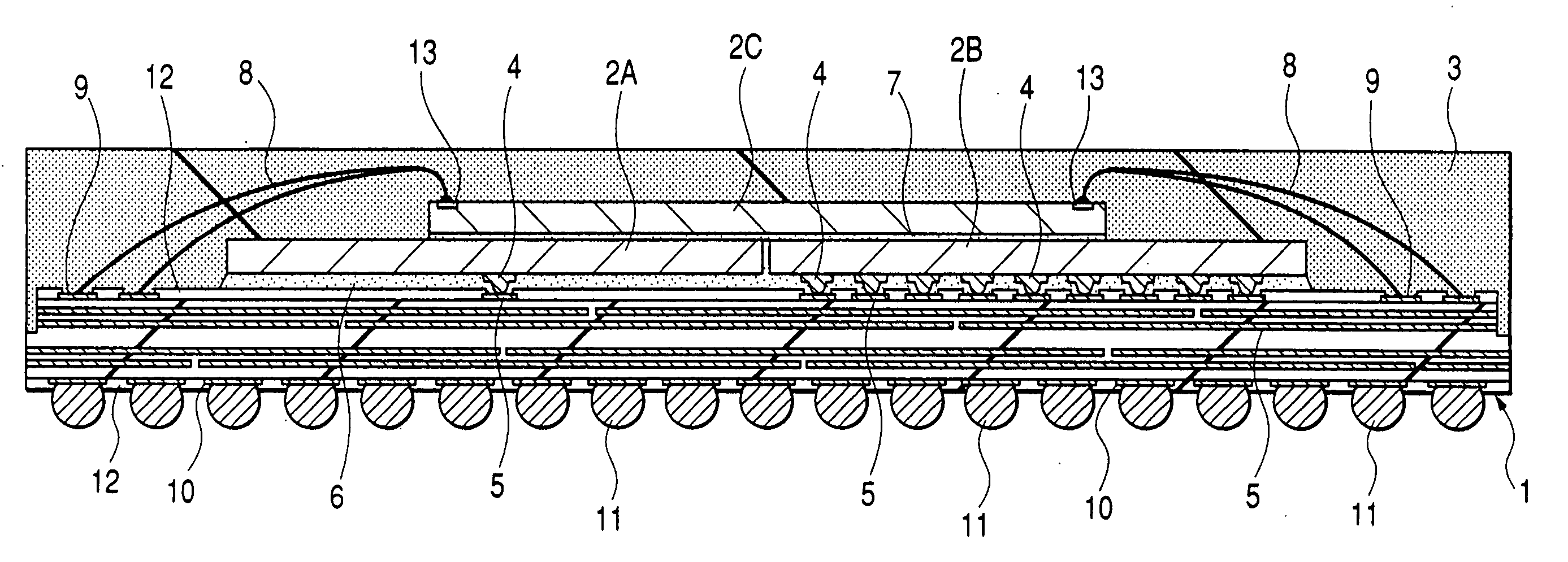

Semiconductor device and manufacturing method thereof

InactiveUS20060189031A1Improve reliabilityLow costSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

Of three chips (2A), (2B), and (2C) mounted on a main surface of a package substrate (1) in a multi-chip module (MCM), a chip (2A) with a DRAM formed thereon and a chip (2B) with a flash memory formed thereon are electrically connected to wiring lines (5) of the package substrate (1) through Au bumps (4), and a gap formed between main surfaces (lower surfaces) of the chips (2A), (2B) and a main surface of the package substrate (1) is filled with an under-fill resin (6). A chip (2C) with a high-speed microprocessor formed thereon is mounted over the two chips (2A) and (2B) and is electrically connected to bonding pads (9) of the package substrate (1) through Au wires (8).

Owner:RENESAS ELECTRONICS CORP

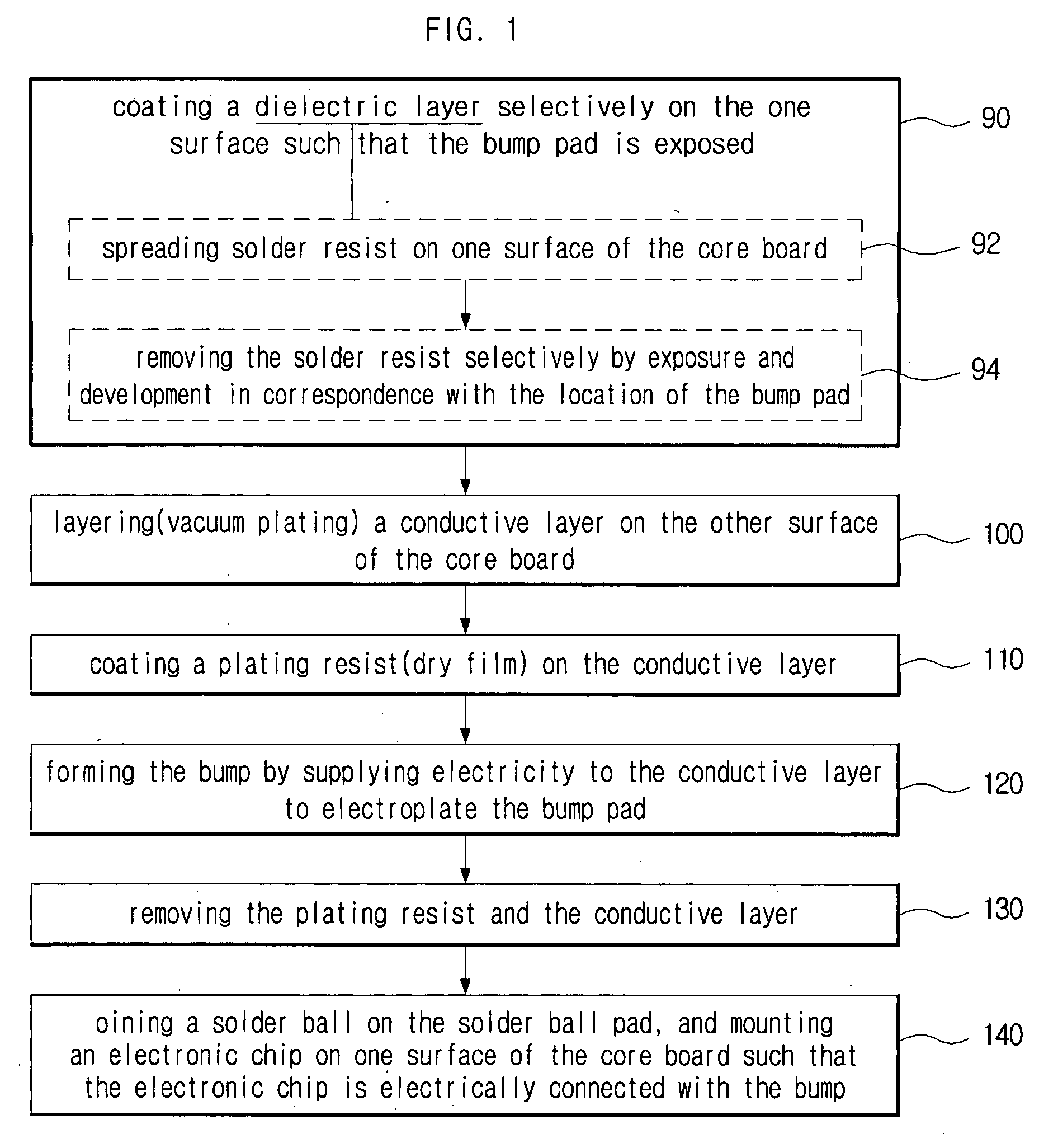

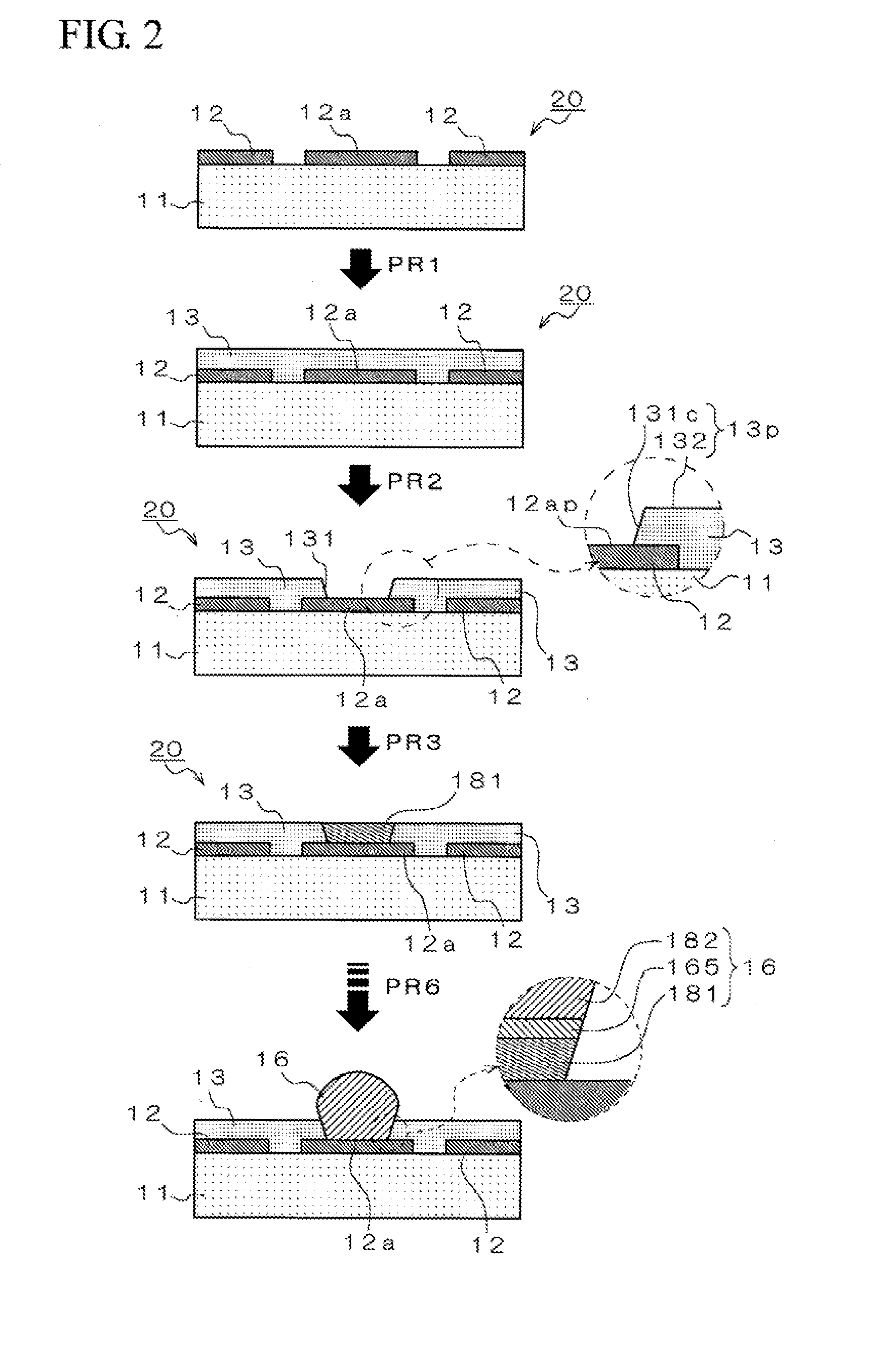

Manufacturing method package substrate

InactiveUS20070298546A1Reduce defective rateUniform heightSemiconductor/solid-state device detailsSolid-state devicesResistTin plating

A manufacturing method of a package substrate is disclosed. The method for manufacturing a package substrate is by forming a bump on a bump pad in a core board, where a first circuit pattern including the bump pad is formed on one surface, a second circuit pattern electrically connected with the first circuit pattern is formed on the other surface, and a dielectric layer is selectively coated on the one surface such that the bump pad is exposed. The method includes layering a conductive layer on the other surface of the core board, coating a plating resist on the conductive layer, forming the bump by supplying electricity to the conductive layer to electroplate the bump pad, and removing the plating resist and the conductive layer. This makes it possible to omit the coining process and increase the density of the circuit by forming a fine bump by an electro tin plating method with small plating thickness deviation without designing additional plating bus lines, and improves the electrical performance without remaining plating bus lines.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

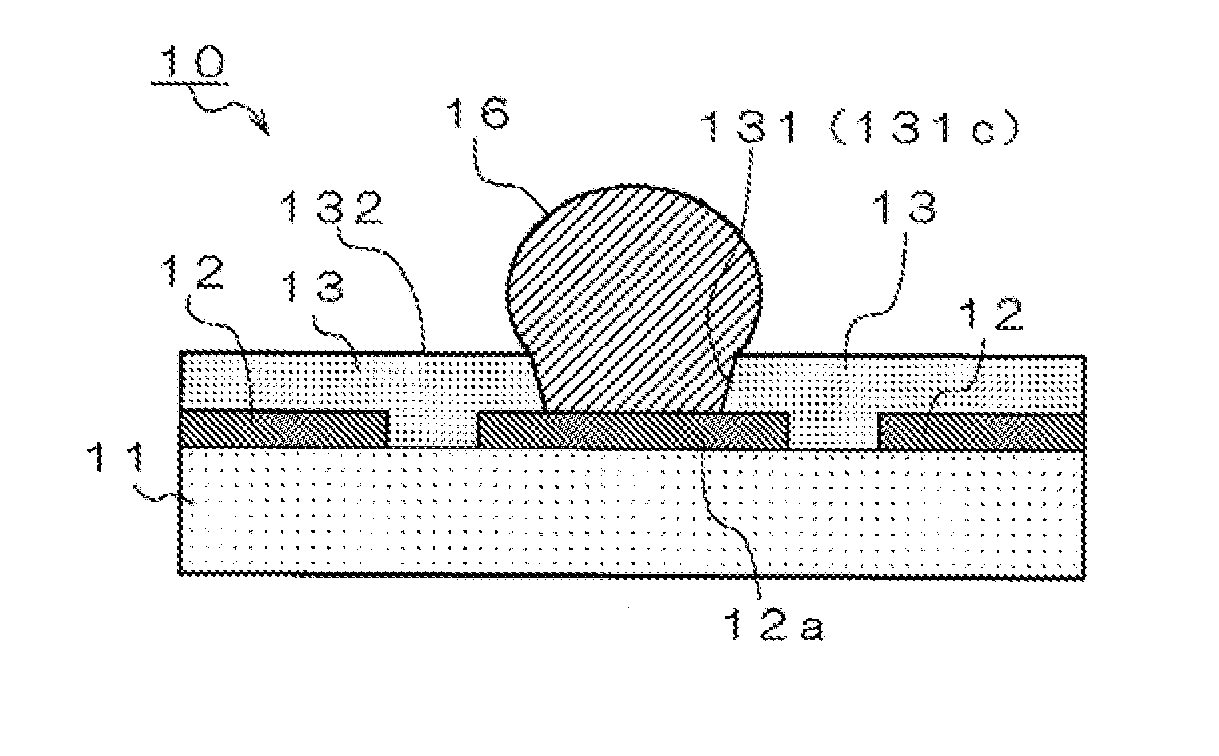

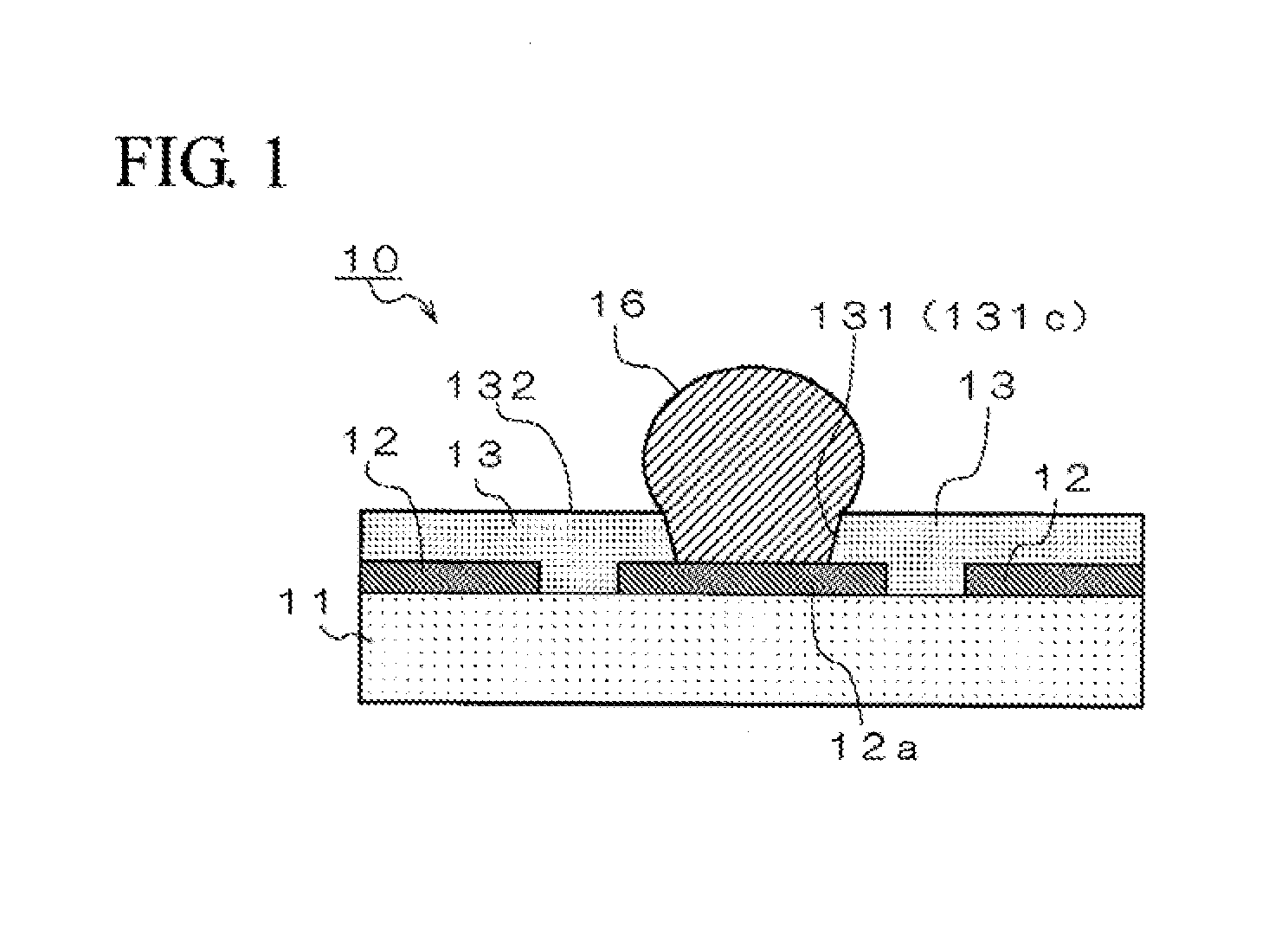

Wiring board and method of manufacturing the same

InactiveUS20120152598A1Efficiently obtainedImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesResistElectrical conductor

Disclosed is a method for manufacturing a wiring board including a conductor layer, a solder resist layer laminated on the conductor layer, and a conductor post to be electrically connected to a conductor layer which is disposed in a lower portion of a through-hole provided in the solder resist layer, the method including a through-hole boring process of boring the through-hole in the solder resist layer containing a thermosetting resin to expose the conductor layer within the through-hole; a first conductor part forming process of forming a first conductor part composed mainly of copper within the through-hole; and a second conductor part forming process of forming a second conductor part composed mainly of tin, copper, or a solder on the first conductor part, in this order.

Owner:NGK SPARK PLUG CO LTD

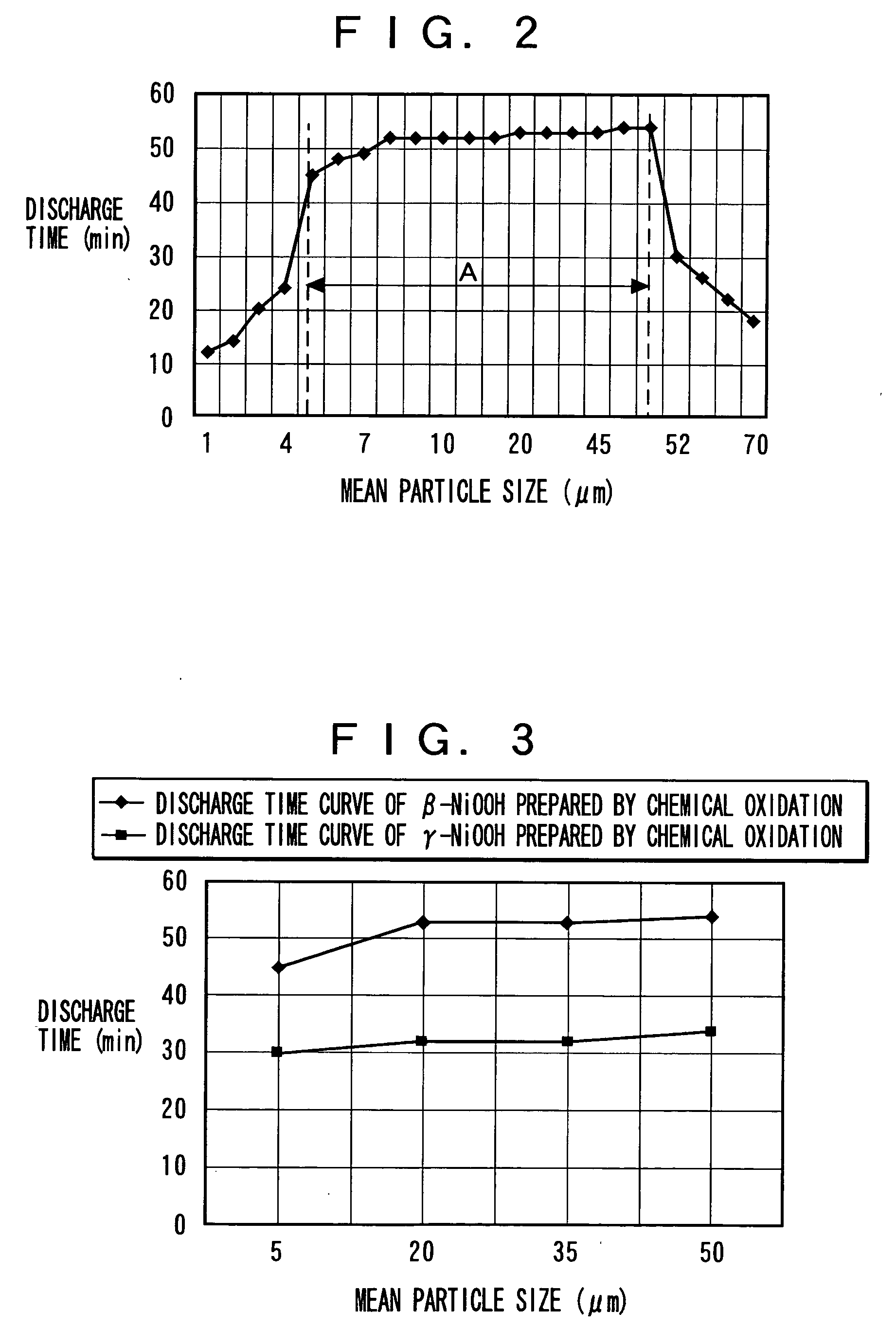

Alkaline battery

InactiveUS20050008936A1Excellent cycle characteristicsReduce conductivityElectrode carriers/collectorsAlkaline accumulator electrodesPotassium hydroxideEngineering

The present invention provides an alkaline battery suitable for use as a primary or secondary battery as a power source of electronic appliances. The battery is excellent in discharge characteristics under a heavy load and in cycle characteristics. The alkaline battery (100) comprises a cathode mix (3) containing β-nickel oxy-hydroxide, an anode mix (5) containing zinc as a main component of anode active material, and an alkali solution as an electrolyte, wherein the cathode mix (3) includes a mixture of β-nickel oxy-hydroxide, graphite powder, and a potassium hydroxide solution in a given weight ratio. The β-nickel oxy-hydroxide is prepared by chemical oxidation and has an approximately spherical shape of particle with a mean particle size in the range of 5 to 50 μm.

Owner:SONY CORP

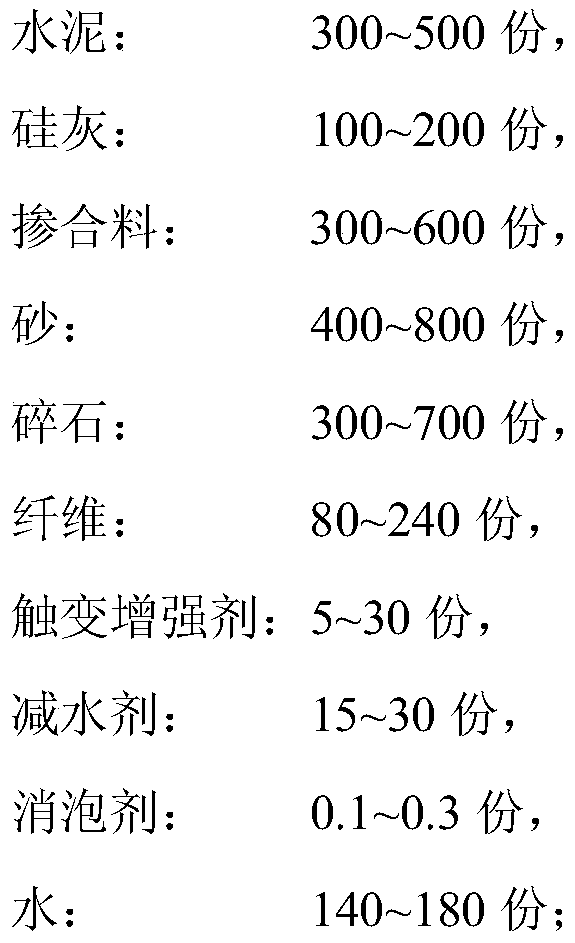

Low-viscosity and easy-pumping ultrahigh performance concrete and preparation method thereof

The invention discloses a low-viscosity and easy-pumping ultrahigh performance concrete and a preparation method thereof. The concrete comprises, by mass, 300-500 parts of cement, 100-200 parts of silica fume, 300-600 parts of an admixture, 400-800 parts of sands, 300-700 parts of crushed stones, 80-240 parts of fibers, 5-30 parts of a thixotropic enhancer, 15-30 parts of a water reducer, 0.1-0.3part of an antifoaming agent and 140-180 parts of water. The low-viscosity and easy-pumping ultrahigh performance concrete of the invention has a high fluidity and a low viscosity, the pumping resistance is only 0.015-0.025 MPa / m, and the compressive strength after 28 d standard curing is 180 MPa or above. In addition, the low-viscosity and easy-pumping ultrahigh performance concrete of the present invention has a typical low cement content, so the shrinkage of the ultrahigh performance concrete is significantly reduced, the use amount of the cement is significantly reduced, and the environmental pollution is reduced.

Owner:JIANGSU SOBUTE NEW MATERIALS +1

Semiconductor package

InactiveUS7378732B2High-density packagingHigh-density packaging and easilySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSemiconductor device

A plurality of semiconductor packages is collectively fabricated on a wafer in a batch process and the wafer is then diced to obtain discrete semiconductor packages. The semiconductor package is a stacked body formed by bonding two or more semiconductor devices. Each semiconductor device comprises a substrate and a device pattern formed on a surface of the substrate. The semiconductor devices are stacked in such a fashion that a device pattern surface of the lower semiconductor device faces a non-device pattern surface of the semiconductor device stacked on the same.

Owner:SHINKO ELECTRIC IND CO LTD

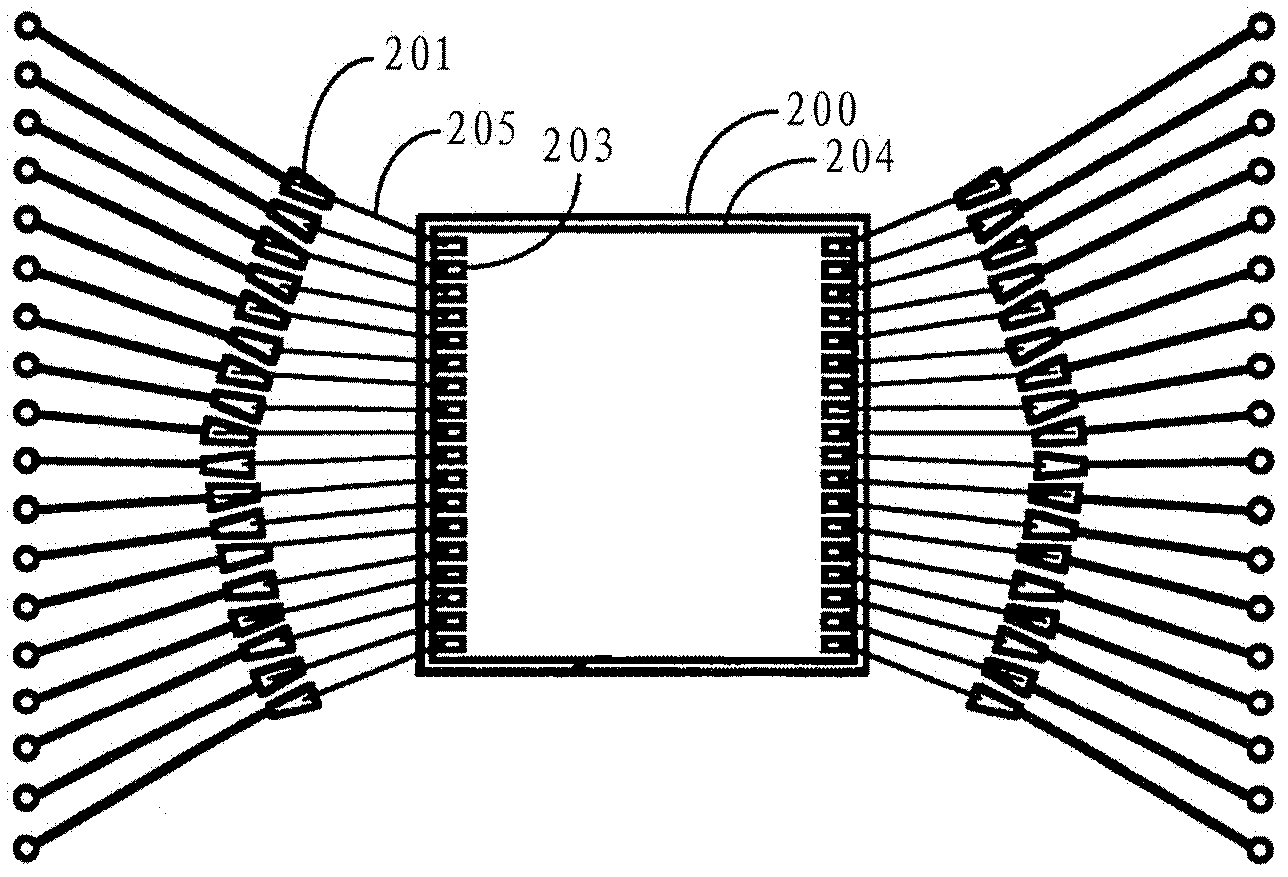

Staggered-pins structure for substrate

ActiveCN102610584AHigh density packagingSmall sizeSemiconductor/solid-state device detailsSolid-state devicesExternal circuitEngineering

The invention discloses a staggered-pins structure for a substrate; in the staggered-pins structure for the substrate, a solder pad arranged on a chip of the substrate is electrically connected with a pin by a bonding lead; the pin is connected to an external circuit through a circuit line, wherein each pin is in regular hexagon shape; a plurality of pins are staggered along an arrangement direction of the solder pad on the chip; according to the staggered-pins structure for the substrate, the space of the pin part can be utilized in maximum so as to realize high-density encapsulation; in addition, the size of an encapsulation piece can be reduced.

Owner:SAMSUNG SEMICON CHINA RES & DEV +1