Manufacturing method of array substrate as well as array substrate and display device

An array substrate and substrate technology, applied in the field of liquid crystal display, can solve the problems of increased manufacturing time and manufacturing costs, and achieve the effects of reducing signal delay, reducing parasitic capacitance, and reducing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

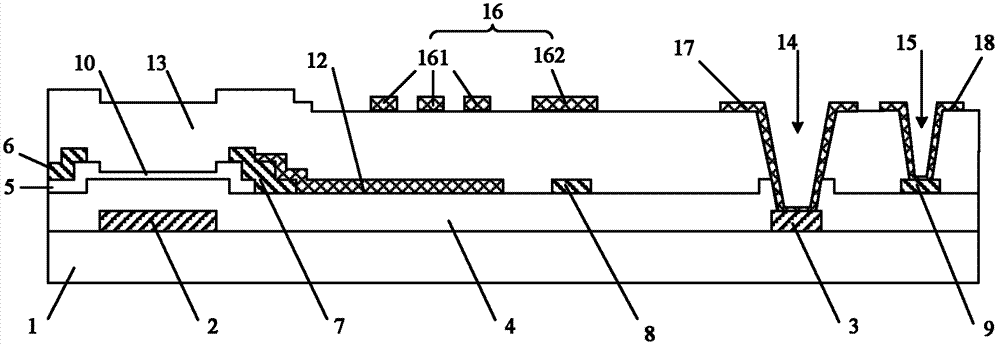

Embodiment 1

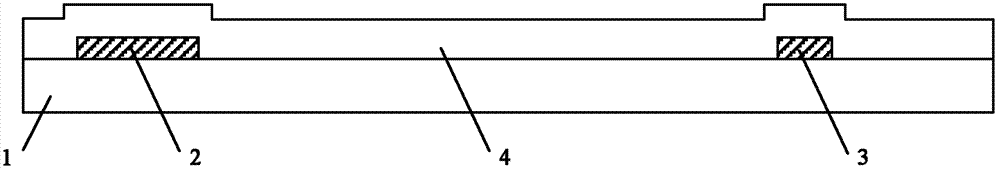

[0084] Step S11, providing a substrate, forming gate lines, gate electrodes and gate pads on the substrate;

[0085] First, sputtering, thermal evaporation or other film-forming methods can be used to form a gate metal layer on a glass substrate or other types of transparent substrates. The gate metal layer can be made of chromium (Cr), molybdenum (Mo), aluminum (Al), Copper (Cu), tungsten (W), neodymium (Nd) and their alloys, and the gate metal layer can be one or more layers; then, a photoresist is formed on the gate metal layer; secondly, a patterned The mask plate exposes and develops the photoresist to form a photoresist mask; again, the photoresist mask is used to etch the gate metal layer to form patterns of gate lines, gate electrodes and gate pads; finally, Strip remaining photoresist. It should be noted that, in this step, while forming the patterns of the gate lines, gate electrodes and gate pads, the common electrode lines can also be formed.

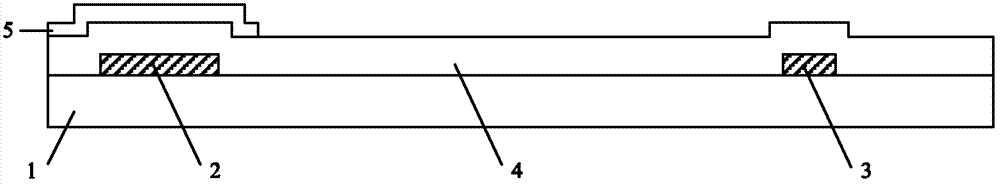

[0086] Step S12, f...

Embodiment 2

[0109] Step S21, providing a substrate, and forming gate lines, gate electrodes and gate pads on the substrate;

[0110] First, sputtering, thermal evaporation or other film-forming methods can be used to form a gate metal layer on a glass substrate or other types of transparent substrates. The gate metal layer can be made of chromium (Cr), molybdenum (Mo), aluminum (Al), Copper (Cu), tungsten (W), neodymium (Nd) and their alloys, and the gate metal layer can be one or more layers; then, a photoresist is formed on the gate metal layer; secondly, a patterned The mask plate exposes and develops the photoresist to form a photoresist mask; again, the photoresist mask is used to etch the gate metal layer to form patterns of gate lines, gate electrodes and gate pads; finally, Strip remaining photoresist. It should be noted that, in this step, while forming the patterns of the gate lines, gate electrodes and gate pads, the common electrode lines can also be formed.

[0111] Step S2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More