VLSI layout planning centralized constrain implementing method

An implementation method and centralized technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of difficult manual layout, difficulty in meeting various constraints at the same time, etc., to avoid convergence reduction and save the conversion process. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] ①. Read the layout input information, store the area, length, width, type, connection and constraint information of each module;

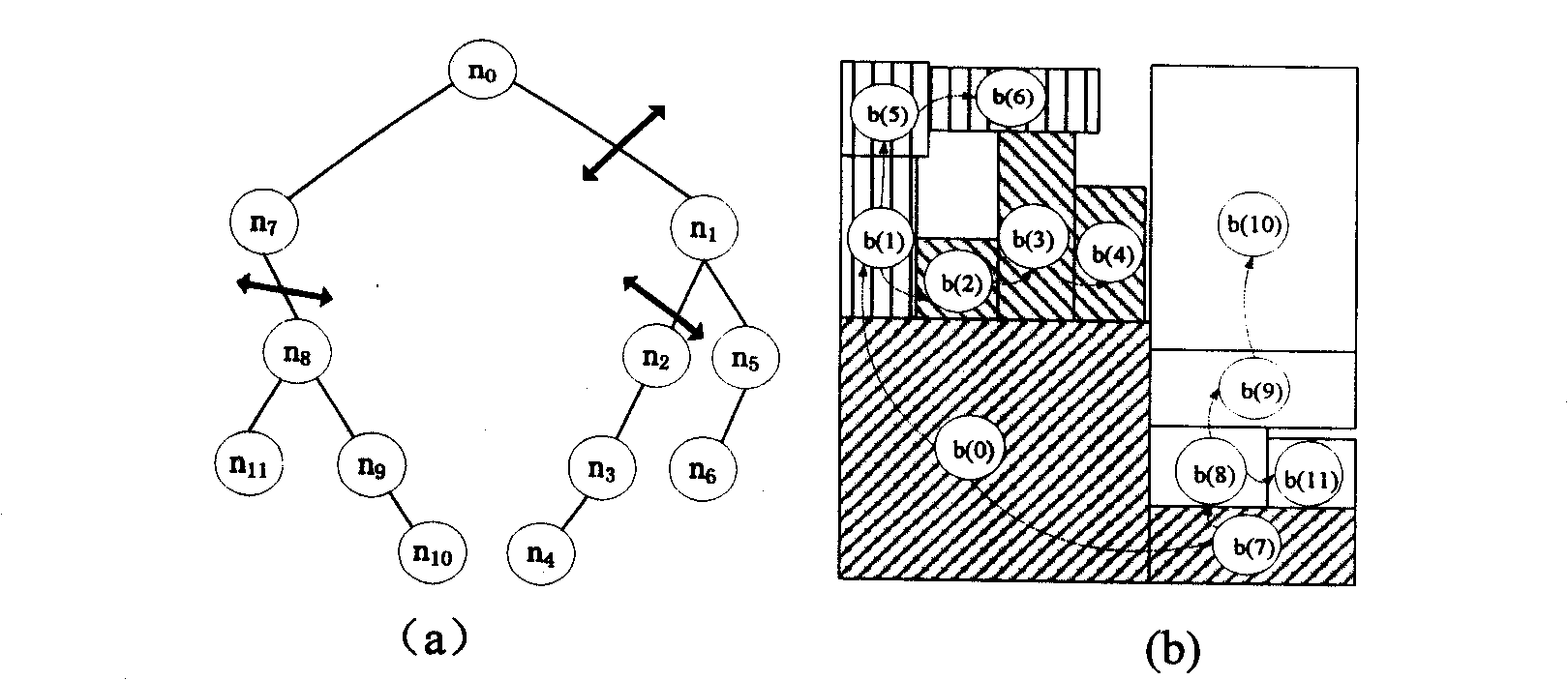

[0046] ②. Construct the allowable initial layout according to the requirements of centralized constraints: first connect the modules involved in each constraint into subtrees, and divide the modules not involved in constraints into subtrees separately, and then connect the subtrees to form an overall B*-tree. ;

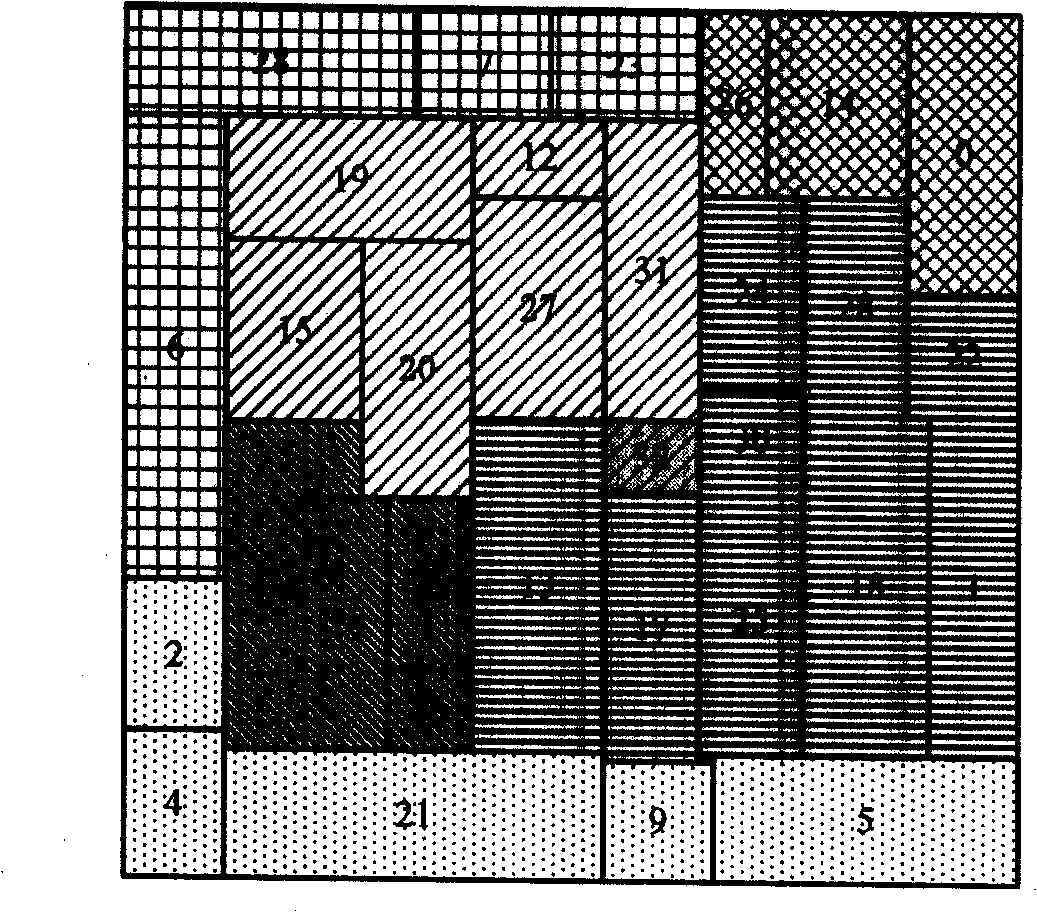

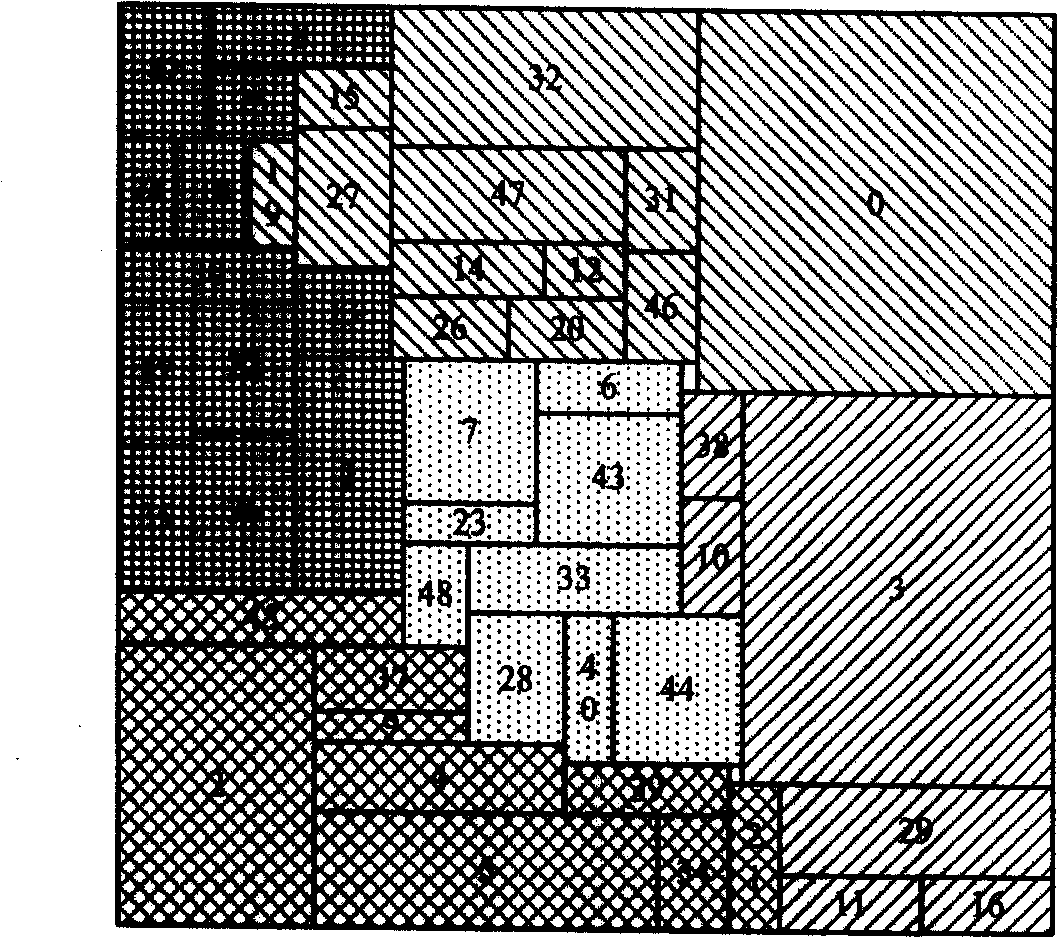

[0047] ③. The simulated annealing algorithm is used to optimize the global factors such as area.

[0048] The basic operations in simulated annealing are rotation, exchange, deletion and insertion. The operation method is: (1) Rotation operation: exchange the length and width of a certain module. (2) When the basic operations of exchange, deletion, and insertion are all performed on internal nodes of the same subtree, that is, when two nodes are exchanged or deleted nodes and inserted nodes are performed in the same subtree, such ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More