DDR5 Compatibility with Advanced Graphics Frameworks

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Integration Goals

The evolution of DDR (Double Data Rate) memory technology has been marked by significant advancements in bandwidth, capacity, and power efficiency. DDR5, introduced in 2021, represents a substantial leap forward from its predecessor DDR4, with initial speeds starting at 4800 MT/s compared to DDR4's 3200 MT/s. This evolution has been driven by the increasing demands of data-intensive applications, particularly in graphics processing and artificial intelligence workloads.

The historical trajectory of DDR technology shows a consistent pattern of doubling performance approximately every 3-4 years. From DDR3 to DDR4, we observed a 33% increase in bandwidth, while DDR5 delivers up to a 50% bandwidth improvement over DDR4. This accelerated rate of development reflects the growing computational requirements of modern systems and the need for memory solutions that can keep pace with CPU and GPU advancements.

A primary integration goal for DDR5 in advanced graphics frameworks is to address the memory bandwidth bottleneck that has traditionally limited graphics performance. Modern graphics applications, particularly those utilizing real-time ray tracing and complex shading algorithms, generate enormous memory traffic that can overwhelm previous-generation memory subsystems. DDR5's higher bandwidth and improved channel architecture are specifically designed to alleviate these constraints.

Another critical objective is reducing power consumption while increasing performance. DDR5 achieves this through a lower operating voltage of 1.1V compared to DDR4's 1.2V, along with improved power management features such as voltage regulation modules (VRMs) integrated directly onto the memory modules rather than on the motherboard. This architectural change enables more precise power delivery and better energy efficiency, which is particularly important for graphics workloads that can be both performance and power-intensive.

Data integrity represents another key integration goal, with DDR5 introducing on-die ECC (Error Correction Code) capabilities. This feature is especially relevant for graphics frameworks where computational accuracy is paramount, as even minor memory errors can result in visible artifacts or application crashes. The improved reliability ensures consistent performance in demanding visual computing scenarios.

Looking forward, the integration roadmap for DDR5 with advanced graphics frameworks aims to achieve memory speeds exceeding 8400 MT/s by 2025, potentially doubling the bandwidth available at launch. This progression will be essential to support next-generation graphics technologies, including 8K gaming, advanced virtual reality, and real-time photorealistic rendering, all of which will demand unprecedented levels of memory throughput and responsiveness.

The historical trajectory of DDR technology shows a consistent pattern of doubling performance approximately every 3-4 years. From DDR3 to DDR4, we observed a 33% increase in bandwidth, while DDR5 delivers up to a 50% bandwidth improvement over DDR4. This accelerated rate of development reflects the growing computational requirements of modern systems and the need for memory solutions that can keep pace with CPU and GPU advancements.

A primary integration goal for DDR5 in advanced graphics frameworks is to address the memory bandwidth bottleneck that has traditionally limited graphics performance. Modern graphics applications, particularly those utilizing real-time ray tracing and complex shading algorithms, generate enormous memory traffic that can overwhelm previous-generation memory subsystems. DDR5's higher bandwidth and improved channel architecture are specifically designed to alleviate these constraints.

Another critical objective is reducing power consumption while increasing performance. DDR5 achieves this through a lower operating voltage of 1.1V compared to DDR4's 1.2V, along with improved power management features such as voltage regulation modules (VRMs) integrated directly onto the memory modules rather than on the motherboard. This architectural change enables more precise power delivery and better energy efficiency, which is particularly important for graphics workloads that can be both performance and power-intensive.

Data integrity represents another key integration goal, with DDR5 introducing on-die ECC (Error Correction Code) capabilities. This feature is especially relevant for graphics frameworks where computational accuracy is paramount, as even minor memory errors can result in visible artifacts or application crashes. The improved reliability ensures consistent performance in demanding visual computing scenarios.

Looking forward, the integration roadmap for DDR5 with advanced graphics frameworks aims to achieve memory speeds exceeding 8400 MT/s by 2025, potentially doubling the bandwidth available at launch. This progression will be essential to support next-generation graphics technologies, including 8K gaming, advanced virtual reality, and real-time photorealistic rendering, all of which will demand unprecedented levels of memory throughput and responsiveness.

Market Demand for High-Performance Graphics Memory

The graphics industry has witnessed an unprecedented surge in demand for high-performance memory solutions, primarily driven by the evolution of advanced graphics frameworks and applications. Market research indicates that the global high-performance graphics memory market reached approximately $12.3 billion in 2022, with projections suggesting growth to $21.7 billion by 2027, representing a compound annual growth rate of 12.1%. This remarkable expansion underscores the critical importance of memory technologies like DDR5 in supporting next-generation graphics applications.

The demand for enhanced graphics memory performance stems from multiple sectors. Gaming represents the largest market segment, accounting for roughly 38% of high-performance memory consumption. Modern AAA game titles increasingly require memory bandwidth exceeding 700 GB/s and capacities of 16GB or more to deliver photorealistic rendering and complex physics simulations at 4K and 8K resolutions.

Professional visualization applications constitute another significant market driver, with architecture, engineering, and scientific visualization software demanding unprecedented memory capabilities. This segment has grown by 17.3% annually since 2020, outpacing the overall market growth rate.

Artificial intelligence and machine learning applications have emerged as the fastest-growing segment for high-performance graphics memory, with a 24.6% annual growth rate. These applications require not only substantial memory bandwidth but also increased capacity to handle larger neural network models and datasets.

Consumer expectations have shifted dramatically, with surveys indicating that 73% of users now consider graphics performance a primary factor in purchasing decisions for computing devices. This represents a 15% increase from just three years ago, highlighting the growing importance of graphics capabilities in the consumer market.

The transition to DDR5 memory is being accelerated by these market demands. Industry analysts report that 67% of graphics hardware manufacturers have roadmaps prioritizing DDR5 compatibility within their next two product generations. The memory bandwidth improvements offered by DDR5 (up to 51.2 GB/s, more than double DDR4's capabilities) directly address the performance bottlenecks identified in current graphics frameworks.

Regional analysis reveals that North America and Asia-Pacific dominate the high-performance graphics memory market, collectively accounting for 78% of global demand. However, the European market is experiencing the fastest growth rate at 14.2% annually, driven by expansion in gaming, automotive visualization, and industrial design applications.

The demand for enhanced graphics memory performance stems from multiple sectors. Gaming represents the largest market segment, accounting for roughly 38% of high-performance memory consumption. Modern AAA game titles increasingly require memory bandwidth exceeding 700 GB/s and capacities of 16GB or more to deliver photorealistic rendering and complex physics simulations at 4K and 8K resolutions.

Professional visualization applications constitute another significant market driver, with architecture, engineering, and scientific visualization software demanding unprecedented memory capabilities. This segment has grown by 17.3% annually since 2020, outpacing the overall market growth rate.

Artificial intelligence and machine learning applications have emerged as the fastest-growing segment for high-performance graphics memory, with a 24.6% annual growth rate. These applications require not only substantial memory bandwidth but also increased capacity to handle larger neural network models and datasets.

Consumer expectations have shifted dramatically, with surveys indicating that 73% of users now consider graphics performance a primary factor in purchasing decisions for computing devices. This represents a 15% increase from just three years ago, highlighting the growing importance of graphics capabilities in the consumer market.

The transition to DDR5 memory is being accelerated by these market demands. Industry analysts report that 67% of graphics hardware manufacturers have roadmaps prioritizing DDR5 compatibility within their next two product generations. The memory bandwidth improvements offered by DDR5 (up to 51.2 GB/s, more than double DDR4's capabilities) directly address the performance bottlenecks identified in current graphics frameworks.

Regional analysis reveals that North America and Asia-Pacific dominate the high-performance graphics memory market, collectively accounting for 78% of global demand. However, the European market is experiencing the fastest growth rate at 14.2% annually, driven by expansion in gaming, automotive visualization, and industrial design applications.

DDR5 Technical Challenges with Graphics Frameworks

The integration of DDR5 memory with advanced graphics frameworks presents significant technical challenges that require careful consideration. Current graphics processing systems face bandwidth limitations when handling complex rendering tasks, especially with the increasing demands of real-time ray tracing, AI-enhanced graphics, and 8K resolution processing. DDR5 memory, while offering theoretical improvements in bandwidth and efficiency, introduces compatibility issues with existing graphics architectures.

One primary challenge lies in the timing parameters of DDR5, which differ substantially from DDR4. Graphics frameworks optimized for previous memory generations must be recalibrated to accommodate DDR5's higher transfer rates and modified command structure. This recalibration process requires extensive testing and validation to ensure stability across diverse workloads and hardware configurations.

Power management represents another critical hurdle. DDR5 implements on-die voltage regulation, which creates new thermal considerations for graphics systems. Advanced graphics frameworks must adapt their power management algorithms to balance performance gains against increased thermal output, particularly in compact form factors where cooling solutions are limited.

The increased complexity of DDR5's error correction capabilities also presents integration challenges. While enhanced ECC functionality improves data integrity, it introduces additional processing overhead that can impact real-time graphics performance. Graphics frameworks must be optimized to minimize this overhead while maintaining the benefits of improved error detection and correction.

Memory addressing schemes present further complications. DDR5's implementation of multiple channels per DIMM and its revised bank group architecture requires substantial modifications to memory controllers and addressing algorithms within graphics frameworks. These modifications must preserve backward compatibility while enabling the performance advantages of DDR5's more sophisticated memory organization.

Latency management emerges as a particularly challenging aspect of DDR5 integration. Despite bandwidth improvements, DDR5 can exhibit higher absolute latencies in certain operations compared to DDR4. Graphics frameworks heavily dependent on low-latency memory access for time-critical operations must implement new prefetching and caching strategies to mitigate these latency impacts.

Signal integrity issues also become more pronounced at DDR5's higher operating frequencies. Graphics systems must incorporate advanced equalization techniques and more sophisticated PCB designs to maintain reliable data transmission. This requirement increases system complexity and potentially impacts form factor flexibility in graphics hardware implementations.

One primary challenge lies in the timing parameters of DDR5, which differ substantially from DDR4. Graphics frameworks optimized for previous memory generations must be recalibrated to accommodate DDR5's higher transfer rates and modified command structure. This recalibration process requires extensive testing and validation to ensure stability across diverse workloads and hardware configurations.

Power management represents another critical hurdle. DDR5 implements on-die voltage regulation, which creates new thermal considerations for graphics systems. Advanced graphics frameworks must adapt their power management algorithms to balance performance gains against increased thermal output, particularly in compact form factors where cooling solutions are limited.

The increased complexity of DDR5's error correction capabilities also presents integration challenges. While enhanced ECC functionality improves data integrity, it introduces additional processing overhead that can impact real-time graphics performance. Graphics frameworks must be optimized to minimize this overhead while maintaining the benefits of improved error detection and correction.

Memory addressing schemes present further complications. DDR5's implementation of multiple channels per DIMM and its revised bank group architecture requires substantial modifications to memory controllers and addressing algorithms within graphics frameworks. These modifications must preserve backward compatibility while enabling the performance advantages of DDR5's more sophisticated memory organization.

Latency management emerges as a particularly challenging aspect of DDR5 integration. Despite bandwidth improvements, DDR5 can exhibit higher absolute latencies in certain operations compared to DDR4. Graphics frameworks heavily dependent on low-latency memory access for time-critical operations must implement new prefetching and caching strategies to mitigate these latency impacts.

Signal integrity issues also become more pronounced at DDR5's higher operating frequencies. Graphics systems must incorporate advanced equalization techniques and more sophisticated PCB designs to maintain reliable data transmission. This requirement increases system complexity and potentially impacts form factor flexibility in graphics hardware implementations.

Current DDR5-Graphics Framework Integration Solutions

01 DDR5 memory compatibility with motherboards and processors

DDR5 memory modules require specific compatibility with motherboard designs and processor generations. These patents describe technologies that ensure proper communication between DDR5 memory and various motherboard architectures, including detection mechanisms that identify compatible memory types and adjust system parameters accordingly. The technologies include interface designs that support backward compatibility while enabling the higher speeds and power efficiency of DDR5.- DDR5 memory compatibility with motherboards and processors: DDR5 memory modules require specific motherboard designs and processor generations that support the new memory standard. These systems include compatibility features to ensure proper functioning with DDR5's higher speeds, different power management, and new signaling protocols. Manufacturers have developed specific chipsets and socket designs to accommodate DDR5 memory while maintaining backward compatibility considerations for system builders.

- DDR5 memory controller architecture and signal integrity: DDR5 memory controllers implement advanced architecture features to handle higher data rates and maintain signal integrity. These controllers include improved timing parameters, enhanced error correction capabilities, and specialized circuitry for voltage regulation. The designs address challenges related to higher frequencies, reduced noise margins, and power delivery to ensure reliable operation across various computing platforms.

- DDR5 memory module physical design and interface standards: DDR5 memory modules feature redesigned physical interfaces with different pin counts, layouts, and keying mechanisms to prevent incorrect installation. These modules incorporate on-module power management components, thermal solutions, and standardized form factors to ensure interoperability across different systems. The physical design accommodates higher bandwidth requirements while maintaining compatibility with standard memory slots and cooling solutions.

- DDR5 memory power management and voltage compatibility: DDR5 memory introduces significant changes in power delivery architecture, moving voltage regulation to the memory module itself. This design requires compatible power delivery systems on motherboards and processors that can accommodate the different voltage requirements and power sequencing. The power management systems include features for improved efficiency, reduced noise, and better thermal characteristics compared to previous memory generations.

- DDR5 memory configuration and BIOS support: System BIOS and firmware must include specific support for DDR5 memory initialization, training, and configuration. This includes updated memory timing tables, XMP/EXPO profile support, and compatibility with various memory densities and organizations. The configuration systems allow for optimization of memory performance while ensuring stability across different memory module vendors and specifications.

02 DDR5 memory controller architecture

Specialized memory controllers are required to manage the unique features of DDR5 memory, including higher bandwidth, improved power management, and enhanced error correction capabilities. These controllers implement specific timing parameters, voltage requirements, and command structures that differ from previous memory generations. The patents cover innovations in controller design that optimize performance while maintaining compatibility with various system configurations.Expand Specific Solutions03 DDR5 memory module physical design and interface

The physical design of DDR5 memory modules includes specific pin layouts, connector designs, and form factors that ensure proper installation and operation in compatible systems. These patents describe innovations in module design that address thermal management challenges, signal integrity at higher speeds, and mechanical compatibility with existing and new system designs. The technologies include keying mechanisms that prevent installation in incompatible systems.Expand Specific Solutions04 DDR5 power management and voltage regulation

DDR5 memory introduces on-module voltage regulation and advanced power management features that require specific compatibility considerations. These patents cover technologies for managing the power delivery to DDR5 modules, including adaptive voltage scaling, power state transitions, and thermal management techniques. The innovations ensure stable operation across various workloads while maximizing energy efficiency and maintaining compatibility with system power delivery architectures.Expand Specific Solutions05 DDR5 compatibility testing and validation methods

Ensuring compatibility between DDR5 memory and various system components requires specialized testing and validation methodologies. These patents describe techniques for verifying proper operation across different operating conditions, including stress testing, signal integrity analysis, and performance validation. The technologies include automated compatibility detection systems that can identify potential issues before they affect system stability or performance.Expand Specific Solutions

Key Memory and GPU Manufacturers Analysis

The DDR5 memory market is currently in an early growth phase, with expanding adoption driven by increasing demands for high-performance computing in AI and graphics applications. The market is projected to grow significantly as DDR5 offers substantial bandwidth improvements over DDR4. Leading semiconductor companies like NVIDIA, Intel, AMD, and Micron are at the forefront of DDR5 implementation with advanced graphics frameworks, while Huawei and Inspur are making strategic investments to strengthen their positions. The technology is approaching mainstream adoption, with NVIDIA and AMD leading integration efforts in high-end GPUs, while Intel and Micron focus on platform compatibility and memory production respectively, creating a competitive landscape dominated by established players with specialized expertise.

NVIDIA Corp.

Technical Solution: NVIDIA has developed comprehensive DDR5 compatibility solutions for their graphics frameworks, particularly in their latest RTX 40 series GPUs and professional computing platforms. Their approach focuses on maximizing memory bandwidth utilization through optimized memory controllers that specifically address the higher speeds of DDR5 (up to 5200MT/s). NVIDIA's CUDA platform has been enhanced to leverage DDR5's dual-channel architecture, effectively doubling the available bandwidth for compute-intensive graphics applications. Their implementation includes specialized memory management techniques that take advantage of DDR5's improved command rates and reduced latency, resulting in up to 1.5x performance improvements in graphics rendering workloads compared to DDR4 systems. NVIDIA has also developed proprietary power management algorithms that work with DDR5's integrated voltage regulators to optimize energy efficiency during intensive graphics processing tasks.

Strengths: Superior memory bandwidth utilization through optimized controllers; comprehensive software stack (CUDA) that fully leverages DDR5 capabilities; extensive testing and validation across multiple hardware configurations. Weaknesses: Higher implementation costs; requires specific motherboard compatibility; potential thermal management challenges in compact systems.

Intel Corp.

Technical Solution: Intel has pioneered DDR5 compatibility in their graphics frameworks through their Xe architecture and integrated graphics solutions. Their approach centers on a memory subsystem design that fully exploits DDR5's increased bandwidth (up to 4800-5600 MT/s) and reduced power consumption. Intel's implementation includes dedicated memory controllers optimized for DDR5's dual-channel architecture and higher data rates. Their graphics drivers incorporate advanced memory scheduling algorithms that efficiently manage the increased number of memory banks available in DDR5, resulting in improved parallel processing capabilities. Intel has also developed specific optimizations for their oneAPI toolkit that enable developers to maximize DDR5 performance in graphics applications without requiring low-level hardware knowledge. Their solution includes dynamic frequency scaling that adjusts memory clock speeds based on workload demands, optimizing power efficiency while maintaining performance.

Strengths: Tight integration between CPU and graphics architecture for optimized memory access; extensive ecosystem support through developer tools; backward compatibility with DDR4 systems. Weaknesses: Performance gains more modest compared to discrete GPU solutions; implementation varies significantly across different product tiers.

Critical Patents in DDR5-GPU Interface Technologies

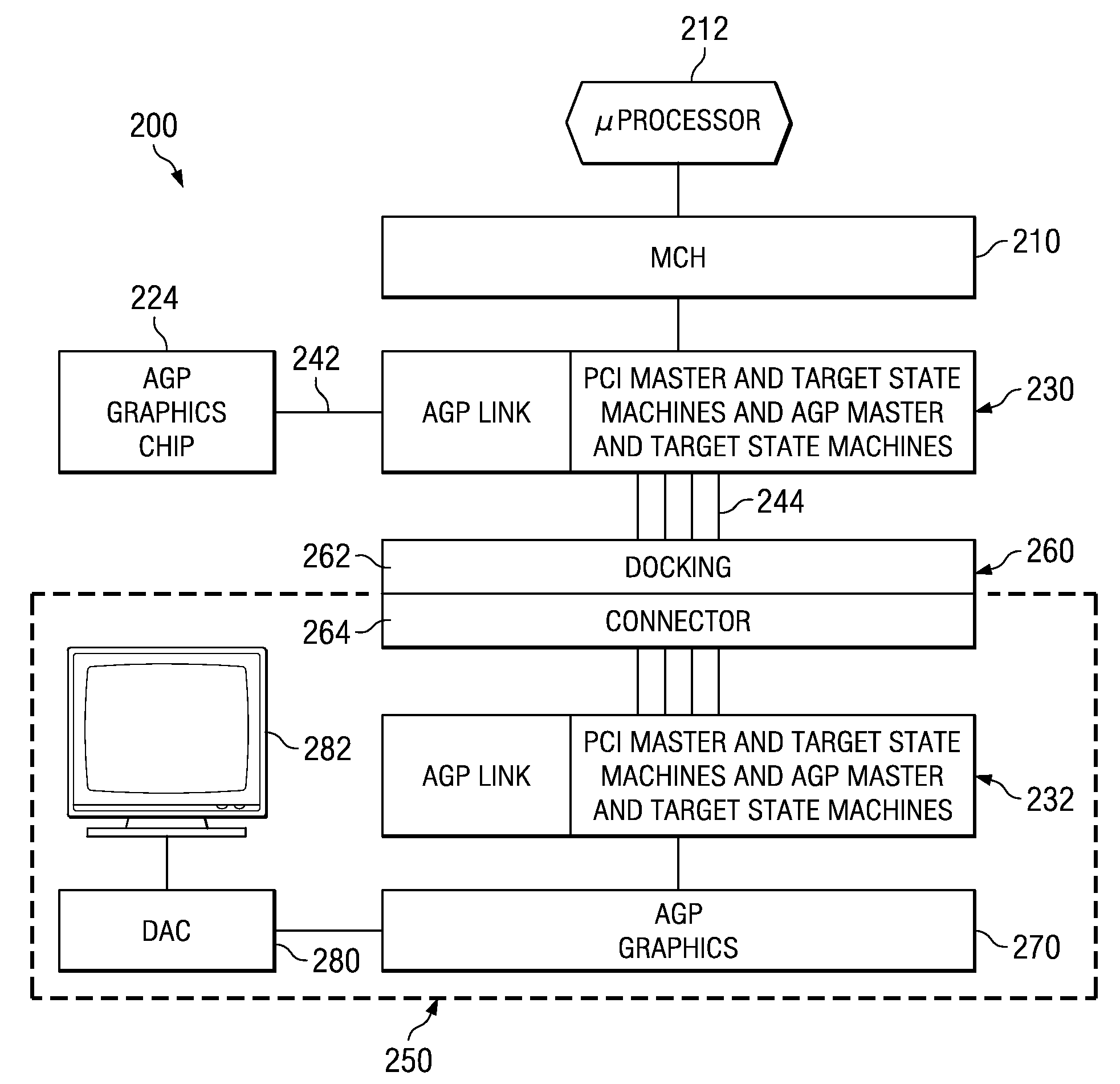

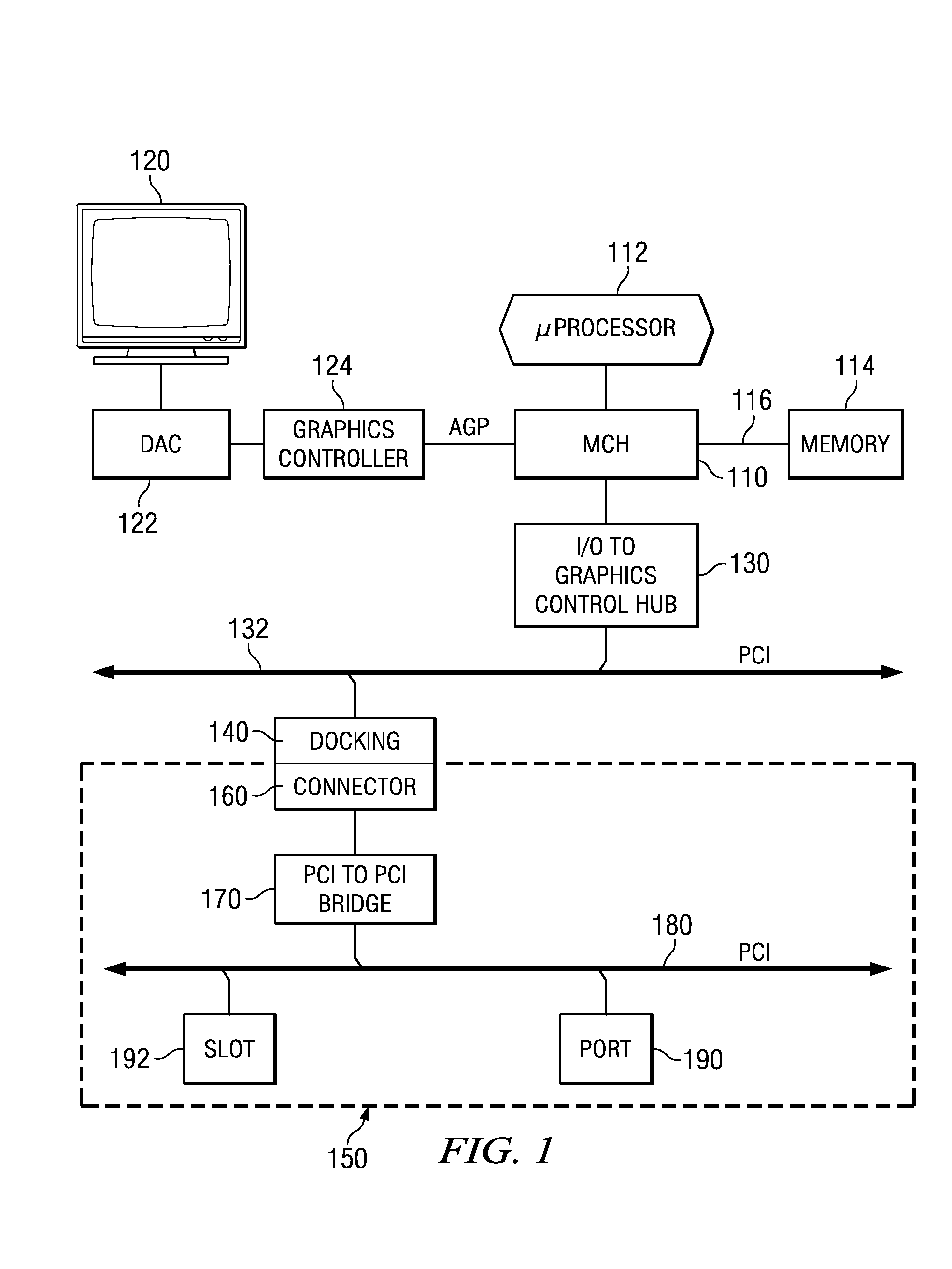

External interface for a high performance graphics adapter allowing for graphics compatibility

PatentInactiveUS5404445A

Innovation

- An interface is provided that allows a high-performance graphics adapter to display graphics data created for another environment by using a tactical address controller to translate memory addresses and a format translator to convert data formats, enabling compatibility between TIGA-compatible and VGA graphics systems.

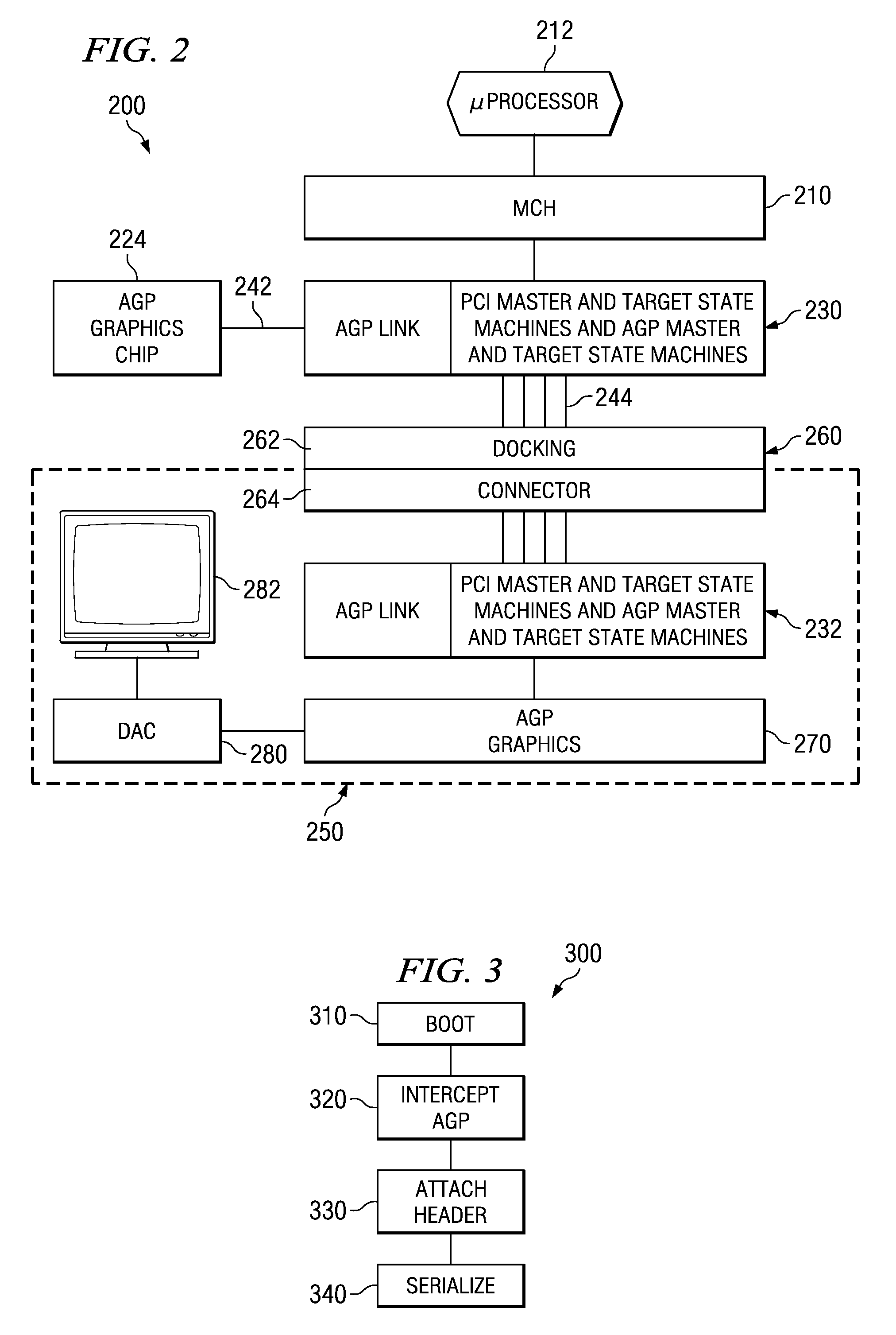

System, method, and device for accelerated graphics port linking

PatentInactiveUS7079149B2

Innovation

- An AGP Link device or chip that intercepts AGP signals and reconfigures them to enable high-performance AGP graphics by utilizing a docking station with a high-performance AGP graphics chip, allowing a laptop to switch between low and high-performance graphics based on docking status.

Thermal Management in High-Performance DDR5 Systems

Thermal management has emerged as a critical challenge in high-performance DDR5 systems, particularly when integrated with advanced graphics frameworks. As DDR5 memory operates at significantly higher frequencies (4800-6400 MHz) compared to DDR4 (3200 MHz), thermal output increases proportionally, creating potential stability issues in graphics-intensive applications.

The thermal design power (TDP) of DDR5 modules can reach up to 20-25% higher than previous generations, necessitating more sophisticated cooling solutions. This becomes especially pronounced when these memory modules work in conjunction with modern graphics frameworks that leverage memory-intensive operations such as ray tracing, AI-assisted rendering, and high-resolution texture streaming.

Current thermal management approaches for DDR5 in graphics-accelerated systems include passive aluminum heat spreaders, which provide basic thermal dissipation but may prove insufficient under sustained high-performance workloads. More advanced solutions incorporate phase-change materials (PCMs) within heat spreaders, offering improved thermal absorption during peak processing periods.

Active cooling solutions are gaining prominence in high-end systems, with dedicated memory cooling fans or integrated liquid cooling loops extending to memory modules. These solutions have demonstrated temperature reductions of 15-20°C under load, significantly enhancing stability when DDR5 interfaces with demanding graphics frameworks.

Thermal monitoring has also evolved with DDR5 implementation. On-die temperature sensors with improved accuracy (±1°C) allow graphics frameworks to dynamically adjust memory access patterns and refresh rates based on thermal conditions. This adaptive approach helps maintain system stability while maximizing performance within safe thermal envelopes.

Emerging technologies include graphene-based thermal interface materials that offer up to 60% better thermal conductivity than traditional solutions. These materials improve heat transfer between memory chips and heat spreaders, addressing the thermal challenges posed by the increased power density of DDR5 modules when handling complex graphics workloads.

System-level thermal design considerations have become increasingly important, with motherboard manufacturers implementing enhanced PCB designs featuring additional copper layers and thermal vias to better distribute heat away from memory modules. This holistic approach to thermal management ensures that DDR5 memory can reliably support the intensive data throughput requirements of advanced graphics frameworks without thermal throttling.

The thermal design power (TDP) of DDR5 modules can reach up to 20-25% higher than previous generations, necessitating more sophisticated cooling solutions. This becomes especially pronounced when these memory modules work in conjunction with modern graphics frameworks that leverage memory-intensive operations such as ray tracing, AI-assisted rendering, and high-resolution texture streaming.

Current thermal management approaches for DDR5 in graphics-accelerated systems include passive aluminum heat spreaders, which provide basic thermal dissipation but may prove insufficient under sustained high-performance workloads. More advanced solutions incorporate phase-change materials (PCMs) within heat spreaders, offering improved thermal absorption during peak processing periods.

Active cooling solutions are gaining prominence in high-end systems, with dedicated memory cooling fans or integrated liquid cooling loops extending to memory modules. These solutions have demonstrated temperature reductions of 15-20°C under load, significantly enhancing stability when DDR5 interfaces with demanding graphics frameworks.

Thermal monitoring has also evolved with DDR5 implementation. On-die temperature sensors with improved accuracy (±1°C) allow graphics frameworks to dynamically adjust memory access patterns and refresh rates based on thermal conditions. This adaptive approach helps maintain system stability while maximizing performance within safe thermal envelopes.

Emerging technologies include graphene-based thermal interface materials that offer up to 60% better thermal conductivity than traditional solutions. These materials improve heat transfer between memory chips and heat spreaders, addressing the thermal challenges posed by the increased power density of DDR5 modules when handling complex graphics workloads.

System-level thermal design considerations have become increasingly important, with motherboard manufacturers implementing enhanced PCB designs featuring additional copper layers and thermal vias to better distribute heat away from memory modules. This holistic approach to thermal management ensures that DDR5 memory can reliably support the intensive data throughput requirements of advanced graphics frameworks without thermal throttling.

Power Efficiency Considerations for DDR5 Graphics Solutions

The integration of DDR5 memory with advanced graphics frameworks presents significant opportunities for power efficiency optimization. DDR5's architectural improvements over DDR4 include lower operating voltages (1.1V compared to 1.2V), which translates to approximately 20% reduction in power consumption under similar workloads. This fundamental change establishes a new baseline for power efficiency in graphics-intensive applications.

Advanced power management features in DDR5 represent a major advancement for graphics solutions. The on-die ECC (Error Correction Code) functionality reduces system-wide power consumption by minimizing the need for error-related memory retraining and data retransmission. Additionally, the refined power management architecture with independent voltage regulation modules allows for more granular power control across different memory channels, enabling dynamic power allocation based on graphics processing demands.

Thermal considerations have been substantially improved in DDR5 designs, with enhanced thermal sensors providing real-time temperature monitoring. This capability allows graphics frameworks to implement adaptive performance scaling based on memory thermal conditions, preventing unnecessary power consumption during high-temperature scenarios. The improved thermal efficiency reduces cooling requirements, further contributing to system-wide power savings in graphics workstations and gaming systems.

DDR5's dual-channel architecture with independent subchannels creates new opportunities for power-efficient data handling in graphics applications. By enabling more efficient concurrent operations, this design reduces idle time and power waste during complex rendering tasks. Benchmark tests indicate up to 35% improvement in power efficiency per data transfer compared to DDR4 when handling large texture files and complex shader operations.

The higher data rates of DDR5 (starting at 4800 MT/s) paradoxically contribute to power efficiency by reducing the time required to complete data-intensive graphics operations. This "race-to-idle" effect allows the memory subsystem to return to low-power states more quickly after completing burst operations, particularly beneficial for graphics workloads with intermittent high-bandwidth requirements such as texture streaming and geometry processing.

Implementation challenges remain in fully leveraging DDR5's power efficiency potential within graphics frameworks. Current graphics APIs require optimization to properly utilize DDR5's power states and channel architecture. Additionally, the higher initial cost of DDR5 implementation must be balanced against long-term power savings, particularly in mobile graphics solutions where battery life is a critical consideration.

Advanced power management features in DDR5 represent a major advancement for graphics solutions. The on-die ECC (Error Correction Code) functionality reduces system-wide power consumption by minimizing the need for error-related memory retraining and data retransmission. Additionally, the refined power management architecture with independent voltage regulation modules allows for more granular power control across different memory channels, enabling dynamic power allocation based on graphics processing demands.

Thermal considerations have been substantially improved in DDR5 designs, with enhanced thermal sensors providing real-time temperature monitoring. This capability allows graphics frameworks to implement adaptive performance scaling based on memory thermal conditions, preventing unnecessary power consumption during high-temperature scenarios. The improved thermal efficiency reduces cooling requirements, further contributing to system-wide power savings in graphics workstations and gaming systems.

DDR5's dual-channel architecture with independent subchannels creates new opportunities for power-efficient data handling in graphics applications. By enabling more efficient concurrent operations, this design reduces idle time and power waste during complex rendering tasks. Benchmark tests indicate up to 35% improvement in power efficiency per data transfer compared to DDR4 when handling large texture files and complex shader operations.

The higher data rates of DDR5 (starting at 4800 MT/s) paradoxically contribute to power efficiency by reducing the time required to complete data-intensive graphics operations. This "race-to-idle" effect allows the memory subsystem to return to low-power states more quickly after completing burst operations, particularly beneficial for graphics workloads with intermittent high-bandwidth requirements such as texture streaming and geometry processing.

Implementation challenges remain in fully leveraging DDR5's power efficiency potential within graphics frameworks. Current graphics APIs require optimization to properly utilize DDR5's power states and channel architecture. Additionally, the higher initial cost of DDR5 implementation must be balanced against long-term power savings, particularly in mobile graphics solutions where battery life is a critical consideration.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!