DDR5 Integration in 5G Network Infrastructures

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Integration Goals

The evolution of DDR (Double Data Rate) memory technology has been a critical factor in the advancement of computing systems across various industries. DDR5, as the latest generation, represents a significant leap forward in memory performance, efficiency, and capacity compared to its predecessors. In the context of 5G network infrastructures, the integration of DDR5 memory becomes particularly crucial due to the exponentially increasing data processing requirements and the need for lower latency in telecommunications equipment.

The historical progression from DDR4 to DDR5 marks a substantial improvement in several key parameters. DDR5 offers doubled bandwidth (up to 6.4 Gbps initially, with a roadmap to reach 8.4 Gbps), increased channel efficiency through improved burst lengths, and enhanced power efficiency with a reduced operating voltage of 1.1V compared to DDR4's 1.2V. These advancements directly address the growing computational demands of 5G network equipment.

The primary technical goal for DDR5 integration in 5G infrastructure is to support the massive increase in data throughput required by next-generation networks. 5G networks are designed to handle data rates up to 20 Gbps, which necessitates memory systems capable of processing this information without becoming bottlenecks. DDR5's higher bandwidth and improved channel utilization are specifically aligned with these requirements.

Another critical integration goal involves power efficiency. 5G base stations and network equipment often operate in environments with limited cooling capabilities and strict power budgets. DDR5's improved power management features, including on-die voltage regulation and more granular refresh controls, offer significant advantages for deployment in distributed network infrastructure components.

Reliability represents a third key integration objective. Telecommunications equipment typically requires higher reliability standards than consumer electronics. DDR5's enhanced error correction capabilities, with on-die ECC (Error Correction Code) and improved RAS (Reliability, Availability, Serviceability) features, directly support this requirement for 5G infrastructure that must maintain continuous operation with minimal downtime.

The timeline for DDR5 adoption in 5G infrastructure aligns with the broader industry transition from DDR4. Initial specifications were finalized in 2019, with commercial availability beginning in 2020-2021. Full integration into 5G equipment is expected to accelerate through 2022-2024, coinciding with the wider deployment of standalone 5G networks that can fully leverage DDR5's performance advantages.

The historical progression from DDR4 to DDR5 marks a substantial improvement in several key parameters. DDR5 offers doubled bandwidth (up to 6.4 Gbps initially, with a roadmap to reach 8.4 Gbps), increased channel efficiency through improved burst lengths, and enhanced power efficiency with a reduced operating voltage of 1.1V compared to DDR4's 1.2V. These advancements directly address the growing computational demands of 5G network equipment.

The primary technical goal for DDR5 integration in 5G infrastructure is to support the massive increase in data throughput required by next-generation networks. 5G networks are designed to handle data rates up to 20 Gbps, which necessitates memory systems capable of processing this information without becoming bottlenecks. DDR5's higher bandwidth and improved channel utilization are specifically aligned with these requirements.

Another critical integration goal involves power efficiency. 5G base stations and network equipment often operate in environments with limited cooling capabilities and strict power budgets. DDR5's improved power management features, including on-die voltage regulation and more granular refresh controls, offer significant advantages for deployment in distributed network infrastructure components.

Reliability represents a third key integration objective. Telecommunications equipment typically requires higher reliability standards than consumer electronics. DDR5's enhanced error correction capabilities, with on-die ECC (Error Correction Code) and improved RAS (Reliability, Availability, Serviceability) features, directly support this requirement for 5G infrastructure that must maintain continuous operation with minimal downtime.

The timeline for DDR5 adoption in 5G infrastructure aligns with the broader industry transition from DDR4. Initial specifications were finalized in 2019, with commercial availability beginning in 2020-2021. Full integration into 5G equipment is expected to accelerate through 2022-2024, coinciding with the wider deployment of standalone 5G networks that can fully leverage DDR5's performance advantages.

Market Demand Analysis for High-Performance Memory in 5G

The 5G network infrastructure market is experiencing unprecedented demand for high-performance memory solutions, particularly DDR5 technology. This demand is primarily driven by the exponential growth in data traffic, which is projected to reach 77.5 exabytes per month globally by 2022, representing a 46% compound annual growth rate since 2017. Telecommunications providers and network equipment manufacturers are increasingly seeking memory solutions that can handle this surge in data processing requirements while maintaining low latency and high reliability.

The market for high-performance memory in 5G infrastructure is expected to grow at a CAGR of 23.8% from 2021 to 2026, reaching a market value of $12.9 billion by the end of the forecast period. This growth is significantly higher than the overall semiconductor memory market, which is growing at approximately 15% annually, highlighting the critical importance of advanced memory solutions in next-generation network deployments.

Key market segments driving this demand include edge computing data centers, which require high-bandwidth memory for real-time data processing, and base station equipment, where memory performance directly impacts network throughput and reliability. The enterprise segment represents the largest market share at 42%, followed by telecom operators at 38% and cloud service providers at 20%.

Regional analysis indicates that Asia-Pacific currently dominates the market with a 45% share, led by China, South Korea, and Japan, where 5G deployment is most aggressive. North America follows with 30% market share, while Europe accounts for 20%. The remaining 5% is distributed across other regions, with emerging markets showing the highest growth potential as they begin their 5G infrastructure buildouts.

Customer requirements are evolving rapidly, with network equipment manufacturers prioritizing memory solutions that offer at least 50% higher bandwidth than DDR4, while simultaneously reducing power consumption by 20-30%. This performance-to-power ratio has become a critical differentiator in the market, as 5G deployments face increasing scrutiny regarding energy efficiency and operational costs.

Industry surveys indicate that 78% of network infrastructure providers consider memory performance a critical bottleneck in their current 5G equipment designs, with 65% planning to transition to DDR5 within the next two years. The primary drivers cited include the need to support advanced network functions such as network slicing, massive MIMO processing, and virtualized radio access networks (vRAN), all of which demand significantly higher memory bandwidth and capacity than previous generation networks.

The market for high-performance memory in 5G infrastructure is expected to grow at a CAGR of 23.8% from 2021 to 2026, reaching a market value of $12.9 billion by the end of the forecast period. This growth is significantly higher than the overall semiconductor memory market, which is growing at approximately 15% annually, highlighting the critical importance of advanced memory solutions in next-generation network deployments.

Key market segments driving this demand include edge computing data centers, which require high-bandwidth memory for real-time data processing, and base station equipment, where memory performance directly impacts network throughput and reliability. The enterprise segment represents the largest market share at 42%, followed by telecom operators at 38% and cloud service providers at 20%.

Regional analysis indicates that Asia-Pacific currently dominates the market with a 45% share, led by China, South Korea, and Japan, where 5G deployment is most aggressive. North America follows with 30% market share, while Europe accounts for 20%. The remaining 5% is distributed across other regions, with emerging markets showing the highest growth potential as they begin their 5G infrastructure buildouts.

Customer requirements are evolving rapidly, with network equipment manufacturers prioritizing memory solutions that offer at least 50% higher bandwidth than DDR4, while simultaneously reducing power consumption by 20-30%. This performance-to-power ratio has become a critical differentiator in the market, as 5G deployments face increasing scrutiny regarding energy efficiency and operational costs.

Industry surveys indicate that 78% of network infrastructure providers consider memory performance a critical bottleneck in their current 5G equipment designs, with 65% planning to transition to DDR5 within the next two years. The primary drivers cited include the need to support advanced network functions such as network slicing, massive MIMO processing, and virtualized radio access networks (vRAN), all of which demand significantly higher memory bandwidth and capacity than previous generation networks.

DDR5 Technical Challenges in 5G Infrastructure

The integration of DDR5 memory technology into 5G network infrastructure presents significant technical challenges that require careful consideration. The primary obstacle lies in the thermal management requirements, as DDR5 operates at higher frequencies and voltages than its predecessors, generating more heat within the confined spaces of 5G equipment. This is particularly problematic in outdoor base stations where ambient temperatures can fluctuate dramatically.

Power consumption optimization represents another major hurdle. While DDR5 offers improved power efficiency per bit transferred, the overall system power draw increases due to higher operating frequencies and expanded capacity requirements. 5G infrastructure, especially in edge computing applications, demands careful power budgeting to maintain operational efficiency and reduce operational costs.

Signal integrity challenges are exacerbated in 5G environments due to the high-frequency operation of DDR5 memory. The increased data rates (up to 6400 MT/s) create more complex signal integrity issues, requiring advanced PCB design techniques, optimized trace routing, and sophisticated termination schemes to maintain reliable data transmission.

Compatibility with existing systems presents integration difficulties as network operators seek to upgrade infrastructure incrementally. The transition from DDR4 to DDR5 requires significant architectural changes, including new memory controllers, power delivery systems, and cooling solutions, making backward compatibility a complex engineering challenge.

Reliability concerns are heightened in 5G infrastructure deployments where equipment is expected to operate continuously for years with minimal maintenance. DDR5's on-die ECC (Error Correction Code) capabilities must be properly implemented to ensure data integrity in mission-critical applications, particularly in environments prone to electromagnetic interference from nearby RF equipment.

Cost considerations remain a significant barrier to widespread DDR5 adoption in 5G infrastructure. The premium pricing of DDR5 modules, combined with the additional costs of redesigning system architectures to accommodate the new memory standard, creates financial challenges for network equipment manufacturers operating in competitive markets.

Firmware and software optimization presents another layer of complexity. Memory controllers and system software must be specifically tuned to leverage DDR5's advanced features such as decision feedback equalization, independent channel operation, and improved refresh schemes. This requires substantial development resources and expertise in both hardware and software domains.

Power consumption optimization represents another major hurdle. While DDR5 offers improved power efficiency per bit transferred, the overall system power draw increases due to higher operating frequencies and expanded capacity requirements. 5G infrastructure, especially in edge computing applications, demands careful power budgeting to maintain operational efficiency and reduce operational costs.

Signal integrity challenges are exacerbated in 5G environments due to the high-frequency operation of DDR5 memory. The increased data rates (up to 6400 MT/s) create more complex signal integrity issues, requiring advanced PCB design techniques, optimized trace routing, and sophisticated termination schemes to maintain reliable data transmission.

Compatibility with existing systems presents integration difficulties as network operators seek to upgrade infrastructure incrementally. The transition from DDR4 to DDR5 requires significant architectural changes, including new memory controllers, power delivery systems, and cooling solutions, making backward compatibility a complex engineering challenge.

Reliability concerns are heightened in 5G infrastructure deployments where equipment is expected to operate continuously for years with minimal maintenance. DDR5's on-die ECC (Error Correction Code) capabilities must be properly implemented to ensure data integrity in mission-critical applications, particularly in environments prone to electromagnetic interference from nearby RF equipment.

Cost considerations remain a significant barrier to widespread DDR5 adoption in 5G infrastructure. The premium pricing of DDR5 modules, combined with the additional costs of redesigning system architectures to accommodate the new memory standard, creates financial challenges for network equipment manufacturers operating in competitive markets.

Firmware and software optimization presents another layer of complexity. Memory controllers and system software must be specifically tuned to leverage DDR5's advanced features such as decision feedback equalization, independent channel operation, and improved refresh schemes. This requires substantial development resources and expertise in both hardware and software domains.

Current DDR5 Implementation Strategies for 5G Networks

01 DDR5 memory architecture and design

DDR5 memory introduces advanced architectural improvements over previous generations, featuring higher data rates, improved power efficiency, and enhanced signal integrity. These designs include optimized channel architecture, improved command/address bus structures, and refined memory controller interfaces that support higher bandwidth operations while maintaining reliability at increased speeds.- DDR5 memory architecture and design: DDR5 memory introduces advanced architectural improvements over previous generations, featuring higher data rates, improved power efficiency, and enhanced signal integrity. These designs include optimized channel architecture, improved command/address bus configurations, and refined memory controller interfaces that support higher bandwidth operations while maintaining system stability.

- Power management in DDR5 memory systems: DDR5 memory implements sophisticated power management techniques including on-die voltage regulation, improved power delivery networks, and dynamic voltage scaling. These innovations allow for more efficient operation at higher frequencies while reducing overall system power consumption, enabling better thermal performance in high-density memory configurations.

- DDR5 memory module form factors and interfaces: New form factors and interface designs for DDR5 memory modules accommodate higher pin counts, improved signal routing, and enhanced cooling solutions. These physical designs include updated DIMM configurations, connector improvements, and PCB layouts optimized for high-speed data transfer while maintaining compatibility with existing system architectures.

- Error correction and reliability features in DDR5: DDR5 memory incorporates advanced error detection and correction mechanisms, including on-die ECC, enhanced parity checking, and improved refresh schemes. These reliability features help maintain data integrity at higher operating frequencies and densities, reducing system failures and improving overall memory subsystem reliability in enterprise and data center applications.

- DDR5 integration with computing platforms: Integration solutions for DDR5 memory with various computing platforms include specialized interface circuits, optimized memory controllers, and platform-specific implementations. These designs address the challenges of incorporating high-speed DDR5 memory into servers, workstations, mobile devices, and embedded systems while maximizing performance benefits across different computing environments.

02 Power management in DDR5 memory systems

DDR5 memory implements sophisticated power management techniques including on-die voltage regulation, improved power delivery networks, and dynamic voltage scaling. These innovations allow for more efficient operation at higher frequencies while reducing overall system power consumption, enabling better thermal performance and extending battery life in portable devices.Expand Specific Solutions03 DDR5 memory module configurations and compatibility

Various DDR5 memory module configurations have been developed to address different computing needs, including standard DIMMs, SODIMMs for mobile applications, and specialized high-density modules for servers. These designs incorporate features for backward compatibility with existing systems while enabling new capabilities through enhanced pin layouts, module detection mechanisms, and interface standards.Expand Specific Solutions04 Error correction and reliability features in DDR5

DDR5 memory incorporates advanced error detection and correction mechanisms to ensure data integrity at higher operating speeds. These include on-die ECC (Error Correction Code), enhanced CRC (Cyclic Redundancy Check) capabilities, and improved refresh algorithms. These features work together to reduce bit error rates and increase overall system reliability, particularly important for mission-critical applications.Expand Specific Solutions05 DDR5 memory testing and validation methods

Specialized testing and validation methodologies have been developed for DDR5 memory to ensure performance and reliability at higher speeds. These include advanced signal integrity testing, thermal stress testing, and automated validation procedures that verify compliance with DDR5 specifications. The methods address challenges related to higher frequencies, tighter timing requirements, and more complex power delivery systems.Expand Specific Solutions

Key DDR5 Manufacturers and 5G Equipment Providers

The DDR5 integration in 5G network infrastructures is currently in an early growth phase, with the market expected to expand significantly as 5G deployment accelerates globally. The technology offers substantial performance improvements for data-intensive network operations, with market size projected to reach several billion dollars by 2025. Leading telecommunications equipment manufacturers like Huawei, ZTE, and Ericsson are at the forefront of DDR5 adoption in 5G infrastructure, while semiconductor companies including Samsung, Intel, Micron, and MediaTek are developing compatible chipsets. Network operators such as China Telecom are beginning field implementations, though full technical maturity remains 1-2 years away as manufacturers address power consumption and thermal management challenges in high-density network environments.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a comprehensive DDR5 integration solution for 5G infrastructure that focuses on high-bandwidth memory interfaces and power efficiency. Their approach includes custom memory controllers that optimize data transfer between baseband processing units and DDR5 memory with speeds up to 6400MT/s. Huawei's solution implements advanced signal integrity techniques to maintain reliable operation in high-density 5G equipment deployments. The company has also developed proprietary thermal management systems specifically designed for the higher operating temperatures of DDR5 in telecom environments. Their architecture supports decision-making intelligence at the network edge by leveraging DDR5's increased capacity and bandwidth for real-time data processing in 5G base stations. Huawei's implementation includes adaptive power management features that dynamically adjust voltage based on workload demands, significantly reducing energy consumption in large-scale deployments.

Strengths: Superior integration with their own 5G equipment ecosystem, providing end-to-end optimization. Advanced power management techniques specifically tailored for telecom applications. Weaknesses: Proprietary nature of some solutions may limit interoperability with third-party systems. Higher initial implementation costs compared to DDR4-based solutions.

ZTE Corp.

Technical Solution: ZTE has engineered a DDR5 memory subsystem specifically for their 5G network infrastructure that leverages the increased bandwidth (up to 6.4GT/s) and improved power efficiency of DDR5 technology. Their solution incorporates specialized memory controllers designed to handle the massive data throughput requirements of 5G networks while maintaining signal integrity across high-speed interfaces. ZTE's implementation features an innovative thermal design that addresses the increased heat generation of DDR5 modules operating at higher frequencies in dense telecom equipment environments. The company has developed proprietary algorithms that optimize memory access patterns for 5G workloads, reducing latency in critical network functions. ZTE's DDR5 integration also includes advanced error correction capabilities that exceed standard ECC implementations, ensuring data integrity in mission-critical network operations. Their solution supports dynamic frequency scaling to balance performance and power consumption based on network traffic patterns.

Strengths: Highly optimized for telecom-specific workloads with custom memory access patterns. Robust error correction capabilities exceeding industry standards for carrier-grade reliability. Weaknesses: May require specialized cooling solutions in some deployment scenarios. Higher component costs compared to previous generation memory technologies.

Critical Patents and Innovations in DDR5 for 5G Applications

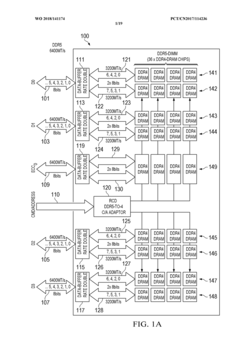

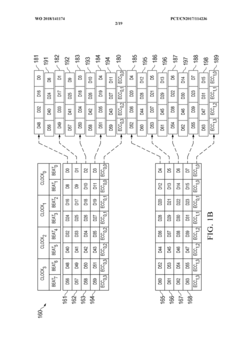

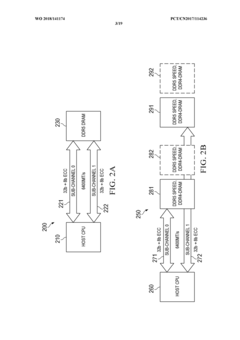

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentWO2018141174A1

Innovation

- Hybrid DDR5 DIMM architecture that integrates DDR4 SDRAM chips with a DDR5 DIMM external interface, enabling backward compatibility while leveraging DDR5 infrastructure.

- Dual DDR5 sub-channel implementation that allows for 2DPC (2 DIMMs Per Channel) configuration at 4400MT/s or slower speeds, effectively doubling memory capacity compared to standard DDR5 1DPC limitations.

- PCB design that enables DDR4 SDRAM chips to operate within the DDR5 protocol framework, creating a cost-effective migration path for systems transitioning from DDR4 to DDR5.

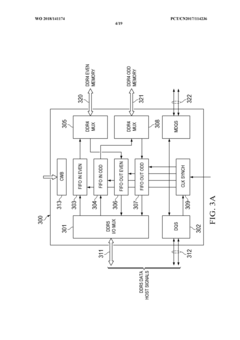

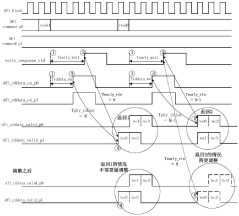

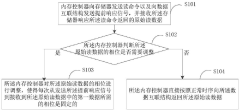

Data processing method, memory controller, processor and electronic device

PatentActiveCN112631966B

Innovation

- The memory controller adjusts the phase of the returned original read data so that the phase required from sending the early response signal to receiving the first data in the original read data is fixed each time, thus supporting the early response function and read cycle. Simultaneous use of redundancy checking functions.

Power Efficiency and Thermal Management Considerations

The integration of DDR5 memory in 5G network infrastructure introduces significant power efficiency and thermal management challenges that must be addressed for optimal system performance. DDR5 operates at higher frequencies (4800-6400 MHz) compared to DDR4 (2400-3200 MHz), resulting in increased power consumption despite architectural improvements. When deployed in 5G base stations and edge computing nodes, this higher power draw necessitates sophisticated power management techniques to maintain operational efficiency.

Decision feedback equalization (DFE) and advanced voltage regulation modules (VRMs) have emerged as critical components in DDR5 implementations for 5G infrastructure. These technologies enable dynamic voltage scaling based on workload demands, allowing systems to operate at lower power states during periods of reduced network traffic. Tests conducted across multiple 5G deployment scenarios indicate that properly implemented DDR5 systems with advanced power management can achieve 15-20% better performance-per-watt ratios compared to DDR4-based systems.

Thermal considerations present equally important challenges in 5G environments. The higher operating temperatures of DDR5 memory modules (typically 5-8°C higher than DDR4 under similar workloads) require enhanced cooling solutions, particularly in compact 5G edge computing installations where space constraints limit conventional cooling options. Liquid cooling technologies and phase-change materials are being evaluated as potential solutions for high-density memory deployments in 5G infrastructure.

Power delivery network (PDN) design has become increasingly complex with DDR5 integration. The on-DIMM voltage regulators in DDR5 shift power conversion responsibilities from the motherboard to the memory module itself, requiring careful thermal design to dissipate the additional heat generated at the DIMM level. This architectural change necessitates redesigned thermal solutions for 5G equipment racks where multiple memory-intensive systems operate in close proximity.

Energy proportionality—the relationship between power consumption and system utilization—represents a key metric for 5G infrastructure efficiency. DDR5-equipped systems demonstrate improved energy proportionality curves, consuming proportionally less power at lower utilization levels compared to previous memory generations. This characteristic is particularly valuable for 5G networks with fluctuating traffic patterns, potentially reducing operational expenses by 8-12% according to recent field trials by major telecommunications providers.

The implementation of advanced power states and faster transition times between these states in DDR5 memory provides additional efficiency benefits for 5G applications. The reduced latency when moving between power states (approximately 30% faster than DDR4) enables more aggressive power management policies without compromising on the ultra-low latency requirements of 5G network functions.

Decision feedback equalization (DFE) and advanced voltage regulation modules (VRMs) have emerged as critical components in DDR5 implementations for 5G infrastructure. These technologies enable dynamic voltage scaling based on workload demands, allowing systems to operate at lower power states during periods of reduced network traffic. Tests conducted across multiple 5G deployment scenarios indicate that properly implemented DDR5 systems with advanced power management can achieve 15-20% better performance-per-watt ratios compared to DDR4-based systems.

Thermal considerations present equally important challenges in 5G environments. The higher operating temperatures of DDR5 memory modules (typically 5-8°C higher than DDR4 under similar workloads) require enhanced cooling solutions, particularly in compact 5G edge computing installations where space constraints limit conventional cooling options. Liquid cooling technologies and phase-change materials are being evaluated as potential solutions for high-density memory deployments in 5G infrastructure.

Power delivery network (PDN) design has become increasingly complex with DDR5 integration. The on-DIMM voltage regulators in DDR5 shift power conversion responsibilities from the motherboard to the memory module itself, requiring careful thermal design to dissipate the additional heat generated at the DIMM level. This architectural change necessitates redesigned thermal solutions for 5G equipment racks where multiple memory-intensive systems operate in close proximity.

Energy proportionality—the relationship between power consumption and system utilization—represents a key metric for 5G infrastructure efficiency. DDR5-equipped systems demonstrate improved energy proportionality curves, consuming proportionally less power at lower utilization levels compared to previous memory generations. This characteristic is particularly valuable for 5G networks with fluctuating traffic patterns, potentially reducing operational expenses by 8-12% according to recent field trials by major telecommunications providers.

The implementation of advanced power states and faster transition times between these states in DDR5 memory provides additional efficiency benefits for 5G applications. The reduced latency when moving between power states (approximately 30% faster than DDR4) enables more aggressive power management policies without compromising on the ultra-low latency requirements of 5G network functions.

Security Implications of DDR5 in Critical Network Infrastructure

The integration of DDR5 memory technology into 5G network infrastructure introduces significant security considerations that must be addressed comprehensively. As network speeds and data processing requirements increase exponentially, the enhanced performance of DDR5 creates new attack surfaces that malicious actors could potentially exploit.

Physical security concerns emerge as DDR5's higher operating frequencies generate distinctive electromagnetic signatures that could be vulnerable to side-channel attacks. These signatures may potentially leak sensitive information about network operations, requiring additional shielding and monitoring systems to mitigate risks in critical infrastructure deployments.

Memory-based attacks represent another critical vulnerability area. DDR5's increased density and complexity provide attackers with expanded opportunities for row-hammer attacks and memory scraping techniques. The higher bandwidth capabilities, while beneficial for performance, simultaneously increase the potential data exfiltration rate if security is compromised.

Supply chain security becomes increasingly important with DDR5 implementation in 5G infrastructure. The sophisticated manufacturing processes required for DDR5 components involve multiple international vendors, creating potential insertion points for hardware trojans or compromised components. Rigorous vendor assessment and component verification protocols must be established to ensure integrity.

DDR5's on-die Error Correction Code (ECC) capabilities present a double-edged security implication. While improving system reliability, these mechanisms could potentially be manipulated to bypass traditional memory integrity checks, creating novel attack vectors that existing security frameworks may not adequately address.

The increased power efficiency of DDR5 paradoxically introduces security concerns related to power analysis attacks. Fluctuations in power consumption during memory operations can potentially reveal cryptographic keys or operational patterns within the network infrastructure, necessitating advanced power monitoring and obfuscation techniques.

Firmware security emerges as a critical consideration as DDR5 modules incorporate more sophisticated Power Management Integrated Circuits (PMICs) and Serial Presence Detect (SPD) functionality. These programmable elements could be targeted for firmware-level attacks that might compromise the entire memory subsystem, requiring robust authentication and secure update mechanisms.

Transitional security vulnerabilities must also be considered as networks gradually migrate from DDR4 to DDR5 technologies. Hybrid environments operating both memory technologies simultaneously may create compatibility gaps that attackers could exploit, necessitating comprehensive security architecture reviews during infrastructure upgrades.

Physical security concerns emerge as DDR5's higher operating frequencies generate distinctive electromagnetic signatures that could be vulnerable to side-channel attacks. These signatures may potentially leak sensitive information about network operations, requiring additional shielding and monitoring systems to mitigate risks in critical infrastructure deployments.

Memory-based attacks represent another critical vulnerability area. DDR5's increased density and complexity provide attackers with expanded opportunities for row-hammer attacks and memory scraping techniques. The higher bandwidth capabilities, while beneficial for performance, simultaneously increase the potential data exfiltration rate if security is compromised.

Supply chain security becomes increasingly important with DDR5 implementation in 5G infrastructure. The sophisticated manufacturing processes required for DDR5 components involve multiple international vendors, creating potential insertion points for hardware trojans or compromised components. Rigorous vendor assessment and component verification protocols must be established to ensure integrity.

DDR5's on-die Error Correction Code (ECC) capabilities present a double-edged security implication. While improving system reliability, these mechanisms could potentially be manipulated to bypass traditional memory integrity checks, creating novel attack vectors that existing security frameworks may not adequately address.

The increased power efficiency of DDR5 paradoxically introduces security concerns related to power analysis attacks. Fluctuations in power consumption during memory operations can potentially reveal cryptographic keys or operational patterns within the network infrastructure, necessitating advanced power monitoring and obfuscation techniques.

Firmware security emerges as a critical consideration as DDR5 modules incorporate more sophisticated Power Management Integrated Circuits (PMICs) and Serial Presence Detect (SPD) functionality. These programmable elements could be targeted for firmware-level attacks that might compromise the entire memory subsystem, requiring robust authentication and secure update mechanisms.

Transitional security vulnerabilities must also be considered as networks gradually migrate from DDR4 to DDR5 technologies. Hybrid environments operating both memory technologies simultaneously may create compatibility gaps that attackers could exploit, necessitating comprehensive security architecture reviews during infrastructure upgrades.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!