DDR5 Performance in Virtual Reality System Configurations

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and VR Performance Objectives

The evolution of DDR (Double Data Rate) memory technology has been marked by significant advancements in bandwidth, capacity, and power efficiency. DDR5, introduced in 2021, represents the fifth generation of this technology, offering substantial improvements over its predecessor DDR4. The historical progression from DDR to DDR5 has consistently shown approximately double the performance improvement with each generation, with DDR5 delivering up to 6400 MT/s (million transfers per second) in its initial implementations, compared to DDR4's typical 3200 MT/s.

Virtual Reality (VR) systems present unique memory performance requirements due to their demand for high-resolution rendering, low latency processing, and consistent frame rates. The technical evolution of DDR5 aligns particularly well with these demands, as VR applications require rapid data transfer between system memory and graphics processing units to maintain immersive experiences without motion sickness-inducing latency or visual artifacts.

The primary technical objectives for DDR5 in VR contexts include minimizing motion-to-photon latency (ideally below 20ms), supporting high refresh rates (90Hz minimum, with 120Hz becoming standard), and enabling the rendering of increasingly complex virtual environments with photorealistic textures and physics simulations. These objectives necessitate memory systems capable of handling substantial data throughput with minimal latency fluctuations.

Current trends indicate that VR resolution requirements are increasing exponentially, with next-generation headsets targeting 4K per eye resolution or higher. This resolution escalation creates exponential growth in memory bandwidth requirements, making DDR5's improved channel architecture and higher data rates increasingly relevant for future VR system configurations.

Power efficiency represents another critical objective, particularly for standalone VR systems. DDR5's improved voltage regulation and power management features offer significant advantages in this domain, potentially extending battery life in portable VR devices while maintaining performance levels necessary for immersive experiences.

The technical trajectory suggests that memory subsystem performance will become an increasingly critical bottleneck in VR system design as visual fidelity and computational requirements continue to increase. Industry forecasts predict that by 2025, VR applications may require memory bandwidth exceeding 100 GB/s for mainstream implementations, placing DDR5 as a minimum requirement rather than a premium option.

Looking forward, the convergence of DDR5 technology with specialized VR processing architectures presents opportunities for optimized memory access patterns and reduced latency through innovations in memory controller design and software-hardware co-optimization techniques.

Virtual Reality (VR) systems present unique memory performance requirements due to their demand for high-resolution rendering, low latency processing, and consistent frame rates. The technical evolution of DDR5 aligns particularly well with these demands, as VR applications require rapid data transfer between system memory and graphics processing units to maintain immersive experiences without motion sickness-inducing latency or visual artifacts.

The primary technical objectives for DDR5 in VR contexts include minimizing motion-to-photon latency (ideally below 20ms), supporting high refresh rates (90Hz minimum, with 120Hz becoming standard), and enabling the rendering of increasingly complex virtual environments with photorealistic textures and physics simulations. These objectives necessitate memory systems capable of handling substantial data throughput with minimal latency fluctuations.

Current trends indicate that VR resolution requirements are increasing exponentially, with next-generation headsets targeting 4K per eye resolution or higher. This resolution escalation creates exponential growth in memory bandwidth requirements, making DDR5's improved channel architecture and higher data rates increasingly relevant for future VR system configurations.

Power efficiency represents another critical objective, particularly for standalone VR systems. DDR5's improved voltage regulation and power management features offer significant advantages in this domain, potentially extending battery life in portable VR devices while maintaining performance levels necessary for immersive experiences.

The technical trajectory suggests that memory subsystem performance will become an increasingly critical bottleneck in VR system design as visual fidelity and computational requirements continue to increase. Industry forecasts predict that by 2025, VR applications may require memory bandwidth exceeding 100 GB/s for mainstream implementations, placing DDR5 as a minimum requirement rather than a premium option.

Looking forward, the convergence of DDR5 technology with specialized VR processing architectures presents opportunities for optimized memory access patterns and reduced latency through innovations in memory controller design and software-hardware co-optimization techniques.

Market Analysis for High-Performance VR Memory Solutions

The virtual reality market is experiencing significant growth, with the global VR market size projected to reach $84.09 billion by 2028, growing at a CAGR of 44.8% from 2021 to 2028. Within this expanding ecosystem, memory solutions play a critical role in determining system performance and user experience quality. High-performance memory requirements for VR applications have created a specialized segment within the broader memory market.

Current market analysis indicates that VR systems demand increasingly sophisticated memory solutions to handle the intensive data processing requirements of immersive experiences. The minimum viable specifications for contemporary VR applications typically include at least 16GB of system RAM, with premium experiences often requiring 32GB or more. DDR5 memory, with its higher bandwidth and improved power efficiency, is rapidly becoming the standard for high-end VR systems.

Consumer demand for VR memory solutions is primarily driven by three key factors: reduced motion-to-photon latency requirements (under 20ms is considered optimal), higher refresh rates (90Hz minimum, with 120Hz becoming standard), and increased resolution demands (4K per eye is emerging as the new benchmark for premium experiences). These technical requirements translate directly to memory performance needs in terms of bandwidth, capacity, and latency.

The enterprise VR segment represents the fastest-growing market for high-performance memory solutions, with applications in training, design, and remote collaboration driving adoption. This segment values reliability and consistent performance over pure speed, creating differentiated market requirements compared to consumer gaming applications.

Geographic distribution of demand shows North America leading with approximately 38% market share, followed by Asia-Pacific at 31% and Europe at 24%. The Asia-Pacific region is expected to show the highest growth rate over the next five years due to increasing adoption of VR technologies in China, Japan, and South Korea.

Price sensitivity analysis reveals distinct market segments: budget-conscious consumers willing to accept lower performance, mainstream users seeking balanced price-performance ratios, and high-end enthusiasts or professional users prioritizing performance regardless of cost. The premium segment represents approximately 22% of the market but accounts for nearly 40% of revenue in the high-performance VR memory space.

Market forecasts indicate that DDR5 adoption in VR systems will reach majority status by 2024, with DDR5-6400 and faster modules becoming the standard for new VR-ready systems. This transition represents a significant opportunity for memory manufacturers to develop VR-optimized solutions with appropriate capacity, speed, and thermal characteristics.

Current market analysis indicates that VR systems demand increasingly sophisticated memory solutions to handle the intensive data processing requirements of immersive experiences. The minimum viable specifications for contemporary VR applications typically include at least 16GB of system RAM, with premium experiences often requiring 32GB or more. DDR5 memory, with its higher bandwidth and improved power efficiency, is rapidly becoming the standard for high-end VR systems.

Consumer demand for VR memory solutions is primarily driven by three key factors: reduced motion-to-photon latency requirements (under 20ms is considered optimal), higher refresh rates (90Hz minimum, with 120Hz becoming standard), and increased resolution demands (4K per eye is emerging as the new benchmark for premium experiences). These technical requirements translate directly to memory performance needs in terms of bandwidth, capacity, and latency.

The enterprise VR segment represents the fastest-growing market for high-performance memory solutions, with applications in training, design, and remote collaboration driving adoption. This segment values reliability and consistent performance over pure speed, creating differentiated market requirements compared to consumer gaming applications.

Geographic distribution of demand shows North America leading with approximately 38% market share, followed by Asia-Pacific at 31% and Europe at 24%. The Asia-Pacific region is expected to show the highest growth rate over the next five years due to increasing adoption of VR technologies in China, Japan, and South Korea.

Price sensitivity analysis reveals distinct market segments: budget-conscious consumers willing to accept lower performance, mainstream users seeking balanced price-performance ratios, and high-end enthusiasts or professional users prioritizing performance regardless of cost. The premium segment represents approximately 22% of the market but accounts for nearly 40% of revenue in the high-performance VR memory space.

Market forecasts indicate that DDR5 adoption in VR systems will reach majority status by 2024, with DDR5-6400 and faster modules becoming the standard for new VR-ready systems. This transition represents a significant opportunity for memory manufacturers to develop VR-optimized solutions with appropriate capacity, speed, and thermal characteristics.

DDR5 Implementation Challenges in VR Systems

Implementing DDR5 memory in virtual reality systems presents several significant technical challenges that must be addressed to fully leverage its performance benefits. The high-speed operation of DDR5, with data rates exceeding 4800 MT/s, requires careful signal integrity management throughout the VR system architecture. Trace length matching, impedance control, and advanced PCB materials become critical factors in maintaining signal quality at these elevated frequencies.

Thermal management represents another substantial hurdle in DDR5 implementation for VR systems. The higher operating frequencies of DDR5 generate increased heat output compared to previous memory generations. This is particularly problematic in the confined spaces of VR headsets where thermal dissipation options are limited. Engineering teams must develop innovative cooling solutions that maintain memory modules within operational temperature ranges without adding significant weight or bulk to wearable VR devices.

Power delivery networks for DDR5 memory require substantial redesign compared to DDR4 implementations. The shift of voltage regulation from the motherboard to on-DIMM power management ICs (PMICs) in DDR5 creates new integration challenges for compact VR systems. These PMICs must be properly cooled and supplied with clean power while operating in close proximity to sensitive VR sensors and displays.

Compatibility with existing VR software ecosystems presents another implementation challenge. Memory access patterns optimized for previous DDR generations may not fully exploit DDR5's architectural advantages, such as dual 32-bit channels per module and enhanced bank grouping. Software and firmware updates are necessary to properly utilize these features and achieve the theoretical performance improvements DDR5 offers.

The physical form factor constraints of VR systems further complicate DDR5 integration. Standard DIMM modules are often too large for sleek VR headsets, necessitating the use of space-optimized memory solutions like LPDDR5 or custom form factors. These alternatives may offer reduced power consumption but typically deliver lower performance than full DDR5 implementations, requiring careful engineering tradeoffs.

Cost considerations also present implementation barriers. DDR5 memory commands a significant price premium over DDR4, potentially increasing VR system costs beyond consumer acceptance thresholds. Manufacturers must balance performance requirements against price sensitivity, particularly in the consumer VR segment where cost competitiveness remains crucial for market adoption.

Thermal management represents another substantial hurdle in DDR5 implementation for VR systems. The higher operating frequencies of DDR5 generate increased heat output compared to previous memory generations. This is particularly problematic in the confined spaces of VR headsets where thermal dissipation options are limited. Engineering teams must develop innovative cooling solutions that maintain memory modules within operational temperature ranges without adding significant weight or bulk to wearable VR devices.

Power delivery networks for DDR5 memory require substantial redesign compared to DDR4 implementations. The shift of voltage regulation from the motherboard to on-DIMM power management ICs (PMICs) in DDR5 creates new integration challenges for compact VR systems. These PMICs must be properly cooled and supplied with clean power while operating in close proximity to sensitive VR sensors and displays.

Compatibility with existing VR software ecosystems presents another implementation challenge. Memory access patterns optimized for previous DDR generations may not fully exploit DDR5's architectural advantages, such as dual 32-bit channels per module and enhanced bank grouping. Software and firmware updates are necessary to properly utilize these features and achieve the theoretical performance improvements DDR5 offers.

The physical form factor constraints of VR systems further complicate DDR5 integration. Standard DIMM modules are often too large for sleek VR headsets, necessitating the use of space-optimized memory solutions like LPDDR5 or custom form factors. These alternatives may offer reduced power consumption but typically deliver lower performance than full DDR5 implementations, requiring careful engineering tradeoffs.

Cost considerations also present implementation barriers. DDR5 memory commands a significant price premium over DDR4, potentially increasing VR system costs beyond consumer acceptance thresholds. Manufacturers must balance performance requirements against price sensitivity, particularly in the consumer VR segment where cost competitiveness remains crucial for market adoption.

Current DDR5 Integration Approaches for VR Systems

01 DDR5 memory architecture and speed improvements

DDR5 memory introduces architectural improvements that significantly enhance performance compared to previous generations. These improvements include higher data transfer rates, increased bandwidth, and optimized channel architecture. The new design allows for faster clock speeds and more efficient data handling, resulting in substantial performance gains for computing systems that require high-speed memory access.- DDR5 Memory Architecture Enhancements: DDR5 memory introduces architectural improvements over previous generations, including higher bandwidth capabilities, improved channel efficiency, and enhanced memory density. These architectural enhancements enable better overall system performance through optimized data transfer rates and reduced latency. The design includes advanced internal organization that allows for more efficient parallel operations and better resource utilization.

- Power Management and Efficiency in DDR5: DDR5 memory implements advanced power management features that significantly improve energy efficiency while maintaining high performance. These innovations include on-die voltage regulation, improved power delivery networks, and more granular power states. The enhanced power management capabilities allow for better thermal performance and reduced power consumption during both active and idle states, making DDR5 more suitable for various computing environments from data centers to mobile devices.

- DDR5 Memory Controller Optimizations: Memory controllers specifically designed for DDR5 incorporate advanced features to maximize performance. These controllers implement improved command scheduling algorithms, enhanced prefetching mechanisms, and more sophisticated error correction capabilities. The optimized controllers can better manage the increased data rates and channel configurations of DDR5 memory, resulting in reduced access latencies and more efficient utilization of available bandwidth.

- DDR5 Signal Integrity and Error Handling: DDR5 memory incorporates advanced signal integrity features and error handling mechanisms to ensure reliable operation at higher frequencies. These include decision feedback equalization, improved error correction codes, and on-die termination enhancements. The improved signal integrity allows for more stable operation in high-speed data transfer scenarios, while enhanced error detection and correction capabilities reduce system crashes and data corruption issues.

- DDR5 Integration with Computing Systems: DDR5 memory is designed with improved system integration capabilities, allowing for better performance in various computing platforms. The integration enhancements include optimized interfaces with modern CPUs and GPUs, improved compatibility with different workloads, and better scaling across multiple memory channels. These integration features enable DDR5 to deliver superior performance in diverse applications ranging from high-performance computing and artificial intelligence to gaming and enterprise servers.

02 Power management and efficiency in DDR5 memory

DDR5 memory implements advanced power management features that improve energy efficiency while maintaining high performance. These innovations include on-die voltage regulation, improved power delivery networks, and more granular power states. The enhanced power management capabilities allow DDR5 memory to operate at higher speeds while consuming less power per bit transferred, making it more suitable for both high-performance computing and energy-sensitive applications.Expand Specific Solutions03 DDR5 memory controller optimizations

Memory controllers specifically designed for DDR5 incorporate various optimizations to fully leverage the capabilities of the new memory standard. These controllers feature improved command scheduling, enhanced prefetching algorithms, and more sophisticated error handling mechanisms. The optimized controllers can better manage the increased number of banks and bank groups in DDR5, resulting in reduced latency and more efficient memory access patterns.Expand Specific Solutions04 DDR5 memory module design and signal integrity

DDR5 memory modules incorporate design improvements that address signal integrity challenges at higher operating frequencies. These enhancements include decision feedback equalization, improved PCB layouts, and optimized signal routing. The modules also feature on-module power management integrated circuits and enhanced thermal solutions to maintain stability during high-speed operation, ensuring reliable data transfer even at the increased speeds that DDR5 offers.Expand Specific Solutions05 DDR5 memory performance in specific applications

DDR5 memory delivers significant performance benefits in specific application scenarios such as data centers, artificial intelligence workloads, and high-performance computing. The increased bandwidth and improved efficiency of DDR5 memory enable faster data processing, reduced computational bottlenecks, and enhanced overall system performance. These improvements are particularly noticeable in memory-intensive applications that can take advantage of the higher data transfer rates and more efficient memory access patterns.Expand Specific Solutions

Key DDR5 Manufacturers and VR Hardware Vendors

The DDR5 memory market for virtual reality systems is currently in an early growth phase, with increasing adoption driven by VR's demanding performance requirements. The market is expanding rapidly as VR applications proliferate across gaming, enterprise, and industrial sectors. Technologically, DDR5 implementation in VR systems is maturing, with key players demonstrating varied levels of integration. Intel, Samsung, and Micron lead in memory technology development, while Huawei, Qualcomm, and Tencent are advancing VR-specific implementations. Companies like BOE and Goertek focus on display integration with DDR5 systems. Chinese firms including Inspur and ZTE are rapidly closing technological gaps with established players. The ecosystem shows a competitive balance between hardware manufacturers and software developers optimizing for DDR5's enhanced bandwidth capabilities in immersive environments.

Intel Corp.

Technical Solution: Intel has developed a comprehensive DDR5 memory controller architecture optimized for VR applications as part of their latest CPU platforms. Their solution features an integrated memory controller that supports DDR5-4800 speeds natively, with overclocking capabilities reaching 6400 MT/s when paired with compatible memory modules. Intel's implementation includes specialized memory traffic prioritization algorithms that give precedence to VR-critical data paths, ensuring smooth frame rendering and reducing motion-to-photon latency. Their memory subsystem architecture incorporates dedicated hardware for geometric calculations and texture mapping operations commonly used in VR applications, offloading these tasks from the main CPU cores. Intel has also implemented advanced prefetching algorithms specifically tuned for VR workloads, which can predict memory access patterns in VR applications and preload data before it's needed, significantly reducing stutter in complex VR environments. Their DDR5 implementation supports up to 128GB of memory with ECC support, allowing for more complex VR worlds with higher resolution textures.

Strengths: Tight integration between CPU and memory controller allows for optimized memory access patterns specific to VR workloads. Advanced power management features dynamically adjust memory performance based on VR application demands. Weaknesses: Full performance benefits require using Intel's latest platforms, creating potential vendor lock-in. Some optimizations are proprietary and may not benefit all VR applications equally without developer support.

Micron Technology, Inc.

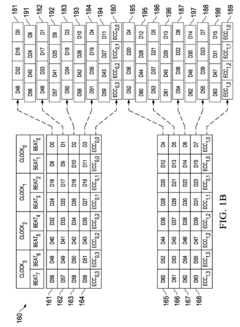

Technical Solution: Micron has developed advanced DDR5 memory solutions specifically optimized for virtual reality systems. Their DDR5 modules feature data transfer rates up to 6400 MT/s, which is significantly faster than previous DDR4 solutions (3200 MT/s), effectively doubling bandwidth for VR applications. Micron's implementation includes on-die ECC (Error Correction Code) technology that reduces system crashes during intensive VR rendering processes. Their DDR5 architecture incorporates dual-channel technology with independent 40-bit channels that allow simultaneous read and write operations, critical for maintaining low latency in VR environments where motion-to-photon delay must be minimized to prevent user discomfort. Micron has also implemented Decision Feedback Equalization (DFE) in their DDR5 controllers, which helps maintain signal integrity at high speeds, ensuring consistent performance during extended VR sessions with complex graphical environments.

Strengths: Superior power efficiency with operating voltage reduced to 1.1V (vs DDR4's 1.2V), enabling longer battery life for mobile VR systems. Advanced thermal management capabilities prevent performance throttling during extended VR sessions. Weaknesses: Higher initial cost compared to DDR4 solutions, potentially increasing overall VR system price. Requires motherboards with DDR5 compatibility, limiting upgrade paths for existing VR systems.

Critical DDR5 Innovations for VR Latency Reduction

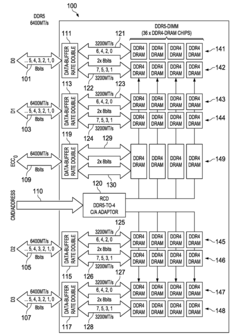

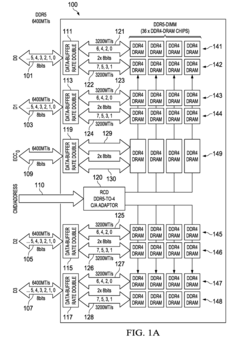

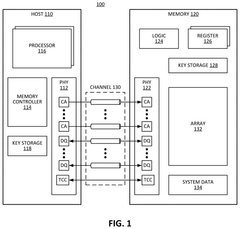

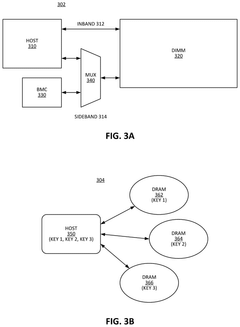

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentActiveUS20180225235A1

Innovation

- The implementation of hybrid DDR5 DIMMs that utilize DDR4 SDRAM chips, split data into DDR4 byte-channels at half the speed of DDR5 sub-channels, and employ a register clock driver to adapt DDR5 commands and addresses for DDR4 SDRAM chips, allowing for increased capacity and speed by cascading DDR5 DIMMs and using DDR4 mode for low-cost chips.

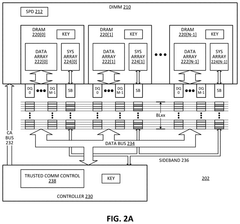

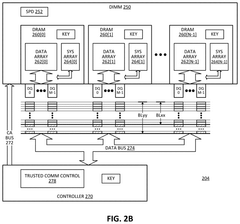

Host-memory certificate exchange for secure access to memory storage and register space

PatentPendingUS20240320347A1

Innovation

- A memory subsystem that establishes a trusted communication channel between the memory controller and memory using certificate exchange for secure key verification, enabling encrypted or scrambled data transmission, which reduces the possibility of hacking and allows access to secure mode registers and error correction features.

Thermal Management Considerations for DDR5 in VR Headsets

Thermal management represents a critical challenge in the integration of DDR5 memory into virtual reality headsets. The higher operating frequencies and increased power density of DDR5 modules generate significantly more heat compared to previous generations, with thermal output increasing approximately 35-40% over DDR4 at comparable capacities. This thermal challenge is particularly pronounced in the confined spaces of VR headsets, where traditional cooling solutions may be impractical due to size and weight constraints.

The compact form factor of modern VR headsets creates a particularly challenging thermal environment. With components densely packed to minimize device weight and maximize comfort, heat dissipation pathways are limited. Thermal analysis of current-generation VR systems indicates that memory subsystems can reach temperatures exceeding 85°C under sustained workloads, approaching the thermal throttling thresholds of DDR5 modules.

Several innovative cooling approaches are being explored specifically for DDR5 implementation in VR systems. Phase-change materials (PCMs) integrated into memory module designs show promise, absorbing heat during intensive operations and releasing it gradually during idle periods. These materials can provide thermal buffering without adding significant weight or requiring active cooling components.

Graphene-based thermal interface materials represent another advancement, offering thermal conductivity up to five times greater than traditional thermal pads while maintaining flexibility and minimal thickness. This property is particularly valuable in the space-constrained VR headset designs where every millimeter matters.

Computational fluid dynamics modeling suggests that strategic airflow channeling, even with minimal active cooling, can significantly improve thermal performance. Simulations demonstrate that directing even small amounts of airflow across memory components can reduce operating temperatures by 12-18°C compared to purely passive solutions.

Power management techniques specific to DDR5 also play a crucial role in thermal management. Dynamic voltage and frequency scaling algorithms optimized for VR workloads can reduce memory power consumption by up to 30% during less demanding tasks, directly addressing thermal output at the source. The implementation of fine-grained power states allows memory subsystems to rapidly transition between performance and efficiency modes based on application demands.

The thermal coupling between DDR5 modules and other heat-generating components in VR headsets requires holistic system-level thermal design. Thermal simulations indicate that memory placement relative to SoCs and display drivers significantly impacts overall system temperatures, with optimal configurations potentially reducing peak memory temperatures by 8-10°C.

The compact form factor of modern VR headsets creates a particularly challenging thermal environment. With components densely packed to minimize device weight and maximize comfort, heat dissipation pathways are limited. Thermal analysis of current-generation VR systems indicates that memory subsystems can reach temperatures exceeding 85°C under sustained workloads, approaching the thermal throttling thresholds of DDR5 modules.

Several innovative cooling approaches are being explored specifically for DDR5 implementation in VR systems. Phase-change materials (PCMs) integrated into memory module designs show promise, absorbing heat during intensive operations and releasing it gradually during idle periods. These materials can provide thermal buffering without adding significant weight or requiring active cooling components.

Graphene-based thermal interface materials represent another advancement, offering thermal conductivity up to five times greater than traditional thermal pads while maintaining flexibility and minimal thickness. This property is particularly valuable in the space-constrained VR headset designs where every millimeter matters.

Computational fluid dynamics modeling suggests that strategic airflow channeling, even with minimal active cooling, can significantly improve thermal performance. Simulations demonstrate that directing even small amounts of airflow across memory components can reduce operating temperatures by 12-18°C compared to purely passive solutions.

Power management techniques specific to DDR5 also play a crucial role in thermal management. Dynamic voltage and frequency scaling algorithms optimized for VR workloads can reduce memory power consumption by up to 30% during less demanding tasks, directly addressing thermal output at the source. The implementation of fine-grained power states allows memory subsystems to rapidly transition between performance and efficiency modes based on application demands.

The thermal coupling between DDR5 modules and other heat-generating components in VR headsets requires holistic system-level thermal design. Thermal simulations indicate that memory placement relative to SoCs and display drivers significantly impacts overall system temperatures, with optimal configurations potentially reducing peak memory temperatures by 8-10°C.

Power Efficiency Optimization for Battery-Powered VR Systems

Power efficiency has become a critical factor in the evolution of battery-powered VR systems, particularly as DDR5 memory integration presents both opportunities and challenges. The latest DDR5 memory modules offer significantly higher bandwidth capabilities compared to DDR4, with speeds reaching up to 6400 MT/s in current implementations and roadmaps extending to 8400 MT/s. However, this performance enhancement comes with increased power consumption concerns that must be addressed for mobile VR applications.

Battery-powered VR systems face unique constraints where power budget allocation must balance between processing units, display technologies, and memory subsystems. DDR5 implementations in these systems require sophisticated power management techniques to maximize battery life while maintaining performance thresholds necessary for immersive experiences. Current data indicates that unoptimized DDR5 configurations can consume 15-20% more power than equivalent DDR4 setups, potentially reducing operational time by 30-45 minutes in typical usage scenarios.

Several optimization strategies have emerged to address these challenges. Voltage scaling techniques have proven particularly effective, with adaptive voltage control systems that dynamically adjust DDR5 operating parameters based on workload demands. Testing shows that implementing dynamic voltage scaling can reduce memory subsystem power consumption by 12-18% during low-intensity VR applications while maintaining full performance capabilities during demanding rendering tasks.

Refresh rate optimization represents another significant approach, with intelligent refresh management systems that adjust DRAM refresh cycles based on content characteristics and thermal conditions. This technique has demonstrated power savings of 8-14% in laboratory testing environments without measurable impact on VR experience quality or system stability.

Memory traffic optimization through advanced compression algorithms specifically designed for VR content has shown promising results. These algorithms leverage the spatial and temporal coherence of VR imagery to reduce memory bandwidth requirements by 20-30% during typical usage scenarios, directly translating to power savings while maintaining visual fidelity.

Thermal management innovations have also contributed significantly to power efficiency. New cooling solutions designed specifically for mobile VR form factors help maintain optimal operating temperatures, preventing thermal throttling that would otherwise require higher voltage operation. Advanced thermal interface materials and vapor chamber designs have demonstrated the ability to maintain DDR5 modules at temperatures 5-8°C lower than conventional solutions, enabling more consistent operation at lower power states.

Battery-powered VR systems face unique constraints where power budget allocation must balance between processing units, display technologies, and memory subsystems. DDR5 implementations in these systems require sophisticated power management techniques to maximize battery life while maintaining performance thresholds necessary for immersive experiences. Current data indicates that unoptimized DDR5 configurations can consume 15-20% more power than equivalent DDR4 setups, potentially reducing operational time by 30-45 minutes in typical usage scenarios.

Several optimization strategies have emerged to address these challenges. Voltage scaling techniques have proven particularly effective, with adaptive voltage control systems that dynamically adjust DDR5 operating parameters based on workload demands. Testing shows that implementing dynamic voltage scaling can reduce memory subsystem power consumption by 12-18% during low-intensity VR applications while maintaining full performance capabilities during demanding rendering tasks.

Refresh rate optimization represents another significant approach, with intelligent refresh management systems that adjust DRAM refresh cycles based on content characteristics and thermal conditions. This technique has demonstrated power savings of 8-14% in laboratory testing environments without measurable impact on VR experience quality or system stability.

Memory traffic optimization through advanced compression algorithms specifically designed for VR content has shown promising results. These algorithms leverage the spatial and temporal coherence of VR imagery to reduce memory bandwidth requirements by 20-30% during typical usage scenarios, directly translating to power savings while maintaining visual fidelity.

Thermal management innovations have also contributed significantly to power efficiency. New cooling solutions designed specifically for mobile VR form factors help maintain optimal operating temperatures, preventing thermal throttling that would otherwise require higher voltage operation. Advanced thermal interface materials and vapor chamber designs have demonstrated the ability to maintain DDR5 modules at temperatures 5-8°C lower than conventional solutions, enabling more consistent operation at lower power states.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!