DDR5 vs PSRAM: Efficiency in Portable Device Applications

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Memory Evolution and Objectives

Memory technology has undergone significant evolution since the introduction of the first dynamic random-access memory (DRAM) in the late 1960s. The trajectory has consistently followed Moore's Law, with memory density doubling approximately every 18 months while costs per bit have decreased. From DDR1 to the current DDR5 standard, each generation has brought substantial improvements in bandwidth, capacity, and power efficiency, addressing the growing demands of computing applications.

PSRAM (Pseudo Static RAM) represents a parallel evolutionary path, combining DRAM's cost-effectiveness with SRAM's ease of use. Initially developed for embedded systems, PSRAM has found increasing relevance in portable devices where power constraints are critical. The technology has evolved from asynchronous interfaces to modern low-power synchronous designs that compete directly with traditional DRAM in specific application contexts.

The portable device market has experienced explosive growth over the past decade, creating unique memory requirements that differ substantially from traditional computing environments. These devices demand memory solutions that balance performance with extreme power efficiency, compact form factors, and cost sensitivity. This market evolution has created a technological inflection point where traditional memory hierarchies are being reconsidered.

DDR5, as the latest DRAM standard, brings significant improvements over DDR4, including higher bandwidth (up to 6400 MT/s initially), improved power efficiency through voltage reduction to 1.1V, and enhanced signal integrity. However, its design still prioritizes high-performance computing environments rather than ultra-portable applications. The standard's complexity and power requirements, while improved, remain challenging for battery-powered devices with strict thermal constraints.

PSRAM technology has evolved specifically to address portable device constraints, offering self-refresh capabilities that eliminate the need for complex refresh circuitry in the host controller. Modern PSRAM implementations feature low-power standby modes, rapid wake-up times, and simplified interfaces that reduce both hardware complexity and power consumption. These characteristics make PSRAM particularly attractive for edge computing devices, wearables, and IoT applications.

The primary objective of this technical research is to conduct a comprehensive comparative analysis of DDR5 and PSRAM technologies specifically within the context of portable device applications. The analysis aims to identify the optimal memory solution based on power efficiency metrics, performance characteristics under typical workloads, thermal considerations, physical implementation constraints, and total system cost implications. Additionally, the research seeks to establish a framework for memory technology selection based on application-specific requirements and constraints.

PSRAM (Pseudo Static RAM) represents a parallel evolutionary path, combining DRAM's cost-effectiveness with SRAM's ease of use. Initially developed for embedded systems, PSRAM has found increasing relevance in portable devices where power constraints are critical. The technology has evolved from asynchronous interfaces to modern low-power synchronous designs that compete directly with traditional DRAM in specific application contexts.

The portable device market has experienced explosive growth over the past decade, creating unique memory requirements that differ substantially from traditional computing environments. These devices demand memory solutions that balance performance with extreme power efficiency, compact form factors, and cost sensitivity. This market evolution has created a technological inflection point where traditional memory hierarchies are being reconsidered.

DDR5, as the latest DRAM standard, brings significant improvements over DDR4, including higher bandwidth (up to 6400 MT/s initially), improved power efficiency through voltage reduction to 1.1V, and enhanced signal integrity. However, its design still prioritizes high-performance computing environments rather than ultra-portable applications. The standard's complexity and power requirements, while improved, remain challenging for battery-powered devices with strict thermal constraints.

PSRAM technology has evolved specifically to address portable device constraints, offering self-refresh capabilities that eliminate the need for complex refresh circuitry in the host controller. Modern PSRAM implementations feature low-power standby modes, rapid wake-up times, and simplified interfaces that reduce both hardware complexity and power consumption. These characteristics make PSRAM particularly attractive for edge computing devices, wearables, and IoT applications.

The primary objective of this technical research is to conduct a comprehensive comparative analysis of DDR5 and PSRAM technologies specifically within the context of portable device applications. The analysis aims to identify the optimal memory solution based on power efficiency metrics, performance characteristics under typical workloads, thermal considerations, physical implementation constraints, and total system cost implications. Additionally, the research seeks to establish a framework for memory technology selection based on application-specific requirements and constraints.

Portable Device Memory Market Analysis

The portable device memory market has experienced significant growth over the past decade, driven primarily by the proliferation of smartphones, tablets, wearables, and IoT devices. As of 2023, the global portable device memory market is valued at approximately 28 billion USD, with projections indicating a compound annual growth rate of 6.8% through 2028. This growth trajectory is underpinned by increasing consumer demand for devices with enhanced performance capabilities and longer battery life.

Memory components represent a critical factor in portable device design, accounting for roughly 20-30% of the bill of materials cost in many consumer electronics. The market has witnessed a gradual shift from traditional memory solutions toward more power-efficient alternatives, with manufacturers increasingly prioritizing performance-per-watt metrics over raw speed capabilities.

DDR5 memory currently dominates the high-performance segment, capturing approximately 45% market share in premium portable devices. However, PSRAM solutions have gained significant traction in the mid-range and entry-level segments, where power efficiency considerations often outweigh performance requirements. PSRAM implementations have seen a 34% year-over-year growth in adoption rates across wearables and IoT applications specifically.

Regional analysis reveals distinct market preferences, with North American and European markets favoring high-performance DDR5 solutions in premium devices, while Asia-Pacific markets demonstrate stronger adoption of PSRAM technologies across broader device categories. This regional variation reflects differences in consumer priorities and price sensitivity across global markets.

The competitive landscape features traditional memory manufacturers like Samsung, SK Hynix, and Micron dominating DDR5 production, while specialized firms including Cypress Semiconductor, ISSI, and Winbond have established strong positions in the PSRAM segment. Recent market consolidation through strategic acquisitions has intensified competition, with several major semiconductor companies expanding their memory portfolios to address the growing demand for energy-efficient solutions.

Consumer behavior analysis indicates a growing awareness of battery life as a primary purchase consideration, with 67% of consumers ranking extended usage time above processing speed when selecting portable devices. This shift in consumer priorities has accelerated manufacturer interest in memory technologies that optimize the balance between performance and power consumption, creating favorable market conditions for PSRAM adoption in specific application scenarios.

Memory components represent a critical factor in portable device design, accounting for roughly 20-30% of the bill of materials cost in many consumer electronics. The market has witnessed a gradual shift from traditional memory solutions toward more power-efficient alternatives, with manufacturers increasingly prioritizing performance-per-watt metrics over raw speed capabilities.

DDR5 memory currently dominates the high-performance segment, capturing approximately 45% market share in premium portable devices. However, PSRAM solutions have gained significant traction in the mid-range and entry-level segments, where power efficiency considerations often outweigh performance requirements. PSRAM implementations have seen a 34% year-over-year growth in adoption rates across wearables and IoT applications specifically.

Regional analysis reveals distinct market preferences, with North American and European markets favoring high-performance DDR5 solutions in premium devices, while Asia-Pacific markets demonstrate stronger adoption of PSRAM technologies across broader device categories. This regional variation reflects differences in consumer priorities and price sensitivity across global markets.

The competitive landscape features traditional memory manufacturers like Samsung, SK Hynix, and Micron dominating DDR5 production, while specialized firms including Cypress Semiconductor, ISSI, and Winbond have established strong positions in the PSRAM segment. Recent market consolidation through strategic acquisitions has intensified competition, with several major semiconductor companies expanding their memory portfolios to address the growing demand for energy-efficient solutions.

Consumer behavior analysis indicates a growing awareness of battery life as a primary purchase consideration, with 67% of consumers ranking extended usage time above processing speed when selecting portable devices. This shift in consumer priorities has accelerated manufacturer interest in memory technologies that optimize the balance between performance and power consumption, creating favorable market conditions for PSRAM adoption in specific application scenarios.

DDR5 and PSRAM Technical Challenges

DDR5 and PSRAM memory technologies face distinct technical challenges in portable device applications, with each technology presenting unique obstacles that impact their efficiency and implementation. DDR5, as the latest generation of dynamic random-access memory, encounters significant power consumption issues in portable environments. Despite its advanced power management features like voltage regulation on-die (PMIC integration), the fundamental refresh requirements of dynamic memory cells continue to demand substantial energy, creating thermal management challenges in compact device designs.

The high-speed operation of DDR5 (4800-6400 MT/s) necessitates complex signal integrity solutions, including equalization techniques and precise timing control. These requirements increase implementation complexity and component costs, making DDR5 integration particularly challenging for space-constrained portable devices with strict power budgets.

PSRAM (Pseudo Static RAM) presents a different set of challenges. While offering lower power consumption than DDR5, PSRAM suffers from limited density capabilities, typically maxing out at 512Mb per die compared to DDR5's multi-gigabit capacities. This density limitation restricts PSRAM's applicability in data-intensive portable applications like advanced AI processing or high-resolution multimedia handling.

Interface compatibility poses another significant hurdle for both technologies. DDR5 requires dedicated high-speed memory controllers and specialized PCB design considerations, while PSRAM often uses proprietary interfaces that vary between manufacturers, complicating standardization efforts and potentially creating vendor lock-in scenarios.

Manufacturing scalability represents a divergent challenge between these technologies. DDR5 benefits from massive industry investment in DRAM manufacturing infrastructure but faces increasing process complexity at advanced nodes. PSRAM, despite its simpler cell structure, receives comparatively less manufacturing focus, resulting in higher per-bit costs and limited availability from fewer suppliers.

Reliability in portable environments presents unique challenges for both memory types. DDR5's sophisticated error correction capabilities (on-die ECC) must contend with the increased error rates that come with lower operating voltages and higher frequencies. PSRAM offers better inherent resilience to environmental factors but lacks the advanced error management features of DDR5, potentially compromising data integrity in harsh mobile conditions.

The thermal envelope constraints of portable devices create perhaps the most significant implementation challenge. DDR5's higher performance comes with increased thermal output that must be managed within the limited cooling capabilities of compact devices. PSRAM generates less heat but its performance limitations may necessitate architectural compromises that impact overall system efficiency.

The high-speed operation of DDR5 (4800-6400 MT/s) necessitates complex signal integrity solutions, including equalization techniques and precise timing control. These requirements increase implementation complexity and component costs, making DDR5 integration particularly challenging for space-constrained portable devices with strict power budgets.

PSRAM (Pseudo Static RAM) presents a different set of challenges. While offering lower power consumption than DDR5, PSRAM suffers from limited density capabilities, typically maxing out at 512Mb per die compared to DDR5's multi-gigabit capacities. This density limitation restricts PSRAM's applicability in data-intensive portable applications like advanced AI processing or high-resolution multimedia handling.

Interface compatibility poses another significant hurdle for both technologies. DDR5 requires dedicated high-speed memory controllers and specialized PCB design considerations, while PSRAM often uses proprietary interfaces that vary between manufacturers, complicating standardization efforts and potentially creating vendor lock-in scenarios.

Manufacturing scalability represents a divergent challenge between these technologies. DDR5 benefits from massive industry investment in DRAM manufacturing infrastructure but faces increasing process complexity at advanced nodes. PSRAM, despite its simpler cell structure, receives comparatively less manufacturing focus, resulting in higher per-bit costs and limited availability from fewer suppliers.

Reliability in portable environments presents unique challenges for both memory types. DDR5's sophisticated error correction capabilities (on-die ECC) must contend with the increased error rates that come with lower operating voltages and higher frequencies. PSRAM offers better inherent resilience to environmental factors but lacks the advanced error management features of DDR5, potentially compromising data integrity in harsh mobile conditions.

The thermal envelope constraints of portable devices create perhaps the most significant implementation challenge. DDR5's higher performance comes with increased thermal output that must be managed within the limited cooling capabilities of compact devices. PSRAM generates less heat but its performance limitations may necessitate architectural compromises that impact overall system efficiency.

Current DDR5 and PSRAM Solutions

01 DDR5 memory architecture and performance improvements

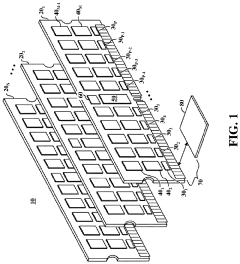

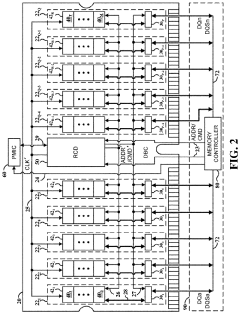

DDR5 memory technology offers significant performance improvements over previous generations through architectural enhancements. These include higher data transfer rates, improved power efficiency, and enhanced channel architecture. DDR5 implements decision feedback equalization, on-die termination, and advanced error correction capabilities to maintain signal integrity at higher speeds. The technology also features independent channels that can operate simultaneously, reducing latency and increasing overall memory bandwidth.- DDR5 memory architecture and performance improvements: DDR5 memory technology offers significant performance improvements over previous generations through architectural enhancements. These improvements include higher data transfer rates, increased bandwidth, and better power efficiency. DDR5 implements decision feedback equalization, improved refresh mechanisms, and on-die ECC to enhance reliability while reducing power consumption. The architecture also supports higher density memory modules and improved channel utilization.

- PSRAM technology optimization for mobile and IoT applications: PSRAM (Pseudo Static RAM) technology has been optimized for low-power applications such as mobile devices and IoT systems. These optimizations include improved refresh mechanisms that maintain data while minimizing power consumption, enhanced interface designs for faster data access, and architectural modifications that balance performance with power efficiency. PSRAM provides DRAM-like density with SRAM-like interface simplicity, making it suitable for battery-powered devices requiring moderate memory capacity.

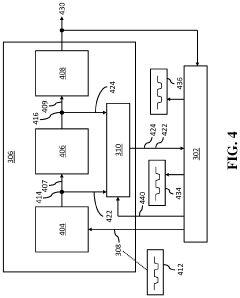

- Memory controller designs for efficiency optimization: Advanced memory controller designs play a crucial role in optimizing the efficiency of both DDR5 and PSRAM technologies. These controllers implement sophisticated algorithms for command scheduling, power management, and thermal regulation. Features include dynamic frequency scaling, intelligent refresh control, and adaptive voltage positioning. Memory controllers also manage the interface between processors and memory subsystems, optimizing data transfer paths and reducing latency through predictive techniques.

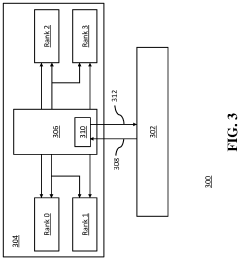

- Integration of DDR5 and PSRAM in heterogeneous memory systems: Heterogeneous memory systems that integrate both DDR5 and PSRAM technologies can achieve optimal balance between performance, power efficiency, and cost. These systems utilize memory tiering approaches where frequently accessed data is stored in faster memory while less critical data resides in more power-efficient memory. Memory management techniques include intelligent data migration, predictive caching, and workload-aware memory allocation. Such integration enables devices to adapt memory usage based on application requirements and power constraints.

- Power efficiency techniques in modern memory technologies: Both DDR5 and PSRAM implement advanced power efficiency techniques to reduce energy consumption while maintaining performance. These techniques include fine-grained power states, voltage regulation modules integrated directly on memory modules, and intelligent clock gating. Additional power-saving features include temperature-compensated refresh rates, partial array self-refresh, and dynamic voltage and frequency scaling. These technologies also implement power-aware command scheduling and optimized termination schemes to minimize idle power consumption.

02 PSRAM technology optimization for low power applications

PSRAM (Pseudo Static RAM) technology combines the density of DRAM with the ease of use of SRAM, making it particularly efficient for low-power applications. PSRAM implementations feature self-refresh mechanisms that reduce power consumption while maintaining data integrity. Advanced PSRAM designs incorporate power-saving modes, optimized refresh cycles, and improved cell structures to enhance energy efficiency while providing fast access times. These optimizations make PSRAM suitable for mobile devices and IoT applications where power efficiency is critical.Expand Specific Solutions03 Memory controller designs for efficient DDR5 and PSRAM operation

Specialized memory controllers are designed to maximize the efficiency of DDR5 and PSRAM technologies. These controllers implement advanced scheduling algorithms, dynamic frequency scaling, and intelligent power management to optimize memory operations. Features such as command reordering, bank group management, and adaptive refresh timing help reduce latency and improve throughput. Memory controllers also incorporate interface optimizations that reduce signal integrity issues and enable higher data transfer rates while maintaining low power consumption.Expand Specific Solutions04 Integration of DDR5 and PSRAM in system-on-chip designs

System-on-chip (SoC) designs increasingly integrate DDR5 and PSRAM technologies to achieve optimal performance and power efficiency. These integrated solutions feature optimized memory subsystems with dedicated interconnects, shared cache hierarchies, and intelligent memory management units. The integration enables reduced signal path lengths, lower latency, and improved power efficiency. Advanced SoC designs implement heterogeneous memory architectures that combine the strengths of both memory technologies to meet diverse application requirements while minimizing overall system power consumption.Expand Specific Solutions05 Testing and validation methodologies for memory efficiency

Specialized testing and validation methodologies are developed to ensure the efficiency of DDR5 and PSRAM memory technologies. These include advanced simulation techniques, hardware-accelerated testing platforms, and comprehensive performance analysis tools. Testing methodologies focus on measuring and optimizing key efficiency metrics such as power consumption, data transfer rates, latency, and thermal characteristics. Validation procedures incorporate stress testing under various operating conditions to ensure reliable operation while maintaining efficiency across different workloads and environmental conditions.Expand Specific Solutions

Key Memory Manufacturers Landscape

The DDR5 vs PSRAM competition in portable devices is evolving rapidly, with the market currently in a growth phase as demand for efficient memory solutions increases. Major players like Samsung Electronics, Micron Technology, and SK Hynix dominate the DDR5 segment, while companies such as Renesas Electronics, Infineon Technologies, and QUALCOMM are advancing PSRAM technologies. The market is characterized by a technological dichotomy: DDR5 offers superior performance but with higher power consumption, while PSRAM provides better energy efficiency crucial for battery-powered devices. Technical maturity varies, with DDR5 being more established in high-performance applications, while PSRAM continues to gain traction in ultra-low-power portable devices where battery life is paramount.

QUALCOMM, Inc.

Technical Solution: Qualcomm has integrated advanced memory management technologies into their Snapdragon platforms that optimize the use of both DDR5 and PSRAM in portable devices. Their Memory Boost technology dynamically allocates resources between DDR5 and PSRAM based on application requirements, utilizing DDR5's high bandwidth for data-intensive tasks while leveraging PSRAM's power efficiency for background processes. Qualcomm's implementation includes a proprietary memory controller that supports LPDDR5 speeds up to 6.4 Gbps while incorporating adaptive refresh rate technology that reduces refresh operations by up to 40% during periods of low memory utilization. For ultra-mobile applications, their system architecture enables seamless switching between memory types with latency under 10ns, ensuring responsive performance while maximizing battery life through intelligent power management that can reduce memory subsystem power consumption by up to 35% compared to static memory configurations.

Strengths: Highly integrated solutions that optimize both memory technologies; sophisticated power management algorithms; extensive ecosystem support through Snapdragon platform. Weaknesses: Solutions primarily tied to Qualcomm SoCs; limited standalone memory offerings; higher implementation complexity requiring specialized expertise.

MediaTek, Inc.

Technical Solution: MediaTek has developed a hybrid memory architecture for portable devices that intelligently balances DDR5 and PSRAM technologies based on application requirements. Their UltraSave Memory technology implements fine-grained power states with up to 8 different power modes that can be dynamically applied to different memory regions. MediaTek's implementation supports LPDDR5 with data rates up to 6.4 Gbps while incorporating proprietary compression algorithms that effectively increase available bandwidth by 15-20% for common mobile workloads. For always-on applications, their architecture includes dedicated PSRAM regions with ultra-fast wake times under 5μs that maintain critical system information while consuming less than 1mW of power. MediaTek's memory controller includes adaptive voltage scaling that continuously optimizes operating parameters based on temperature and workload characteristics, extending battery life in portable applications by up to 25% compared to fixed-voltage implementations.

Strengths: Excellent power efficiency through adaptive algorithms; innovative compression technology increases effective bandwidth; seamless integration with MediaTek SoCs. Weaknesses: Limited standalone memory offerings; optimization benefits primarily realized within MediaTek ecosystem; higher implementation complexity.

Critical Memory Patents Analysis

Controller and access method for DDR PSRAM and operating method thereof

PatentActiveUS8593902B2

Innovation

- A controller architecture with single and double rate processing units, a selector, output buffer, data strobe gating unit, and data receiver is introduced, enabling selective data rate operations and precise data strobe signal management to handle both single and double data rate data transfers on a common bus, eliminating the need for masking and ensuring valid data latching.

Register clock driver with chip select loopback

PatentActiveUS20240094762A1

Innovation

- Integration of a loopback circuit within the RCD to sample chip select signals from multiple points, allowing the host controller to determine the source of signal integrity issues and enabling testing during normal operations, thereby maintaining signal integrity.

Power Efficiency Comparison

Power consumption is a critical factor in portable device applications, where battery life directly impacts user experience. When comparing DDR5 and PSRAM technologies, significant differences emerge in their power efficiency profiles that influence their suitability for various portable device applications.

DDR5 memory typically operates at higher voltages (1.1V) compared to PSRAM (1.8V for older generations, with newer variants operating at 1.2V or even lower). However, this voltage comparison alone doesn't tell the complete story. DDR5's sophisticated power management features, including voltage regulation modules (VRMs) integrated directly onto the memory modules, enable more precise power delivery and reduced power loss compared to external regulation systems used in previous generations.

PSRAM demonstrates superior efficiency during idle states, consuming significantly less power when not actively performing read/write operations. This characteristic is particularly valuable in portable devices that spend considerable time in standby mode. Tests indicate that PSRAM can achieve standby power consumption as low as 10-15μW per chip, while DDR5 typically requires 50-100mW even in its lowest power states.

During active operations, DDR5 exhibits higher instantaneous power draw but completes tasks more rapidly due to its superior bandwidth (starting at 4800 MT/s compared to PSRAM's typical 166-200 MHz). This speed advantage allows DDR5 systems to return to low-power states more quickly, potentially offsetting the higher active power consumption in certain workload scenarios.

Thermal considerations also factor into overall power efficiency. DDR5's higher operating temperatures necessitate additional cooling solutions in compact portable devices, indirectly increasing power requirements. PSRAM operates at lower temperatures, reducing thermal management overhead and associated power costs.

Power scaling characteristics differ significantly between these technologies. DDR5 power consumption scales almost linearly with data throughput, while PSRAM shows more favorable sub-linear scaling at lower throughput levels commonly encountered in portable applications like IoT devices and wearables.

Implementation-specific optimizations further influence efficiency profiles. DDR5 benefits from advanced power-saving features like dynamic voltage and frequency scaling (DVFS), while PSRAM leverages simpler circuit designs with fewer transistors per bit cell, reducing leakage current and static power consumption.

For portable applications with intermittent high-performance requirements, hybrid memory systems combining both technologies may offer optimal power efficiency, utilizing PSRAM for low-power standby operation and DDR5 for performance-intensive tasks.

DDR5 memory typically operates at higher voltages (1.1V) compared to PSRAM (1.8V for older generations, with newer variants operating at 1.2V or even lower). However, this voltage comparison alone doesn't tell the complete story. DDR5's sophisticated power management features, including voltage regulation modules (VRMs) integrated directly onto the memory modules, enable more precise power delivery and reduced power loss compared to external regulation systems used in previous generations.

PSRAM demonstrates superior efficiency during idle states, consuming significantly less power when not actively performing read/write operations. This characteristic is particularly valuable in portable devices that spend considerable time in standby mode. Tests indicate that PSRAM can achieve standby power consumption as low as 10-15μW per chip, while DDR5 typically requires 50-100mW even in its lowest power states.

During active operations, DDR5 exhibits higher instantaneous power draw but completes tasks more rapidly due to its superior bandwidth (starting at 4800 MT/s compared to PSRAM's typical 166-200 MHz). This speed advantage allows DDR5 systems to return to low-power states more quickly, potentially offsetting the higher active power consumption in certain workload scenarios.

Thermal considerations also factor into overall power efficiency. DDR5's higher operating temperatures necessitate additional cooling solutions in compact portable devices, indirectly increasing power requirements. PSRAM operates at lower temperatures, reducing thermal management overhead and associated power costs.

Power scaling characteristics differ significantly between these technologies. DDR5 power consumption scales almost linearly with data throughput, while PSRAM shows more favorable sub-linear scaling at lower throughput levels commonly encountered in portable applications like IoT devices and wearables.

Implementation-specific optimizations further influence efficiency profiles. DDR5 benefits from advanced power-saving features like dynamic voltage and frequency scaling (DVFS), while PSRAM leverages simpler circuit designs with fewer transistors per bit cell, reducing leakage current and static power consumption.

For portable applications with intermittent high-performance requirements, hybrid memory systems combining both technologies may offer optimal power efficiency, utilizing PSRAM for low-power standby operation and DDR5 for performance-intensive tasks.

Integration Constraints in Compact Devices

The integration of memory technologies into portable devices presents significant engineering challenges due to the inherent physical constraints of compact form factors. DDR5 and PSRAM technologies each impose distinct integration requirements that must be carefully evaluated when designing space-constrained portable applications.

DDR5 memory modules typically require more complex PCB layouts with stringent signal integrity considerations. The high-speed data transfer rates of DDR5 (up to 6400 MT/s) necessitate careful trace routing, impedance matching, and power delivery network design. These requirements often translate to larger PCB area allocation and more complex layer stacking, which can be problematic in ultra-thin devices where vertical space is at a premium.

Thermal management represents another critical integration constraint. DDR5 operates at higher frequencies than its predecessors, generating more heat within a confined space. Portable devices, which often lack active cooling solutions, must rely on passive thermal dissipation techniques that may be insufficient for sustained high-performance DDR5 operation, potentially leading to thermal throttling.

PSRAM, by contrast, offers more favorable integration characteristics for compact devices. Its simplified interface requires fewer signal lines and less complex PCB routing, resulting in smaller footprint requirements. The reduced pin count of PSRAM modules (typically 10-24 pins versus 200+ for DDR5 DIMM modules) allows for more flexible placement options within tight spatial constraints.

Power delivery infrastructure represents a significant integration consideration. DDR5 implementations require dedicated voltage regulators on-module, which adds complexity but improves power efficiency. However, these additional components increase the overall solution size. PSRAM operates with simpler power requirements, often compatible with existing low-power system rails, eliminating the need for additional power management circuitry.

Manufacturing and assembly considerations also impact integration feasibility. DDR5's fine-pitch BGA packages demand high-precision assembly equipment and processes, which may exceed the capabilities of some portable device manufacturing lines. PSRAM's more forgiving package options and relaxed assembly tolerances align better with existing portable device manufacturing ecosystems.

Electromagnetic interference (EMI) mitigation becomes increasingly challenging in compact devices where components are placed in close proximity. DDR5's higher operating frequencies generate more electromagnetic noise, requiring additional shielding and isolation measures that consume precious space. PSRAM's lower operating frequencies produce less EMI, simplifying compliance with regulatory requirements without extensive shielding.

DDR5 memory modules typically require more complex PCB layouts with stringent signal integrity considerations. The high-speed data transfer rates of DDR5 (up to 6400 MT/s) necessitate careful trace routing, impedance matching, and power delivery network design. These requirements often translate to larger PCB area allocation and more complex layer stacking, which can be problematic in ultra-thin devices where vertical space is at a premium.

Thermal management represents another critical integration constraint. DDR5 operates at higher frequencies than its predecessors, generating more heat within a confined space. Portable devices, which often lack active cooling solutions, must rely on passive thermal dissipation techniques that may be insufficient for sustained high-performance DDR5 operation, potentially leading to thermal throttling.

PSRAM, by contrast, offers more favorable integration characteristics for compact devices. Its simplified interface requires fewer signal lines and less complex PCB routing, resulting in smaller footprint requirements. The reduced pin count of PSRAM modules (typically 10-24 pins versus 200+ for DDR5 DIMM modules) allows for more flexible placement options within tight spatial constraints.

Power delivery infrastructure represents a significant integration consideration. DDR5 implementations require dedicated voltage regulators on-module, which adds complexity but improves power efficiency. However, these additional components increase the overall solution size. PSRAM operates with simpler power requirements, often compatible with existing low-power system rails, eliminating the need for additional power management circuitry.

Manufacturing and assembly considerations also impact integration feasibility. DDR5's fine-pitch BGA packages demand high-precision assembly equipment and processes, which may exceed the capabilities of some portable device manufacturing lines. PSRAM's more forgiving package options and relaxed assembly tolerances align better with existing portable device manufacturing ecosystems.

Electromagnetic interference (EMI) mitigation becomes increasingly challenging in compact devices where components are placed in close proximity. DDR5's higher operating frequencies generate more electromagnetic noise, requiring additional shielding and isolation measures that consume precious space. PSRAM's lower operating frequencies produce less EMI, simplifying compliance with regulatory requirements without extensive shielding.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!