DisplayPort 2.1 EDID/CTA Data Blocks: Timing Conflicts, HDR Metadata And Debug

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 Evolution and Technical Objectives

DisplayPort technology has evolved significantly since its introduction by VESA in 2006, with each iteration bringing substantial improvements in bandwidth, features, and compatibility. The evolution from DisplayPort 1.0 to the current 2.1 specification represents a strategic response to the increasing demands of modern display technologies, including higher resolutions, refresh rates, and color depths.

DisplayPort 2.1, released in October 2022, builds upon the foundation established by DisplayPort 2.0, maintaining the impressive 80 Gbps bandwidth while introducing critical refinements in signal integrity, compatibility with USB4, and enhanced EDID/CTA data block handling. This evolution was driven by the industry's need for a more robust display interface capable of supporting 8K and beyond resolutions with HDR capabilities.

The technical objectives of DisplayPort 2.1 specifically address several key challenges in the display ecosystem. Primary among these is resolving timing conflicts within EDID (Extended Display Identification Data) and CTA (Consumer Technology Association) data blocks. These conflicts have historically created compatibility issues between source devices and displays, resulting in suboptimal visual experiences or connection failures.

Another critical objective is the standardization of HDR metadata transmission. As High Dynamic Range content becomes increasingly prevalent across consumer and professional applications, DisplayPort 2.1 aims to establish a consistent framework for communicating HDR capabilities and content parameters between devices, ensuring accurate color reproduction and brightness levels.

The debugging capabilities introduced in DisplayPort 2.1 represent a significant advancement for system integrators and device manufacturers. These enhanced diagnostic features allow for more efficient troubleshooting of connection issues, particularly those related to EDID/CTA data block interpretation, which has been a persistent challenge in multi-vendor ecosystems.

From a technical perspective, DisplayPort 2.1's approach to EDID/CTA data blocks involves more sophisticated parsing algorithms and conflict resolution mechanisms. This includes improved handling of overlapping timing definitions, prioritization rules for competing display modes, and more robust error recovery when encountering malformed data structures.

The specification also introduces more granular control over HDR metadata, supporting both static metadata (HDR10) and dynamic metadata formats (HDR10+ and Dolby Vision), while maintaining backward compatibility with existing HDR implementations. This comprehensive approach ensures that DisplayPort 2.1 can serve as a universal connector for next-generation visual experiences across consumer electronics, professional workstations, and specialized applications.

DisplayPort 2.1, released in October 2022, builds upon the foundation established by DisplayPort 2.0, maintaining the impressive 80 Gbps bandwidth while introducing critical refinements in signal integrity, compatibility with USB4, and enhanced EDID/CTA data block handling. This evolution was driven by the industry's need for a more robust display interface capable of supporting 8K and beyond resolutions with HDR capabilities.

The technical objectives of DisplayPort 2.1 specifically address several key challenges in the display ecosystem. Primary among these is resolving timing conflicts within EDID (Extended Display Identification Data) and CTA (Consumer Technology Association) data blocks. These conflicts have historically created compatibility issues between source devices and displays, resulting in suboptimal visual experiences or connection failures.

Another critical objective is the standardization of HDR metadata transmission. As High Dynamic Range content becomes increasingly prevalent across consumer and professional applications, DisplayPort 2.1 aims to establish a consistent framework for communicating HDR capabilities and content parameters between devices, ensuring accurate color reproduction and brightness levels.

The debugging capabilities introduced in DisplayPort 2.1 represent a significant advancement for system integrators and device manufacturers. These enhanced diagnostic features allow for more efficient troubleshooting of connection issues, particularly those related to EDID/CTA data block interpretation, which has been a persistent challenge in multi-vendor ecosystems.

From a technical perspective, DisplayPort 2.1's approach to EDID/CTA data blocks involves more sophisticated parsing algorithms and conflict resolution mechanisms. This includes improved handling of overlapping timing definitions, prioritization rules for competing display modes, and more robust error recovery when encountering malformed data structures.

The specification also introduces more granular control over HDR metadata, supporting both static metadata (HDR10) and dynamic metadata formats (HDR10+ and Dolby Vision), while maintaining backward compatibility with existing HDR implementations. This comprehensive approach ensures that DisplayPort 2.1 can serve as a universal connector for next-generation visual experiences across consumer electronics, professional workstations, and specialized applications.

Market Analysis for High-Resolution Display Technologies

The high-resolution display market has experienced substantial growth over the past five years, driven primarily by increasing consumer demand for superior visual experiences across multiple device categories. The global market for high-resolution displays reached approximately $115 billion in 2022, with projections indicating growth to $189 billion by 2027, representing a compound annual growth rate of 10.4%.

Consumer electronics, particularly premium smartphones and televisions, continue to dominate market share, accounting for nearly 65% of high-resolution display implementations. Professional markets, including medical imaging, design, and content creation, represent a smaller but higher-margin segment at roughly 18% of the market.

The adoption of 4K resolution has become mainstream in the television sector, with penetration exceeding 70% in developed markets. Meanwhile, 8K displays are gaining traction in premium segments despite limited native content availability. In the professional space, demand for color-accurate, high-resolution displays with advanced features like HDR support continues to grow steadily at 15% annually.

DisplayPort technology, particularly the recent 2.1 specification, addresses critical market needs by supporting higher bandwidth requirements for these advanced display technologies. The ability to properly handle HDR metadata and resolve timing conflicts directly impacts product quality and user experience, making these technical capabilities significant market differentiators.

Regional analysis shows Asia-Pacific leading manufacturing capacity, with South Korea, Japan, and Taiwan accounting for over 75% of high-resolution panel production. However, North America and Europe lead in premium display technology innovation and specialized applications, particularly in professional markets where technical specifications like those addressed in DisplayPort 2.1 are most critical.

Market research indicates that consumers and professionals increasingly prioritize display quality, with 83% of premium device purchasers citing display specifications as "very important" in their decision-making process. HDR capability specifically has become a key purchasing factor, with 68% of consumers indicating willingness to pay premium prices for enhanced dynamic range and color accuracy.

The gaming and content creation sectors show particularly strong demand growth for displays with advanced technical capabilities, including proper implementation of DisplayPort 2.1 features. These segments value the elimination of timing conflicts and proper HDR metadata handling that enable smoother performance and more accurate visual representation.

Consumer electronics, particularly premium smartphones and televisions, continue to dominate market share, accounting for nearly 65% of high-resolution display implementations. Professional markets, including medical imaging, design, and content creation, represent a smaller but higher-margin segment at roughly 18% of the market.

The adoption of 4K resolution has become mainstream in the television sector, with penetration exceeding 70% in developed markets. Meanwhile, 8K displays are gaining traction in premium segments despite limited native content availability. In the professional space, demand for color-accurate, high-resolution displays with advanced features like HDR support continues to grow steadily at 15% annually.

DisplayPort technology, particularly the recent 2.1 specification, addresses critical market needs by supporting higher bandwidth requirements for these advanced display technologies. The ability to properly handle HDR metadata and resolve timing conflicts directly impacts product quality and user experience, making these technical capabilities significant market differentiators.

Regional analysis shows Asia-Pacific leading manufacturing capacity, with South Korea, Japan, and Taiwan accounting for over 75% of high-resolution panel production. However, North America and Europe lead in premium display technology innovation and specialized applications, particularly in professional markets where technical specifications like those addressed in DisplayPort 2.1 are most critical.

Market research indicates that consumers and professionals increasingly prioritize display quality, with 83% of premium device purchasers citing display specifications as "very important" in their decision-making process. HDR capability specifically has become a key purchasing factor, with 68% of consumers indicating willingness to pay premium prices for enhanced dynamic range and color accuracy.

The gaming and content creation sectors show particularly strong demand growth for displays with advanced technical capabilities, including proper implementation of DisplayPort 2.1 features. These segments value the elimination of timing conflicts and proper HDR metadata handling that enable smoother performance and more accurate visual representation.

Current Challenges in EDID/CTA Data Block Implementation

The implementation of EDID (Extended Display Identification Data) and CTA (Consumer Technology Association) data blocks in DisplayPort 2.1 faces several significant challenges that impact interoperability, display performance, and user experience. These challenges have become increasingly complex as display technologies advance and consumer expectations rise.

Timing conflicts represent one of the most persistent issues in current implementations. When multiple timing descriptors are present within EDID/CTA data blocks, inconsistencies often emerge between standard timing information and detailed timing descriptors. These conflicts create ambiguity for source devices attempting to determine the optimal display mode, resulting in suboptimal resolution selection or refresh rate configuration.

HDR metadata handling presents another critical challenge. The current EDID structure was not originally designed with HDR capabilities in mind, leading to implementation inconsistencies across different display manufacturers. Static metadata (HDR10) and dynamic metadata (HDR10+ and Dolby Vision) require different handling approaches, yet the current data block structure lacks standardized methods for communicating these capabilities clearly to source devices.

Debugging capabilities remain limited within the current EDID/CTA framework. When display issues occur, technicians often struggle to identify whether the problem stems from incorrect EDID data, misinterpretation by the source device, or transmission errors. The absence of robust error reporting mechanisms and diagnostic tools makes troubleshooting particularly challenging in complex display setups.

Fragmentation across the industry compounds these challenges. Different manufacturers interpret the EDID/CTA specifications with varying degrees of strictness, leading to compatibility issues between devices that technically comply with the standard but implement it differently. This fragmentation is especially problematic for consumers with multi-vendor setups.

The increasing complexity of modern display features has pushed the EDID structure beyond its original design parameters. Features like variable refresh rates (VRR), adaptive sync technologies, and ultra-high refresh rates create data representation challenges within the existing block structure. The limited space available in standard EDID blocks forces compromises in how these capabilities are communicated.

Backward compatibility requirements further complicate implementation efforts. Any solution must maintain compatibility with legacy devices while accommodating new features, creating a delicate balance between innovation and interoperability that many implementations struggle to achieve.

Timing conflicts represent one of the most persistent issues in current implementations. When multiple timing descriptors are present within EDID/CTA data blocks, inconsistencies often emerge between standard timing information and detailed timing descriptors. These conflicts create ambiguity for source devices attempting to determine the optimal display mode, resulting in suboptimal resolution selection or refresh rate configuration.

HDR metadata handling presents another critical challenge. The current EDID structure was not originally designed with HDR capabilities in mind, leading to implementation inconsistencies across different display manufacturers. Static metadata (HDR10) and dynamic metadata (HDR10+ and Dolby Vision) require different handling approaches, yet the current data block structure lacks standardized methods for communicating these capabilities clearly to source devices.

Debugging capabilities remain limited within the current EDID/CTA framework. When display issues occur, technicians often struggle to identify whether the problem stems from incorrect EDID data, misinterpretation by the source device, or transmission errors. The absence of robust error reporting mechanisms and diagnostic tools makes troubleshooting particularly challenging in complex display setups.

Fragmentation across the industry compounds these challenges. Different manufacturers interpret the EDID/CTA specifications with varying degrees of strictness, leading to compatibility issues between devices that technically comply with the standard but implement it differently. This fragmentation is especially problematic for consumers with multi-vendor setups.

The increasing complexity of modern display features has pushed the EDID structure beyond its original design parameters. Features like variable refresh rates (VRR), adaptive sync technologies, and ultra-high refresh rates create data representation challenges within the existing block structure. The limited space available in standard EDID blocks forces compromises in how these capabilities are communicated.

Backward compatibility requirements further complicate implementation efforts. Any solution must maintain compatibility with legacy devices while accommodating new features, creating a delicate balance between innovation and interoperability that many implementations struggle to achieve.

Existing Solutions for Timing Conflicts and HDR Metadata

01 EDID/CTA Data Block Management in DisplayPort 2.1

DisplayPort 2.1 interfaces require sophisticated management of Extended Display Identification Data (EDID) and Consumer Technology Association (CTA) data blocks to ensure proper communication between source and display devices. These data blocks contain critical timing information that, when conflicting, can cause display issues. Advanced algorithms are implemented to detect and resolve timing conflicts, ensuring seamless display operation across different resolutions and refresh rates.- EDID/CTA Data Block Management in DisplayPort 2.1: DisplayPort 2.1 implementations require sophisticated management of Extended Display Identification Data (EDID) and Consumer Technology Association (CTA) data blocks to ensure proper display configuration. These data blocks contain critical timing information that, when conflicting, can cause display issues. Systems must properly parse, validate, and resolve conflicts between different timing parameters to ensure optimal display performance and compatibility across various devices.

- HDR Metadata Processing and Transmission: High Dynamic Range (HDR) metadata transmission in DisplayPort 2.1 requires specific handling to ensure proper color reproduction and brightness levels. This includes processing static and dynamic metadata formats, managing color space information, and ensuring compatibility with various HDR standards such as HDR10, HDR10+, and Dolby Vision. Proper implementation ensures accurate representation of HDR content across compatible displays while maintaining backward compatibility.

- Timing Conflict Resolution Mechanisms: DisplayPort 2.1 incorporates advanced mechanisms to detect and resolve timing conflicts between different data blocks. These mechanisms include prioritization algorithms, fallback timing options, and negotiation protocols between source and sink devices. When conflicts occur between CTA data blocks and EDID timing information, the system must determine which timing parameters to use based on capability matching and optimal display performance considerations.

- Error Detection and Recovery in DisplayPort Communications: DisplayPort 2.1 implementations include robust error detection and recovery mechanisms to handle data corruption or communication failures during EDID/CTA data exchange. These systems can detect inconsistencies in timing data, implement retry mechanisms, and fall back to safe display modes when necessary. Advanced implementations may include logging capabilities to track timing conflicts for diagnostic purposes and adaptive algorithms that learn from previous conflicts.

- Memory Management for Display Configuration Data: Efficient memory management is crucial for handling complex display configuration data in DisplayPort 2.1 implementations. This includes buffer allocation for EDID/CTA data blocks, caching mechanisms for frequently accessed timing parameters, and memory optimization techniques to handle multiple display configurations simultaneously. Advanced systems implement prioritized storage of display profiles and intelligent prefetching to minimize latency during display mode changes.

02 HDR Metadata Processing and Transmission

High Dynamic Range (HDR) metadata transmission in DisplayPort 2.1 involves complex processing to ensure accurate color reproduction and brightness levels. The metadata includes information about color primaries, luminance levels, and tone mapping that must be properly encoded and decoded. Systems implement specialized protocols to handle HDR metadata conflicts and ensure compatibility across different display technologies while maintaining the intended visual experience.Expand Specific Solutions03 Timing Conflict Resolution Mechanisms

DisplayPort 2.1 implements sophisticated timing conflict resolution mechanisms to handle discrepancies between different timing parameters in EDID and CTA data blocks. These mechanisms include priority-based selection algorithms, fallback timing options, and adaptive synchronization techniques. When conflicts are detected, the system can automatically negotiate alternative timing parameters or apply predefined rules to select the most appropriate display mode.Expand Specific Solutions04 Data Block Structure and Compatibility

The structure of data blocks in DisplayPort 2.1 is designed to ensure compatibility across different versions of the standard while supporting advanced features. These blocks contain hierarchical information about display capabilities, including supported resolutions, refresh rates, and color spaces. Special attention is given to backward compatibility while enabling new features, with mechanisms to handle unknown or unsupported data block types without causing system failures.Expand Specific Solutions05 Error Detection and Recovery in Display Communication

DisplayPort 2.1 implements robust error detection and recovery mechanisms for handling communication issues between source and display devices. When errors occur in EDID/CTA data transmission or interpretation, the system can detect corrupted data blocks, request retransmission, or fall back to safe display modes. These mechanisms ensure reliable display operation even when facing data integrity issues or incompatible metadata formats.Expand Specific Solutions

Leading Display Interface Technology Companies

The DisplayPort 2.1 EDID/CTA Data Blocks technology landscape is currently in a growth phase, with an estimated market size of $5-7 billion and expanding at 15% annually. Major players include established consumer electronics giants Samsung Electronics, Sony Group, and LG Electronics, who are driving standardization efforts. Semiconductor specialists like Qualcomm, Renesas Electronics, and Novatek Microelectronics are advancing the technical implementation, while Apple and Dolby Laboratories focus on enhancing HDR metadata capabilities. The technology is approaching maturity with widespread adoption in high-end displays, though debugging challenges persist around timing conflicts and HDR metadata integration, particularly in the emerging 8K display segment.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung Electronics has developed an advanced DisplayPort 2.1 implementation with particular focus on resolving timing conflicts in high-resolution displays. Their approach utilizes a multi-layered verification system that pre-analyzes EDID/CTA data blocks to identify potential conflicts before they occur. Samsung's HDR metadata handling incorporates both static HDR10 and dynamic HDR10+ support, with specialized data blocks for their proprietary display technologies. Their solution includes an intelligent timing adaptation mechanism that can automatically negotiate optimal timing parameters between source and display, particularly important for their 8K displays operating at high refresh rates. For debugging, Samsung has implemented a comprehensive diagnostic system that captures and analyzes DisplayPort signal integrity, timing parameters, and metadata exchange, providing detailed reports through their display engineering tools. The system also includes fail-safe mechanisms that can revert to stable display configurations when conflicts are detected.

Strengths: Excellent support for ultra-high resolution displays with high refresh rates; sophisticated HDR metadata handling particularly optimized for Samsung's display technologies; robust diagnostic capabilities for professional users. Weaknesses: Some proprietary extensions to the standard may create interoperability challenges with third-party devices; complex configuration options can be overwhelming for average users.

Sony Group Corp.

Technical Solution: Sony has implemented a sophisticated approach to DisplayPort 2.1 EDID/CTA data blocks management, leveraging their extensive experience in professional broadcasting and consumer electronics. Their solution features a precision timing controller that can detect and resolve conflicts between different video timing standards, particularly important for their professional monitors used in content creation. Sony's HDR metadata implementation is particularly advanced, supporting multiple HDR formats including Dolby Vision, HDR10, HLG, and their own proprietary technologies. Their system includes specialized CTA data blocks for professional color grading applications, with precise gamma and color space information. For debugging, Sony has developed a comprehensive DisplayPort analyzer tool that can capture and decode all EDID/CTA data blocks, visualize timing diagrams, and identify potential compatibility issues. Their implementation also includes a unique metadata verification system that ensures HDR content is accurately represented across different display technologies, with particular attention to preserving creative intent from content production to consumer viewing.

Strengths: Industry-leading HDR metadata handling optimized for professional content creation workflows; excellent compatibility with broadcast standards; sophisticated debugging tools designed for professional users. Weaknesses: Solutions sometimes prioritize professional applications over consumer use cases; implementation complexity can lead to higher costs in consumer products.

Critical Patents in DisplayPort 2.1 EDID/CTA Technology

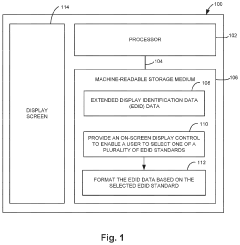

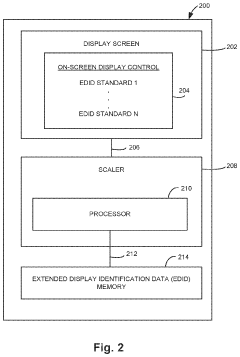

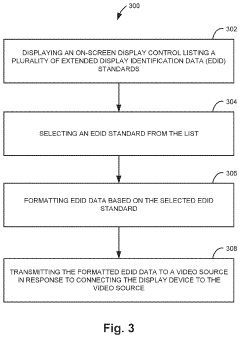

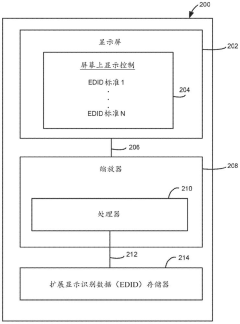

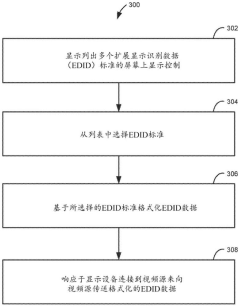

Selection of an extended display identification data standard

PatentActiveUS20210327392A1

Innovation

- A display device with on-screen display (OSD) control allows users to select from various EDID standards, such as VESA E-EDID, VESA Display-ID, and CEA 861, and enables the formatting and updating of EDID data to support preferred resolutions and refresh rates.

Expanded selection of display identification data criteria

PatentInactiveCN110462581B

Innovation

- By introducing on-screen display (OSD) control in display devices, users can choose the most suitable one from multiple EDID standards and format EDID data according to the selected standard, support different resolutions and refresh rates, and even allow Customized and encrypted EDID standard.

Interoperability Testing and Debugging Methodologies

Effective interoperability testing for DisplayPort 2.1 EDID/CTA Data Blocks requires systematic methodologies to identify and resolve timing conflicts, HDR metadata issues, and other compatibility challenges. A comprehensive testing framework should incorporate both automated and manual verification processes to ensure reliable detection of implementation discrepancies.

Protocol analyzers serve as primary diagnostic tools, capturing real-time data exchanges between source and sink devices. When investigating timing conflicts, these analyzers can pinpoint exact moments where EDID data block interpretation deviates from specifications, particularly in scenarios involving multiple display timing formats coexisting within the same descriptor blocks.

Cross-platform validation represents another critical testing dimension, where DisplayPort implementations must be verified across diverse hardware ecosystems. This includes testing against legacy systems to ensure backward compatibility while maintaining support for newer features like HDR metadata extensions.

Automated compliance test suites provide standardized verification of EDID/CTA data block handling. These tools can systematically exercise edge cases where timing conflicts commonly occur, such as when display devices advertise overlapping or contradictory timing capabilities. The most effective test suites incorporate reference golden files representing both compliant and non-compliant EDID structures.

For HDR metadata debugging specifically, specialized test patterns that exercise the full dynamic range capabilities are essential. These patterns should verify proper handling of static metadata (HDR10), dynamic metadata (HDR10+, Dolby Vision), and the correct signaling of color primaries and luminance parameters through the EDID/CTA extension blocks.

Field testing with real-world content represents the final validation layer, where actual media content with varying HDR characteristics is displayed across multiple sink devices. This helps identify subtle interoperability issues that might not manifest during synthetic testing.

Documentation of debugging procedures is equally important, establishing clear workflows for isolating whether timing conflicts originate from source misinterpretation or sink misrepresentation of capabilities. Effective debug logs should capture EDID read operations, parsing decisions, and final display mode selections to create an audit trail for troubleshooting.

Collaborative industry testing events provide valuable opportunities to verify implementations against a diverse ecosystem of devices, often revealing edge cases not covered by formal compliance tests. These events have proven particularly valuable for resolving HDR metadata interoperability challenges across the DisplayPort ecosystem.

Protocol analyzers serve as primary diagnostic tools, capturing real-time data exchanges between source and sink devices. When investigating timing conflicts, these analyzers can pinpoint exact moments where EDID data block interpretation deviates from specifications, particularly in scenarios involving multiple display timing formats coexisting within the same descriptor blocks.

Cross-platform validation represents another critical testing dimension, where DisplayPort implementations must be verified across diverse hardware ecosystems. This includes testing against legacy systems to ensure backward compatibility while maintaining support for newer features like HDR metadata extensions.

Automated compliance test suites provide standardized verification of EDID/CTA data block handling. These tools can systematically exercise edge cases where timing conflicts commonly occur, such as when display devices advertise overlapping or contradictory timing capabilities. The most effective test suites incorporate reference golden files representing both compliant and non-compliant EDID structures.

For HDR metadata debugging specifically, specialized test patterns that exercise the full dynamic range capabilities are essential. These patterns should verify proper handling of static metadata (HDR10), dynamic metadata (HDR10+, Dolby Vision), and the correct signaling of color primaries and luminance parameters through the EDID/CTA extension blocks.

Field testing with real-world content represents the final validation layer, where actual media content with varying HDR characteristics is displayed across multiple sink devices. This helps identify subtle interoperability issues that might not manifest during synthetic testing.

Documentation of debugging procedures is equally important, establishing clear workflows for isolating whether timing conflicts originate from source misinterpretation or sink misrepresentation of capabilities. Effective debug logs should capture EDID read operations, parsing decisions, and final display mode selections to create an audit trail for troubleshooting.

Collaborative industry testing events provide valuable opportunities to verify implementations against a diverse ecosystem of devices, often revealing edge cases not covered by formal compliance tests. These events have proven particularly valuable for resolving HDR metadata interoperability challenges across the DisplayPort ecosystem.

Compliance and Certification Requirements

DisplayPort 2.1 compliance and certification processes represent a critical framework ensuring interoperability across the display ecosystem. The Video Electronics Standards Association (VESA) has established comprehensive certification programs specifically addressing EDID/CTA data blocks implementation, with particular focus on resolving timing conflicts, standardizing HDR metadata transmission, and facilitating effective debugging protocols.

Manufacturers seeking DisplayPort 2.1 certification must submit their products to VESA-authorized test centers where specialized test equipment validates proper implementation of EDID (Extended Display Identification Data) and CTA (Consumer Technology Association) data blocks. These certification procedures include rigorous verification of timing parameters to identify and eliminate potential conflicts that could result in display artifacts or connection failures.

The certification process specifically examines how devices handle conflicting timing information between EDID blocks and CTA extensions. Products must demonstrate robust fallback mechanisms when encountering contradictory timing data, with priority given to CTA-861 timing extensions over legacy EDID timing descriptors as specified in the DisplayPort 2.1 standard.

For HDR metadata certification, devices must accurately process and transmit all mandatory HDR metadata formats including static metadata (HDR10), dynamic metadata (HDR10+), and Dolby Vision profiles. Testing procedures verify proper implementation of CTA-861.G HDR static metadata blocks and the optional dynamic metadata extensions. Source devices must correctly read and interpret these blocks, while display devices must accurately report their HDR capabilities.

Debug capabilities represent another critical certification requirement. Certified products must implement the mandatory debug interfaces specified in DisplayPort 2.1, including the ability to expose EDID/CTA parsing errors through standardized diagnostic interfaces. This facilitates field troubleshooting and enables system integrators to identify compatibility issues efficiently.

VESA has introduced a tiered certification approach for DisplayPort 2.1, with different compliance levels addressing various aspects of the specification. The "DisplayPort 2.1 EDID/CTA Compliance" certification specifically focuses on data block handling, while the comprehensive "DisplayPort 2.1 Full Compliance" certification encompasses all aspects of the standard including physical layer requirements.

The certification timeline typically requires 4-8 weeks for completion, with manufacturers receiving detailed compliance reports highlighting any identified issues. Products failing certification must address deficiencies and undergo retesting. Successfully certified products receive the official DisplayPort 2.1 certification mark and are listed in VESA's public certification database, providing consumers and integrators with confidence in product interoperability.

Manufacturers seeking DisplayPort 2.1 certification must submit their products to VESA-authorized test centers where specialized test equipment validates proper implementation of EDID (Extended Display Identification Data) and CTA (Consumer Technology Association) data blocks. These certification procedures include rigorous verification of timing parameters to identify and eliminate potential conflicts that could result in display artifacts or connection failures.

The certification process specifically examines how devices handle conflicting timing information between EDID blocks and CTA extensions. Products must demonstrate robust fallback mechanisms when encountering contradictory timing data, with priority given to CTA-861 timing extensions over legacy EDID timing descriptors as specified in the DisplayPort 2.1 standard.

For HDR metadata certification, devices must accurately process and transmit all mandatory HDR metadata formats including static metadata (HDR10), dynamic metadata (HDR10+), and Dolby Vision profiles. Testing procedures verify proper implementation of CTA-861.G HDR static metadata blocks and the optional dynamic metadata extensions. Source devices must correctly read and interpret these blocks, while display devices must accurately report their HDR capabilities.

Debug capabilities represent another critical certification requirement. Certified products must implement the mandatory debug interfaces specified in DisplayPort 2.1, including the ability to expose EDID/CTA parsing errors through standardized diagnostic interfaces. This facilitates field troubleshooting and enables system integrators to identify compatibility issues efficiently.

VESA has introduced a tiered certification approach for DisplayPort 2.1, with different compliance levels addressing various aspects of the specification. The "DisplayPort 2.1 EDID/CTA Compliance" certification specifically focuses on data block handling, while the comprehensive "DisplayPort 2.1 Full Compliance" certification encompasses all aspects of the standard including physical layer requirements.

The certification timeline typically requires 4-8 weeks for completion, with manufacturers receiving detailed compliance reports highlighting any identified issues. Products failing certification must address deficiencies and undergo retesting. Successfully certified products receive the official DisplayPort 2.1 certification mark and are listed in VESA's public certification database, providing consumers and integrators with confidence in product interoperability.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!