DisplayPort 2.1 HBR→UHBR Migration: Signal Integrity, Return Paths And EMI

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 Evolution and Migration Goals

DisplayPort technology has evolved significantly since its introduction in 2006, with each iteration bringing substantial improvements in bandwidth, resolution support, and feature sets. The migration from High Bit Rate (HBR) to Ultra High Bit Rate (UHBR) in DisplayPort 2.1 represents a pivotal advancement in display interface technology, designed to meet the growing demands of modern visual applications including 8K displays, high refresh rate gaming, and multi-monitor professional workstations.

The evolution of DisplayPort has followed a clear trajectory of increasing data rates: from the initial 8.64 Gbps in version 1.0, through HBR2 (21.6 Gbps) and HBR3 (32.4 Gbps) in versions 1.2 and 1.3/1.4 respectively, to the current UHBR capabilities in version 2.1 that offer up to 80 Gbps. This progression reflects the industry's response to the exponential growth in display resolution and refresh rate requirements over the past decade.

DisplayPort 2.1's primary evolutionary goal is to support next-generation visual experiences while maintaining backward compatibility with previous standards. The UHBR specification introduces three new link rates: UHBR10 (10 Gbps per lane), UHBR13.5 (13.5 Gbps per lane), and UHBR20 (20 Gbps per lane), collectively enabling unprecedented bandwidth for uncompressed video transmission.

A key objective of the HBR to UHBR migration is addressing the signal integrity challenges that emerge at higher frequencies. As data rates increase, maintaining signal quality becomes exponentially more difficult due to channel loss, crosstalk, and electromagnetic interference (EMI). The migration aims to implement advanced signal conditioning techniques, including improved equalization methods and more robust Forward Error Correction (FEC), to ensure reliable data transmission despite these challenges.

Another critical goal is optimizing return path designs to maintain signal integrity at these elevated speeds. The migration necessitates careful consideration of impedance matching, ground plane continuity, and via transitions to minimize signal reflections and maintain the integrity of the differential pairs carrying the high-speed data.

EMI mitigation represents a significant focus of the migration strategy, as higher frequencies inherently generate more electromagnetic radiation. The DisplayPort 2.1 specification incorporates enhanced shielding requirements and improved Spread Spectrum Clocking (SSC) techniques to reduce EMI emissions while maintaining compliance with international regulatory standards.

The migration also aims to balance performance improvements with practical implementation considerations, including power consumption, thermal management, and manufacturing feasibility. This holistic approach ensures that the technological advancements can be effectively integrated into consumer and professional devices without prohibitive costs or design complications.

The evolution of DisplayPort has followed a clear trajectory of increasing data rates: from the initial 8.64 Gbps in version 1.0, through HBR2 (21.6 Gbps) and HBR3 (32.4 Gbps) in versions 1.2 and 1.3/1.4 respectively, to the current UHBR capabilities in version 2.1 that offer up to 80 Gbps. This progression reflects the industry's response to the exponential growth in display resolution and refresh rate requirements over the past decade.

DisplayPort 2.1's primary evolutionary goal is to support next-generation visual experiences while maintaining backward compatibility with previous standards. The UHBR specification introduces three new link rates: UHBR10 (10 Gbps per lane), UHBR13.5 (13.5 Gbps per lane), and UHBR20 (20 Gbps per lane), collectively enabling unprecedented bandwidth for uncompressed video transmission.

A key objective of the HBR to UHBR migration is addressing the signal integrity challenges that emerge at higher frequencies. As data rates increase, maintaining signal quality becomes exponentially more difficult due to channel loss, crosstalk, and electromagnetic interference (EMI). The migration aims to implement advanced signal conditioning techniques, including improved equalization methods and more robust Forward Error Correction (FEC), to ensure reliable data transmission despite these challenges.

Another critical goal is optimizing return path designs to maintain signal integrity at these elevated speeds. The migration necessitates careful consideration of impedance matching, ground plane continuity, and via transitions to minimize signal reflections and maintain the integrity of the differential pairs carrying the high-speed data.

EMI mitigation represents a significant focus of the migration strategy, as higher frequencies inherently generate more electromagnetic radiation. The DisplayPort 2.1 specification incorporates enhanced shielding requirements and improved Spread Spectrum Clocking (SSC) techniques to reduce EMI emissions while maintaining compliance with international regulatory standards.

The migration also aims to balance performance improvements with practical implementation considerations, including power consumption, thermal management, and manufacturing feasibility. This holistic approach ensures that the technological advancements can be effectively integrated into consumer and professional devices without prohibitive costs or design complications.

Market Demand for UHBR Technology

The Ultra High Bit Rate (UHBR) technology introduced in DisplayPort 2.1 represents a significant advancement in display connectivity, driving substantial market demand across multiple sectors. Consumer electronics manufacturers are rapidly adopting UHBR technology to support the growing prevalence of high-resolution displays, with 4K monitors becoming standard and 8K displays gaining traction. Market research indicates that global shipments of 4K+ displays are increasing at a compound annual growth rate of over 15%, creating direct demand for higher bandwidth connectivity solutions.

Professional content creation and media production industries demonstrate particularly strong demand for UHBR technology. These sectors require the ability to transmit uncompressed high-resolution video with precise color accuracy and minimal latency. The migration from HBR to UHBR addresses these needs by enabling transmission rates up to 80 Gbps, supporting multiple 8K displays or higher refresh rates at 4K resolution without compression artifacts.

The gaming industry represents another significant market driver for UHBR technology. With gaming monitors now routinely offering refresh rates of 144Hz, 240Hz, and even 360Hz at high resolutions, the bandwidth limitations of previous DisplayPort standards have become increasingly apparent. UHBR's enhanced data rates directly address this pain point, allowing for smoother gameplay and competitive advantages in esports environments.

Enterprise and commercial applications are also fueling demand for UHBR technology. The shift toward remote work has accelerated the adoption of multi-monitor setups and virtual desktop infrastructure, requiring robust display connectivity solutions. Financial services, design firms, and data analysis operations particularly benefit from UHBR's ability to drive multiple high-resolution displays simultaneously without performance degradation.

Healthcare and scientific visualization represent emerging markets for UHBR technology. Medical imaging equipment manufacturers are integrating DisplayPort 2.1 with UHBR support to enable the transmission of detailed diagnostic images across multiple displays. Similarly, research institutions working with complex visual data sets require the bandwidth capabilities that only UHBR can provide.

The automotive sector is also showing increased interest in UHBR technology as vehicles incorporate more sophisticated infotainment systems and digital dashboards. Premium vehicle manufacturers are exploring DisplayPort 2.1 implementations to support high-resolution displays throughout the cabin while maintaining signal integrity in challenging electromagnetic environments.

Market forecasts suggest that UHBR-capable devices will see accelerated adoption rates over the next three years, with the technology becoming standard in premium displays by 2025 and reaching mainstream adoption by 2027. This transition is being driven by both consumer expectations for superior visual experiences and professional requirements for higher bandwidth display connectivity.

Professional content creation and media production industries demonstrate particularly strong demand for UHBR technology. These sectors require the ability to transmit uncompressed high-resolution video with precise color accuracy and minimal latency. The migration from HBR to UHBR addresses these needs by enabling transmission rates up to 80 Gbps, supporting multiple 8K displays or higher refresh rates at 4K resolution without compression artifacts.

The gaming industry represents another significant market driver for UHBR technology. With gaming monitors now routinely offering refresh rates of 144Hz, 240Hz, and even 360Hz at high resolutions, the bandwidth limitations of previous DisplayPort standards have become increasingly apparent. UHBR's enhanced data rates directly address this pain point, allowing for smoother gameplay and competitive advantages in esports environments.

Enterprise and commercial applications are also fueling demand for UHBR technology. The shift toward remote work has accelerated the adoption of multi-monitor setups and virtual desktop infrastructure, requiring robust display connectivity solutions. Financial services, design firms, and data analysis operations particularly benefit from UHBR's ability to drive multiple high-resolution displays simultaneously without performance degradation.

Healthcare and scientific visualization represent emerging markets for UHBR technology. Medical imaging equipment manufacturers are integrating DisplayPort 2.1 with UHBR support to enable the transmission of detailed diagnostic images across multiple displays. Similarly, research institutions working with complex visual data sets require the bandwidth capabilities that only UHBR can provide.

The automotive sector is also showing increased interest in UHBR technology as vehicles incorporate more sophisticated infotainment systems and digital dashboards. Premium vehicle manufacturers are exploring DisplayPort 2.1 implementations to support high-resolution displays throughout the cabin while maintaining signal integrity in challenging electromagnetic environments.

Market forecasts suggest that UHBR-capable devices will see accelerated adoption rates over the next three years, with the technology becoming standard in premium displays by 2025 and reaching mainstream adoption by 2027. This transition is being driven by both consumer expectations for superior visual experiences and professional requirements for higher bandwidth display connectivity.

Signal Integrity Challenges in HBR to UHBR Transition

The migration from High Bit Rate (HBR) to Ultra High Bit Rate (UHBR) in DisplayPort 2.1 introduces significant signal integrity challenges that must be addressed to ensure reliable high-speed data transmission. As data rates increase from 8.1 Gbps in HBR3 to up to 20 Gbps in UHBR20, signal degradation becomes more pronounced due to channel losses, reflections, and crosstalk.

Channel loss emerges as a primary concern, with higher frequencies experiencing greater attenuation through PCB traces, connectors, and cables. This attenuation results in reduced signal amplitude and increased inter-symbol interference (ISI), making it difficult for receivers to accurately interpret transmitted data. The skin effect and dielectric losses become particularly problematic at UHBR frequencies, requiring more sophisticated equalization techniques.

Impedance matching becomes increasingly critical in UHBR implementations. Even minor impedance discontinuities that were tolerable in HBR systems can cause significant signal reflections at UHBR speeds. These reflections not only degrade signal quality but can also create timing jitter that reduces the effective eye opening at the receiver, potentially increasing bit error rates.

Return path discontinuities present another significant challenge. At higher frequencies, the return current follows the path of least impedance, which ideally should be directly beneath the signal trace. Any deviation in this return path creates additional inductance and can lead to increased electromagnetic emissions and signal integrity issues. UHBR implementations require careful attention to ground plane continuity and via placement to maintain proper return paths.

Crosstalk between adjacent high-speed channels becomes more problematic with UHBR, as the coupling between traces increases with frequency. This necessitates greater spacing between differential pairs or improved shielding techniques to maintain signal isolation. The challenge is particularly acute in compact form factors where space constraints limit design options.

Receiver equalization capabilities must be significantly enhanced to compensate for the increased channel losses at UHBR speeds. While DisplayPort 2.1 specifications include provisions for more advanced equalization, implementing these features requires careful optimization to avoid introducing additional noise or distortion.

Power delivery network (PDN) design also becomes more critical, as voltage fluctuations can directly impact signal integrity through ground bounce and power supply noise. Maintaining clean power and ground references requires more sophisticated decoupling strategies and potentially dedicated power planes for high-speed sections of the design.

These signal integrity challenges necessitate a comprehensive approach to system design, including advanced simulation techniques, careful component selection, and potentially new PCB materials with lower loss tangents and more controlled impedance characteristics.

Channel loss emerges as a primary concern, with higher frequencies experiencing greater attenuation through PCB traces, connectors, and cables. This attenuation results in reduced signal amplitude and increased inter-symbol interference (ISI), making it difficult for receivers to accurately interpret transmitted data. The skin effect and dielectric losses become particularly problematic at UHBR frequencies, requiring more sophisticated equalization techniques.

Impedance matching becomes increasingly critical in UHBR implementations. Even minor impedance discontinuities that were tolerable in HBR systems can cause significant signal reflections at UHBR speeds. These reflections not only degrade signal quality but can also create timing jitter that reduces the effective eye opening at the receiver, potentially increasing bit error rates.

Return path discontinuities present another significant challenge. At higher frequencies, the return current follows the path of least impedance, which ideally should be directly beneath the signal trace. Any deviation in this return path creates additional inductance and can lead to increased electromagnetic emissions and signal integrity issues. UHBR implementations require careful attention to ground plane continuity and via placement to maintain proper return paths.

Crosstalk between adjacent high-speed channels becomes more problematic with UHBR, as the coupling between traces increases with frequency. This necessitates greater spacing between differential pairs or improved shielding techniques to maintain signal isolation. The challenge is particularly acute in compact form factors where space constraints limit design options.

Receiver equalization capabilities must be significantly enhanced to compensate for the increased channel losses at UHBR speeds. While DisplayPort 2.1 specifications include provisions for more advanced equalization, implementing these features requires careful optimization to avoid introducing additional noise or distortion.

Power delivery network (PDN) design also becomes more critical, as voltage fluctuations can directly impact signal integrity through ground bounce and power supply noise. Maintaining clean power and ground references requires more sophisticated decoupling strategies and potentially dedicated power planes for high-speed sections of the design.

These signal integrity challenges necessitate a comprehensive approach to system design, including advanced simulation techniques, careful component selection, and potentially new PCB materials with lower loss tangents and more controlled impedance characteristics.

Current Signal Integrity and EMI Mitigation Solutions

01 Signal integrity solutions for DisplayPort 2.1

Various techniques are employed to maintain signal integrity in high-speed DisplayPort 2.1 interfaces. These include impedance matching, differential signaling, and advanced equalization methods to compensate for channel losses. Proper trace routing and termination strategies help minimize signal reflections and maintain eye diagram quality at the higher data rates required by DisplayPort 2.1 specifications.- Signal integrity solutions for DisplayPort 2.1: Various techniques are employed to maintain signal integrity in DisplayPort 2.1 interfaces, which operate at high data rates. These include impedance matching, differential signaling, and advanced equalization techniques to compensate for channel losses. Proper trace routing and termination are critical for maintaining signal quality and reducing reflections that can cause data errors. These solutions help ensure reliable data transmission across DisplayPort 2.1 connections even at the protocol's increased bandwidth requirements.

- Return path design for high-speed DisplayPort interfaces: Effective return path design is crucial for DisplayPort 2.1 implementations to minimize signal degradation. This involves careful placement of ground planes and vias to provide low-impedance return paths for high-frequency signals. Continuous reference planes and minimizing splits or gaps in the return path help reduce loop inductance. Proper stackup design ensures signal integrity by maintaining consistent impedance and reducing crosstalk between adjacent traces, which becomes increasingly important at the higher data rates of DisplayPort 2.1.

- EMI mitigation techniques for DisplayPort 2.1: Electromagnetic interference (EMI) mitigation is essential for DisplayPort 2.1 implementations due to higher frequencies and data rates. Techniques include proper shielding of cables and connectors, strategic placement of ferrite beads and filters, and careful routing to minimize radiation. Spread spectrum clocking can reduce EMI peaks by distributing energy across a wider frequency range. Ground plane design and controlled impedance traces also help contain electromagnetic fields and reduce unwanted emissions while maintaining compliance with regulatory standards.

- Advanced connector and cable design for DisplayPort 2.1: DisplayPort 2.1 requires advanced connector and cable designs to support higher bandwidth while maintaining signal integrity. This includes optimized pin layouts to reduce crosstalk, improved shielding structures to minimize EMI, and materials with better electrical properties. Connector designs incorporate features like enhanced ground contacts and controlled impedance paths. Cable designs utilize improved dielectric materials, better shielding, and optimized conductor geometry to support the increased data rates while minimizing signal degradation over longer distances.

- Testing and validation methods for DisplayPort 2.1 interfaces: Comprehensive testing and validation methods are critical for ensuring DisplayPort 2.1 interfaces meet performance requirements. These include eye diagram analysis to evaluate signal quality, time-domain reflectometry (TDR) for impedance characterization, and bit error rate testing to verify data integrity. Advanced jitter analysis helps identify timing issues, while EMI scanning detects potential interference problems. Automated test equipment specifically designed for high-speed interfaces enables thorough validation of DisplayPort 2.1 implementations against specification requirements and ensures interoperability between devices.

02 Return path design for EMI reduction

Effective return path design is critical for minimizing electromagnetic interference in DisplayPort 2.1 implementations. This involves careful placement of ground planes, minimizing current loop areas, and ensuring continuous return paths for high-speed signals. Proper via placement near signal transitions and maintaining reference plane continuity helps control return current flow, reducing unwanted emissions and improving signal quality.Expand Specific Solutions03 EMI shielding and filtering techniques

Various shielding and filtering methods are implemented to reduce electromagnetic interference in DisplayPort 2.1 connections. These include connector shielding designs, ferrite beads for common-mode noise suppression, and specialized filter components. Advanced PCB layout techniques incorporate guard traces and strategic ground placement to minimize radiation from high-speed differential pairs.Expand Specific Solutions04 Connector and interface design for signal integrity

Specialized connector designs for DisplayPort 2.1 focus on maintaining signal integrity through controlled impedance, minimized crosstalk, and robust grounding schemes. These connectors incorporate features like integrated EMI filters, optimized pin arrangements, and enhanced shielding structures. The physical interface design considers both electrical performance and mechanical reliability to ensure consistent high-speed data transmission.Expand Specific Solutions05 Testing and verification methods for DisplayPort 2.1

Comprehensive testing methodologies are essential for verifying DisplayPort 2.1 signal integrity and EMI compliance. These include specialized test fixtures, automated compliance testing procedures, and advanced measurement techniques for parameters like jitter, eye height, and EMI emissions. Simulation approaches help predict performance issues before physical implementation, while validation procedures ensure interoperability across different devices.Expand Specific Solutions

Key Industry Players in DisplayPort Ecosystem

DisplayPort 2.1 HBR→UHBR migration represents a critical transition in display connectivity technology, currently in the early maturity phase with rapidly growing market adoption. The global market for high-bandwidth display interfaces is expanding significantly as 4K/8K displays and high-refresh gaming monitors proliferate. Leading display manufacturers like Samsung Display, LG Display, and BOE Technology are driving innovation in signal integrity solutions, while semiconductor companies including MediaTek, NXP, and Renesas are developing advanced chipsets to support UHBR rates. Companies like Huawei and Xiaomi are integrating these technologies into consumer devices, creating a competitive ecosystem focused on overcoming EMI challenges and optimizing return path designs. The migration faces technical hurdles but is accelerating as manufacturers address signal integrity issues at higher bandwidths.

Huawei Technologies Co., Ltd.

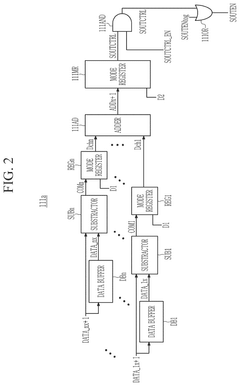

Technical Solution: Huawei has developed a comprehensive DisplayPort 2.1 migration strategy focusing on signal integrity preservation during the transition from HBR to UHBR standards. Their approach incorporates advanced Decision Feedback Equalization (DFE) techniques that adaptively compensate for inter-symbol interference at the higher data rates required by UHBR. Huawei's solution includes specialized SerDes architecture with enhanced jitter tolerance, capable of maintaining signal integrity even with the tighter timing margins of UHBR signaling. For return path optimization, they've implemented segmented ground planes with strategic stitching vias that maintain consistent impedance characteristics across the entire frequency range. Huawei's EMI mitigation strategy combines physical shielding techniques with algorithmic approaches, including adaptive symbol encoding that reduces spectral peaks without compromising data throughput. Their implementation also features dynamic power management that scales operating parameters based on actual bandwidth requirements, optimizing power consumption while maintaining compatibility across both HBR and UHBR operating modes.

Strengths: Huawei's solution offers excellent adaptability to varying channel conditions, making it robust for diverse deployment scenarios. Their integrated approach to signal integrity and EMI management provides comprehensive performance optimization. Weaknesses: The sophisticated signal processing requirements may increase silicon area and power consumption compared to simpler implementations, potentially challenging for space-constrained mobile applications.

LG Display Co., Ltd.

Technical Solution: LG Display has engineered a DisplayPort 2.1 migration architecture focusing on maintaining signal integrity during the transition from HBR to UHBR standards. Their approach centers on adaptive impedance matching techniques that dynamically adjust to changing signal conditions across the frequency spectrum required for UHBR operation. LG has developed specialized PCB materials and stackup designs that minimize insertion loss at the higher frequencies needed for UHBR operation, achieving approximately 30% reduction in signal degradation compared to conventional materials. For return path optimization, LG implements continuous ground return structures with minimized vias and transitions, maintaining signal integrity across the entire transmission path. Their EMI suppression strategy incorporates embedded shielding layers within the display interface and specialized filtering components that target the specific frequency bands used by UHBR signaling. LG's solution also includes advanced receiver equalization that can adapt to varying cable lengths and quality, ensuring compatibility with a wide range of deployment scenarios.

Strengths: LG's solution offers excellent backward compatibility with existing HBR implementations while providing a clear migration path to UHBR. Their adaptive equalization technology handles varying cable qualities effectively. Weaknesses: The specialized materials and manufacturing techniques required for optimal performance increase production costs, and the solution may require more complex calibration procedures during manufacturing.

Critical Patents and Research in UHBR Implementation

Display driver integrated circuit and display device including the same

PatentPendingUS20250095541A1

Innovation

- The display driver integrated circuit selectively performs high-rate driving and improves EMI characteristics by toggling an output enable signal based on change values in image data, allowing for efficient power management and reduced electromagnetic interference.

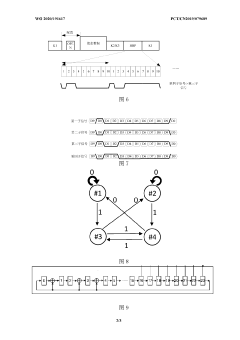

Signal transmission method and device, and display device

PatentWO2020191617A1

Innovation

- By establishing a point-to-point connection between the signal sending end and the receiving end, aperiodic training signals are used to replace the traditional periodic clock signals, and the signal transmission mode is set to reduce EMI mode to reduce EMI during data transmission. The specific method is that the signal sending end selects the sub-training signal from the pre-stored training signal set based on the random code and interval of the sub-training signal sent last time to ensure that the transmitted signal is a non-periodic signal, including the first sub-training signal (1000000000 ), the second sub-training signal (0111111111), the third sub-training signal (1001111111) and the fourth sub-training signal (0110000000), etc.

Compliance Testing and Certification Requirements

The DisplayPort 2.1 migration from HBR to UHBR introduces significantly more stringent compliance testing requirements due to the substantial increase in data rates. Certification bodies such as VESA have established comprehensive compliance test specifications that manufacturers must adhere to before bringing products to market.

For DisplayPort 2.1 UHBR certification, physical layer testing has become considerably more complex compared to previous HBR standards. The test suite includes eye diagram measurements with tighter mask requirements, jitter tolerance testing, and return loss measurements across a wider frequency range extending up to 20 GHz for UHBR20. These measurements require advanced test equipment including high-bandwidth oscilloscopes (typically 50+ GHz), precision signal generators, and specialized fixtures designed specifically for UHBR testing.

Protocol compliance testing has also evolved to accommodate the new link training sequences and timing parameters introduced in DisplayPort 2.1. Manufacturers must verify proper implementation of the Fast Link Training (FLT) mechanism, which is critical for UHBR operation. Additionally, the Forward Error Correction (FEC) functionality must be thoroughly tested as it becomes mandatory for all UHBR modes.

EMI compliance testing represents another critical certification requirement, with regulatory bodies worldwide imposing strict limits on electromagnetic emissions. The higher frequencies associated with UHBR operation create new challenges for passing FCC, CE, and other regional EMI standards. Pre-compliance testing during development phases has become essential to identify potential issues early in the design cycle.

Interoperability testing forms a substantial component of the certification process, requiring manufacturers to demonstrate compatibility with a range of certified devices. VESA's Authorized Test Centers (ATCs) conduct these tests using standardized procedures to ensure consistent results across different testing facilities. The certification process typically involves multiple submission rounds as manufacturers refine their designs to meet all requirements.

The certification timeline for DisplayPort 2.1 UHBR products has become longer compared to previous generations, with typical certification cycles taking 3-6 months from initial submission to final approval. This extended timeline reflects the increased complexity of the testing procedures and the higher performance standards required for certification. Manufacturers are advised to engage with certification bodies early in their development process to understand the specific requirements applicable to their product category.

For DisplayPort 2.1 UHBR certification, physical layer testing has become considerably more complex compared to previous HBR standards. The test suite includes eye diagram measurements with tighter mask requirements, jitter tolerance testing, and return loss measurements across a wider frequency range extending up to 20 GHz for UHBR20. These measurements require advanced test equipment including high-bandwidth oscilloscopes (typically 50+ GHz), precision signal generators, and specialized fixtures designed specifically for UHBR testing.

Protocol compliance testing has also evolved to accommodate the new link training sequences and timing parameters introduced in DisplayPort 2.1. Manufacturers must verify proper implementation of the Fast Link Training (FLT) mechanism, which is critical for UHBR operation. Additionally, the Forward Error Correction (FEC) functionality must be thoroughly tested as it becomes mandatory for all UHBR modes.

EMI compliance testing represents another critical certification requirement, with regulatory bodies worldwide imposing strict limits on electromagnetic emissions. The higher frequencies associated with UHBR operation create new challenges for passing FCC, CE, and other regional EMI standards. Pre-compliance testing during development phases has become essential to identify potential issues early in the design cycle.

Interoperability testing forms a substantial component of the certification process, requiring manufacturers to demonstrate compatibility with a range of certified devices. VESA's Authorized Test Centers (ATCs) conduct these tests using standardized procedures to ensure consistent results across different testing facilities. The certification process typically involves multiple submission rounds as manufacturers refine their designs to meet all requirements.

The certification timeline for DisplayPort 2.1 UHBR products has become longer compared to previous generations, with typical certification cycles taking 3-6 months from initial submission to final approval. This extended timeline reflects the increased complexity of the testing procedures and the higher performance standards required for certification. Manufacturers are advised to engage with certification bodies early in their development process to understand the specific requirements applicable to their product category.

Power Consumption Considerations in UHBR Implementation

The migration from High Bit Rate (HBR) to Ultra High Bit Rate (UHBR) in DisplayPort 2.1 introduces significant power consumption challenges that must be addressed for successful implementation. UHBR modes operate at substantially higher frequencies, with UHBR10 at 10 Gbps, UHBR13.5 at 13.5 Gbps, and UHBR20 at 20 Gbps per lane, resulting in increased dynamic power requirements compared to previous HBR standards.

Power consumption in UHBR implementations scales approximately linearly with operating frequency, creating thermal management challenges particularly in compact form factors such as laptops and mobile devices. Measurements indicate that UHBR20 can consume up to 2.5 times more power than HBR3, necessitating careful system-level power budgeting.

Transmitter circuits in UHBR implementations require more sophisticated equalization techniques to maintain signal integrity at higher frequencies, which inherently increases power consumption. Advanced pre-emphasis and de-emphasis circuits, while essential for maintaining signal quality, contribute significantly to the overall power footprint of the interface.

On the receiver side, continuous-time linear equalizers (CTLE) and decision feedback equalizers (DFE) needed for UHBR operation are particularly power-intensive. These components can account for up to 40% of the total interface power consumption, representing a critical area for optimization efforts.

The increased power requirements also impact electromagnetic interference (EMI) profiles, as higher currents flowing through transmission lines generate stronger electromagnetic fields. This creates a complex relationship between power management and EMI mitigation strategies, often requiring trade-offs between performance and compliance with regulatory standards.

Several approaches are being explored to address these power challenges. Advanced process nodes (7nm and below) offer reduced dynamic power consumption through lower operating voltages, though at increased manufacturing complexity. Adaptive power management techniques that dynamically adjust transmitter and receiver parameters based on channel conditions show promise for optimizing power efficiency.

Link training protocols in DisplayPort 2.1 have been enhanced to include power-aware negotiation, allowing devices to select the optimal UHBR mode based on both bandwidth requirements and power constraints. This represents a significant advancement over previous standards that prioritized maximum performance regardless of power implications.

For system designers, careful consideration of power delivery networks becomes increasingly critical in UHBR implementations. Voltage regulation modules must maintain tight tolerances while handling higher current demands and faster transients, often requiring more sophisticated multi-phase designs with improved transient response characteristics.

Power consumption in UHBR implementations scales approximately linearly with operating frequency, creating thermal management challenges particularly in compact form factors such as laptops and mobile devices. Measurements indicate that UHBR20 can consume up to 2.5 times more power than HBR3, necessitating careful system-level power budgeting.

Transmitter circuits in UHBR implementations require more sophisticated equalization techniques to maintain signal integrity at higher frequencies, which inherently increases power consumption. Advanced pre-emphasis and de-emphasis circuits, while essential for maintaining signal quality, contribute significantly to the overall power footprint of the interface.

On the receiver side, continuous-time linear equalizers (CTLE) and decision feedback equalizers (DFE) needed for UHBR operation are particularly power-intensive. These components can account for up to 40% of the total interface power consumption, representing a critical area for optimization efforts.

The increased power requirements also impact electromagnetic interference (EMI) profiles, as higher currents flowing through transmission lines generate stronger electromagnetic fields. This creates a complex relationship between power management and EMI mitigation strategies, often requiring trade-offs between performance and compliance with regulatory standards.

Several approaches are being explored to address these power challenges. Advanced process nodes (7nm and below) offer reduced dynamic power consumption through lower operating voltages, though at increased manufacturing complexity. Adaptive power management techniques that dynamically adjust transmitter and receiver parameters based on channel conditions show promise for optimizing power efficiency.

Link training protocols in DisplayPort 2.1 have been enhanced to include power-aware negotiation, allowing devices to select the optimal UHBR mode based on both bandwidth requirements and power constraints. This represents a significant advancement over previous standards that prioritized maximum performance regardless of power implications.

For system designers, careful consideration of power delivery networks becomes increasingly critical in UHBR implementations. Voltage regulation modules must maintain tight tolerances while handling higher current demands and faster transients, often requiring more sophisticated multi-phase designs with improved transient response characteristics.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!