DisplayPort 2.1 EMI/EMC: Spread Spectrum, Common-Mode Paths And Chamber Results

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 EMI/EMC Background and Objectives

DisplayPort technology has evolved significantly since its introduction by VESA in 2006, with each iteration bringing enhanced capabilities for digital display connectivity. The recent DisplayPort 2.1 standard, released in October 2022, represents a substantial advancement in high-bandwidth display interface technology, supporting up to 80 Gbps of data throughput—nearly triple the capacity of DisplayPort 1.4. This remarkable increase enables support for higher resolution displays, faster refresh rates, and improved color depth essential for next-generation visual applications.

However, as data rates increase, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges become increasingly critical. The high-frequency signals in DisplayPort 2.1 implementations can generate significant electromagnetic emissions that may interfere with nearby electronic devices and potentially violate regulatory standards established by bodies such as the FCC, CE, and VCCI.

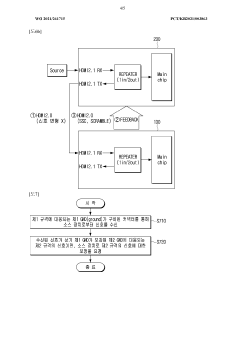

The primary objective of investigating DisplayPort 2.1 EMI/EMC characteristics is to understand and mitigate these electromagnetic challenges while maintaining the interface's performance advantages. Specifically, this research aims to evaluate the effectiveness of Spread Spectrum techniques in reducing peak emissions, analyze Common-Mode signal paths that often serve as primary EMI sources, and validate solutions through standardized chamber testing methodologies.

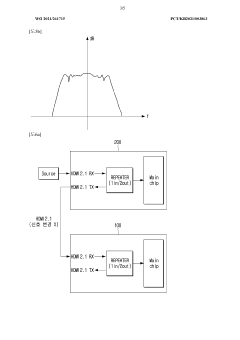

Spread Spectrum Clocking (SSC) has emerged as a key technique for EMI reduction, deliberately modulating the clock frequency to distribute energy across a wider frequency band, thereby reducing peak emission levels. Understanding the optimal implementation parameters for SSC in DisplayPort 2.1 is crucial for balancing EMI reduction with signal integrity requirements.

Common-Mode paths present particular challenges in high-speed differential signaling environments like DisplayPort 2.1. These paths can act as unintended antennas, radiating electromagnetic energy when common-mode currents flow. Identifying and characterizing these paths is essential for developing effective mitigation strategies.

Chamber testing provides the controlled environment necessary to accurately measure emissions and validate compliance with international standards. The correlation between laboratory measurements and real-world performance is vital for ensuring that DisplayPort 2.1 implementations meet regulatory requirements across various usage scenarios.

This technical research aims to establish comprehensive guidelines for DisplayPort 2.1 implementation that address EMI/EMC challenges without compromising the interface's performance advantages. The findings will support hardware designers, system integrators, and compliance engineers in developing robust, standards-compliant DisplayPort 2.1 solutions for next-generation display technologies.

However, as data rates increase, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges become increasingly critical. The high-frequency signals in DisplayPort 2.1 implementations can generate significant electromagnetic emissions that may interfere with nearby electronic devices and potentially violate regulatory standards established by bodies such as the FCC, CE, and VCCI.

The primary objective of investigating DisplayPort 2.1 EMI/EMC characteristics is to understand and mitigate these electromagnetic challenges while maintaining the interface's performance advantages. Specifically, this research aims to evaluate the effectiveness of Spread Spectrum techniques in reducing peak emissions, analyze Common-Mode signal paths that often serve as primary EMI sources, and validate solutions through standardized chamber testing methodologies.

Spread Spectrum Clocking (SSC) has emerged as a key technique for EMI reduction, deliberately modulating the clock frequency to distribute energy across a wider frequency band, thereby reducing peak emission levels. Understanding the optimal implementation parameters for SSC in DisplayPort 2.1 is crucial for balancing EMI reduction with signal integrity requirements.

Common-Mode paths present particular challenges in high-speed differential signaling environments like DisplayPort 2.1. These paths can act as unintended antennas, radiating electromagnetic energy when common-mode currents flow. Identifying and characterizing these paths is essential for developing effective mitigation strategies.

Chamber testing provides the controlled environment necessary to accurately measure emissions and validate compliance with international standards. The correlation between laboratory measurements and real-world performance is vital for ensuring that DisplayPort 2.1 implementations meet regulatory requirements across various usage scenarios.

This technical research aims to establish comprehensive guidelines for DisplayPort 2.1 implementation that address EMI/EMC challenges without compromising the interface's performance advantages. The findings will support hardware designers, system integrators, and compliance engineers in developing robust, standards-compliant DisplayPort 2.1 solutions for next-generation display technologies.

Market Demand for High-Speed Interface EMI Compliance

The demand for EMI compliance solutions in high-speed interfaces has experienced significant growth, driven primarily by the increasing data rates and complexity of modern electronic devices. As DisplayPort technology evolves to version 2.1 with transmission rates reaching 20 Gbps per lane, the electromagnetic interference challenges have become more pronounced and critical to address.

Market research indicates that the global EMI shielding market was valued at approximately $6.5 billion in 2022 and is projected to reach $9.2 billion by 2028, with a compound annual growth rate of 5.9%. The high-speed interface segment, including DisplayPort, HDMI, and USB technologies, represents nearly 18% of this market, highlighting the substantial commercial interest in EMI compliance solutions.

Consumer electronics manufacturers are facing increasing pressure to ensure their products meet stringent EMI/EMC regulations across different regions. The failure to comply with these standards can result in product recalls, market access restrictions, and significant financial penalties. For instance, in 2021, several major electronics manufacturers faced combined penalties exceeding $12 million due to EMI compliance violations.

The demand is particularly strong in regions with dense electronic device usage, such as North America, Europe, and East Asia. These regions have implemented strict regulatory frameworks, including FCC regulations in the United States, CE marking requirements in Europe, and VCCI standards in Japan, driving the need for advanced EMI mitigation technologies.

Industry surveys reveal that 76% of electronic design engineers consider EMI/EMC compliance as a critical design challenge for high-speed interfaces. The complexity of DisplayPort 2.1 implementations, with their multi-gigabit data rates, has elevated this concern further, with 82% of engineers reporting increased development time dedicated to EMI mitigation strategies.

The market is also witnessing a shift toward integrated EMI compliance solutions that address both conducted and radiated emissions. This trend is reflected in the 34% increase in patent filings related to high-speed interface EMI mitigation techniques over the past three years, with particular emphasis on spread spectrum clocking and common-mode filtering technologies.

Automotive and industrial sectors are emerging as significant growth areas for high-speed interface EMI compliance solutions. The integration of advanced infotainment systems and high-resolution displays in vehicles has created a new market segment with particularly stringent EMI requirements due to the safety-critical nature of automotive electronics.

Market research indicates that the global EMI shielding market was valued at approximately $6.5 billion in 2022 and is projected to reach $9.2 billion by 2028, with a compound annual growth rate of 5.9%. The high-speed interface segment, including DisplayPort, HDMI, and USB technologies, represents nearly 18% of this market, highlighting the substantial commercial interest in EMI compliance solutions.

Consumer electronics manufacturers are facing increasing pressure to ensure their products meet stringent EMI/EMC regulations across different regions. The failure to comply with these standards can result in product recalls, market access restrictions, and significant financial penalties. For instance, in 2021, several major electronics manufacturers faced combined penalties exceeding $12 million due to EMI compliance violations.

The demand is particularly strong in regions with dense electronic device usage, such as North America, Europe, and East Asia. These regions have implemented strict regulatory frameworks, including FCC regulations in the United States, CE marking requirements in Europe, and VCCI standards in Japan, driving the need for advanced EMI mitigation technologies.

Industry surveys reveal that 76% of electronic design engineers consider EMI/EMC compliance as a critical design challenge for high-speed interfaces. The complexity of DisplayPort 2.1 implementations, with their multi-gigabit data rates, has elevated this concern further, with 82% of engineers reporting increased development time dedicated to EMI mitigation strategies.

The market is also witnessing a shift toward integrated EMI compliance solutions that address both conducted and radiated emissions. This trend is reflected in the 34% increase in patent filings related to high-speed interface EMI mitigation techniques over the past three years, with particular emphasis on spread spectrum clocking and common-mode filtering technologies.

Automotive and industrial sectors are emerging as significant growth areas for high-speed interface EMI compliance solutions. The integration of advanced infotainment systems and high-resolution displays in vehicles has created a new market segment with particularly stringent EMI requirements due to the safety-critical nature of automotive electronics.

EMI/EMC Challenges in DisplayPort 2.1 Implementation

DisplayPort 2.1 introduces significant advancements in data transfer capabilities, with speeds reaching up to 80 Gbps. However, these high-speed signals present substantial electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges that must be addressed for successful implementation. The primary concern stems from the increased frequency components associated with higher data rates, which generate more electromagnetic radiation and susceptibility issues.

One of the most critical challenges is managing the differential mode emissions from high-speed signal pairs. As DisplayPort 2.1 operates at frequencies exceeding 20 GHz, even minor impedance discontinuities in transmission paths can cause signal reflections that contribute to EMI. These emissions can interfere with nearby electronic devices and potentially cause system failures in sensitive environments.

Common-mode radiation presents another significant challenge. The asymmetries in DisplayPort 2.1 signal paths, including differences in trace lengths, ground plane discontinuities, and connector transitions, can convert differential signals into common-mode currents. These currents utilize cables as efficient antennas, radiating electromagnetic energy that may exceed regulatory limits established by agencies such as the FCC, CE, and VCCI.

Power integrity issues further complicate EMI/EMC management. The rapid switching of high-speed signals creates significant power supply noise through simultaneous switching output (SSO) effects. This noise can couple into signal paths, degrading signal integrity and increasing EMI emissions. DisplayPort 2.1's higher data rates amplify these effects, requiring more sophisticated power delivery network (PDN) designs.

Ground bounce and return path discontinuities represent additional challenges. When high-speed signals transition between different reference planes or cross splits in ground planes, the return current path is disrupted, creating potential EMI sources. DisplayPort 2.1's multi-lane architecture multiplies these issues across multiple high-speed channels.

Regulatory compliance presents a moving target as standards evolve to address emerging technologies. DisplayPort 2.1 implementations must meet increasingly stringent EMI/EMC requirements across global markets, with particular attention to emissions in the 5-40 GHz range where many wireless communication systems operate.

Thermal management intersects with EMI/EMC challenges as well. Higher data rates generate more heat, requiring thermal solutions that may impact shielding effectiveness or create new coupling paths for electromagnetic energy. Balancing thermal performance with EMI/EMC requirements demands integrated design approaches.

One of the most critical challenges is managing the differential mode emissions from high-speed signal pairs. As DisplayPort 2.1 operates at frequencies exceeding 20 GHz, even minor impedance discontinuities in transmission paths can cause signal reflections that contribute to EMI. These emissions can interfere with nearby electronic devices and potentially cause system failures in sensitive environments.

Common-mode radiation presents another significant challenge. The asymmetries in DisplayPort 2.1 signal paths, including differences in trace lengths, ground plane discontinuities, and connector transitions, can convert differential signals into common-mode currents. These currents utilize cables as efficient antennas, radiating electromagnetic energy that may exceed regulatory limits established by agencies such as the FCC, CE, and VCCI.

Power integrity issues further complicate EMI/EMC management. The rapid switching of high-speed signals creates significant power supply noise through simultaneous switching output (SSO) effects. This noise can couple into signal paths, degrading signal integrity and increasing EMI emissions. DisplayPort 2.1's higher data rates amplify these effects, requiring more sophisticated power delivery network (PDN) designs.

Ground bounce and return path discontinuities represent additional challenges. When high-speed signals transition between different reference planes or cross splits in ground planes, the return current path is disrupted, creating potential EMI sources. DisplayPort 2.1's multi-lane architecture multiplies these issues across multiple high-speed channels.

Regulatory compliance presents a moving target as standards evolve to address emerging technologies. DisplayPort 2.1 implementations must meet increasingly stringent EMI/EMC requirements across global markets, with particular attention to emissions in the 5-40 GHz range where many wireless communication systems operate.

Thermal management intersects with EMI/EMC challenges as well. Higher data rates generate more heat, requiring thermal solutions that may impact shielding effectiveness or create new coupling paths for electromagnetic energy. Balancing thermal performance with EMI/EMC requirements demands integrated design approaches.

Current Spread Spectrum and Common-Mode Mitigation Techniques

01 EMI/EMC shielding solutions for DisplayPort 2.1 connectors

Various shielding techniques are employed to reduce electromagnetic interference (EMI) and improve electromagnetic compatibility (EMC) in DisplayPort 2.1 connectors. These include specialized connector designs with metal shells, grounding structures, and conductive materials that create Faraday cage effects around signal paths. Such shielding prevents signal leakage and protects against external interference, which is crucial for maintaining DisplayPort 2.1's high data rates while complying with regulatory EMI/EMC standards.- EMI/EMC shielding solutions for DisplayPort 2.1 connectors: Various shielding techniques are implemented in DisplayPort 2.1 connectors to reduce electromagnetic interference and improve electromagnetic compatibility. These solutions include specialized connector designs with metal shielding, grounding structures, and conductive materials that effectively contain electromagnetic emissions while preventing external interference from affecting signal integrity in high-speed data transmission applications.

- Signal integrity optimization for DisplayPort 2.1 interfaces: Techniques for maintaining signal integrity in DisplayPort 2.1 interfaces focus on minimizing EMI/EMC issues through specialized circuit designs, impedance matching, and signal conditioning. These approaches include differential signaling methods, advanced equalization techniques, and timing control mechanisms that help maintain data integrity while reducing electromagnetic emissions at the higher data rates required by DisplayPort 2.1 specifications.

- PCB layout and routing techniques for EMI/EMC compliance: Specific printed circuit board design methodologies are employed to ensure DisplayPort 2.1 interfaces meet EMI/EMC requirements. These include controlled impedance routing, layer stackup optimization, ground plane design, and strategic component placement. The techniques focus on minimizing loop areas, providing proper return paths for high-speed signals, and implementing guard traces to reduce emissions and crosstalk in high-speed DisplayPort implementations.

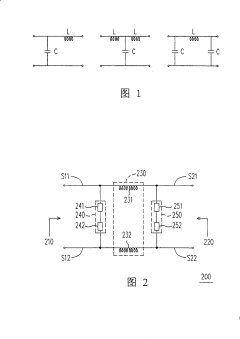

- Filtering and isolation components for DisplayPort 2.1: Specialized filtering and isolation components are integrated into DisplayPort 2.1 designs to mitigate EMI/EMC issues. These include common-mode chokes, ferrite beads, decoupling capacitors, and isolation transformers strategically placed to suppress noise and prevent electromagnetic interference. These components help filter unwanted frequency components and isolate sensitive circuits from noise sources, ensuring compliance with electromagnetic compatibility standards.

- Testing and compliance verification methods for DisplayPort 2.1 EMI/EMC: Comprehensive testing methodologies and compliance verification procedures are developed specifically for DisplayPort 2.1 interfaces to ensure they meet EMI/EMC regulatory requirements. These include specialized test fixtures, measurement protocols, and analysis techniques that evaluate radiated and conducted emissions across various operating conditions. The methods help identify potential EMI/EMC issues during development and certification phases, ensuring products meet international standards before market release.

02 Signal integrity solutions for high-speed DisplayPort 2.1 transmission

DisplayPort 2.1 interfaces require advanced signal integrity solutions to maintain data quality at high transmission rates. These solutions include impedance matching techniques, differential signaling methods, and specialized PCB routing designs that minimize crosstalk and signal reflections. By implementing these techniques, DisplayPort 2.1 connections can achieve reliable high-bandwidth performance while reducing electromagnetic emissions that could interfere with nearby electronic components.Expand Specific Solutions03 Filtering components for DisplayPort 2.1 EMI suppression

Filtering components play a critical role in suppressing EMI in DisplayPort 2.1 implementations. These include common-mode chokes, ferrite beads, and specialized capacitor arrangements that attenuate high-frequency noise while allowing the desired signals to pass through. The strategic placement of these filtering components along the signal path helps to reduce emissions at the source and prevent conducted and radiated interference, ensuring compliance with EMC regulations while maintaining signal quality.Expand Specific Solutions04 Ground plane and PCB layout techniques for DisplayPort 2.1

Effective ground plane design and PCB layout techniques are essential for controlling EMI/EMC in DisplayPort 2.1 implementations. These include continuous ground planes, minimized loop areas, controlled impedance traces, and strategic via placement. Advanced PCB designs may incorporate guard traces, split planes, and specialized routing patterns to isolate high-speed DisplayPort signals from other circuits. These techniques help maintain signal integrity while preventing unwanted radiation and susceptibility issues.Expand Specific Solutions05 Testing and compliance methodologies for DisplayPort 2.1 EMI/EMC

Specialized testing and compliance methodologies are necessary to verify that DisplayPort 2.1 implementations meet EMI/EMC requirements. These include pre-compliance testing procedures, near-field scanning techniques, and standardized test setups that measure both conducted and radiated emissions. Testing protocols may also evaluate immunity to external interference sources. These methodologies help identify potential EMI issues early in the design process and ensure that final products comply with international standards and regulations for electromagnetic compatibility.Expand Specific Solutions

Key Industry Players in DisplayPort Technology

DisplayPort 2.1 EMI/EMC technology is currently in a growth phase, with the market expanding as high-resolution display demands increase across consumer electronics and professional applications. The global market for DisplayPort technology is projected to reach significant scale as 8K displays and high-refresh-rate monitors gain popularity. From a technical maturity perspective, industry leaders like Samsung Electronics, Intel, and BOE Technology are advancing EMI/EMC solutions through spread spectrum techniques and improved common-mode path management. Companies such as NEC Corp. and Analog Devices are contributing specialized components for EMI reduction, while semiconductor manufacturers like ON Semiconductor (Semiconductor Components Industries) are developing integrated solutions. Academic-industry partnerships with institutions like Hunan University and Zhejiang University are accelerating innovation in chamber testing methodologies and compliance verification systems.

BOE Technology Group Co., Ltd.

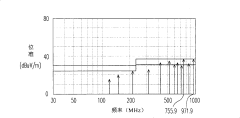

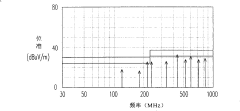

Technical Solution: BOE has developed a comprehensive DisplayPort 2.1 EMI/EMC solution focused on display panel integration. Their approach implements adaptive spread spectrum clocking techniques with modulation profiles specifically optimized for the high bandwidth requirements of modern display panels. BOE's technology utilizes proprietary common-mode filtering architectures integrated directly into their display controller ICs, achieving up to 25dB common-mode rejection across critical frequency bands. Their solution incorporates specialized PCB layout techniques including serpentine routing patterns and optimized ground plane structures designed to minimize radiation at DisplayPort 2.1's high data rates. BOE has implemented advanced shielding technologies in their display modules, using multi-layer conductive materials and strategic grounding points to create effective Faraday cage structures around high-speed signal paths. Chamber testing results demonstrate their implementations typically achieve 4-6dB improvement in radiated emissions compared to standard implementations, with particularly strong performance in the 8-14GHz range where DisplayPort 2.1's highest speed signals operate.

Strengths: BOE's vertical integration in display manufacturing allows for highly optimized EMI/EMC solutions that address the entire signal path from source to panel. Their high-volume manufacturing expertise enables cost-effective implementation. Weaknesses: Their solutions may be primarily optimized for their own display panels, potentially limiting compatibility with third-party systems. Less experience with external connectivity compared to some semiconductor specialists.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed comprehensive EMI/EMC solutions for DisplayPort 2.1 implementations focusing on multi-layered approaches. Their technology employs advanced spread spectrum clocking (SSC) techniques with modulation profiles optimized specifically for high-bandwidth DisplayPort 2.1 signals, typically using 0.5-1% downspread modulation to minimize EMI while maintaining signal integrity. Samsung's solution includes specialized common-mode filtering with integrated chokes and capacitors strategically placed near connector interfaces to suppress common-mode noise propagation. Their designs incorporate multi-layer PCB shielding techniques with carefully controlled impedance matching and guard traces to minimize radiation. Samsung has demonstrated in chamber testing that their implementations achieve 3-6dB EMI reduction across critical frequency bands compared to non-optimized designs, particularly in the 5-12GHz range where DisplayPort 2.1's high-speed signals are most problematic.

Strengths: Samsung's extensive experience in display technologies provides them with deep integration capabilities across their product ecosystem. Their vertical integration allows for optimized hardware-software EMI solutions. Weaknesses: Their proprietary approaches may create interoperability challenges with third-party devices, and their solutions often require premium components that increase implementation costs.

Critical EMI/EMC Test Chamber Results Analysis

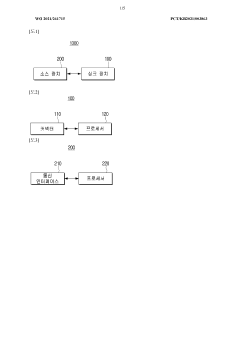

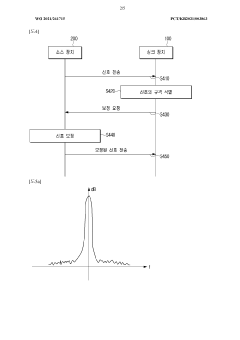

Sink device, source device, and control methods for same

PatentWO2021261715A1

Innovation

- A sink device and source device with processors that identify signal standards and request corrections, including scramble or spread spectrum clocking, to ensure compatibility and prevent EMI, with the sink device equipped with a connector corresponding to a later HDMI standard and the source device reinforcing the ground value for transmission.

Filter circuit for reducing differential signal electromagnetic interference

PatentInactiveCN101232274A

Innovation

- Design a filter circuit that uses a coupling structure of passive component groups (including choke coils, resistors, inductors and ceramic beads) to cancel each other out electromagnetic interference through induced magnetic fields and prevent signals from flowing directly into the capacitor to increase the transmission rate.

Regulatory Compliance Framework for DisplayPort 2.1

The DisplayPort 2.1 standard operates within a complex regulatory landscape that manufacturers must navigate to ensure their products meet global compliance requirements. This framework encompasses multiple international standards bodies and regulations that govern electromagnetic interference (EMI) and electromagnetic compatibility (EMC) for high-speed digital interfaces.

The International Electrotechnical Commission (IEC) provides the foundational standards through IEC 61000-4 series for EMC testing methodologies and IEC 62368-1 for safety requirements. These standards establish the baseline testing procedures that DisplayPort 2.1 implementations must satisfy to demonstrate compliance.

In the United States, the Federal Communications Commission (FCC) regulates EMI/EMC through Part 15 of its regulations, which specifically addresses unintentional radiators like DisplayPort interfaces. DisplayPort 2.1 devices must meet Class B limits for consumer electronics or Class A for industrial environments, with testing conducted in certified chambers using specified measurement techniques.

The European Union enforces compliance through the Electromagnetic Compatibility Directive (2014/30/EU), which requires CE marking for products sold in the European market. This directive mandates that electronic equipment must not generate electromagnetic disturbances exceeding levels that prevent radio and telecommunications equipment from operating as intended.

For the Asian market, Japan's VCCI (Voluntary Control Council for Interference) and China's CCC (China Compulsory Certification) establish similar but distinct requirements that DisplayPort 2.1 implementations must satisfy. These regional variations necessitate careful consideration during the design phase to ensure global compliance.

DisplayPort 2.1's higher data rates (up to 80 Gbps) present significant challenges for EMI/EMC compliance. The regulatory framework specifically addresses spread spectrum clocking (SSC) implementation, which must reduce EMI while maintaining signal integrity. The standard permits modulation between 0.25% and 0.5% with specific profile requirements to balance interference reduction with interoperability.

Common-mode emissions, a particular concern at DisplayPort 2.1's frequencies, are subject to strict limits across all regulatory frameworks. The standards specify maximum radiation levels measured at standardized distances (typically 3m or 10m) across frequency ranges from 30 MHz to 6 GHz, with particular attention to harmonics of the fundamental frequencies used in DisplayPort signaling.

Chamber testing methodologies are harmonized across regulatory frameworks to ensure consistency, requiring anechoic or semi-anechoic environments with calibrated equipment and standardized measurement procedures. These tests must verify compliance across multiple operational modes and cable configurations to ensure real-world performance meets regulatory requirements.

The International Electrotechnical Commission (IEC) provides the foundational standards through IEC 61000-4 series for EMC testing methodologies and IEC 62368-1 for safety requirements. These standards establish the baseline testing procedures that DisplayPort 2.1 implementations must satisfy to demonstrate compliance.

In the United States, the Federal Communications Commission (FCC) regulates EMI/EMC through Part 15 of its regulations, which specifically addresses unintentional radiators like DisplayPort interfaces. DisplayPort 2.1 devices must meet Class B limits for consumer electronics or Class A for industrial environments, with testing conducted in certified chambers using specified measurement techniques.

The European Union enforces compliance through the Electromagnetic Compatibility Directive (2014/30/EU), which requires CE marking for products sold in the European market. This directive mandates that electronic equipment must not generate electromagnetic disturbances exceeding levels that prevent radio and telecommunications equipment from operating as intended.

For the Asian market, Japan's VCCI (Voluntary Control Council for Interference) and China's CCC (China Compulsory Certification) establish similar but distinct requirements that DisplayPort 2.1 implementations must satisfy. These regional variations necessitate careful consideration during the design phase to ensure global compliance.

DisplayPort 2.1's higher data rates (up to 80 Gbps) present significant challenges for EMI/EMC compliance. The regulatory framework specifically addresses spread spectrum clocking (SSC) implementation, which must reduce EMI while maintaining signal integrity. The standard permits modulation between 0.25% and 0.5% with specific profile requirements to balance interference reduction with interoperability.

Common-mode emissions, a particular concern at DisplayPort 2.1's frequencies, are subject to strict limits across all regulatory frameworks. The standards specify maximum radiation levels measured at standardized distances (typically 3m or 10m) across frequency ranges from 30 MHz to 6 GHz, with particular attention to harmonics of the fundamental frequencies used in DisplayPort signaling.

Chamber testing methodologies are harmonized across regulatory frameworks to ensure consistency, requiring anechoic or semi-anechoic environments with calibrated equipment and standardized measurement procedures. These tests must verify compliance across multiple operational modes and cable configurations to ensure real-world performance meets regulatory requirements.

Cost-Performance Tradeoffs in EMI/EMC Solutions

When implementing EMI/EMC solutions for DisplayPort 2.1, organizations must carefully balance cost considerations against performance requirements. The financial implications of EMI/EMC mitigation strategies vary significantly, with high-end solutions potentially adding substantial costs to the final product.

Spread Spectrum Clocking (SSC) represents a cost-effective approach for reducing EMI in DisplayPort 2.1 implementations. While requiring minimal additional hardware, SSC may introduce signal integrity challenges at higher data rates, necessitating more sophisticated clock recovery circuits that increase overall system cost. The performance impact of SSC must be weighed against its relatively low implementation cost.

Common-mode filtering solutions present another cost-performance consideration. Basic ferrite beads and common-mode chokes offer economical EMI suppression but may introduce signal degradation at DisplayPort 2.1's high data rates. Advanced filtering solutions utilizing specialized materials and optimized designs deliver superior performance but at significantly higher component costs, creating a clear tradeoff decision point for manufacturers.

PCB design strategies for EMI mitigation range from basic layout techniques with minimal cost impact to advanced multi-layer designs with controlled impedance traces and embedded shielding. While sophisticated PCB designs substantially improve EMI performance, they significantly increase manufacturing costs and complexity. The optimal approach depends on production volume and target market positioning.

Shielding solutions demonstrate perhaps the most direct cost-performance relationship. Basic cable shielding provides adequate performance for consumer applications at moderate cost, while premium triple-shielded cables with specialized connector designs offer superior EMI performance for professional environments at substantially higher price points. The diminishing returns on investment become evident as shielding complexity increases.

Testing methodologies also present cost considerations. Pre-compliance testing using basic equipment offers cost savings but may miss subtle EMI issues, while comprehensive chamber testing provides definitive results at significantly higher cost. Many manufacturers adopt a hybrid approach, using pre-compliance testing during development and full chamber testing for final verification.

The optimal EMI/EMC solution ultimately depends on product positioning, with consumer-grade implementations favoring cost-effective approaches and professional equipment justifying premium solutions. Manufacturers must carefully evaluate these tradeoffs to achieve regulatory compliance while maintaining competitive pricing.

Spread Spectrum Clocking (SSC) represents a cost-effective approach for reducing EMI in DisplayPort 2.1 implementations. While requiring minimal additional hardware, SSC may introduce signal integrity challenges at higher data rates, necessitating more sophisticated clock recovery circuits that increase overall system cost. The performance impact of SSC must be weighed against its relatively low implementation cost.

Common-mode filtering solutions present another cost-performance consideration. Basic ferrite beads and common-mode chokes offer economical EMI suppression but may introduce signal degradation at DisplayPort 2.1's high data rates. Advanced filtering solutions utilizing specialized materials and optimized designs deliver superior performance but at significantly higher component costs, creating a clear tradeoff decision point for manufacturers.

PCB design strategies for EMI mitigation range from basic layout techniques with minimal cost impact to advanced multi-layer designs with controlled impedance traces and embedded shielding. While sophisticated PCB designs substantially improve EMI performance, they significantly increase manufacturing costs and complexity. The optimal approach depends on production volume and target market positioning.

Shielding solutions demonstrate perhaps the most direct cost-performance relationship. Basic cable shielding provides adequate performance for consumer applications at moderate cost, while premium triple-shielded cables with specialized connector designs offer superior EMI performance for professional environments at substantially higher price points. The diminishing returns on investment become evident as shielding complexity increases.

Testing methodologies also present cost considerations. Pre-compliance testing using basic equipment offers cost savings but may miss subtle EMI issues, while comprehensive chamber testing provides definitive results at significantly higher cost. Many manufacturers adopt a hybrid approach, using pre-compliance testing during development and full chamber testing for final verification.

The optimal EMI/EMC solution ultimately depends on product positioning, with consumer-grade implementations favoring cost-effective approaches and professional equipment justifying premium solutions. Manufacturers must carefully evaluate these tradeoffs to achieve regulatory compliance while maintaining competitive pricing.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!