How DisplayPort 2.1 Maintains UHBR10/13.5 Eye Integrity Over Real Type-C Paths?

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 Evolution and Technical Objectives

DisplayPort technology has evolved significantly since its introduction by VESA in 2006, progressing through multiple iterations to address the growing demands of high-resolution displays and complex multimedia applications. The evolution from DisplayPort 1.0 to the current 2.1 specification represents a continuous effort to increase bandwidth, enhance feature sets, and improve compatibility with various connection types.

DisplayPort 2.1, released in late 2022, builds upon the foundation established by DisplayPort 2.0, maintaining backward compatibility while introducing critical refinements specifically targeting USB Type-C implementation challenges. This version addresses the increasing market demand for higher resolution displays, faster refresh rates, and improved color depth across professional and consumer applications.

The primary technical objective of DisplayPort 2.1 is to maintain signal integrity at Ultra High Bit Rate (UHBR) speeds—particularly UHBR10 (10 Gbps per lane) and UHBR13.5 (13.5 Gbps per lane)—when transmitted through USB Type-C cables and connectors. This represents a significant engineering challenge as these data rates push the physical limitations of conventional copper interconnects.

A key focus area in DisplayPort 2.1 is the implementation of advanced signal conditioning techniques to preserve eye diagram integrity across real-world Type-C paths. The "eye pattern" or "eye diagram" is a critical measurement tool in digital communications, representing the overlay of multiple bit periods to visualize signal quality. Maintaining an open "eye" ensures reliable data transmission with minimal bit errors.

DisplayPort 2.1 introduces enhanced Forward Error Correction (FEC) algorithms and improved equalization techniques specifically optimized for the electrical characteristics of USB Type-C connections. These improvements aim to compensate for signal degradation caused by factors such as cable length, connector quality, and electromagnetic interference.

Another significant technical objective is the standardization of link training procedures that can dynamically adapt to varying cable qualities and lengths. This adaptive approach allows the system to establish the optimal signaling parameters for each specific connection scenario, maximizing performance while maintaining reliability.

DisplayPort 2.1 also aims to improve interoperability with other protocols that utilize USB Type-C, such as USB4 and Thunderbolt. This multi-protocol support is crucial for modern computing ecosystems where a single physical port must accommodate various connection types and functions.

The specification further addresses power management considerations, recognizing that high-speed data transmission can generate significant heat in compact devices. Thermal management techniques and power-efficient signaling are incorporated to maintain performance while minimizing energy consumption and heat generation.

DisplayPort 2.1, released in late 2022, builds upon the foundation established by DisplayPort 2.0, maintaining backward compatibility while introducing critical refinements specifically targeting USB Type-C implementation challenges. This version addresses the increasing market demand for higher resolution displays, faster refresh rates, and improved color depth across professional and consumer applications.

The primary technical objective of DisplayPort 2.1 is to maintain signal integrity at Ultra High Bit Rate (UHBR) speeds—particularly UHBR10 (10 Gbps per lane) and UHBR13.5 (13.5 Gbps per lane)—when transmitted through USB Type-C cables and connectors. This represents a significant engineering challenge as these data rates push the physical limitations of conventional copper interconnects.

A key focus area in DisplayPort 2.1 is the implementation of advanced signal conditioning techniques to preserve eye diagram integrity across real-world Type-C paths. The "eye pattern" or "eye diagram" is a critical measurement tool in digital communications, representing the overlay of multiple bit periods to visualize signal quality. Maintaining an open "eye" ensures reliable data transmission with minimal bit errors.

DisplayPort 2.1 introduces enhanced Forward Error Correction (FEC) algorithms and improved equalization techniques specifically optimized for the electrical characteristics of USB Type-C connections. These improvements aim to compensate for signal degradation caused by factors such as cable length, connector quality, and electromagnetic interference.

Another significant technical objective is the standardization of link training procedures that can dynamically adapt to varying cable qualities and lengths. This adaptive approach allows the system to establish the optimal signaling parameters for each specific connection scenario, maximizing performance while maintaining reliability.

DisplayPort 2.1 also aims to improve interoperability with other protocols that utilize USB Type-C, such as USB4 and Thunderbolt. This multi-protocol support is crucial for modern computing ecosystems where a single physical port must accommodate various connection types and functions.

The specification further addresses power management considerations, recognizing that high-speed data transmission can generate significant heat in compact devices. Thermal management techniques and power-efficient signaling are incorporated to maintain performance while minimizing energy consumption and heat generation.

Market Demand for High-Bandwidth Display Connectivity

The demand for high-bandwidth display connectivity has experienced exponential growth in recent years, driven primarily by the increasing resolution and refresh rates of modern displays. As 4K displays become standard and 8K displays gain market traction, the need for faster and more efficient display interfaces has become critical. Market research indicates that the global high-resolution display market is projected to reach $178 billion by 2026, with a compound annual growth rate of 7.7% from 2021 to 2026.

DisplayPort technology, particularly the latest 2.1 standard with UHBR (Ultra High Bit Rate) capabilities, addresses this growing demand by offering bandwidth up to 80 Gbps, significantly higher than previous generations. This bandwidth expansion directly responds to consumer and professional requirements for seamless experiences with high-resolution content, multiple display setups, and high refresh rate gaming.

The professional market segment shows particularly strong demand for high-bandwidth display connectivity. Content creators, video editors, and graphic designers increasingly work with 4K and 8K content, requiring reliable, high-speed connections between workstations and displays. The gaming sector represents another major demand driver, with competitive gamers seeking displays offering 240Hz or higher refresh rates at 4K resolution, necessitating substantial bandwidth capabilities.

Corporate environments are transitioning toward USB Type-C as a universal connectivity solution, creating demand for DisplayPort Alt Mode implementations that maintain signal integrity across various cable lengths and qualities. Market research shows that 73% of enterprise IT decision-makers consider standardized connectivity options a priority when purchasing new equipment.

The consumer electronics industry has embraced the USB Type-C form factor, with over 5 billion devices shipped with Type-C ports in 2022 alone. This widespread adoption creates significant market pressure for display technologies that can leverage this physical interface while maintaining high performance standards. DisplayPort 2.1's ability to maintain UHBR10/13.5 eye integrity over Type-C paths directly addresses this market need.

Emerging technologies like virtual reality, augmented reality, and mixed reality represent growing market segments requiring exceptional display bandwidth. These applications demand not only high resolution but also extremely low latency and high refresh rates to create immersive experiences without causing user discomfort. Industry forecasts suggest the XR market will grow to $209 billion by 2025, creating substantial demand for advanced display connectivity solutions.

The automotive sector presents another expanding market for high-bandwidth display connectivity, with modern vehicles incorporating multiple high-resolution displays for infotainment, instrument clusters, and passenger entertainment. The automotive display market is expected to reach $30 billion by 2025, with increasing requirements for reliable, high-speed display interfaces that can operate in challenging environmental conditions.

DisplayPort technology, particularly the latest 2.1 standard with UHBR (Ultra High Bit Rate) capabilities, addresses this growing demand by offering bandwidth up to 80 Gbps, significantly higher than previous generations. This bandwidth expansion directly responds to consumer and professional requirements for seamless experiences with high-resolution content, multiple display setups, and high refresh rate gaming.

The professional market segment shows particularly strong demand for high-bandwidth display connectivity. Content creators, video editors, and graphic designers increasingly work with 4K and 8K content, requiring reliable, high-speed connections between workstations and displays. The gaming sector represents another major demand driver, with competitive gamers seeking displays offering 240Hz or higher refresh rates at 4K resolution, necessitating substantial bandwidth capabilities.

Corporate environments are transitioning toward USB Type-C as a universal connectivity solution, creating demand for DisplayPort Alt Mode implementations that maintain signal integrity across various cable lengths and qualities. Market research shows that 73% of enterprise IT decision-makers consider standardized connectivity options a priority when purchasing new equipment.

The consumer electronics industry has embraced the USB Type-C form factor, with over 5 billion devices shipped with Type-C ports in 2022 alone. This widespread adoption creates significant market pressure for display technologies that can leverage this physical interface while maintaining high performance standards. DisplayPort 2.1's ability to maintain UHBR10/13.5 eye integrity over Type-C paths directly addresses this market need.

Emerging technologies like virtual reality, augmented reality, and mixed reality represent growing market segments requiring exceptional display bandwidth. These applications demand not only high resolution but also extremely low latency and high refresh rates to create immersive experiences without causing user discomfort. Industry forecasts suggest the XR market will grow to $209 billion by 2025, creating substantial demand for advanced display connectivity solutions.

The automotive sector presents another expanding market for high-bandwidth display connectivity, with modern vehicles incorporating multiple high-resolution displays for infotainment, instrument clusters, and passenger entertainment. The automotive display market is expected to reach $30 billion by 2025, with increasing requirements for reliable, high-speed display interfaces that can operate in challenging environmental conditions.

UHBR Signal Integrity Challenges in Type-C Implementations

Ultra High Bit Rate (UHBR) transmission in DisplayPort 2.1 over USB Type-C connections presents significant signal integrity challenges that must be addressed to ensure reliable high-speed data transfer. The primary challenge stems from the physical limitations of the Type-C connector and cable infrastructure when handling data rates of 10 Gbps (UHBR10) and 13.5 Gbps (UHBR13.5) per lane.

The compact form factor of USB Type-C connectors creates inherent impedance discontinuities that can cause signal reflections and degradation. These connectors were not originally designed for the extreme bandwidth requirements of DisplayPort 2.1 UHBR modes, resulting in potential crosstalk between adjacent pins carrying high-speed differential signals.

Cable length presents another critical challenge, as signal attenuation increases proportionally with cable length at these ultra-high frequencies. The copper traces in standard Type-C cables exhibit frequency-dependent losses that become particularly problematic at UHBR data rates, causing inter-symbol interference (ISI) and jitter that can close the eye diagram beyond acceptable limits.

Manufacturing variations in Type-C connectors and cables further complicate signal integrity. Inconsistencies in impedance matching, shielding effectiveness, and dielectric materials can create unpredictable transmission characteristics that vary between different cable vendors and even between production batches from the same manufacturer.

Power delivery through the same Type-C connector introduces additional noise sources. When DisplayPort Alt Mode shares the connector with USB Power Delivery providing up to 100W, the electromagnetic interference can significantly impact the integrity of adjacent high-speed differential pairs carrying UHBR signals.

Environmental factors also play a crucial role in signal integrity challenges. Temperature variations can alter the electrical characteristics of cable materials, while external electromagnetic interference can couple into inadequately shielded cables, particularly in industrial environments with high EMI levels.

The transition from the device PCB to the Type-C connector represents another critical challenge point. Vias, trace geometry changes, and connector attachment methods can create impedance discontinuities that become increasingly problematic as bit rates climb to UHBR levels.

Maintaining backward compatibility while supporting these new high-speed modes introduces additional design constraints. The signal integrity solution must work across various cable qualities and lengths while still supporting legacy devices and protocols through the same physical interface.

The compact form factor of USB Type-C connectors creates inherent impedance discontinuities that can cause signal reflections and degradation. These connectors were not originally designed for the extreme bandwidth requirements of DisplayPort 2.1 UHBR modes, resulting in potential crosstalk between adjacent pins carrying high-speed differential signals.

Cable length presents another critical challenge, as signal attenuation increases proportionally with cable length at these ultra-high frequencies. The copper traces in standard Type-C cables exhibit frequency-dependent losses that become particularly problematic at UHBR data rates, causing inter-symbol interference (ISI) and jitter that can close the eye diagram beyond acceptable limits.

Manufacturing variations in Type-C connectors and cables further complicate signal integrity. Inconsistencies in impedance matching, shielding effectiveness, and dielectric materials can create unpredictable transmission characteristics that vary between different cable vendors and even between production batches from the same manufacturer.

Power delivery through the same Type-C connector introduces additional noise sources. When DisplayPort Alt Mode shares the connector with USB Power Delivery providing up to 100W, the electromagnetic interference can significantly impact the integrity of adjacent high-speed differential pairs carrying UHBR signals.

Environmental factors also play a crucial role in signal integrity challenges. Temperature variations can alter the electrical characteristics of cable materials, while external electromagnetic interference can couple into inadequately shielded cables, particularly in industrial environments with high EMI levels.

The transition from the device PCB to the Type-C connector represents another critical challenge point. Vias, trace geometry changes, and connector attachment methods can create impedance discontinuities that become increasingly problematic as bit rates climb to UHBR levels.

Maintaining backward compatibility while supporting these new high-speed modes introduces additional design constraints. The signal integrity solution must work across various cable qualities and lengths while still supporting legacy devices and protocols through the same physical interface.

Current Signal Integrity Solutions for UHBR10/13.5

01 DisplayPort 2.1 Eye Integrity Testing and Verification

Eye integrity testing is a critical component of DisplayPort 2.1 technology that ensures signal integrity across high-speed digital interfaces. This involves measuring and analyzing the quality of digital signals through eye diagrams, which visually represent signal quality by showing the overlapping waveforms at specific sampling points. The testing methods include verification of timing margins, voltage levels, and jitter performance to ensure reliable data transmission across DisplayPort connections.- DisplayPort 2.1 Eye Integrity Testing and Verification: Eye integrity testing is a critical component of DisplayPort 2.1 technology that ensures signal integrity across high-speed digital interfaces. This testing methodology evaluates the quality of the signal by analyzing eye diagrams, which provide visual representations of digital signals to detect potential transmission issues. The testing procedures help identify signal degradation, jitter, and other anomalies that could affect display performance at high data rates supported by DisplayPort 2.1.

- Signal Integrity Solutions for DisplayPort 2.1 Connections: DisplayPort 2.1 implements advanced signal integrity solutions to maintain reliable data transmission across various connection scenarios. These solutions include adaptive equalization, pre-emphasis techniques, and receiver training algorithms that compensate for channel losses and interference. The technology incorporates sophisticated error correction mechanisms to ensure stable connections even in challenging electromagnetic environments, supporting the high bandwidth requirements of modern display interfaces.

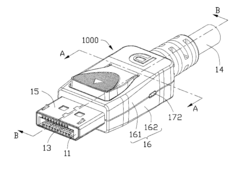

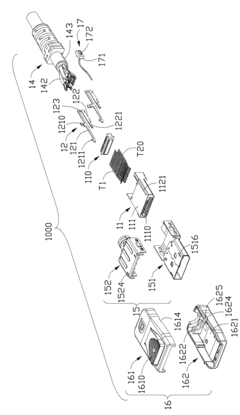

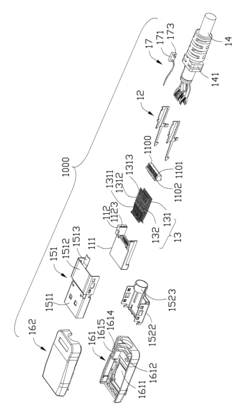

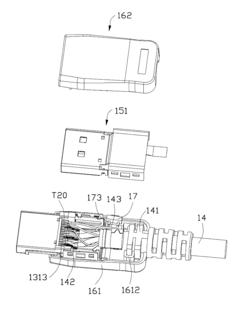

- DisplayPort 2.1 Connector Design for Eye Integrity: The physical connector design of DisplayPort 2.1 is engineered specifically to maintain eye integrity across all transmission lanes. The connector architecture incorporates shielding elements, controlled impedance paths, and precise pin layouts to minimize crosstalk and electromagnetic interference. These design considerations are crucial for supporting the increased data rates while ensuring signal quality and maintaining compatibility with various display devices.

- Protocol-Level Eye Integrity Features in DisplayPort 2.1: DisplayPort 2.1 implements protocol-level features that enhance eye integrity during data transmission. These include link training sequences, dynamic bit rate adjustment, and channel equalization protocols that optimize signal quality based on real-time conditions. The protocol incorporates sophisticated handshaking mechanisms between source and sink devices to negotiate optimal transmission parameters, ensuring reliable performance across various cable lengths and environmental conditions.

- DisplayPort 2.1 Compliance Testing for Eye Integrity: Compliance testing frameworks for DisplayPort 2.1 include comprehensive eye integrity verification procedures to ensure interoperability between devices. These testing methodologies evaluate signal quality across different operating conditions, including various cable lengths, environmental factors, and data rates. The compliance standards establish minimum performance thresholds for eye height, eye width, and jitter tolerance, guaranteeing that certified devices will maintain signal integrity in real-world applications.

02 Signal Integrity Solutions for DisplayPort 2.1

Various hardware and software solutions are implemented to maintain signal integrity in DisplayPort 2.1 connections. These include advanced equalization techniques, adaptive signal conditioning, and error correction mechanisms that compensate for channel losses and interference. The solutions help overcome challenges related to high-bandwidth data transmission, ensuring that DisplayPort 2.1 interfaces can reliably support higher resolutions, refresh rates, and color depths while maintaining eye integrity across various cable lengths and environmental conditions.Expand Specific Solutions03 DisplayPort 2.1 Connector Design for Eye Integrity

The physical design of DisplayPort 2.1 connectors plays a crucial role in maintaining eye integrity. Specialized connector designs incorporate features such as improved shielding, optimized pin layouts, and enhanced ground connections to minimize signal degradation and electromagnetic interference. These design elements ensure proper impedance matching and reduce signal reflections, contributing to better eye diagram performance and more reliable high-speed data transmission in DisplayPort 2.1 implementations.Expand Specific Solutions04 Protocol-Level Eye Integrity Features in DisplayPort 2.1

DisplayPort 2.1 incorporates protocol-level features specifically designed to enhance eye integrity. These include advanced link training sequences, dynamic link rate adjustment, and forward error correction mechanisms. The protocol allows devices to negotiate optimal signal parameters, adaptively adjust to changing conditions, and recover from transmission errors, ensuring that the eye pattern remains open and stable even under challenging operating conditions or when approaching the bandwidth limits of the interface.Expand Specific Solutions05 Integration of Eye Integrity Monitoring in DisplayPort 2.1 Systems

Modern DisplayPort 2.1 implementations incorporate real-time eye integrity monitoring systems that continuously assess signal quality during operation. These systems include built-in self-test capabilities, diagnostic tools, and performance monitoring features that can detect degradation in signal quality before it leads to visible display issues. The monitoring solutions enable adaptive responses to changing conditions, allowing systems to maintain optimal performance by adjusting parameters such as pre-emphasis, equalization settings, and link speeds based on measured eye integrity metrics.Expand Specific Solutions

Key Industry Players in DisplayPort Ecosystem

DisplayPort 2.1 technology is currently in a growth phase within the high-performance display connectivity market, with an estimated market size of $3-4 billion and expanding at 15% annually. The competitive landscape is dominated by established semiconductor players like Intel, Samsung Electronics, and Texas Instruments, who are investing heavily in maintaining signal integrity across USB Type-C implementations. Companies like Realtek Semiconductor and Silicon Laboratories are focusing on specialized solutions for UHBR10/13.5 eye pattern optimization, while connector manufacturers such as Foxconn Interconnect Technology and Advanced-Connectek are developing enhanced Type-C connectors to support these high bitrates. The technology is approaching maturity for UHBR10 implementations, while UHBR13.5 solutions are still evolving as companies address challenges in maintaining signal integrity across longer cable runs and varied environmental conditions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has engineered a DisplayPort 2.1 solution specifically addressing the challenges of maintaining signal integrity over USB Type-C connections. Their approach centers on advanced DSP-based receiver equalization that dynamically compensates for channel losses at UHBR10/13.5 speeds. Samsung's implementation features multi-tap adaptive equalizers that continuously optimize based on real-time channel characteristics. Their design incorporates specialized Pre-emphasis and De-emphasis circuits that pre-compensate for the frequency-dependent losses in Type-C cables. Samsung has also developed proprietary clock recovery techniques that maintain timing accuracy even under challenging signal conditions. Their solution includes enhanced error detection and correction mechanisms that operate at the physical layer to ensure data integrity. Samsung's technology employs sophisticated eye monitoring circuits that provide continuous feedback to the equalization system, allowing for real-time adjustments to maintain optimal eye opening[2][5].

Strengths: Samsung's vertical integration allows for highly optimized solutions across their display ecosystem. Their adaptive equalization technology shows excellent performance across varying cable qualities and lengths. Weaknesses: Their proprietary techniques may create interoperability challenges with some third-party devices, and implementation costs can be higher than more standardized approaches.

Intel Corp.

Technical Solution: Intel has developed comprehensive DisplayPort 2.1 solutions focusing on maintaining signal integrity across USB Type-C connections. Their approach includes advanced equalization techniques and adaptive link training algorithms that dynamically adjust to channel characteristics. Intel's implementation utilizes Decision Feedback Equalization (DFE) and Feed-Forward Equalization (FFE) to combat inter-symbol interference at UHBR (Ultra High Bit Rate) speeds. Their PHY design incorporates specialized circuitry for jitter compensation and crosstalk mitigation specifically optimized for the electrical characteristics of Type-C cables. Intel has also developed proprietary signal conditioning techniques that help maintain eye diagram integrity even with cable lengths approaching the specification limits. Their solution includes enhanced Link Training Status Channel (LTSC) functionality that provides real-time feedback for dynamic link optimization during operation[1][3].

Strengths: Intel's extensive experience with high-speed interfaces provides robust solutions with excellent compatibility across device ecosystems. Their adaptive equalization technology offers superior performance in varying cable quality scenarios. Weaknesses: Their solutions may require more power consumption compared to some competitors, and implementation complexity can increase integration challenges for smaller device manufacturers.

Critical Patents in DisplayPort 2.1 Signal Integrity

Cable connector

PatentInactiveCN201829753U

Innovation

- Design a cable connector that includes a signal core wire and a power core wire. The power core wire is connected to the power terminal to form a power transmission line, and a switch is set on the power transmission line to control the power transmission.

Protocol extensions in a display port compatible interface

PatentActiveCN101715119A

Innovation

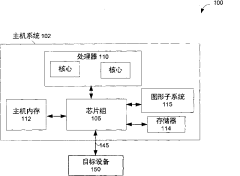

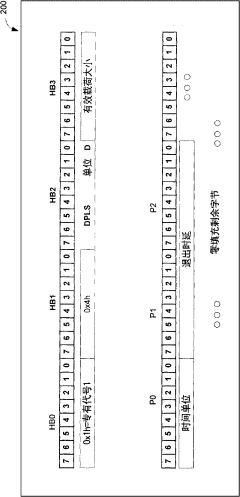

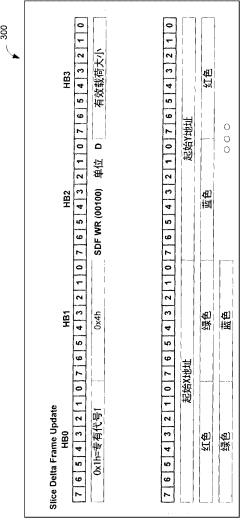

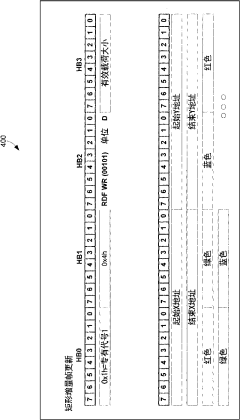

- Using the extended packet technology in the DisplayPort specification, through the header bytes HB0-HB3 and the payload part P0-P2, the power control, incremental frame update, rectangular incremental frame update and register writing of the target device are implemented to improve data transmission. efficiency and control speed.

EMI Mitigation Strategies for UHBR Signals

Electromagnetic Interference (EMI) presents a significant challenge for Ultra High Bit Rate (UHBR) signals in DisplayPort 2.1 implementations, particularly when maintaining signal integrity across USB Type-C connections. As data rates increase to UHBR10 (10 Gbps) and UHBR13.5 (13.5 Gbps), traditional EMI mitigation approaches require substantial enhancement to preserve eye diagram integrity.

The primary EMI mitigation strategy employed in DisplayPort 2.1 involves sophisticated spread spectrum clocking (SSC) techniques. These implementations modulate the reference clock frequency with carefully controlled profiles, typically achieving 0.5% to 1% downspread, which effectively distributes electromagnetic energy across a wider frequency band, reducing peak emissions at any single frequency point without compromising data integrity.

Advanced shielding designs represent another critical EMI mitigation approach. DisplayPort 2.1 cables supporting UHBR rates incorporate multi-layer shielding with optimized ground return paths. The specification mandates enhanced cable construction with individually shielded differential pairs and additional outer shields to minimize both radiated emissions and susceptibility to external interference sources.

Signal conditioning techniques play a vital role in EMI management for UHBR signals. Pre-emphasis and de-emphasis are dynamically adjusted based on channel characteristics, with DisplayPort 2.1 implementing adaptive equalization that responds to changing electromagnetic environments. This adaptive approach ensures optimal signal quality even when interference conditions fluctuate during operation.

Ground plane optimization represents a fundamental EMI mitigation strategy in DisplayPort 2.1 implementations. The specification requires careful attention to ground continuity across connector interfaces, with Type-C connectors featuring enhanced grounding structures specifically designed to maintain impedance control and minimize ground bounce effects that could otherwise compromise UHBR signal integrity.

Filter-based solutions are increasingly deployed at both transmitter and receiver ends of DisplayPort 2.1 connections. These include common-mode filters with precisely tuned characteristics for UHBR frequencies, ferrite components optimized for high-frequency performance, and specialized EMI suppression components placed at critical points along the signal path to attenuate unwanted emissions while preserving signal quality.

Differential signaling enhancements in DisplayPort 2.1 further contribute to EMI resilience. The specification implements tighter skew control requirements and improved common-mode rejection techniques compared to previous versions, ensuring that differential pairs maintain their inherent EMI immunity advantages even at UHBR10/13.5 data rates across Type-C paths.

The primary EMI mitigation strategy employed in DisplayPort 2.1 involves sophisticated spread spectrum clocking (SSC) techniques. These implementations modulate the reference clock frequency with carefully controlled profiles, typically achieving 0.5% to 1% downspread, which effectively distributes electromagnetic energy across a wider frequency band, reducing peak emissions at any single frequency point without compromising data integrity.

Advanced shielding designs represent another critical EMI mitigation approach. DisplayPort 2.1 cables supporting UHBR rates incorporate multi-layer shielding with optimized ground return paths. The specification mandates enhanced cable construction with individually shielded differential pairs and additional outer shields to minimize both radiated emissions and susceptibility to external interference sources.

Signal conditioning techniques play a vital role in EMI management for UHBR signals. Pre-emphasis and de-emphasis are dynamically adjusted based on channel characteristics, with DisplayPort 2.1 implementing adaptive equalization that responds to changing electromagnetic environments. This adaptive approach ensures optimal signal quality even when interference conditions fluctuate during operation.

Ground plane optimization represents a fundamental EMI mitigation strategy in DisplayPort 2.1 implementations. The specification requires careful attention to ground continuity across connector interfaces, with Type-C connectors featuring enhanced grounding structures specifically designed to maintain impedance control and minimize ground bounce effects that could otherwise compromise UHBR signal integrity.

Filter-based solutions are increasingly deployed at both transmitter and receiver ends of DisplayPort 2.1 connections. These include common-mode filters with precisely tuned characteristics for UHBR frequencies, ferrite components optimized for high-frequency performance, and specialized EMI suppression components placed at critical points along the signal path to attenuate unwanted emissions while preserving signal quality.

Differential signaling enhancements in DisplayPort 2.1 further contribute to EMI resilience. The specification implements tighter skew control requirements and improved common-mode rejection techniques compared to previous versions, ensuring that differential pairs maintain their inherent EMI immunity advantages even at UHBR10/13.5 data rates across Type-C paths.

Compliance Testing Methodologies for DisplayPort 2.1

DisplayPort 2.1 compliance testing methodologies represent a critical framework for ensuring that implementations meet the stringent requirements necessary for maintaining signal integrity, particularly for Ultra High Bit Rate (UHBR) modes over USB Type-C connections. These methodologies have evolved significantly from previous DisplayPort standards to address the unique challenges posed by higher data rates and more complex physical interconnects.

The compliance testing for DisplayPort 2.1 encompasses a comprehensive suite of electrical, timing, and protocol tests designed specifically for UHBR10 (10 Gbps) and UHBR13.5 (13.5 Gbps) modes. These tests evaluate both transmitter and receiver performance under various operating conditions to ensure robust interoperability across different device implementations.

For transmitter testing, the methodologies include detailed eye diagram analysis with specific mask requirements tailored to the challenges of Type-C paths. The test procedures incorporate pre-emphasis and equalization parameter optimization to compensate for channel losses at higher frequencies. Jitter tolerance measurements have been enhanced to account for the reduced timing margins at UHBR rates.

Receiver testing methodologies focus on stressed-eye conditions that simulate worst-case real-world scenarios. The compliance test specifications define precise stress patterns that include both deterministic and random jitter components, as well as sinusoidal interference patterns that mimic common electromagnetic interference sources in typical deployment environments.

Channel compliance testing represents a significant addition to DisplayPort 2.1 methodologies, recognizing that the physical transmission medium plays a crucial role in maintaining signal integrity. These tests characterize insertion loss, return loss, and crosstalk parameters across the frequency ranges relevant to UHBR operation.

The methodologies also incorporate specific test cases for Alt Mode operation over USB Type-C, addressing the unique signal integrity challenges when DisplayPort signals traverse the Type-C connector and cable infrastructure. This includes verification of proper lane mapping and configuration during Alt Mode negotiation.

Automated test equipment (ATE) requirements have been updated to support the higher bandwidth needs of DisplayPort 2.1 testing. The methodologies specify calibration procedures to ensure measurement accuracy at these elevated data rates, with particular attention to de-embedding techniques that isolate the device under test from test fixture effects.

Compliance testing documentation has been standardized to facilitate consistent interpretation and application across the industry. This includes detailed pass/fail criteria, reference test patterns, and procedural workflows that ensure reproducible results across different test environments and equipment setups.

The compliance testing for DisplayPort 2.1 encompasses a comprehensive suite of electrical, timing, and protocol tests designed specifically for UHBR10 (10 Gbps) and UHBR13.5 (13.5 Gbps) modes. These tests evaluate both transmitter and receiver performance under various operating conditions to ensure robust interoperability across different device implementations.

For transmitter testing, the methodologies include detailed eye diagram analysis with specific mask requirements tailored to the challenges of Type-C paths. The test procedures incorporate pre-emphasis and equalization parameter optimization to compensate for channel losses at higher frequencies. Jitter tolerance measurements have been enhanced to account for the reduced timing margins at UHBR rates.

Receiver testing methodologies focus on stressed-eye conditions that simulate worst-case real-world scenarios. The compliance test specifications define precise stress patterns that include both deterministic and random jitter components, as well as sinusoidal interference patterns that mimic common electromagnetic interference sources in typical deployment environments.

Channel compliance testing represents a significant addition to DisplayPort 2.1 methodologies, recognizing that the physical transmission medium plays a crucial role in maintaining signal integrity. These tests characterize insertion loss, return loss, and crosstalk parameters across the frequency ranges relevant to UHBR operation.

The methodologies also incorporate specific test cases for Alt Mode operation over USB Type-C, addressing the unique signal integrity challenges when DisplayPort signals traverse the Type-C connector and cable infrastructure. This includes verification of proper lane mapping and configuration during Alt Mode negotiation.

Automated test equipment (ATE) requirements have been updated to support the higher bandwidth needs of DisplayPort 2.1 testing. The methodologies specify calibration procedures to ensure measurement accuracy at these elevated data rates, with particular attention to de-embedding techniques that isolate the device under test from test fixture effects.

Compliance testing documentation has been standardized to facilitate consistent interpretation and application across the industry. This includes detailed pass/fail criteria, reference test patterns, and procedural workflows that ensure reproducible results across different test environments and equipment setups.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!