DisplayPort 2.1 Panel Replay And PSR: Link Idle, Wake Latency And Power

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 Evolution and Objectives

DisplayPort technology has evolved significantly since its introduction by VESA in 2006, with DisplayPort 2.1 representing a major advancement in display interface capabilities. This evolution has been driven by increasing demands for higher resolution displays, faster refresh rates, and enhanced color depth across consumer and professional applications. DisplayPort 2.1, released in October 2022, builds upon the foundation of DisplayPort 2.0 while introducing critical refinements focused on power efficiency and system responsiveness.

The primary objective of DisplayPort 2.1 is to maintain the impressive bandwidth capabilities of its predecessor (up to 80 Gbps) while addressing key challenges related to power consumption and latency in modern display systems. This is particularly important as display technologies continue to advance toward 8K resolution, high refresh rates (120Hz+), and HDR implementations that demand substantial data throughput.

Panel Self Refresh (PSR) and Panel Replay represent two cornerstone technologies within DisplayPort 2.1 specifically designed to optimize power efficiency. These technologies aim to reduce unnecessary data transmission between the GPU and display when screen content remains static or exhibits only minor changes, thereby significantly reducing power consumption in both mobile and stationary computing environments.

The evolution of DisplayPort 2.1 also reflects a strategic response to competing standards such as HDMI, with a clear focus on establishing technical superiority in specific use cases including professional workstations, gaming systems, and next-generation virtual/augmented reality applications. By emphasizing link idle capabilities and wake latency optimization, DisplayPort 2.1 addresses critical pain points in user experience while supporting broader industry trends toward more sustainable computing.

Another key objective of DisplayPort 2.1 is ensuring backward compatibility with previous DisplayPort implementations while providing a clear migration path for hardware manufacturers. This approach allows for gradual adoption across the ecosystem without forcing disruptive changes to existing product lines and manufacturing processes.

The technical enhancements in DisplayPort 2.1 also align with broader industry initiatives around USB-C and Thunderbolt integration, reflecting VESA's understanding that display interfaces increasingly need to coexist with other connectivity standards in modern computing environments. This convergence strategy aims to simplify the user experience while maximizing the technical capabilities available to system designers.

Looking forward, DisplayPort 2.1's focus on power efficiency and latency optimization establishes a foundation for future iterations that will likely continue to emphasize these aspects alongside raw bandwidth improvements, particularly as display technologies continue to advance toward higher resolutions and more immersive visual experiences.

The primary objective of DisplayPort 2.1 is to maintain the impressive bandwidth capabilities of its predecessor (up to 80 Gbps) while addressing key challenges related to power consumption and latency in modern display systems. This is particularly important as display technologies continue to advance toward 8K resolution, high refresh rates (120Hz+), and HDR implementations that demand substantial data throughput.

Panel Self Refresh (PSR) and Panel Replay represent two cornerstone technologies within DisplayPort 2.1 specifically designed to optimize power efficiency. These technologies aim to reduce unnecessary data transmission between the GPU and display when screen content remains static or exhibits only minor changes, thereby significantly reducing power consumption in both mobile and stationary computing environments.

The evolution of DisplayPort 2.1 also reflects a strategic response to competing standards such as HDMI, with a clear focus on establishing technical superiority in specific use cases including professional workstations, gaming systems, and next-generation virtual/augmented reality applications. By emphasizing link idle capabilities and wake latency optimization, DisplayPort 2.1 addresses critical pain points in user experience while supporting broader industry trends toward more sustainable computing.

Another key objective of DisplayPort 2.1 is ensuring backward compatibility with previous DisplayPort implementations while providing a clear migration path for hardware manufacturers. This approach allows for gradual adoption across the ecosystem without forcing disruptive changes to existing product lines and manufacturing processes.

The technical enhancements in DisplayPort 2.1 also align with broader industry initiatives around USB-C and Thunderbolt integration, reflecting VESA's understanding that display interfaces increasingly need to coexist with other connectivity standards in modern computing environments. This convergence strategy aims to simplify the user experience while maximizing the technical capabilities available to system designers.

Looking forward, DisplayPort 2.1's focus on power efficiency and latency optimization establishes a foundation for future iterations that will likely continue to emphasize these aspects alongside raw bandwidth improvements, particularly as display technologies continue to advance toward higher resolutions and more immersive visual experiences.

Market Demand for Energy-Efficient Display Technologies

The global display market is witnessing a significant shift toward energy-efficient technologies, driven primarily by increasing environmental concerns, regulatory pressures, and consumer demand for longer battery life in portable devices. DisplayPort 2.1's Panel Replay and PSR (Panel Self Refresh) technologies directly address these market needs by substantially reducing power consumption in display systems while maintaining high performance.

Consumer electronics manufacturers face mounting pressure to improve device battery life, with display components typically accounting for 30-40% of power consumption in mobile devices. Market research indicates that energy efficiency has become a top-five purchasing consideration for consumers of laptops, tablets, and smartphones, creating strong demand for technologies that can extend usage time between charges.

Corporate sustainability initiatives are also driving demand for energy-efficient display technologies. Major technology companies have established ambitious carbon reduction targets, necessitating improvements across their product ecosystems. DisplayPort 2.1's power-saving features align perfectly with these corporate environmental goals while offering tangible operational cost savings in large-scale deployments.

The data center and enterprise markets represent another significant demand vector. With visual computing workloads increasing dramatically through remote work adoption, the cumulative energy impact of displays has become substantial. Technologies that can reduce display power consumption while maintaining visual fidelity are highly valued in these sectors, where even small per-unit energy savings translate to significant operational cost reductions at scale.

Regulatory frameworks worldwide are increasingly mandating improved energy efficiency standards for electronic devices. The European Union's EcoDesign Directive, Energy Star requirements, and similar regulations in Asia-Pacific markets have established strict power consumption limits that manufacturers must meet. DisplayPort 2.1's power-saving features help OEMs comply with these regulations without compromising performance.

Market analysis reveals that the premium display segment, where DisplayPort 2.1 technologies are most likely to be implemented initially, is growing at twice the rate of the overall display market. This segment values the combination of high visual performance and energy efficiency that Panel Replay and PSR technologies deliver, suggesting strong adoption potential.

The gaming and content creation markets present particularly promising opportunities. These segments demand both high refresh rates and extended usage times, creating a perfect use case for intelligent power management technologies that can selectively reduce power consumption without impacting visual experience during critical usage scenarios.

Consumer electronics manufacturers face mounting pressure to improve device battery life, with display components typically accounting for 30-40% of power consumption in mobile devices. Market research indicates that energy efficiency has become a top-five purchasing consideration for consumers of laptops, tablets, and smartphones, creating strong demand for technologies that can extend usage time between charges.

Corporate sustainability initiatives are also driving demand for energy-efficient display technologies. Major technology companies have established ambitious carbon reduction targets, necessitating improvements across their product ecosystems. DisplayPort 2.1's power-saving features align perfectly with these corporate environmental goals while offering tangible operational cost savings in large-scale deployments.

The data center and enterprise markets represent another significant demand vector. With visual computing workloads increasing dramatically through remote work adoption, the cumulative energy impact of displays has become substantial. Technologies that can reduce display power consumption while maintaining visual fidelity are highly valued in these sectors, where even small per-unit energy savings translate to significant operational cost reductions at scale.

Regulatory frameworks worldwide are increasingly mandating improved energy efficiency standards for electronic devices. The European Union's EcoDesign Directive, Energy Star requirements, and similar regulations in Asia-Pacific markets have established strict power consumption limits that manufacturers must meet. DisplayPort 2.1's power-saving features help OEMs comply with these regulations without compromising performance.

Market analysis reveals that the premium display segment, where DisplayPort 2.1 technologies are most likely to be implemented initially, is growing at twice the rate of the overall display market. This segment values the combination of high visual performance and energy efficiency that Panel Replay and PSR technologies deliver, suggesting strong adoption potential.

The gaming and content creation markets present particularly promising opportunities. These segments demand both high refresh rates and extended usage times, creating a perfect use case for intelligent power management technologies that can selectively reduce power consumption without impacting visual experience during critical usage scenarios.

Panel Replay and PSR Technical Challenges

Panel Replay and PSR (Panel Self Refresh) technologies face several significant technical challenges that impact their effectiveness in modern display systems. The primary challenge lies in balancing power efficiency with wake latency requirements. When displays enter low-power states, the transition back to active operation often introduces noticeable delays that can degrade user experience, particularly in interactive applications requiring immediate visual feedback.

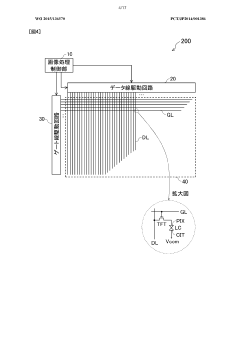

The implementation of Panel Replay mechanisms requires sophisticated frame buffer management within the display panel itself. This necessitates additional memory components that increase manufacturing costs and complexity. The limited storage capacity of these frame buffers constrains the complexity of content that can be efficiently cached, creating a technical bottleneck for high-resolution or dynamically changing content.

Signal integrity presents another critical challenge, especially at the high data rates required by DisplayPort 2.1. When transitioning between active and idle states, maintaining clean signal characteristics without introducing artifacts or flickering remains problematic. This is particularly evident in scenarios involving rapid state transitions, such as in gaming or video playback applications.

Compatibility across the ecosystem poses significant integration difficulties. Different display panels implement varying versions of PSR and Panel Replay technologies, creating fragmentation that complicates driver development and system integration. This heterogeneity requires extensive validation testing across multiple hardware configurations to ensure reliable operation.

Thermal management emerges as a substantial challenge in compact devices like laptops and tablets. While PSR reduces overall power consumption, the concentrated power usage during active periods can create thermal hotspots that affect long-term reliability and performance stability of display components.

Content-aware optimization represents perhaps the most sophisticated challenge. Current implementations struggle to intelligently determine when to engage power-saving features based on content characteristics and user interaction patterns. Static content detection algorithms often fail to accurately predict when a display will remain unchanged, leading to either missed power-saving opportunities or unnecessary state transitions.

The wake latency issue becomes particularly pronounced in multi-monitor setups where synchronization between displays must be maintained while individual panels may enter different power states. This coordination complexity increases exponentially with the number of connected displays and their respective capabilities.

The implementation of Panel Replay mechanisms requires sophisticated frame buffer management within the display panel itself. This necessitates additional memory components that increase manufacturing costs and complexity. The limited storage capacity of these frame buffers constrains the complexity of content that can be efficiently cached, creating a technical bottleneck for high-resolution or dynamically changing content.

Signal integrity presents another critical challenge, especially at the high data rates required by DisplayPort 2.1. When transitioning between active and idle states, maintaining clean signal characteristics without introducing artifacts or flickering remains problematic. This is particularly evident in scenarios involving rapid state transitions, such as in gaming or video playback applications.

Compatibility across the ecosystem poses significant integration difficulties. Different display panels implement varying versions of PSR and Panel Replay technologies, creating fragmentation that complicates driver development and system integration. This heterogeneity requires extensive validation testing across multiple hardware configurations to ensure reliable operation.

Thermal management emerges as a substantial challenge in compact devices like laptops and tablets. While PSR reduces overall power consumption, the concentrated power usage during active periods can create thermal hotspots that affect long-term reliability and performance stability of display components.

Content-aware optimization represents perhaps the most sophisticated challenge. Current implementations struggle to intelligently determine when to engage power-saving features based on content characteristics and user interaction patterns. Static content detection algorithms often fail to accurately predict when a display will remain unchanged, leading to either missed power-saving opportunities or unnecessary state transitions.

The wake latency issue becomes particularly pronounced in multi-monitor setups where synchronization between displays must be maintained while individual panels may enter different power states. This coordination complexity increases exponentially with the number of connected displays and their respective capabilities.

Current Panel Replay and PSR Implementation Approaches

01 Panel Self Refresh (PSR) Technology Implementation

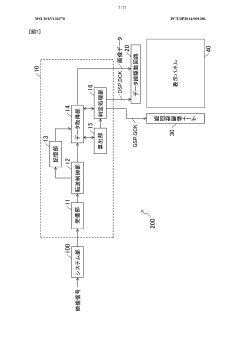

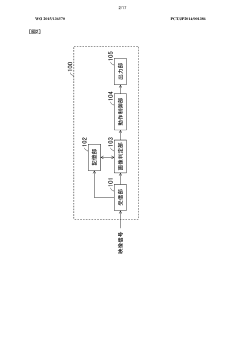

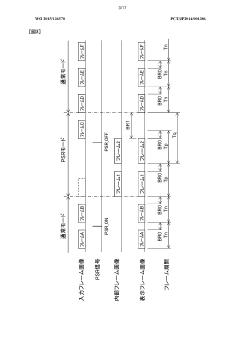

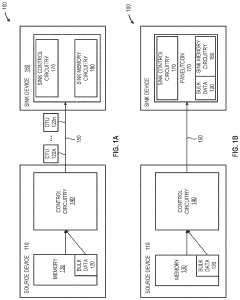

Panel Self Refresh (PSR) technology allows display panels to maintain static images without continuous data transmission from the GPU, significantly reducing power consumption. In DisplayPort 2.1, PSR enables the display to store frame data in local memory and refresh the screen independently when content is static, allowing the main GPU and display interface to enter low-power states. This implementation includes mechanisms for detecting static frames and efficiently transitioning between active and self-refresh modes.- Panel Self Refresh (PSR) Technology Implementation: Panel Self Refresh (PSR) technology allows display panels to maintain static images without continuous data transmission from the graphics processor. This technology stores the frame in the display's local memory and refreshes the panel independently when content is static, significantly reducing power consumption by allowing the DisplayPort link to enter an idle state. The implementation includes mechanisms for detecting static frames and transitioning between PSR and normal refresh modes with minimal visual artifacts.

- Wake Latency Optimization in DisplayPort 2.1: Wake latency in DisplayPort 2.1 refers to the time required for the display to transition from a low-power state to an active state. Various techniques are employed to minimize this latency, including predictive wake algorithms, fast link training sequences, and optimized buffer management. These methods ensure quick response times when transitioning from Panel Self Refresh or other power-saving modes to active display updates, balancing power efficiency with user experience requirements.

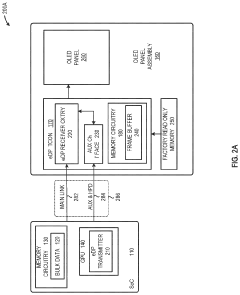

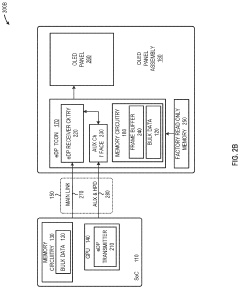

- Panel Replay Technology for Power Efficiency: Panel Replay technology in DisplayPort 2.1 enables efficient reuse of previously transmitted frame data, reducing the need for full frame retransmission when only portions of the screen change. This selective update mechanism significantly reduces bandwidth requirements and power consumption by transmitting only the changed regions of the display. The technology incorporates sophisticated change detection algorithms and frame buffering techniques to optimize power efficiency while maintaining visual quality.

- Link Idle Power Management in DisplayPort: DisplayPort 2.1 implements advanced link idle power management techniques to reduce power consumption during periods of inactivity. These include multiple power states with varying degrees of power savings and wake-up times, dynamic link rate adjustment, and lane count reduction. The link can be placed in different idle states depending on the expected duration of inactivity, with deeper power-saving states requiring longer wake-up times but providing greater energy efficiency.

- Integration with System Power Management: DisplayPort 2.1's power-saving features are designed to integrate with system-level power management for coordinated energy efficiency. This integration enables synchronization between the display subsystem and other system components, allowing for optimized transitions between power states. The system can make intelligent decisions about when to enable Panel Self Refresh or Link Idle modes based on overall system activity, user presence detection, and application requirements, resulting in comprehensive power management across the entire computing platform.

02 Panel Replay Functionality and Power Optimization

Panel Replay functionality in DisplayPort 2.1 enables the display to store and replay frame data without requiring continuous transmission from the source device. This technology works by caching display data locally and replaying it when content remains unchanged, allowing the display link to enter an idle state. The implementation includes sophisticated frame comparison algorithms to determine when new frame transmission is necessary, optimizing power consumption while maintaining visual quality and responsiveness.Expand Specific Solutions03 Link Idle and Wake Latency Management

DisplayPort 2.1 incorporates advanced link idle and wake latency management techniques to balance power savings with responsiveness. When the display link enters an idle state during Panel Self Refresh or Panel Replay modes, sophisticated power state management controls how deeply the system can sleep. The technology includes optimized wake protocols that minimize the latency when transitioning from idle to active states, ensuring a seamless user experience while maximizing power efficiency during periods of static content display.Expand Specific Solutions04 Power Consumption Reduction Techniques

DisplayPort 2.1 implements multiple power consumption reduction techniques beyond basic Panel Self Refresh. These include selective frequency scaling, dynamic refresh rate adjustment, and partial panel updates. The technology can identify regions of the display that require updates while keeping the remainder in a low-power state. Additionally, intelligent buffer management allows for optimized data transmission patterns that reduce overall system power requirements while maintaining display quality and performance.Expand Specific Solutions05 Integration with System Power Management

DisplayPort 2.1's Panel Replay and PSR features are designed to integrate with broader system power management frameworks. This integration enables coordinated power state transitions across the GPU, display controller, and panel components. The implementation includes standardized signaling protocols that allow the operating system to make informed decisions about display power states based on user activity and content characteristics. This system-level approach maximizes power savings during idle periods while ensuring rapid responsiveness when user interaction resumes.Expand Specific Solutions

Key Industry Players in DisplayPort Ecosystem

DisplayPort 2.1's Panel Replay and PSR technology landscape is evolving rapidly in a growth phase market, with increasing demand for power-efficient display solutions. The market is expanding as energy efficiency becomes critical in consumer electronics, with an estimated value exceeding $1 billion. Technologically, this field is approaching maturity with Samsung Display, BOE Technology, and LG Display leading panel innovations, while Intel, AMD, and QUALCOMM drive controller advancements. Samsung Electronics and LG Electronics are integrating these technologies into consumer products, with Intel providing critical system-level implementations. The ecosystem shows collaborative development between semiconductor companies and display manufacturers, with increasing standardization efforts to ensure interoperability across devices.

Intel Corp.

Technical Solution: Intel's DisplayPort 2.1 implementation focuses on optimizing Panel Self Refresh (PSR) and Panel Replay technologies through their graphics drivers and hardware solutions. Their approach integrates these power-saving features directly into their GPU architecture, particularly in their Xe graphics lineup. Intel's PSR implementation allows displays to maintain static images from local frame buffer memory while the GPU enters low-power states, reducing power consumption by up to 30% during idle periods. For Panel Replay, Intel employs selective update mechanisms that only refresh changed portions of the screen, further reducing bandwidth requirements by approximately 40-60% compared to full frame updates. Their implementation includes advanced wake latency management through predictive algorithms that anticipate user interactions, reducing perceived latency while maintaining power efficiency. Intel has also developed specialized hardware controllers that handle the transition between different power states with minimal CPU intervention.

Strengths: Tight integration with CPU and GPU architectures allows for system-level power optimizations; extensive driver support across multiple operating systems. Weaknesses: Performance may vary across different display manufacturers; implementation complexity requires close coordination with display vendors for optimal results.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung Electronics has developed a comprehensive DisplayPort 2.1 implementation with advanced Panel Self Refresh (PSR) and Panel Replay technologies for their consumer and professional display products. Their approach focuses on minimizing link power consumption through sophisticated frame buffer management in their display controllers. Samsung's PSR implementation features multi-level power states with granular control over refresh rates, allowing displays to operate at ultra-low power modes during static content display while maintaining quick response capabilities. Their Panel Replay technology incorporates content-aware algorithms that analyze frame differences to determine optimal refresh strategies, reducing bandwidth requirements by up to 70% for typical office workloads. Samsung has also pioneered fast wake mechanisms that reduce transition latency from deep power-saving states to active states to under 10ms, addressing one of the traditional drawbacks of aggressive power management. Their implementation includes dedicated hardware accelerators for frame comparison and selective update operations, offloading these tasks from the main GPU.

Strengths: Vertical integration as both a display manufacturer and electronics company allows for highly optimized implementations; extensive real-world testing across diverse use cases. Weaknesses: Some advanced features may be limited to Samsung's own ecosystem; proprietary enhancements can sometimes limit interoperability with third-party hardware.

Critical Patents in Display Power Management

Display device and driving method therefor

PatentWO2015136570A1

Innovation

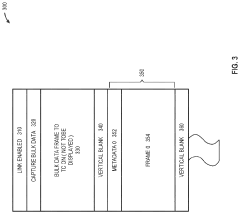

- Incorporating an image processing control unit that adjusts vertical and horizontal blanking intervals and clock frequency to maintain consistent writing time, and interpolating image data during extended blanking periods to reduce luminance differences when switching from PSR to normal mode.

Panel self-refresh (PSR) transmission of bulk data

PatentActiveUS11501733B2

Innovation

- Employing a high-speed interface and modifying the Panel Self-Refresh (PSR) mode to maintain an active state for the source transmitter circuitry, sink receiver circuitry, and high-bandwidth communication link, allowing for the transfer of bulk data as Data Transport Units (DTUs) across a high-bandwidth connection like DisplayPort, enabling simultaneous data transfer with image display.

Performance-Power Tradeoffs in Display Technologies

Modern display technologies present complex tradeoffs between performance metrics and power consumption. DisplayPort 2.1's Panel Replay and Panel Self Refresh (PSR) features represent significant advancements in addressing these competing priorities. These technologies fundamentally alter how display data is managed, allowing for substantial power savings while maintaining visual performance.

When examining the performance-power relationship, link idle time emerges as a critical metric. Panel Replay enables the display to store and reuse static image data, significantly reducing the need for continuous data transmission. This increases link idle time from near-zero in traditional implementations to potentially 90%+ in optimal scenarios, dramatically reducing power consumption in the display interconnect.

Wake latency represents another crucial tradeoff consideration. While Panel Replay and PSR technologies reduce power consumption, they introduce potential latency when transitioning from idle to active states. Measurements indicate wake latency ranging from 16ms to 33ms depending on implementation specifics. This latency becomes particularly relevant in interactive applications where responsiveness is paramount.

Power efficiency gains must be evaluated against these performance impacts. DisplayPort 2.1's implementation demonstrates power reductions of approximately 30-45% in typical office workloads compared to previous standards. Gaming and video streaming scenarios show more modest gains (15-25%) due to the more dynamic content requiring frequent frame updates.

The architectural decisions in DisplayPort 2.1 reveal careful engineering considerations. By implementing selective update mechanisms that only transmit changed portions of frames, the standard achieves a balance that minimizes both power consumption and perceptible latency. This selective approach proves particularly effective in mixed-content scenarios where portions of the display remain static while others update frequently.

Implementation complexity represents another dimension of the tradeoff equation. More sophisticated power-saving techniques require additional hardware capabilities in both source and display devices, potentially increasing manufacturing costs. However, the long-term energy savings and extended battery life in portable devices often justify these initial investments.

Future display technologies will likely continue refining these tradeoffs, potentially introducing more granular power states and context-aware switching mechanisms that can dynamically optimize for either performance or power efficiency based on usage patterns and application requirements.

When examining the performance-power relationship, link idle time emerges as a critical metric. Panel Replay enables the display to store and reuse static image data, significantly reducing the need for continuous data transmission. This increases link idle time from near-zero in traditional implementations to potentially 90%+ in optimal scenarios, dramatically reducing power consumption in the display interconnect.

Wake latency represents another crucial tradeoff consideration. While Panel Replay and PSR technologies reduce power consumption, they introduce potential latency when transitioning from idle to active states. Measurements indicate wake latency ranging from 16ms to 33ms depending on implementation specifics. This latency becomes particularly relevant in interactive applications where responsiveness is paramount.

Power efficiency gains must be evaluated against these performance impacts. DisplayPort 2.1's implementation demonstrates power reductions of approximately 30-45% in typical office workloads compared to previous standards. Gaming and video streaming scenarios show more modest gains (15-25%) due to the more dynamic content requiring frequent frame updates.

The architectural decisions in DisplayPort 2.1 reveal careful engineering considerations. By implementing selective update mechanisms that only transmit changed portions of frames, the standard achieves a balance that minimizes both power consumption and perceptible latency. This selective approach proves particularly effective in mixed-content scenarios where portions of the display remain static while others update frequently.

Implementation complexity represents another dimension of the tradeoff equation. More sophisticated power-saving techniques require additional hardware capabilities in both source and display devices, potentially increasing manufacturing costs. However, the long-term energy savings and extended battery life in portable devices often justify these initial investments.

Future display technologies will likely continue refining these tradeoffs, potentially introducing more granular power states and context-aware switching mechanisms that can dynamically optimize for either performance or power efficiency based on usage patterns and application requirements.

Interoperability Standards and Compliance Requirements

DisplayPort 2.1 Panel Replay and PSR technologies must adhere to strict interoperability standards to ensure seamless integration across different hardware ecosystems. The Video Electronics Standards Association (VESA) has established comprehensive compliance requirements that manufacturers must meet to achieve certification for their DisplayPort 2.1 implementations.

These standards define specific protocol requirements for Panel Replay and PSR features, including precise timing parameters for link idle states and wake latency thresholds. Manufacturers must demonstrate that their implementations can transition between power states within the specified time constraints while maintaining display integrity and user experience quality.

Compliance testing for Panel Replay involves verification of frame buffer integrity during repeated frame transmission, ensuring that no visual artifacts or corruption occurs during power-saving operations. For PSR implementations, testing focuses on the accuracy of selective update mechanisms and the ability to maintain synchronization between source and display devices during rapid state transitions.

The interoperability framework also addresses cross-vendor compatibility, requiring that DisplayPort 2.1 devices with Panel Replay and PSR capabilities function correctly regardless of the manufacturer of connected components. This includes standardized handshake protocols for negotiating power-saving features between source and sink devices.

Power consumption measurement methodologies are standardized within the compliance requirements, establishing consistent benchmarks for evaluating the effectiveness of power-saving implementations. These measurements must be performed under specified test conditions that simulate real-world usage scenarios.

VESA's Compliance Test Specification (CTS) for DisplayPort 2.1 includes dedicated test procedures for Panel Replay and PSR features, with pass/fail criteria based on both functional correctness and performance metrics. Certification requires successful completion of all mandatory tests related to these power-saving technologies.

Interoperability with legacy DisplayPort versions is also addressed in the standards, defining fallback behaviors when newer devices connect with older equipment that may not support advanced power-saving features. This ensures backward compatibility while maximizing power efficiency when supported by all connected devices.

The compliance requirements are regularly updated to address emerging implementation challenges and to incorporate feedback from the industry ecosystem. Manufacturers seeking certification must stay current with these evolving standards to ensure their products remain compliant and interoperable across the DisplayPort ecosystem.

These standards define specific protocol requirements for Panel Replay and PSR features, including precise timing parameters for link idle states and wake latency thresholds. Manufacturers must demonstrate that their implementations can transition between power states within the specified time constraints while maintaining display integrity and user experience quality.

Compliance testing for Panel Replay involves verification of frame buffer integrity during repeated frame transmission, ensuring that no visual artifacts or corruption occurs during power-saving operations. For PSR implementations, testing focuses on the accuracy of selective update mechanisms and the ability to maintain synchronization between source and display devices during rapid state transitions.

The interoperability framework also addresses cross-vendor compatibility, requiring that DisplayPort 2.1 devices with Panel Replay and PSR capabilities function correctly regardless of the manufacturer of connected components. This includes standardized handshake protocols for negotiating power-saving features between source and sink devices.

Power consumption measurement methodologies are standardized within the compliance requirements, establishing consistent benchmarks for evaluating the effectiveness of power-saving implementations. These measurements must be performed under specified test conditions that simulate real-world usage scenarios.

VESA's Compliance Test Specification (CTS) for DisplayPort 2.1 includes dedicated test procedures for Panel Replay and PSR features, with pass/fail criteria based on both functional correctness and performance metrics. Certification requires successful completion of all mandatory tests related to these power-saving technologies.

Interoperability with legacy DisplayPort versions is also addressed in the standards, defining fallback behaviors when newer devices connect with older equipment that may not support advanced power-saving features. This ensures backward compatibility while maximizing power efficiency when supported by all connected devices.

The compliance requirements are regularly updated to address emerging implementation challenges and to incorporate feedback from the industry ecosystem. Manufacturers seeking certification must stay current with these evolving standards to ensure their products remain compliant and interoperable across the DisplayPort ecosystem.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!