DisplayPort 2.1 FRL/DP Interop: Sink Capabilities, Training States And Fallbacks

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 Evolution and Objectives

DisplayPort technology has evolved significantly since its introduction by VESA in 2006, progressing through multiple iterations to address increasing bandwidth demands and enhanced display capabilities. The evolution from DisplayPort 1.0 to the current 2.1 specification represents a strategic response to the growing requirements for higher resolution displays, faster refresh rates, and more complex multi-display configurations in both consumer and professional environments.

DisplayPort 2.1, released in October 2022, builds upon the foundation established by DisplayPort 2.0, maintaining backward compatibility while introducing critical refinements for interoperability with other standards. A key advancement in this evolution is the incorporation of the Fixed Rate Link (FRL) signaling mode alongside the traditional DisplayPort (DP) signaling, creating a hybrid architecture that enhances flexibility across different implementation scenarios.

The primary objectives of DisplayPort 2.1 focus on addressing several critical industry needs. First, it aims to support ultra-high-definition visual experiences with 8K and beyond resolution capabilities, HDR content, and high refresh rates that exceed 120Hz. This is achieved through its impressive maximum bandwidth of 80 Gbps, a substantial increase from previous generations.

Second, DisplayPort 2.1 seeks to establish seamless interoperability between DisplayPort and HDMI ecosystems, particularly through the FRL/DP interoperation capabilities. This interoperability is crucial for device manufacturers who must support multiple interface standards while minimizing implementation complexity and cost.

Third, the specification aims to enhance reliability through improved training states and fallback mechanisms. These features ensure stable connections even under challenging conditions, with the system capable of negotiating optimal performance parameters or gracefully degrading to lower performance modes when necessary.

The evolution also reflects VESA's response to emerging market trends, including the proliferation of portable devices with limited physical space for connectors, the increasing adoption of USB Type-C as a universal connector, and the growing demand for wireless display technologies. DisplayPort 2.1's Alt Mode functionality for USB Type-C represents a strategic alignment with these trends.

Looking forward, DisplayPort 2.1 establishes a foundation for future innovations in display technology, including support for advanced features like augmented reality, virtual reality, and computational displays. The specification's architecture anticipates these developments through its extensible protocol structure and forward-compatible design principles.

DisplayPort 2.1, released in October 2022, builds upon the foundation established by DisplayPort 2.0, maintaining backward compatibility while introducing critical refinements for interoperability with other standards. A key advancement in this evolution is the incorporation of the Fixed Rate Link (FRL) signaling mode alongside the traditional DisplayPort (DP) signaling, creating a hybrid architecture that enhances flexibility across different implementation scenarios.

The primary objectives of DisplayPort 2.1 focus on addressing several critical industry needs. First, it aims to support ultra-high-definition visual experiences with 8K and beyond resolution capabilities, HDR content, and high refresh rates that exceed 120Hz. This is achieved through its impressive maximum bandwidth of 80 Gbps, a substantial increase from previous generations.

Second, DisplayPort 2.1 seeks to establish seamless interoperability between DisplayPort and HDMI ecosystems, particularly through the FRL/DP interoperation capabilities. This interoperability is crucial for device manufacturers who must support multiple interface standards while minimizing implementation complexity and cost.

Third, the specification aims to enhance reliability through improved training states and fallback mechanisms. These features ensure stable connections even under challenging conditions, with the system capable of negotiating optimal performance parameters or gracefully degrading to lower performance modes when necessary.

The evolution also reflects VESA's response to emerging market trends, including the proliferation of portable devices with limited physical space for connectors, the increasing adoption of USB Type-C as a universal connector, and the growing demand for wireless display technologies. DisplayPort 2.1's Alt Mode functionality for USB Type-C represents a strategic alignment with these trends.

Looking forward, DisplayPort 2.1 establishes a foundation for future innovations in display technology, including support for advanced features like augmented reality, virtual reality, and computational displays. The specification's architecture anticipates these developments through its extensible protocol structure and forward-compatible design principles.

Market Demand Analysis for High-Speed Display Interfaces

The high-speed display interface market is experiencing unprecedented growth driven by increasing demand for higher resolution displays, faster refresh rates, and enhanced visual experiences across multiple sectors. Current market analysis indicates that the global display interface market is projected to grow significantly through 2028, with DisplayPort and HDMI technologies leading the segment.

Consumer electronics represents the largest market segment, with 4K and 8K televisions, gaming monitors, and professional displays requiring increasingly sophisticated interface solutions. The gaming industry particularly drives demand for high refresh rates (144Hz, 240Hz, and beyond) and low latency connections that only the latest interface standards can deliver.

Professional markets, including medical imaging, digital signage, and content creation, require interfaces capable of handling color-accurate, high-resolution video streams. The shift toward remote work has accelerated demand for high-quality video conferencing solutions, further expanding the market for advanced display interfaces.

The automotive sector represents an emerging growth area, with modern vehicles incorporating multiple high-resolution displays requiring robust, high-bandwidth connections. As autonomous driving technologies advance, the need for interfaces capable of handling multiple video streams simultaneously will increase substantially.

Market research indicates strong regional variations in adoption patterns. North America and Asia-Pacific lead in early adoption of cutting-edge display technologies, with Europe following closely. China has emerged as both a major consumer market and manufacturing hub for display interface technologies.

Interoperability between different standards, such as DisplayPort 2.1 FRL and traditional DP modes, has become a critical market requirement. End users increasingly expect seamless compatibility across devices, creating demand for solutions that can intelligently negotiate capabilities and training states between source and sink devices.

The market shows clear preference for backward compatibility, with consumers expecting new devices to work with existing equipment. This has positioned technologies like DisplayPort 2.1, which offers robust fallback mechanisms between different operational modes, as particularly valuable in the marketplace.

Industry surveys reveal that reliability during mode transitions ranks among the top three concerns for both consumer and professional users, highlighting the importance of well-implemented training states and fallback mechanisms in display interface technologies.

Consumer electronics represents the largest market segment, with 4K and 8K televisions, gaming monitors, and professional displays requiring increasingly sophisticated interface solutions. The gaming industry particularly drives demand for high refresh rates (144Hz, 240Hz, and beyond) and low latency connections that only the latest interface standards can deliver.

Professional markets, including medical imaging, digital signage, and content creation, require interfaces capable of handling color-accurate, high-resolution video streams. The shift toward remote work has accelerated demand for high-quality video conferencing solutions, further expanding the market for advanced display interfaces.

The automotive sector represents an emerging growth area, with modern vehicles incorporating multiple high-resolution displays requiring robust, high-bandwidth connections. As autonomous driving technologies advance, the need for interfaces capable of handling multiple video streams simultaneously will increase substantially.

Market research indicates strong regional variations in adoption patterns. North America and Asia-Pacific lead in early adoption of cutting-edge display technologies, with Europe following closely. China has emerged as both a major consumer market and manufacturing hub for display interface technologies.

Interoperability between different standards, such as DisplayPort 2.1 FRL and traditional DP modes, has become a critical market requirement. End users increasingly expect seamless compatibility across devices, creating demand for solutions that can intelligently negotiate capabilities and training states between source and sink devices.

The market shows clear preference for backward compatibility, with consumers expecting new devices to work with existing equipment. This has positioned technologies like DisplayPort 2.1, which offers robust fallback mechanisms between different operational modes, as particularly valuable in the marketplace.

Industry surveys reveal that reliability during mode transitions ranks among the top three concerns for both consumer and professional users, highlighting the importance of well-implemented training states and fallback mechanisms in display interface technologies.

Technical Challenges in FRL/DP Interoperability

The interoperability between Fixed Rate Link (FRL) and DisplayPort (DP) protocols presents significant technical challenges that must be addressed to ensure seamless connectivity across different display technologies. One fundamental challenge lies in the architectural differences between these protocols, as FRL was designed for HDMI 2.1 while DisplayPort has its own distinct signaling methodology. These differences create compatibility issues when devices need to support both standards simultaneously.

Signal integrity becomes particularly problematic at higher data rates, where the electrical characteristics of FRL and DP differ substantially. The voltage levels, pre-emphasis settings, and equalization requirements vary between protocols, making it difficult to design hardware that can effectively switch between modes without signal degradation or loss. This challenge is exacerbated when considering the backward compatibility requirements with legacy devices.

Training sequence incompatibilities represent another major hurdle. FRL and DP each employ unique link training procedures to establish optimal connections. When a sink device must support both protocols, it must correctly identify the incoming signal type and apply the appropriate training sequence. Failures in this identification process can result in unsuccessful connections or suboptimal performance, particularly at higher bandwidths where margin for error is minimal.

State machine management presents complex synchronization issues. The transition between FRL and DP states must be handled gracefully to prevent lockups or undefined behaviors. This requires sophisticated state tracking and fallback mechanisms that can detect when a connection attempt is failing and revert to a more reliable configuration without user intervention.

Clock recovery mechanisms differ significantly between the protocols, with DP using embedded clocking while FRL relies on separate clock signals. This fundamental difference requires dual-mode sinks to implement parallel clock recovery circuits, increasing design complexity and potentially introducing timing jitter when switching between modes.

Power management considerations also present challenges, as the two protocols have different requirements for maintaining link integrity during low-power states. Devices must carefully manage power transitions to ensure that neither protocol's requirements are violated, which could result in connection drops or retraining delays.

Protocol negotiation timing is particularly critical, as mismatches in expected response times between source and sink can lead to timeouts and connection failures. Implementing robust timeout handling and retry mechanisms becomes essential for reliable interoperability in real-world environments with varying cable qualities and electromagnetic interference conditions.

Signal integrity becomes particularly problematic at higher data rates, where the electrical characteristics of FRL and DP differ substantially. The voltage levels, pre-emphasis settings, and equalization requirements vary between protocols, making it difficult to design hardware that can effectively switch between modes without signal degradation or loss. This challenge is exacerbated when considering the backward compatibility requirements with legacy devices.

Training sequence incompatibilities represent another major hurdle. FRL and DP each employ unique link training procedures to establish optimal connections. When a sink device must support both protocols, it must correctly identify the incoming signal type and apply the appropriate training sequence. Failures in this identification process can result in unsuccessful connections or suboptimal performance, particularly at higher bandwidths where margin for error is minimal.

State machine management presents complex synchronization issues. The transition between FRL and DP states must be handled gracefully to prevent lockups or undefined behaviors. This requires sophisticated state tracking and fallback mechanisms that can detect when a connection attempt is failing and revert to a more reliable configuration without user intervention.

Clock recovery mechanisms differ significantly between the protocols, with DP using embedded clocking while FRL relies on separate clock signals. This fundamental difference requires dual-mode sinks to implement parallel clock recovery circuits, increasing design complexity and potentially introducing timing jitter when switching between modes.

Power management considerations also present challenges, as the two protocols have different requirements for maintaining link integrity during low-power states. Devices must carefully manage power transitions to ensure that neither protocol's requirements are violated, which could result in connection drops or retraining delays.

Protocol negotiation timing is particularly critical, as mismatches in expected response times between source and sink can lead to timeouts and connection failures. Implementing robust timeout handling and retry mechanisms becomes essential for reliable interoperability in real-world environments with varying cable qualities and electromagnetic interference conditions.

Current FRL/DP Interoperability Solutions

01 DisplayPort and HDMI interoperability capabilities

DisplayPort 2.1 includes features for interoperability with HDMI, particularly through FRL (Fixed Rate Link) technology. This allows sink devices to handle both DisplayPort and HDMI signals, providing flexibility for different display connections. The sink capabilities include detection mechanisms to identify the incoming signal type and adjust processing accordingly, enabling seamless switching between DisplayPort and HDMI modes without user intervention.- DisplayPort and HDMI interoperability capabilities: DisplayPort 2.1 includes features for interoperability with HDMI, specifically through Fixed Rate Link (FRL) mode. This interoperability allows DisplayPort sinks to communicate with HDMI sources and vice versa, enabling compatibility across different display interface standards. The sink device can advertise its capabilities to the source, including supported resolutions, color formats, and refresh rates, allowing for optimal connection configuration.

- Training states and link establishment protocols: DisplayPort 2.1 implements sophisticated training states to establish and maintain stable connections. These training sequences involve a series of steps where the source and sink devices exchange information to optimize link parameters such as voltage swing, pre-emphasis, and equalization. The training process ensures reliable data transmission at high bandwidths and includes fallback mechanisms to lower data rates if optimal connection cannot be established.

- Fallback mechanisms and adaptive link management: When optimal connection parameters cannot be established, DisplayPort 2.1 implements fallback mechanisms to ensure continued functionality. These mechanisms automatically reduce link speed, lane count, or feature set to maintain a stable connection. The adaptive link management continuously monitors connection quality and can dynamically adjust parameters in response to changing conditions, ensuring the best possible performance under varying circumstances.

- Sink capability detection and advertisement: DisplayPort 2.1 includes enhanced sink capability detection mechanisms where sink devices can advertise their supported features to source devices. This includes information about supported resolutions, color depths, refresh rates, audio formats, and other capabilities. The capability exchange occurs during initial link training and enables the source to configure the connection optimally for the specific sink device, maximizing compatibility and performance.

- Multi-stream transport and bandwidth allocation: DisplayPort 2.1 supports Multi-Stream Transport (MST) capabilities with improved bandwidth allocation for multiple display streams. This feature allows a single DisplayPort connection to drive multiple displays by dividing the available bandwidth. The sink device can report its MST capabilities, and the system can intelligently allocate bandwidth based on the requirements of each connected display. This enables flexible multi-display setups while maintaining compatibility with various display configurations.

02 Training states for link establishment

DisplayPort 2.1 implements sophisticated training states to establish optimal connections between source and sink devices. These training sequences allow devices to negotiate parameters such as link speed, lane count, and signal characteristics. The training process involves multiple states including clock recovery, channel equalization, and symbol lock, ensuring reliable high-bandwidth connections even in challenging signal environments. Failed training attempts trigger fallback mechanisms to establish connections at lower performance levels.Expand Specific Solutions03 Fallback mechanisms for compatibility

When optimal connection parameters cannot be established, DisplayPort 2.1 implements fallback mechanisms to ensure continued functionality. These fallbacks include reducing link rates, decreasing lane count, or switching to more robust signaling modes. The system progressively tries less demanding configurations until a stable connection is achieved, prioritizing connection stability over maximum performance when necessary. This ensures displays remain functional even under suboptimal connection conditions.Expand Specific Solutions04 Sink device capability detection and reporting

DisplayPort 2.1 includes enhanced capability detection mechanisms where sink devices report their supported features to source devices. This includes supported resolutions, refresh rates, color depths, and audio formats. The capability reporting uses standardized data structures that allow source devices to optimize output parameters based on sink capabilities. This bidirectional communication ensures optimal video and audio quality while preventing configuration attempts that exceed device limitations.Expand Specific Solutions05 Physical layer adaptations for FRL/DP interoperability

The physical layer of DisplayPort 2.1 includes specific adaptations to support FRL/DP interoperability. These include adjustable voltage levels, impedance matching, and connector pin assignments that maintain compatibility across different standards. The physical layer can dynamically reconfigure signal characteristics based on the detected connection type, ensuring signal integrity across different cable types and lengths. This adaptability extends to power management features that adjust based on the connected device requirements.Expand Specific Solutions

Key Industry Players in Display Interface Market

DisplayPort 2.1 FRL/DP Interop technology is currently in the growth phase of its industry lifecycle, with the market expanding as high-resolution display demands increase. Major players like Samsung Electronics, Apple, and LG Electronics are driving adoption through implementation in their premium display products. The technology is approaching maturity with established companies like Realtek Semiconductor and NXP providing chipset solutions, though interoperability challenges remain. Companies including QUALCOMM and BOE Technology are actively developing compatible solutions to address the growing ecosystem. The market is characterized by collaboration between semiconductor manufacturers and consumer electronics companies to ensure seamless integration across different display technologies and legacy systems.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered an advanced DisplayPort 2.1 implementation with particular focus on the FRL/DP interoperability challenges in high-resolution display applications. Their solution incorporates a Dynamic Link Training system that continuously adapts to changing signal conditions, particularly beneficial for mobile devices where environmental factors can fluctuate. Samsung's implementation features a comprehensive Sink Capability Discovery mechanism that not only reads standard DPCD registers but also performs advanced feature detection through proprietary extensions. For training states, Samsung employs a Parallel Processing approach that simultaneously evaluates multiple lane configurations to minimize training time. Their fallback system implements a Hierarchical Quality Reduction strategy that intelligently reduces specific visual parameters based on content type - preserving text clarity in productivity applications while maintaining color accuracy in creative workloads. Samsung has also developed an innovative Fast Recovery mechanism that can restore previous working configurations within milliseconds when transient interference occurs.

Strengths: Exceptional performance in mobile environments with changing signal conditions. Content-aware fallback strategies that preserve the most important visual aspects based on usage context. Weaknesses: Some advanced features require Samsung displays to achieve full functionality. Higher implementation complexity increases development costs and time-to-market.

Apple, Inc.

Technical Solution: Apple has developed a comprehensive DisplayPort 2.1 implementation focusing on seamless interoperability between Fixed Rate Link (FRL) and DisplayPort modes. Their solution incorporates adaptive training algorithms that dynamically optimize link parameters based on real-time signal quality assessment. Apple's implementation features an enhanced Link Training Status Channel (LTSC) that provides more granular feedback during training states, allowing for faster convergence and more reliable connections. The system includes sophisticated fallback mechanisms that can gracefully degrade from higher bandwidth modes to lower ones without user-perceptible interruptions, maintaining display continuity even when signal integrity issues are detected. Apple has also implemented advanced sink capability detection that goes beyond the standard DPCD (DisplayPort Configuration Data) reads, allowing for more optimized link establishment based on the specific capabilities of connected displays.

Strengths: Exceptional user experience with seamless mode transitions and minimal visual disruptions during fallbacks. Superior compatibility with a wide range of display devices due to comprehensive sink capability detection. Weaknesses: Proprietary extensions to the standard may limit interoperability with non-Apple ecosystem devices. Higher implementation complexity increases hardware costs.

Core Innovations in Sink Capability Detection

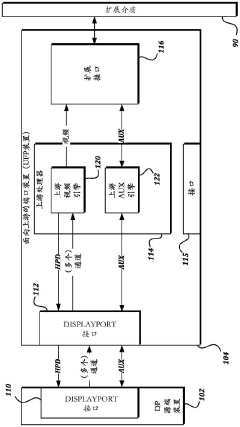

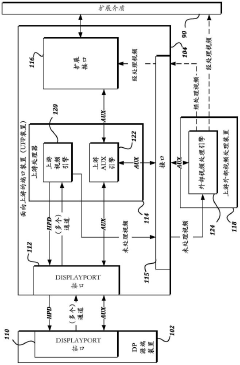

Apparatus and method for bridging video information through extended media

PatentPendingCN116521591A

Innovation

- Through the connection of upstream and downstream-facing port devices (UFP and DFP) to the extended media, link training and communication between DisplayPort source and sink devices are achieved, allowing manipulation without transmission distance and media restrictions. Video and audio content.

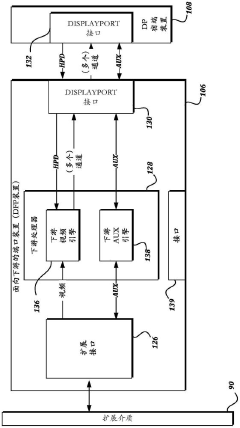

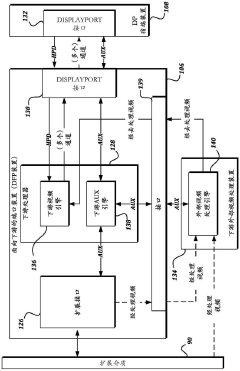

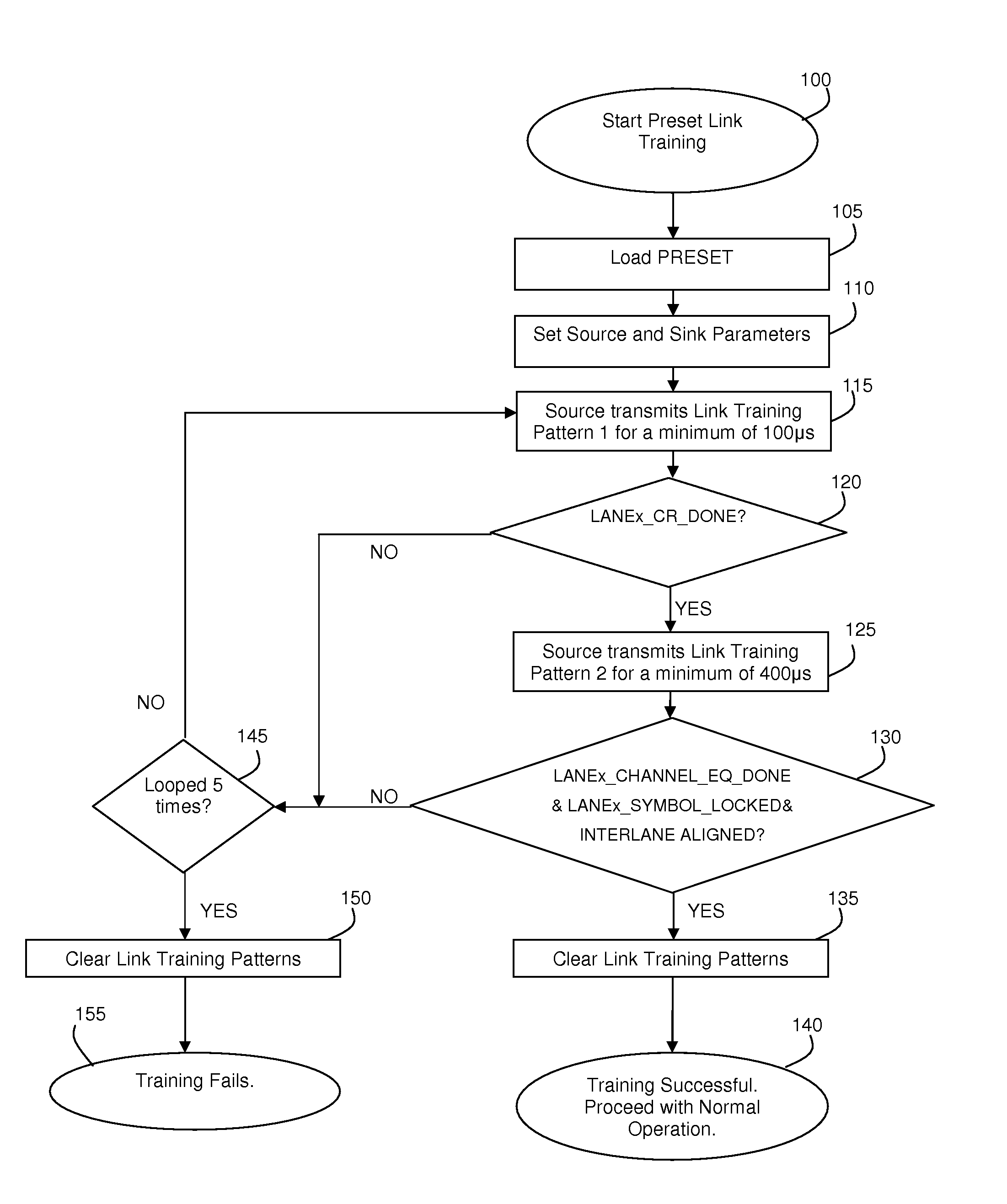

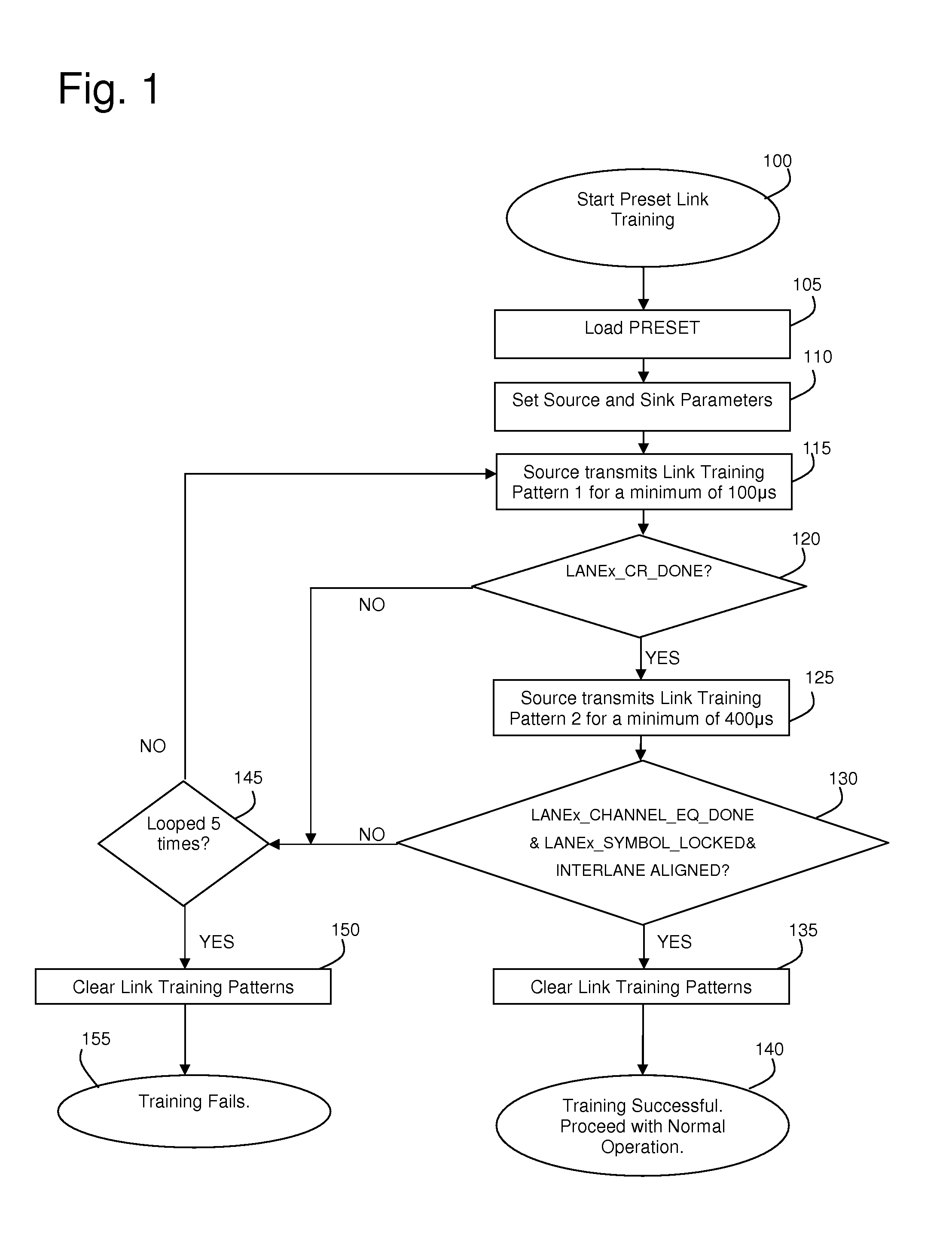

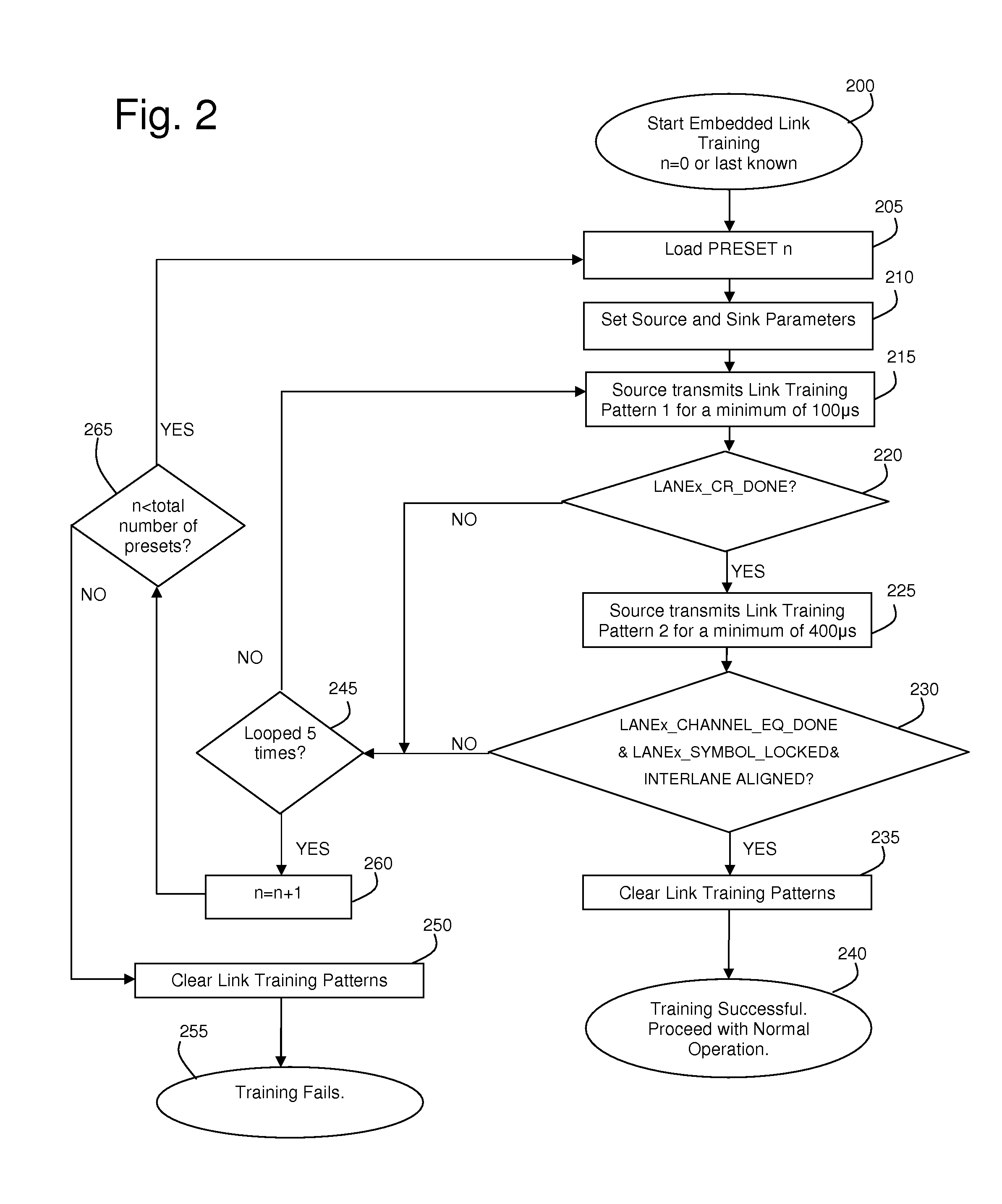

System and method for embedded displayport link training

PatentInactiveUS7853731B1

Innovation

- A preset link training method is implemented where a set of preset parameters is loaded into both the source and sink devices, and Link Training is performed using these parameters. If successful, the link is established; if not, the process repeats with different preset parameters until a successful link is achieved, minimizing power consumption and ensuring signal integrity.

Compliance Testing Methodologies

Compliance testing for DisplayPort 2.1 FRL/DP Interop requires comprehensive methodologies to ensure proper implementation of sink capabilities, training states, and fallback mechanisms. These testing procedures are critical for validating that devices can successfully negotiate connections across different operational modes.

The primary compliance testing approach involves a systematic verification of sink device capabilities through Compliance Test Patterns (CTPs). These patterns are specifically designed to stress the physical layer connections and verify proper handling of training sequences. Testing begins with capability discovery, where the source device reads the sink's Extended Display Identification Data (EDID) and DisplayID to determine supported features and modes.

Link training state verification forms a crucial component of compliance testing. Test equipment must simulate various training sequences to verify that sink devices properly respond to each state transition. This includes testing Fixed Rate Link (FRL) training, DisplayPort native mode training, and the critical interoperability transitions between these modes. Specialized test equipment captures and analyzes the sink's responses to each training state to ensure conformance with the DisplayPort 2.1 specification.

Fallback mechanism testing represents another essential aspect of compliance methodology. Test procedures must verify that when higher bandwidth modes fail, devices properly negotiate down to lower bandwidth modes rather than failing completely. This involves deliberately introducing signal degradation or errors to trigger fallback behaviors, then verifying the sink device responds according to specification by attempting alternative link configurations.

Timing analysis during mode transitions provides valuable insights into compliance. Test equipment must measure the time required for sink devices to respond to mode change requests, training sequence elements, and fallback triggers. These measurements must fall within the timing parameters specified in the DisplayPort 2.1 standard to ensure interoperability across different manufacturer implementations.

Electrical compliance testing forms the foundation of physical layer verification. This includes measuring voltage levels, transition times, jitter tolerance, and other signal integrity parameters across the full range of supported link rates. For DisplayPort 2.1, this extends to the higher bandwidth capabilities introduced in this specification version, with particular attention to the electrical requirements during mode transitions between FRL and native DisplayPort operation.

Automated compliance test software plays an increasingly important role in standardizing test procedures. These tools typically provide comprehensive test suites that exercise all aspects of the DisplayPort 2.1 specification, generating detailed reports highlighting any non-compliant behaviors. This automation ensures consistent testing methodology across different testing facilities and reduces the potential for human error in complex test sequences.

The primary compliance testing approach involves a systematic verification of sink device capabilities through Compliance Test Patterns (CTPs). These patterns are specifically designed to stress the physical layer connections and verify proper handling of training sequences. Testing begins with capability discovery, where the source device reads the sink's Extended Display Identification Data (EDID) and DisplayID to determine supported features and modes.

Link training state verification forms a crucial component of compliance testing. Test equipment must simulate various training sequences to verify that sink devices properly respond to each state transition. This includes testing Fixed Rate Link (FRL) training, DisplayPort native mode training, and the critical interoperability transitions between these modes. Specialized test equipment captures and analyzes the sink's responses to each training state to ensure conformance with the DisplayPort 2.1 specification.

Fallback mechanism testing represents another essential aspect of compliance methodology. Test procedures must verify that when higher bandwidth modes fail, devices properly negotiate down to lower bandwidth modes rather than failing completely. This involves deliberately introducing signal degradation or errors to trigger fallback behaviors, then verifying the sink device responds according to specification by attempting alternative link configurations.

Timing analysis during mode transitions provides valuable insights into compliance. Test equipment must measure the time required for sink devices to respond to mode change requests, training sequence elements, and fallback triggers. These measurements must fall within the timing parameters specified in the DisplayPort 2.1 standard to ensure interoperability across different manufacturer implementations.

Electrical compliance testing forms the foundation of physical layer verification. This includes measuring voltage levels, transition times, jitter tolerance, and other signal integrity parameters across the full range of supported link rates. For DisplayPort 2.1, this extends to the higher bandwidth capabilities introduced in this specification version, with particular attention to the electrical requirements during mode transitions between FRL and native DisplayPort operation.

Automated compliance test software plays an increasingly important role in standardizing test procedures. These tools typically provide comprehensive test suites that exercise all aspects of the DisplayPort 2.1 specification, generating detailed reports highlighting any non-compliant behaviors. This automation ensures consistent testing methodology across different testing facilities and reduces the potential for human error in complex test sequences.

Power Efficiency Considerations

Power efficiency has emerged as a critical consideration in DisplayPort 2.1 FRL/DP interoperability implementations, particularly as display resolutions and refresh rates continue to increase. The power consumption profiles of DisplayPort 2.1 vary significantly across different operational modes, with Fixed Rate Link (FRL) and traditional DisplayPort (DP) modes exhibiting distinct energy utilization patterns.

In FRL mode, power consumption scales with link rate and active lane count. Higher link rates (up to 20 Gbps per lane) enable greater bandwidth but at the cost of increased power draw. The training sequence itself consumes additional power during the establishment of stable connections, with longer training sequences resulting in higher cumulative energy expenditure.

Sink capabilities directly impact power efficiency, as more capable sinks may support advanced power management features such as selective lane activation and dynamic link rate adjustment. These capabilities allow the system to optimize power consumption based on actual bandwidth requirements rather than operating at maximum capacity continuously.

The training states in DisplayPort 2.1 FRL/DP interoperability scenarios present opportunities for power optimization. During the Clock Recovery phase, power consumption can be minimized by implementing efficient clock recovery algorithms that reduce the time required to establish symbol lock. Similarly, during the Channel Equalization phase, adaptive equalization techniques can be employed to optimize signal integrity while minimizing power draw.

Fallback mechanisms, while essential for reliability, introduce power efficiency challenges. When a high-bandwidth connection fails to establish, the system falls back to lower link rates or fewer lanes, potentially requiring multiple training attempts. Each failed training sequence represents wasted energy, making efficient fallback strategies crucial for overall power efficiency.

Modern implementations increasingly incorporate dynamic power scaling based on content requirements. For example, when displaying static content, the system can reduce refresh rates or link rates to conserve power without compromising user experience. This content-aware power management represents a significant advancement in DisplayPort 2.1 energy efficiency.

Thermal considerations also play a crucial role in power efficiency, as higher operating temperatures can increase power consumption through leakage currents. Effective thermal management strategies, including optimized component placement and improved heat dissipation, can indirectly improve power efficiency by maintaining optimal operating temperatures.

In FRL mode, power consumption scales with link rate and active lane count. Higher link rates (up to 20 Gbps per lane) enable greater bandwidth but at the cost of increased power draw. The training sequence itself consumes additional power during the establishment of stable connections, with longer training sequences resulting in higher cumulative energy expenditure.

Sink capabilities directly impact power efficiency, as more capable sinks may support advanced power management features such as selective lane activation and dynamic link rate adjustment. These capabilities allow the system to optimize power consumption based on actual bandwidth requirements rather than operating at maximum capacity continuously.

The training states in DisplayPort 2.1 FRL/DP interoperability scenarios present opportunities for power optimization. During the Clock Recovery phase, power consumption can be minimized by implementing efficient clock recovery algorithms that reduce the time required to establish symbol lock. Similarly, during the Channel Equalization phase, adaptive equalization techniques can be employed to optimize signal integrity while minimizing power draw.

Fallback mechanisms, while essential for reliability, introduce power efficiency challenges. When a high-bandwidth connection fails to establish, the system falls back to lower link rates or fewer lanes, potentially requiring multiple training attempts. Each failed training sequence represents wasted energy, making efficient fallback strategies crucial for overall power efficiency.

Modern implementations increasingly incorporate dynamic power scaling based on content requirements. For example, when displaying static content, the system can reduce refresh rates or link rates to conserve power without compromising user experience. This content-aware power management represents a significant advancement in DisplayPort 2.1 energy efficiency.

Thermal considerations also play a crucial role in power efficiency, as higher operating temperatures can increase power consumption through leakage currents. Effective thermal management strategies, including optimized component placement and improved heat dissipation, can indirectly improve power efficiency by maintaining optimal operating temperatures.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!