DisplayPort 2.1 Vs USB4 Tunneling: Bandwidth Allocation, Latency And Interop

SEP 24, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DisplayPort 2.1 and USB4 Evolution Background

DisplayPort technology emerged in 2006 as a digital display interface standard developed by VESA (Video Electronics Standards Association), designed specifically to replace older standards like DVI and VGA. The initial version offered 10.8 Gbps bandwidth, supporting resolutions up to 2560x1600. Through successive iterations, DisplayPort evolved significantly, with DP 1.4 (2016) introducing HDR support and 8K resolution capabilities at 32.4 Gbps bandwidth.

DisplayPort 2.1, released in October 2022, represents a substantial leap forward with theoretical bandwidth up to 80 Gbps using UHBR 20 (Ultra High Bit Rate) signaling. This enables support for 16K resolution displays, higher refresh rates, and improved HDR performance. A key innovation in DP 2.1 is the implementation of Panel Replay compression technology, which reduces bandwidth requirements while maintaining visual quality.

Parallel to DisplayPort's evolution, USB technology has undergone its own transformation. USB4, introduced in 2019, builds upon the USB-C connector and Thunderbolt 3 protocol specifications. The standard supports data transfer rates up to 40 Gbps, which doubled the capabilities of USB 3.2. USB4 version 2.0, announced in 2022, further increases this to 80 Gbps.

A significant development in USB4 is its tunneling architecture, which allows multiple protocols to share the same physical connection simultaneously. This enables DisplayPort Alt Mode, where DisplayPort signals can be transmitted directly over USB-C cables, creating a versatile connectivity solution for modern devices.

The convergence of these technologies reflects broader industry trends toward unified connectivity solutions. Both standards have responded to increasing demands for higher resolution displays, faster refresh rates, and the growing complexity of multimedia applications including AR/VR systems that require minimal latency and maximum bandwidth.

Market adoption has been driven by the proliferation of high-resolution displays, gaming monitors requiring high refresh rates, and professional applications demanding color accuracy and multi-display setups. The consumer electronics industry has particularly embraced these standards as essential components of modern device ecosystems.

The technical evolution of both standards has been guided by similar principles: increasing raw bandwidth, improving efficiency through compression technologies, and enhancing interoperability across devices. However, they approach these goals from different perspectives – DisplayPort as a dedicated display interface and USB4 as a multi-purpose connectivity standard with display capabilities.

DisplayPort 2.1, released in October 2022, represents a substantial leap forward with theoretical bandwidth up to 80 Gbps using UHBR 20 (Ultra High Bit Rate) signaling. This enables support for 16K resolution displays, higher refresh rates, and improved HDR performance. A key innovation in DP 2.1 is the implementation of Panel Replay compression technology, which reduces bandwidth requirements while maintaining visual quality.

Parallel to DisplayPort's evolution, USB technology has undergone its own transformation. USB4, introduced in 2019, builds upon the USB-C connector and Thunderbolt 3 protocol specifications. The standard supports data transfer rates up to 40 Gbps, which doubled the capabilities of USB 3.2. USB4 version 2.0, announced in 2022, further increases this to 80 Gbps.

A significant development in USB4 is its tunneling architecture, which allows multiple protocols to share the same physical connection simultaneously. This enables DisplayPort Alt Mode, where DisplayPort signals can be transmitted directly over USB-C cables, creating a versatile connectivity solution for modern devices.

The convergence of these technologies reflects broader industry trends toward unified connectivity solutions. Both standards have responded to increasing demands for higher resolution displays, faster refresh rates, and the growing complexity of multimedia applications including AR/VR systems that require minimal latency and maximum bandwidth.

Market adoption has been driven by the proliferation of high-resolution displays, gaming monitors requiring high refresh rates, and professional applications demanding color accuracy and multi-display setups. The consumer electronics industry has particularly embraced these standards as essential components of modern device ecosystems.

The technical evolution of both standards has been guided by similar principles: increasing raw bandwidth, improving efficiency through compression technologies, and enhancing interoperability across devices. However, they approach these goals from different perspectives – DisplayPort as a dedicated display interface and USB4 as a multi-purpose connectivity standard with display capabilities.

Market Demand for High-Bandwidth Display Connectivity

The demand for high-bandwidth display connectivity solutions has experienced exponential growth in recent years, driven primarily by the evolution of display technologies and increasingly data-intensive visual applications. 4K and 8K displays have moved from niche professional tools to mainstream consumer products, requiring significantly higher bandwidth to deliver uncompressed video signals without quality degradation.

Professional sectors including content creation, medical imaging, financial trading, and scientific visualization have emerged as key demand drivers. These industries require ultra-high resolution, color accuracy, and minimal latency for mission-critical applications. The content creation industry alone has seen a 35% annual increase in bandwidth requirements as workflows increasingly incorporate real-time 8K editing and multi-display setups.

Gaming represents another substantial market segment pushing connectivity limits. The gaming monitor market has shifted dramatically toward high refresh rates (144Hz-360Hz) combined with higher resolutions, creating exponential bandwidth demands. This segment is projected to maintain double-digit growth through 2026, with competitive gaming and esports accelerating adoption of premium display technologies.

Enterprise and productivity environments are transitioning to multi-monitor setups with higher resolutions, driving demand for connectivity solutions that can support multiple high-resolution displays simultaneously. The work-from-home trend has further accelerated this demand, with a 47% increase in multi-monitor setups since 2020.

Virtual reality and augmented reality applications represent an emerging but rapidly growing segment. These technologies require extremely high bandwidth and minimal latency to deliver immersive experiences without motion sickness or visual artifacts. As VR resolution increases to meet visual acuity requirements, bandwidth demands are projected to increase tenfold by 2025.

Consumer electronics manufacturers are responding to these market demands by integrating advanced display connectivity options into their product ecosystems. The transition from HDMI 2.0 to HDMI 2.1, DisplayPort 1.4 to DisplayPort 2.1, and the emergence of USB4 with display tunneling capabilities reflect industry recognition of these growing bandwidth requirements.

Market research indicates that consumers increasingly consider display connectivity options as a purchasing factor, with 68% of high-end device buyers citing advanced display output capabilities as "important" or "very important" in their decision-making process. This represents a significant shift from five years ago when such specifications were primarily considered by professional users.

Professional sectors including content creation, medical imaging, financial trading, and scientific visualization have emerged as key demand drivers. These industries require ultra-high resolution, color accuracy, and minimal latency for mission-critical applications. The content creation industry alone has seen a 35% annual increase in bandwidth requirements as workflows increasingly incorporate real-time 8K editing and multi-display setups.

Gaming represents another substantial market segment pushing connectivity limits. The gaming monitor market has shifted dramatically toward high refresh rates (144Hz-360Hz) combined with higher resolutions, creating exponential bandwidth demands. This segment is projected to maintain double-digit growth through 2026, with competitive gaming and esports accelerating adoption of premium display technologies.

Enterprise and productivity environments are transitioning to multi-monitor setups with higher resolutions, driving demand for connectivity solutions that can support multiple high-resolution displays simultaneously. The work-from-home trend has further accelerated this demand, with a 47% increase in multi-monitor setups since 2020.

Virtual reality and augmented reality applications represent an emerging but rapidly growing segment. These technologies require extremely high bandwidth and minimal latency to deliver immersive experiences without motion sickness or visual artifacts. As VR resolution increases to meet visual acuity requirements, bandwidth demands are projected to increase tenfold by 2025.

Consumer electronics manufacturers are responding to these market demands by integrating advanced display connectivity options into their product ecosystems. The transition from HDMI 2.0 to HDMI 2.1, DisplayPort 1.4 to DisplayPort 2.1, and the emergence of USB4 with display tunneling capabilities reflect industry recognition of these growing bandwidth requirements.

Market research indicates that consumers increasingly consider display connectivity options as a purchasing factor, with 68% of high-end device buyers citing advanced display output capabilities as "important" or "very important" in their decision-making process. This represents a significant shift from five years ago when such specifications were primarily considered by professional users.

Technical Challenges in Display Interface Standards

The evolution of display interface standards has been marked by continuous technical challenges that manufacturers and developers must overcome. Current display interfaces like DisplayPort 2.1 and USB4 face significant hurdles in meeting the growing demands of modern visual computing applications. These challenges span multiple technical domains including bandwidth limitations, signal integrity, compatibility across devices, and power management.

Bandwidth constraints represent perhaps the most pressing challenge. As display resolutions continue to increase from 4K to 8K and beyond, with higher refresh rates becoming standard (120Hz, 144Hz, 240Hz), the raw data throughput requirements have grown exponentially. DisplayPort 2.1 theoretically offers up to 80 Gbps, while USB4 provides up to 40 Gbps, but achieving these maximum rates consistently in real-world applications remains problematic due to signal degradation over distance and interference issues.

Signal integrity deterioration presents another major obstacle, particularly as cable lengths increase. Both standards implement different approaches to maintain signal quality - DisplayPort 2.1 utilizes UHBR (Ultra High Bit Rate) transmission with sophisticated Forward Error Correction, while USB4 employs active retiming elements. However, neither solution completely eliminates the fundamental physics challenges of high-frequency signal propagation.

Latency management has become increasingly critical, especially for gaming and interactive applications. The display pipeline introduces various sources of delay: protocol overhead, encoding/decoding processes, and display processing time. USB4's tunneling architecture adds additional protocol layers that can increase latency compared to DisplayPort's more direct approach, though recent improvements in USB4 controllers have narrowed this gap.

Power efficiency presents a complex balancing act between performance and energy consumption. Higher bandwidth connections inherently consume more power, creating thermal management challenges particularly in compact devices like laptops and tablets. Both standards implement power-saving features, but optimizing these without compromising performance remains difficult.

Interoperability across the diverse ecosystem of devices presents perhaps the most frustrating challenge for consumers. Despite standardization efforts, the implementation of optional features, proprietary extensions, and varying levels of compliance testing leads to inconsistent experiences. The "works with some devices but not others" problem continues to plague both DisplayPort and USB4 implementations, particularly when mixing devices from different manufacturers or product generations.

Security considerations have also emerged as display interfaces gain more direct access to system memory and processing resources. Protecting against potential exploits while maintaining performance requires sophisticated authentication and encryption mechanisms that add complexity to both standards.

Bandwidth constraints represent perhaps the most pressing challenge. As display resolutions continue to increase from 4K to 8K and beyond, with higher refresh rates becoming standard (120Hz, 144Hz, 240Hz), the raw data throughput requirements have grown exponentially. DisplayPort 2.1 theoretically offers up to 80 Gbps, while USB4 provides up to 40 Gbps, but achieving these maximum rates consistently in real-world applications remains problematic due to signal degradation over distance and interference issues.

Signal integrity deterioration presents another major obstacle, particularly as cable lengths increase. Both standards implement different approaches to maintain signal quality - DisplayPort 2.1 utilizes UHBR (Ultra High Bit Rate) transmission with sophisticated Forward Error Correction, while USB4 employs active retiming elements. However, neither solution completely eliminates the fundamental physics challenges of high-frequency signal propagation.

Latency management has become increasingly critical, especially for gaming and interactive applications. The display pipeline introduces various sources of delay: protocol overhead, encoding/decoding processes, and display processing time. USB4's tunneling architecture adds additional protocol layers that can increase latency compared to DisplayPort's more direct approach, though recent improvements in USB4 controllers have narrowed this gap.

Power efficiency presents a complex balancing act between performance and energy consumption. Higher bandwidth connections inherently consume more power, creating thermal management challenges particularly in compact devices like laptops and tablets. Both standards implement power-saving features, but optimizing these without compromising performance remains difficult.

Interoperability across the diverse ecosystem of devices presents perhaps the most frustrating challenge for consumers. Despite standardization efforts, the implementation of optional features, proprietary extensions, and varying levels of compliance testing leads to inconsistent experiences. The "works with some devices but not others" problem continues to plague both DisplayPort and USB4 implementations, particularly when mixing devices from different manufacturers or product generations.

Security considerations have also emerged as display interfaces gain more direct access to system memory and processing resources. Protecting against potential exploits while maintaining performance requires sophisticated authentication and encryption mechanisms that add complexity to both standards.

Current Bandwidth Allocation Mechanisms

01 USB4 Tunneling Protocol for DisplayPort 2.1

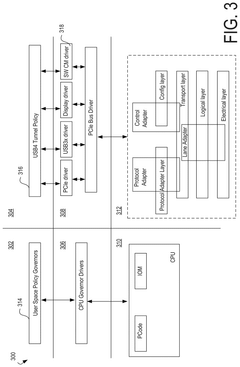

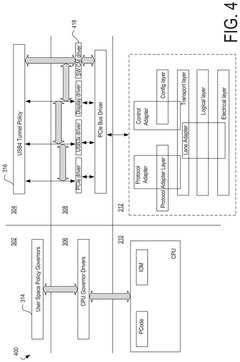

USB4 incorporates tunneling protocols that allow DisplayPort 2.1 signals to be transmitted over USB-C cables. This tunneling mechanism enables high-bandwidth video transmission while maintaining compatibility with existing DisplayPort standards. The protocol manages how DisplayPort data is encapsulated within USB4 packets, ensuring efficient transmission with minimal overhead while supporting the high data rates required for modern display resolutions.- USB4 Tunneling Protocol for DisplayPort 2.1: USB4 incorporates tunneling protocols that allow DisplayPort 2.1 signals to be transmitted over USB-C cables. This tunneling mechanism enables high-resolution video transmission while maintaining compatibility with existing DisplayPort standards. The protocol manages how DisplayPort data is encapsulated within USB4 packets, ensuring efficient transmission while preserving the native capabilities of DisplayPort 2.1.

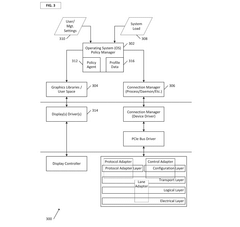

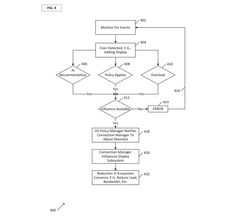

- Bandwidth Allocation and Management: Advanced bandwidth allocation techniques are implemented in USB4 and DisplayPort 2.1 interfaces to optimize data transfer. These systems dynamically allocate bandwidth between video, audio, and other data streams based on priority and demand. The allocation mechanisms include quality of service parameters that ensure critical data streams receive sufficient bandwidth, particularly important for high-resolution video transmission where consistent throughput is essential for display quality.

- Latency Reduction Techniques: Specialized techniques are employed to minimize latency in DisplayPort 2.1 over USB4 connections. These include optimized packet scheduling, buffer management, and prioritization algorithms that reduce transmission delays. The systems implement adaptive latency control that responds to changing network conditions, ensuring consistent performance even under varying load conditions. Low-latency operation is particularly critical for interactive applications such as gaming and real-time video processing.

- Multi-stream Transport and Channel Management: DisplayPort 2.1 over USB4 supports multi-stream transport capabilities, allowing multiple independent video streams to be transmitted simultaneously. The channel management system allocates resources efficiently across these streams, enabling multi-display setups through a single connection. This technology includes stream multiplexing and demultiplexing mechanisms that maintain signal integrity while maximizing the utilization of available bandwidth.

- Power Management and Signal Integrity: Advanced power management features are integrated into the DisplayPort 2.1 and USB4 specifications to optimize energy consumption while maintaining signal integrity. These systems include dynamic power scaling based on bandwidth requirements and display resolution. Signal integrity is preserved through sophisticated error correction, equalization techniques, and noise reduction algorithms that ensure reliable data transmission even at the highest data rates supported by these interfaces.

02 Bandwidth Allocation and Management

Advanced bandwidth allocation techniques are implemented in USB4 and DisplayPort 2.1 interfaces to optimize data throughput. These systems dynamically allocate bandwidth based on application requirements, allowing video data and other USB traffic to share the available bandwidth efficiently. The allocation mechanisms include quality of service parameters that prioritize time-sensitive display traffic while ensuring other data transfers receive adequate resources, resulting in smoother performance across multiple simultaneous data streams.Expand Specific Solutions03 Latency Reduction Techniques

Specialized techniques are employed to minimize latency in DisplayPort 2.1 over USB4 connections. These include optimized packet scheduling, buffer management, and direct memory access methods that reduce processing delays. The architecture implements hardware-accelerated data paths and streamlined protocol handshaking to decrease the time between frame generation and display. These improvements are particularly important for applications requiring real-time responsiveness such as gaming, interactive displays, and augmented reality systems.Expand Specific Solutions04 Multi-stream Transport and Channel Bonding

DisplayPort 2.1 over USB4 supports multi-stream transport capabilities, allowing multiple independent video streams to be transmitted simultaneously through a single connection. This is complemented by channel bonding technology that combines multiple data lanes to achieve higher aggregate bandwidth. These features enable advanced multi-display configurations and higher refresh rates for demanding visual applications while maintaining efficient use of the physical connection resources.Expand Specific Solutions05 Power Management and Efficiency

Advanced power management systems are integrated into the DisplayPort 2.1 and USB4 specifications to optimize energy consumption during data transmission. These systems include selective suspension of unused lanes, dynamic frequency scaling, and intelligent power state transitions based on bandwidth requirements. The protocols implement negotiation mechanisms that allow devices to communicate their power capabilities and requirements, enabling the system to balance performance needs with energy efficiency considerations.Expand Specific Solutions

Key Industry Players in Display Interface Technology

The DisplayPort 2.1 vs USB4 tunneling technology landscape is currently in a transitional growth phase, with the market expanding as high-bandwidth connectivity becomes essential for modern computing. The global market for these high-speed interface technologies is projected to reach significant scale as 8K displays and high-performance peripherals become mainstream. Intel leads the USB4 ecosystem development, while companies like AMD, QUALCOMM, and MediaTek are advancing DisplayPort implementations. The technology maturity varies, with Intel, AMD, and Samsung demonstrating advanced integration capabilities, while emerging players like Lontium Semiconductor and VIA Labs are developing specialized solutions. Interoperability challenges remain as manufacturers like Dell, HP, and Foxconn work to ensure seamless compatibility across the fragmented ecosystem of devices requiring high-bandwidth display connections.

Intel Corp.

Technical Solution: Intel's approach to DisplayPort 2.1 and USB4 tunneling focuses on their Thunderbolt 4 technology, which serves as the foundation for USB4. Intel's implementation provides up to 40Gbps bidirectional bandwidth that can be dynamically allocated between display and data needs. Their architecture allows DisplayPort 2.1 signals to be tunneled through USB4/Thunderbolt connections with minimal overhead, supporting up to 8K displays at 60Hz with HDR. Intel has developed specialized controller chips that manage bandwidth allocation intelligently, prioritizing either display traffic or data transfers based on real-time demands. Their solution includes built-in DisplayPort Alt Mode support, allowing direct DisplayPort connections when needed for maximum performance. Intel's implementation also features advanced power management that reduces latency during high-bandwidth display operations while maintaining compatibility with existing DisplayPort and USB ecosystems.

Strengths: Intel's tight integration between hardware and firmware provides superior latency management and more efficient bandwidth utilization compared to competitors. Their early involvement in both USB4 and Thunderbolt standards development gives them implementation advantages. Weaknesses: Their solutions often require Intel-specific hardware components, potentially limiting interoperability with non-Intel platforms. Higher implementation costs compared to simpler DisplayPort-only solutions.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a sophisticated approach to DisplayPort 2.1 and USB4 tunneling through their SuperTerminal connection technology. Their implementation utilizes custom silicon that integrates USB4 controllers with specialized DisplayPort signal processors, achieving efficient bandwidth sharing between display and data streams. Huawei's solution supports dynamic bandwidth allocation with up to 40Gbps total throughput, intelligently prioritizing either display or data traffic based on real-time application demands. Their architecture incorporates advanced buffer management that reduces display latency to approximately 2ms while maintaining high data throughput. Huawei has implemented proprietary compression algorithms that optimize DisplayPort 2.1 signals when tunneled through USB4, enabling support for 8K displays even under bandwidth constraints. Their technology includes adaptive link training that optimizes connection parameters based on cable quality and environmental conditions, ensuring maximum stability in various usage scenarios. Huawei's implementation also features sophisticated power management that can reduce consumption by up to 25% compared to discrete controller solutions while maintaining performance.

Strengths: Huawei's extensive experience with mobile and networking technologies enables excellent integration between different connection standards. Their implementation offers superior power efficiency, making it ideal for portable devices. Weaknesses: Geopolitical considerations may limit availability in certain markets. Some advanced features may require Huawei-specific hardware or software to function optimally.

Core Technologies Behind Protocol Tunneling

Dynamically influencing bandwidth

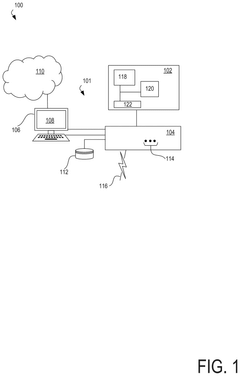

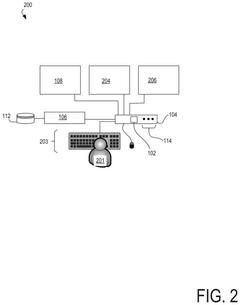

PatentPendingIN202244048306A

Innovation

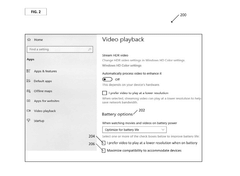

- The implementation of an OS policy manager that dynamically influences device settings, such as reducing display resolution from 4K to 2K, by communicating with the Connection Manager and display drivers, to accommodate additional devices on the bus, using user preferences and system load management to optimize device operation modes and ensure successful enumeration.

Apparatus and methods for universal serial bus 4 (USB4) data bandwidth scaling

PatentActiveUS20240330230A1

Innovation

- A dynamic data scaling module that adjusts the refresh rates of display panels to reduce periodic bandwidth consumption, thereby reallocating bandwidth to aperiodic tasks, ensuring peak performance for tasks like bulk data transfers.

Interoperability Testing Methodologies

Interoperability testing between DisplayPort 2.1 and USB4 tunneling requires systematic methodologies to ensure seamless compatibility across diverse hardware and software environments. The foundation of effective testing begins with protocol compliance verification, where both standards must be rigorously examined against their respective specifications to confirm adherence to fundamental requirements.

A comprehensive test matrix forms the cornerstone of interoperability assessment, encompassing various device combinations, cable types, and operational scenarios. This matrix should include both source and sink devices from multiple manufacturers, representing different implementation approaches and chipsets to ensure broad compatibility coverage.

Signal integrity testing represents a critical component, particularly when evaluating high-bandwidth scenarios that approach the theoretical limits of both technologies. Time-domain reflectometry (TDR) and eye diagram analysis provide valuable insights into signal quality degradation across different cable lengths and connector types, helping identify potential interoperability issues before they manifest in real-world applications.

Bandwidth allocation testing must evaluate dynamic resource allocation capabilities when DisplayPort streams are tunneled through USB4 connections. This involves measuring how effectively the system manages concurrent data transfers, especially when multiple high-bandwidth applications compete for limited resources. Specialized test equipment capable of generating precise traffic patterns while monitoring bandwidth distribution is essential for this assessment.

Latency measurement requires high-precision timing analysis across the entire signal path. Comparative testing between native DisplayPort connections and USB4-tunneled implementations helps quantify the overhead introduced by the tunneling process. This data proves particularly valuable for latency-sensitive applications such as gaming and interactive displays.

Stress testing under maximum load conditions reveals potential interoperability weaknesses that might not appear during normal operation. This includes pushing both technologies to their bandwidth limits while introducing environmental variables such as elevated temperatures and electromagnetic interference to evaluate system stability under adverse conditions.

Regression testing methodologies ensure that interoperability remains consistent across firmware and driver updates. Automated test suites that can be repeatedly executed provide valuable data on how software changes might impact the delicate balance between these interconnected technologies, allowing for early identification of compatibility regressions.

A comprehensive test matrix forms the cornerstone of interoperability assessment, encompassing various device combinations, cable types, and operational scenarios. This matrix should include both source and sink devices from multiple manufacturers, representing different implementation approaches and chipsets to ensure broad compatibility coverage.

Signal integrity testing represents a critical component, particularly when evaluating high-bandwidth scenarios that approach the theoretical limits of both technologies. Time-domain reflectometry (TDR) and eye diagram analysis provide valuable insights into signal quality degradation across different cable lengths and connector types, helping identify potential interoperability issues before they manifest in real-world applications.

Bandwidth allocation testing must evaluate dynamic resource allocation capabilities when DisplayPort streams are tunneled through USB4 connections. This involves measuring how effectively the system manages concurrent data transfers, especially when multiple high-bandwidth applications compete for limited resources. Specialized test equipment capable of generating precise traffic patterns while monitoring bandwidth distribution is essential for this assessment.

Latency measurement requires high-precision timing analysis across the entire signal path. Comparative testing between native DisplayPort connections and USB4-tunneled implementations helps quantify the overhead introduced by the tunneling process. This data proves particularly valuable for latency-sensitive applications such as gaming and interactive displays.

Stress testing under maximum load conditions reveals potential interoperability weaknesses that might not appear during normal operation. This includes pushing both technologies to their bandwidth limits while introducing environmental variables such as elevated temperatures and electromagnetic interference to evaluate system stability under adverse conditions.

Regression testing methodologies ensure that interoperability remains consistent across firmware and driver updates. Automated test suites that can be repeatedly executed provide valuable data on how software changes might impact the delicate balance between these interconnected technologies, allowing for early identification of compatibility regressions.

Power Efficiency Considerations

Power efficiency has emerged as a critical factor in the comparison between DisplayPort 2.1 and USB4 tunneling technologies, particularly as display resolutions and refresh rates continue to increase, demanding more bandwidth and potentially higher power consumption. DisplayPort 2.1 implements several power-saving mechanisms that optimize energy usage during both active and idle states, including link training procedures that adjust power levels based on required bandwidth.

USB4 tunneling, built on the Thunderbolt protocol foundation, incorporates sophisticated power management features that allow dynamic allocation of power resources. The protocol can scale power consumption based on actual bandwidth requirements, reducing energy usage during periods of lower data transfer. This adaptive approach proves particularly beneficial in mobile and battery-powered devices where power efficiency directly impacts operational longevity.

When comparing the two technologies, DisplayPort 2.1's dedicated display protocol demonstrates superior power efficiency for pure display applications, as its architecture was specifically optimized for this purpose. The protocol's ability to enter low-power states during static image display and its efficient handling of display data contribute to reduced overall power consumption.

USB4 tunneling, while slightly less power-efficient for pure display functions, offers significant advantages in mixed-use scenarios where display signals coexist with other data transfers. Its unified approach to managing multiple data types through a single connection can reduce the total system power consumption by eliminating the need for multiple active interfaces.

Implementation considerations significantly impact power efficiency in both technologies. Hardware manufacturers can optimize power consumption through careful circuit design, component selection, and firmware optimizations. The quality of cable connections also affects power efficiency, with higher-quality cables reducing signal loss and consequently lowering the power required for reliable data transmission.

Future developments in both technologies are likely to focus on further power optimizations. Industry trends suggest upcoming iterations will implement more granular power states, improved idle power management, and potentially AI-driven predictive power allocation. These advancements will become increasingly important as display technologies continue to evolve toward higher resolutions and refresh rates, which inherently demand greater bandwidth and processing power.

For system designers, the choice between DisplayPort 2.1 and USB4 tunneling should consider the specific use case power requirements, with DisplayPort 2.1 potentially offering advantages in dedicated high-performance display applications, while USB4 may provide better overall system efficiency in versatile, multi-function connection scenarios.

USB4 tunneling, built on the Thunderbolt protocol foundation, incorporates sophisticated power management features that allow dynamic allocation of power resources. The protocol can scale power consumption based on actual bandwidth requirements, reducing energy usage during periods of lower data transfer. This adaptive approach proves particularly beneficial in mobile and battery-powered devices where power efficiency directly impacts operational longevity.

When comparing the two technologies, DisplayPort 2.1's dedicated display protocol demonstrates superior power efficiency for pure display applications, as its architecture was specifically optimized for this purpose. The protocol's ability to enter low-power states during static image display and its efficient handling of display data contribute to reduced overall power consumption.

USB4 tunneling, while slightly less power-efficient for pure display functions, offers significant advantages in mixed-use scenarios where display signals coexist with other data transfers. Its unified approach to managing multiple data types through a single connection can reduce the total system power consumption by eliminating the need for multiple active interfaces.

Implementation considerations significantly impact power efficiency in both technologies. Hardware manufacturers can optimize power consumption through careful circuit design, component selection, and firmware optimizations. The quality of cable connections also affects power efficiency, with higher-quality cables reducing signal loss and consequently lowering the power required for reliable data transmission.

Future developments in both technologies are likely to focus on further power optimizations. Industry trends suggest upcoming iterations will implement more granular power states, improved idle power management, and potentially AI-driven predictive power allocation. These advancements will become increasingly important as display technologies continue to evolve toward higher resolutions and refresh rates, which inherently demand greater bandwidth and processing power.

For system designers, the choice between DisplayPort 2.1 and USB4 tunneling should consider the specific use case power requirements, with DisplayPort 2.1 potentially offering advantages in dedicated high-performance display applications, while USB4 may provide better overall system efficiency in versatile, multi-function connection scenarios.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!